#### UC Berkeley UC Berkeley Electronic Theses and Dissertations

#### Title

Enabling Full-Stack DNN Accelerator Design and Evaluation on Synthesizable Hardware

#### Permalink

https://escholarship.org/uc/item/0sp5w390

#### Author

Genc, Hasan Nazim

#### **Publication Date**

2024

Peer reviewed|Thesis/dissertation

Enabling Full-Stack DNN Accelerator Design and Evaluation on Synthesizable Hardware

By

Hasan Nazim Genc

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Krste Asanovic, Chair Yakun Sophia Shao Borivoje Nikolic Vijay Janapa Reddi

Summer 2024

Enabling Full-Stack DNN Accelerator Design and Evaluation on Synthesizable Hardware

Copyright 2024 by Hasan Nazim Genc

#### Abstract

#### Enabling Full-Stack DNN Accelerator Design and Evaluation on Synthesizable Hardware

by

Hasan Nazim Genc

#### Doctor of Philosophy in Computer Science

University of California, Berkeley

Krste Asanovic, Chair

The growing diversity of computationally demanding DNN workloads, together with the long-running decline of technology-scaling trends, has motivated the design of a great many diverse specialized hardware accelerators. While these accelerators provide significant improvements to performance and energy consumption — making the modern wave of AI innovation possible — they introduce significant challenges to computer architects, programmers, and hardware designers, due to the difficulty of (i) exploring the very broad design space they represent, (ii) translating such designs rapidly to high-quality RTL and software libraries, and (iii) evaluating such designs in realistic full-system contexts early on in the design process.

Prior work has attempted to address these difficulties by proposing new accelerator design frameworks which allow users to change only a few settings in a config file, or a few lines of a domain-specific language, from which they can rapidly generate new synthesizable hardware, or new high-level models that can guide architectural decisions. Many of these frameworks also attempt to make accelerator design more principled by *separating* the different concerns which go into accelerator design, so that each can be explored individually, and in relation to other design choices.

However, prior accelerator generators and design frameworks often lack the ability to provide users visibility into the impact that the *full* system and software stack have upon DNN accelerator performance, such as the potential for outer caches, virtual address translation mechanisms, or host CPUs to bottleneck performance if they have not been carefully tuned along with the accelerator's functional units or spatial arrays. Prior accelerator design frameworks which separate out different design concerns are also are not capable of generating high-quality RTL for *both* dense and sparse accelerator ASICs, which limits their ability to cover various modern workloads which sparsify DNN layers to improve performance or energy efficiency. This thesis presents two projects, Gemmini and Stellar, which address these difficulties. Gemmini is a DNN accelerator evaluation framework which, while generating efficient spatial arrays and accelerators, is primarily intended to help users evaluate the impact of SoC components *outside* of the accelerator itself, such as external caches or virtual address translation mechanisms, upon overall DNN accelerator performance. Stellar is another framework which provides abstractions that help users to design and explore different components of both dense and sparse accelerators, while separating out the different concerns that go into accelerator design, such as an accelerator's functionality, its dataflow, the sparse/dense data formats it supports, its load-balancing strategies, and the private memory buffers it is equipped with. Gemmini-generated dense DNN accelerators achieve 87% the performance of prior state-of-the-art accelerators such as NVDLA on image classification networks such as ResNet50, and enable insights into how minor changes to system components such as TLBs can improve end-to-end DNN performance by up to 15%. Stellar-generated accelerators achieve up to 92% the performance of hand-written accelerators, with less than 15% area overhead and power overheads on various DNN layers as low as 7%.

To my son.

## Contents

| Co       | ontents                                            | ii  |

|----------|----------------------------------------------------|-----|

| Li       | ist of Figures                                     | iv  |

| Li       | ist of Tables                                      | vii |

| 1        | Introduction                                       | 1   |

| <b>2</b> | Background: The Spatial Accelerator Design Space   | 3   |

|          | 2.1 Spatial Accelerators                           | 3   |

|          | 2.2 Dense Accelerator Generators                   | 4   |

|          | 2.3 Sparse Accelerator Generators                  | 12  |

|          | 2.4 Full-Stack, Full-System Visibility             | 16  |

|          | 2.5 Summary                                        | 16  |

| 3        | Gemmini: Full-Stack Evaluation of DNN Accelerators | 18  |

|          | 3.1 Introduction                                   | 18  |

|          | 3.2 Gemmini Generator                              | 20  |

|          | 3.3 Gemmini Evaluation                             | 38  |

|          | 3.4 Gemmini Case Studies                           | 42  |

|          | 3.5 Summary                                        | 46  |

| 4        | Stellar: Designing and Synthesizing Accelerators   | 47  |

|          | 4.1 Introduction                                   | 47  |

|          | 4.2 Specifying Accelerators in Stellar             | 49  |

|          | 4.3 Hardware Generation in Stellar                 | 57  |

|          | 4.4 Limitations                                    | 71  |

|          | 4.5 Programming Interface                          | 71  |

|          | 4.6 Evaluation                                     | 73  |

|          | 4.7 Summary                                        | 78  |

| <b>5</b> | Conclusion                                         | 79  |

|          | 5.1 Future Work                                    | 80  |

| 5.2 Lessons Learned | 81 |

|---------------------|----|

| Bibliography        | 83 |

iii

## List of Figures

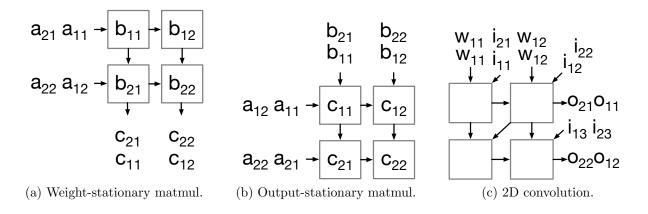

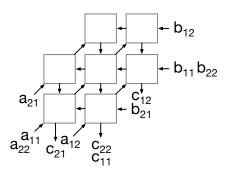

| Spatial arrays with different dataflows for matrix multiplications and two-dimension convolutions.                                                                                                                                                                                                                                          | al<br>6                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

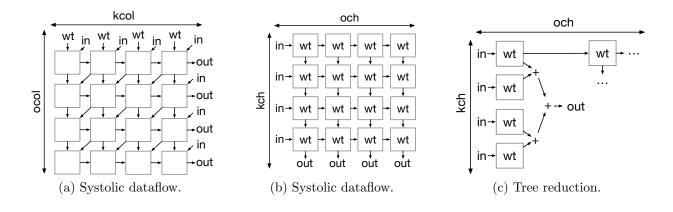

| Dataflows for convolutions specified by spatially unrolling the loop axes in Listing $2.1$ as proposed by Interstellar [07]                                                                                                                                                                                                                 | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

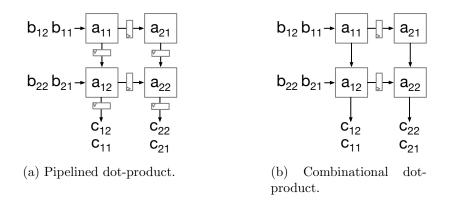

| PE underutilization caused by spatially unrolling the kch dimension from List-                                                                                                                                                                                                                                                              | 0<br>9                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

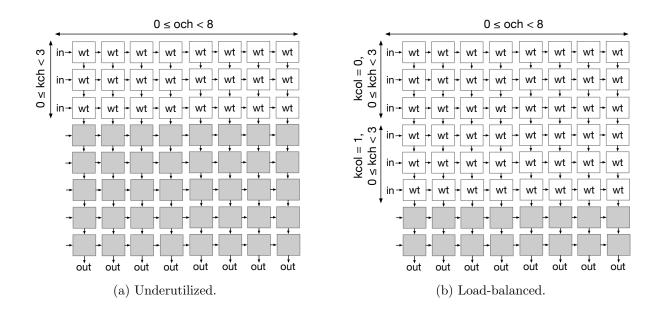

| Different pipelining strategies for spatial arrays whose dataflows keep the same elements stationary. The design in (a) pipelines the multiply-accumulates used                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| A spatial array with a hexagonal dataflow. This dataflow cannot be described                                                                                                                                                                                                                                                                | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| to a different physical spatial array dimension                                                                                                                                                                                                                                                                                             | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| distributed, small register files local to each PE                                                                                                                                                                                                                                                                                          | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

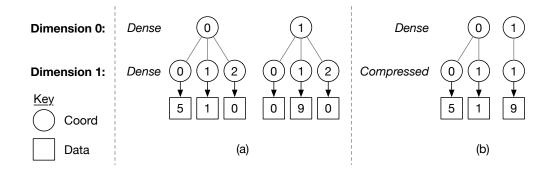

| and (b) in the CSR format.                                                                                                                                                                                                                                                                                                                  | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

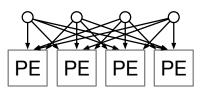

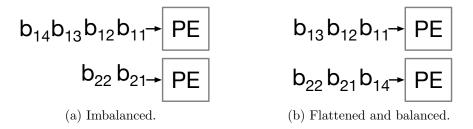

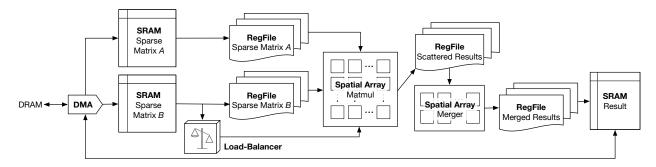

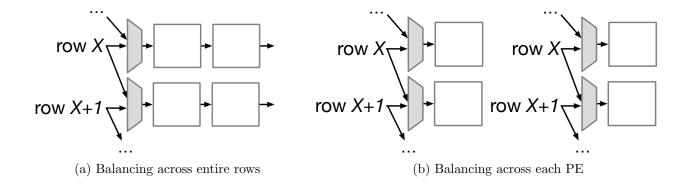

| NoCs required for different types of work-sharing and load-balancing between PEs in a spatial array whose workloads may be imbalanced. $\ldots$ $\ldots$ $\ldots$ Load-balancing a spatial array whose PEs consume an imbalanced tensor <i>B</i> by flattening and retiling the elements of <i>B</i> . In (a), each PE consumes a different | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| row of $B$ , but in (b), each PE can consume elements from any row of $B$                                                                                                                                                                                                                                                                   | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

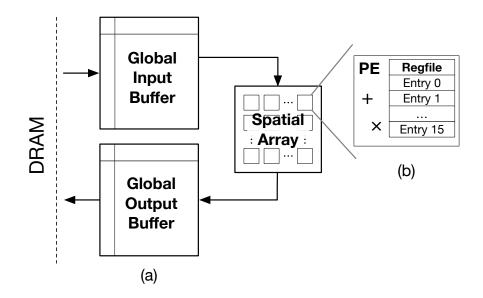

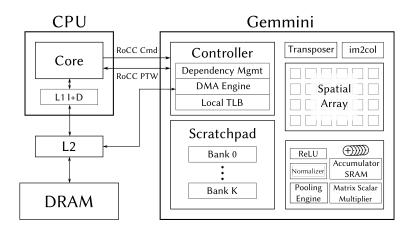

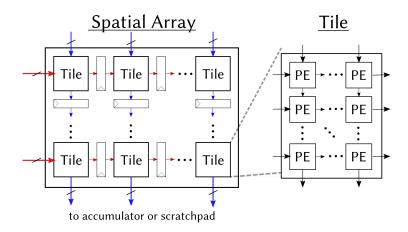

| Gemmini hardware architectural template overview                                                                                                                                                                                                                                                                                            | 19<br>20                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| between multiply-and-accumulate units.                                                                                                                                                                                                                                                                                                      | $\frac{22}{23}$                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| The order in which inputs stream into a matmul spatial array that computes                                                                                                                                                                                                                                                                  | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| The systolic transposer included in Gemmini-generated accelerators while transposing two matrices, $A$ and $B$ , back-to-back.                                                                                                                                                                                                              | 20<br>27                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                             | Dataflows for convolutions specified by spatially unrolling the loop axes in Listing 2.1, as proposed by Interstellar [97]PE underutilization caused by spatially unrolling the kch dimension from Listing 2.1, which is small for a subset of common DNN layersDifferent pipelining strategies for spatial arrays whose dataflows keep the same elements stationary. The design in (a) pipelines the multiply-accumulates used to calculate a vector dot-product |

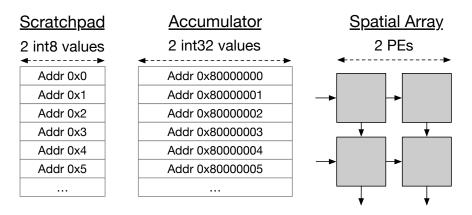

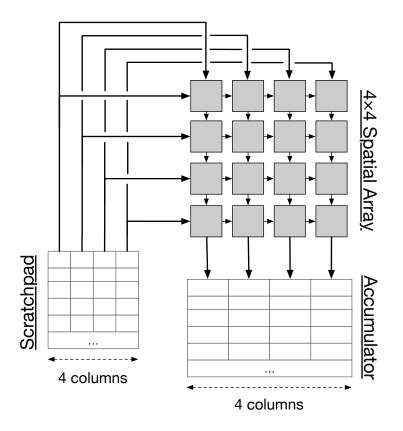

| 3.7   | Scratchpad and accumulator addressing scheme for a $2 \times 2$ spatial array                                                                                                                                       | 28              |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 3.8   | The scratchpad and accumulator columns each connect to only one or two PEs                                                                                                                                          | 200             |

| 20    | along the edges of the matmul array                                                                                                                                                                                 | 29              |

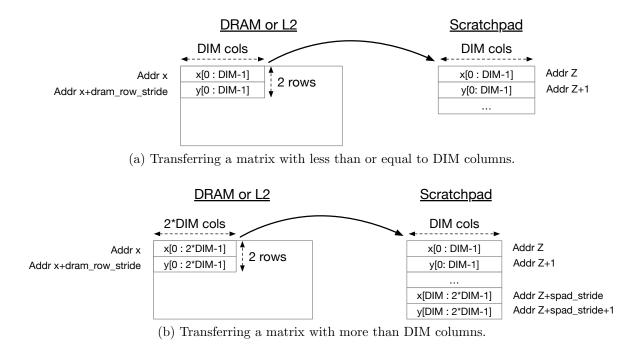

| 3.9   | How Gemmini's DMA moves matrices between DRAM or outer caches, and Gem-<br>mini's private scratchpad, based on programmer-defined strides                                                                           | 31              |

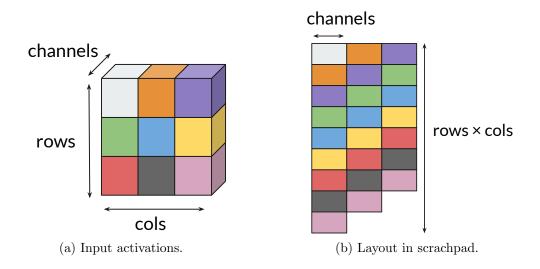

| 3.10  | Gemmini's DMA replicates input activation data in the scratchpad when the input channels are smaller than the number of scratchpad columns. When the                                                                |                 |

| 3.11  | number of input channels is larger, no such replication occurs                                                                                                                                                      | 32              |

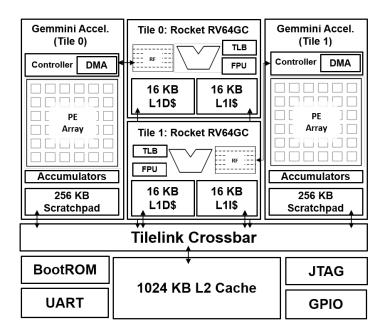

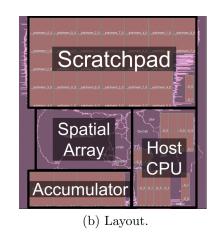

| 3.12  | accelerator                                                                                                                                                                                                         | 36              |

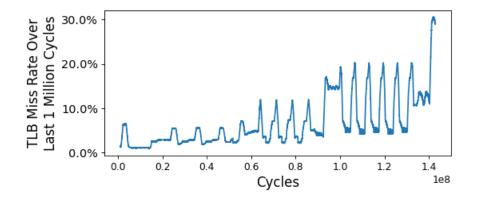

| 9 1 9 | well as a shared L2 cache and standard peripherals                                                                                                                                                                  | $\frac{38}{39}$ |

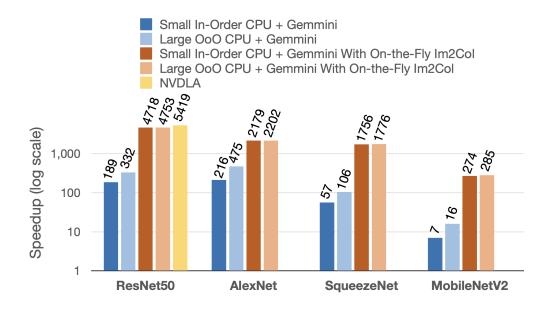

|       | Speedup compared to an in-order CPU baseline. For CNNs, im2col was performed                                                                                                                                        |                 |

|       | on either the CPU, or on the accelerator.                                                                                                                                                                           | 40              |

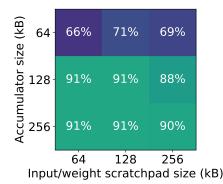

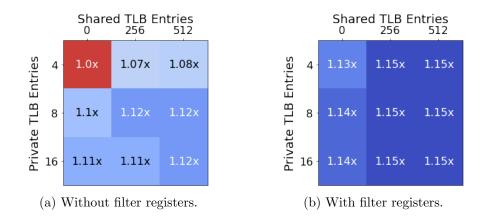

| 3.15  | The matmul utilization while performing a BERT inference on Gemmini, with different scratchpad and accumulator sizes.                                                                                               | 41              |

| 3.16  | The time spent on different operations during a I-BERT inference. For all se-                                                                                                                                       |                 |

|       | quence lengths, the total execution time is dominated by matmuls                                                                                                                                                    | 42              |

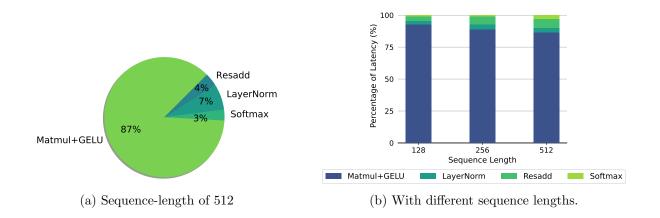

| 3.17  | Normalized performance of ResNet50 inference on Gemmini-generated accelerator                                                                                                                                       | 49              |

| 3 18  | with different private and shared TLB sizes                                                                                                                                                                         | 43              |

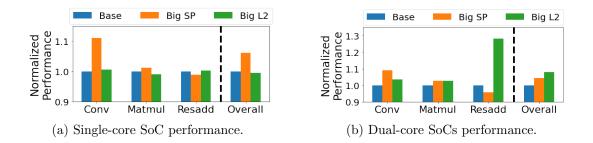

| 0.10  | the performance of the Base configuration in Table 3.5                                                                                                                                                              | 45              |

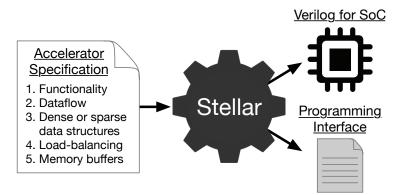

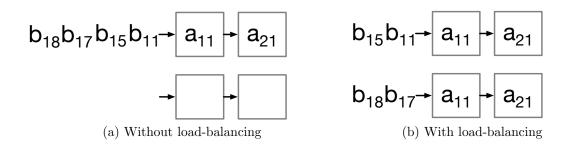

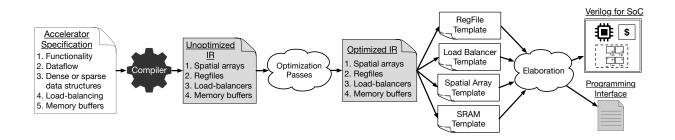

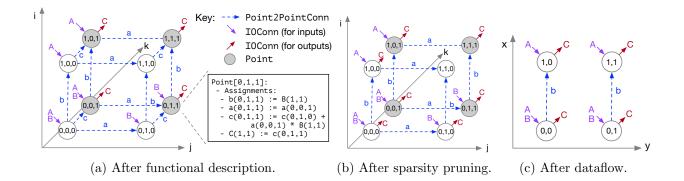

| 4.1   | A simplified illustration of Stellar's accelerator specification and hardware gen-<br>eration process, from the user-specified inputs on the left to the Verilog and<br>programming interface outputs on the right. | 48              |

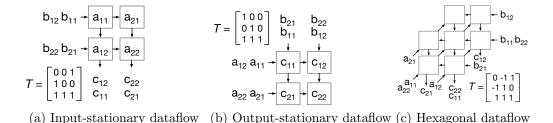

| 4.2   | Examples of space-time-transforms (each named $T$ ) and the dense matmul dataflows                                                                                                                                  | -               |

|       | that result from them                                                                                                                                                                                               | 50              |

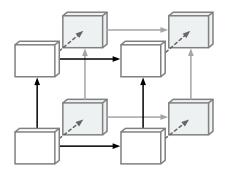

| 4.3   | A three-dimensional spatial array generated by Stellar                                                                                                                                                              | 52              |

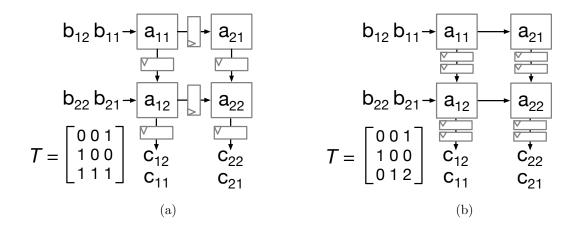

| 4.4   | Different pipelining strategies for the input-stationary matmul accelerator in Fig-                                                                                                                                 | 53              |

| 4.5   | ure 4.2a                                                                                                                                                                                                            | 53              |

| 4.0   | ified as a sparse CSR matrix.                                                                                                                                                                                       | 54              |

| 4.6   | The output-stationary matrix from Figure 4.2b when the A-matrix conforms to                                                                                                                                         | 01              |

|       | the A100 2:4 sparsity format $[64]$ .                                                                                                                                                                               | 55              |

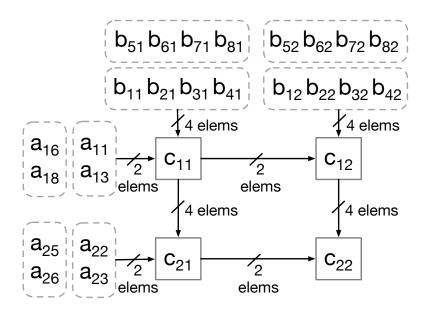

| 4.7   | The sparse matmul array from Figure 4.5, executing an imbalanced <i>B</i> -matrix with and without load-balancing.                                                                                                  | 55              |

| 4.8   | An overview of the hardware generation process for Stellar, from the initial archi-<br>tectural specification, to the unoptimized and optimized IRs, to the final Verilog                                           |                 |

|       | and programming interface outputs                                                                                                                                                                                   | 56              |

| 4.9  | Hardware architecture overview for an example sparse matrix-multiplication ac-<br>celerator. | 56 |

|------|----------------------------------------------------------------------------------------------|----|

| 4.10 |                                                                                              | 00 |

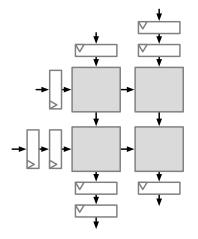

|      | description to a physically realizable two-dimensional spatial array.                        | 58 |

| 4 11 | The effect of more or less flexible load-balancing strategies on PE-to-PE commu-             | 00 |

| 1.11 | nication.                                                                                    | 60 |

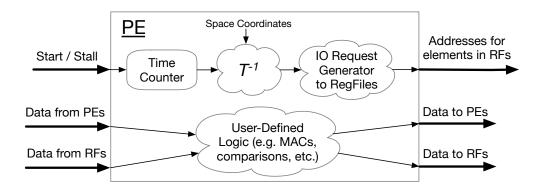

| 4.12 | The architecture for a Stellar PE.                                                           | 60 |

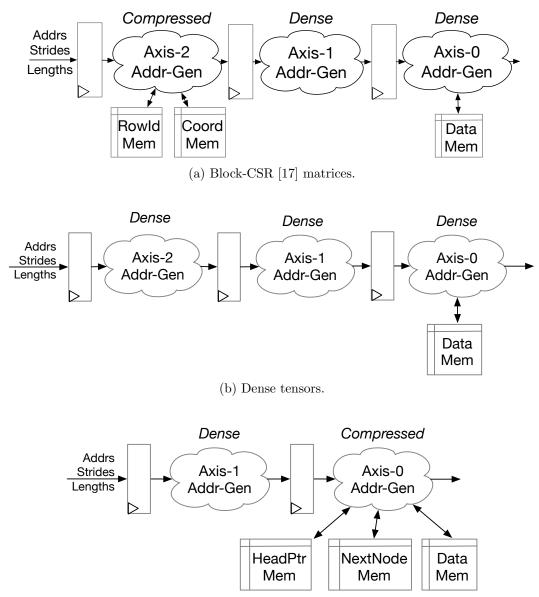

|      | The read/write pipeline stages for a private memory buffer storing tensors with              |    |

|      | different dense and sparse data formats.                                                     | 62 |

| 4.14 | Tiling two-dimensional $2 \times 2$ matrices out of an imbalanced CSR matrix                 | 63 |

| 4.15 | The read/write pipeline stages for a private memory buffer dense matrices, with              |    |

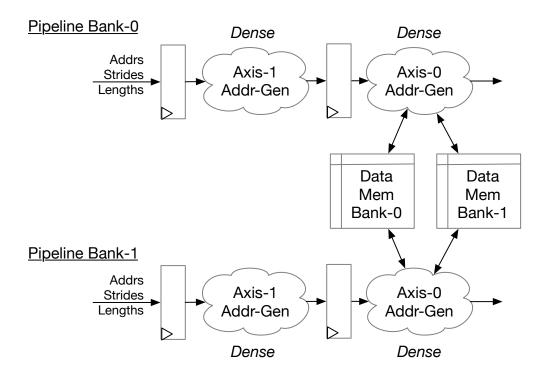

|      | two pipeline banks and two SRAM banks.                                                       | 65 |

| 4.16 | Delay registers surrounding a dense matmul array.                                            | 66 |

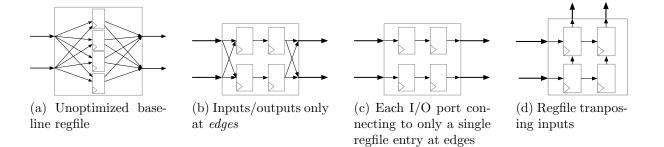

| 4.17 | Various register files generated by Stellar, with more or less aggressive optimiza-          |    |

|      | tions. All regfiles in this figure have four entries, two input ports on the left, and       |    |

|      | two output ports on the right. Observe that when input/output ports can only                 |    |

|      | connect to regfile <i>edges</i> , elements must travel through the regfile entries so they   |    |

|      | can reach the output ports.                                                                  | 67 |

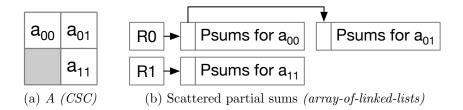

|      | Scattered partial sums generated by OuterSPACE.                                              | 70 |

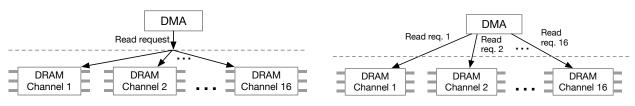

| 4.19 | DMA designs that can be generated by Stellar. Both may access the same number                |    |

|      | of DRAM channels with the same maximum DRAM bandwidth, but (b) is better                     | 70 |

| 4 90 | for pointer-chasing workloads                                                                | 70 |

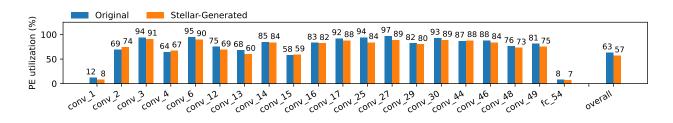

| 4.20 | celerators on ResNet50.                                                                      | 74 |

| 4 91 | Performance and power consumption of Stellar-generated and handwritten dense                 | 14 |

| 1.41 | and sparse accelerators.                                                                     | 75 |

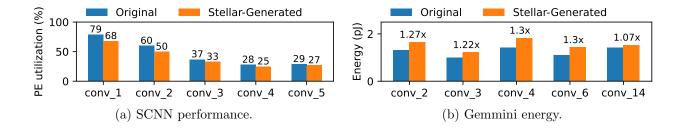

| 4.22 |                                                                                              |    |

|      | separate row of the partial matrices, and every PE only outputs a single element             |    |

|      | every cycle. In (b), the different rows of the partial matrices are flattened into a         |    |

|      | single fiber from which multiple elements are merged every cycle                             | 76 |

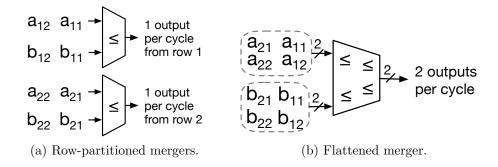

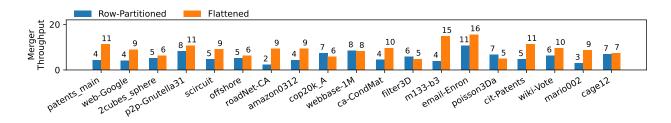

| 4.23 |                                                                                              |    |

|      | and flattened mergers when merging partial matrices with SpArch's proposed                   |    |

|      | execution order $[104]$                                                                      | 77 |

## List of Tables

| 2.1 | A comparison of DNN accelerator generators and design frameworks. * The dataflow specification is <i>implicit</i> to the functional description, and not separated. ** Various dataflow options are provided by the framework, but users cannot add their own custom dataflows. † Supports sparse memory traffic, but not sparse execution on spatial arrays. ‡ Block sparsity | 5  |  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

| 3.1 | A summary of Gemmini hardware-configurable parameters. For the integer ranges, all power-of-2 values between the maximum and minimum are permitted. All parameters are independent of each other, and the size of the total search space is                                                                                                                                    |    |  |

|     | the cross-product of all possible parameter values                                                                                                                                                                                                                                                                                                                             | 21 |  |

| 3.2 | Legal and illegal transpositions on Gemmini.                                                                                                                                                                                                                                                                                                                                   | 27 |  |

| 3.3 | DNN kernels available in Gemmini's mid-level programming interface                                                                                                                                                                                                                                                                                                             | 33 |  |

| 3.4 | Gemmini's low-level ISA, summarized.                                                                                                                                                                                                                                                                                                                                           |    |  |

| 3.5 | Gemmini SoC configurations for the system-level resource partitioning case study.                                                                                                                                                                                                                                                                                              | 44 |  |

| 4.1 | A representative subset of the commands in Stellar's RISC-V ISA. Each instruc-<br>tion has two 64-bit register arguments, <i>Rs1</i> and <i>Rs2</i> . Bits [63:20] in Rs1 are<br>currently unused.                                                                                                                                                                             | 72 |  |

| 4.2 | Area comparison between Gemmini accelerators                                                                                                                                                                                                                                                                                                                                   | 75 |  |

| 4.3 | The SparseSuite matrices we include in our evaluation.                                                                                                                                                                                                                                                                                                                         | 78 |  |

|     |                                                                                                                                                                                                                                                                                                                                                                                |    |  |

#### Acknowledgments

It may be cliche to say, but is undeniably true, that this PhD was only possible through the advice, input, and tireless help of a great many people, to whom I am deeply grateful.

First and foremost, I am grateful for the help and advice of Krste Asanović, my advisor, and Sophia Shao, who I have long regarded as a sort of unofficial advisor. Krste accepted me into his research group, and through all these years, has always been ready to provide me with invaluable feedback on everything from high-level research goals and directions to low-level hardware design problems. I would be well-content to understand anything by the end of my life as well as he understands computers. Sophia, on the other hand, joined our lab shortly after I did, as a new professor, and I cannot imagine how different this experience would have been without her there. She helped me find an angle by which to differentiate my first project, Gemmini, from the many DNN accelerators which came before and after it, allowing us to finally find a home for the work after earlier attempts had failed. Since then, she has never hesitated to help me identify research problems worth solving, ask the hard questions necessary to deliver a project to a satisfactory conclusion, or to dive deep into the cause of any hardware or software inefficiency.

I am also grateful to my other dissertation committee members, Borivoje Nikolic and Vijay Janapa Reddi. Both provided me with invaluable feedback from my quals all the way up to my final dissertation years later. Vijay, in fact, began advising me when I was only an undergrad sophomore, and I am thankful that he was willing to serve on my dissertation committee at the end when I at last graduated with my final degree.

I am also grateful to Ameer Haj-Ali, Alon Amid, Vighnesh Iyer, and Seah Kim, who were my earliest collaborators at Berkeley. One's earliest collaborators set the baseline for what one expects from future collaborators, and I was lucky that they set a high baseline for me indeed. Closer to the end of my PhD, Prashanth Ganesh and Hansung Kim also worked very closely with me, meeting the aforementioned standard easily. Without such friends and co-authors, none of my work would have gotten anywhere close to the finish line.

Furthermore, I worked with a great many other people during this process; I list some of them below, but by no means is this a complete list. John Wright, Daniel Grubb, Harrison Liew, and Colin Schmidt helped me complete my first tape-out; though the process was grueling, sitting around them (and Vighnesh) every day, all day, for several weeks on a large table in BWRC was the only thing that made it possible to squeak out a violation-free design at the end. Dima Nikiforov and Simon Guo helped me create tutorials for Gemmini; the slides they helped me make and present have since been downloaded hundreds (perhaps thousands) of times online. Jerry Zhao and Abraham Gonzalez helped me get unstuck whenever Chipyard, or hardware design in general, stumped me (I got stuck quite often). Qijing Jenny Huang and Grace Dinh knew much about topics of which I knew very little; their assistance saved me much time and effort. I am grateful also to Vikram Jain, Coleman Hooper, Josh Kang, Kris Dong, Gilbert Bernstein, Yuka Ikarashi, Charles Hong, Sehoon Kim, Amir Gholami, Ja Wattanawong, Albert Ou, Howard Mao, Kevin Anderson, Sahil Bhatia, Igor Kozachenko, Adam Izraelevitz, Brendan Sweeney, Richard Lin, Behzad Boroujerdian, Matthew Halpern, Marcelino Almeida, Yazhou Zu, Srivatsan Krishnan, Ting-Wu Rudy Chin, David Biancolin, John Koenig, and Schuyler Eldridge. If there are others whom I have neglected to mention, the fault is with my memory and not with your contributions.

I was fortunate also to have a large number of undergraduate and Master's assistants over the past six years, including Richard Yan, Avinash Nandakumar, Leena Elzeiny, Divija Hasteer, Pranav Prakash, SooHyuk Cho, Sherry Fan, and Kareem Ahmad. They made excellent contributions to my projects, and often surprised me by surpassing the work that I would have expected from a PhD student.

The assistance of the staff at SLICE (formerly ADEPT [formerly ASPIRE]) was also indispensable and I am grateful therefore to Kostadin Ilov, Ria Briggs, and Tamille Chouteau. To Kosta, I apologize for the times I forced machines to reboot.

Finally, I am grateful to my family: to my wife, Selva, who followed me across states, made the long nights and debugging marathons much easier to bear, and who reminded me that a much bigger, more important world exists outside of the IDE and waveform viewer; to my parents, Emine and Ismail, who never tired of celebrating every small success and providing encouragement when facing every big difficulty; and to my sister, Fatma, who, unlike me, had the good sense to become a real doctor. Their constant caring love and support has been the pillar on which my whole life rests.

## Chapter 1 Introduction

Modern computer architects find themselves squeezed from both ends: as DNN (deep neural network) workloads continue to place ever-higher compute and memory capacity demands on their underlying hardware, the transistor-scaling laws which traditionally made such hardware faster, smaller, and more efficient have gradually plateaued. The pressing need to accelerate such applications despite the (partial) demise of Moore's Law and other technology-scaling trends has motivated architects to search for optimizations further up the hardware-software-system stack: through microarchitectural innovations; through more careful scheduling or partitioning of DNN operations across multiple functional units, accelerators, or independent chips [43]; or through the *co-design* of separate hardware and software components so that neither imposes unnecessary inefficiencies on the other.

Such strategies have succeeded in accelerating DNN workloads, not only in academia, but also in commercial products [64]. However, these techniques typically require an increase in the complexity of both hardware and software designs. For example, simple systolic arrays may need to be made more reconfigurable [25]; balanced cache-hierarchies may need to become *im*balanced with each cache independently tuned for a different tensor [58]; sophisticated load-balancing techniques may necessitate expensive NoCs (networks-on-chip) to cope with unevenly-distributed workloads; or software schedules may become so complicated that new programming languages are needed for programmers to easily represent them across different accelerators [36].

The complexity and diversity these solutions impose spans across the hardware-softwaresystem stack. The immense diversity of DNN models and software workloads is matched by an equal variety of co-designed specialized hardware accelerators. A single accelerator may need to run multiple workloads simultaneously, or a single DNN workload may need multiple accelerators for different operations that it executes — in either case, the exact partitioning of resources among competing hardware and software components, and the interactions across different layers of the stack can cause subtle and difficult-to-diagnose bottlenecks and unexpected inefficiencies.

To maintain high architect and engineer productivity in the face of this complexity, new tools are needed: to design and explore diverse accelerator solutions, and to evaluate their performance and efficiency once they've been integrated into a full-system, full-stack environment. This work describes two such tools, *Gemmini* [22] and *Stellar*, which enable developers to (i) rapidly explore accelerator designs for DNN (and other) workloads, (ii) automatically generate high-quality RTL for complete, programmable SoCs containing their accelerators, and (iii) evaluate how their accelerators run on real-world end-to-end workloads, when interacting with both external hardware on the SoC and with the higher-level software stack.

Gemmini is a DNN accelerator generator, which includes a flexible programming stack and various counters and profilers which are designed to evaluate the impact of SoC components *outside* of the accelerator itself, such as external caches or virtual address translation mechanisms, upon overall DNN accelerator performance. The accelerator generator, written in Chisel [3], primarily targets dense CNN and transformer inference workloads, although it also includes support for certain other applications such as DNN training. Gemmini covers a wide design-space of dense DNN accelerator designs, with different spatial arrays, integer or floating-point datatypes, dataflows, and memory-hierarchies, and generates RTL for them which achieves real-time performance on real-world workloads.

Stellar, on the other hand, is designed to cover a wider space of accelerator designs for both dense and sparse workloads. Stellar introduces abstractions that allow users to separate out the different concerns that go into accelerator design: the *functionality* of an accelerator, its *dataflow*, the dense or sparse *data formats* it supports, and its *load-balancing* strategies. Once users specify their accelerators using these abstractions, Stellar generates high-quality RTL which achieves comparable performance and area efficiency to handwritten Verilog designs from prior work.

Together, the two works together enable architects to more quickly design, generate, and evaluate novel accelerators in a full-system, full-stack context. Chapter 2 describes prior, related work and provides further background on accelerator design and accelerator generators. Chapter 3 provides an in-depth description of Gemmini, as well as case studies showing how it can be used to derive interesting insights into how "full-system components" affect DNN accelerator performance. Chapter 4 introduces Stellar, describes how its frontend enables architects to quickly design and explore accelerators, and how it then generates highquality RTL based on users' frontend descriptions. Finally, Chapter 5 concludes the thesis and describes future research opportunities building on the work described here.

### Chapter 2

# **Background:** The Spatial Accelerator Design Space

The growing diversity of DNN workloads has spurred the development of an equally wide variety of specialized hardware accelerators, typically incorporating highly-parallel "spatial arrays" which are responsible for executing most arithmetic operations. To expedite the creation of so many accelerators, prior work has proposed a number of automated accelerator generators, which allow users to co-design or tune their hardware and software workloads at higher levels of abstractions and then generate high-fidelity models or high-quality RTL, as opposed to having users write new ad-hoc RTL by hand for every new accelerator design point. However, prior accelerator generators either fail to provide insight into the impact that all the different components of the hardware-software-system stack have upon accelerator performance, or they fail to generate actual synthesizable RTL for the full design space of sparse and dense DNN workloads — limitations which are addressed by Gemmini [22] and Stellar.

This chapter describes spatial accelerators from prior work (Section 2.1), as well as highlevel generators and frameworks for both dense (Section 2.2) and sparse (Section 2.3) accelerator design. Section 2.4 describes how prior accelerator generators, for either sparse or dense workloads, provided only limited insight into how the *full* hardware/software stack determines overall accelerator performance and efficiency. Finally, Section 2.5 describes how our work addresses these limitations. Table 2.1 summarizes how our work compares to prior accelerator generators and design frameworks.

#### 2.1 Spatial Accelerators

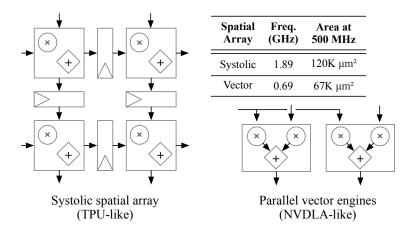

Researchers have proposed a large variety of novel DNN accelerators with different performance and energy-efficiency targets for different applications across a diverse set of deployment scenarios [9, 18, 60, 86]. At the architecture level, different DNN accelerators exploit different reuse patterns to build specialized memory hierarchies [98] and interconnect networks [48] to improve performance and energy efficiency. Most existing hardware DNN architectures are largely spatial, where parallel execution units are laid out spatially either in a systolic fashion, as in the case of the TPU, or in parallel vector units like Brainwave [21] and NVDLA [80]. Many exploit either structured or unstructured sparsity in their workloads (typically imposed during or after training at a small cost to accuracy) in order to achieve higher performance or energy efficiency [14, 15, 31, 64, 71, 67].

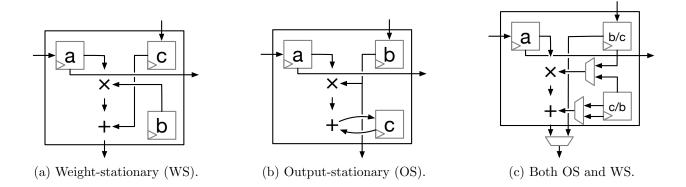

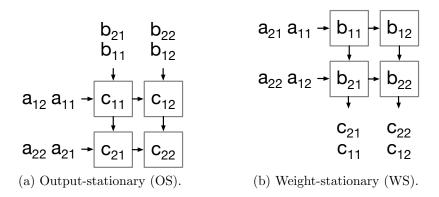

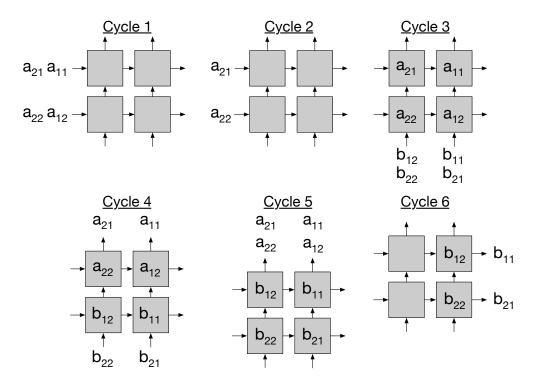

The design space for dense accelerators is well understood as they typically differ in the dataflows they support (which may be fixed or runtime-configurable), the quantized or unquantized datatypes they operate on, the functional operations they can perform (e.g., ReLU, GeLU, or other activation functions for more recent DNNs), or in their resource constraints, e.g. for small accelerators targeting low-power edge devices or for high-performance accelerators located in the cloud.

Sparse accelerators differ in even more ways, due to the wide variety of sparsity distributions and the corresponding sparse data formats in sparse workloads. Some sparse accelerators are designed for extremely sparse workloads, where far fewer than 1% of elements are non-zeros [66, 82, 104, 102]. Conversely, accelerators optimized for sparse DNNs [68, 64, 72] target matrix densities ranging from 30% to 70%. The vast range of sparsity levels necessitates the adoption of distinct sparse data formats and hardware designs, exposing a substantial design space.

As a result, existing accelerator designs generally differ from each other in *multiple* ways. For example, recent sparse accelerator proposals commonly propose not only new hardware dataflows but also new sparse formats and load-balancing strategies [82]. This inherent diversity complicates the process of comparing different accelerators, making it challenging to discern *which* feature contributes to specific improvements or drawbacks. However, such nuanced comparisons are crucial for architects, providing insights into the key principles underlying each design and guiding the selection of optimal solutions for specific workloads.

Furthermore, although spatial arrays often attract a disproportionate amount of interest from hardware designers, they sit within a wider SoC and hardware/software stack, where components outside of the spatial arrays themselves may interact in unexpected ways to influence workload performance and efficiency. For example, cache and memory hierarchies, host CPUs, page-table walkers, and even operating system interrupt and prioritization schemes can impose delays which prevent the spatial accelerator from achieving high utilizations. Some prior work has attempted to address these sources of inefficiency from "external" components [35, 27, 57], but tools that provide users with visibility into how all these components interact holistically have traditionally not been available for DNN accelerator designers.

#### 2.2 Dense Accelerator Generators

To help meet the ever-growing demand for custom dense spatial accelerator designs, prior efforts have developed hardware-generation frameworks that systematically enumerate the dense design space. These frameworks allow designs to be expressed along orthogonal design

| A Solitation of the second of |                      |                             |      |      | Dense    | 1000 | TIMINOMOLING |        |        | 2               | ~ Las            |   |      |    |                     |          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------------|------|------|----------|------|--------------|--------|--------|-----------------|------------------|---|------|----|---------------------|----------|

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      |                             |      |      |          |      |              | ×      | JONE   |                 |                  |   |      |    |                     |          |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      |                             | NO Y | A ST | AL'S COL |      | T            | No the | NIT WE | <sup>r</sup> d? | Jois and a start |   | -{}- | 12 | ALITATION OF STREET | tellars. |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                      |                             | >    | >    | ×        |      | ×            | >      |        | >               | >                |   |      |    |                     | >        |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                      | Dataflow                    | >    | >    | ×        | ×    | >            | >      | >      | >               | >                | > |      | *  | **                  | >        |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Design<br>Parameters | Sparse Data<br>Structures   | ×    | ×    |          |      | ×            | ×      | ×      | >               | >                | > |      | ×  | ×                   | >        |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                      | Load-<br>Balancing          | ×    | >    | ×        | ×    | ×            | ×      | ×      | ×               | >                | × | >    | ×  | ×                   | >        |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      | Private Mem-<br>ory Buffers | >    | >    | >        | >    | >            | ×      | >      | >               | >                | > |      | >  | >                   | >        |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      | Datatypes                   |      | ×    | >        | ×    | ×            | ×      | >      | ×               | ×                | × |      |    | >                   | >        |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Hardware             | Simulators                  | ×    | ×    | >        | >    | ×            | ×      | ×      | >               | >                | > |      | ×  | ×                   | ×        |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Outputs              | RTL                         | >    | >    | >        | >    | >            | >      | >      | ×               | ×                | × |      |    | >                   | >        |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Programming          | Application-<br>Level       | >    | >    | >        | >    | ×            | >      | >      | ×               | ×                | × |      | >  | >                   | >        |