## **UCLA**

## **UCLA Electronic Theses and Dissertations**

#### **Title**

Cross-Layer Approaches for Monitoring, Margining and Mitigation of Circuit Variability

#### **Permalink**

https://escholarship.org/uc/item/0tq9b8mt

#### **Author**

Lai, Liangzhen

## **Publication Date**

2015

Peer reviewed|Thesis/dissertation

## University of California

Los Angeles

# Cross-Layer Approaches for Monitoring, Margining and Mitigation of Circuit Variability

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical Engineering

by

Liangzhen Lai

#### Abstract of the Dissertation

# Cross-Layer Approaches for Monitoring, Margining and Mitigation of Circuit Variability

by

### Liangzhen Lai

Doctor of Philosophy in Electrical Engineering University of California, Los Angeles, 2015 Professor Puneet Gupta, Chair

With technology scaling, circuit performance has become more sensitive to various sources of variability, including manufacturing variations, ambient fluctuations, and circuit wear-out. These increased variations have created new challenges for conventional hardware guard-banding, as the additional design margin diminishes the benefits of technology scaling. This dissertation aims at reducing total system design margin with cross-layer approaches on monitoring, margining and mitigation of circuit variability.

Since hardware and software adaptation can be used to reduce design margin with the exposed hardware variability provided by hardware monitors, we start by proposing two different types of performance monitors that can achieve better monitoring accuracy and smaller monitoring overhead. We also demonstrate the use of these performance monitors in system adaptation with our end-to-end implementation of software testbeds.

We also study the dynamic variations and reliability margining problem in presence of monitor-and-actuate adaptation and emerging system contexts. In a system with monitor-and-actuate adaptation, dynamic variations require extra margin for monitor and actuate latencies. We analyze and study the margining problem considering different choices of the monitor and actuator types. System reliability margining strategies are also proposed for circuits in the "dark silicon" era, where the low-level design margin should consider the

contexts of high-level power/thermal constraints.

Last, we propose a clock gating methodology to mitigate the aging induced clock skew, which is difficult to monitor and resolve through adaptation. For certain phenomena and variation sources, for example, soft error rates at different location/altitude, we also propose system/cloud-based monitors. An emulation platform is built to study the impacts of dynamic power management schemes on system reliability.

The dissertation of Liangzhen Lai is approved.

Milos Ercegovac

Sudhakar Pamarti

Mani Srivastava

Puneet Gupta, Committee Chair

University of California, Los Angeles 2015

To mine.

# TABLE OF CONTENTS

| 1 | Intr | oducti       | on                                                                 | 1  |

|---|------|--------------|--------------------------------------------------------------------|----|

|   | 1.1  | Propos       | sed Margin Reduction Approaches                                    | 2  |

|   |      | 1.1.1        | Accurate and Inexpensive Monitoring for Variability-Aware System . | 3  |

|   |      | 1.1.2        | Margining for Emerging Systems                                     | 4  |

|   |      | 1.1.3        | Reliability Mitigation                                             | 5  |

|   | 1.2  | Thesis       | Outline                                                            | 6  |

| 2 | DD   | $RO~{ m Re}$ | eplica Monitor                                                     | 7  |

|   | 2.1  | DDRC         | Motivation and Overview                                            | 7  |

|   | 2.2  | Path S       | Sensitivity Extraction and Clustering                              | 8  |

|   | 2.3  | DDRC         | O Synthesis                                                        | 9  |

|   |      | 2.3.1        | Gate Module                                                        | 9  |

|   |      | 2.3.2        | ILP-based Synthesis                                                | 11 |

|   | 2.4  | Delay        | Estimation                                                         | 11 |

|   |      | 2.4.1        | Path-based Estimation                                              | 11 |

|   |      | 2.4.2        | Cluster-based Estimation                                           | 12 |

|   | 2.5  | Simula       | ation and Silicon Result Highlights                                | 12 |

|   | 2.6  | RedCo        | oper: A Testbed for Variability-aware System                       | 14 |

|   |      | 2.6.1        | Variability-Aware Software Duty-Cycling                            | 14 |

|   |      | 2.6.2        | Testbed Implementation and System Demonstration                    | 15 |

| 3 | Slac | ckProb       | e In Situ Monitoring Methodology                                   | 21 |

| 3.1 | SlackI  | Probe Introduction                        | 21 |

|-----|---------|-------------------------------------------|----|

| 3.2 | Slack I | Probe Overview                            | 23 |

|     | 3.2.1   | Monitor Working Principle                 | 23 |

|     | 3.2.2   | Monitor Insertion Flow                    | 24 |

|     | 3.2.3   | Possible Applications of the Monitors     | 25 |

| 3.3 | Path S  | Selection and Graph Reduction             | 26 |

|     | 3.3.1   | Path Selection Criteria                   | 26 |

|     | 3.3.2   | Circuit Graph Reduction                   | 28 |

| 3.4 | Monit   | or Location Selection                     | 28 |

|     | 3.4.1   | Monitor Coverage and Delay Margin         | 29 |

|     | 3.4.2   | Problem Formulation                       | 31 |

|     | 3.4.3   | Problem Conversion                        | 32 |

|     | 3.4.4   | Problem Solution                          | 34 |

| 3.5 | Monit   | or Cost Metrics and Comparison Analysis   | 35 |

|     | 3.5.1   | Monitor Power Cost                        | 35 |

|     | 3.5.2   | Layout Interference Cost                  | 35 |

|     | 3.5.3   | Implementation Flow Comparison            | 36 |

|     | 3.5.4   | Monitoring Efficiency and Observability   | 37 |

|     | 3.5.5   | Clock Matching                            | 40 |

|     | 3.5.6   | Overall Monitor Insertion Cost Function   | 40 |

| 3.6 | Exper   | imental Results                           | 42 |

|     | 3.6.1   | Experiment Setup                          | 42 |

|     | 362     | Results on Different Processor Renchmarks | 49 |

|              |       | 3.6.3   | Impact of Opportunism Window                                  | 43 |

|--------------|-------|---------|---------------------------------------------------------------|----|

|              |       | 3.6.4   | Results on Different Monitor Delay Margin                     | 43 |

|              |       | 3.6.5   | Extrapolation for Low Voltage Scenarios                       | 45 |

|              |       | 3.6.6   | Monitoring Efficiency and Observability                       | 47 |

|              |       | 3.6.7   | Practical and Implementation Considerations                   | 49 |

|              | 3.7   | Slack P | Probe Conclusions                                             | 53 |

| 4            | Sys   | tem-le  | vel Dynamic Variation Margining in Presence of Monitoring and |    |

| $\mathbf{A}$ | ctuat | ion .   |                                                               | 55 |

|              | 4.1   | Chapt   | er Introduction                                               | 55 |

|              | 4.2   | System  | m Margining Strategy                                          | 56 |

|              |       | 4.2.1   | Margin Breakdown                                              | 56 |

|              |       | 4.2.2   | System Margin Analysis                                        | 57 |

|              | 4.3   | Case S  | Study Experiments                                             | 59 |

|              |       | 4.3.1   | Dynamic Variation Sources                                     | 59 |

|              |       | 4.3.2   | Case Studies for Temperature Variations                       | 60 |

|              |       | 4.3.3   | System Design Implication                                     | 62 |

|              | 4.4   | Chapt   | er Conclusion                                                 | 64 |

| 5            | Har   | dware   | Reliability Margining for the Dark Silicon Era                | 65 |

|              | 5.1   | Chapt   | er Introduction                                               | 65 |

|              | 5.2   | Chapt   | er Background                                                 | 67 |

|              |       | 5.2.1   | EM Modeling                                                   | 68 |

|              |       | 5.2.2   | BTI Modeling                                                  | 69 |

|              |       | 5.2.3   | Margining for EM and BTI                                      | 69 |

|   | 5.3 | Power          | , Thermal and Accumulation Models          | 70 |

|---|-----|----------------|--------------------------------------------|----|

|   |     | 5.3.1          | Accumulation Model                         | 70 |

|   |     | 5.3.2          | Power and Thermal Model                    | 73 |

|   | 5.4 | Reliab         | oility Margining with Power Constraints    | 74 |

|   |     | 5.4.1          | Management Policy and Power Constraints    | 75 |

|   |     | 5.4.2          | Problem Formulation                        | 75 |

|   | 5.5 | Reliab         | oility Margining with Thermal Constraints  | 76 |

|   |     | 5.5.1          | Interpreting the Thermal Constraints       | 76 |

|   |     | 5.5.2          | Formulation                                | 77 |

|   | 5.6 | Exper          | imental Results and Discussion             | 78 |

|   |     | 5.6.1          | Experiment Setup                           | 78 |

|   |     | 5.6.2          | EM Results                                 | 79 |

|   |     | 5.6.3          | BTI Results                                | 82 |

|   |     | 5.6.4          | Pessimism in Our Approach                  | 82 |

|   | 5.7 | Chapt          | er Conclusion                              | 84 |

| 6 | BT. | $I	ext{-}Gate$ | r Aging Resilient Clock Gating Methodology | 85 |

|   | 6.1 | BTI-C          | Gater Introduction                         | 85 |

|   | 6.2 | Effects        | s of N/PBTI on Clock Distribution Network  | 86 |

|   |     | 6.2.1          | N/PBTI Mechanism and Modeling              | 87 |

|   |     | 6.2.2          | N/PBTI on Clock Path Delay                 | 88 |

|   | 6.3 | N/PB           | TI-induced Clock Skew under Clock Gating   | 88 |

|   |     | 6.3.1          | Clock Gating Use Cases                     | 89 |

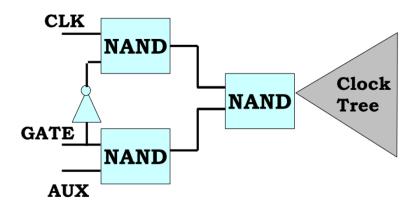

|   |     | 6.3.2          | Clock Gating Implementation with ICG Cell  | 90 |

|    |     | 0.3.3  | Clock Skew Induced by N/PBII                                | 91  |

|----|-----|--------|-------------------------------------------------------------|-----|

|    |     | 6.3.4  | Clock Uncertainty and Design Margining                      | 93  |

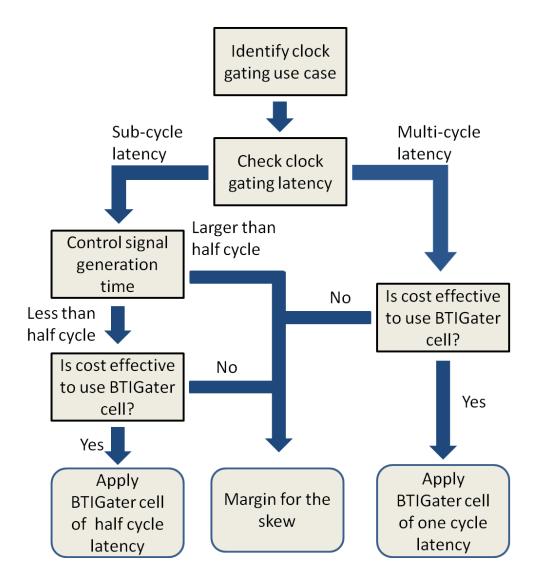

|    | 6.4 | N/PB   | TI-Resilient Clock Gating Methodology                       | 94  |

|    |     | 6.4.1  | Clock Gating Latency                                        | 95  |

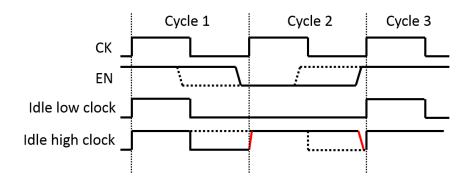

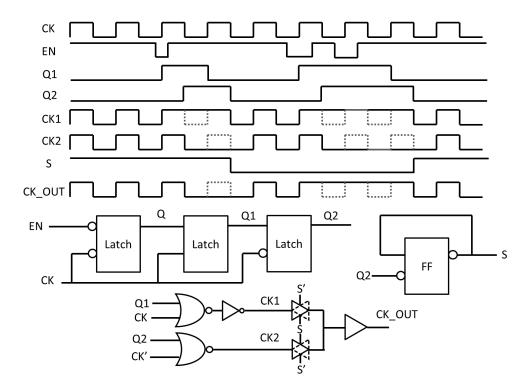

|    |     | 6.4.2  | Proposed BTI-Gater Cell of Half Cycle Latency               | 96  |

|    |     | 6.4.3  | Proposed BTI-Gater Cell of One Cycle Latency                | 97  |

|    |     | 6.4.4  | Mitigation Methodology                                      | 98  |

|    |     | 6.4.5  | Software Sleep Scheduling Techniques                        | 96  |

|    | 6.5 | Experi | imental Results                                             | 101 |

|    |     | 6.5.1  | Experiment Setup                                            | 103 |

|    |     | 6.5.2  | N/PBTI-Induced Skew Analysis                                | 103 |

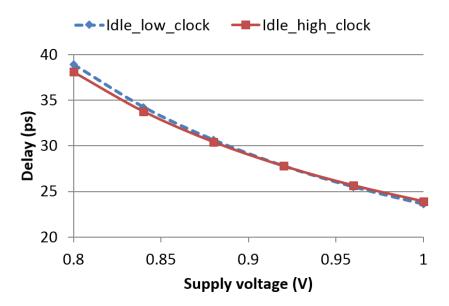

|    |     | 6.5.3  | BTI-Gater Cell Results                                      | 104 |

|    |     | 6.5.4  | Case Study for BTI-Gater Applicability                      | 106 |

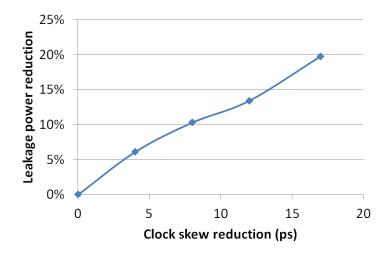

|    |     | 6.5.5  | Case Study for Power Saving                                 | 107 |

|    | 6.6 | Relate | d Work                                                      | 109 |

|    | 6.7 | Chapt  | er Conclusions                                              | 11( |

| 7  | Eva | luatin | g and Exploiting Impacts of Dynamic Power Management Scheme | es  |

| on | Sys | tem R  | eliability                                                  | 112 |

|    | 7.1 | Chapt  | er Introduction                                             | 112 |

|    | 7.2 | Chapt  | er Background                                               | 114 |

|    |     | 7.2.1  | Radiation-Induced Soft Error                                | 114 |

|    |     | 7.2.2  | Hardware Support for Power Management                       | 116 |

|    |     | 7.2.3  | Power Management in Linux Kernel                            | 117 |

|    |     |        |                                                             |     |

|              | 7.3   | Reliab  | ility Evaluation of Power Management Schemes                   |

|--------------|-------|---------|----------------------------------------------------------------|

|              |       | 7.3.1   | Base Platform for Reliability Evaluation                       |

|              |       | 7.3.2   | Hardware Configuration and Modeling                            |

|              |       | 7.3.3   | Platform System Customization                                  |

|              |       | 7.3.4   | Results of Reliability Evaluation                              |

|              | 7.4   | Exploi  | ting Power Management Schemes for Reliability                  |

|              |       | 7.4.1   | SER Estimation Mechanism                                       |

|              |       | 7.4.2   | Forbidden-State Based Policy                                   |

|              |       | 7.4.3   | Dynamic State Enabling/Disabling Policy                        |

|              |       | 7.4.4   | Experimental Evaluation of Reliability Management Policies 133 |

|              |       | 7.4.5   | Policy Effectiveness Evaluation                                |

|              | 7.5   | Chapt   | er Conclusion                                                  |

| 8            | Con   | ıclusio | n                                                              |

| $\mathbf{R}$ | efere | nces .  |                                                                |

# LIST OF FIGURES

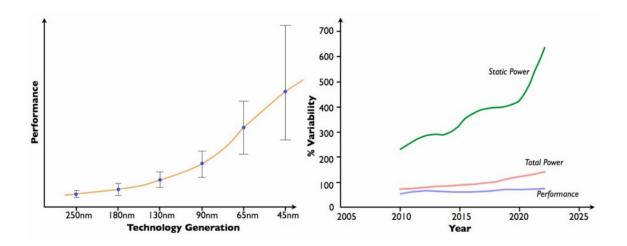

| 1.1  | Power and performance variability increase with technology [itr09]                                                                                                                                                                      | 2  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

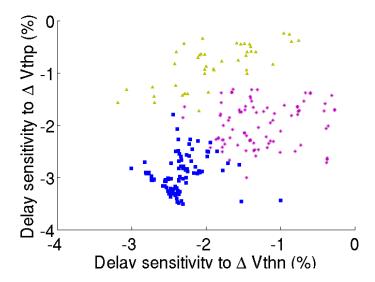

| 2.1  | Every dot represents delay sensitivities of a critical path in a design. In this example, we cluster the paths into 3 different clusters indicated by different colors. The results are based on SPICE simulation using commercial 45nm |    |

|      | process technology. Critical paths are extracted from AES [ope]                                                                                                                                                                         | 8  |

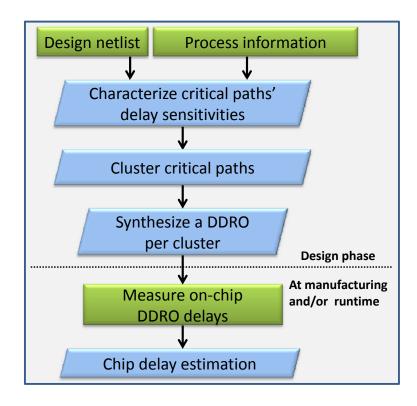

| 2.2  | Overview of <i>DDRO</i> design methodology                                                                                                                                                                                              | 9  |

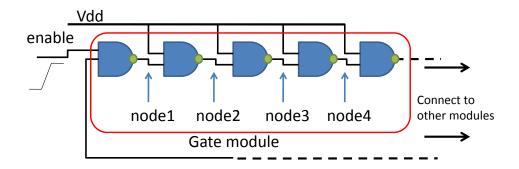

| 2.3  | Illustration of a gate module in a <i>DDRO</i>                                                                                                                                                                                          | 10 |

| 2.4  | Simulation results show that the sensitivities under different input slews {5ps, 50ps} and output loads {FO1, FO5} combinations converge as the number of                                                                               |    |

|      | stages in a gate module increases                                                                                                                                                                                                       | 10 |

| 2.5  | Simulation results of $DDRO$ on Cortex-M0 with global variation only (left)                                                                                                                                                             |    |

|      | and both global and local variations (right)                                                                                                                                                                                            | 13 |

| 2.6  | Testchip die photo and layout illustration                                                                                                                                                                                              | 13 |

| 2.7  | Mean delay estimation error obtained from <i>DDROs</i> and inverter-based ROs.                                                                                                                                                          |    |

|      | Estimation errors are calculated by taking the absolute difference between                                                                                                                                                              |    |

|      | normalized estimation and normalized chip delay. RVT and HVT are the two                                                                                                                                                                |    |

|      | Vt options for the inverters                                                                                                                                                                                                            | 14 |

| 2.8  | Designing a software stack for variability-aware duty cycling [Wan13a]                                                                                                                                                                  | 16 |

| 2.9  | RedCooper Testbed                                                                                                                                                                                                                       | 17 |

| 2.10 | Software Adaptation Illustration                                                                                                                                                                                                        | 18 |

| 2.11 | A snapshot of the demo hardware                                                                                                                                                                                                         | 19 |

| 3.1  | to inserting monitors at destination registers, the monitor inserted at A can              |    |

|------|--------------------------------------------------------------------------------------------|----|

|      | monitor the path delay even when the transition does not propagate to the                  |    |

|      | destination register (i.e., $T_1$ at $C$ ). But the monitor inserted at node A cannot      |    |

|      |                                                                                            | 24 |

| 3.2  | Monitor insertion flow                                                                     | 25 |

| 3.3  | Opportunism window is the margin saving comparing to worst-case design.                    |    |

|      | Monitor delay margin is the delay margin of the delay matching chain which                 |    |

|      | will be discussed in detail in Section 3.4.1                                               | 27 |

| 3.4  | Example of path-monitor pairs                                                              | 30 |

| 3.5  | Example of treating the nets in $I_{n_4} := \{n_2, n_4\}$ as a node. Cyclic flow as in (b) |    |

|      | is impossible because margin at $n_2$ must be larger than margin at $n_5$ . In (b),        |    |

|      | $n_2 \in I_{n_4}$ implies $n_5 \in I_{n_4}$                                                | 34 |

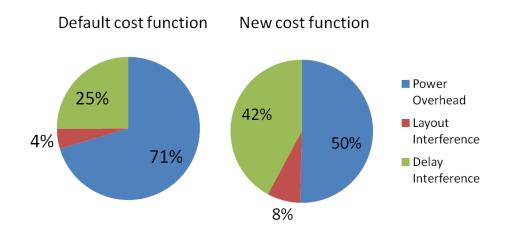

| 3.6  | Monitor cost breakdown examples for a sample circuit node                                  | 41 |

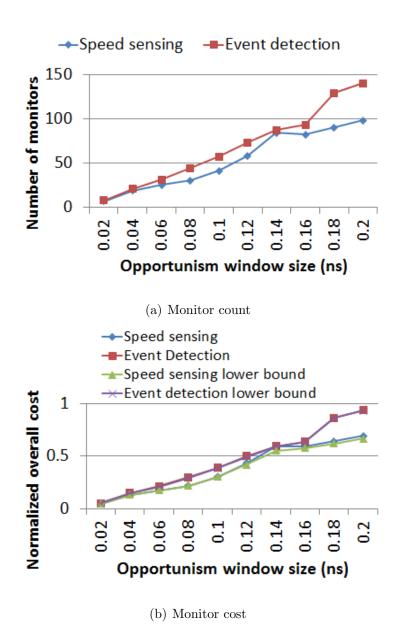

| 3.7  | Monitor count and cost for processor A with different opportunism window size              | 45 |

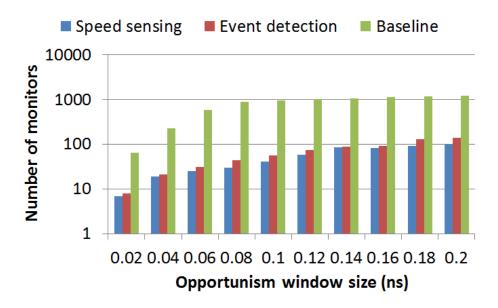

| 3.8  | Monitor count comparison between <i>SlackProbe</i> and baseline. The y-axis is             |    |

|      | plotted in log scale                                                                       | 46 |

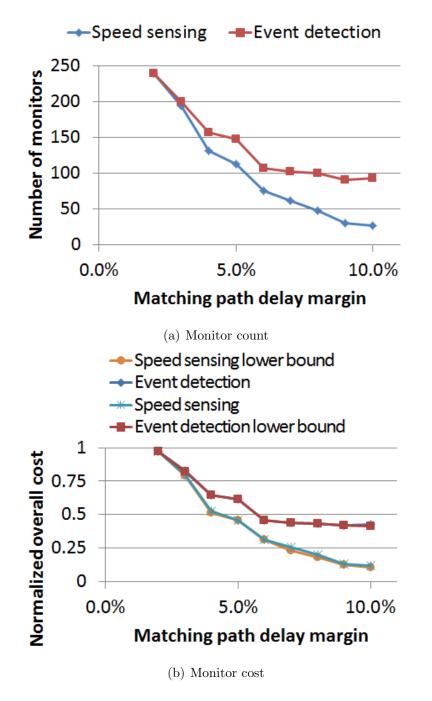

| 3.9  | Monitor count and cost vs. delay margin for processor A $\ldots \ldots \ldots$             | 47 |

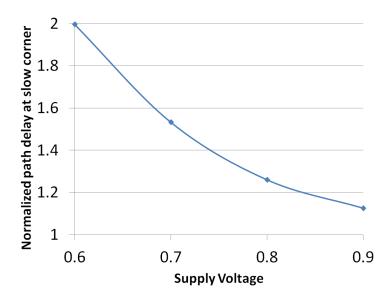

| 3.10 | Delay of a circuit path at slow corner. All path delay numbers are normalized              |    |

|      | to the corresponding delay at typical corner. The variation has larger impact              |    |

|      | at lower supply voltage.                                                                   | 48 |

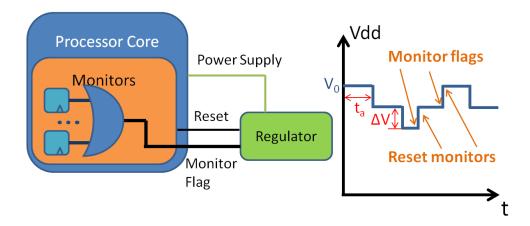

| 3.11 | Example application: the monitors give a one bit flag to the voltage regula-               |    |

|      | tor, the regulator reset the monitors after a corresponding voltage adaptation             |    |

|      | operation                                                                                  | 51 |

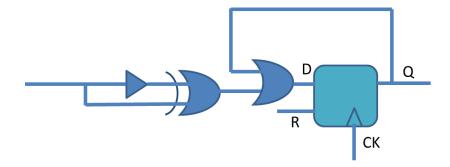

| 3.12 | Implemented monitor structure: the flag is sticky with an external reset                   | 51 |

| 0.10 | path endpoints, thus do not need extra cells other than the minimum required       |     |

|------|------------------------------------------------------------------------------------|-----|

|      | 6 cells                                                                            | 52  |

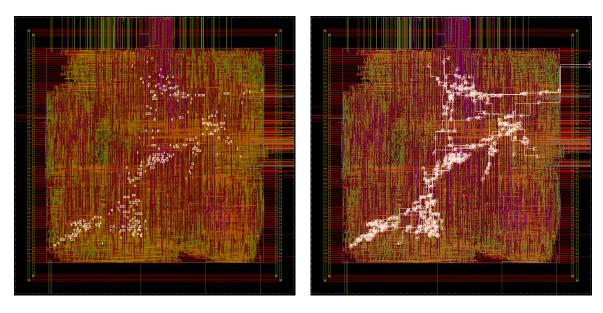

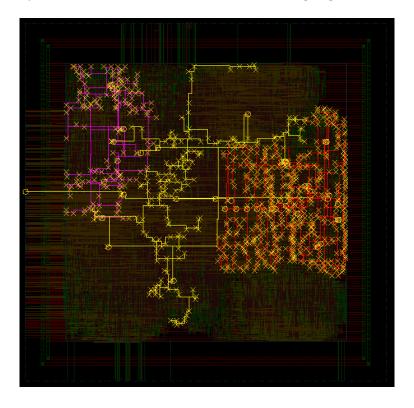

| 3.14 | Final layout of processor A with the inserted monitors placed and routed           | 54  |

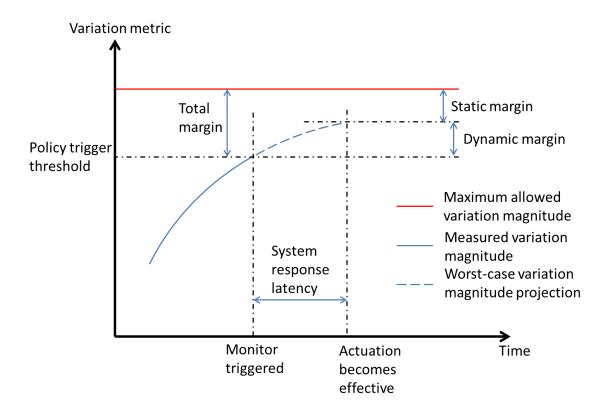

| 4.1  | Illustrate of the threshold-triggering policy                                      | 58  |

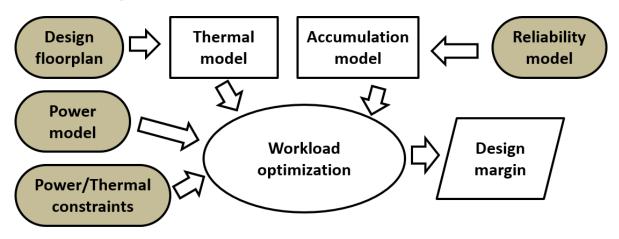

| 5.1  | Margining Methodology Overview.                                                    | 67  |

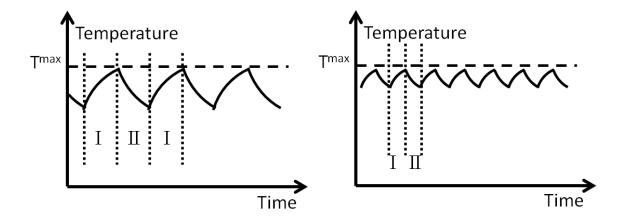

| 5.2  | Example of two workload cases. Both cases are alternating their power states       |     |

|      | between I and II while keeping the temperature under the thermal limit             | 77  |

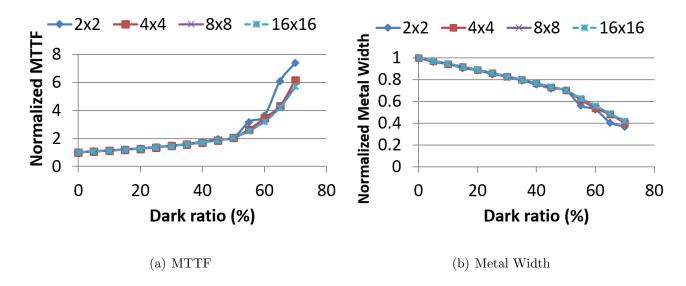

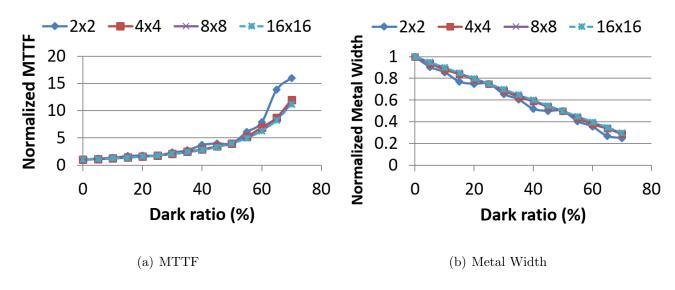

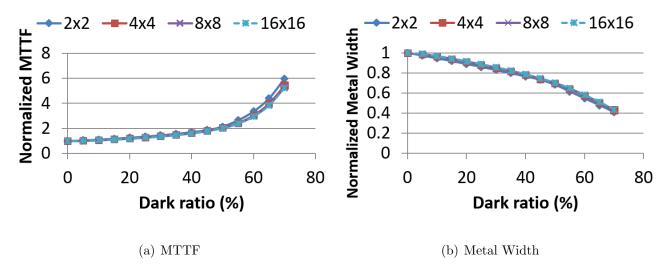

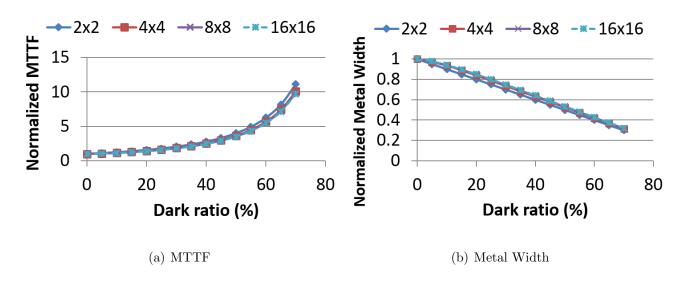

| 5.3  | EM results with power constraints for local power distribution network             | 80  |

| 5.4  | EM results with power constraints for signal wires.                                | 80  |

| 5.5  | EM results with thermal constraints for local power network                        | 81  |

| 5.6  | EM results with thermal constraints for signal wires                               | 81  |

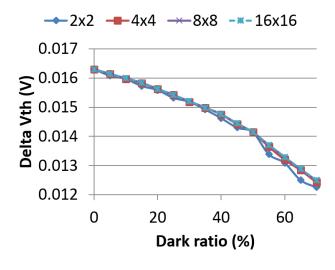

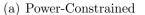

| 5.7  | BTI results of Vth degradation with power constraints and thermal con-             |     |

|      | straints                                                                           | 83  |

| 6.1  | Effects of NBTI and PBTI on clock paths                                            | 89  |

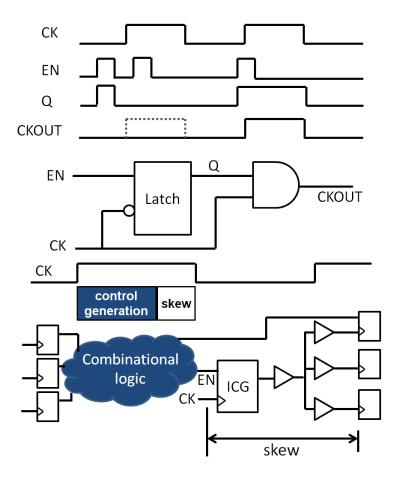

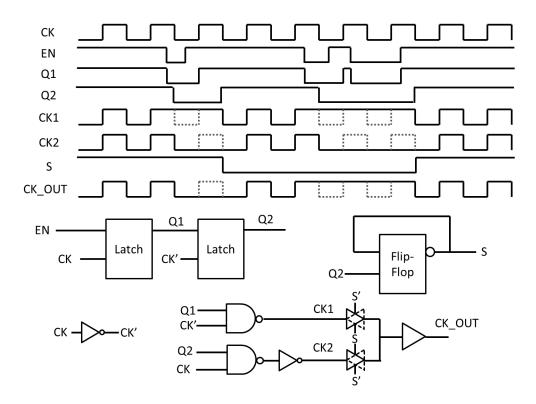

| 6.2  | Conventional ICG cell and its usage in circuits. The timing behavior of the ICG    |     |

|      | cell is similar to an edge-triggered element.                                      | 92  |

| 6.3  | Imbalanced signal duty ratio $(D)$ for gated clock branch and regular clock branch | 93  |

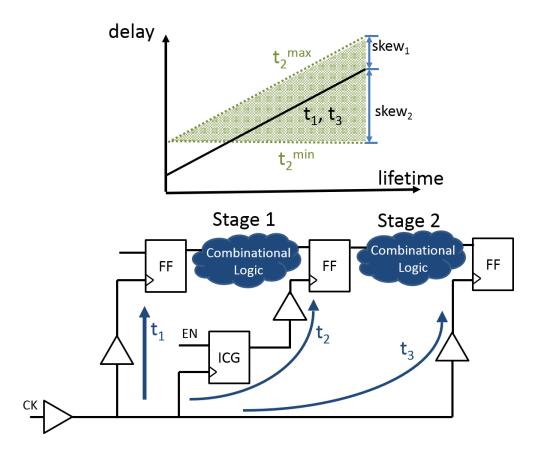

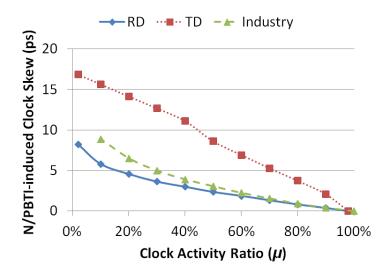

| 6.4  | Sample illustration of N/PBTI-induced clock skew and clock uncertainty             | 94  |

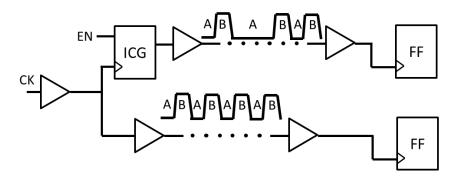

| 6.5  | Illustration of the clock gating latency issue                                     | 95  |

| 6.6  | BTI-Gater cell with half cycle clock gating latency                                | 96  |

| 6.7  | BTI-Gater cell with one cycle clock gating latency                                 | 98  |

| 6.8  | N/PRTI-induced clock skew mitigation methodology                                   | 100 |

| 6.9  | Gater is very small                                                                  | 105 |

|------|--------------------------------------------------------------------------------------|-----|

| 6.10 | Layout for processor B with clock distribution networks highlighted (ungated part    |     |

|      | in yellow, Case IV in purple and Case V in red)                                      | 106 |

| 6.11 | Clock skew with conventional ICG cell for Case I                                     | 108 |

| 6.12 | Leakage power saving by Vt-assignment with different clock reduction for Case I $$ . | 108 |

| 6.13 | The ICG cell proposed in [Cha09a]                                                    | 110 |

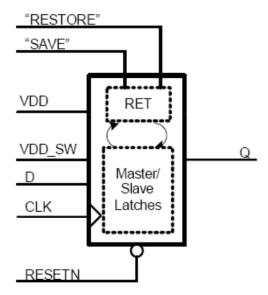

| 7.1  | An example of state retention Flip-Flop [Kea07]. The retention part is pow-          |     |

|      | ered by a different supply rail than the main master/slave latches                   | 117 |

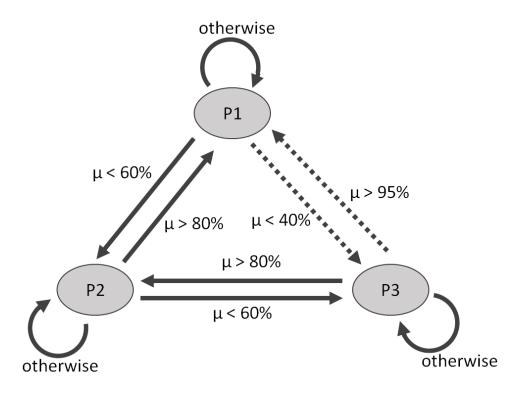

| 7.2  | State transition diagram example based on CPU utilization $\mu$ for CPUFreq          |     |

|      | governors. Ondemand governor can switch between any two levels while con-            |     |

|      | servative governor can only switch between neighboring levels. The switching         |     |

|      | threshold values are configurable in Linux kernel, and we use the default values     |     |

|      | for ondemand governor                                                                | 119 |

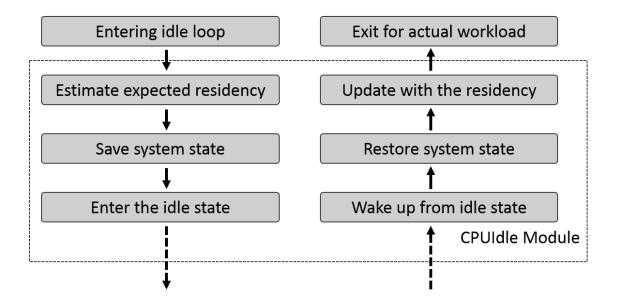

| 7.3  | CPUIdle module flow chart                                                            | 120 |

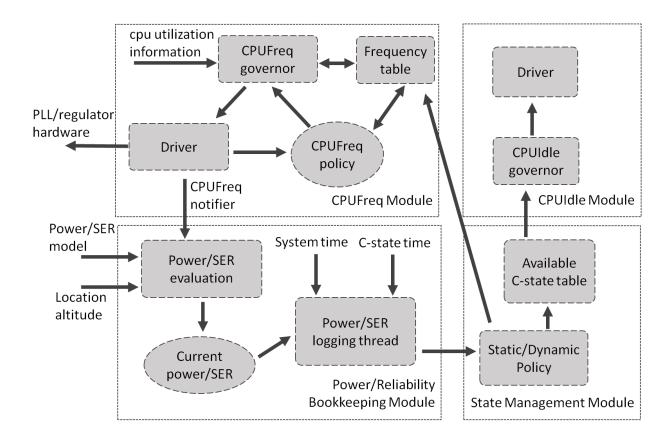

| 7.4  | Overall block diagram                                                                | 124 |

| 7.5  | Photo of the hardware evaluation platform setup based on BeagleBone Black            |     |

|      | development board                                                                    | 126 |

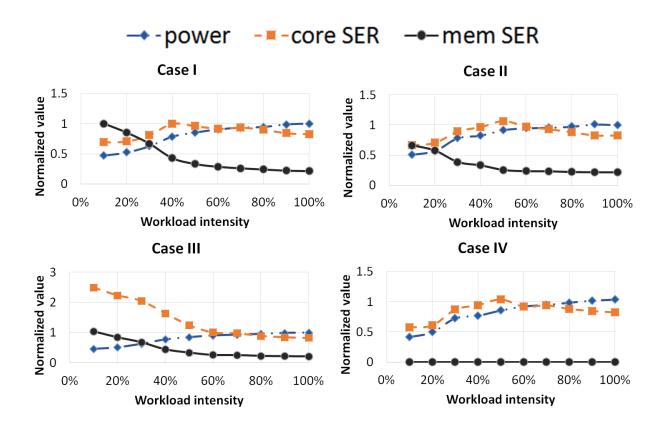

| 7.6  | Power/SER Results of different hardware configuration cases with different           |     |

|      | software workload intensity at sea level. 100% workload intensity means the          |     |

|      | system is fully loaded and has no performance slack                                  | 127 |

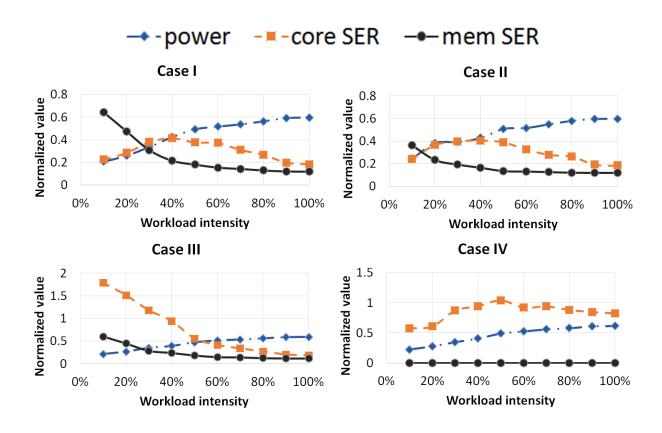

| 7.7  | Power/SER Results of different hardware configuration cases with different           |     |

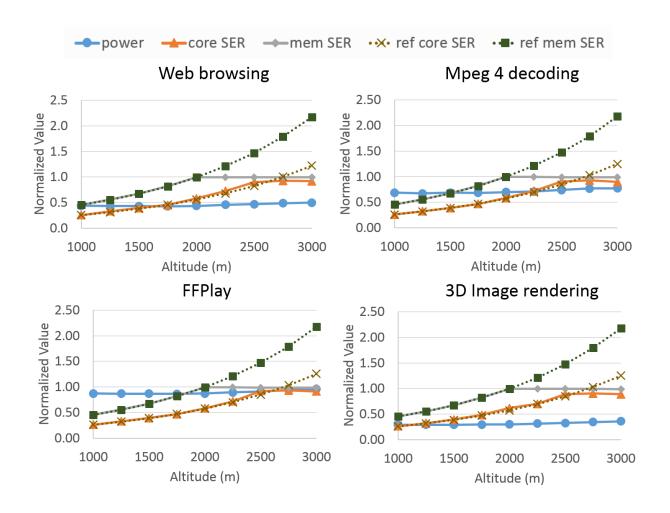

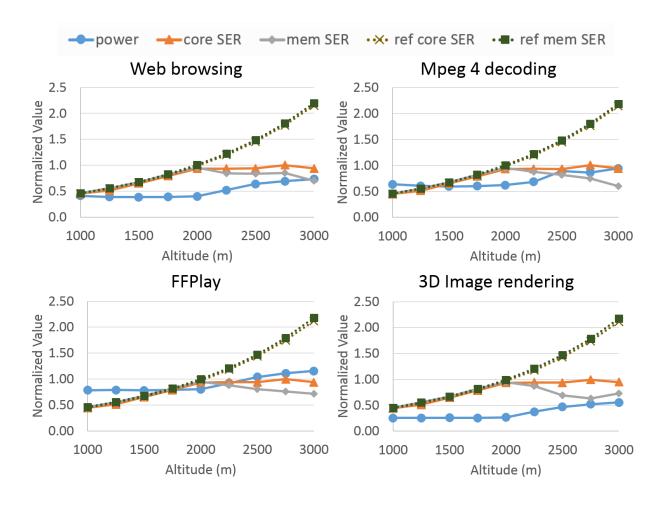

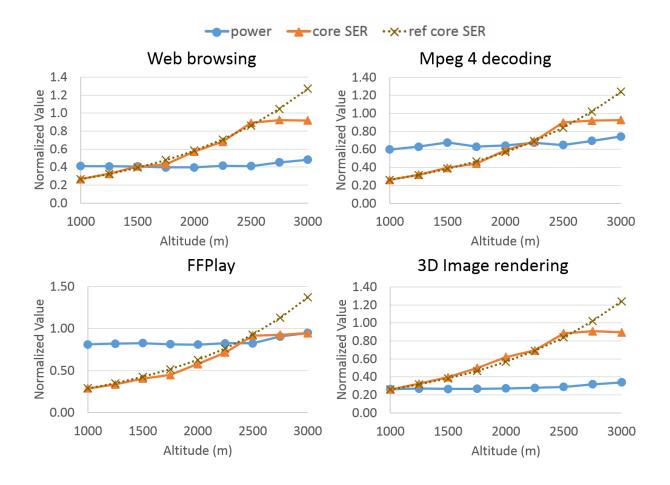

|      | software workload intensity for 28nm technology                                      | 128 |

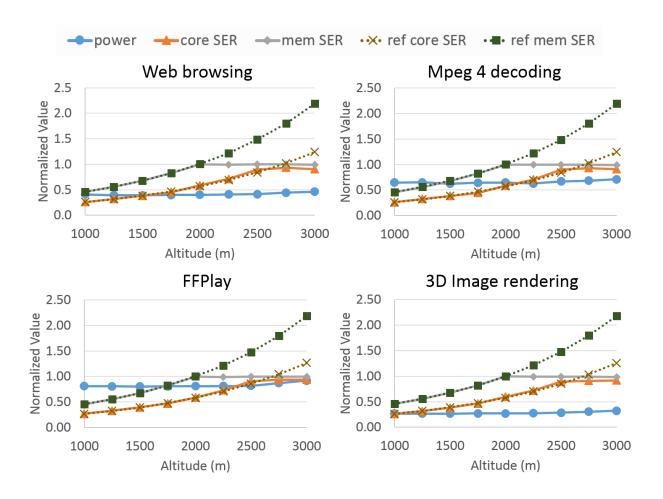

| 7.8  | Power/SER Results of different software benchmarks on case I with dynamic            |     |

|      | policy                                                                               | 134 |

| 1.9  | Power/SER Results of different software benchmarks on case II with dynamic      |     |

|------|---------------------------------------------------------------------------------|-----|

|      | policy                                                                          | 135 |

| 7.10 | Power/SER Results of different software benchmarks on case III with dynamic     |     |

|      | policy                                                                          | 136 |

| 7.11 | Power/SER Results of different software benchmarks on case IV with dynamic      |     |

|      | policy                                                                          | 137 |

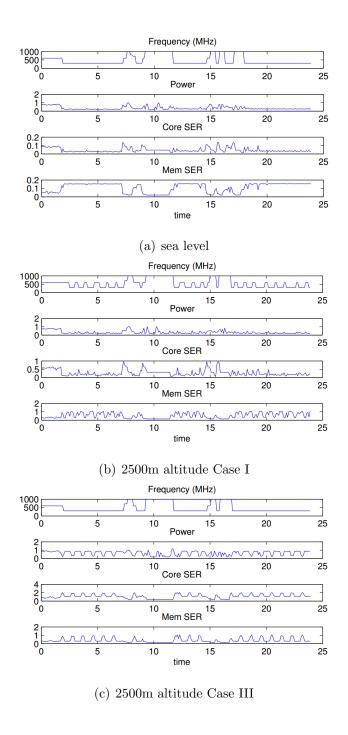

| 7.12 | An example of web browsing benchmark execution with different altitude and      |     |

|      | hardware cases. For case I, P-states are exploited by the policy while C-states |     |

|      | are used for case III. Note some y-axis scale for the figures are different     | 142 |

| 8.1  | Estimate of the margin of different variability sources and projected margin    |     |

|      | saving from our approaches for 45nm process technology                          | 144 |

# LIST OF TABLES

| 2.1 | System Demonstration Result Highlights                                                                                    | 20  |

|-----|---------------------------------------------------------------------------------------------------------------------------|-----|

| 3.1 | Implementation information of the processor benchmarks                                                                    | 44  |

| 3.2 | Experimental results on the processor benchmarks                                                                          | 44  |

| 3.3 | Monitoring efficiency and observability results                                                                           | 50  |

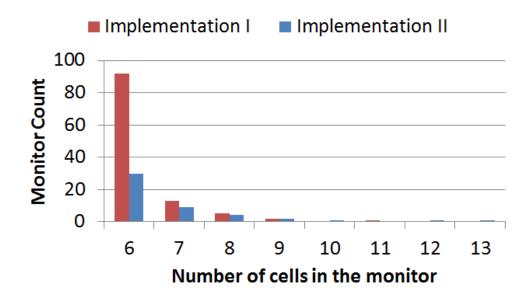

| 3.4 | Implementation results on processor A                                                                                     | 52  |

| 4.1 | List of Actuators                                                                                                         | 61  |

| 4.2 | List of Thermal Monitors                                                                                                  | 62  |

| 4.3 | Case Study on Dynamic and Static Margin                                                                                   | 63  |

| 5.1 | Glossary of Terminology                                                                                                   | 71  |

| 6.1 | Summary of different clock gating cases                                                                                   | 103 |

| 6.2 | Clock path delay and skew (in ps) under different aging models and activities                                             |     |

|     | using conventional ICG cells                                                                                              | 104 |

| 6.3 | Clock activity $\mathrm{ratio}(\mu)$ and $\mathrm{signal}$ duty $\mathrm{ratio}(D)$ results for different software bench- |     |

|     | marks                                                                                                                     | 107 |

| 7.1 | Table of different hardware implementations                                                                               | 121 |

| 7.2 | Table of different CPUFreq states spec used                                                                               | 125 |

| 7.3 | Table of different CPUIdle states spec used                                                                               | 125 |

| 7.4 | Normalized power/core SER/memory SER results of different software bench-                                                 |     |

|     | marks with different configuration cases at sea level                                                                     | 129 |

| 7.5 | The additional power of running the benchmarks with our policies compared |     |

|-----|---------------------------------------------------------------------------|-----|

|     | to the optimal P-state and C-state selection schemes                      | 141 |

## $V_{ITA}$

2010 Bachelor of Engineering (Honors Research Option), Electronic Engineering, Hong Kong University of Science and Technology.

2012 Master of Science, Electrical Engineering, UCLA.

#### **PUBLICATIONS**

- T. B. Chan, P. Gupta, A. Kahng, and L. Lai, "DDRO: A Novel Performance Monitoring Methodology Based on Design-Dependent Ring Oscillators," in *IEEE International Symposium on Quality Electronic Design*, Mar. 2012.

- L. Lai, V. Chandra, R. Aitken, and P. Gupta, "SlackProbe: A low overhead in situ online timing slack monitoring methodology," in *IEEE/ACM Design, Automation and Test in Europe*, Mar. 2013.

- L. Wanner, S. Elmalaki, L. Lai, P. Gupta, and M. Srivastava, "VarEMU: An Emulation Testbed for Variability-Aware Software," in *ACM International Conference on Hardware/Software Codesign and System Synthesis*, Oct. 2013.

- L. Lai and P. Gupta, "Accurate and inexpensive performance monitoring for variability-aware systems," in *Proc. Asia and South Pacific Design Automation Conference*, Jan. 2014.

- L. Lai, V. Chandra, P. Gupta "Evaluating and Exploiting Impacts of Dynamic Power Management Schemes on System Reliability" in *International Conference on Compilers, Archi-*xix

- G. Leung, L. Lai, P. Gupta, and C. O. Chui, "Device- and Circuit-Level Variability Caused by Line Edge Roughness for Sub-32nm Finfet Technologies," *Electron Devices, IEEE Transactions on*, vol.59, no.8, pp.2057,2063, Aug. 2012

- T.-B. Chan, P. Gupta, A. B. Kahng, and L. Lai, "Synthesis and Analysis of Design-Dependent Ring Oscillator (DDRO) Performance Monitors," *Very Large Scale Integration* (VLSI) Systems, IEEE Transactions on, vol.22, no.10, pp.2117,2130, Oct. 2014

- L. Lai, V. Chandra, R. Aitken, and P. Gupta, "BTI-Gater: An Aging-Resilient Clock Gating Methodology," *IEEE Journal on Emerging and Selected Topics in Circuits and Systems*, vol. 4, pp. 180-189, Jun. 2014.

- L. Lai, V. Chandra, R. Aitken, and P. Gupta, "SlackProbe: A Flexible and Efficient In Situ Timing Slack Monitoring Methodology," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 33, pp. 1168-1179, Aug. 2014.

- L. Wanner, L. Lai, A. Rahimi, M. Gottscho, P. Mercati, C.-H. Huang, F. Sala, Y. Agarwal, L. Dolecek, N. Dutt, P. Gupta, R. Gupta, R. Jhala, R. Kumar, S. Lerner, M. Subhasish, A. Nicolau, T. S. Rosing, M. B. Srivastava, S. Swanson, D. Sylvester, and Y. Zhou, "NSF Expedition on Variability-Aware Software: Recent Results and Contributions," *De Gruyter Information Technology (it)*, vol. 57, pp. 181-198, June 2015.

## CHAPTER 1

## Introduction

Semiconductor manufacturing process scaling has been the primary driver for innovations and performance/power improvements in computer systems. With technology scaling to nano-scale range, hardware variability continues to increase due to increasing amounts of manufacturing variability, ambient fluctuations and circuit wear-out (e.g., N/PBTI, HCI etc.) degradations. Considering the power and performance variability as shown in Fig. 1.1, these increased variations have led to increased margin in designing reliable integrated systems, which takes up significant amounts of system's performance/power and diminishes the potential benefits of scaling.

This dissertation aims at reducing total system design margin, including efforts in developing methodologies for monitoring, margining and mitigation of circuit variability. These methodologies are mainly cross-layer approaches that can span multiple layers of system abstraction. We focus on cross-layer approaches due to the following reasons:

- System adaptation can be made more efficient with cross-layer approaches. By capturing and exposing hardware variability to the software/system level, corresponding hardware and software adaptation can opportunistically reduce or even eliminate the design margin [Gup12].

- System design margin is determined by the accuracy and efficiency of the entire monitor-and-actuate adaptation process. Over-optimizing a single component without considering the full-system may not improve the system margin, as components from other layers may be the bottleneck.

Figure 1.1: Power and performance variability increase with technology [itr09]

- Design margin is usually derived and applied during hardware design time with pessimistic assumptions. Certain system/architecture-level information can be used to reduce the margin by relaxing some of these assumptions.

- System margin may be dominated by the existence of certain pathological scenarios.

These pathological scenarios may be caused by behaviors from different layers of system abstraction. Cross-layer approaches may be required as single-layer approaches may be inadequate to avoid these scenarios.

- Some hardware-related phenomena are difficult to monitor by hardware monitors alone. For example, soft error rate is extremely difficult to monitor due to the rare occurrence nature and unique ambient (i.e., location/altitude) dependence. Cross-layer approaches can use system and even cloud-based information for better monitoring.

## 1.1 Proposed Margin Reduction Approaches

Our efforts in margin reduction can be classified as three parts: monitoring, margining and mitigation.

#### 1.1.1 Accurate and Inexpensive Monitoring for Variability-Aware System

For monitoring, we focus on the circuit performance variability, due to the following reasons:

- (i) Circuit delay change is the manifestation of most of the variability effects and many reliability-related phenomena. Reducing delay margin effectively reduces the design margin caused by these variability sources and reliability issues.

- (ii) Unlike power, which behaves like "sum of variables", circuit delay is dictated by the slowest path, i.e., behaving like "maximum of variables". This creates additional complexity and unique context-dependence for delay-related issues, including its modeling, monitoring and margining.

- (iii) Under many circumstances, delay variation and other types of variations are actually interchangeable. For example, power variation can be translated into delay variation through voltage scaling or body-biasing. Therefore, reducing delay margin can reduce other types of design margin as well.

If hardware variability can be captured and exposed to the software/system level during runtime, corresponding hardware and software adaptation can opportunistically reduce or even eliminate the design margin [Gup12]. The quality of these adaptation schemes depends on the quality of the monitors. Therefore, part of the proposed research focuses on improving the quality (i.e., accuracy and overhead) of these delay monitors.

There are mainly two classes of delay monitors that aim at monitoring circuit performance (i.e., measuring circuit critical path delay). They are replica monitors and in situ monitors.

Replica monitors, also known as canary circuits, [Dra07,Bhu06,Liu10,Cha12b] are standalone circuits which are designed to mimic the timing behavior of the original circuits. By measuring the replica circuit delay, one can estimate the delay of the original circuits. Typically, the replicas are simple circuits, e.g., simple paths or ring oscillators. Therefore, replicas are usually non-intrusive and with low overhead, but may be inadequate to cover

the heterogeneity within the original circuits. Furthermore, replica monitors may fail to capture the variation that is local to real circuits such as random manufacturing variations and circuit aging.

In situ monitors measure the delay directly from the circuit paths [Fic10, Kim13, Bow09]. They can accurately capture the real path delay, but with significant overhead, especially when a large number of registers are timing critical.

We propose two circuit performance methodologies. Design-dependent ring oscillator (DDRO) [Cha13b] designs and leverages multiple replicas to accurately monitor circuit performance. SlackProbe [Lai13] inserts in situ monitors at both path intermediate nets and path endpoints, which can greatly reduce the overhead of in situ monitoring.

#### 1.1.2 Margining for Emerging Systems

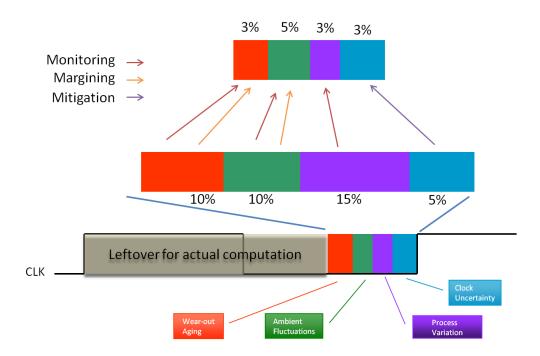

For system with adaptation, the margin derivation should consider the entire monitor-and-actuate process. Over or under optimizing any single component can result in wasting resources or bottlenecking the performance. We classify the dynamic variation margin and analyze different parts with the choices of monitor/actuator types.

Even though design margin is usually determined at hardware design time without full knowledge of the higher layers of the system stack, certain architecture-level behavior information can be utilized to better estimate the necessary hardware design margin. For example, voltage boosting is a popular architecture-level technique for high-end processors, which use higher supply voltage to achieve temporary performance gain when permitted by the thermal conditions. This makes the boosted supply voltage and maximum operating temperature the worst-case aging conditions for design margining. However, typical power consumption under voltage boosting exceeds the chip's thermal design power (TDP). This makes it impossible to retain the worst-case aging conditions for long time. Therefore, if the architecture-level power/thermal models and management policies are available, the hardware may use a better-than-worst-case operating condition for deriving the necessary

margin.

#### 1.1.3 Reliability Mitigation

Some types of delay variation are difficult to resolve through adaptation. For example, high-level adaptations have limited effects on clock skew due to aging in clock distribution network, because the adaptation effect will be applied on all clock paths and thus will cancel each other out.

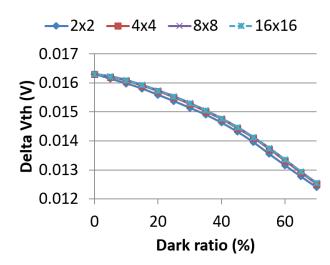

The clock distribution network usually has balanced structure and invariant signal pattern, which makes it very robust against N/PBTI-induced delay degradation. However, this may not hold for clock distribution networks with clock gating features [Liu12]. The imbalanced clock signal pattern due to clock gating can result in imbalanced degradation on different clock paths, causing N/PBTI-induced clock skew.

We propose BTI-Gater, which consists of cross-layer solutions to mitigate N/PBTI-induced clock skew. Two Integrated Clock Gating (ICG) cell circuits are proposed to balance the clock signal pattern. A methodology is also proposed to select the appropriate ICG cell, based on the micro-architecture and architecture context. An example of software sleep scheduling is described in conjunction with BTI-Gater to avoid certain pathological aging scenarios.

For certain reliability phenomena, such as soft error rates, it is extremely difficult to make an estimate using hardware monitors. So we have proposed system/cloud-based virtual sensing to capture varying ambient conditions for soft error rates. We also develop a hardware evaluation platform based on an embedded/mobile development board and standard Linux kernel. We demonstrate the use of our platform to evaluate the system's power and radiation-induced soft error rate in presence of system power management schemes, with different application workloads and various hardware design configurations.

#### 1.2 Thesis Outline

The objective of this dissertation is to reduce the system design margin with cross-layer approaches. The key contributions of this work can be summarized as follows:

- *DDRO* replica delay monitoring methodology is proposed in Chapter 2. *DDRO* designs and leverages *multiple* replica monitors to accurately monitor circuit performance.

- SlackProbe in situ delay monitoring methodology is proposed in Chapter 3. SlackProbe inserts in situ delay monitors at both path intermediate nets and path endpoints, which can greatly reduce the overhead of in situ monitoring.

- Dynamic variation margining, in presence of monitor-and-actuate adaptation, is described in Chapter 4. We classify and analyze different parts of the system margin for monitoring and actuation.

- Hardware reliability margining for circuits in the "dark silicon" era is presented in Chapter 5. We propose methodologies for deriving the reliability margin considering the high-level power/thermal constraints.

- BTI-Gater clock gating methodology is proposed in Chapter 6. BTI-Gater consists of cross-layer solutions to eliminate N/PBTI-induced clock skew.

- Our study on evaluating and exploiting impacts of dynamic power management schemes

on system reliability is presented in Chapter 7. We propose system/cloud-based soft

error rate monitors and simple forbidden-state based policies for monitoring and adaptation.

## CHAPTER 2

## DDRO Replica Monitor

#### 2.1 DDRO Motivation and Overview

In order to accurately estimate the circuit delay, replica monitors should be designed to follow the timing behavior of original circuits under variations. We know that the circuit's performance is determined by delay of the slowest path, i.e., critical path. Therefore, the replica should be designed to follow the timing behavior of the critical path.

Due to variations, there may be a number of potential critical paths and they may behave differently under variations, which makes a single replica monitor inadequate. The motivation of DDRO is shown in Fig. 2.1, in which each dot represents the delta delay of one critical path under variations of PMOS threshold voltage Vthp (y-axis) and NMOS threshold voltage Vthn (x-axis). The critical path delay sensitivities form natural clusters, which implies that multiple replica monitors can be designed to cover these clusters.

An overview of DDRO monitoring strategy is shown in Fig. 2.2. First, we extract critical paths of a design and characterize their delay sensitivities to variation sources. Second, we cluster the critical paths based on the sensitivities, and synthesize DDROs to match delay sensitivity of the clusters. By matching DDRO and cluster delay sensitivities, we ensure that the synthesized DDROs have good correlation with the critical paths. Since we use only standard cells (gates) to synthesize the DDROs, the design and placement of DDROs can be easily integrated with conventional implementation flows. Based on DDRO frequencies, we can estimate chip delay during manufacturing or runtime.

Figure 2.1: Every dot represents delay sensitivities of a critical path in a design. In this example, we cluster the paths into 3 different clusters indicated by different colors. The results are based on SPICE simulation using commercial 45nm process technology. Critical paths are extracted from AES [ope].

## 2.2 Path Sensitivity Extraction and Clustering

Delay sensitivity of path i  $(V_i^{path})$  can be obtained using finite differences, i.e., taking the  $\Delta delay$  by perturbing each variation source by  $1\sigma$ . After characterizing all path delay sensitivities, we can cluster the critical paths. The objective function of the clustering is defined as

minimize

$$\sum_{i=1}^{N} (w_i \times |\mathbf{V}_i^{path} - \mathbf{V}_k^{ro}|)$$

(2.1)

where the summation is taken over paths i in cluster k, and  $w_i$  is the probability of a critical path delay exceeding the clock period of the design. The weight factor  $w_i$  is added so that we can impose a higher penalty for having mismatched delay sensitivities on a path with higher probability to fail (less timing slack). Detailed derivation of  $w_i$  can be found in [Cha13b].

Figure 2.2: Overview of *DDRO* design methodology.

## 2.3 DDRO Synthesis

#### 2.3.1 Gate Module

For the ease of synthesizing DDRO, we use gate module as basic building block. A gate module is constructed as several identical gates connected in series as illustrated in Fig. 2.3.

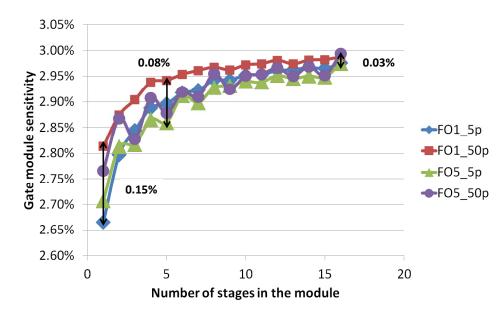

This repeated pattern can help decouple the load and slew interaction between gates. Simulation results in Fig. 2.4 show that the sensitivity difference due to different input slew and output load is reduced from 0.15% to 0.03%, as the number of stages in a gate module increases from 1 to 15. In this work, we use 5-stage gate modules as a trade-off between stability of sensitivity and total area of a gate module. For a gate with multiple input pins, gate delays through different input pins will have different delay sensitivities. Thus, each gate module type is defined with respect to a specific input pin. Extra input pins of a multi-

Figure 2.3: Illustration of a gate module in a *DDRO*.

input gate are assigned to high or low to make a gate module inverting or buffering (see Fig. 2.3).

Figure 2.4: Simulation results show that the sensitivities under different input slews {5ps, 50ps} and output loads {FO1, FO5} combinations converge as the number of stages in a gate module increases.

Since the interconnect also affects path delay sensitivity, we use different wirelength in building our gate modules. Gate modules with different wirelength are considered as different instance types even if they have the same gate type.

#### 2.3.2 ILP-based Synthesis

Given a delay sensitivity target ( $\mathbf{V}^{ro}$ ) obtained from path clustering, we want to choose the number of each gate module in a DDRO, so that the delay sensitivities of the DDRO match the targeted delay sensitivities. Because of its unique structure, gate module delay variation is less sensitive to input slew and output load. Since each gate module type is instantiated a discrete number of times, we can formulate DDRO synthesis as an integer linear programming (ILP) problem, where the integer variable is the number of certain gate modules in the synthesized DDRO. Appropriate constraints are applied to limit the maximum RO length. Detailed description of gate module and ILP formulation can be found in [Cha13b].

#### 2.4 Delay Estimation

#### 2.4.1 Path-based Estimation

As shown in Fig. 2.2, at manufacturing and/or runtime, *DDRO* delay is measured and used to estimate chip delay.

Each critical path delay can be estimated by DDROs. Given M DDROs, we can represent delay sensitivity of each path  $(\mathbf{V}_i^{path})$  as a linear combination of DDRO delay sensitivity  $(\mathbf{V}_k^{ro})$  (k = 1, ..., M) as in Equation (2.2).

$$\mathbf{V}_{i}^{path} = \sum_{k=1}^{M} b_{ik} \cdot \mathbf{V}_{k}^{ro} + \mathbf{V}_{i}^{res\_path}$$

(2.2)

where  $b_{ik}$  is a  $[1 \times M]$  matrix containing constant coefficients and  $\mathbf{V}_{i}^{res\_path}$  is a  $[1 \times Q]$  matrix that represents the decomposition residue.

Using  $b_{ik}$ , we can estimate the path delay by:

$$d_{i}^{path} = d_{i}^{nom\_path} \left(1 + \sum_{k=1}^{M} \underbrace{(b_{ik} \mathbf{V}_{k}^{ro} \cdot \mathbf{g})}_{\text{uncertainty}} + \underbrace{u_{i}}_{\text{uncertainty}}\right)$$

where  $u_{i} = l_{i}^{path} + \mathbf{V}_{i}^{res\_path} \cdot \mathbf{g}$  (2.3)

where **g** is global variation vector,  $l_i^{path}$  is the local variation of the path. Equation (2.3) shows that  $d_i^{path}$  consists of a measurable term and an uncertainty term. While the value of the measurable term can be determined from the delays of DDROs, the value of the uncertainty term cannot be measured directly.

#### 2.4.2 Cluster-based Estimation

The path-based estimation method requires one estimation for each critical path, which can cause significant computation and storage overhead. To reduce the overhead, we propose to utilize the clustering nature of critical paths and to have one estimation for each path cluster. We calculate the maximum delay of paths in each cluster using the method in [Vis06], assuming that the means of path delays correspond to their nominal values. The outcome of this step gives us the expected maximum delay. But more importantly, it also extracts the sensitivity of the maximum delay to variation sources ( $\mathbf{V}^{max}$ ). Similar to the path-based approach, we treat the cluster as a pseudo path with delay sensitivity  $\mathbf{V}^{max}$ . Simulation results show that the estimation error of this approximation approach compared to the reference method is very small.

## 2.5 Simulation and Silicon Result Highlights

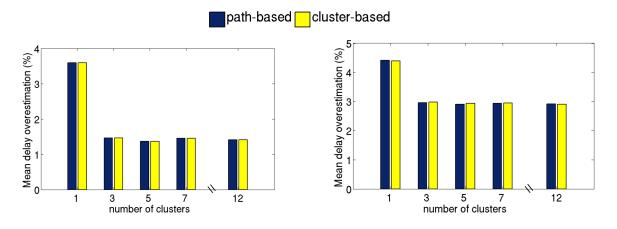

To validate *DDRO* performance monitoring methodology, we synthesized, placed and routed processor benchmark circuits using a commercial 45nm SOI technology. Some simulation results of *DDRO* on Cortex-M0 [Corb] are highlighted in Fig. 2.5. For global variation only case, using more *DDROs* can dramatically decrease mean overestimation (i.e., required delay

margin). But this benefit becomes less in presence of local variation. The results show that the estimation error of cluster-based approximation, compared to the path-based approach, is very small.

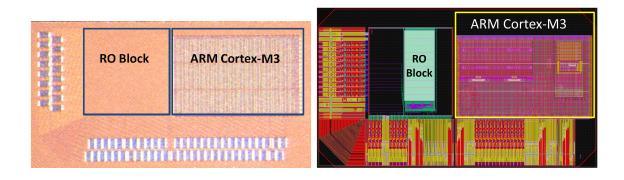

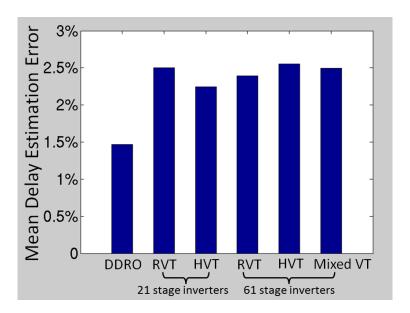

A testchip was taped out with DDRO-based performance monitoring using a 45nm IBM SOI technology with dual- $V_{th}$  (RVT and HVT) libraries. The testchip has an ARM Cortex-M3 microprocessor [Corc] with five DDROs. For comparison, we also implemented several inverter-based ROs in the testchip. The silicon measurement results are shown in Fig. 2.7. The measurement results show that by using five DDROs, we can reduce the mean delay estimation error by 35% (from 2.3% to 1.5%) compared to generic inverter-based ROs.

Figure 2.5: Simulation results of *DDRO* on Cortex-M0 with global variation only (left) and both global and local variations (right).

Figure 2.6: Testchip die photo and layout illustration

Figure 2.7: Mean delay estimation error obtained from *DDROs* and inverter-based ROs. Estimation errors are calculated by taking the absolute difference between normalized estimation and normalized chip delay. RVT and HVT are the two Vt options for the inverters.

## 2.6 RedCooper: A Testbed for Variability-aware System

In this section, we will present our implementation of a complete end-to-end system [Aga] that demonstrates the use of hardware monitors with both hardware and software adaptation. We first describe the software adaptation concept of variability-aware software duty-cycling. Then we present our testbed implementation and variability-aware system demonstration.

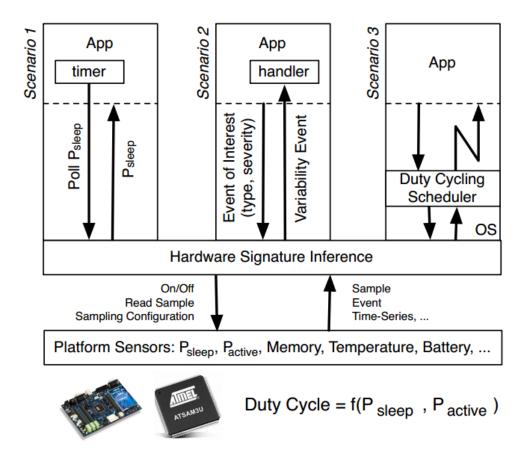

### 2.6.1 Variability-Aware Software Duty-Cycling

For battery-powered embedded sensing system, the total lifetime energy is usually constrained. In order to meet the lifetime requirements, one particularly common power management techniques is duty cycling, where the system is at default in a sleep state and woken up periodically to attend to pending tasks and events. A system with higher duty cycle may, for example, sample sensors for longer intervals or at higher rates, increasing data quality. A

typical application-level goal is to maximize quality of data through higher duty cycles, while meeting a lifetime goal. Conventional approach determines duty cycles by either worst-case power specifications or datasheet power values, which may be heavily guardbanded. If the system's power consumption can be measured and exposed to the software, the application may be able to adapt its duty cycle rate and increase its QoS opportunistically according to the hardware power consumption status [Wan13a].

For example, for a fixed lifetime energy budget E and specified targeting lifetime constraints L, the software duty cycle rate DC can be calculated through the following equation [Wan13a]:

$$P_A \cdot DC + P_S \cdot (1 - DC) = \frac{E}{L}$$

$$DC = \frac{E - L \cdot P_S}{L \cdot (P_A - P_S)}$$

(2.4)

where  $P_A$  and  $P_S$  are the active and sleep power consumption respectively. By determining  $P_A$  and  $P_S$  on a per-instance basis, the duty cycle may be tailored to maximize active time for each individual sensor under a given deployment scenario (temperature profile, lifetime requirement, battery capacity).

There are several different ways that such an opportunistic stack may be organized as shown in Fig. 2.8. The scenarios differ in how the sense-and-adapt functionality is split between applications and the operating system. In this work, we use the last scenario, where variability is largely offloaded to the operating system.

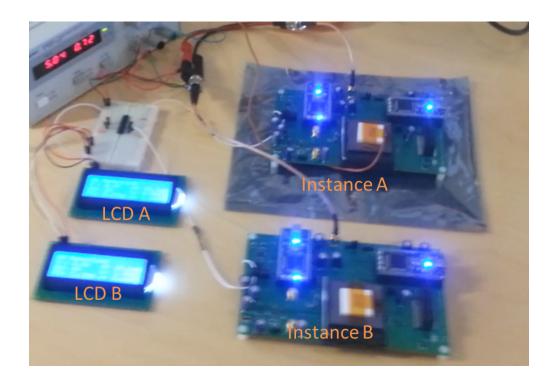

## 2.6.2 Testbed Implementation and System Demonstration

The testbed is built upon *DDRO* testchip (Fig. 2.6). On the testchip, there are on-chip performance monitors (*DDRO*) and leakage sensors. For the purpose of demonstrating software duty-cycling, we also implement on-board power sensors to measure the power consumption of the testchip. the power of the Cortex-M3 processor and the (on-chip) SRAM memory are measured separately. A picture of the testbed board is shown in Fig. 2.11. Because *DDRO*

Figure 2.8: Designing a software stack for variability-aware duty cycling [Wan13a] and the processor are implemented as separate blocks when taping-out the testchip, we use on-board MCUs [mbe] to sample the monitor readings and feed into the on-chip SRAM.

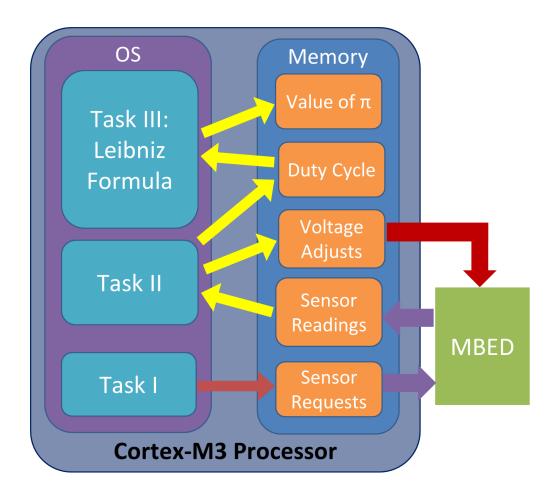

The software running on the M3 core is shown in Fig. 2.10. The operating system (OS) is based on CoOS [CoO]. Three tasks are implemented within the OS:

- Task I sends the sensing request by writing to a pre-specified memory location. Upon seeing the request, the on-board MCUs will start reading the sensor values and write the sensor readings directly to certain memory locations.

- Task II acts as the central adaptation center, which reads the sensor readings, including *DDRO* frequencies, current drawn by the M3 core, current drawn by the on-chip

Figure 2.9: RedCooper Testbed.

SRAM, and the on-chip leakage sensor. *DDRO* frequencies are used to calculate the performance slack and determine the adjusted voltage. The current and leakage sensor values are used to calculate the feasible duty cycle using Equation (2.4). The duty cycle rate is further translate to the number of iterations for Task III.

• Task III is the main application running in the OS, which calculates the value of  $\pi$  with its best effort under the constrained duty cycle.

In this demo, all three OS tasks are fired every 10 seconds. We set the processor to run at a fixed 600 MHz clock frequency. The active power includes both the core and SRAM power consumption. The sleep power includes the SRAM power and the projected leakage power of the core.

A snapshot of the entire hardware is shown in Fig. 2.11. We have two copies of *RedCooper* running side-by-side. Each testbed is equipped with an LCD reporting the system status.

Figure 2.10: Software Adaptation Illustration.

Some results are highlighted in Table  $2.1.^1$  At room temperature, Instance B system has smaller sleep power than Instance A, which implies the potential of achieving high duty cycle rate. Therefore, the adaptive software set the number of iterations (DC) at 49 for Instance B and the calculation error is smaller. After heating up Instance A from room temperature to about  $45^{\circ}C$ , the system shows its capability for both runtime software and hardware adaptation (see last column in Table 2.1). The voltage is boosted to compensate the performance loss. Software duty-cycle is reduced to compensate the increased power consumption. If the system is without hardware sensors and designed for the worst-case scenario (including process variations and temperature fluctuations), the number of iterations

<sup>&</sup>lt;sup>1</sup>The complete demo video can be found at http://nanocad.ee.ucla.edu/Main/Codesign

Figure 2.11: A snapshot of the demo hardware.

(DC), as in this demo, will be at most 18 (the case for Instance A after heat-up) with 1.865% calculation error. With the hardware sensors and adaptations, we are able to achieve 49 iterations and calculation error as small as 0.668%.

Table 2.1: System Demonstration Result Highlights

|                   | Instance A         | Instance B          | Instance A          |  |

|-------------------|--------------------|---------------------|---------------------|--|

|                   | (room temperature) | (room temperature)  | (after heat-up)     |  |

| Supply Voltage    | 0.93 V             | 0.96 V              | 0.96 V              |  |

| Active power      | 23.81 mW           | $24.29~\mathrm{mW}$ | $26.50~\mathrm{mW}$ |  |

| Sleep power       | 4.74 mW            | 1.63 mW             | 7.58 mW             |  |

| DC                | 27                 | 49                  | 18                  |  |

| Calculated $\pi$  | 3.1028             | 3.1206              | 3.2002              |  |

| Calculation error | 1.235%             | 0.668%              | 1.865%              |  |

## CHAPTER 3

# SlackProbe In Situ Monitoring Methodology

With *DDRO* methodology, replica monitors can predict global variation near perfectly. But the accuracy is still limited and constrained by local variation. In situ monitors can capture the actual path delay, including local variation, but usually incur significant overhead. We observe that most of existing work focuses on monitoring destination registers. In this chapter, we introduce a novel and flexible in situ monitoring methodology, *SlackProbe*, which inserts monitors at both path endpoints and path intermediate nets.

## 3.1 SlackProbe Introduction

With increasing amounts of manufacturing variability, ambient fluctuation and circuit wearout (e.g., NBTI, HCI etc.), it is necessary to identify chip delay either statically (e.g., speed binning) or dynamically with both hardware and software adaptive schemes [Gup12]. There are various classes of monitors that are targeted at measuring circuit path delay.

Canary or replica circuits [Dra07, Cha12a] are stand-alone circuits which are intended to mimic the timing behavior of the original circuits. The delay of the real circuit can be estimated through measuring delay of the replicas. Tunable [Tsc09] and design-dependent [Cha12a] replica circuits can reduce the mismatch of the real circuit and replica. Replica monitors are usually non-intrusive, but may fail to capture the variations that are local to real circuits such as random manufacturing variations and circuit aging.

In situ monitors measure the delay directly from the circuit paths. Fick et al. [Fic10] use

a Time-to-Digital Converter (TDC) to measure the critical path delay. Wang et al. [Wan08] measure delay by reconstructing the critical path as Ring-Oscillators (ROs). Another approach to measure circuit path delay is to measure the timing slack. Since critical paths typically end at registers, special flip-flops can be used as slack monitors. Razor [Ern03, Das09] uses customized flip-flops to detect timing failures due to setup time violation and correct them through a pipeline flush or architectural replay. Similar approaches that reduce timing margin, but not to the point of failure, include delaying data signals [Fuk09], advancing clock signals [Reb10] or using different flip-flop structures [Eir07, Kur10, Aga07, Das10, Sat07].

In situ monitors can accurately capture the real path delay, but with significant overhead, especially when large number of registers are timing critical. Some methods can be used to reduce the overhead (e.g., [Hir12]), but with a loss in accuracy. Better monitor designs, e.g., [Kim13], can also reduce the overhead, but are still fundamentally limited by the large number of monitors requited. We observe that existing methods focus exclusively on monitoring path endpoints (i.e., destination registers). In this work, we propose SlackProbe, a low overhead, in situ, on-line timing slack monitoring methodology. SlackProbe monitors in situ timing slack of selected circuit nets, including intermediate nets along circuit paths, which is more power and area efficient. This work is an extension of [Lai13]. The key contributions of our work include the following:

- (i) We propose a novel slack monitoring methodology allowing placing monitors at intermediate nets along circuit paths

- (ii) We develop a metric named "opportunism window", which allows us to flexibly select the set of critical paths to be monitored.

- (iii) We formulate and convert the path-based monitor insertion formulation into a edgebased Linear Programming (LP) problem and solve it near its theoretical lower bound

- (iv) We perform a thorough analysis of the potential benefits and caveats of such a monitoring methodology, including monitoring cost, monitoring efficiency and observability, timing margin and design perturbation.

The rest of the chapter is organized as follows: Section 3.2 gives an overview of the proposed monitoring methodology. Section 3.3 describes the critical path selection and circuit graph reduction process. Section 3.4 presents the monitor insertion problem formulation and solution. Section 3.5 discusses the monitor cost metrics and comparison between *SlackProbe* and conventional approaches. Section 3.6 presents the experimental results. Section 3.7 concludes this chapter.

#### 3.2 SlackProbe Overview

#### 3.2.1 Monitor Working Principle

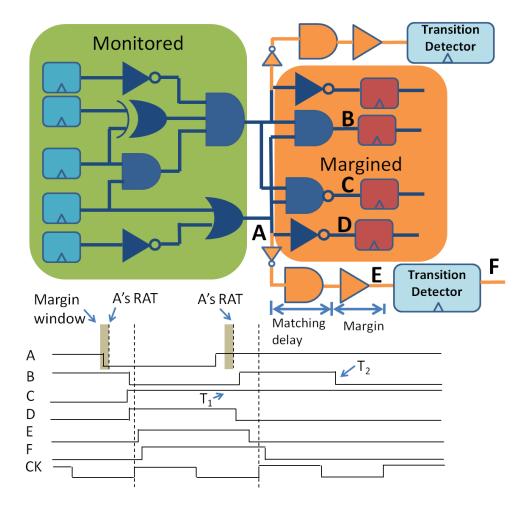

The monitor working principle is shown through an example in Fig. 3.1. If a monitor is inserted at an intermediate node A, a "probe", which consists of delay matching gates and a transition detector, is connected to A through a minimum size inverter. Signal transitions at node A are transferred through the delay chain to the transition detector and compared with the incoming clock edge. If the transition is close to its Required Arrival Time (RAT), i.e., within the margin window as in Fig. 3.1, a corresponding signal transition will arrive at node E after the clock edge. This triggers the transition detector and flags a signal indicating an impending delay failure.

The monitor inserted at node A is capable of monitor the delay of all critical paths passing through A. As shown in Fig. 3.1, instead of monitoring all four destination registers, SlackProbe can use only two monitors while achieving the same path coverage.

Different transition detector designs as in [Reb10, Bow09]. can be applied here. Slack-Probe also allows monitors to be inserted at path endpoints where monitors as in [Ern03, Das09, Fuk09, Eir07] can be used as well. Since the additional margin makes the monitor detect an impending timing failure rather than an actual one, there is no datapath metastability issue as raised and discussed in [Bow09]. The metastability issue of the monitor signal either results in a more pessimistic detection or is guardbanded by the monitor delay margin.

Figure 3.1: SlackProbe working principle. As shown in the timing diagram, compared to inserting monitors at destination registers, the monitor inserted at A can monitor the path delay even when the transition does not propagate to the destination register (i.e.,  $T_1$  at C). But the monitor inserted at node A cannot capture transitions that do not pass through A (i.e.,  $T_2$  at B).

## 3.2.2 Monitor Insertion Flow

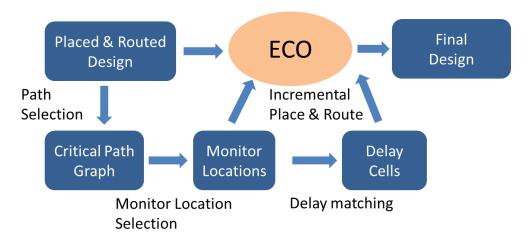

With the proposed monitoring strategy, the problem now becomes *when*, *where* and *how* to insert these monitors. In this work, we propose the monitor insertion flow as in Fig. 3.2. Different alternatives will also be discussed and compared against conventional approaches.

Monitor insertion starts with a placed and routed design, as the timing information is more accurate at this stage. Since we only care about timing-critical paths, a path selection process is applied to extract timing-critical paths and to construct the critical path graph. Then, monitor locations are picked from the graph using our proposed method. For each of the monitor locations, a delay cell path is synthesized. The final insertion flow is similar to Engineering Change Order (ECO) where the monitors are incrementally placed and routed. ECO metrics like those in [Lee12] are applied when picking monitor locations to minimize the perturbation to the original design.

Figure 3.2: Monitor insertion flow

#### 3.2.3 Possible Applications of the Monitors

Since different applications will have different requirements for the monitor, we discuss possible monitor applications here as examples before introducing the detailed implementation flow.

One possible application is to use the monitors as timing-failure event predictors and combine them with some of the existing error resilience mechanisms like in [Das09, Cho14, Foj13]. In this case, the monitors have to capture all signal transition events that may result in timing errors.

Another possible application is to use the monitors as speed sensors which indicate whether current operation condition is close to possible timing failure or not. This can be used by systems with adaptation capabilities like Adaptive Voltage Scaling (AVS), Adaptive Body Bias (ABB) or Dynamic Voltage and Frequency Scaling (DVFS) to account for manufacturing variations, ambient conditions as well as circuit aging effects such as Negative Bias Temperature Instability (NBTI), Positive Bias Temperature Instability (PBTI) and Hot-Carrier Injection (HCI). Since variations are either static or changing slowly, the monitor requirements can be relaxed to capture only the delay changes instead of all transition events.

## 3.3 Path Selection and Graph Reduction

## 3.3.1 Path Selection Criteria

As shown in Fig. 3.2, given a placed and routed design, the first step is to identify the part of the design that may be timing critical. Depending on the application, different criticality criteria may be applied for the selection process.

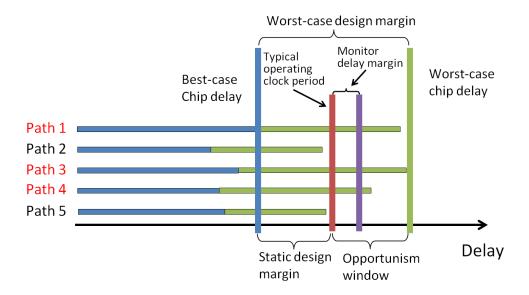

In this work, we propose a flexible path selection method by introducing user-defined opportunism window. As illustrated in Fig. 3.3, opportunism window and monitor margin (discussed in detail in Section 3.4.1) will dictate the potential monitoring benefits. Typical worst-case design sets its delay margin for the worst-case scenario, i.e., all chips will run at a frequency slow enough for the worst-case chip delay regardless of what the actual delay is. In the presence of monitors, we may reduce the design margin and decrease the default operating clock period should be selected and monitored. The amount of design margin reduction is called opportunism window, within which the circuit will operate opportunistically at its best effort. The size of opportunism window determines the total number of circuit paths to be monitored, thus affecting the monitoring overhead. There is a natural trade-off between monitoring

benefits and monitoring overhead when deciding the *opportunism window* and monitor delay margin. We will discuss and explore this trade-off in later sections and experiments.

This path selection method does not require any knowledge of correlation in the variations between the delay of different paths. Therefore, it can be used to select paths for applications like aging sensors, where exact delay degradations are context dependent with little preassumed correlation.

Another possible path selection method is based on the process corners as described in [Lai13], where paths are selected based on their timing slacks at particular process corners. Other path selection methods such as statistical methods [Xie10] can also be used in SlackProbe depending on the specific applications.

Figure 3.3: Opportunism window is the margin saving comparing to worst-case design. Monitor delay margin is the delay margin of the delay matching chain which will be discussed in detail in Section 3.4.1.

## 3.3.2 Circuit Graph Reduction

Although opportunism window is a path-based criteria, we can utilize the block-based property of Static Timing Analysis (STA) and construct a circuit graph which contains all the selected critical paths.

If a path is selected as timing critical as illustrated in Fig. 3.3, the path's worst-case delay falls into the *opportunism window*. Equivalently, if we run STA using the worst-case corner library, it will also imply that the path's timing slack at the worst-case corner is smaller than the size of *opportunism window*. Based on the following two key properties of STA:

- (i) The slacks of all pins along a path are equal or smaller than slack of the path

- (ii) The slack of a path equals to the largest slack of all pins along that path

We can obtain a reduced circuit graph by removing the pins with slacks larger than the size of opportunism window and then removing the unconnected gates/nets. The critical paths in the original circuit graph are still preserved in the reduced graph because of property 1. All paths in the reduced graph are timing critical because of property 2. Therefore, we can work on the reduced graph instead of the original circuit graph when analyzing the monitor insertion. Unless otherwise specified, circuit graph discussed in the rest of the chapter refers to the reduced graph.

## 3.4 Monitor Location Selection

In this section, we describe our proposed monitor location selection method. We first discuss how monitors interact with different paths. Then we formulate the monitor location selection problem and describe our proposed solution.

## 3.4.1 Monitor Coverage and Delay Margin

After selecting the critical paths and obtaining the reduced circuit graph, *SlackProbe* will determine the set of candidate locations for monitor insertion. Before analyzing the location selection problem, we first discuss how paths are monitored by the inserted slack monitors.

## 3.4.1.1 Delay Margin for Paths

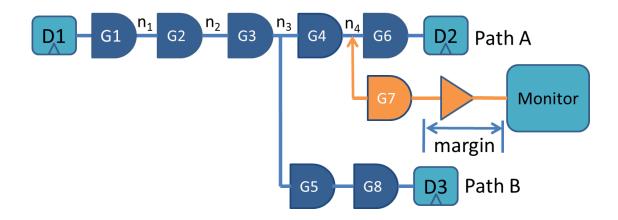

If the monitor is placed at some intermediate net, the path delay before the monitor can be captured by the monitor. But some extra delay margin will be required for the remaining part of the path. As shown in Fig. 3.4, there are three types of relations between monitor and a path:

- (i) The path passes through the net, for example path A in Fig. 3.4. Since the delay up to G4 can be captured by the monitor, the delay path should account for the delay uncertainty of G6.

- (ii) The path branches out at some net before the monitor, for example path B in Fig. 3.4. Depending on the application and gate type of G4, the monitor may be treated as being inserted between G3 and G5 with G4 as part of the delay matching. If the application is speed sensing, path B can be considered as being monitored with delay uncertainty of G4, G5 and G8. If the application is event detection, only G4 with gate types that are transparent to signal transitions (e.g., inverter, buffer) are allowed.

- (iii) None of the path instances fall in the fan-in cone of the monitor net. In this case, we consider that the path is not monitored.

## 3.4.1.2 Delay Margin for Monitors

Although different paths may require different delay margin, each monitor will have only one margin matching chain. The monitor margin should account for worst delay uncertainty after

Figure 3.4: Example of path-monitor pairs

monitor insertion point and guarantee that the delay chain is always slower than margined part of monitored circuit paths.

In the example in Fig. 3.4, the delay margin should account for the mismatch between original path (i.e., from  $n_4$  to  $D_2$ ) and delay matching chain (i.e., from  $n_4$  to the monitor). Theoretically, the best case delay of the delay matching chain should match the worst case delay of the original path. But this may be too pessimistic since the delay is likely to be correlated. Similar to on-chip variation modeling, in this work the delay chain is designed so that its delay at typical process corner matches the worst case delay of the original path. In Fig. 3.4, the equivalent delay margin in this case equals the delay of  $G_6$  at slow process corner (i.e., delay of the delay matching chain at typical process corner) minus the delay of  $G_6$  at typical process corner. This margin is considered as the delay uncertainty of  $G_6$ .

The required delay margin for each circuit nets can be calculated based on conventional STA tool flow. We first perform timing analysis using typical process corner libraries and obtain the arrival time  $d_i^{tt}$  and timing slack  $s_i^{tt}$  for each net. Then we perform timing analysis using slow process corner libraries and obtain the arrival time  $d_i^{ss}$  and timing slack  $s_i^{ss}$  as well. The required delay margin can be derived by:

$$Margin_i = (s_{tt} - s_{ss}) - (d_{ss} - d_{ss})$$

(3.1)

Methods as in [Cha12a] or [Tsc09] can also be applied to synthesize a replica-like path to reduce the margin for delay mismatch due to global variation.

## 3.4.1.3 Overall Margin

Because the final delay margin for the entire circuit will be dominated by the monitor with the largest margin, we define the delay margin cost as the maximum monitor delay margin constraint  $\epsilon$  on each monitor. The delay margin  $\epsilon$  is used to determine the set of feasible monitor candidate locations and the corresponding circuit nets that can be monitored.

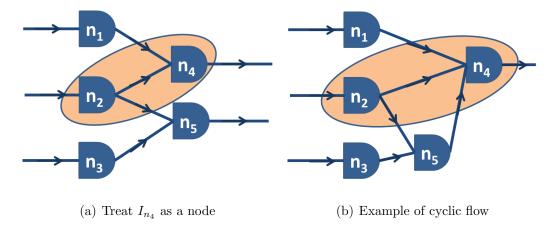

For example, for a given  $\epsilon$ , we can analyze the implication of inserting a monitor at a net  $n_i$ . If the margin required by  $n_i$  is smaller than  $\epsilon$ , all paths passing through  $n_i$  will be monitored. Depending on the application, we may also want to consider another net  $n_j$  in the fan-in cone of  $n_i$  (like  $n_3$  in Fig. 3.4). If the margin required by paths branching out at  $n_j$  is also smaller than  $\epsilon$  (like path B in Fig. 3.4),  $n_j$  can also be monitored by the monitor at  $n_i$ . All paths passing through  $n_j$  will be monitored. Therefore, we can define a set  $I_{n_i}$  as the nets that can be included as being monitored by the monitor at  $n_i$ .

If we represent a path as the set of nets it passes through, the timing margin constraint can be stated as: with a given monitor delay margin constraint  $\epsilon$ , for any critical path  $P_k$ , there exists a monitor at net  $n_i$ , such that  $P_k \cap I_{n_i} \neq \emptyset$ . For different candidate locations, monitor insertion may have different cost in terms of power, design perturbation etc. Here we use  $c_i$  as the cost associated with net  $n_i$ . The detailed derivation of  $c_i$  will be discussed in Section 3.5.

#### 3.4.2 Problem Formulation