# UC San Diego UC San Diego Electronic Theses and Dissertations

# Title

Machine Learning Techniques for Data Storage Systems: Modeling, Coding, and Detection

# Permalink

https://escholarship.org/uc/item/0v184594

# Author

Zheng, Simeng

# Publication Date

2024

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA SAN DIEGO

#### Machine Learning Techniques for Data Storage Systems: Modeling, Coding, and Detection

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

Electrical Engineering (Communication Theory and Systems)

by

Simeng Zheng

Committee in charge:

Professor Paul H. Siegel, Chair Professor Ramesh Rao Professor Steven J. Swanson Professor Nuno Vasconcelos

Copyright Simeng Zheng, 2024 All rights reserved. The Dissertation of Simeng Zheng is approved, and it is acceptable in quality and form for publication on microfilm and electronically.

University of California San Diego

2024

### DEDICATION

To my loves

| Dissertat             | ion Approv                             | al Page                                                                                                             | iii                        |

|-----------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------|

| Dedicati              | on                                     |                                                                                                                     | iv                         |

| Table of              | Contents .                             |                                                                                                                     | v                          |

| List of F             | igures                                 |                                                                                                                     | viii                       |

| List of T             | ables                                  |                                                                                                                     | xii                        |

| Acknow                | ledgements                             |                                                                                                                     | xiii                       |

| Vita                  |                                        |                                                                                                                     | xvii                       |

| Abstract              | of the Diss                            | ertation                                                                                                            | xix                        |

| Chapter<br>1.1<br>1.2 | Data Stora                             | luction                                                                                                             | 1<br>2<br>3                |

| Chapter<br>2.1<br>2.2 | Measurem                               | Characterization Platform                                                                                           | 6<br>7<br>9                |

| Chapter<br>3.1<br>3.2 | Introduction<br>Flash Mem<br>3.2.1 Fla | Gen: Spatio-temporal Generator for Flash Memory Systems<br>on<br>hory and Spatio-temporal Noise<br>sh Memory Basics | 10<br>11<br>14<br>14       |

| 3.3                   | Flash-Gen<br>3.3.1 Fla<br>3.3.2 Spa    | atio-temporal CharacteristicsFormulationSh-Gen Architecture Formulationatio-temporal Fusionplementation Details     | 16<br>18<br>19<br>20<br>21 |

| 3.4                   | Flash-Gen 3.4.1 Fla                    | Coding Workflow                                                                                                     | 24<br>24<br>29             |

| 3.5                   | Statistical 2.3.5.1 Dis                | Analysis of Flash-Gen<br>stribution Analysis<br>or Rate Estimation                                                  | 30<br>31<br>34             |

| 3.6                   | Performane<br>3.6.1 LD<br>3.6.2 De     | ce of Flash-Gen Coding Workflow<br>PC Decoding Performance<br>sign of Constrained Codes<br>scussion                 | 36<br>36<br>40<br>42       |

### TABLE OF CONTENTS

| 3.7                                                    | Conclusion                                                              | 42  |  |

|--------------------------------------------------------|-------------------------------------------------------------------------|-----|--|

| Chapter 4 Optimal Shaping Codes for a TLC Flash Memory |                                                                         |     |  |

| 4.1                                                    |                                                                         | 45  |  |

| 4.2                                                    |                                                                         | 47  |  |

| 4.3                                                    |                                                                         | 50  |  |

|                                                        |                                                                         |     |  |

| Chapte                                                 | Efficient Constrained Codes That Enable Page Separation in Modern Flash |     |  |

|                                                        | Memories                                                                | 52  |  |

| 5.1                                                    | Introduction                                                            | 53  |  |

| 5.2                                                    | Patterns, Mapping, and 2D RR Coding                                     | 56  |  |

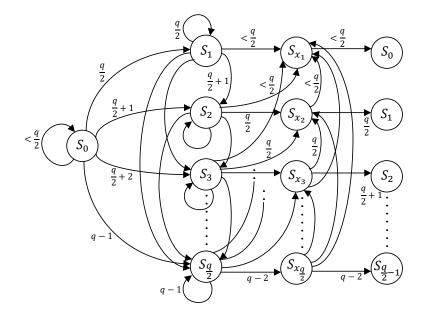

| 5.3                                                    | RR-LOCO Coding Over GF(2)                                               | 60  |  |

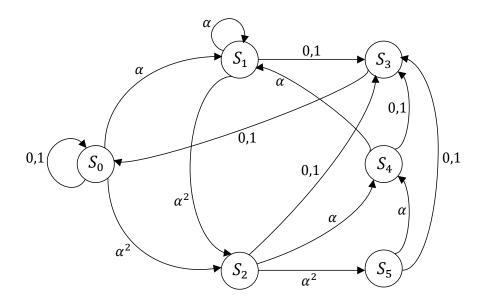

| 5.4                                                    | RR-LOCO Coding Over $GF(4)$                                             | 64  |  |

| 5.5                                                    | Rate, Complexity, and Error Propagation                                 | 72  |  |

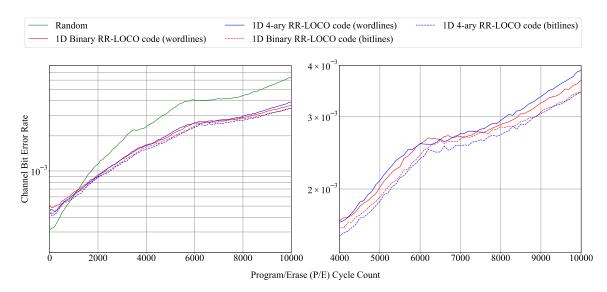

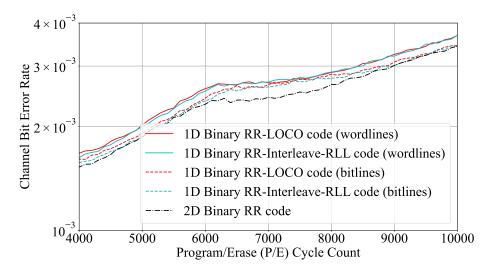

| 5.6                                                    |                                                                         | 81  |  |

| 5.7                                                    | Conclusion                                                              | 87  |  |

|                                                        |                                                                         |     |  |

| Chapte                                                 | er 6 Code-Aware Storage Channel Modeling via Machine Learning           | 88  |  |

| 6.1                                                    | Introduction                                                            | 89  |  |

| 6.2                                                    | NAND Flash Memory and ICI Mitigation                                    | 90  |  |

|                                                        | 6.2.1 NAND Flash Memory Basics                                          | 90  |  |

|                                                        | 6.2.2 ICI Mitigation via Constrained Coding                             | 92  |  |

| 6.3                                                    | Code-aware Storage Channel Modeling                                     | 93  |  |

|                                                        | 6.3.1 Review of Generative Flash Modeling                               | 93  |  |

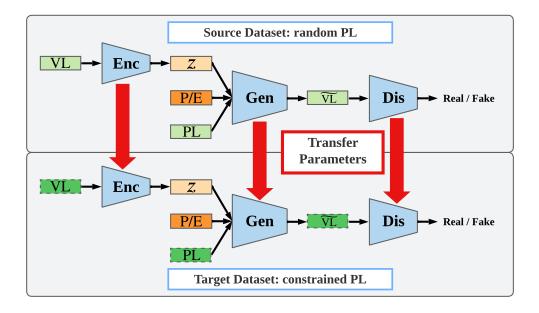

|                                                        | 6.3.2 Code-aware Generative Flash Modeling                              | 94  |  |

|                                                        | 6.3.3 Transfer Learning Configuration                                   | 95  |  |

| 6.4                                                    | Experimental Results and Analysis                                       | 96  |  |

|                                                        | 6.4.1 Experimental Settings                                             | 97  |  |

|                                                        | 6.4.2 PDF Analysis                                                      | 99  |  |

|                                                        | 6.4.3 Iteration Number Analysis                                         | 102 |  |

| 6.5                                                    | Conclusion                                                              | 102 |  |

|                                                        |                                                                         |     |  |

| Chapte                                                 | PR-NN: RNN-based Detection for Coded Partial-Response Channels          | 104 |  |

| 7.1                                                    | Introduction                                                            | 105 |  |

|                                                        | 7.1.1 Background on magnetic recording                                  | 105 |  |

|                                                        | 7.1.2 Machine learning for coded communication                          | 107 |  |

|                                                        | 7.1.3 Our Contribution                                                  | 108 |  |

| 7.2                                                    | System Architecture and Detectors                                       | 109 |  |

|                                                        | 7.2.1 System model                                                      | 109 |  |

|                                                        | 7.2.2 Digital channel implementation                                    | 114 |  |

|                                                        | 7.2.3 Signal Detection Methods                                          | 116 |  |

|                                                        | 7.2.4 Detector implementation details                                   | 118 |  |

| 7.3                                                    | •                                                                       | 120 |  |

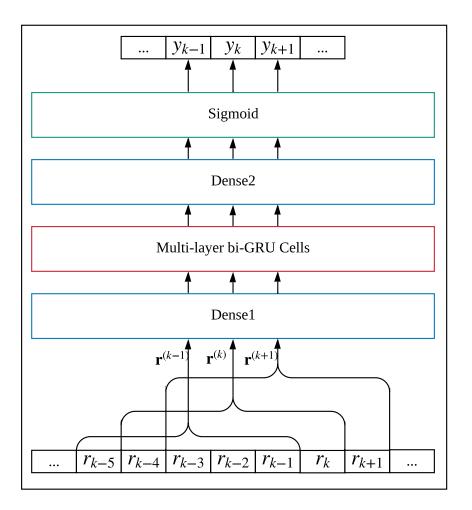

|                                                        | 7.3.1 Neural Network Architecture                                       | 121 |  |

|                | 7.3.2  | Data Acquisition                                     | 127 |

|----------------|--------|------------------------------------------------------|-----|

|                | 7.3.3  | Training Methodology                                 | 129 |

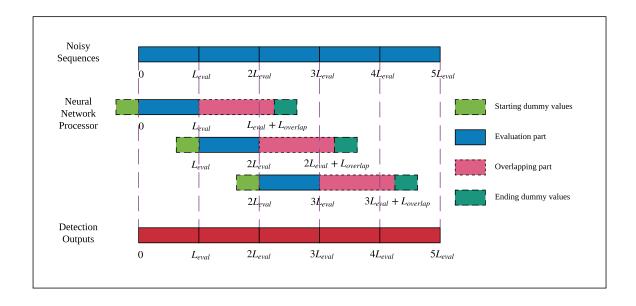

|                | 7.3.4  | Evaluation Process                                   | 129 |

|                | 7.3.5  | Computational Complexity Analysis                    | 131 |

| 7.4            | Experi | mental Results                                       | 132 |

|                | 7.4.1  | Experimental Setup                                   | 133 |

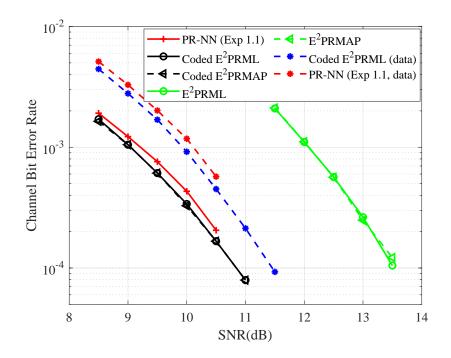

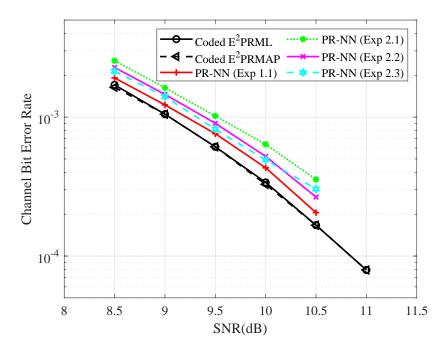

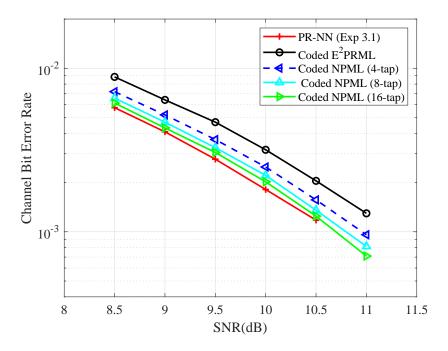

|                | 7.4.2  | Scenario 1: Individual Training Experiments          | 133 |

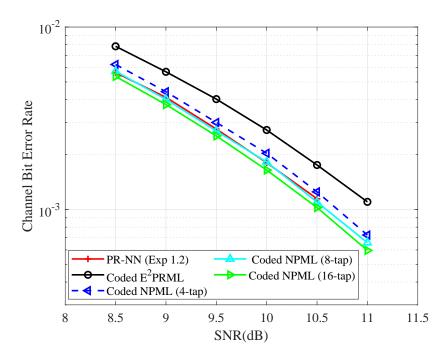

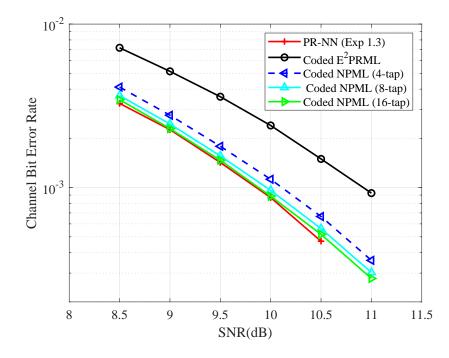

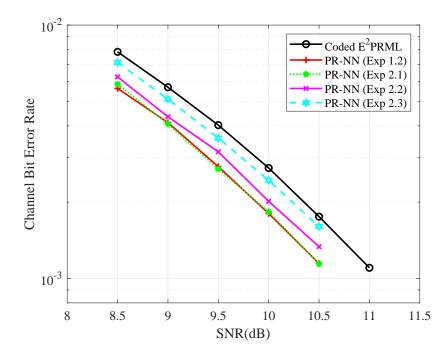

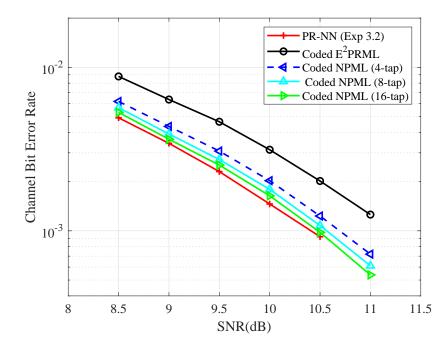

|                | 7.4.3  | Scenario 2: Joint Training Experiments               | 135 |

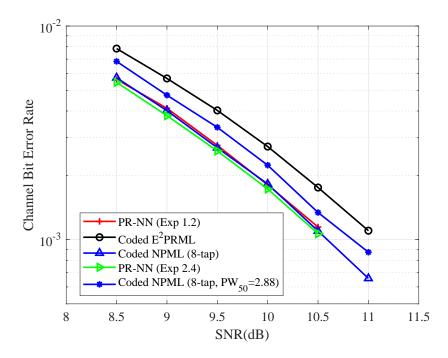

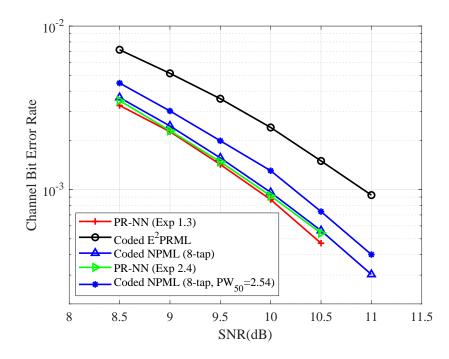

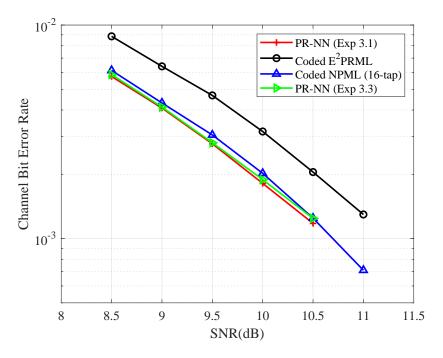

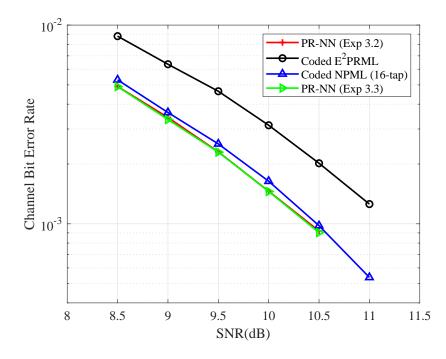

|                | 7.4.4  | Scenario 3: "Realistic" Equalized Lorentzian Channel | 142 |

|                | 7.4.5  | Experimental Analysis                                | 143 |

| 7.5            | Conclu | sion                                                 | 143 |

| 7.6            | Append | dix                                                  | 144 |

| Bibliography 1 |        |                                                      | 146 |

### LIST OF FIGURES

| Figure 2.1.  | The FPGA testboard is the flash characterization platform                                                                                                                                                | 8  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.2.  | The system of coding incorporation module on flash characterization plat-<br>form.                                                                                                                       | 9  |

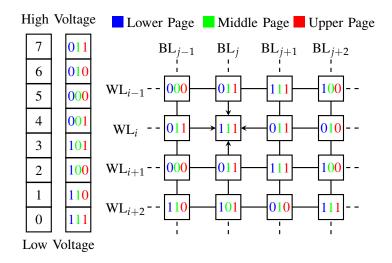

| Figure 3.1.  | Example mapping of cell program levels to binary representations in TLC flash and schematic diagram of a 2-D TLC flash memory block                                                                      | 15 |

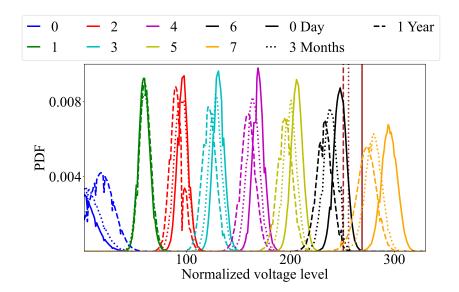

| Figure 3.2.  | PDF visualizations of a 3D TLC NAND flash memory for measured voltage levels at three retention time stamps.                                                                                             | 16 |

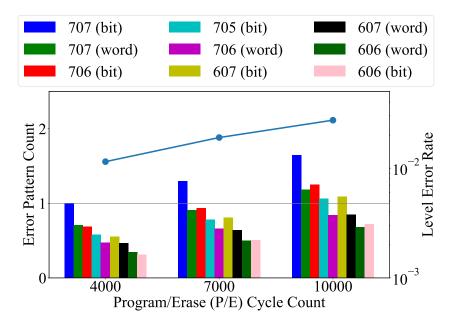

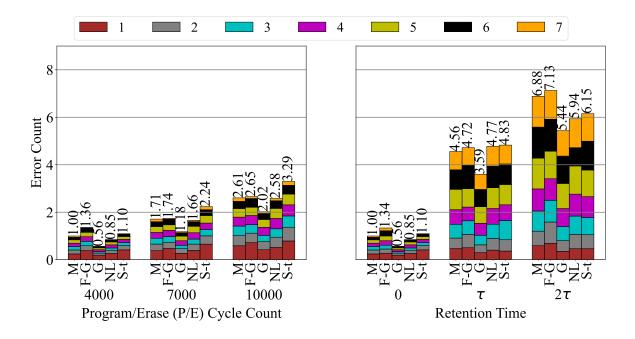

| Figure 3.3.  | Count of top error-prone patterns and level error rate at selected P/E cycles without retention. The error pattern counts are normalized by the count of pattern 707 in BL direction at 4000 P/E cycles. | 17 |

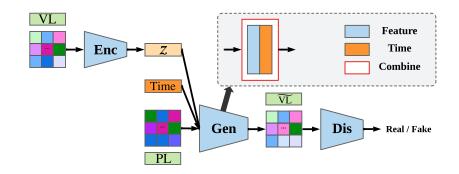

| Figure 3.4.  | Flash-Gen architecture: encoder, generator, and discriminator constitute the generative modeling architecture.                                                                                           | 19 |

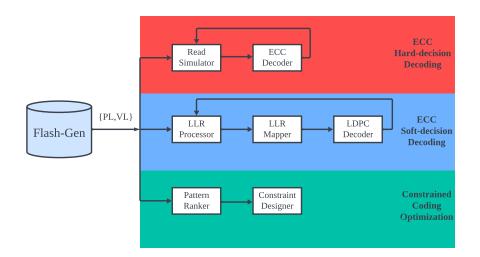

| Figure 3.5.  | Flash-Gen coding workflow: Flash-Gen error correction coding workflow with hard-decision decoding mode and soft-decision decoding mode, and Flash-Gen constrained coding workflow.                       | 25 |

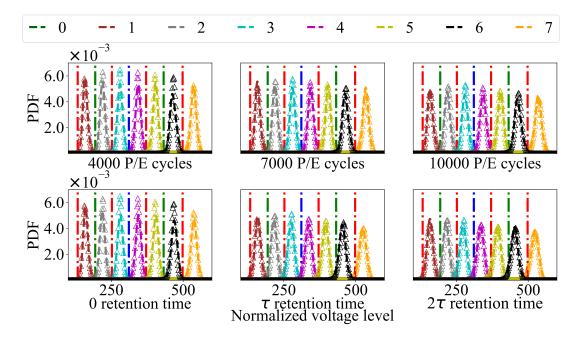

| Figure 3.6.  | PDF visualizations for measured and Flash-Gen generated voltage levels at various time stamps: 4000, 7000, and 10000 P/E cycles; 0, $\tau$ , and $2\tau$ retention time.                                 | 31 |

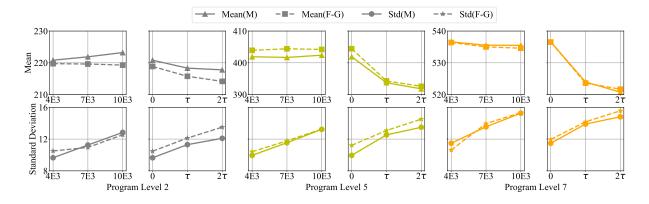

| Figure 3.7.  | Change in mean and standard deviation values for PL at 2, 5, and 7 when P/E cycle count or retention time increases.                                                                                     | 33 |

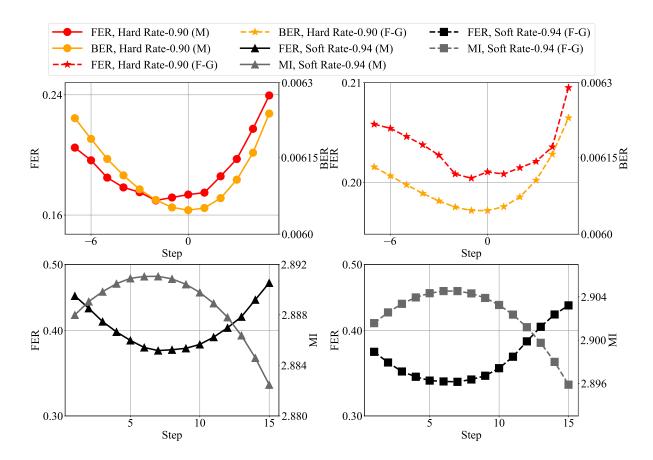

| Figure 3.8.  | Total error rates of measured ('M'), Flash-Gen ('F-G'), Gaussian ('G'),<br>Normal-Laplace ('NL'), Student's t ('S-t') model                                                                              | 34 |

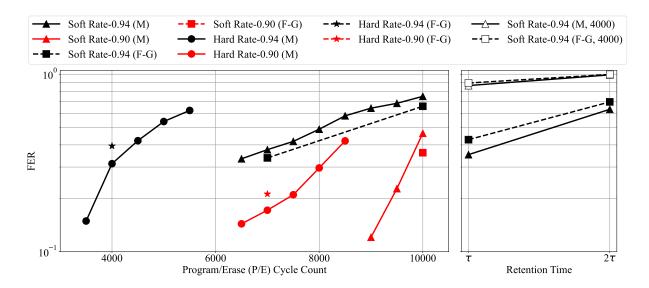

| Figure 3.9.  | Frame error rate (FER) comparison with LDPC codes of measured data and Flash-Gen reconstructed dataset.                                                                                                  | 37 |

| Figure 3.10. | Variations in the hard-decision decoding threshold and soft-decision de-<br>coding thresholds change the decoding performance and the metric values.                                                     | 39 |

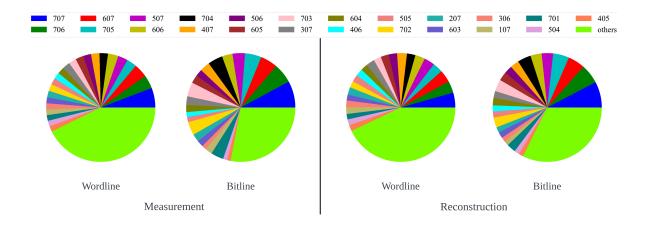

| Figure 3.11. | Pie charts showing pattern-dependent error probabilities for measured and Flash-Gen generated voltages at 7000 P/E cycles.                                                                               | 40 |

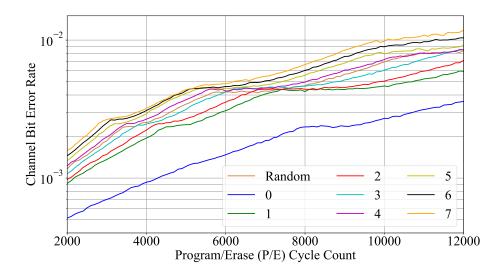

| Figure 4.1. | Measured BER of pseudorandom data after inducing wear with data that<br>is dominated by a single program level from P/E cycle 2000 to P/E cycle<br>12000.                                                 | 46  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

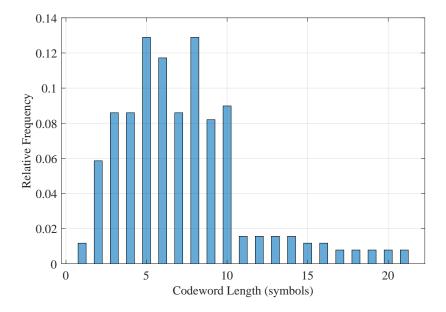

| Figure 4.2. | Histogram of codeword length in optimal shaping codes with codebook size 256.                                                                                                                             | 48  |

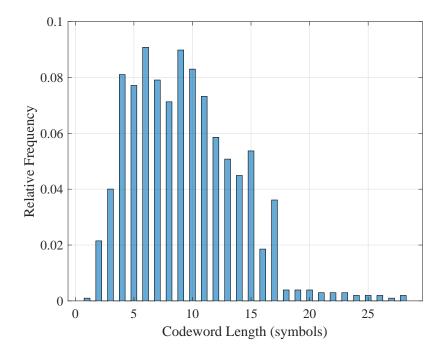

| Figure 4.3. | Histogram of codeword length in optimal shaping codes with codebook size 1024.                                                                                                                            | 49  |

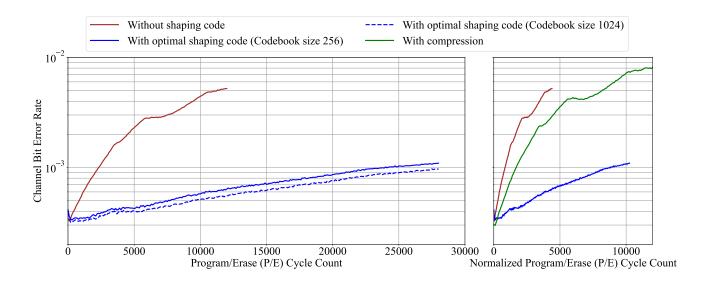

| Figure 4.4. | Measured channel BER comparison of data without shaping code, with optimal shaping codes (codebook sizes $256$ and $1024$ ), and with compression.                                                        | 50  |

| Figure 5.1. | The left-most pages of a 2D Flash grid with data encoded via the proposed 2D binary RR coding scheme. Symbol $x$ means bit can be 0 or 1 freely                                                           | 59  |

| Figure 5.2. | An FSTD of a 1D constrained sequence forbidding level patterns in $\mathcal{L}_q$ , for any $q$ . Here, we operate directly on level patterns for simplicity                                              | 74  |

| Figure 5.3. | An FSTD of a 1D 4-ary constrained sequence forbidding patterns in $\mathcal{R}^4$                                                                                                                         | 76  |

| Figure 5.4. | Measured channel BER comparison of random data, 1D binary RR-LOCO coded data along wordlines or bitlines, and 1D 4-ary RR-LOCO coded data along wordlines or bitlines                                     | 83  |

| Figure 5.5. | Measured channel BER comparison of 1D binary RR-LOCO coded data,<br>1D binary interleaved RLL-(0, 1) coded data along wordlines or bitlines,<br>2D binary RR coded data.                                  | 83  |

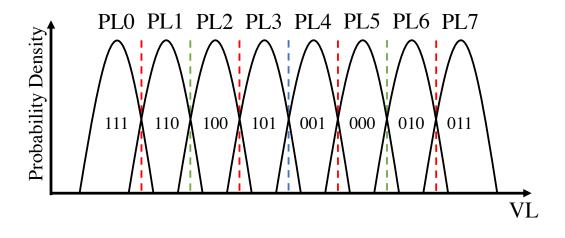

| Figure 6.1. | Voltage distributions and a recursive alternate Gray mapping (RAGM) between cell program levels and binary logic values of a TLC NAND flash memory.                                                       | 91  |

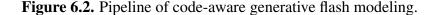

| Figure 6.2. | Pipeline of code-aware generative flash modeling.                                                                                                                                                         | 94  |

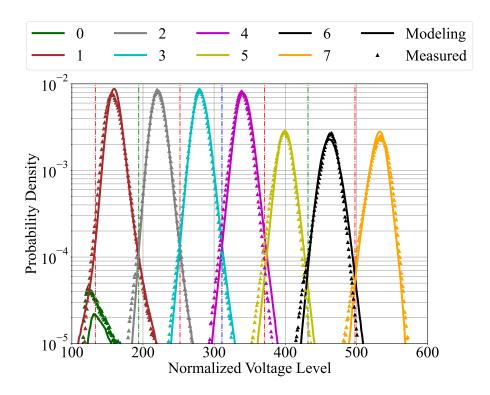

| Figure 6.3. | PDF plots in logarithmic scale for measured and regenerated voltage levels (experiment I-Pre/T-WL/E-WL) at 7000 P/E cycles. The visualization is based on dataset $\{(PL^{S_{WL}}, VL^{S_{WL}}, P/E)\}$ . | 100 |

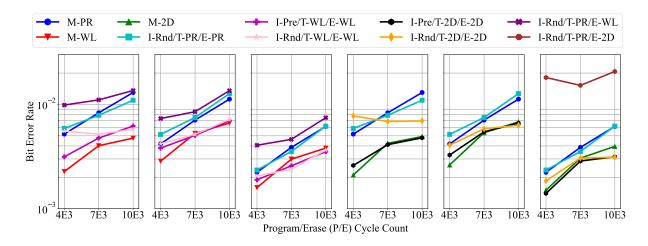

| Figure 6.4. | BER comparisons: the leftmost (resp., rightmost) three sub-figures show lower, middle, and upper page BERs for $S_{WL}$ -coded (resp., $S_{2D}$ -coded) data.                                             | 101 |

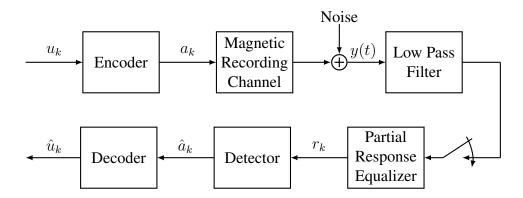

| Figure 7.1. | System architecture.                                                                                                                                                                                      | 109 |

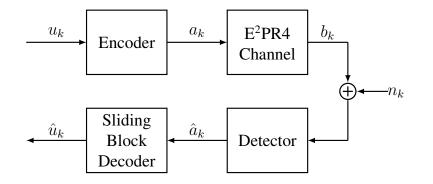

| Figure 7.2. | Discrete model for simulation, where $n_k$ represents the additive distortion.                                                                                                                            | 113 |

| Figure 7.3.  | $(1,\infty)$ -RLL input-constrained E <sup>2</sup> PR4 channel state machine                                                                                                | 116 |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

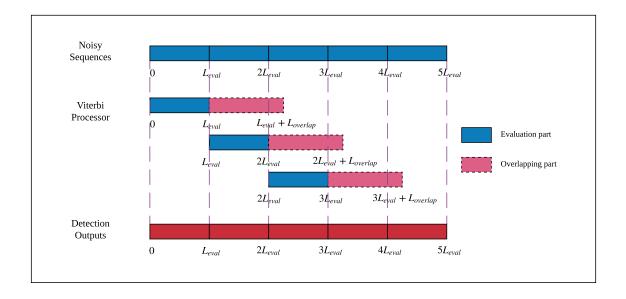

| Figure 7.4.  | Sliding-window evaluation process for Viterbi detection                                                                                                                     | 120 |

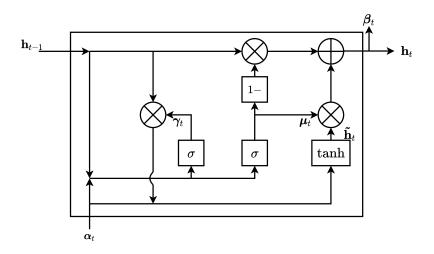

| Figure 7.5.  | Structure of one GRU cell.                                                                                                                                                  | 122 |

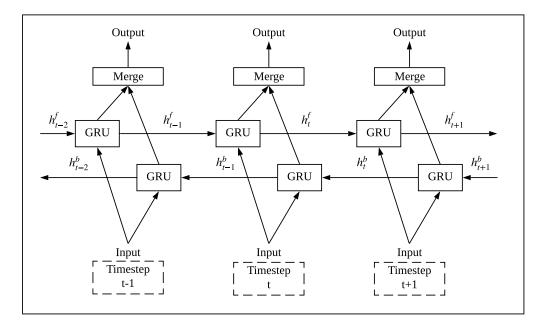

| Figure 7.6.  | Structure of unfolded bi-directional GRUs                                                                                                                                   | 123 |

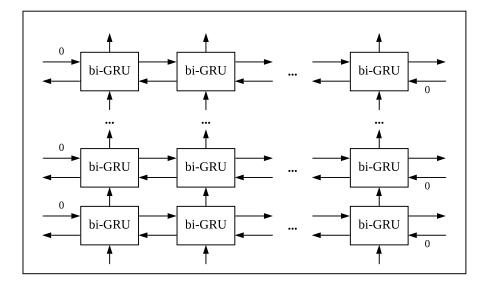

| Figure 7.7.  | Model of multi-layer bi-directional GRUs.                                                                                                                                   | 124 |

| Figure 7.8.  | Network architecture for proposed PR-NN                                                                                                                                     | 126 |

| Figure 7.9.  | Sliding-window evaluation process for PR-NN detector.                                                                                                                       | 130 |

| Figure 7.10. | Scenario 1: Individual training with AWGN.                                                                                                                                  | 135 |

| Figure 7.11. | Scenario 1: Individual training with ACN (for two channel densities) when $PW_{50}/T_c = 2.54$                                                                              | 136 |

| Figure 7.12. | Scenario 1: Individual training with ACN (for two channel densities) when $PW_{50}/T_c = 2.88$                                                                              | 136 |

| Figure 7.13. | Scenario 2: Joint training with AWGN and ACN ( $PW_{50}/T_c = 2.54$ ) and evaluation on AWGN.                                                                               | 137 |

| Figure 7.14. | Scenario 2: Joint training with AWGN and ACN ( $PW_{50}/T_c = 2.54$ ) and evaluation on ACN ( $PW_{50}/T_c = 2.54$ ).                                                       | 137 |

| Figure 7.15. | Scenario 2: Joint training with ACN when $PW_{50}/T_c = 2.54$ and ACN when $PW_{50}/T_c = 2.88$ and evaluation on ACN when $PW_{50}/T_c = 2.54$                             | 138 |

| Figure 7.16. | Scenario 2: Joint training with ACN when $PW_{50}/T_c = 2.54$ and ACN when $PW_{50}/T_c = 2.88$ and evaluation on ACN when $PW_{50}/T_c = 2.88$                             | 138 |

| Figure 7.17. | Scenario 3: Individual training with "realistic" datasets at $PW_{50}/T_c = 2.54$<br>and evaluation on "realistic" datasets at $PW_{50}/T_c = 2.54$                         | 139 |

| Figure 7.18. | Scenario 3: Individual training with "realistic" datasets at $PW_{50}/T_c = 2.88$<br>and evaluation on "realistic" datasets at $PW_{50}/T_c = 2.88$                         | 139 |

| Figure 7.19. | Scenario 3: Joint training with "realistic" datasets for both $PW_{50}/T_c = 2.54$ and $PW_{50}/T_c = 2.88$ and evaluation on "realistic" datasets for $PW_{50}/T_c = 2.54$ | 140 |

| Figure 7.20. | Scenario 3: Joint training with "realistic" datasets for both $PW_{50}/T_c =$ |     |

|--------------|-------------------------------------------------------------------------------|-----|

|              | 2.54 and $PW_{50}/T_c = 2.88$ and evaluation on "realistic" datasets for      |     |

|              | $PW_{50}/T_c = 2.88$                                                          | 140 |

### LIST OF TABLES

| Table 4.1. | Symbol Probabilities and Costs for Optimal Shaping Codes                                                                                                                | 48  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 5.1. | Capacity Comparison Between $C_{\mathcal{L}_q}^{1D}$ , 1D Binary RR Capacity $C_{RR2}^{1D}$ , and 1D 4-ary RR Capacity $C_{RR4}^{1D}$                                   | 73  |

| Table 5.2. | Comparisons of Rate, Complexity, and Error Propagation at the Same Length Between 2D RR and 1D Binary RR Constrained Coding Schemes .                                   | 79  |

| Table 5.3. | Comparisons of Minimum Coded Data, Complexity, and Error Propaga-<br>tion to Achieve Certain Rate Between 1D Binary RR and 1D 4-ary RR<br>Constrained Coding Schemes    | 80  |

| Table 6.1. | Numerical Values of Pattern-Dependent Error Rates for the Most Severe ICI Patterns                                                                                      | 91  |

| Table 6.2. | Sizes of Training and Evaluation Datasets                                                                                                                               | 96  |

| Table 6.3. | Modeling Experiments and Training Iterations                                                                                                                            | 98  |

| Table 6.4. | Total Variation Distance                                                                                                                                                | 99  |

| Table 7.1. | Starting and Ending Dummy Values for Each State in the Coded E <sup>2</sup> PR4<br>State Machine. "Unknown" Means Unknown Starting or Ending State for<br>the Sequence. | 128 |

| Table 7.2. | Batch Size Settings for the Training Datasets and Evaluation Cases in Each Experiment of the Three Scenarios                                                            | 134 |

#### ACKNOWLEDGEMENTS

I would like to thank many people for understanding, supporting, and helping me during my Ph.D. life at UCSD. It is challenging that half of my Ph.D. time was spent during the COVID pandemic.

First and foremost, I would like to sincerely thank my advisor, Professor Paul H. Siegel. As a lecturer, He is a professional advisor in coding theory series courses, leading us from course to research problems. he is the most responsible lecturer in ECE 250 and I am lucky to be the TA in his course. As an advisor, his insights on data storage and his guidance on research help me realize and overcome technical challenges in HDD and SSD. I am also grateful for all the on-campus, beach, thanksgiving, and virtual parties we have ever enjoyed. Paul is a devoted researcher, a brilliant mentor, a passionate lecturer, and a kind friend. I am deeply grateful to be his student.

I would appreciate many professors for their help over the years. I must thank Nuno Vasconcelos for the extraordinary machine learning series courses and for serving on my preliminary exam committee and defense committee. I would express my gratitude to Ramesh Rao for the valuable TA opportunity in ECE 250 and for serving on my preliminary exam committee and defense committee. I would appreciate Steven Swanson for serving on my defense committee and for organizing NVMW. I would like to thank Alon Orlitsky for the information theory course and for hosting beautiful ITA workshops. I am thankful for all lecturers: Robert Lugannani, Laurence B. Milstein, Young-Han Kim, Alexander Vardy, Xinyu Zhang, Manuela Vasconcelos, Todd Kemp, Niema Moshiri, Pengtao Xie, and Bryan Chin. I particularly enjoyed interesting discussions with Anxiao (Andrew) Jiang in ITA and NVMW. I am indebted to Ahmed Hareedy and Robert Calderbank for our wonderful collaboration on read-and-run constrained codes. I would thank Richard Wesel for organizing NASIT 2022 at UCLA and giving me an unforgettable information theory summer school. I would like to thank Brian M. Kurkoski for the stimulating discussion on ITA graduation day. I would thank Paul H. Siegel, Tara Javidi, Alon Oslitsky, and Ken Zeger for selecting me as the recipient of the 2023-2024 Shannon Graduate Fellowship. I sincerely appreciate Qin Huang at Beihang University for introducing me to the world of coding theory and giving me courage to explore further in this fantastic field.

It has been an exceptional experience for me to collaborate with those talented researchers: Yi Liu, Michael Baluja, Ahmed Hareedy, Robert Calderbank, Chih-Hui Ho, Wenyu Peng, Andrew Tan, Carolina Fernández, Ismael González Valenzuela. I am grateful to CMRR STAR Group members: Pengfei Huang, Yonglong Li, Yi Liu, Andreas Lenz, Wei Wu, Karthik Nagarjuna Tunuguntla, Navya Sree Prem, Shahar Dror, Yang Qiu, Michael Baluja, Ziwei Liu, Omer Sabary, Wenyu Peng, Sarah Ekaireb, Goldie Jin, Zachary Taylor Blair, Andrew Tan, and Ziyuan Zhu. We had so many exciting conversations in both research and life. I would appreciate help from the industry: Naoaki Kokubun, Hironori Uchikawa, Dongmin Shin, Sangho Yun. I would also thank my TAs: Bentao Zhang, Chih-Hui Ho, and Hanwen Yao for their high-level teaching professionalism.

Outside UCSD, I have been lucky to have internships in industry-leading companies: I would thank Joseph B. Soriaga, Arash Behboodi, and Jilei Hou at Qualcomm. Exploring generative models for wireless communication systems inspires several ideas in my thesis. I would also appreciate Ned Varnica, Erich Haratsch, and Mats Öberg at Marvell. My research particularly benefits from understanding NAND flash architecture during Marvell internship. The patents demonstrate the fruitful internships.

I would like to thank CMRR staff: Marina Robenko, Yvonne Gao, Octavio Ochoa, Raymond Descoteaux, and the cleaning staff, for providing me with a comfortable place for research.

I am super lucky to have my friends in San Diego: Jiaye Zhou, Chenlin Liu, Zhaoyuan He, Gehua Qin, Jiong Liu, Yang Qiu, Song Wang, Jingqi Huang, Kun Qian, Xin Xiao, Yang Fu, Chongbin Zhang, Susu Luo, Kan Wang, and Kaiyan Yan. My life at San Diego is colorful and joyful with your consistent company. I would also appreciate all my friends from Chongqing No. 1 Middle School and Beihang University. Our friendship which spans over ten years is an extremely precious treasure. I would thank all my friends for participating in my joys and

sorrows throughout the years.

Most importantly, I would appreciate my parents for their love, support, and caring. I dedicate this dissertation to them.

The research was supported in part by the NSF under Grant CCF-2212437, Koxia Corporation, Marvell Technology, and the Center for Memory and Recording Research at the University of California San Diego.

Chapter 3 is in part a reprint of the material in the paper: Simeng Zheng, Chih-Hui Ho, Wenyu Peng, and Paul H. Siegel, "Flash-Gen: Spatio-temporal generator for flash memory systems," submitted to *IEEE Transactions on Communications*. The work was presented at DATE 2023: Simeng Zheng, Chih-Hui Ho, Wenyu Peng, and Paul H. Siegel, "Spatio-temporal modeling for flash memory channels using conditional generative nets," in *Proc. Design, Automation & Test in Europe Conference & Exhibition*, Antwerp, Belgium, Apr. 2023.

Chapter 4 is in part a reprint of the material in the paper: Simeng Zheng, Andrew Tan, Carolina Fernández, Ismael González Valenzuela, and Paul H. Siegel, "Optimal shaping codes for a TLC flash memory," in *Annual Non-Volatile Memories Workshop (NVMW)*, La Jolla, CA, USA, Mar. 2024. The work was presented at Annual Non-Volatile Memories Workshop (NVMW) in Mar. 2024.

Chapter 5 is in part a reprint of the material in the paper: Ahmed Hareedy, Simeng Zheng, Paul H. Siegel, and Robert Calderbank, "Efficient constrained codes that enable page separation in modern flash memories," *IEEE Transactions on Communications*, vol. 71, no. 12, pp. 6834–6848, Dec. 2023. The work was also presented in part at ICC 2022 and NVMW 2024: A. Hareedy, S. Zheng, P. H. Siegel, and R. Calderbank, "Read-and-run constrained coding for modern flash devices," in *Proc. IEEE International Conference Communications (ICC)*, Seoul, South Korea, May 2022; Ahmed Hareedy, Simeng Zheng, Paul H. Siegel, and Robert Calderbank, "Read-and-run constrained coding for modern flash devices," in *Proc. IEEE International Conference Communications (ICC)*, Seoul, South Korea, May 2022; Ahmed Hareedy, Simeng Zheng, Paul H. Siegel, and Robert Calderbank, "Read-and-run constrained coding for modern flash memories," in *Annual Non-Volatile Memories Workshop (NVMW)*, La Jolla, CA, USA, Mar. 2024.

Chapter 6 is in part a reprint of the material in the paper: S. Zheng and P. H. Siegel,

"Code-aware storage channel modeling via machine learning," in *Proc. IEEE Information Theory Workshop (ITW)*, Mumbai, India, Nov. 2022, pp. 196–201. The work was presented at ITW 2022.

Chapter 7 is in part a reprint of the material in the paper: Simeng Zheng, Yi Liu, and Paul H. Siegel, "PR-NN: RNN-based detection for coded partial-response channels," *IEEE Journal on Selected Areas in Communications*, vol. 39, no. 7, pp. 1967–1982, July 2021. The work was also presented in part at ITW 2020: Simeng Zheng, Yi Liu, and Paul H. Siegel, "RNN-based detection for coded partial-response channels," in *Proc. IEEE Information Theory Workshop (ITW)*, Riva del Garda, Italy, Apr. 2021.

#### VITA

D '1

2014 2010

| 2014–2018 | University, China                                                                                                                     |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------|

| 2018–2020 | Master of Science in Electrical and Computer Engineering (Communication Theory<br>and Systems), University of California San Diego    |

| 2020–2024 | Doctor of Philosophy in Electrical and Computer Engineering (Communication<br>Theory and Systems), University of California San Diego |

| 2023–2024 | Shannon Graduate Fellowship                                                                                                           |

#### PUBLICATIONS

Simeng Zheng, Andrew Tan, Carolina Fernandez, Ismael González Valenzuela, and Paul H. Siegel, "Code-aware storage channel modeling via transfer learning," to be submitted to *IEEE Transactions on Communications*.

Simeng Zheng, Chih-Hui Ho, Wenyu Peng, and Paul H. Siegel, "Flash-Gen: Spatio-temporal generator for flash memory systems," submitted to *IEEE Transactions on Communications*.

Ahmed Hareedy, Simeng Zheng, Paul H. Siegel, and Robert Calderbank, "Efficient constrained codes that enable page separation in modern flash memories," *IEEE Transactions on Communications*, vol. 71, no. 12, pp. 6834–6848, Dec. 2023.

Simeng Zheng, Yi Liu, and Paul H. Siegel, "PR-NN: RNN-based detection for coded partialresponse channels," *IEEE Journal on Selected Areas in Communications*, vol. 39, no. 7, pp. 1967–1982, July 2021.

Simeng Zheng, Andrew Tan, Carolina Fernández, Ismael González Valenzuela, and Paul H. Siegel, "Optimal shaping codes for a TLC flash memory," in *Annual Non-Volatile Memories Workshop (NVMW)*, La Jolla, CA, USA, Mar. 2024.

Ahmed Hareedy, Simeng Zheng, Paul H. Siegel, and Robert Calderbank, "Read-and-run constrained coding for modern flash memories," in *Annual Non-Volatile Memories Workshop* (*NVMW*), La Jolla, CA, USA, Mar. 2024.

Simeng Zheng, Chih-Hui Ho, Wenyu Peng, and Paul H. Siegel, "Spatio-temporal modeling for flash memory channels using conditional generative nets," in *Proc. Design, Automation & Test in Europe Conference & Exhibition*, Antwerp, Belgium, Apr. 2023.

S. Zheng and P. H. Siegel, "Code-aware storage channel modeling via machine learning," in *Proc. IEEE Information Theory Workshop (ITW)*, Mumbai, India, Nov. 2022, pp. 196–201.

A. Hareedy, S. Zheng, P. H. Siegel, and R. Calderbank, "Read-and-run constrained coding for modern flash devices," in *Proc. IEEE International Conference Communications (ICC)*, Seoul, South Korea, May 2022.

Simeng Zheng, Yi Liu, and Paul H. Siegel, "RNN-based detection for coded partial-response channels," in *Proc. IEEE Information Theory Workshop (ITW)*, Riva del Garda, Italy, Apr. 2021.

Qin Huang, Simeng Zheng, Yuanhan Ni, Zulin Wang, and Shuai Wang, "Querying policies based on sparse matrices for noisy 20 questions," in *Proc. IEEE International Symposium on Information Theory (ISIT)*, Paris, France, July 2019.

#### ABSTRACT OF THE DISSERTATION

#### Machine Learning Techniques for Data Storage Systems: Modeling, Coding, and Detection

by

Simeng Zheng

#### Doctor of Philosophy in Electrical Engineering (Communication Theory and Systems)

University of California San Diego, 2024

Professor Paul H. Siegel, Chair

As data explodes in modern applications, such as the Internet of Things (IoT), the needs for storage devices drastically increase. Solid state drives (SSDs) and hard disk drives (HDDs) are two main data storage devices. SSDs store data in flash memories, while HDDs store data in magnetic disks. To extend the lifetime and enhance the reliability of data storage devices, we utilize machine learning as the fundamental tool for three data storage modules: modeling in flash memory systems, error correction and constrained coding schemes, and detection method in magnetic recording channels.

The modeling part of the dissertation is devoted to proposing a novel data-driven approach,

referred to as Flash-Gen, to generating NAND flash memory read voltages in both space and time using conditional generative networks. This generative modeling method reconstructs read voltages from an individual memory cell based on the program levels of the cell and its surrounding cells, as well as the time stamp, in a time-efficient, resource-saving, and function-comprehensive manner. As the needs for data-dependent channel models, we further extend the generative modeling approach to the coded storage channel. We train the generative models via transferring knowledge from models pre-trained with pseudo-random data. This technique can accelerate the training process and improve model accuracy in reconstructing the read voltages induced by constrained input data throughout the flash memory lifetime.

The coding part of the dissertation designs practical coding workflow and proposes new constrained and shaping coding schemes for flash memories. We propose a flash system optimization procedure, referred to as the Flash-Gen coding workflow, that leverages reconstructed read voltages from Flash-Gen for the development of error correction codes (ECCs) and constrained codes. Flash-Gen coding workflow can effectively address a range of important tasks, including threshold determination, coding performance estimation, and pattern characterization. We then formulate inter-cell interference (ICI)-mitigation constrained codes and distribution-matching shaping codes. The proposed coding schemes both achieve remarkable lifetime improvement.

The detection part of the dissertation builds recurrent neural network (RNN)-based detection for magnetic recording channels with partial-response equalization, which is referred to as *Partial-Response Neural Network* (PR-NN). PR-NN outperforms classical detection methods, such as the Viterbi detector, under multiple "realistic" environments and preserves the detection performance across different channel conditions.

# Chapter 1 Introduction

# **1.1 Data Storage and Machine Learning**

In recent years, machine learning has proven to be highly effective across various applications, particularly in the fields of computer vision and natural language processing. The ongoing revolution in artificial intelligence is profoundly reshaping the fields of data storage systems. We treat data storage devices, such as flash memories and magnetic drives, as a communication system. The communication system takes an input write signal and produces an output read signal. The coding techniques, including error correction codes (ECCs) and constrained codes, aim to recover the distorted data and mitigate various types of error sources in storage devices. Machine learning can be a critical tool to analyze and assist the necessary modules in data storage systems [51].

Understanding the NAND flash memory channel has become more and more challenging due to the continually increasing density and the complex distortions arising from the write and read mechanisms. Several mathematical models could reconstruct the read voltage distributions [11, 67, 78, 95] and hard bit errors [94, 112]. As system becomes more and more complicated, machine learning has been exploited to model flash memory channels [73, 75–77]. Machine learning-based modeling approaches are also proposed for wireless communication channels [5, 93] and DNA storage channels [53]. In this dissertation, we develop a spatiotemporal generative modeling approach for flash memory systems. Furthermore, we transfer the knowledge from the pretrained generative models to data-dependent cases, which accelerates the training process and preserves the reconstruction quality.

We then study a variety of error correction and mitigation mechanisms based on the understanding of channels. Error correction codes use parity check bits to detect and correct the bit errors that occur within flash memory. The typical ECC algorithm is low-density parity-check (LDPC) codes [10,46,123]. Constrained codes forbid error-prone patterns in both flash memories and hard disk drives to mitigate inter-cell and inter-symbol distortions distortions [1,23,30,34, 35,39,49,55,86,111,115,121,128]. Shaping codes, the distribution-matching codes, find several

successful applications in flash devices by optimizing the wear costs associated with program levels [70–72, 104]. In this dissertation, the practical LDPC coding workflow is designed to optimize LDPC coding schemes for flash memory. Efficient constrained coding is formulated to enable page separation and the optimal shaping code is constructed to minimize the wear costs for the TLC flash device.

Exploring data storage systems and analyzing data protection schemes, we aim to study the data detection techniques for data storage systems. The classical detection method for magnetic recording channels with constrained coding is trellis-based sequence detection [4, 20, 21, 54, 117]. Deep neural networks are applied to communication and storage decoders [7, 26, 32, 52, 59, 68, 89, 101, 105, 106, 110]. The RNN-based detection, capable of streaming data inputs and preserving detection results under several situations, are proposed in this dissertation.

The synergy between machine learning and data storage systems is stimulating crucial mutual advancement [51]. Information theory is also important for machine learning models and their data. As models and data are stored in storage clusters, coding theory can protect model parameters and data from distortions [45].

# **1.2 Dissertation Overview**

In this dissertation, we first introduce the data characterization platform for flash memory. Then, we propose generative modeling methods for flash memory systems. According to our error characterization for flash memories, we propose the optimal shaping coding scheme and the efficient constrained coding method for flash memories. We further design code-aware and data-dependent generative models. We finally establish the machine learning-based and robust detector for partial-response channels. The dissertation is organized as follows.

In Chapter 2, we introduce the FPGA platform for TLC flash memory characterization. We explore the flash conditions using hard read mode and soft read mode. We design the data-dependent workflow to incorporate coding schemes into the write information. The flash charaterization platform serves as the experimental foundation for all modeling, coding, and detection work in later chapters.

In Chapter 3, we propose Flash-Gen framework to generate flash memory read voltages in both space and time using conditional generative networks. We then utilize the reconstructed read voltages for the development of error correction codes (ECCs) and constrained codes. This coding development process can effectively address a range of important tasks, including threshold determination, coding performance estimation, and inter-cell interference (ICI) pattern characterization. The system modeling for flash memory motivates our researches on coding schemes in Chapter 4 and Chapter 5.

In Chapter 4, we establish the optimal shaping codes for a TLC flash memory. In TLC flash devices, three bits are stored in each cell to represent one of 8 program levels and wear costs for 8 levels are different during the repeated program and erase operations. The goal of shaping codes is to optimally shaping the probability distribution of sequences so that sequences with high wear costs have low probability and sequences with low wear costs have high probability. We demonstrate  $10 \times$  chip lifetime improvement based on Spanish-language texts.

In Chapter 5, we suggest new constrained coding schemes referred to as *read-and-run* (RR). The idea is to avoid error-prone patterns by coding data either only on the left-most page or only on the two left-most pages while leaving data on all remaining pages uncoded. The page separation idea preserves high access speed and the coding on one or two pages reduces the rate loss without impacting the device reliability. We verify RR codes using several constrained coding schemes, including lexicographically-ordered constrained (LOCO) codes, interleaved run-length limited (RLL) codes, and two-dimensional (2D) constrained codes. The notable performance gain is achieved via RR coding on our flash characterization platform.

In Chapter 6, we extend our Flash-Gen approach to the data-dependent storage channel. To reduce the experimental overhead associated with collecting extensive measurements from constrained program/read data, we train Flash-Gen models via transferring knowledge from models pre-trained with pseudo-random data. This technique can accelerate the training process and improve model accuracy in reconstructing the read voltages induced by constrained input data.

In Chapter 7, we investigate the use of recurrent neural network (RNN)-based detection of magnetic recording channels with inter-symbol interference (ISI). We refer to the proposed detection method, which is intended for recording channels with partial-response equalization, as *Partial-Response Neural Network* (PR-NN). We train bi-directional gated recurrent units (bi-GRUs) to recover the ISI channel inputs from noisy channel output sequences and evaluate the network performance when applied to continuous, streaming data. We demonstrate that the PR-NN detector outperforms Viterbi detection and achieves the performance of *Noise-Predictive Maximum Likelihood* (NPML) detection in additive colored noise (ACN) at different channel densities. We further show that PR-NN maintains its performance when jointly trained with two different channel conditions.

# Chapter 2

# **Flash Characterization Platform**

# 2.1 Measurement Method

As shown in Fig. 2.1, the flash characterization platform is an FPGA platform and can control and communicate with vendor triple-level cell (TLC) flash chips [8]. The developed software API can operate low-level hardware actions. We use the software API to simulate the write/read/erase operation cycle in flash chips.

The basic unit of data storage in NAND flash memory is a floating-gate transistor, referred to as a cell. The cells are organized into an interconnected 2-D array, called a block, via horizontal wordlines (WLs) and vertical bitlines (BLs). In our chip, each block has the right plane and the left plane. The flash memory chip is composed of a collection of such blocks. The basic unit of write and read operations in flash memory is a page, corresponding to a logical bit position in a wordline of a block. For TLC flash, the three pages are referred to as the lower, middle, and upper page. On the other hand, the basic unit of an erase operation is an entire block.

We briefly summarize functions:

- Program: write data on a wordline. Each wordline must be written three times as required by the TLC device's 3-stage program sequence.

- Erase: erase data in a block.

- Soft Read: read the voltage level for all cells on a page. The voltage level is fine-grained information about the voltage written to each cell.

- Hard Read: read the bit information for all cells on a page.

We conduct program/read/erase experiments as follows:

- 1. Erase flash memory block under test.

- 2. Program all pages of block under test with pseudo-random data.

Figure 2.1. The FPGA testboard is the flash characterization platform.

- 3. We initially set values of read cycles. After the specific program/erase (P/E) cycles, perform a hard or soft read operation on the tested block. If we set retention time as 0, the read operation will be implemented instantly. Otherwise, the read operation will be implemented after the retention time.

- 4. For each cell, record the read information for post-processing.

The post-processing method for hard read signals focus on BER at different time stamps. In Chapter 5 and Chapter 4, we operate hard measurement experiments to verify bit error rate (BER) performance on designed coding schemes. The post-processing methods for soft read signals include probability density function (PDF) visualization, statistical analysis, error-prone patterns recognition, and read threshold determination. In Chapter 3 and Chapter 6, we operate soft measurement experiments to analyze measured and reconstructed signals.

Figure 2.2. The system of coding incorporation module on flash characterization platform.

# 2.2 Coding Incorporation Module

We design the coding incorporation module to write encoded data instead of pseudorandom data into flash chip. The idea is to replace the memory of write variable with encoded data. We utilize Dump/Restore function in the Xilinx tool store.

We present the system of the coding incorporation module in Fig. 2.2. We perform program/read/erase experiments in the online part. We prepare coded data sequences and post-process read data in the offline part.

Due to the variation of mappings between manufacturers and product generations, we propose mapping conversion between the classical recursive alternate Gray mapping (RAGM) and vendor mapping to keep the consistency of programmed data. In TLC flash device, the mapping function converts 3 bits in one cell into 8 program levels and the demapping function represents 8 program levels into 3 information bits.

# **Chapter 3**

# **Flash-Gen: Spatio-temporal Generator for Flash Memory Systems**

# 3.1 Introduction

NAND flash memory is a non-volatile data storage medium, widely utilized in consumer electronics and large-scale data centers [10]. The basic storage unit in a flash memory is a floating-gate transistor, referred to as a cell. The cell can encode one or multiple bits of data as a discrete set of charge levels induced by a program operation. During a read operation, the program level is determined by measuring the threshold voltage of the cell. As the manufacturers scale down to a smaller flash memory chip and more bits are stored in one cell, identifying the voltage level stored in the cell becomes more and more difficult. This scaling of flash memory is accompanied by diminished memory reliability and reduced device endurance.

The distribution of read voltage levels corresponding to a program level is influenced by a variety of distortions. The distortions in NAND flash memory are manifold, including programming errors, inter-cell interference (ICI) due to parasitic capacitance coupling between adjacent cells, cell wear during program/erase (P/E) cycling, cell charge loss due to data retention, and program/read disturb effects. As the cell bit density increases and the gap between adjacent program levels decreases, these distortions and the reduced separation of the read voltage distributions of neighboring levels lead to an increase in error probability.

In order to compensate for the sophisticated noise and recover the stored bits in each cell, solid-state drives (SSDs), composed of a number of flash chips, incorporate advanced coding schemes within their controllers. Commonly used coding schemes in SSD controllers are error-correction codes (ECCs). Typical ECCs employed in flash controllers are Bose-Chaudhuri-Hocquenghem (BCH) codes and low-density parity-check (LDPC) codes [10,46]. As the NAND flash devices wear out under repeatedly program and erase operations or perform read operations with extended wait time, the bit error rate (BER) of the flash chip increases. When BER exceeds the maximum number of errors that ECC can correct, it becomes impossible to fully recover the read information, resulting in data loss. The endurance of an SSD is determined by the number of program/erase (P/E) cycles that can be performed without uncorrectable errors.

Constrained codes are another type of coding scheme, which avoids patterns prone to errors caused by inter-cell interference (ICI) effects [34, 38, 39]. The primary cause of ICI stems from the charge propagation from cells programmed with high levels to neighboring cells programmed with lower levels. Constrained codes aim to characterize and forbid those problematic patterns in flash devices.

The characterization of complicated flash errors and the design of these reliabilityenhancing coding algorithms rely upon a comprehensive understanding of the flash memory system. A common approach for system characterization is to treat a flash cell as a communication channel. The communication channel takes an input program level and produces an output voltage level. An accurate model of the channel is therefore an indispensable tool. Moreover, such a model can potentially obviate the need for hardware- and time-intensive data collection for use in evaluating and optimizing the coding algorithms.

Several mathematical and machine learning models supported by empirical measurements or simulated voltages in flash memory have appeared in the literature. Cai et al. [11] model the voltage distribution in 2-bit per cell MLC flash devices as a Gaussian distribution. Parnell et al. [95] proposed a parameterized Normal-Laplace mixture model that more accurately describes MLC flash read voltage distributions. Luo et al. [78] proposed another accurate and computationally more efficient model for MLC flash, based on a modified version of the Student's t-distribution and a temporal power law. Statistical analysis of hard bit errors in [94, 112] and characterization of dominant error patterns in [12, 67] offer additional empirical understanding of flash memories.

Recently, there has been great interest in the application of machine learning in communications and networking, including data storage. For example, machine learning can be used to design robust signal detectors in magnetic recording [128] and establish LDPC decoders with flexible code lengths and column weights [123]. Machine learning has also been exploited to model flash memory channels. Liu et al. [77] used a neural network (NN) to model simulated read voltages as a function of P/E cycles for one individual program level in isolated MLC flash cells. Liu et al. [75] provided flash memory conditions to a NN to model voltage distributions for 3D NAND flash. Liu et al. [76] used a time-dependent NN to predict page error counts in TLC flash. Liu et al. [73] generated errors in 3D NAND flash using a conditional generative adversarial network (GAN) architecture.

However, as effective as these mathematical or machine learning models have been in the scenarios to which they have been applied, none has provided an accurate model of both spatial and temporal characteristics of flash memory read voltages and none could serve as the basis for read channel design tasks such as read threshold optimization, error-prone pattern ranking, and performance evaluation of ECCs and constrained codes.

Generative modeling techniques such as the Generative Adversarial Network (GAN) [31], the Variational Auto-Encoder (VAE) [62], and diffusion models [43] have been successfully applied to several situations, such as image processing [50]. Generative modeling has now became an important tool for analyzing both wireless communication systems and DNA storage systems. For example, GAN has been applied to capture the channel impulse response distribution in multi-input and multi-output (MIMO) wireless communication channel [93] and VAE is an essential model to reconstruct authentic communication signals [5]. GAN has also been used to learn the error statistics of a DNA storage channel and to provide a simulation tool for developing improved error-correction coding and DNA sequence recovery algorithms [53].

In view of the demonstrated power of neural networks in learning complex multidimensional distributions, we propose the use of conditional generative nets as an approach to modeling flash memory read voltages in both space and time. The read voltages of each cell can be regenerated by the learned model from an array of program levels. We refer to this generative modeling method as Flash-Gen. We summarize our contributions in this work as follows:

1. We propose a comprehensive, flexible, and data-driven Flash-Gen model to accurately reconstruct soft read voltages at each individual cell unit of flash memory. This machine learning approach can be flexibly applied to flash memories of any technology generation

and chip feature size.

- 2. We formulate a temporally controllable, conditional VAE-GAN network to regenerate cell read voltages from the program levels of an array of flash memory cells and a time stamp representing the P/E cycle count and the retention time.

- 3. We propose the Flash-Gen coding workflow. This workflow simulates the "realistic" error correction environment with LDPC codes in an SSD controller and emulates multiple necessary steps in hard-decision and soft-decision decoding. It also estimates the relative frequencies of spatially-dependent and pattern-dependent ICI-induced hard read errors to help the design of constrained codes.

- 4. We validate the proposed Flash-Gen on a 1X-nm, 3-bit per cell (TLC) NAND flash chip across various wear conditions. The evaluation metrics used to compare the model outputs to measurements include the read voltage distributions at different time stamps, the measure of central dispersion of different program levels, and the error counts of different program levels.

- 5. We explore several essential applications of Flash-Gen coding workflow with practical LDPC codes and constrained codes. By evaluating LDPC decoding performance, analyzing the threshold selection during read process, and ranking error-prone patterns for constrained code design and evaluation, we demonstrate the consistency between Flash-Gen coding workflow and realistic NAND flash controller.

# **3.2** Flash Memory and Spatio-temporal Noise

#### **3.2.1** Flash Memory Basics

We start from the basic unit cell in a flash chip. Today's flash memories are capable of storing single or multiple bits (e.g., 2 to 5 bits) per cell, where the *n*-bit strings correspond to  $q = 2^n$  program levels. The cells are organized into an interconnected two-dimensional (2D)

**Figure 3.1.** (Left) Example mapping of cell program levels to binary representations in TLC flash. (Right) Schematic diagram of a TLC flash memory block showing the 2-D array of cells connected in the horizontal direction by wordlines (WLs) and in the vertical direction by bitlines (BLs).

array, called a block, via horizontal wordlines (WLs) and vertical bitlines (BLs). The flash memory chip is composed of a collection of such blocks. In 3D NAND flash, these 2D arrays are stacked vertically to achieve larger volumetric density [74, 94]. Fig. 3.1 depicts a schematic diagram of a planar TLC flash memory block and an example of a Gray mapping from the q = 8program levels to the corresponding data words of n = 3 binary digits.

The basic unit of write (i.e., program) and read operations in flash memory is a page, corresponding to a logical bit position in a wordline of a block. We refer to the program level as PL and the soft read voltage level as VL. On the other hand, the basic unit of an erase operation is an entire block.

In the program operation, we refer to the PLs of three consecutive cells along WLs or BLs as a pattern. As an example, in Fig. 3.1, the programmed levels  $PL_{i-1,j}PL_{i,j}PL_{i+1,j}$  in WLs (i-1), i, (i+1) of BL *j*, correspond to bit strings "011", "111", "011", which we associate with the pattern 707 in the vertical (BL) direction.

**Figure 3.2.** PDF visualizations of a 3D TLC NAND flash memory for measured voltage levels at no retention time, 3 months retention, and 1 year retention time when P/E cycle count is 10,000 P/E. Solid curves, dotted curves, and dashed curves correspond to distributions of retention time 0 day, 3 months, and 1 year, respectively. Three brown vertical lines are the optimal read threshold between program level 6 (color black) and program level 7 (color orange).

#### **3.2.2** Spatio-temporal Characteristics

Flash memory channels suffer from distortions of a spatio-temporal nature, where ICI effects correspond to spatial characteristics, P/E cycling noise and retention noise correspond to temporal characteristics.

**Spatial effects**: ICI refers to the phenomenon where programming of a cell induces changes in the voltage levels of neighboring cells within its block. In particular, the read voltage level of a cell programmed to a low level may be inadvertently increased if its adjacent cells are programmed to high levels, i.e., when the programming pattern is high-low-high. As an example in Fig. 3.1, if we program a pattern  $PL_{i,j-1}PL_{i,j}PL_{i,j+1} = 707$  in WL *i* or  $PL_{i-1,j}PL_{i,j}PL_{i+1,j} = 707$  in BL *j* in a TLC chip, the read voltage  $VL_{i,j}$  may be increased by its high adjacent cells. During data detection, the recovered program level of the central "victim" cell may therefore be erroneously interpreted as an incorrect level. ICI typically differs in the WL and BL directions.

**Figure 3.3.** Count of top error-prone patterns and level error rate at selected P/E cycles without retention. The error pattern counts are normalized by the count of pattern 707 in BL direction at 4000 P/E cycles.

**Temporal effects**: P/E cycling gradually wears out the oxide layer of a cell. Data retention causes the programmed cell to diffuse electrons over time. As a result of these effects, the information stored in a cell can be misread. The changes of the read voltage distributions over the range of retention time are shown in Fig. 3.2. The retention noise systematically shifts the read thresholds to lower normalized voltage values as the retention time increases. For example, the read thresholds between program level 6 and program level 7 in three different retention timestamps are shown as brown vertical lines.

The integrated distortions of spatial ICI and temporal P/E cycling errors can be observed in Fig. 3.3. As the P/E cycle count increases, the error rate is increasing. For an individual P/E cycle count, the cell errors are clearly affected by neighboring program levels. Pattern 707 in the BL direction is the most severely affected by ICI. Moreover, patterns 707, 706, and 607 in the BL direction are more error-prone than those in the WL direction.

## 3.3 Flash-Gen Formulation

We define the flash memory system as a communication channel. Program level PL is from channel input domain  $\mathcal{P}$  and voltage level VL is from channel output domain  $\mathcal{V}$ . The relationship between PL and VL can be represented as VL = FM(PL), where  $FM(\cdot) : \mathcal{P} \to \mathcal{V}$ denotes the flash memory channel. More specifically, we consider the channel model in a rectangular region of a block,

$$\begin{bmatrix} \vdots & & \\ VL_{i-1,j-1} & VL_{i-1,j} & VL_{i-1,j+1} \\ \cdots & VL_{i,j-1} & VL_{i,j} & VL_{i,j+1} & \cdots \\ VL_{i+1,j-1} & VL_{i+1,j} & VL_{i+1,j+1} \\ \vdots & & \end{bmatrix} = FM \begin{pmatrix} \begin{bmatrix} & \vdots & & \\ PL_{i-1,j-1} & PL_{i-1,j} & PL_{i-1,j+1} \\ \cdots & PL_{i,j-1} & PL_{i,j} & PL_{i,j+1} & \cdots \\ PL_{i+1,j-1} & PL_{i+1,j} & PL_{i+1,j+1} \\ \vdots & & \end{bmatrix} \end{pmatrix},$$

where  $PL_{i,j}$  and  $VL_{i,j}$  correspond to the program level and voltage level of one cell, where *i* and *j* represent the WL and BL position of the cell, shown in Fig. 3.1.

When program level PL is given, voltage level  $VL_{i,j}$  will be corrupted by both temporal and spatial factors. Temporal distortions arise from repeated program and erase operations, as well as from the time delay between program and read operations. Spatial distortions are caused by problematic program patterns giving rise to ICI.

In this section, we present the framework of our Flash-Gen model. As program levels from flash blocks and specific time stamps are provided, voltage levels can be sampled from Flash-Gen efficiently and accurately. We adopt a conditional VAE-GAN (cVAE-GAN) architecture [64] as the basis for our architecture. The network architecture is depicted in Fig. 3.4, where the fusion of the VAE [62] and GAN [31] can leverage the information from the latent space to produce high-quality and guarantee accurate reconstruction with the help of the discriminator. The spatio-temporal combination module incorporates temporal information, i.e., P/E cycles and retention into the voltage reconstruction. Our goal is to learn a mapping  $FM(\cdot)$  between program levels and soft read voltage levels at various time stamps, where the reconstructed voltage levels accurately reflect the spatial and temporal nature of the channel.

**Figure 3.4.** Flash-Gen architecture: encoder, generator, and discriminator constitute the generative modeling architecture. Here, z is the latent vector; Time is the corresponding time stamp (P/E cycle count and retention time discussed in this project); PL is the array of program levels, VL is the array of measured read voltage levels, and  $\widetilde{VL}$  is the reconstructed array of read voltage levels.

#### **3.3.1** Flash-Gen Architecture Formulation

Given program level  $PL \in \mathcal{P}$ , read voltage level  $VL \in \mathcal{V}$ , temporal factor time stamp representing P/E cycle count  $T_{P/E}$  and the retention time  $T_{\gamma}$ , we aim to learn the analytically intractable likelihood  $P(VL|PL, T_{P/E}, T_{\gamma})$ , with the goal of capturing the spatio-temporal nature of the flash memory channel.

Fig. 3.4 summarizes the architecture of our Flash-Gen. The conditional VAE-GAN architecture consists of three components: an encoder (*Enc*), a generator (*Gen*), and a discriminator (*Dis*). The encoder maps the read voltages to the latent vector z at a specific  $T_{P/E}$  cycle count and retention time  $T_{\gamma}$  and replaces the prior distribution P(z) in the GAN with the learned posterior distribution  $P(z|VL, T_{P/E}, T_{\gamma})$ . The decoder in the VAE shares its weights with the GAN generator [31]. In the conditional setting, the variational lower bound of  $P(VL|T_{P/E}, T_{\gamma})$ can be derived as

$$\log P(\mathbf{VL}|T_{\mathbf{P/E}}, T_{\gamma}) \ge -D_{KL}(Q(z|\mathbf{VL}, T_{\mathbf{P/E}}, T_{\gamma})||P(z|T_{\mathbf{P/E}}, T_{\gamma})) + \mathbb{E}_{Q(z|\mathbf{VL}, T_{\mathbf{P/E}}, T_{\gamma})}[\log(P(\mathbf{VL}|z, T_{\mathbf{P/E}}, T_{\gamma}))],$$

(3.1)

where  $D_{KL}$  represents the Kullback-Leibler (KL) divergence. The distribution  $Q(z|VL, T_{P/E}, T_{\gamma})$ of the latent vector z is trained to approach  $P(z|T_{P/E}, T_{\gamma})$  via the KL loss  $\mathcal{L}_{KL}$ , where  $P(z|T_{P/E}, T_{\gamma})$  is assumed to be a multivariate Gaussian distribution.

Generator will take both the learned latent vector and PL as input and generate a "fake"  $\widetilde{\text{VL}}$ . The latent vectors are sampled from  $Q(z|\text{VL}, T_{\text{P/E}}, T_{\gamma})$  using the re-parameterization trick [62]. When sampling different latent vectors *z* from the same distribution, we can generate multiple arrays of plausible voltages levels. The variations in these output arrays for a given array of program levels reflect the stochasticity of the channel. The discriminator measures the difference between PL and  $\widetilde{\text{VL}}$ . The loss in the conditional GAN part is

$$\mathcal{L}_{GAN} = \log(1 - Dis(\text{PL}, Gen(\text{PL}, T_{\text{P/E}}, T_{\gamma}, z))) + \log(Dis(\text{PL}, \text{VL})).$$

(3.2)

Similar to VAE-GAN [64], we encourage the reconstructed voltage levels to match the authentic voltage levels, using the  $\ell_2$ -norm to measure the reconstruction loss

$$\mathcal{L}_{recon} = ||\mathbf{V}\mathbf{L} - Gen(\mathbf{P}\mathbf{L}, T_{\mathbf{P}/\mathbf{E}}, T_{\gamma}, z)||_2.$$

(3.3)

Combining these equations, we formulate the loss function of the cVAE-GAN architecture as

$$\min_{Gen,Enc} \max_{Dis} \mathcal{L}_{GAN} + \alpha \mathcal{L}_{recon} + \beta \mathcal{L}_{KL}.$$

(3.4)

#### **3.3.2** Spatio-temporal Fusion

To capture the spatial ICI effects in the channel model, we implement the generator using a convolutional neural network (CNN), where VL is reconstructed from the PL values in its cell and neighboring cells. To generate VL at an explicit time stamp, we control the generator with an additional temporal factor and incorporate the time stamp into generator *Gen*.

In order for generator to be aware of time stamps, we inject some encoded information about the time inputs. There are many choices of value expressions. We represent the time inputs as a *d*-dimensional vector using powers or exponential values. We encode the normalized P/E cycle count using expressive powers, e.g.,  $T_{P/E}^2$ ,  $\sqrt{T_{P/E}}$ , etc. The *d*-dimensional vector of P/E cycle can be formulated as  $[T_{P/E}^{0.5}, T_{P/E}^1, T_{P/E}^{1.5}, ...]$ . Inspired by the modeling of retention noise in [67], we represent the normalized retention time using various exponential values  $e^{-\nu T_{\gamma}}$ , where  $\nu$  is a constant parameter. The encoded vector can be presented as  $[e^{-1T_{\gamma}}, e^{-0.75T_{\gamma}}, e^{-0.5T_{\gamma}}, ...]$ .

We illustrate the fusion mechanism in generator using controllable P/E cycle count. We first encode the normalized P/E cycle count into a *d*-dimensional P/E vector, which contains expressive powers of the normalized P/E cycle. Then, we spatially replicate the *d*-dimensional P/E vector to the feature map with appropriate size  $H \times W \times d$  and concatenate it with the  $H \times W \times C$  feature from each layer in *Gen*, where  $H \times W$  is the spatial dimension of the feature from each convolutional layer and *C* is the number of channels in the CNN. The channel-wise fusion produces the final feature with size  $H \times W \times (C + d)$  of each layer. The fusion of the features from the program levels and the P/E feature maps guarantees the spatial-temporal characteristics of the reconstructed voltage levels. The controllable retention time shares the same fusion architecture with different encoded time vectors.

#### 3.3.3 Implementation Details

**Datasets**: We validate the proposed Flash-Gen using datasets collected from one commercial 1X-nm TLC flash chip. We prepare two datasets for verification: P/E cycling dataset and retention dataset. We conduct the P/E cycling experiment by erasing a block, programming pseudo-random data, and reading voltage levels at selected P/E cycle counts with fixed retention time. We record the {PL, VL} dataset at selected P/E cycles 4000, 7000, and 10000 with immediate reads. For the retention datasets, we repeatedly erase and program blocks with pseudo-random data to predefined P/E cycle counts, and read voltage levels after a certain retention time at room temperature. We record the {PL, VL} dataset at 4000 P/E cycles with 0 retention time,  $\tau$  retention time, and  $2\tau$  retention time.

In order to fit blocks of recorded data into the network architecture, we crop the  $\{PL, VL\}$  pairs of the recorded blocks into non-overlapping  $64 \times 64$  2-D arrays. In P/E cycling dataset, the

number of 2-D arrays in the training set is  $1.5 \times 10^5$  (5 × 10<sup>4</sup> for each P/E cycle) and the size of the evaluation dataset is  $2.1 \times 10^4$  (7 × 10<sup>3</sup> for each P/E cycle). In retention dataset, the number of 2-D arrays in the training set is  $9 \times 10^4$  (3 × 10<sup>4</sup> for each retention time) and the size of the evaluation dataset is  $2.1 \times 10^4$  (7 × 10<sup>3</sup> for each retention time).

Network: The three network modules in Fig. 3.4 refer to: ResNet [41] (*Enc*), U-net [99] (*Gen*), and PatchGAN [50] (*Dis*). The dimensions of latent vector z and time vector are both set to 6. The following descriptions of the modules exploit the terminologies in the corresponding references.

- Encoder: We use the two residual blocks, each of which contains two 3 × 3 convolutional layers with stride 1 and padding 1. We then add two linear layers, which map output features to mean and variance for the latent vector.

- 2. Generator: Ck denotes a Convolution-BatchNorm-ReLU layer with k output channels. All convolutions are  $4 \times 4$  kernels applied with stride 2 and padding 1. The network architecture before spatio-temporal fusion can be described as

(Down Part) C64, C128, C256, C512, C512, C512, (Up Part) C512, C512, C256, C128, C64, C1.

where we inject latent vector z by replication and concatenation into every layer in the "Down" part [132], and each layer in the "Up" part receives skip connections from the corresponding layer in the "Down" part [99].

3. Discriminator *Dis*: The input to the discriminator is the concatenation of fake voltage levels and program levels. With the same naming convention as in the generator, we express the discriminator as *C*64, *C*128, *C*1.

We compared the cVAE-GAN model to other popular generative modeling architectures: conditional GAN [50], conditional VAE [108], and Bicycle GAN [132]. When we compare

the total variational distance of voltage distributions between measured data and sampled data from the evaluation dataset, the cVAE-GAN model reconstructs the read voltage levels with the highest quality. The numerical results of comparison are not included due to the space limitation.

**Remark 1.** Flash-Gen can be generalized to any multi-level flash device including 3D NAND flash. In order to characterize the severe layer-to-layer interference in 3D flash [73, 94], we can crop the 3D arrays of collected {PL, VL} pairs and modify the Flash-Gen network realization to include 3D convolutional networks in all of the modules.

Learning: We trained Flash-Gen models given dataset from scratch. We settled upon the training parameters after several experiments. Adam optimizer is used with learning rate  $2 \times 10^{-4}$ . Parameters in the loss function (3.4) are set to  $\alpha = 10$  and  $\beta = 0.01$ . The P/E cycling Flash-Gen is trained with recorded {PL, VL} dataset at P/E cycle counts 4000, 7000, and 10000. The total number of iterations is  $5.25 \times 10^5$  for P/E cycling Flash-Gen and the batch size is 2. The retention Flash-Gen is trained with a dataset reflecting retention times 0,  $\tau$ , and  $2\tau$ , where  $\tau$ is chosen to observe noticeable differences in level distributions at the three time stamps. The total number of iterations number is  $6.3 \times 10^5$  and the batch size is again 2.

During evaluation, we use program levels and latent vector z sampled from a standard multivariate Gaussian distribution. For each program level array, we sample 10 different latent vectors to evaluate the learned model.

**Time**: A major benefit of Flash-Gen is observed by comparing the measurement time from the real chip and the inference time of Flash-Gen. When we collect one block of data at selected P/E cycles with no retention age, it requires approximately 4 hours on our FPGA-based platform and the block cannot store information for further usage due to the high error rates. The retention datasets require waiting time to record voltage levels. However, in the Flash-Gen, the data generation of one block can be completed within 400 seconds under CPU mode (Intel i7-9700K, 3.60GHz×8) and no flash block is wasted.

### **3.4 Flash-Gen Coding Workflow**

Preserving data integrity in NAND flash involves dealing with temporal and spatial distortions. Coding is a powerful technique for mitigating, detecting, and correcting errors in data storage. Designing appropriate coding schemes takes several factors into consideration, like error correction capability, storage overhead, and read latency. To search for optimal coding design, a large number of experiments regarding threshold determination and code optimization are needed, which consumes excessive time and hardware resources. Read voltages sampled from classical mathematical distributions or generated by machine learning-based models do not accurately reflect the spatio-temporal characteristics of flash memory channels.

Therefore, we propose the Flash-Gen coding procedure. Flash-Gen coding workflow simulates three practical coding applications: hard-decision decoding of LDPC codes, soft-decision decoding of LDPC codes, and optimization of constrained codes. The detailed task modules are illustrated in Fig. 3.5. Our applications are not limited to these three coding tasks and can be extended to other signal-processing scenarios. For example, reconstructed {PL, VL} containing spatio-temporal information can help the design of maximum a posteriori (MAP) and Gaussian approximation (GA) detectors [2].

#### 3.4.1 Flash-Gen LDPC Coding Workflow

We first discuss the use of Flash-Gen in the evaluation of ECCs, specifically, LDPC codes. Modern flash devices employ advanced ECCs within their controllers to detect and correct a number of errors when data is read out from flash memory. A stronger ECC can tolerate more errors but consumes more power and latency.

We briefly overview the two stages of error correction and their related data recovery tasks [10]: 1) Hard-decision decoding: The flash chip reads each page using the set of hard thresholds, where the flash chip compares the read voltage with thresholds and determines the read bit for each page. Then ECC decoder performs the hard-decision decoding process on the

**Figure 3.5.** Flash-Gen coding workflow: Flash-Gen serves as a database to provide unlimited accurate {PL, VL} pairs for coding techniques. We propose error correction coding flow with both hard-decision decoding mode and soft-decision decoding mode and constrained coding flow.