# UC Berkeley UC Berkeley Electronic Theses and Dissertations

# Title

Hybrid Switched-Capacitor Converter Design: State-Space Dynamical Modeling and Passive Device Characterization

**Permalink** https://escholarship.org/uc/item/0vg4j3mb

Author Brooks, Nathan Charles

Publication Date 2023

Peer reviewed|Thesis/dissertation

Hybrid Switched-Capacitor Converter Design: State-Space Dynamical Modeling and Passive Device Characterization

By

Nathan Brooks

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering — Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Associate Professor Robert Pilawa-Podgurski, Chair Professor Kris Pister Assistant Professor Minjie Chen Assistant Professor Jessica Boles

Summer 2023

Hybrid Switched-Capacitor Converter Design: State-Space Dynamical Modeling and Passive Device Characterization

> Copyright 2023 By Nathan Brooks

#### Abstract

# Hybrid Switched-Capacitor Converter Design: State-Space Dynamical Modeling and Passive Device Characterization

By

Nathan Brooks

Doctor of Philosophy in Engineering — Electrical Engineering and Computer Sciences

University of California, Berkeley

Associate Professor Robert Pilawa-Podgurski, Chair

Power electronics design best configures available electrical devices—transistors, inductors, and capacitors—to realize a theoretical power conversion function in the smallest, lightest, cheapest, and most efficient manner. In particular, hybrid switched-capacitor converters are a contemporary and high-performance class of circuit topology utilizing both inductors and capacitors. To better understand how these converters behave and are realized in practice, this manuscript will explore several contributing design aspects—modeling, passive devices, and practical printed circuit board layout—applied to a particular circuit topology of active research interest.

First, the thesis will explore the results of a comprehensive survey of commercial passive components and how their figures-of-merit might be used to inform converter design. The survey explores the capabilities of prominent types of discrete capacitors and inductors. Then this manuscript applies this survey to the design of an aluminum electrolytic capacitor bank on the dc-link of a single-phase power conversion system.

Second, this thesis analyzes dynamical modeling for the flying capacitor multilevel (FCML) power converter, a topology with nearly inexhaustible switching state combinations. It presents a simplified derivation and abstraction of a conventional averaged Fourier-derived model for this FCML switching-circuit topology, and it provides extensions to existing work and explores design implications. Next, this manuscript outlines a methodology for deriving a functional, accurate, and computationally efficient discrete-time state-space dynamical model for the FCML converter; this model is validated with results measured from a high-performance hardware prototype.

Finally, the thesis investigates the usage of multilevel converters to demonstrate the underlying feasibility of the single-stage buck-type power factor correction (PFC) rectifier. A high-performance multilevel converter prototype is developed with an especial focus on compactness, high efficiency, and low-inductance layout in the switching commutation loops. Then the theoretic input current harmonics, power factor, and total harmonic distortion of the buck PFC are derived and compared to the prevailing regulatory IEC current emission standards.

"Great are the works of the Lord, studied by all who delight in them." Psalm 111:2

# Contents

| C             | ontents                                                                        | ii       |

|---------------|--------------------------------------------------------------------------------|----------|

| $\mathbf{Li}$ | ist of Figures                                                                 | iv       |

| $\mathbf{Li}$ | ist of Tables                                                                  | ix       |

| 1             | Introduction1.1Introduction1.2Organization of Thesis                           |          |

| Ι             | Passive Components in Power Electronics                                        | 4        |

| <b>2</b>      | Passive Component Survey and Characterization                                  | <b>5</b> |

|               | 2.1 Introduction                                                               | . 5      |

|               | 2.2 Characterizing Components and Defining Performance                         | . 6      |

|               | 2.3 Commercial Capacitor and Inductor Data                                     | . 10     |

|               | 2.4 Sampled Data and Extrapolation: Stored Energy of Class II Ceramic Capacito | ors 16   |

|               | 2.5 Sampled Data and Extrapolation: Capacitor and Inductor Mass                |          |

|               | 2.6 Analyzing the Data                                                         |          |

|               | 2.7 Conclusion                                                                 | . 44     |

| 3             | Application of Passive Component Data to DC-Link Buffering Capacito            | or 45    |

|               | 3.1 Introduction                                                               | . 45     |

|               | 3.2 Defining Performance Metrics                                               | . 45     |

|               | 3.3 Constraining the DC-Link Capacitor                                         | . 48     |

|               | 3.4 Analysis                                                                   | . 53     |

|               | 3.5 Conclusion                                                                 | . 54     |

| Π        | Mo   | deling of the Flying Capacitor Multilevel Converter               | 56  |

|----------|------|-------------------------------------------------------------------|-----|

| 4        | Rev  | iew of Continuous-Time State-Space Modeling for the FCML Con-     |     |

|          | vert |                                                                   | 57  |

|          | 4.1  | Introduction                                                      | 57  |

|          | 4.2  | Background                                                        | 58  |

|          | 4.3  | Simplified Model                                                  | 62  |

|          | 4.4  | Dominant Time Constant                                            | 68  |

|          | 4.5  | Future Improvements and Conclusions                               | 73  |

| <b>5</b> | Disc | crete-Time State-Space Modeling for the FCML Converter            | 75  |

|          | 5.1  | Introduction                                                      | 75  |

|          | 5.2  | Modeling Methodology                                              | 77  |

|          | 5.3  | Eigenanalysis                                                     | 85  |

|          | 5.4  | Experimental Validation                                           | 95  |

|          | 5.5  | Impact of Switch Output Capacitance on Flying Capacitor Balancing | 98  |

|          | 5.6  | Including Input Capacitance and Load Resistance in the Model      | 100 |

|          | 5.7  | Alternative Per Cycle Sampling Instants                           | 101 |

|          | 5.8  | Continuous Approximation of the Discrete State-Space System       | 102 |

|          | 5.9  | Conclusion                                                        | 104 |

# IIIMultilevel Converters for Buck-Type Power Factor Correction 105

| 6  | PCH<br>6.1<br>6.2<br>6.3<br>6.4 | B Layout Improvements for the Buck PFC FCML Converter         Introduction | 108<br>114        |  |

|----|---------------------------------|----------------------------------------------------------------------------|-------------------|--|

| 7  | 7.1<br>7.2<br>7.3<br>7.4        | Per Factor and Harmonic Limitations of the Buck PFC ConverterIntroduction  | 121<br>124<br>135 |  |

| Bi | Bibliography                    |                                                                            |                   |  |

# List of Figures

| 2.1  | Schematic denoting series and parallel bank configurations of a capacitor compo-                                  |    |

|------|-------------------------------------------------------------------------------------------------------------------|----|

|      | nent                                                                                                              | 8  |

| 2.2  | Survey of component rated capacitance C versus rated dc voltage $V_{\rm r}$ across all ca-                        |    |

|      | pacitor technologies including aluminum electrolytic, tantalum electrolytic, Class                                |    |

|      | 1 ceramic, Class II ceramic, film, and electrolytic double-layer capacitors (EDLC).                               | 12 |

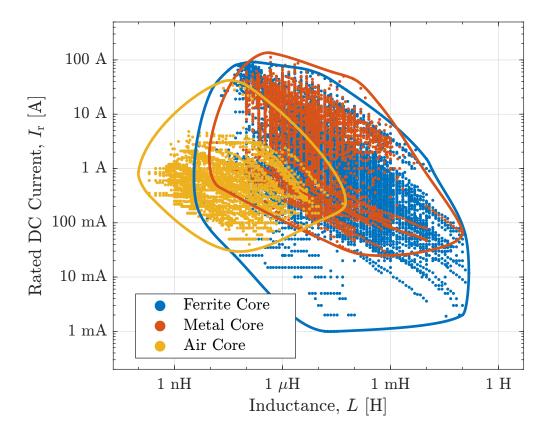

| 2.3  | Survey of component rated inductance $L$ versus rated dc current $I_{\rm r}$ across all                           |    |

|      | inductor technologies including ferrite core, metal (including powdered) core, and                                |    |

|      | air core                                                                                                          | 15 |

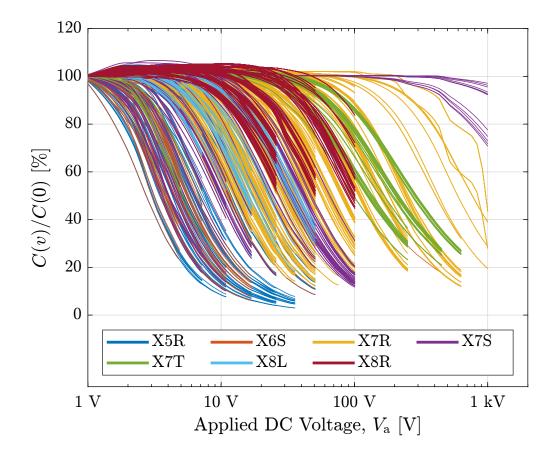

| 2.4  | Applied dc voltage $V_{\rm a}$ versus normalized differential capacitance $C(v)/C(0)$ and                         |    |

|      | distinguished by temperature characteristic. Data is sampling of 2,550 TDK                                        |    |

|      | Class II MLCC capacitors.                                                                                         | 19 |

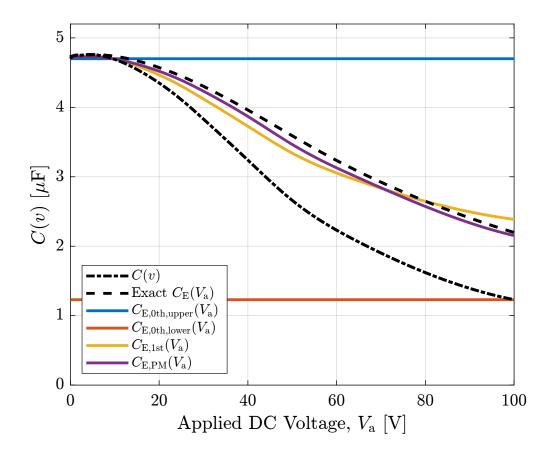

| 2.5  | Applied dc voltage versus differential capacitance $C(v)$ for C5750X7R2A475K230KA                                 |    |

|      | device: $C(0) = 4.7 \mu\text{F}, V_{\text{r}} = 100 \text{V}, \text{X7R}$ . Demonstrates comparison of approxima- |    |

|      | tions for energy-equivalent capacitance $C_{\rm E}(V_{\rm a})$ .                                                  | 21 |

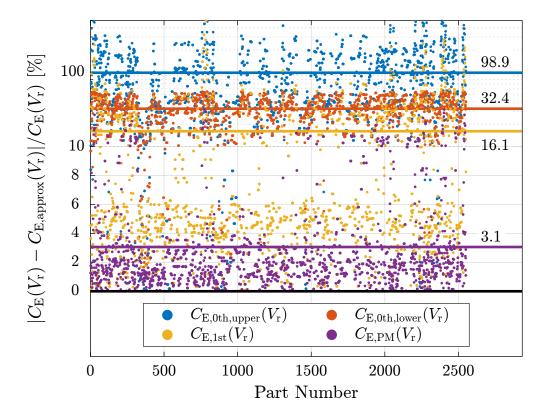

| 2.6  | Percentage error for approximations of energy-equivalent capacitance $C_{\rm E}(V_{\rm r})$ at                    |    |

|      | rated dc voltage $V_{\rm r}$ . Solid horizontal lines indicate the mean percentage error                          |    |

|      | for each corresponding approximation. Data is sampling of 2,550 TDK Class II                                      |    |

|      | MLCC capacitors.                                                                                                  | 22 |

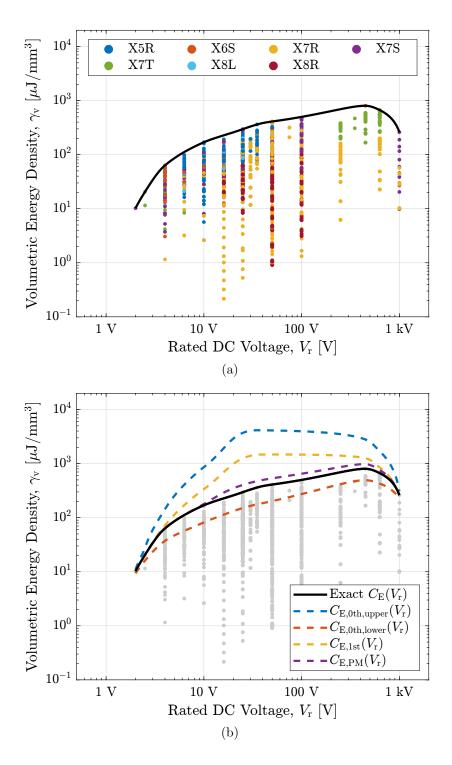

| 2.7  | Rated dc voltage $V_{\rm r}$ versus volumetric energy density $\gamma_{\rm v}$ for TDK Class II MLCC              |    |

|      | capacitors where (a) components are delineated by temperature characteristics                                     |    |

|      | and (b) the Pareto front varies depending on the approximation for $C_{\rm E}(V_{\rm r})$ .                       | 24 |

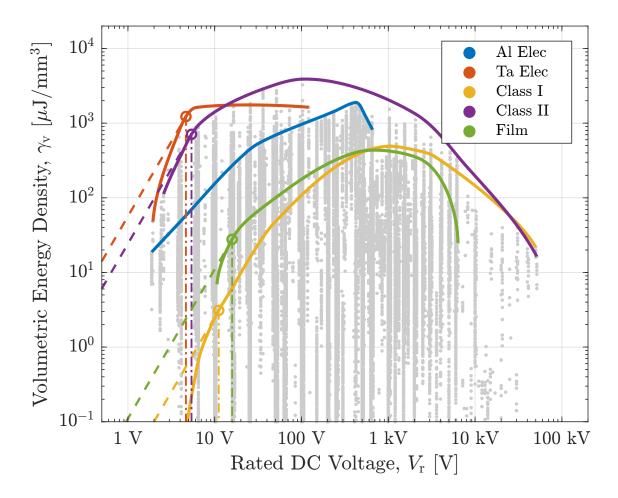

| 2.8  | Commercial capacitor volumetric energy density FOM $\gamma_{\rm v}$ across rated dc voltage                       |    |

|      | $V_{\rm r}$ . The Pareto fronts are highlighted as well as the critical rated voltage $V_{\rm r,crit}$            |    |

|      | where capacitor overrating becomes useful.                                                                        | 31 |

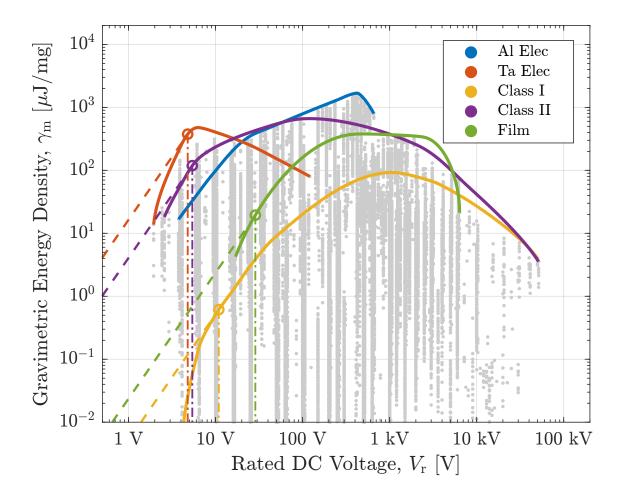

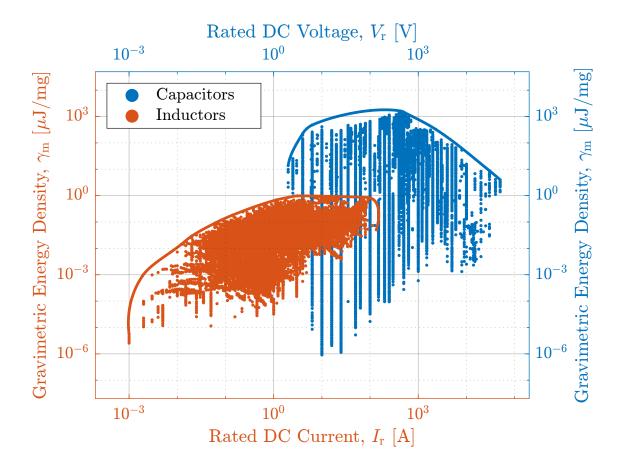

| 2.9  | Commercial capacitor gravimetric energy density FOM $\gamma_{\rm m}$ across rated dc voltage                      |    |

|      | $V_{\rm r}$ . The Pareto fronts are highlighted as well as the critical rated voltage $V_{\rm r,crit}$            |    |

|      | where capacitor overrating becomes useful.                                                                        | 32 |

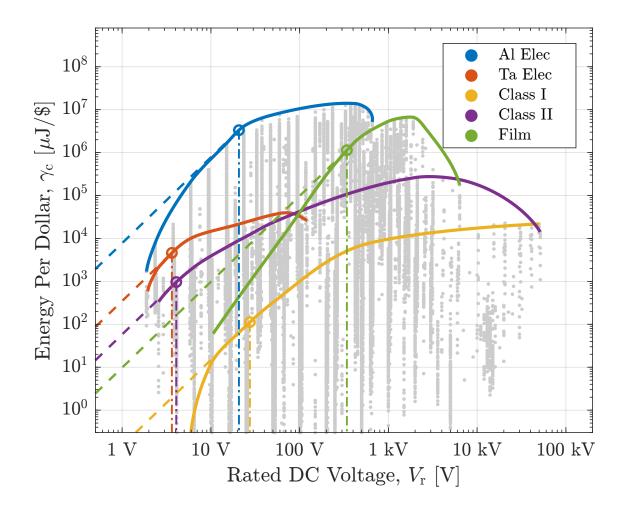

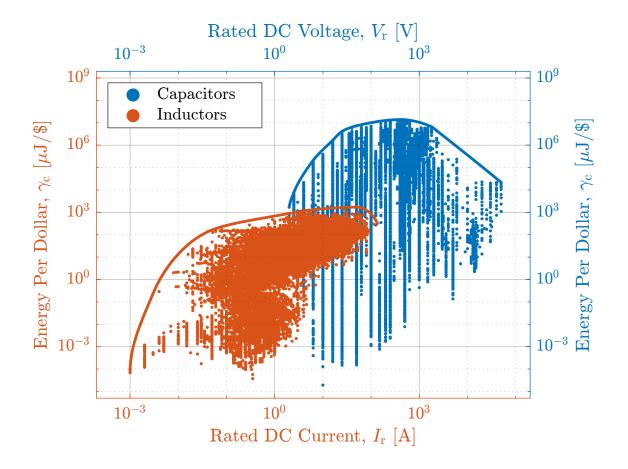

| 2.10 |                                                                                                                   |    |

|      | Pareto fronts are highlighted as well as the critical rated voltage $V_{\rm r,crit}$ where                        |    |

|      | capacitor overrating becomes useful.                                                                              | 33 |

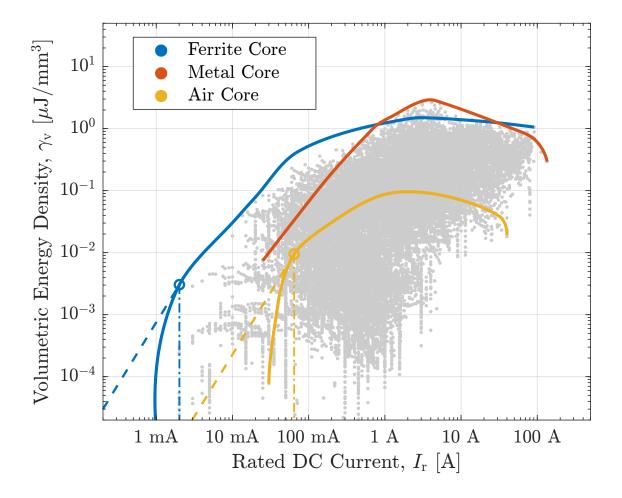

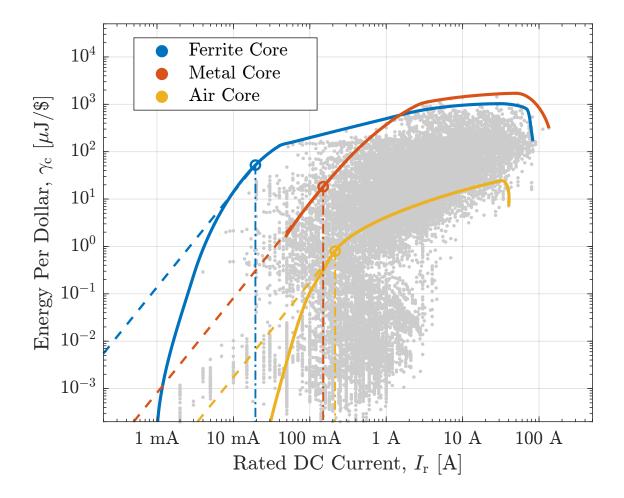

| 2.11 Commercial inductor volumetric energy density FOM $\gamma_{\rm v}$ across rated dc current $I_{\rm r}$ . The Pareto fronts are highlighted as well as the critical rated current $I_{\rm r,crit}$                                                                                                                                                                                                                   | 25              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| where inductor current overrating becomes useful                                                                                                                                                                                                                                                                                                                                                                         | 35              |

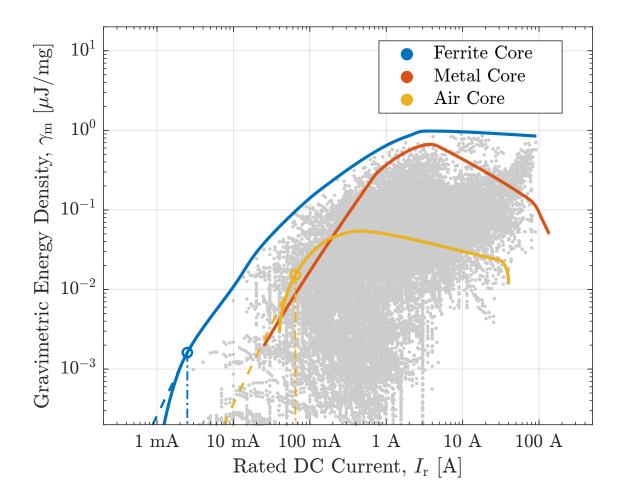

| where inductor current overrating becomes useful                                                                                                                                                                                                                                                                                                                                                                         | 36              |

| inductor current overrating becomes useful                                                                                                                                                                                                                                                                                                                                                                               | 37<br>38        |

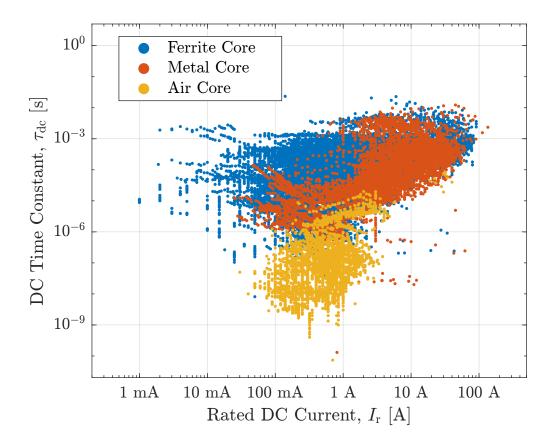

| 2.15 Rated dc current $I_{\rm r}$ versus dc quality factor $\tau_{\rm dc} = \frac{L}{\rm DCR}$ for all commercially sur-                                                                                                                                                                                                                                                                                                 |                 |

| veyed inductors. Data is distinguished by common core types                                                                                                                                                                                                                                                                                                                                                              | 39              |

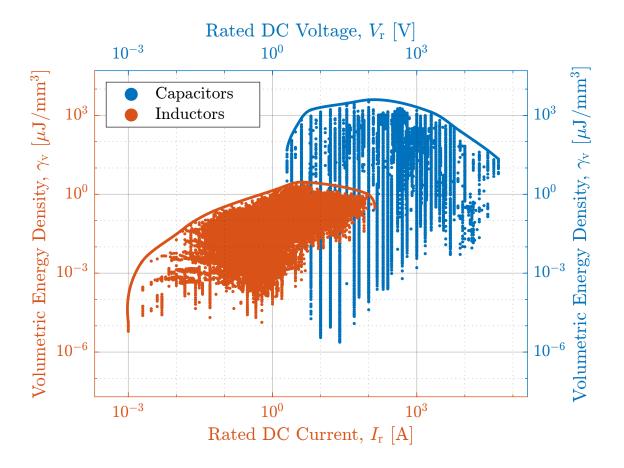

| capacitors have a roughly $1,000 \times$ better maximum volumetric energy density capability compared to commercial inductors.                                                                                                                                                                                                                                                                                           | 41              |

| 2.17 Commercial capacitor versus inductor gravimetric energy density FOM $\gamma_{\rm m}$ across<br>rated dc voltage $V_{\rm r}$ / current $I_{\rm r}$ . From the highlighted Pareto fronts, commercial<br>capacitors have a roughly 2,000× better maximum gravimetric energy density                                                                                                                                    |                 |

| capability compared to commercial inductors                                                                                                                                                                                                                                                                                                                                                                              | 42<br>43        |

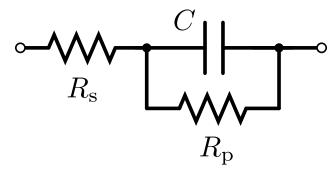

| 3.1 Conventional capacitor lumped circuit model including primary loss and leakage                                                                                                                                                                                                                                                                                                                                       |                 |

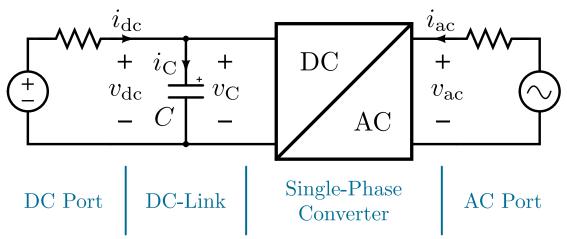

| <ul><li>parasitics.</li><li>3.2 Circuit diagram of dc-link capacitor in a single-phase power conversion system.</li></ul>                                                                                                                                                                                                                                                                                                | $\frac{46}{48}$ |

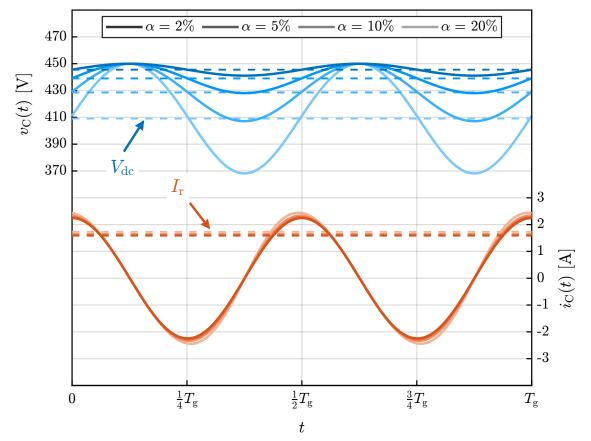

| 3.3 Dc-link capacitor voltage and current waveforms across one full line cycle with period $T_{\rm g}$ and with increasing specification of dc bus voltage ripple ratio $\alpha$ . As the ripple ratio increases, the capacitor is constrained with the same rated voltage                                                                                                                                               | 10              |

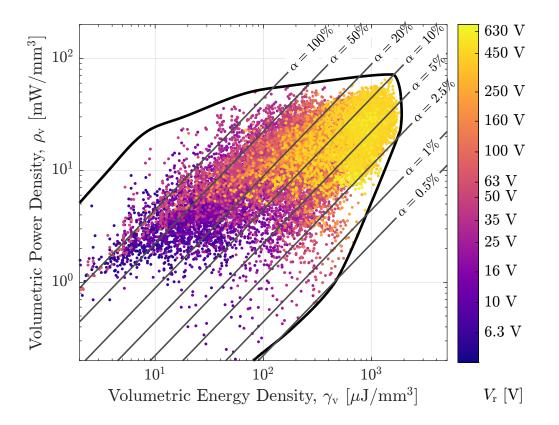

| 1.3.4 Volumetric energy density $\gamma_{\rm v}$ versus power density $\rho_{\rm V}$ versus rated dc voltage $V_{\rm r}$ for all commercially available aluminum electrolytic capacitors. The dc-link capacitor rated energy versus rated power isocline is shown for various ripple ratio $\alpha$ at line frequency $\omega_{\rm g} = 2\pi \cdot 60 \mathrm{rad/s}$ . For a specific $\alpha$ , capacitor banks formed | 50              |

| with components lying above the isocline satisfy energy buffering requirements.                                                                                                                                                                                                                                                                                                                                          | 52              |

v

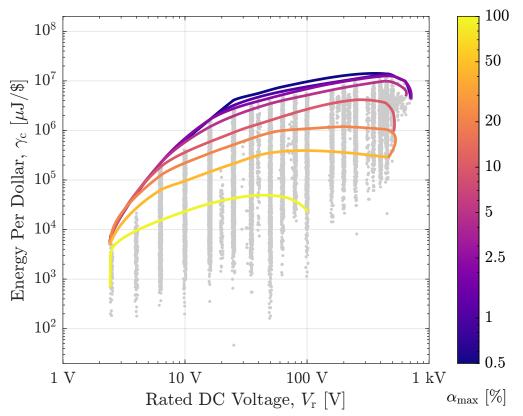

| 3.5                 | Rated dc voltage $V_{\rm r}$ versus energy per unit cost $\gamma_{\rm c}$ for all commercially available<br>aluminum electrolytic capacitors. For increasing bus ripple ratio rating $\alpha_{\rm max}$ , the<br>full data set reduces to only those components satisfying rated energy and power<br>requirements and the best performers in each subset are indicated with Pareto<br>fronts. | 54       |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

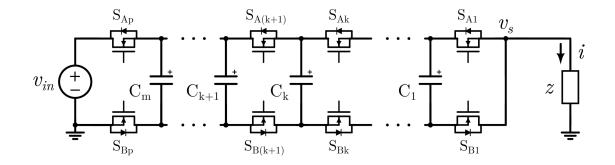

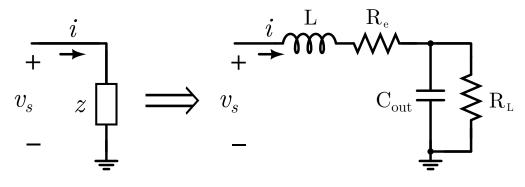

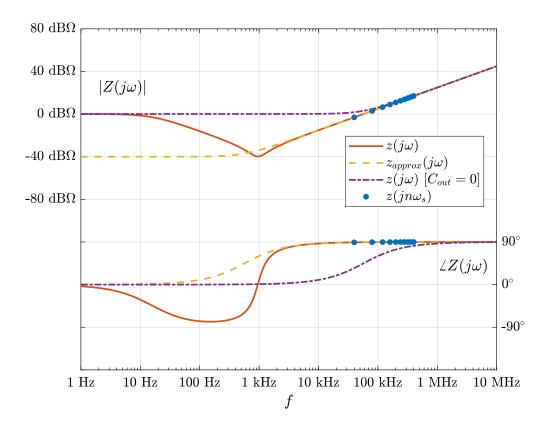

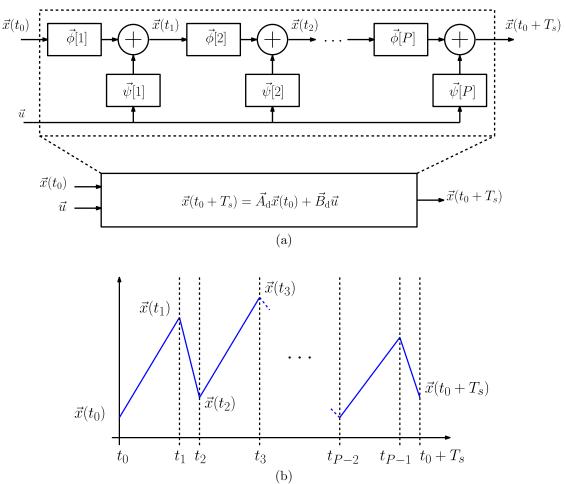

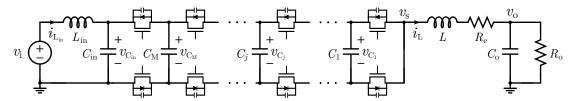

| $4.1 \\ 4.2 \\ 4.3$ | <i>N</i> -level buck-type FCML converter schematic. $m = p - 1 = N - 2$ Buck converter circuit schematic of traditional output impedance Output impedance z as a function of frequency. Includes critical harmonics $z^n$ , approximation pf z, and modeled z without output capacitance. Parameters:                                                                                         | 59<br>64 |

|                     | $L = 2.8 \ \mu \text{H}, R_{\text{e}} = 10 \ \text{m}\Omega, C_{\text{out}} = 10 \ \text{mF}, R = 1 \ \Omega, f_{\text{s}} = 40 \ \text{kHz}.$                                                                                                                                                                                                                                                | 65       |

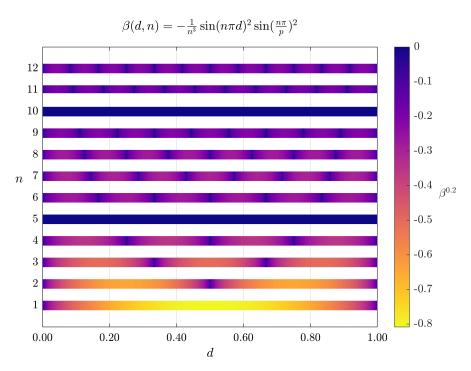

| 4.4<br>4.5          | Values of $\beta(d, n)$ for the 6-level $(p = 5)$ FCML                                                                                                                                                                                                                                                                                                                                        | 67       |

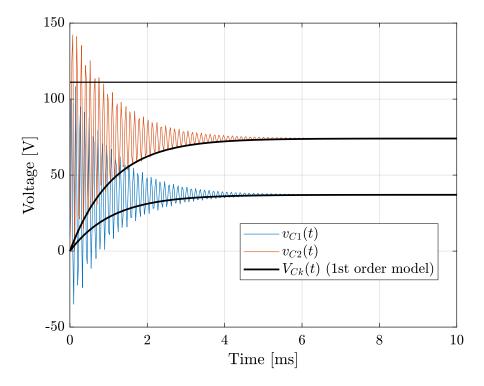

|                     | $v_{\rm in} = 100 \mathrm{V}, \ d = 0.45, \ L = 2.8 \mathrm{\mu H}, \ R_{\rm e} = 10 \mathrm{m}\Omega, \ C_{\rm out} = 10 \mathrm{mF}, \ R_{\rm L} = 1 \Omega, \text{ and} f_{\rm s} = 40 \mathrm{kHz}.$                                                                                                                                                                                      | 70       |

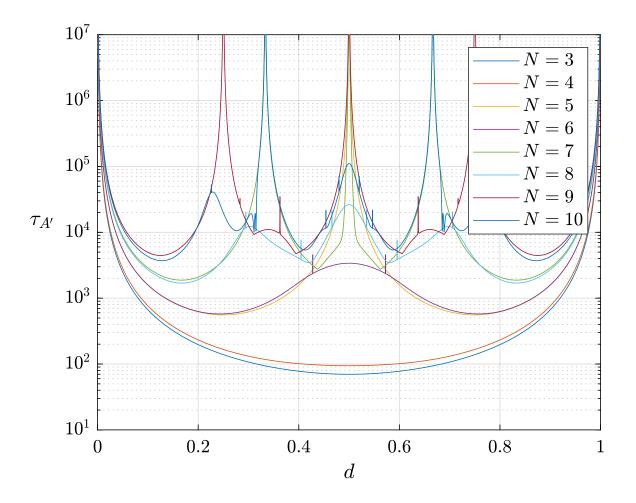

| 4.6                 | Functions of $\tau_{A'}(d, N)$ for duty ratio $d$ and number of FCML levels $N$ with symmetric PSPWM. Parameters: $L = 2.8 \ \mu\text{H}$ , $R_{\rm e} = 10 \ \text{m}\Omega$ , and $f_{\rm s} = 40 \ \text{kHz}$                                                                                                                                                                             | 71       |

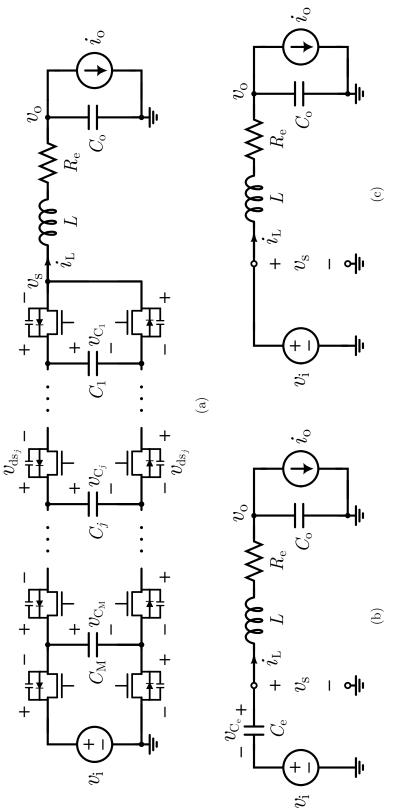

| 5.1                 | (a) General <i>N</i> -level FCML circuit schematic and its equivalent reduced circuit model for switching state (b) with ('Circuit A') and (c) without series connected                                                                                                                                                                                                                       |          |

| 5.2                 | flying capacitor ('Circuit B')                                                                                                                                                                                                                                                                                                                                                                | 76       |

|                     | count and $D = 0.35$ duty ratio.                                                                                                                                                                                                                                                                                                                                                              | 78       |

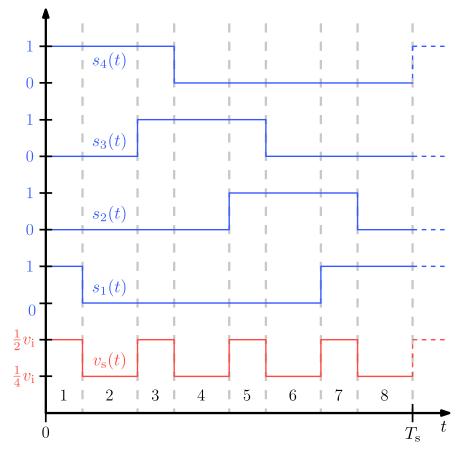

| 5.3                 | Block diagram showing the circuit state $x_i(t)$ accumulated across each switching phase into a full switching period.                                                                                                                                                                                                                                                                        | 85       |

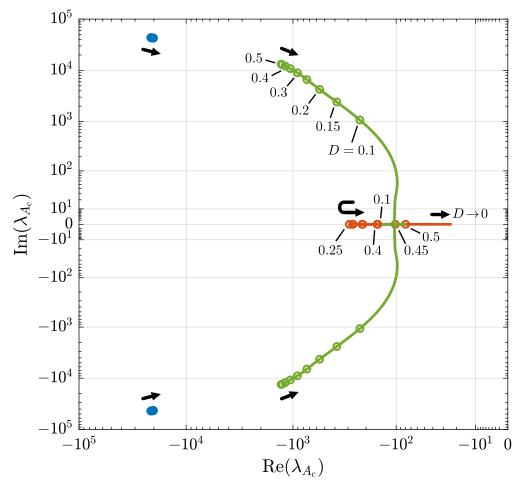

| 5.4                 | Root-locus diagram for eigenvalues of modeled $\vec{A}_c$ with swept duty ratio $D$ for<br>the $N = 5$ level FCML circuit with parameters in Table 5.1. The system and<br>consequent eigenvalues are symmetric about $D = 0.5$ (i.e., $D = 0.2$ is equivalent                                                                                                                                 |          |

|                     | to $D = 0.8$ )                                                                                                                                                                                                                                                                                                                                                                                | 88       |

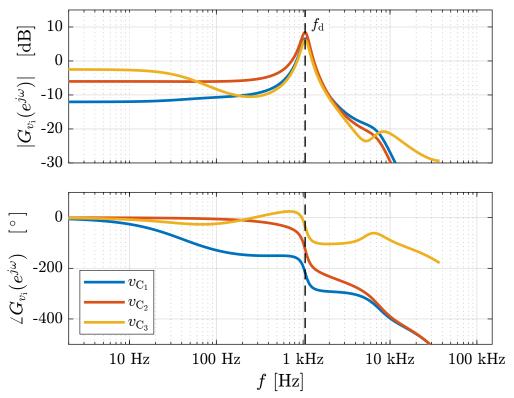

| 5.5                 | Modeled input voltage $v_i$ to flying capacitor $v_{C_j}$ small-signal transfer function magnitude $ G(e^{j\omega}) $ and phase $\angle G(e^{j\omega})$ for the $N = 5$ level FCML circuit with                                                                                                                                                                                               |          |

| 5.6                 | parameters of Table 5.1. The dominant resonant frequency $f_d$ is highlighted.<br>Modeled input voltage $v_i$ to drain-source voltage $v_{ds,j}$ transfer function magnitude $ G(e^{j\omega}) $ for the $N = 5$ level FCML circuit with parameters of Table 5.1. The                                                                                                                          | 91       |

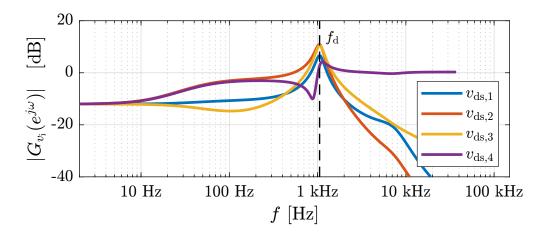

|                     | dominant resonant frequency $f_d$ is highlighted.                                                                                                                                                                                                                                                                                                                                             | 91       |

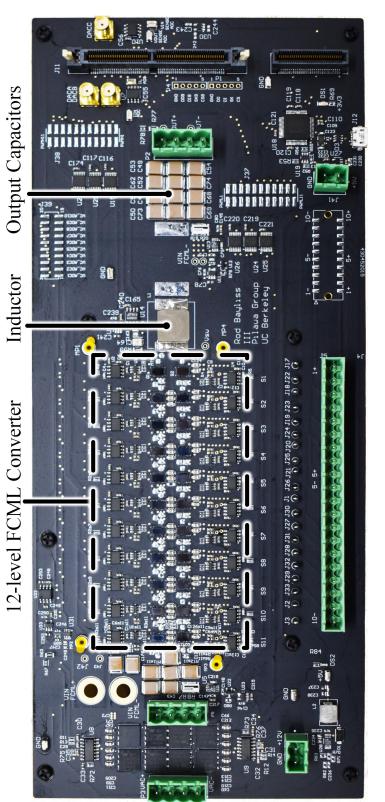

| 5.7                 | Hardware prototype of a high performance 12-level buck FCML converter                                                                                                                                                                                                                                                                                                                         | 92       |

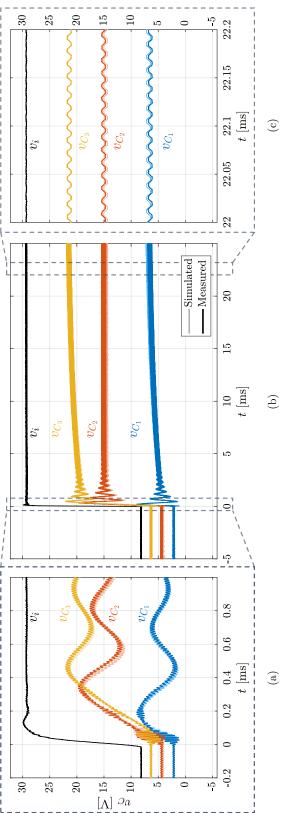

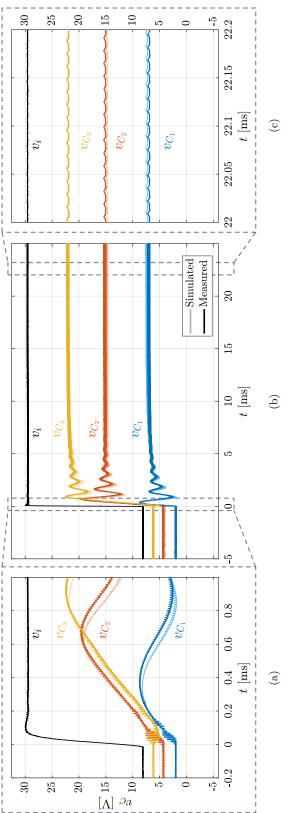

| 5.8                 | Measured versus modeled voltage dynamics for a $v_i = 7.5$ to 30 V step response<br>at $D = 0.5$ (leading symmetric PS-PWM). Highlights include (a) the initial<br>higher-order transients; (b) the full simulation with emphasis on the dominant                                                                                                                                             |          |

|                     | (slowest) system time constant; and (c) the steady-state switching ripple                                                                                                                                                                                                                                                                                                                     | 93       |

| 5.9                                       | Measured versus modeled voltage dynamics for a $v_i = 7.5$ to 30 V step response<br>at $D = 0.25$ (leading symmetric PS-PWM). Highlights include (a) the initial<br>higher-order transients; (b) the full simulation with emphasis on the dominant              |                                           |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

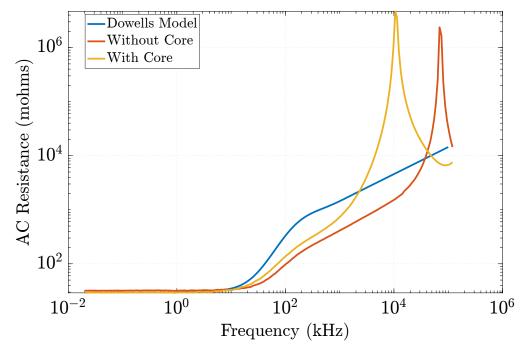

| 5.10                                      | (slowest) system time constant; and (c) the steady-state switching ripple<br>Measured small-signal resistance of the IHLP5050CEER100M01 inductor across                                                                                                         | 94                                        |

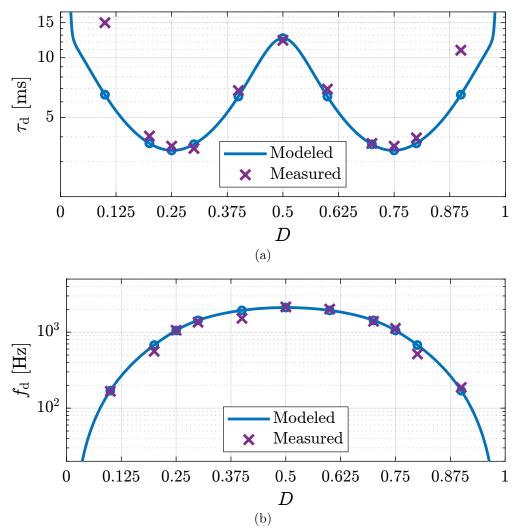

|                                           | frequency. Compared to modeled proximity resistance using Dowell's formula [50]. Measured versus modeled (a) first-order dominant time constant $\tau_d$ and (b) dom-                                                                                           | 95                                        |

|                                           | inant resonant frequency $f_d$ across duty ratio $D$ for the $N = 5$ level FCML converter described in Table 5.1.                                                                                                                                               | 97                                        |

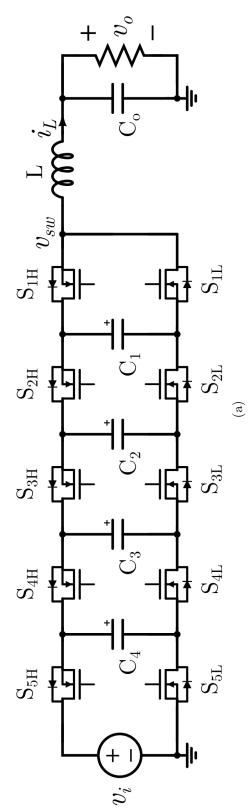

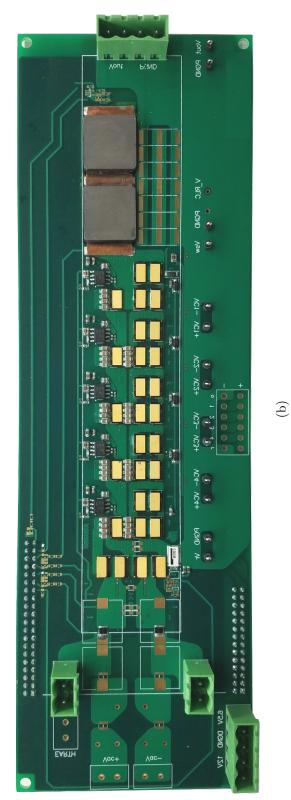

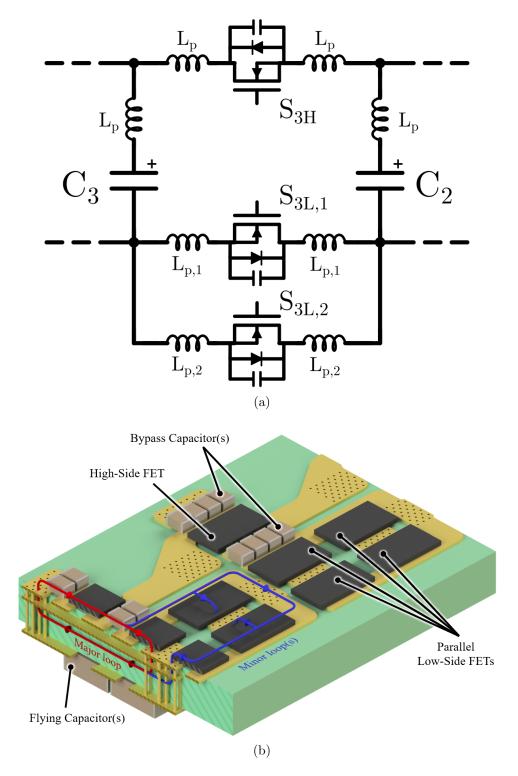

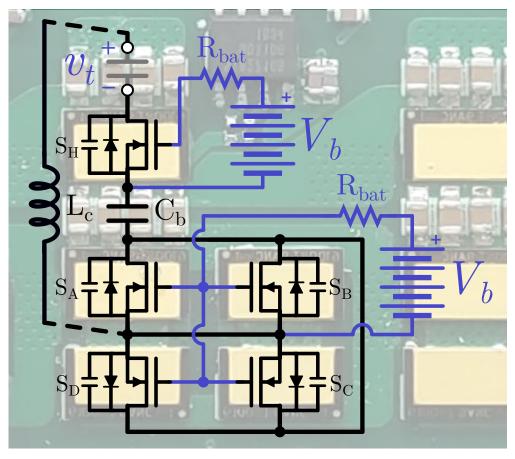

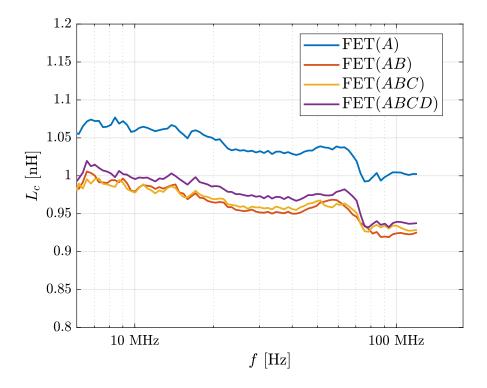

| 6.1                                       | Full 6-level FCML buck converter. (a) Simplified schematic and (b) hardware prototype photograph (front-side).                                                                                                                                                  | 107                                       |

| 6.2                                       | Asymmetrical switching cell definition, implementation, and characterization. (a)<br>Exemplar asymmetrical switching cell with inductive parasitics. (b) Rendered<br>switching cell with delineations for major and minor commutation paths (exag-              |                                           |

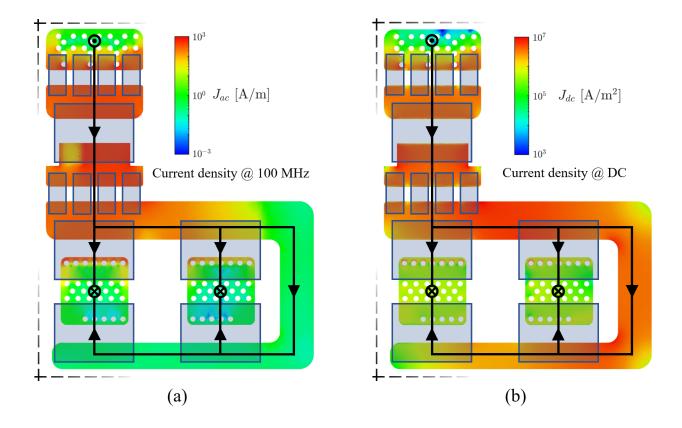

| 6.3                                       | gerated PCB layer thicknesses)                                                                                                                                                                                                                                  | 112                                       |

|                                           | $I_{\rm e} = 1$ A. (a) Illustration of surface current density distribution at a commutation<br>frequency of $f = 100$ MHz readily indicates the major and minor commutation<br>paths. (b) Surface current density distribution at dc demonstrating proper cur- |                                           |

|                                           | rent distribution between parallel FETs                                                                                                                                                                                                                         | 113                                       |

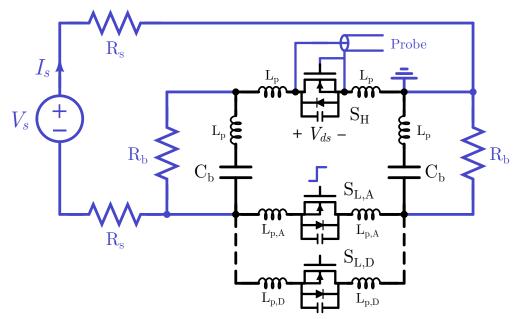

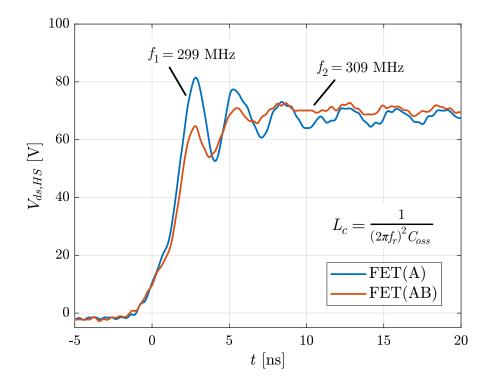

| $\begin{array}{c} 6.4 \\ 6.5 \end{array}$ | Transient-based measurement test circuit schematic. $R_{\rm s} = 100 \ \Omega$ , $R_{\rm b} = 100 \ \mathrm{k}\Omega$ .<br>Measured high-side $V_{\rm ds}$ during LS turn-on for varied configurations of paralleled                                            | 115                                       |

|                                           | low-side FETs. Input voltage $V_s = 70$ V, sink current $I_s = 2$ mA, and per-FET turn-on gate resistance $R_{g,on} = 4\Omega$ .                                                                                                                                | 116                                       |

| 6.6                                       | Impedance-based measurement testbench and overlayed circuit schematic of the switching cell commutation loop across $v_t$ . Batteries $(V_b = 6 \text{ V}, R_{bat} = 1 \text{ k}\Omega)$                                                                        | 110                                       |

| 6.7                                       | keep the GaN FETs in the on-state                                                                                                                                                                                                                               | 117                                       |

| 6.8                                       | are shown for increasingly paralleled quantities of low-side FETs                                                                                                                                                                                               | 118                                       |

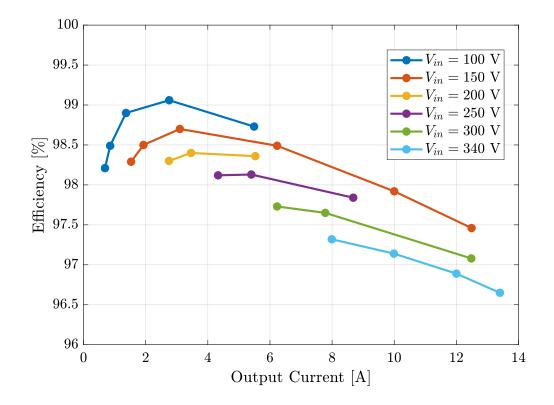

|                                           | tive loads for the 6-level FCML buck converter with asymmetrical switching cell design. Switching frequency $f_s = 100$ kHz and output voltage $V_o = 48$ V                                                                                                     | 119                                       |

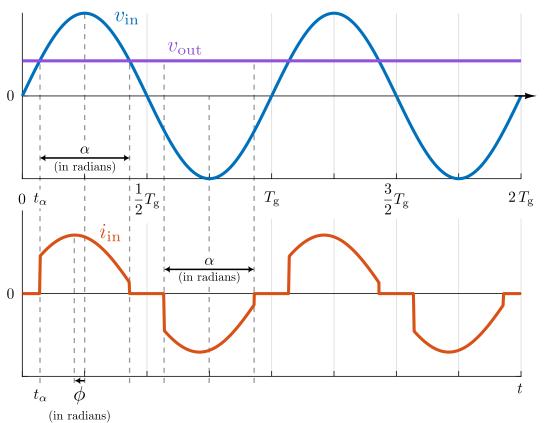

| 7.1                                       | Theoretical voltage and current waveforms for the buck PFC. The conduction angle $\alpha$ and displacement angle of the current $\phi$ are denoted                                                                                                              | 122                                       |

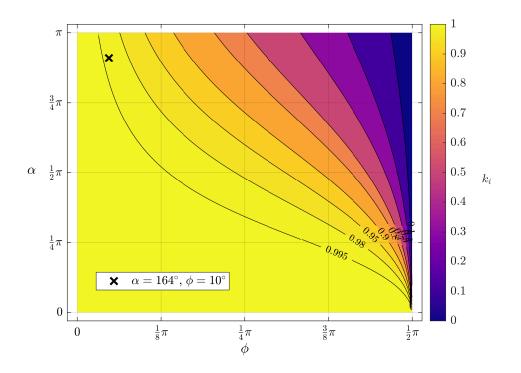

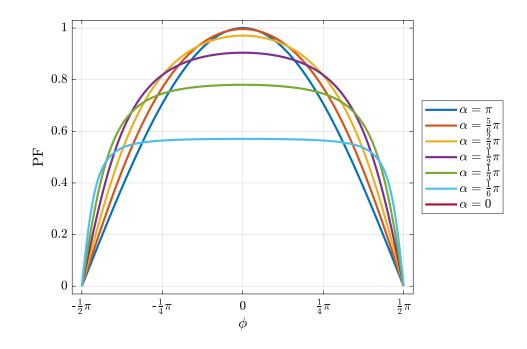

| $7.2 \\ 7.3$                              | Displacement factor $k_i$ as a function of $\alpha$ and $\phi$                                                                                                                                                                                                  | 127                                       |

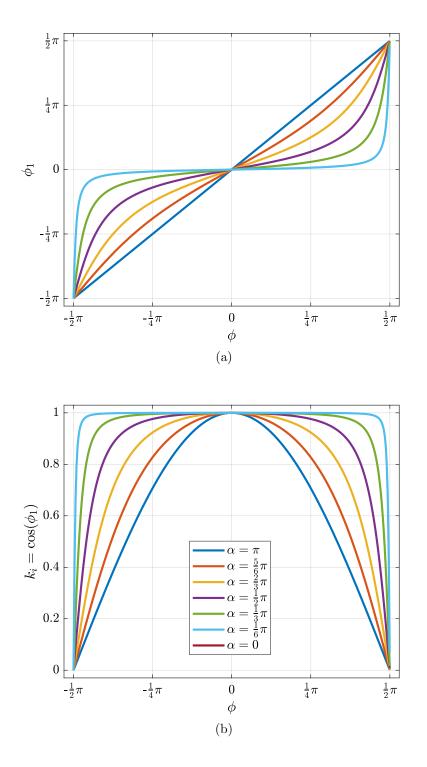

| <u> </u>                                  | for varied $\alpha$ .                                                                                                                                                                                                                                           | 128                                       |

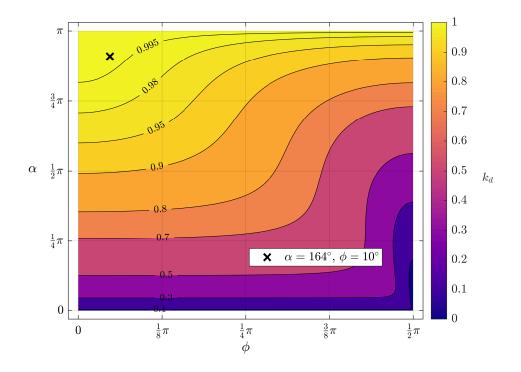

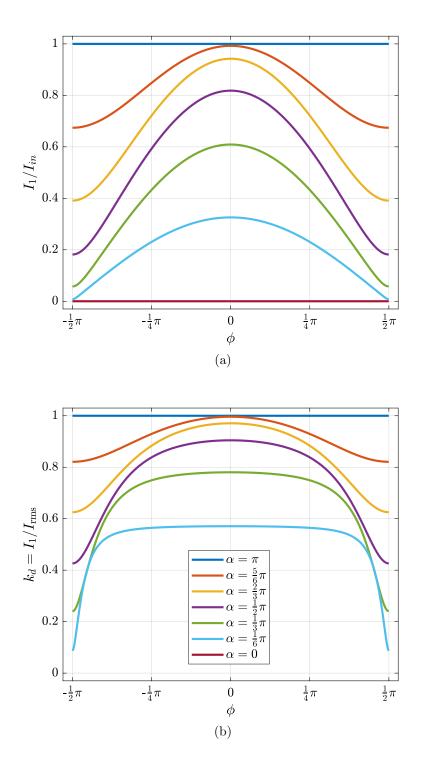

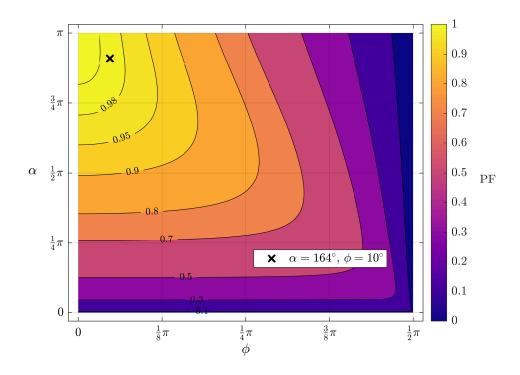

| $7.4 \\ 7.5$                              | Distortion factor $k_d$ as a function of $\alpha$ and $\phi$                                                                                                                                                                                                    | $\begin{array}{c} 129 \\ 130 \end{array}$ |

| 7.6  | Total power factor PF as a function of $\phi$ for varied $\alpha$                             | 132 |  |  |  |

|------|-----------------------------------------------------------------------------------------------|-----|--|--|--|

| 7.7  | Total power factor PF as a function of $\alpha$ and $\phi$                                    | 133 |  |  |  |

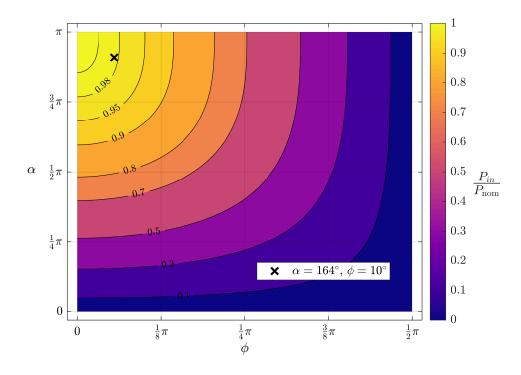

| 7.8  | 7.8 Relationship in $(7.45)$ between nominal power throughput $P_{\text{nom}}$ and real power |     |  |  |  |

|      | throughput $P_{\rm in}$ for the truncated and phase displaced system.                         | 137 |  |  |  |

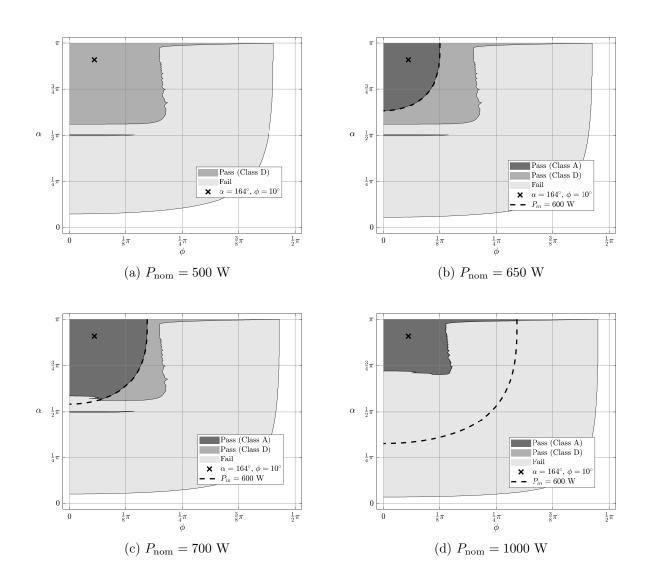

| 7.9  | Theoretical pass/fail compliance regions of truncated input current according to              |     |  |  |  |

|      | IEC 61000-3-2 Class A and D equipment. Nominal rated power $P_{\text{nom}}$ is varied to      |     |  |  |  |

|      | show the transition from Class D to Class A standards                                         | 140 |  |  |  |

| 7.10 | Aggregated theoretical pass/fail compliance regions of truncated input current                |     |  |  |  |

|      | according to IEC 61000-3-2 Class A and D equipment. Nominal rated power                       |     |  |  |  |

|      | $P_{\rm nom}$ is varied to show the transition from Class D to Class A standards              | 141 |  |  |  |

| 7.11 | Theoretical pass/fail compliance bounds $\alpha$ and $\phi$ of IEC 61000-3-2 Class A and      |     |  |  |  |

|      | D equipment. Nominal rated power $P_{\text{nom}}$ is varied                                   | 142 |  |  |  |

| 7.12 | Theoretical pass/fail compliance of truncated input current according to IEC                  |     |  |  |  |

|      | 61000-3-2 Class D equipment (75 W $< P_{\rm in} < 600$ W) standard. $P_{\rm nom} = 500$ W .   | 143 |  |  |  |

| 7.13 | Comparison of theoretical and measured input current waveforms at $P_{\rm nom} = 216$ W       | 144 |  |  |  |

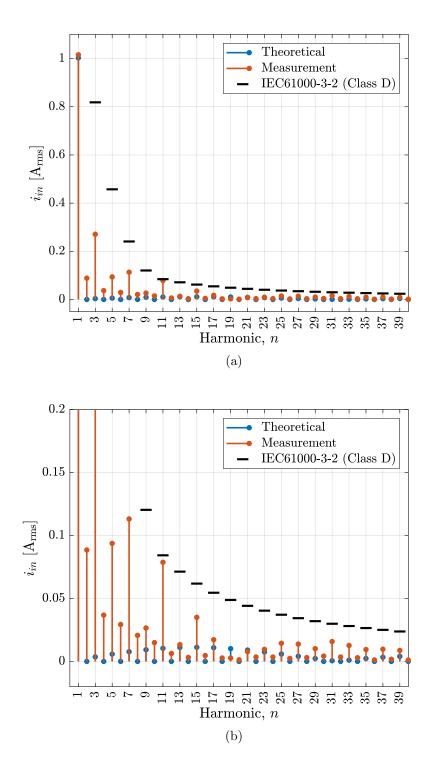

| 7.14 | Theoretical and measured input current harmonic limits compared to IEC61000-                  |     |  |  |  |

|      | 3-2 (Class D) limits at $P_{\rm nom} = 216$ W. (a) zoomed out and (b) zoomed in               | 145 |  |  |  |

|      |                                                                                               |     |  |  |  |

# List of Tables

| 2.1 | Generic capacitor bank specifications and constructed figures-of-merit                                                  | 9   |

|-----|-------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2 | Percentage Error for $C_{\rm E}(V_{\rm r})$ Approximations                                                              | 20  |

| 2.3 | Results of proposed mean fit and empirical power fit for capacitor/inductor vol-<br>umetric mass density (mass/volume). | 28  |

| 2.4 | Summary of Critical Voltages for Capacitor Overrating                                                                   | 30  |

| 2.5 | Summary of Critical Currents for Inductor Overrating                                                                    | 35  |

| 5.1 | Nominal Circuit Parameters                                                                                              | 86  |

| 5.2 | Hardware Component Details                                                                                              | 89  |

| 6.1 | Measurement and simulation results of commutation loop inductance $L_c$ at $f = 100 \text{ MH}_{-}$                     | 110 |

|     | 100 MHz                                                                                                                 | 110 |

| 7.1 | IEC 61000-3-2: Limits for Class D equipment (75 W $< P_{in} < 600$ W) $\ldots \ldots$                                   |     |

| 7.2 | IEC 61000-3-2: Limits for Class A equipment $(P_{in} > 600 \text{ W})$                                                  | 136 |

#### Acknowledgments

This is an extensive list of acknowledgements, but each person mentioned has had a marked influence on my life these past years in graduate school. I would not be who I am today without them.

First, thank you to all of those people who aided me in my research these last few months. You have helped me accomplish so much in too little of an amount of time, and my present vocational goals are possible due to your charitiable efforts. An especial thanks to Finn Giardine, Jiarui Zou, Sam Coday, Nathan Ellis, Bradley Bowles, Elissa Krause, Ting Ge, Rahul Iyer, Nathan Biesterfeld, my advisor Robert Pilawa-Podgurski and my other thesis committee members for their significant editing and contributions towards the writings that invariably became part of this thesis.

This first section acknowledges the past and present members of my research group who have shared so much life with me. Thank you to my graduate student mentors during my earliest years in graduate school: Shibin Qin, Enver Candan, and Zitao Liao. I know that mentoring a barely capable junior graduate student must have had its frustrations, but I appreciate all of your patience. You were and still are each wonderful role models, and continue to inspire me in the ways I engage with and mentor others. I also appreciate the additional past alumni and visitors of our research group: Ting Ge, Zichao Ye, Pourya Assem, Chris Barth, Wen-Chuen (Joseph) Liu, Nathan Pallo, Andrew Stillwell, Yutian Lei, Pei Ng, Sophia Chou, Thomas Foulkes, Yizhe Zhang, Michelle Rentauskas, Yong-Long (Max) Syu, Ivan Petric, Mads Taul and several members prior to my time who I have never had the pleasure of meeting. Our research group's most vital and wonderful feature is its people, and you have all cultivated an especially collaborative, enjoyable, and enduring group culture. The research group today owes to you much of the expectations for joviality and passion towards engineering and study.

I especially want to thank all of the current members of my research group. First, there is my senior cohort: Sam Coday, Maggie Blackwell, Rose Abramson, Kelly Fernandez, as well as postdoctoral student Nathan Ellis. It was great fun to work and struggle diligently together to create something enduring. And thank you to the other members: Logan Horowitz, Rahul Iyer, Yicheng Zhu, Rod Bayliss, Finn Giardine, Jiarui Zou, Sahana Krishnan, Haifah Sambo, Elisa Krause, Nathan Biesterfeld, Nagesh Patel, Jospeh Schaadt, Ben Liao, Will Vavrik, Marrin Nerenberg, and Shalin Shah. I do not have space to acknowledge all of you independently, but just know that many of you have profoundly impacted my life. You have each been a true pleasure to work with and I wish the best for you all as you accomplish your aspirations and succeed in your life's endeavors.

There are several of these individuals I must highlight in particular. Thank you Sam Coday (and your husband, Chance) for your constant willingness to answer my questions about research and teaching. You have always been one step ahead of me, and my path is made easier following in your footsteps. Thank you for being such a personal role model and motivating me to strive towards the best professional I can be: capable and dependable in the eyes of others.

Thank you Shalin Shah for trusting both me and my initially flimsy research vision for large-scale passive component characterization. Your dedicated commitment has strengthened and ultimately realized this now shared vision.

Without Rahul Iyer, Rod Bayliss, Logan Horowitz, and Ivan Petric, the components of my research and thesis relating to the flying capacitor multilevel converter (FCML) would not have materialized as soon. Their efforts in writing, theorizing, and experimenting were instrumental to my success. I am deeply pleased with my time in graduate school and the results of my PhD research, and much of what you read in this thesis is owed to their sincere collaborative efforts. I will further acknowledge these four individuals in particular.

Firstly, Rahul Iyer—a man with an innately adventurous nature. Your kindness, thoughtfulness, and helpfulness have greatly elevated the validity and rigor of my research. I hope your future excursions into the modeling and control of multi-phase power converters can be as impactful to the power electronics field as I dream they can be.

Rod Bayliss, your passion is infectious. You have (quite successfully) encouraged me to more fully engage with the world, something for which I am eternally grateful. And although prudence is certainly important, you have demonstrated to me a more active and less circuitous approach to practice engineering. In having spent much time with you, I suspect the synapses within my brain are now rewired more efficiently.

Logan Horowitz, thanks for being an open, honest friend and sharing so much of your time and your passions. You have an unusually quirky and creative approach to engineering and I look forward to witnessing the future path your life will take.

Ivan Petric, you are without doubt uniquely gifted at making deep friendships. And your technical competence and precision inspires me. I have particularly enjoyed our every past conversation on life, and look forward to every future one.

Now on to other acknowledgments. Thank you to Rose-Hulman, my undergraduate alma matter, for building me a firm foundation of engineering knowledge. There are more than several qualities especially endearing about that school, and it well prepared me for the graduate school. I am especially excited to be working there as a teaching professor after my graduation, surrounded by teachers and a community I hold in such high esteem. I owe a specific thanks to Professors Ed Wheeler, Tina Hudson, and Daniel Moore for being fantastic academic and research advisors.

Thank you to the University of Illinois at Urbana-Champaign for patronizing my early graduate school studies. And thank you Professor Subhonmesh Bose at the University of Illinois for guiding me through my first proper experience as a teaching assistant.

I am greatly appreciative to the University of California, Berkeley for providing me the multitude of opportunities to explore and participate in the pursuit of learning. Thank you Shirley Salanio for being an ever-present advocate and helping me meet my graduation requirements.

Thank you Professors Miki Lustig, Laura Waller, Rikki Mueller, and especially Professor Ana Arias for providing me the wonderful opportunity to be a teaching assistant for the introductory electrical engineering course at Berkeley: EECS 16A. In particular, Ana and Miki inspired me while I watched their unique, lively lectures and educated me as we deliberated course logistics and content. I have learned from you two so much of what a professor can and should be. And you also personally taught me the life-altering impact of just a few encouraging words, and I will forever be grateful for your faith in my untempered abilities.

Much thanks to Alfredo De Goyeneche, Tiffany Chien, Anniruddh Khanwale, Anvitha Kachinthaya, Anish Dhanashekar. As teaching assistants, you inspire as you pursue the best possible experience for students, and I greatly enjoyed those moments we worked together.

Thank you Robert Pilawa for being the best advisor, mentor, and supervisor I could ever hope for. I have grown and matured tremendously under your care, and I truly have few complaints after seven years. You are a role model as a professor, an engineer, a teacher, a husband, and a father. And I would be bereft to not acknowledge your wife, Brooke, and your children. Thank you for supporting him as he rassles our unwieldy research group.

And now into the last section of my acknowledgements. Thank you Josh Hanlon, Mike Hanlon, and Travis Luther for our shared efforts to learn more about the world through literature. Our journey has transformed me.

Thank you Fawaaz Shaffeeullah, Elijah Stanger-Jones, and David Kornfeld: three impressively talented engineers and friends who share with me a penchant for merry competition and tomfoolery. Your dependable camaraderie has uplifted me these past few years.

Thank you Joe Millitello, Max Kelly, Peter and Julianne Larson, Kirsten Sullivan, Nithin Perumal, Daniel McGarry, Alec Tiefenthal, Tyler Miller, Jacob Knispel, and Tim Smith. You have been present during my most joyous and some of my most despairing moments and I treasure our uniquely enduring friendships. Thank you Alex and William for forever changing the course of my life for the better. Now I know the difference between good and evil, and I have sufficient conviction to stand up for what is right when it most matters.

Thank you to my dearest friends these many years: Thomas Jansen, Jonathan Class, Bradley Bowles, and Josh Hanlon. It is commonly said that one's friends are a reflection of their character, but in truth they shape it. I am blessedly overjoyed and gratified knowing you are the people who have shaped me. Thank you especially to Thomas (and your wife Hannah) Jansen. You are a sincere man of faith, family, and friendship. You are the best man I know, you are always there for me, and I am blessed to be your brother.

I appreciate all of the members of my immediate and extended family, as well as family friends. You who have consistently supported and encouraged me since before I could even speak. Thank you Aaron, my (biological) brother, who knows me better than anyone else. I am immeasurably proud of you and your accomplishments and you have always inspired me to be a better man. Thank you Mom and Dad. You have always been the wind in my sails—loving and supporting me in every stage of my life. I owe this wonderful life to you.

I thank You most above all, Jesus Christ my Lord and Savior, whose love has no bound. I share a certainty with a greater man than I who once said, "What is done by what is called myself is, I feel, done by something greater than myself in me." [156]. That 'something' is You, God who, with grace, designed and created this wondrous world and its incomprehensible majesty—including both my mind's capacity for understanding and those marvelous and intensely peculiar phenomenon of electronics I consider with awe and exuberance. For all who read this thesis, please enjoy His work.

# Chapter 1

# Introduction

# 1.1 Introduction

This thesis culminates research of several disparate subtopics aimed at the high-performance design of hybrid switched-capacitor power converter circuit topologies. The formation of semi-meaningful solutions to this design objective requires intensive characterization of presently available capacitors and inductors (Part I); accurate modeling of the periodic, multi-state switching circuits (Part II); and improvements in hardware implementation such as the printed circuit board layout (Part III). This work is by no means definitive, however, it does form a reasonable foundation and highlights avenues of future approach.

# 1.2 Organization of Thesis

# Part I: Passive Components in Power Electronics

High performance power electronics design requires a firm characterization of active and passive components. This part presents a framework for quantifying passive component performance by reviewing existing device characterization methods and applying robust device figures-of-merit.

### Chapter 2: Passive Component Survey and Characterization

Assemblage of a comprehensive survey yields aggregated data for nearly 700,000 commercial capacitors and inductors of all types. To supplement deficiencies in this data, this chapter proposes and validates several empirical expressions to estimate passive component energy storage and mass. Estimation of volumetric mass density per component type allows the approximation of component mass from accessible box volume. Estimation of energyequivalent capacitance in nonlinear Class II ceramic capacitors facilitates the evaluation of stored energy and related energy density figures-of-merit. A phenomenological analysis of the comprehensive component data produces several conclusory determinations about peak energy density capabilities—with respect to volume, mass, and cost—across capacitor and inductor technologies.

# Chapter 3: Application of Passive Component Data to DC-Link Buffering Capacitor

The conventional dc-link aluminum electrolytic capacitor bank simply, efficiently, and costeffectively decouples the instantaneous power mismatch inherent to all single-phase ac-dc power converters. However, the practical realization of the capacitor bank remains largely qualitative and dependent on the opaque performance capabilities of the capacitor technology. This chapter presents an exhaustive survey of commercial aluminum electrolytic capacitors and defines both quantitative and justly comparative device-level figures-of-merit (FOM). By configuring the relative voltage ripple ratio specification  $\alpha$  of the dc bus, these device FOM enable the determination of minimal dc-link capacitor volume, cost, and/or mass. Graphical illustration demonstrates that the set of commercially available yet viable components diminishes as specification  $\alpha$  increases; the realized dc-link capacitor bank volume and cost will grow appreciably for  $\alpha > 10\%$  and  $\alpha > 5\%$ , respectively.

# Part II: Modeling of the Flying Capacitor Multilevel Converter

In recent decades the flying capacitor multilevel (FCML) converter has been demonstrated to be a highly compact and efficient substitute for conventional switched inductive topologies. However, the fundamental dynamical behavior of the additional flying capacitor voltages has not been well characterized to a predictable level for phase-shifted PWM modulation strategies.

# Chapter 4: Review of Continuous-Time State-Space Modeling for the FCML Converter

The dynamical behavior of the flying capacitors in the FCML are unable to be modeled using conventional small-signal linearization and averaging techniques for periodically switched power converters. This chapter revisits the derivation of the frequency-domain generalized average model proposed in [114]. It both simplifies and extends the original analysis and assumptions, and it affirms prior intuition for effects of circuit parameter dependence and duty ratio instability on dynamic performance.

# Chapter 5: Discrete-Time State-Space Modeling for the FCML Converter

With the context of previously defined averaged circuit model, this chapter presents an accurate and computationally efficient analytical model for the buck-type FCML converter which includes the critical influences of parasitic resistance and transistor output capacitance  $C_{oss}$ .

The complete modeling methodology produces a discrete-time state-space dynamical representation applicable to converters with multiple switching states. Analysis of the model eigenvalues elucidates the impacts of parameter variation on capacitor voltage balancing performance—including input-to-state disturbance rejection—in the time and frequency domains. The model is validated against a high-performance 5-level hardware prototype.

# Part III: Multilevel Converters for Buck-Type Power Factor Correction

This final part investigates several practical considerations enabling the use of multilevel converters in buck-type power factor correction (PFC) conversion systems.

### Chapter 6: PCB Layout Improvements for the Buck PFC FCML Converter

Proper utilization of GaN devices generally necessitates ultra-low inductance printed circuit board (PCB) layout in the main commutation loop or switching cell of a power converter. The flying capacitor multilevel (FCML) topology in particular contains many of these switching cells, thus design optimization becomes critical. A novel asymmetrical cell layout design with sub-1 nH commutation loop inductance is proposed for the FCML converter and characterized with a transient- and impedance-based measurement technique in conjunction with 3D field simulation. To validate its efficacy, this switching cell design is demonstrated within a prototype high performance step-down intermediate bus converter supply ( $v_{out} = 48 \text{ V}$ ) with wide input voltage range ( $v_{in} = 48 \text{ to } 340 \text{ V}$ ).

# Chapter 7: Power Factor and Harmonic Limitations of the Buck PFC Converter

The single-phase buck-type PFC converter is incapable of achieving unity power factor because it cannot conduct near the zero-crossing of the ac line. However although imperfect, this conversion system still ably meets current harmonic benchmarks in most practical cases. This chapter investigates the theoretical conversion limitations of the buck-type PFC power converter—including the impact of phase displacement—and derives expressions for fundamental limits according to IEC current harmonic emissions standards.

# Part I

# Passive Components in Power Electronics

# Chapter 2

# Passive Component Survey and Characterization

# 2.1 Introduction

Modern power electronic converters comprise active semiconductor devices (e.g., diodes and transistors), and passive devices to electromagnetically store and release energy (e.g., capacitors, inductors, transformers). A comprehensive understanding of the breadth and capabilities of these devices is required to design and realize a physical converter of desired conversion efficiency, volume, mass, cost, lifetime, and dynamic performance. Both novel and mature component technologies constantly improve over time, and the best-suited device for a particular application depends on the system specification and, even more intricately, on other selected devices.

The choice of optimal circuit topology varies when scrutinizing the passive devices in particular. The most mature switched-mode circuit topologies primarily rely on inductors for energy storage (e.g., buck; boost; buck-boost; flyback; and dual-active bridge, DAB, converters). Since they are difficult to miniaturize [167], inductors continue to demand intense research focus for the device-level design of power converters. The comparably lower losses and higher energy densities of capacitors [133, 42, 203] have motivated the investigation and development of more inductive/capacitive circuit topologies in recent decades: multilevel converters [144] (e.g., modular multilevel converter, MMC [158, 127, 48]; flying capacitor multilevel, FCML, converter [115, 107, 88]); hybrid switched capacitor converters [11, 87, 154, 108] (e.g., series-capacitor buck [121, 74, 157]); and isolated resonant converters [162] (e.g. series-resonant [76, 91]; LLC [100, 49]). These families of power converter topologies are each high-performance and can maximally utilize the energy storage and power throughput capabilities of both capacitors and inductors.

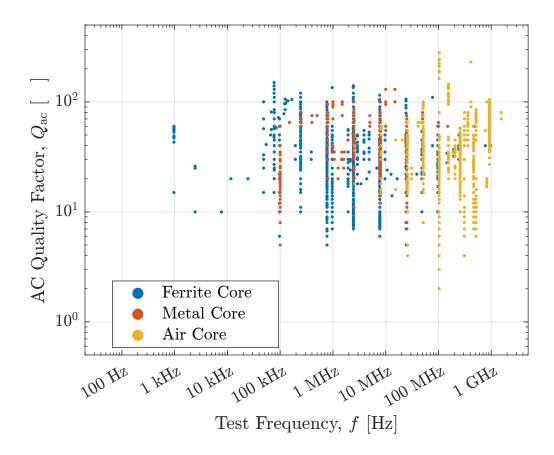

This chapter extends our previous conference paper [203] by aggregating a comprehensive set of device data and motivating useful figures-of-merit (FOM) for comparison and extension to design. Section 2.2 describes general methods for device-level characterization and introduces a framework for producing robust, or maximally applicable, device FOM. Employing comprehensive data collection, this chapter surveys a useful breadth of over 606,000 commercial capacitors and 88,000 commercial inductors as detailed in Section 2.3. Additional sampled data is garnered to supplement and augment particular deficiencies in this large data set. To enable complete characterization of energy storage metrics—the critical benchmark of capacitive and inductive energy storage elements—a sampled set of capacitor data is collected and extrapolated to the full data set as described in Section 2.4. To estimate component mass, a sampled set of components is measured and extrapolated to the full data set as described in Section 2.5. After applying the supplements to energy storage and mass, Section 2.6 investigates several device FOM for all surveyed components. As a demonstration, the analysis compares the energy densities of various capacitor and inductor technologies, specifies the conditions for voltage overrating in capacitors and current overrating in inductors, and examines the quality factor capabilities of inductors.

# 2.2 Characterizing Components and Defining Performance

Making reductive determinations from millions of passive components requires careful consideration of how data is collected and then manipulated into useful quantitative metrics that describe comparative performance trade-offs. The goal is to produce founded statements such as "based on the present available technology, the smallest possible capacitor solution for this application has volume X." To substantiate these claims, this chapter first introduces viable methods of data aggregation and analysis, then motivates useful device FOM.

# **Data Analysis Methods**

There are three general methods to determine the broad capabilities of a set of circuit components, where sets are classified by the distinctive 'type' or 'technology' of the component.

### Analytically derived performance

Utilizing a first principles approach based in physics, one can derive analytical expressions for the lumped circuit model of an electrical device from its internal geometries and constituent material properties. Further determinations are either made directly from the analytical expressions, iteratively fit to measured data, or generated using a probabilistic Monte Carlo simulation. Examples of analytic methods include estimation of the 'macroscopic' hysteretic losses of Class II ceramic capacitors from 'microscopic' properties in [110, 111, 75]; quality factor prediction of air core inductors in [159]; derivation of frequency-dependent volume and loss scaling trends in inductors in [167]; and estimation of parasitics for transistors in [12].

#### Sampled data and extrapolation

Data collection, often measured, can completely characterize circuit phenomenon for small data sets. However for large sets of intractable or unknown data, intelligent data sampling can yield exceedingly meaningful qualitative and quantitative insight. With additional care, the sampled data extrapolates to larger supersets of data—especially with the advent of recent machine-learning (ML) techniques. This sampled data method is applied to predict capacitor ESR and quality factor in [42, 15]; capacitor lifetime in [70, 10, 109]; power loss in inductors in [68, 159]; and power FET losses in [12, 57]. Another variation of this sampled data approach trains ML models to predict core losses in broadly excited inductors [89, 90] and to predict losses in transistors [137].

#### Comprehensive data collection

The proliferation of digitized data and its increasing ease of access enables large-scale, comprehensive, and practically exhaustive collection of component information. Distributors of electrical components have consistently lead efforts to aggregate and disseminate quantitative component information, however, many individual manufacturer/suppliers have drastically broadened their interactive design tools and consumer interfaces as well. A comprehensive consideration of data necessarily enables conclusive interpolative—rather than extrapolative—quantification of performance and a holistic cognizance of notoriously mercurial metrics such as cost. A comprehensive data collection approach in [28] is used to benchmark performance amongst commercial high power switch technologies (> 1 kV and > 1 kA). A recent approach in [137] uses data from commercial capacitors, inductors, and transistors to train ML models and produce optimal converter designs [138].

This chapter primarily employs the *comprehensive data collection* approach for device characterization. In aspects where this method stalls, *sampled data and extrapolation* is utilized to augment the comprehensive data set.

# Defining Useful Device Figures-of-Merit

Meaningful device metrics, deemed figures-of-merit (FOM), must be developed in conjunction with bulk device characterization. A good FOM is a quantitative measure of performance and indisputably indicates better performance for larger (or smaller) values, similar performance for equivalent values, and worse performance for smaller (or larger) values. Although not often accentuated, the FOM philosophy intrinsically permeates the field of engineering and enables quantitative benchmark and comparison of complex systems [82]. These metrics provide a common language for engineers to judge a solution's capabilities or the evolution of a technology [22]. Applied to power electronics—a system comprised of many smaller subsystems—it is possible in principal to relate converter-level FOM to constituent devicelevel FOM to constituent material-level FOM [69, 12].

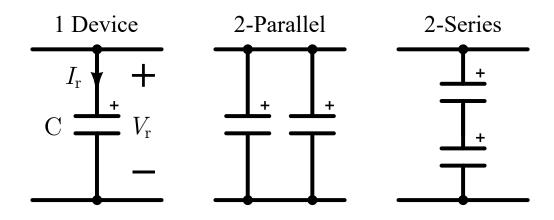

Figure 2.1: Schematic denoting series and parallel bank configurations of a capacitor component.

The 'system scope' in this chapter is a discrete passive component. Others have motivated specific FOM for quantifying the performance of individual electronic devices: capacitors [136], inductors [68], and transistors [94, 12], with the intention of characterizing component application to larger circuits, however, no work has generalized a method for conceiving useful device FOM.

To accomplish this, consider how these devices are utilized. Two-terminal passive devices are commonly configured into series and/or parallel connected component banks to meet specified requirements often relating to energy storage or power throughput. Series-parallel modularity is even common for electrical systems such as power conversion circuits [82, 80] and photovoltaic (PV) panels [61, 19]. Consequently, any metric defined as a FOM in this thesis critically adheres to the following proposed property:

**Property of Series-Parallel Modular Invariance:** A device metric invariant to series and/or parallel configuration of the device.

If a metric adheres to this property, then it is a FOM that can fairly compare devices of various voltage and current ratings and is deemed 'robust'.

The series-parallel modular invariance property is demonstrated schematically in Fig. 2.1 and generalized in Table 2.1 for a series and parallel configuration of a capacitor with specified capacitance C, rated dc voltage  $V_{\rm r}$ , rated rms current  $I_{\rm r}$ , equivalent series resistance ESR, box volume, cost, and mass. In this context, combinations of these base attributes yield some robust FOM which satisfy this property and are agnostic to both series and parallel component configurations—e.g., volumetric energy density  $\gamma_{\rm v}$ , gravimetric power density  $\rho_{\rm m}$ , and loss tangent tan  $\delta$  (or dissipation factor DF).

| Total Specification                                             | 1<br>Device     | 2-<br>Parallel    | 2-Series          | <i>n</i> -Series/<br><i>m</i> -Parallel |

|-----------------------------------------------------------------|-----------------|-------------------|-------------------|-----------------------------------------|

| $C_{ m tot}$                                                    | C               | 2C                | $\frac{1}{2}C$    | $\frac{m}{n}C$                          |

| $V_{ m r,tot}$                                                  | $V_{ m r}$      | $V_{ m r}$        | $2V_{\rm r}$      | $nV_{ m r}$                             |

| $I_{ m r,tot}$                                                  | $I_{ m r}$      | $2I_{\rm r}$      | $I_{ m r}$        | $mI_{ m r}$                             |

| $\mathrm{ESR}_{\mathrm{tot}}$                                   | ESR             | $\frac{1}{2}$ ESR | $2\mathrm{ESR}$   | $\frac{n}{m}$ ESR                       |

| $\operatorname{Vol}_{\operatorname{tot}}$                       | Vol             | $2  \mathrm{Vol}$ | $2  \mathrm{Vol}$ | $nm\mathrm{Vol}$                        |

| $\mathrm{Mass}_{\mathrm{tot}}$                                  | Mass            | 2 Mass            | $2\mathrm{Mass}$  | nm Mass                                 |

| $\operatorname{Cost}_{\operatorname{tot}}$                      | Cost            | $2\mathrm{Cost}$  | $2\mathrm{Cost}$  | $nm \operatorname{Cost}$                |

| $E_{\rm r,tot} = \frac{1}{2}CV_{\rm r}^2$                       | $E_{\rm r}$     | $2E_{\rm r}$      | $2E_{\rm r}$      | $nmE_{\rm r}$                           |

| $P_{\rm r,tot} = V_{\rm r} I_{\rm r}$                           | $P_{\rm r}$     | $2P_{\rm r}$      | $2P_{\rm r}$      | $nmP_{\rm r}$                           |

| $\gamma_{\rm v,tot} = \frac{E_{ m r,tot}}{ m Vol_{tot}}$        | $\gamma_{ m v}$ | $\gamma_{ m v}$   | $\gamma_{ m v}$   | $\gamma_{ m v}$                         |

| $ \rho_{\rm m,tot} = \frac{P_{\rm r,tot}}{{ m Mass}_{ m tot}} $ | $ ho_{ m m}$    | $ ho_{ m m}$      | $ ho_{ m m}$      | $ ho_{ m m}$                            |

| $(\tan \delta)_{\rm tot} = \omega C  {\rm ESR}$                 | $	an \delta$    | $	an \delta$      | $	an \delta$      | $	an \delta$                            |

Table 2.1: Generic capacitor bank specifications and constructed figures-of-merit

# Examples of Robust FOM

Conventional capacitor FOM satisfying the series-parallel modular invariance property include charge-discharge efficiency  $\frac{E_{\text{discharge}}}{E_{\text{charge}}}$  [150, 182, 92]; loss tangent or dissipation factor tan  $\delta$ or quality factor  $Q = \frac{1}{\tan \delta}$  [150, 52, 15]; dielectric loss density  $\frac{P_{\text{loss}}}{\text{Vol}}$  [111]; the Ohms-Farad product  $C \cdot \text{ESR}$  [150, 136]; packaging efficiency, the proportion of active volume within the device to total device volume [136, 65]; energy density of the dielectric material [182, 86, 34, 35]; energy density of the whole capacitor  $\frac{E_r}{\text{Vol}}$ ,  $\frac{E_r}{\text{Mass}}$ , or  $\frac{E_r}{\text{Cost}}$  [102, 130, 77, 182, 85, 37, 15, 92, 151, 45, 155, 52]; power density  $\frac{P_r}{\text{Vol}}$  or  $\frac{P_r}{\text{Mass}}$  [77, 24]; volumetric mass density or specific volume  $\frac{\text{Mass}}{\text{Vol}}$  [203, 22]; and lifetime  $L_0$  [10, 180].

Conventional inductor FOM satisfying the series-parallel modular invariance property includes the ac quality factor  $Q_{\rm ac}$  [67, 72, 78, 98, 193, 18, 159]; relative dissipation factor or relative loss factor  $\frac{\tan \delta}{\mu_{\rm r}}$  [72, 55]; the volumetric core (eddy current or hysteresis) loss  $\frac{P_{\rm loss}}{\rm Vol}$  [68, 78]; and the specific loss density  $\frac{P_{\rm loss}}{M_{\rm ass}}$  [146].

These capacitor and inductor FOM are suitable candidates for component comparison

across the entire device subspace. Future research explorations of these metrics could consider trade-offs and derive connections to the devices' broader system application [24].

# Limited or Operating Condition Specific Capacitor Metrics

Some common-use device metrics, especially for capacitors, are only parallel modular and thus partially satisfy the series-parallel modular invariance property. These metrics can be utilized for device comparison, but require a more restrictive and judicious context, most commonly by only comparing capacitors of a specific rated voltage  $V_r$ . Some examples include current density  $\frac{I_r}{\text{Vol}}$  and  $\frac{I_r}{\text{Mass}}$  [150, 38]; capacitance-related current density  $\frac{C}{I_r}$  [38]; volumetric efficiency or charge density  $\frac{C \cdot V_r}{\text{Vol}}$  [150]; capacitance density, volumetric capacitance, or capacitance volumetric efficiency  $\frac{C}{\text{Vol}}$  [125, 119, 84, 10, 37]; capacitance voltage product per rated current  $\frac{C \cdot V_r}{I_r}$  [150]; cost per farad  $\frac{\text{Cost}}{C}$  [151]; and specific capacitance  $\frac{C \cdot V_r}{\text{Mass}}$  [65, 136, 22].

# Limitations of Series-Parallel Device Configurations

Arbitrarily configuring discrete components in series and in parallel has associated practical limitations: increased layout inductance, asymmetrical current distribution, unbalanced voltage distributions, and lower packing factor [37, 59, 3]. For the purposes of this FOM analysis, these shortcomings—which can be mitigated with conscientious design—are neglected.

# 2.3 Commercial Capacitor and Inductor Data

Desired device FOM are constructed from base metrics, and thus the greater acquisition of base metrics directly enables the determination of more FOM. This section describes the availability and extent of the surveyed data for discrete commercial passive components. It also delineates the capacitor and inductor typologies used throughout this thesis.

# Extent of Available Data – Capacitors

The present distributor data sets contain certain practicable information with varying degrees of consistency: (near) fully available, partially available, or not available. Satiating a partially or unavailable component attribute can enable the determination of secondary metrics (e.g., rated stored energy  $E_r$  and volume) and tertiary FOM (e.g., energy and power density). As discussed in Section 2.2, this requires either supplemental measured data with extrapolation, or theoretic generalization of the component derived from material properties.

The comprehensive data set consists of an aggregation of roughly 606,000 distinct capacitors from the prominent distributor Digikey Electronics.

#### Fully Available Data

Readily available data includes several primary attributes: capacitor rated voltage  $V_r$ ; the zero-voltage differential capacitance C(0) [110]; the dimensional parameters: length, width, height, diameter; and the cost per unit. The secondary attribute 'box' or enclosure volume is computed from the dimensional attributes. For linear capacitors, the secondary attribute of rated stored energy  $E_r$  is calculable in aggregate from these base attributes. However, the prominent Class II ceramic capacitor technology has a nonlinear voltage-dependent capacitance characteristic [110], and thus  $E_r$  cannot be calculated for all capacitor technologies without additional analysis presented in Section 2.4.

#### Partially Available Data

The equivalent series resistance (ESR); loss tangent or dissipation factor  $\tan \delta = DF$ ; rated rms current  $I_r$ ; and lifetime  $L_0$  are all critical attributes for any quantitative performance analysis of capacitor loss and reliability, however, these metrics are unavailable in the overall distributor data set for most capacitor technologies except for some aluminum electrolytic capacitors. Some of these base attributes also maintain a pertinent frequency and temperature dependence, and are inconsistently standardized across manufacturers. Thus even though correction factors are sometimes disclosed, the oftentimes singular values for ESR,  $\tan \delta$ ,  $I_r$ , and  $L_0$  common to catalogs and datasheets are often inadequate for involved electronics design.

To generalize and predict losses, some have collected sampled measurements for realistic, large-signal operating conditions and abstracted broad capacitor trends as a function of frequency, dc voltage bias, and temperature [42]. Others propose an empirical loss equation for capacitors [110, 75, 111], being the dual of the venerable Steinmetz equation for inductors [163, 179]. These models depend on the capacitor's excitation waveforms, and could directly integrate with a comprehensive component data set to generalize loss, however, this requires more extensive data sampling and more study.

#### Unavailable Data

Some primary attributes are essentially unavailable in the distributor data set. For instance, the component mass would be invaluable for quantitative evaluation of weight-optimized power conversion systems, however, presently this information is digitally available for only a select few suppliers. To reconcile the deficiency in mass data, Section 2.5 applies sampled measured data to estimate the mass of all capacitor components as a function of its type, rated voltage  $V_{\rm r}$ , and capacitance C.

# Summary – Capacitors

Commercially viable capacitors are constructed in a variety of technologies best suited for particular electrical applications [150, 152]. Technologies are most easily distinguished by

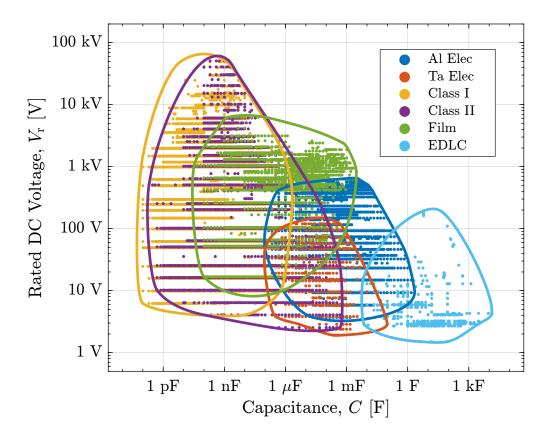

Figure 2.2: Survey of component rated capacitance C versus rated dc voltage  $V_{\rm r}$  across all capacitor technologies including aluminum electrolytic, tantalum electrolytic, Class 1 ceramic, Class II ceramic, film, and electrolytic double-layer capacitors (EDLC).

the dielectric material where certain capacitor types excel in cost, reliability, high-frequency capability, voltage and current ratings, mass, and volume. In this thesis, the capacitors in the comprehensive data set are classified into subsets with distinct elements. Fig. 2.2 illustrates, for the surveyed data, a conventional differentiator between capacitor technologies: the range of possible capacitance C and rated dc voltage  $V_{\rm r}$ .

# Aluminum Electrolytic Capacitor

This capacitor technology is voltage unipolar and known for its relatively low cost and weight; and often comes in a can-style package. Relative to other capacitor technologies, aluminum electrolytic capacitors tend to have high values of ESR correlating to the lowest temperature limits of around 85 °C, low current ratings, and shorter lifetime. Aluminum electrolytic capacitors are made in three distinct varieties: 1) the most common liquid (or wet) electrolyte, 2) a solid polymer electrolyte, and 3) a hybrid liquid-solid electrolyte [22].

# Tantalum Electrolytic Capacitor

A type of unipolar capacitor rated for lower voltages than aluminum electrolytic capacitors. The rated voltage also derates up to 50% at the maximum rated temperature [65]. Tantalum capacitors are relatively costly yet suitable for high-reliability applications. They are produced in either a 'wet' or solid polymer electrolyte variety.

# **Ceramic Capacitor**

The most prolific capacitor technology in production, having the highest dielectric permittivities and utilized in a broad range of applications [125]. They are bipolar and come in different 'classes' dictated by standards [32]. Class I capacitors are distinctly highly stable with voltage and temperature and are suitable for resonance applications. Class II capacitors have ferroelectric dielectric materials—typically barium titanate dielectric (BaTiO<sub>3</sub>)—and are more unstable, having a nonlinear capacitance with respect to applied voltage, operating temperature, and degradation with aging, but have the highest capacitance per volume [10, 192]. Class III capacitors are similar to Class II capacitors but have even greater voltage-temperature instability. Colloquially, Class II and Class III capacitors are often both classified as Class II type ceramic capacitors; this chapter employs the same grouping. Although not considered in this chapter, in recent years ceramic capacitors with antiferroelectric dielectric material—namely lead lanthanum zirconate titanate (PLZT)—are becoming increasingly economical and have competitive performance relative to other capacitor types [31, 35, 37]. As Class I and Class II ceramic capacitors differ greatly in performance, they are always explicitly differentiated within this chapter.

# Film Capacitor

These capacitors typically have a plastic or polymer dielectric material, the most common being polypropylene (PP) or polyethylene terephthalate (PET), a type of polyester [45]. They are also constructed in metallized and non-metallized variants where the former dominates production and has smaller size, lower costs, and self-healing properties [3]. Compared to other capacitor types, film capacitors are bipolar and generally have large volumes, yet are lightweight and very stable. This chapter classifies all film capacitors into one grouping.

# Electrolytic Double-Layer Capacitor (EDLC)

EDLC capacitors, supercapacitors, or ultracapacitors are a unique capacitor technology suited for high-capacity energy storage and applications where batteries would be inconvenient, such as pulsed power. They come in the largest capacitance denominations and are rated for less than 5 V at the device-level [81, 118, 53, 9]. The data set includes EDLC capacitors configured into large series-parallel banks and sold as a single discrete unit.

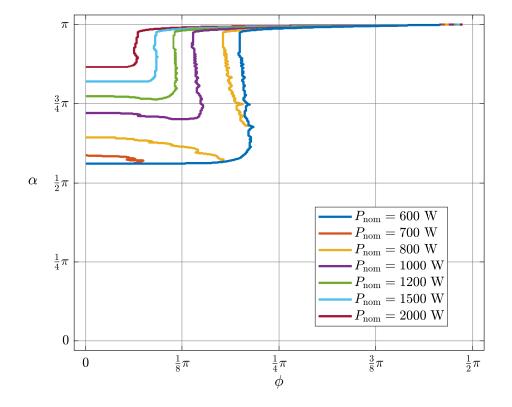

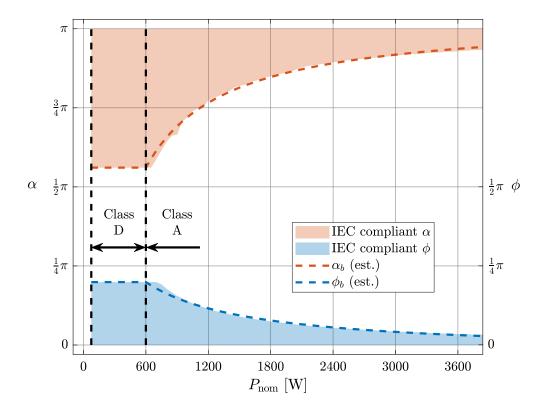

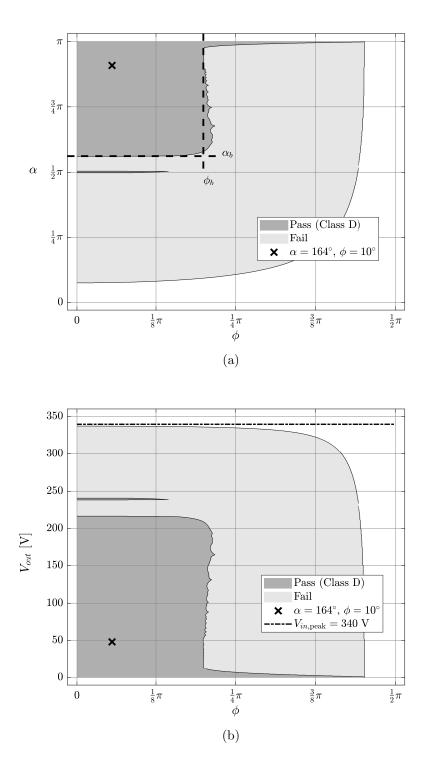

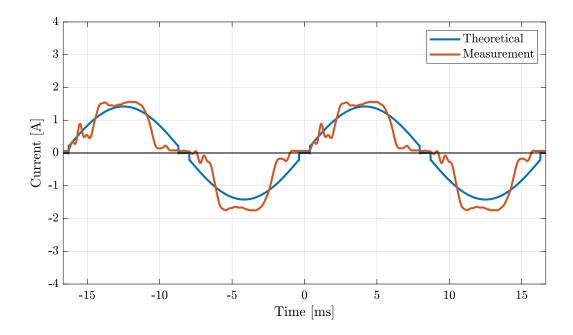

### Other Capacitor Technologies