# UC Berkeley

**Research Reports**

# Title

Vehicle-based Control Computer Systems

**Permalink** https://escholarship.org/uc/item/0wh7c8jv

Author Auslander, David M

Publication Date

This paper has been mechanically scanned. Some errors may have been inadvertently introduced.

# **Vehicle-Based Control Computer Systems**

David M. Auslander

# University of California, Berkeley

California PATH Research Report UCB-ITS-PRR-95-3

This work was performed as part of the California PATH Program of the University of California, in cooperation with the State of California Business, Transportation, and Housing Agency, Department of Transportation; and the United States Department of Transportation, Federal Highway Administration.

The contents of this report reflect the views of the authors who are responsible for the facts and the accuracy of the data presented herein. The contents do not necessarily reflect the official views or policies of the State of California. This report does not constitute a standard, specification, or regulation.

January 1995 ISSN 1055-1425

# Vehicle-Based Control Computer Systems

Final Report - September 1, 1994 PATH Project MOU-61

David M. Auslander Mechanical Engineering Department University of California Berkeley, CA 94720 510-642-4930(office), 510-643-5599(fax) email: dma@euler.berkeley.edu

# Abstract

This report is in two parts: the first part (starting at Section 1) describes a design and implementation methodology for real time software suitable for control of mechanical systems such as vehicles. This method provides for a design description of the system, a means of capturing the system structure in such a way as to modularize the software writing job, and a portable implementation method. The second part (starting at Section 13) is concerned with a particular problem in mechanical system control: estimating velocity when the event rate from a digital encoder is lower than the controller's sample time. Methods are explored for performing this estimation that achieve best accuracy overall, but can also avoid the problem of spurious estimates when the velocity reverses.

# **Table of Contents**

| 1 Part I: Design and Implementation of Real Time Software for Mechanical Control                                                                                                                                                                                                                                                        |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 2 Mechanical System Control: Mechatronics                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 3 Real Time Software       .         3.1 Engineering Design / Computational Performance       .6         3.2 Software Portability       .7         3.3 Control System Organization       .8                                                                                                                                             |  |  |  |  |

| 4 State Transition Logic       .8         4.1 States and Transitions       .9         4.2 Transition Logic Diagrams       10         4.3 Block/Non-Block       .10         4.4 State-Related Code       11         4.5 State Scanning: The Execution Cycle       12         4.6 Task Concurrency: Universal Real Time Solution       12 |  |  |  |  |

| 5 Example: Pulse-Width Modulation (PWM) ,                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 6 Transition Logic Design Tool136.1 Task Specification146.2 State and Transition Specification156.3 Task and Common Code156.4 Code Generation156.5 Compile, Edit and Merge166.6 Execution Shell166.7 Documentation                                                                                                                      |  |  |  |  |

| 7 Task Organization       17         7.1 Task-Related Code       17         7.2 Common Code       17         7.3 Task Process Configuration       17         7.4 Intertask Communication       18         7.5 The Master Task       18                                                                                                  |  |  |  |  |

| 8 Multitasking Performance: The Real World       1         8.1 Priority-Based Scheduling - Resource Shifting       1         8.2 Continuous/Intermittent Tasks       1         8.3 Cooperative Multitasking Modes       2         8.4 Preemptive Multitasking Modes       2                                                             |  |  |  |  |

| <ul><li>8.5 Task Types</li><li>8.6 Supported Environments</li></ul>                                                                                                                                                                                                                                                                                                                                                           | 2 2<br>. 23                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| <ul> <li>9 Inter-task Communication</li> <li>9.1 Data Integrity</li> <li>9.2 Communication Across Processes</li> <li>9.3 Communication Media</li> <li>9.4 Communication Structures</li> </ul>                                                                                                                                                                                                                                 | . 26                                         |

| <ul> <li>10 Example: Stepping Motor Control</li> <li>10.1 Tasks</li> <li>10.2 Documentation</li> <li>10.3 Sample of Code for "Position" Task, Move State</li> <li>10.4 Operating Information</li> </ul>                                                                                                                                                                                                                       | 2 0<br>2 7<br>29<br>. <b>30</b>              |

| 11 Real Time Performance         11.1 Sample Problem for Performance Evaluation         11.2 Counting Task Functions         11.3 Model of a Simple Control Job         11.4 Simulation Mode         11.5 Audit Trace File         11.6 Counting: Performance in Several Environments                                                                                                                                         | . 31<br>. 31<br>. 32<br>. 33<br>. 33<br>. 34 |

| 12 References                                                                                                                                                                                                                                                                                                                                                                                                                 | 37                                           |

| 13 Part II: Velocity Measurement From Widely Spaced Encoder Pulses      13.1 Problem Formulation                                                                                                                                                                                                                                                                                                                              | 38<br>. 38                                   |

| 14 Current Technology14.1 Lines per Period Estimator14.2 Reciprocal Time Estimator14.3 Taylor Series Expansion14.4 Backward Difference Expansion14.5 Least Squares Estimator14.6 Observer Based Estimator                                                                                                                                                                                                                     | . 39<br>. 40<br>41<br>. 41                   |

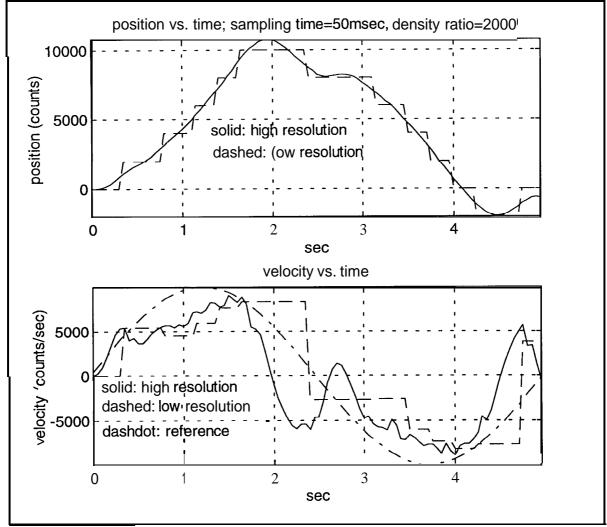

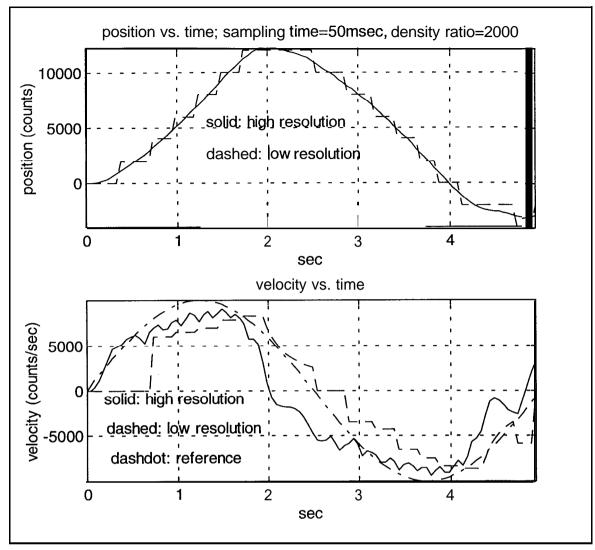

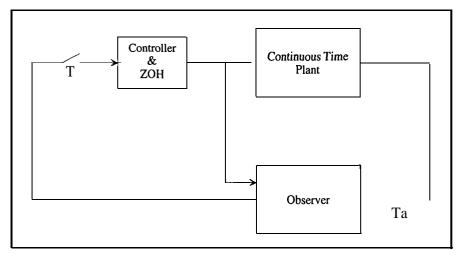

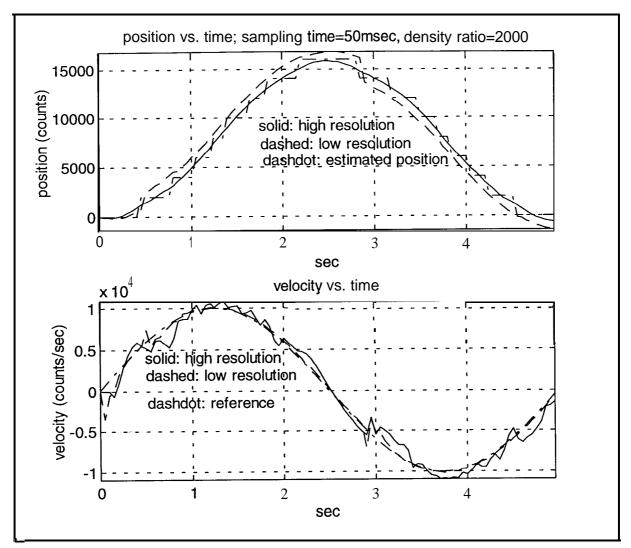

| <ul> <li>15 New Research Areas</li> <li>15.1 Slowly Moving Systems</li> <li>15.2 Transition Logic based Switching Algorithm</li> <li>15.3 Experimental Results: Motor-Mass System</li> <li>15.4 Time delayed averaging method</li> <li>15.5 Asynchronous Multirate Observer Based Estimator</li> <li>15.6 Modified Luenberger Observer with Output Estimator</li> <li>15.7 Experimental Results: Motor-Mass System</li> </ul> | 44<br>46<br>48<br>49<br>50                   |

| 16 Conclusions and Future Work | . 54 |

|--------------------------------|------|

| 17 References                  | . 54 |

# 1 Part I: Design and Implementation of Real Time Software for Mechanical Control

Use of an explicit, formalized design layer is critical to the development of reliable real time software. This section describes such a method, which is a candidate design method for systems of modest complexity. The context for the use of the method is described first, then its structure is described, the associated software, and examples.

# 2 Mechanical System Control: Mechatronics

Mechanical system control is undergoing a revolution in which the primary determinant of system function is becoming the control software. This revolution is enabled by developments occurring in electronic and computer technology. The developments in electronics have made it possible to energetically isolate the four components making up a controlled mechanical system:

- The target system

- Measurement

- Computation

- Actuation

Once isolated from the instruments on one side and the actuators on the other, computation could be implemented using the most effective computing medium, independent of any needs to pass power through the computational element. That medium has been the digital computer, and the medium of expression for digital computers is software.

This ability to isolate is recent. Watt's famous speed governor, for example, combined the instrument, computation and actuation into the **flyball** element. Its computational capability was severely limited by the necessity that it pass power from the power shaft back to the steam valve. Other such examples, where computation is tied to measurement and/or actuation, include automotive carburetors, mastered cam grinders, tracer lathes, DC motor commutation, timing belts used in a variety of machines to coordinate motions, rapid transit car couplings (which are only present to maintain distance; cars are individually powered), and myriads of machines that use linkages, gears, cams, etc., to produce desired motions. Many such systems are being redesigned with software based controllers to maintain these relationships, with associated improvements in performance, productivity (due to much shorter times needed to change products), and reliability.

The term *mechatronics*, attributed to Yasakawa Electric in the early **1970s**, was coined to describe the new kind of mechanical system that could be created when electronics took on the decision-making function formerly performed by mechanical components. The phenomenal improvement in cost/performance of computers since that time has led to a shift from electronics to software as the primary decision-making medium. With that in mind, and with the understanding that decision-making media are likely to change again, the following definition broadens the concept of mechatronics while keeping the original spirit of the term:

# The application of complex decision-making to the operation of physical systems.

With this context, the compucentric nature of modern mechanical system design becomes clearer. Computational **capbilities** and limitations must be considered at all stages of the design and implementation process. In particular, the effectiveness of the final production system will depend very heavily on the quality of the real time software that controls the machine.

### **3 Real Time Software**

Real time software differs from conventional software in that its results must not only be numerically and logically correct, they must also be delivered at the correct time. A design corollary following from this definition, is that real time software must embody the concept of **duration**, which, again, is not part of conventional software. The real time software used in most mechanical system control is also **safety-critical**. Software malfunction can result in serious injury and/or significant property damage, In discussing software-related accidents which resulted in deaths and serious injuries from clinical use of a radiation therapy machine (Therac-25), Leveson and Turner (1993) established a set of software design principles, "...that apparently were violated with the Therac-25...." Those are:

- Documentation should not be an afterthought.

- Software quality assurance practices and standards should be established.

- Designs should be kept simple.

- Ways to get information about errors -- for example, software audit trails -- should be designed into the software from the beginning.

- The software should be subjected to extensive testing and formal analysis at the module and software level; system testing alone is not adequate.

In particular, it was determined that a number of these problems were associated with **asynchronous** operations, which while uncommon in conventional software, are the heart and soul of real time software. Asynchronous operations arise from preemptive, prioritized execution of software modules, and from the interaction of the software with the physical system under control.

Because of preemptive execution, it becomes impossible to predict when groups of program statements will execute relative to other groups, as it is in synchronous software. Errors that depend on particular execution order will only show up on a statistical basis, not predictably. Thus, the technique of repeating execution until the source of an error is found, which is so effective for synchronous (conventional) software, will not work with for this class of real time error.

In a like manner, there are errors that depend on the coincidence of certain sections of program code and events taking place in the physical system. Again, because these systems are not strictly synchronized, they can only have statistical characterization.

# 3.1 Engineering Design / Computational Performance

Too often, the only detailed documentation of real time software is the program itself. Furthermore, the program is usually designed and written for a specific real time target environment. The unfortunate consequence of this is that the engineering aspects of the design problem become inextricably intertwined with the computation aspects. This situation relates directly to the first design principle listed above, "documentation should not be an afterthought." If the system

engineering is separated from the computational technology, then the documentation will have to exist independent of the program; otherwise, documentation can be viewed as an additional burden.

The following definitions will be used to separate these roles as they appear in the proposed methodology:

System engineering: Detailed specification of the relationship between the control software and the mechanical system.

Computational technology: A combination of computational hardware and system software that enables application software based on the engineering specification to meet its operational specifications.

Using these definitions, the engineering specification describes **how** the system works; the computational specification determines its *performance*. As a result of this separation, if a suitable paradigm is adopted to describe the engineering specification, a much broader discussion and examination can be brought to bear because, the **details** of the engineering can be discussed by project participants familiar with the problem, not just those familiar with computing languages and real time programming conventions. This provides for meaningful design review of projects that are software intensive.

# 3.2 Software Portability

In mechanical system control, portability has consequences both for product lifetime and for the design/development cycle. The mechanical part of the system can have a commercial lifetime of anywhere from 5 to 20 years. On the other hand, the computational technology used for its control only has a lifetime of 3 to 5 years. To remain competitive, new versions of the product need to use new computers to take advantage of the ever-increasing computational capability. Doing this cost effectively requires software that will "port" easily from the original target processor to new ones.

Software portability seriously affects the design/implementation cycle as well. Early stages of the software tend to be simulations, done to test hypotheses and to substitute for hardware not yet built. Later stages use laboratory prototypes, then pilot prototypes, then, finally, the actual production system. If software can't migrate from step-to-step in this process, the whole process can become greatly elongated as new software must be created for each step, and there are significant possibilities for introducing new bugs at each stage.

Portability is complicated by the real time constraints. If real time software environments are used as aids in meeting those constraints (kernels, schedulers, real time operating systems), software written for one environment can require substantial rewriting to run in another. Crossing the full spectrum from simulation to production traverses environments in which program structure itself is incompatible. The proposed methodology provides a layer of abstraction one higher than the real time environments, so offers a means of bypassing these incompatibility problems. Further portability challenges arise from the operator interface section of the program, and the interprogram communication for those solutions implemented with multiple processors. These subjects will be discussed briefly here, but remain in need of substantial further work.

#### 3.3 Control System Organization

A two-level organization is used on both the engineering and computational sides of the control software design. On the engineering side, a job is organized into *tusks* and *states*, and, on the computational side, into processes and *threads*.

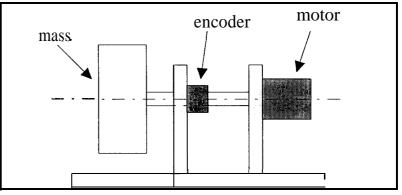

The breakdown of the engineering specification into tasks and then states is a subjective process, requiring considerable engineering judgement. This stage is the primary creative design step. Tasks represent **units** of **work**, and, roughly speaking, can be viewed as cells in a matrix that breaks the control system down along a time-scale dimension and a physical component dimension. For example, along a column representing a motor-driven axis, there could be separate tasks to handle a high speed input (such as an incremental encoder), an actuation output, a servo control, and, perhaps, a motion profiler. Still higher in that column, there could be a coalescence as tasks handled coordinated motion of several axes.

Tasks, in general, are active simultaneously. They are used to describe the parallelism inherent in the physical system. Internally, however, tasks are organized in a strictly sequential manner into states. States describe specific activities within the task; only one state can be active at a time. The primary reason for this distinction between the nature of tasks and states is that sequential activity is a part of many mechanical systems. Even for systems that do not seem to be fundamentally sequential, such as process or web systems, the sequential breakdown within tasks seems to work quite well. During normal operation, tasks tend to stay in only one or two states. However, during startup and shutdown, the task/state structure describes the operation very well. The sequential state structure also serves as one test for appropriate task definition. If tasks are aggregated to much, they will end up with parallel operations which cannot be described effectively by states. Breaking the task into several smaller tasks solves the problem.

On the computational side, *processes* describe computational entities that do not share an address space (this includes independent processors). *Threads,* are computational entities that share an address space but can execute asynchronously. A thread can contain one or more tasks; a process can contain one or more threads.

The organization into processes and threads is purely for performance purposes. As is noted below, there is no theoretical necessity for such organization at all. The organization serves only to meet performance specifications when the chosen processor is not sufficiently fast to meet the specs with a single-thread structure. It does this by shifting processor resources from low priority to high priority tasks. As a further note, the portability requirements enumerated above imply that several different computational organizations will be used in the course of a development project.

## **4** State Transition Logic

The task organizational structured described in this paper is an adaptation of state transition logic (Auslander, 1993a). This adaptation provides for implementation of the structural principles enumerated above. Documentation development is integrated with the software specification procedure, the software produced is inherently modular, and audit trail information can be produced automatically. By extending the transition logic paradigm to cover the entire realm of real time requirements (Auslander, 1993b), two important results are achieved:

1) The discipline associated with following a formal design paradigm is extended to the "low level" as well as high level software tasks.

2) It becomes possible to produce portable code, that is, code which can be generated and compiled to run in a number of different real time environments without changing the user-written portion of the code.

State transition logic is formally defined within finite automata theory (Kohavi, 1970). As used in the design of synchronous sequential circuits, it becomes a formal, mathematical statement of system operation from which direct design of circuits can be done (Sandige, 1990, or any basic text on logic design). When used as a software specification tool, state transition logic takes on a more subjective cast; the transition logic specifies overall structure, but specific code must be written by the user (Domfeld et al, 1980, Bastieans and Van Campenhout, 1993).

The state transition logic concept has been further specialized to mechanical system control through the specification of a functional structure for each state. This structure specifies the organization of code at the state level so that it corresponds closely with the needs of control systems.

The use of transition logic has also been based on the very successful applications of programmable logic controllers (PLCs). These devices, in their simplest form, implement Boolean logic equations, which are scanned continuously. The programming is done using ladder logic, a form of writing Boolean equations that mimics relay implementation of logic. In basing real time software design on transition logic, each state takes on the role of a PLC, greatly extending the scope of problems that can be tackled with the PLC paradigm.

Depending on the nature of the problem being solved, other formulations have been proposed. For example, the language SIGNAL (Le Guemic et al, 1986) was invented for problems which have signal processing as a core activity. Benveniste and Le Guemic (1990) generalize the usage to hybrid dynamical systems.

# 4.1 States and Transitions

**State** specifies the particular aspect of its activity that a task is engaged in at any moment. It is the aspect of the design formalism that expresses **duration**. States are strictly sequential; each task is **in** one state at a time. Typical activities associated with states are:

Moving - a cutting tool moving to position to start a cut, a carriage bringing a part into place, a vehicle holding a velocity.

- Waiting for a switch closure, for a process variable to cross a threshold, for an operator action, for a specified time.

- Processing thermal or chemical processes, material coating in webs.

- Computing where to go, how long to wait, results of a complex measurement.

- Measuring size of a part, location of a registration mark, object features from vision input, proximity.

Each state must be associated with a well-defined activity. When that activity ends, a **transition** to a new activity takes place. There can be any number of transitions to or from a state. Each transition is associated with a specific condition. For example, the condition for leaving a **moving** state could be that the end of the motion was reached, that a measurement indicated that further motion was not necessary, that an exception condition such as stall or excessively large motion error occurred, etc.

#### 4.2 Transition Logic Diagrams

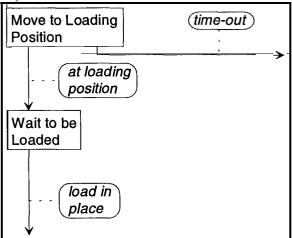

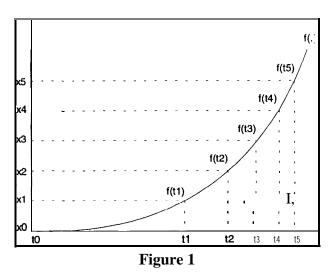

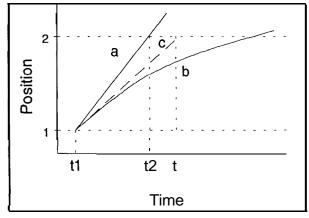

State transition logic can be represented in diagrammatic form. Conventionally, states have been shown with circles, and transitions with curved arrows from one state to another. Each transition is **labelled** with the conditions that specify that transition. This format is inconvenient for **computer**-based graphics, so a modified form, shown in **Figure 1**, is used.

This diagram shows a fragment of the transition logic for a task that controls the movement of a materials handling vehicle. The vehicle moves from one position to another, picking up parts in one position and dropping them off at another. The states are shown with rectangles; a description of the state is given inside the rectangle. The transitions are shown with arrows and the transition conditions are shown inside rounded rectangles. The dashed lines provide an unambiguous indication of which transition the condition is attached to. The **first** "move-to" state shows a typical normal transition as well as an error transition, in this case based on a time-out Diagram

**Figure 1.** Fragment of a Transition Logic Diagram

Although these diagrams are not essential in using transition logic, they are an excellent visualization tool. If a task is compact enough to fit a logic diagram on a single page, the graphical description makes its function much easier to grasp.

#### 4.3 Block/Non-Block

A major feature of PLCs contributing to their success as control components has been that the logic function is continually scanned. The programmer does not deal with program flow control, as must be done when using conventional programming languages. As long as the ladder is active, it is scanned repeatedly, so the user only has to be concerned with the fundamental performance issue of whether the scan rate is adequate for the particular control application.

Transition logic design is based on this same scanning principle for execution of state-related code. In order to achieve greater functional flexibility than is possible with ladder diagrams, however, standard sequential languages are used for coding. To implement a scanning structure with algorithmic languages requires the restriction that only **non-blocking** code can be used. Non-blocking code is a section of program that has predictable execution time; execution time for blocking code cannot be predicted. Examples of blocking code in the C language include, for example, the *scanf()* function call used to get keyboard input from the user. **Scanf** only returns when the requested input values have been typed; if the user goes out for coffee, the function simply waits. Likewise, the commonly used construction to wait for an external event such as a switch closure,

#### while(inbit(bitno) == 0);

is also blocking. If the event never happens, the while loop remains hung.

The restriction to non-blocking code, however, does not cause any loss of generality. Quite the contrary, the transition logic structure is capable of encoding any kind of desired waiting situations, as shown in the example given above. By encoding the "wait" at the transition logic level rather than at the code level, system operations are documented in a medium that any engineeer involved in the project can understand without having to understand the intricacies of the program.

#### 4.4 State-Related Code

The transition logic metaphor encourages the use of modular software by associating most of the user-written code with states. In addition, a formal structure of functions is established for this **state**-related code. Two goals of modular code writing are thus fulfilled:

- a) Sections of code are directly connected to identifiable mechanical system operations,

- b) Individual functions are kept short and easily understood.

For each state, the following functions are defined:

*Entry function:* Executed once on entry to the state. *Action function:* Executed on every scan of the state.

For each transition from the state, the following pair of functions is defined:

*Test function*: Test the condition for transition; returns TRUE or FALSE. *Exitfunction*: Executed if the associated transition is taken.

This structure enforces programming discipline down to the lowest programming level. All of these functions must be non-blocking, so, **test** functions, for example, never wait for transition conditions. They make the test, then return a logic value. Relating code to design-level documentation is also enforced with this structure. Transition logic documentation for each task identifies states in terms of what the mechanical system is doing. Not only is the code relevant to that state immediately identified as well, the code is further broken into its constituent parts.

#### 4.5 State Scanning: The Execution Cycle

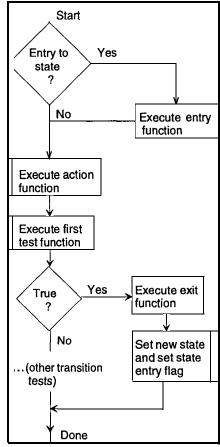

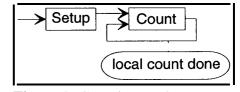

The state scan is shown in **Figure 2.** In addition to establishing the execution order for the staterelated functions, it also provides the basis for parallel operation <u>of tasks</u>.

Each pass through the cycle executes one scan for one task. If this is the first time the scan has been executed for the current state, the **entry** function is executed. The **action** function is always executed. Then, the first **transition test** function is executed. If it returns TRUE to indicate that the transition should be taken, the associated **exit** function is executed and a new state is established for the next scan. Otherwise, subsequent **test** functions are executed in a similar manner. The first **test** function returning TRUE terminates the sequence. Thus, if more than one transition became TRUE at the same time, the one associated with the earliest **test** function would be recognized.

Behind the execution details, there must be a data base of task information. Each task must have a data table specifying its structural information, that is, all of the states and transitions, task parameters such as priority, sample time, etc., and the transient information such as present state and status.

#### 4.6 Task Concurrency: Universal Real Time Solution

Tasks, as noted above, must operate concurrently. This structure provides for parallel operation of tasks, even in the absence of any specific multitasking operating system or scheduler. Because all of the state functions are non-blocking, the scan cycle itself is non-blocking. It can, therefore, be used to scan

each active task in succession. After finishing with all of the tasks, the first task is scanned again. This guarantees fully parallel operation of all tasks. This method of scheduling, **cooperative multitasking**, will be an adequate solution if the total scan time for all tasks is short enough to meet the system timing constraints. If not, a faster computer must be used, or other scheduling solutions must be found. These will be discussed below.

The methodology discussed thus far therefore presents a universal real time solution. It is capable of solving all real time problems, without any special real time constructs or operating systems, *if*

Figure 2. State Scan Cycle

*a fast enough computer is available.* All of the usual real time facilities, semaphores, task synchronization, event-based scheduling, etc., can all be implemented using the formalism of transition logic, with all code non-blocking. If a fast enough computer is not practical, use of preemptive scheduling based on interrupts can be implemented. To do this, the transition logic paradigm must be extended to include designation of task-type, and library code must be included to allow integration of transition logic based code with a variety of real time and/or multiprocessor environments.

#### 5 Example: Pulse-Width Modulation (PWM)

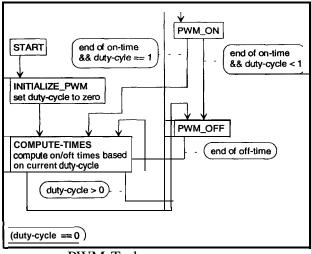

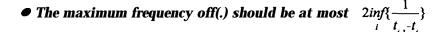

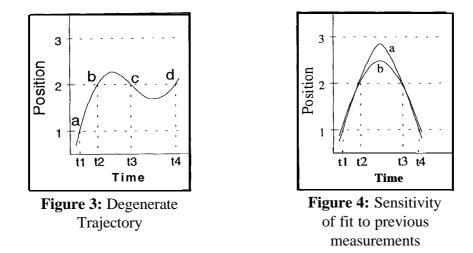

Pulse-width modulation is widely used as an actuation function where there is need for a digital output to the actuating device, but continuous variation in the actuator output is desired. Anytime the actuator plus arget system constitute a low-pass filter, PWM can perform the function of a digital-to-analog converter by exploiting the termporal properties of the low-pass filtering. The PWM signal is usually a retangular-wave of fixed frequency, with variable duty-cycle (i.e., ratio of on-time to cycle time). The logic diagram in **Figure** 3 shows a task to implement PWM.

The task has four states, as shown, and will produce an effective low frequency PWM from software. The maximum frequency depends on the means of measuring time that is utilized, and the timing latencies encountered in running the task. It would be suitable for actuation of a heater or, perhaps, a large motor, but would be too slow for a modest sized motor.

The two main tasks, PWM\_ON and PWM\_OFF, turn the output on (or off) on entry, and then just wait for the end of the specified time interval. COMPUTE-TIMES is active once per cycle to find the appropriate on and Off times in the event that the duty cycle has been changed. The transition conditions take account

of the two special cases -- duty cycles of 0 (never on) and 1 (always on) in addition to normal operation.

This example shows the use of transition logic for a task that is quite low level computationally. Unlike a conventional implementation of such a task, however, the details are readily apparent from the transition logic and reference to the code (not shown here) need only be made to confirm that it accurately translates the transition logic.

#### 6 Transition Logic Design Tool

Manual programming of systems based on transition logic is possible, that is, programming from a transition **logic** diagram or tabular description with no software development tools other than a compiler, editor and linker. There are two major disadvantages to this, however. First, it can be very

tedious because of the large numbers of functions that must be created (and named) and the data tables that must be made to do the bookkeeping the scan execution cycle needs. Second, there is always the temptation, particularly when one is in a hurry, to make changes directly in the program without updating the transition logic. This latter is especially pernicious because it leads to documentation that misrepresents system operation.

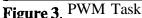

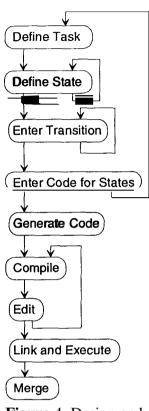

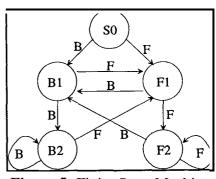

The design tool described here aids in the full program production by keeping track of tasks and transition logic, organizing the writing of state-related code, and generating C files that can be compiled to operate in a variety of environments, including multi-processor systems. It also produces system documentation, with the transition logic listed in tabular rather than graphical format. A schematic of the design and implementation cycle using this software tool is shown in **Figure 4.** It currently runs in MS Windows, but is written using the XVT portable library, so, potentially, can be recompiled for most common operating systems.

#### 6.1 Task Specification

The software design tool (referred to as TRANLOG) keeps track of a single project consisting of any number of tasks. Each task is defined by:

Name Description (one line) Task type Priority Initial status Initial status Initial state Data items (if any) Transition logic structure Task-related code

The **tusk type** and **priority** are not necessary for all execution environments, but are included so portability will be maintained. The types of tasks will be defined in the Multitasking section, below. As the program executes, a task can be active, inactive, waiting, or executing. The **initial status** determines whether the task will be active or inactive when the program first starts. Similarly, the **initial state** determines which state will be entered first each time the task is activated (if a task is de-activated, re-activating it is the same as starting it for the first time). The **data items** are related to task type and can specify such infomation as input ports, sample time, etc.

The details of the transition logic structure are described below. The **tusk-refuted code** consists of code items that support the states. These include functions used by several states, variables that are common across the task, defined constants, etc.

There is no formal structure describing the relationships of the tasks. It is programming convention, however, to designate one task as the **muster tusk** to make sure the system is properly (and safely) initialized. In defining the tasks, only the master task has its initial status set to active; all other tasks are initially inactive. The master task can then activate other tasks in an order the guarantees proper

system start-up. The master task is usually responsible for de-activating and re-activating tasks when necessary as the system proceeds through various operating modes.

#### 6.2 State and Transition Specification

Specification of a state requires a name for the state and a short description. Transitions are defined between already defined states, so it is usually easiest to define all of the states in a task before defining the transitions. Other than associated code, neither states nor transitions require any further information.

The code for states and transitions can be entered while defining the transition logic, or can be entered or edited using an external editor (usually the program development environment that is part of the compiler). A merge facility is supplied so that changes made outside of the transition logic development tool can be captured.

#### 6.3 Task and Common Code

In addition to the entry, action, test and exit functions themselves, it is usually necessary to add some code that is common to sections of the system. There are three places to do **this**. the **tusk code** section is for code that is specific to a single task. It is most often used to define **static** variables that are used across many state functions. Because the non-blocking code of transition logic uses functions that return immediately, information that must be retained within or across states must be declared as **static**, which is normally done in the **tusk code** section. Functions that are only used in a single task can also be defined as part of **tusk code**.

Because the control program created is portable, the tasks can execute in many different environments, ranging from cooperative multitasking in which all tasks execute in the same computational thread, to each task on an independent process, connected, for example, through a network. Thus, in general, tasks will not share the same computational address space so a separate definition is required for any code that will be common to more than one task. The **common code** and **common header** sections are provided for this purpose. When the code is linked, the common code and header sections are linked with every computationally independent component. These sections are most commonly used to **define** functions that are needed in more than one task. The function definitions themselves are put in the **common code** section, and the function prototypes are in the **common header** section.

#### 6.4 Code Generation

Code generation produces a separate source file for each task, files for the common code and common header, and an additional file with internal control information. The target language is C, although it could be modified for any other language with sufficient syntax to support the task and state descriptions. The major jobs done by the code generator are naming all of the state functions and producing data objects that describe each of the tasks and each of the states. These data objects are linked lists containing all of the topological and status information associated with tasks and states. They include the transition information, pointers to relevant functions, etc.

The code generated at this step is still completely portable. The compile/link operation customizes the program for the particular environment it will run in. The usual procedure is to provide **make** files for whatever environments are supported.

#### 6.5 Compile, Edit and Merge

The compile, edit, link sequence is shown in **Figure** 4. As noted above, it is usually desirable to enter all of the states before entering the transitions. The initial code entry is often done while using the transition logic tool, as shown in the figure, although it is not mandatory. After generating code and attempting a compile, it is possible to edit the source code directly, for example, using the interactive development environment of the compiler. This is practically a necessity; it is much too awkward to have to go back to the transition logic tool each time an edit is necessary.

Once this editing is done, however, it is necessary to capture the editing back into the transition logic source file. This is done with the merge step, which is part of the transition logic tool. It copies all user-generated code in the C language source files back into the transition logic source file. The only rules for assuring that this is done successfully are that code is only entered in marked locations in the C source files, and that the names of the files are not changed.

The transition logic tool can be invoked at any time to change or add to the task or state structure. New code is then generated to build a test program.

#### 6.6 Execution Shell

The execution shell is the key to portability. It uses conditional compilation to build programs for any real time environment that is supported. For the simplest environments, it contains all of the necessary scheduling algorithms, giving a completely self-contained program. To

**Figure** 4. Design and Implementation Sequence

interface with other environments, appropriate code structure and library calls are set up to operate in the selected environment. By using this approach, it is possible to keep the user-written code completely portable -- no changes at all are required to recompile for a new operating environment.

The compilation and linking procedure is normally controlled using a MAKE facility associated with the target compiler. At present, creation of MAKE files is not automated.

# 6.7 Documentation

Either working or archival documentation can be produced from the transition logic tool. Working documentation includes a list (text) description of the entire system. For each task, all of the task parameters are listed (name, type, prioirity, initial status,etc.), as well as the task code (the code that is placed at the top of the task file). Then, for each state in the task, all of the transitions from that state are listed along with the description of the reason for the transition. The archival form of the

documentation adds all of the user-written code to the information given in the working documentation.

The working documentation can be used while developing the program, since the code is easily accessible from other routes, for example, using the compiler's editor. The archival documentation contains sufficient information to completely reconstruct the program, even if all of the source files were to disappear. It is, however, harder to read than the working form.

#### 7 Task Organization

The primary form of organization within tasks is the transition logic model. In addition, however, there is need for code that is common within a task or across some or all tasks, which is handled by task-related coded and common code. The file organization of one file per tasks is exploited in defining this code. Inter-task organization includes issues of data exchange among tasks and the control of how and when to activate and deactivate tasks. The former, data exchange, is handled formally, while the latter is handled informally.

#### 7.1 Task-Related Code

This code has been referred to in the description of the transition logic tool itself. It is code that must be within the scope of all parts of the task. Because tasks are complete in a single file, this code can be placed at the top of that file. The most common use of **this** code area is to define **static** variables. The nature of transition logic coding encourages the use of static variables. If, for example, a variable is initialized in an *entry* function and then acted on in **an action** function, it must be declared as static. For variables that **are local** to a single **action** function, **static** class may still have to be used because the function is continually scanned, although the variable need not be visible to the rest of the file. Functions that are used only by a single task can also be defined in the task-code section.

# 7.2 Common Code

Code that has to be visible to more than just one task goes into **common** code. This is, in fact, two sections. One section is common *header* and the other **common** code. The common header is brought into every task file with an **include** statement; the common code is linked to every independent thread.

The **common code** section is most commonly used to define functions of general utility, so they will be available to all tasks. The **common header** is used mostly for prototypes of those functions and **defines.** Note that global variables (*externs*) are not permitted, so this section is not used for global definitions (see the Communication section, below).

#### 7.3 Task Process Configuration

How tasks are distributed among processes is a design decision made by the user. The configuration information must be entered to the transition logic design tool. Any number of configurations can be defined, but one of them must be selected when code is generated. The code generation process puts configuration information into the C source files so it can be used by the execution shell (or shells for a multiprocessor configuration). The default configuration places all tasks in a single process. No user action is required to pick this configuration.

#### 7.4 Intertask Communication

Tasks in a control system exist as part of the solution to a job. As such, tasks will necessarily need to exchange information. The design of a means of implementing that exchange is most severely affected by the need for portability of the user-written source code. In addition, there is the fundamental need to protect the integrity of the data, which can be at risk whenever asynchronous computing components exist. Because of these concerns, intertask data communication is treated formally, through the transition logic design tool. Details are given in Section 8.6.

#### 7.5 The Master Task

A means is needed to activate and deactivate tasks. In particular, virtually all jobs have the problem of orderly task activation during start-up so that, for example, power supplies are turned on before the components they supply power to, and controllers are initialized before setpoints are changed. Activation and deactivation are done with function calls and so are embedded in the code structure rather than being treated formally.

As a convention for handling this chore, a single task is designated **as** the **master** task. In specifying the tasks, only the master task is given an initial status of active; all other tasks are initially inactive. The master task can then have a state structure that turns the other tasks on in a safe manner, including suitable delays and checks to make sure that conditions are proper as each task is activated. Likewise, the master task can orchestrate shutdown so safe conditions are maintained. In between, it can also be responsible for deactivating tasks that are not needed, although it is not always clear whether deactivating is significantly more efficient than giving the task an idle state that waits for the event that triggers the task's next activity.

In relatively simple jobs, it makes sense to have the master task control the operator interface as well, since the context changes in the operator interface follow major changes in task activity very closely.

It should be noted that the this structure is not enforced by any system formalism. It is only a suggested mechanism for task organization.

#### 8 Multitasking Performance: The Real World

The "universal real time solution" as outlined above depends on adequate computational speed to juggle all of the simultaneous activities without regard for the importance or computational characteristics of any of the individual tasks. The real world is not often so kindly! Taking **acount** of these real world concerns, however, only requires modest additions to the design structure as it has been developed thus far. These additions allow for a stronger connection between the engineering system design and the computational technology so that system performance specifications can be met.

## 8.1 Priority-Based Scheduling - Resource Shifting

The essence of living within a finite computing budget is to make sure enough of the computational resource budget is expended on the highest priority tasks. The first addition to the design structure, therefore, is to associate priorities with the tasks. The job of the computational technology, then, is to shift resources away from the low priority tasks and towards the high priority tasks.

How that is to be done depends on the criteria for success. There are at least two ways of measuring performance,

- progress towards a computational goal

- execution within a certain window

These lead to different computational strategies and to fundamental task classifications.

# 8.2 Continuous/Intermittent Tasks

These two performance measures suggest a division of tasks according to performance type. *Continuous* tasks measure success by progress. They will absorb as much computing resource as they are given. *Intermittent* tasks respond to explicit events and have a limited computing function to perform for each event occurrence. Their success is measured by whether the response to the event occurs within a specified time of the event itself.

The universal solution uses only continuous tasks. The nature of a task's response to events is embedded in its transition structure, so no distinction needed to be made in task classification. Using the continuous/intermittent classification, it will be necessary to specify the event to which an intermittent task responds explicit, that is, part of the transition logic design tool, rather than implicit. Thus, there will be a further subdivision within the intermittent tasks; no subdivision of continuous tasks is needed.

Continuous tasks encompass that portion of a control job that is most like conventional computing in the sense that the goal is to deliver a result as soon as possible rather than at a specified time. They thus form the lower priority end of the real time spectrum. Priority distinctions within the continuous tasks can be handled by, on average, giving more resource to the higher priority tasks. Within the "universal" approach, which is still applicable to the continuous tasks, priorities of continuous-type tasks can be recognized by giving high priority tasks more scans than lower priority tasks.

A different approach is required for the intermittent tasks. In the simplest computing environment, that is, a single computing thread, intermittent tasks are distinguished from continuous tasks by two properties,

1) They are only given computing resource (i.e., transition logic scans) when the triggering event has occurred, and,

2) Once they are triggered they are given as many scans as are necessary to complete their activity.

This change alone is sometimes enough to meet performance specifications for a job that could not meet specifications using all continuous tasks (the universal approach). In particular, if the problem is that once triggered, the high priority task does not gets its output produced within the specified window, this will help meet specification because as an intermittent task it will be given all of the computing resource until it completes the response to the event. If, on the other hand, the problem

is one of *latency*, that is, the task does not always start soon enough after the triggering event to meet the specification, then other remedies will be required.

#### 8.3 Cooperative Multitasking Modes

"Multitasking" is a generic term in computing referring to the ability to do more than a single activity at a time. It is usually applied to single-processor configurations. In that context, since digital computers are by their nature only capable of doing one thing at a time, the simultaneity comes from rapid (with respect to the observer) switching from one activity to another, rather than truly simultaneous operation. In the context of real time control software, this definition must be further refined to reflect both the engineering and the computational categories defined above.

First, to map from the engineering system description to the computational implementation, the engineering *task* is the indivisable computing unit. Thus, each computing thread will contain at least one task.

Within any thread that contains more than one task, some form of *scheduling* must be implemented to share the threads computational resource among its tasks. Two forms of scheduling have been implemented for multiple tasks inside a single computing thread, *sequential*, and *recursive*. Since they exist in one thread, these schedulers are referred to *as cooperative multitasking schedulers*. The term "cooperative" is used to describe the fact that the scheduler can never preempt a running program, but can only perform its function when tasks voluntarily return control back to the scheduler.

The success of cooperative schedulers depends on the voluntary return of control, which in standard programming languages is difficult to design consistently. Cooperative schedulers can be used very effectively in the transition logic context, however, because the state functions (entry, action, test, exit) are all specified as nonblocking. Thus, there is always return of control at the end of each state scan which doesn't require any special consideration on the programmer's part.

The simplest of these has already been described in **Figure 2**, and in the subsequent description of the "universal real time solution." By successively applying the scan logic to each task in the thread, all of the tasks are given a share of the computing resource. Following the rules described above, intermittent tasks are given as many scans as they need to complete their current activity, while continuous tasks are given a fixed number of scans for each complete cycle of the scheduler. In the transition logic context, this is called a *sequential* scheduler, since it addresses each task in sequence.

In order to know when an intermittent task should run, the scheduler must keep track of the events to which the tasks are attached. The most common such event is the end of a specified time period. Events are often also based on changes in external signals or on internally generated conditions.

As noted above, intermittent tasks often have a latency specification. Use of the sequential scheduler can lead to longer latencies than can be tolerated because all other tasks must be scanned in succession before the scheduler will return to a given task. A *recursive* scheduler can greatly reduce the latency, particularly if there are a large number of tasks. Instead of scanning tasks sequentially,

the scheduler itself is called alter every scan. When called, it examines the task list to see if any tasks that are higher priority than the currently executing task are ready to execute. If so, the highest priority task is started, while the task that had been running waits. The latency for the highest priority task is thus reduced to no more than the worst case scan time of any single task, rather than the sum of scan times for all of the tasks.

This is a recursion because the scheduler is "calling itself" -- it is initially invoked to start task execution, while running the task it invokes itself again to check to see if higher priority taks need to be run. If any do, they are started, but the scheduler again invokes itself to continue performing priority checks. As the higher priority tasks complete, they return control to the scheduler thereby backing out of the recursion.

The recursive scheduler can achieve the resource shifting needed to help a high priority task meet its real time performance constraints, but it takes significantly more overhead than the sequential scheduler since it is run more often. The net effect is thus to improve the effectiveness of the high priority tasks at the expense of the total amount of computing resource that is available for "productive" use.

#### 8.4 Preemptive Multitasking Modes

If the latency specifications still cannot be met, a preemptive solution will be needed. Such a situation could arise, for example, if the action functions of one or more low priority tasks required substantial amounts of computing time. This does not violate the "nonblocking" condition, which states only that computing time in any of the state functions must be predictable, not that it must be "short." In other cases, it might be necessary to violate the nonblocking condition. Though certainly not desirable, violations could arise due to the need to use software not under the control of the real time programmer. Examples of these might be operator interface software or mathematical software with nondeterministic iterations.

Preemptive scheduling makes use of the computer's interrupt facility, which can, in response to an external event, temporarily halt the execution of whatever code is currently running and start some other code running. Since the interrupt facility is part of the computer's hardware, this preemption takes place on a much faster time scale than can be achieved by the recursive, cooperative scheduler and so, can meet much stricter latency requirements.

Preemption is used to establish a new computing thread. When an interrupt occurs, the current thread is suspended and a new thread is started. These threads share a common memory space, but are otherwise independent entities. At the simplest level, the interrupt mechanism itself is a scheduler. Each interrupt-scheduled thread would thus contain one task. However, interrupt-scheduled threads can contain more than one task. The tasks inside the interrupt-scheduled thread must be scheduled by a cooperative scheduler.

Interrupt-scheduled threads must only contain intermittent tasks. Because the hardware interrupt establishes a priority level ahead of any software-based priorities, if the tasks in an interrupt thread were to ask for "continuous" CPU resource, all other tasks would be locked out. Thus, all of the

continuous tasks must be left in the non-interrupt domain; that is, they get to run whenever no interrupts are active. Threads that are scheduled directly by interrupts must normally be quite short. Because the interrupt mechanism on most computers is constructed in such a way that all other interrupts of the same or lower priority are locked out until the present interrupt is finished, it becomes essential to keep this time as short as possible.

Interrupts can also be used as a mechanism for running schedulers. When this is done, the restriction that only short threads should be run can be relaxed. This is possible because, while the scheduler runs as interrupt-based code, it resets the interrupt mechanism before allowing any user-written code to run. This allows access for all interrupts while the user-written task is running.

Schedulers of this sort come in two flavors:

- 1) Those that operate through the function-call mechanism,

- 2) Those that manipulate the execution context directly.

The most obvious difference between these, particularly in the transition logic environment, is that for the first type of scheduler, the continuous tasks are operated using cooperative scheduling, while the second type can use time-sliced scheduling. The difference is that in cooperative scheduling, the continuous tasks are given access to CPU resource according to the number of transition logic scans they use whereas in time-sliced scheduling, the continuous tasks get CPU resource according to the amount of computing time they use. This can make a performance difference in those cases for which there are significant differences in execution time of specific state functions. Only time-sliced scheduling can handle a case where the nonblocking restriction is violated.

The scheduler that operates via the function-call mechanism is identical to the recursive scheduler described above. The only difference is that instead of being called from the transition logic scanner, it is called from an interrupt. It is thus the same code, but **run** as a reentrant rather than recursive scheduler. However, to avoid two different names for the same scheduler, it will be called a **recursive-interrupt** scheduler.

There are other differences between these scheduling mechanisms as well, particularly relating to how and when tasks can suspend themselves, but these differences are less important in the transition logic environment than they are in other computing environments.

#### 8.5 Task Types

In recognition of the various scheduling methods outlined above, every task must have a designated task type. The task types are the user's indications of **preferred** task type. Depending on the scheduling environment that is actually used, the task may be scheduled using a simpler mechanism than was requested. The distinction between **continuous** and **intermittent** tasks, however, will be maintained in all implemented environments.

The types of tasks that are defined are:

- Hard timer interrupt

- Soft timer interrupt

- One-shot timer

- Digital interrupt

- Sample-time

- Logic event

- Continuous

The first four are all interrupt-scheduled, if an interrupt environment is defined. That means that they operate at interrupt priority and can only be preempted by other, higher priority, interrupts. The **one**-shot timer differs from the other timer-types because it does not automatically reset the timer and run again after it has run once. The timer must be explicitly reset each time. If no interrupt is present, they will be cooperatively multitasked, using either the sequential or recursive scheduler. As interrupt-scheduled tasks, they should be short, relinquishing the CPU quickly after activation.

The sample-time and logic-event types are generally of lower priority, and, given the appropriate execution environment, should be controlled by an interrupt-driven scheduler, of either of the types defined above. Because the tasks execute only after the interrupt system's priority has been reset, they are preemptable by any direct interrupt-driven tasks, and by the interrupt driven scheduler, which can determine at any time if higher priority tasks should be run.

The continuous tasks always operate at lowest priority. They can be either scan or time-slice scheduled.

# **8.6 Supported Environments**

At present, environments of all of the types described above are supported. All of these run on **PC**-type of computers (X86 architecture, **MS/PCDOS** operating system, Microsoft C compilers). A version for QNX (a commercially available real time operating system) is currently being developed.

The simulation and calibrated-time modes are the least affected by the target environment. Although these are currently targeted for PCs, it would take little or no work to target them for other general purpose computing environments. Both sequential and recursive schedulers are implemented in the simulation environment. The calibrated-time environment is the same as the simulation environment, except that the simulation step size is chosen so that simulated time matches real time (at least on average).

The single-thread, real time environment also uses the same scheduling as the simulation mode, either sequential or recursive. It differs from calibrated-time, however, by using an external clock to measure time instead of a calibration. It thus gives accurate time at all times, instead of just on average. This mode is **also** easily ported to any target environment for which a fine enough time granularity is available.

The direct interrupt environment is supported through a locally written package called XIGNAL. This package sets up interrupt hardware and associates the desired interrupt function with the

hardware interrupt. In this mode, all timer and event related tasks are executed tasks are attached to the interrupt. Since there is only one clock available on a PC, all of the time-type tasks are connected to the same clock. Thus, regardless of priority, once a time-type task starts running, it will run to completion before any other timed task can run. There is a somewhat arbitrary decision to be made in the implementation of this mode. That is, whether the sample-time and event based tasks should be connected to the interrupt or left in the cooperative domain. If any of them have long execution times, they could interfere with the higher priority direct interrupt tasks. On the other hand, they have a better chance of meeting time constraints as interrupt-driven tasks.

Since in the direct interrupt mode no reentrance is allowed to the running tasks, it is probable that the interrupt facilities supplied with the compiler would work as well as XIGNAL, and perhaps more efficiently. This has not yet been tested.

Adding the recursive scheduler to the interrupt mode (which then makes it a reentrant scheduler) allows the separation of the sample-time and event tasks from the direct interrupt tasks. Because the recursive scheduler only requires the additional ability to reset the interrupt system's priority, it does not pose much more difficulty for porting than the direct interrupt mode itself. This mode, does, however, require that the interrupt package permit reentrant interrupts. Most interrupts associated with compilers do not permit reentrance so are not suitable for this mode.

Full context-switching scheduling is implemented with another locally written package, **CLOTHO**. In most control applications, the major operational distinction of this scheduler is that it provides for time-slice scheduling of the continuous tasks. This permits the use of ill-behaved tasks (i.e., blocking) or tasks which, while not actually blocking, have unacceptably long execution times.

The following table summarizes the supported environments and gives the abbreviations used in further references to them.

| Name      | Description                                                                                                                                                               |  |  |  |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Seq-Sim   | Sequential scheduler, simulation environment (no real time at all)                                                                                                        |  |  |  |

| Ret-Sim   | Recursive scheduler, simulation environment                                                                                                                               |  |  |  |

| Seq-Calib | Sequential scheduler, time by calibration of step size, single thread                                                                                                     |  |  |  |

| Ret-Calib | Recursive scheduler, time by calibration of step size, single thread                                                                                                      |  |  |  |

| Int       | Direct interrupt scheduling for time and event tasks, number of threads<br>depends on hardware configuration; single thread, sequential scheduler<br>for continuous tasks |  |  |  |

| Name    | Description                                                                                                                                                                                                                                     |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ret-Int | Direct interrupt scheduling for timer and digital IO tasks, interrupt-driven recursive (reentrant) scheduling for sample time and event tasks. Each recursively scheduled task has a unique thread. Sequential scheduling for continuous tasks. |

| Slice   | Direct interrupt and recursive-interrupt scheduling for time and event tasks, time-sliced scheduling for continuous tasks                                                                                                                       |

# 9 Intertask Communication

Communication among tasks is inherent to control software. The design concerns in structuring the communication facilities are data integrity, communication efficiency, and software portability. These must be addressed for data that is explicitly defined by the user/programmer, and data that is integral to the task model, including task status information, state information, task parameters, etc.

# 9.1 Data Integrity

Even when all tasks reside in a single process, they can still be separated into asynchronously executing (lightweight) threads. Since these tasks share teh **adress** space, normal C language syntax such as function calls or external variables, could be used for data transfer across tasks, if any form of preemptive scheduling is used, there is a risk of data corruption. To maintain data integrity, restrictions of **mutual exclusion** must be observed. Mutual exclusion must be invoked whenever the information exchange involves separate threads to prevent the data exchange from being interrupted by a preemptive context switch, leading to the possibility of part of the data exchange being completed before the switch, and then, in the new context, changing that data, thereby leading to corrupted data when the data exchange completes after the preemption is complete. There are ways to prevent this, most commonly by disabling the interrupts during a data exchange, but the user must know when and how to apply them. Furthermore, these methods will fail any time tasks are divided into more than one process.

# 9.2 Communication Across Processes

One attractive way to meet the constraints of several high priority tasks is to use independent processors, one for each such task. This guarantees immediate attention to the highest priority task in each processor, and, rather than the resource shifting associated with real time scheduling, this adds additional resource to meet these requirements. The tradeoff in using multiple processors is that data exchange must go through some external medium to get from one task to another. This has consequences of both overhead to service the medium, and delay for the actual transfer of information. These costs must be balanced against the savings due to less scheduling overhead and the potential increase in total processing resource.

If an application is compiled and linked to run in an environment with independent processes (including the case of multiprocessors) then conventional programming methods for interchange of information among functions (through arguments, return values, global variables) will not work because the independent processes do not share memory address spaces. Since a major goal of this methodology is to retain code portability, standard data exchange mechanisms are not suitable.

## 9.3 Communication Media

Common communication media include shared external memory (for multiple processors that share a bus, for example), networks of all sorts, and point-to-point connections, usually via serial channels, but possibly using parallel channels. Each of these media has different software interface protocols. Again, if portability is to be presenved, the details of these protocols must be hidden from the user. Selection of different mechanisms will have significantly different performance and cost, as well as different distance and environmental constraints. which must be factored into the final system design.

At present, support is provided for point-to-point serial connections and for Ethernet connections using **TC/PIP** protocols.

#### 9.4 Communication Structures

As a result of these factors, the definition of intertask communication has been placed in the transition logic tool, at the same level as task definition. This is important for the portability to various means of inter-process communication and to assure maintenance of data integrity. The model chosen for inter-task communication is that of pseudo-shared memory. Variables set in one task are accessed in other tasks as if they were local variables. The variables involved are specified using two lists for each task -- one list for those variables that are set in the task and available for use by other tasks, the second list for variables set in other tasks and used in this task. Each variable must

be set in one and only one task. This avoids conflicts in usage in which the same variable could be set in two places at nearly the same time, but one of the actions would override the other. Since this is a race condition, there is no way to predict what value the variable would have.

An important implementation factor with this method is that when tasks share a process, the communication overhead must be kept to a minimum. Tasks are grouped together specifically to minimize communication overhead, so this must be recognized when the inter-task communication structure is set up.

#### **10 Example: Stepping Motor Control**

An example of the application of these techniques is given by a stepping motor control program. It is a relatively simple example, but contains enough complexity and hierarchy to show the basics of the methodology.

#### **10.1 Tasks**

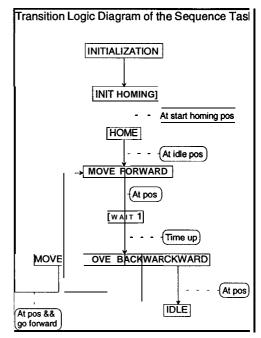

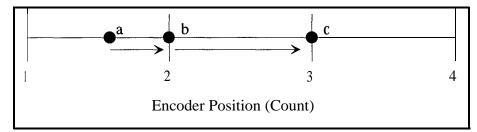

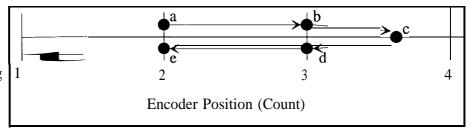

Figure 5. Transition Logic for the *Sequence* Task

The purpose of the control system is to make sequences of moves using a stepper motor. It is organized into three tasks:

1. Sequence control to specify when the moves should be made and to where.

2. Step generation to resolve differences between actual and desired motor position by generating steps at a specified rate.

3. A master task to control start-up and shutdown of the other tasks and to control the operator interface.

The sequence task, **Figure 5**, begins by performing whatever system initialization is necessary, then requests that the stepping motor find its home position. It then enters a loop in containing a forward move, a timed wait and a backward move. This loop is intended to be typical of the kinds of motion that might be commanded in manufacturing or assembly machinery. The actual sequence of events is easily modified by defining a new set of states for that section of the task. The sequence terminates when the **go-forward** flag is no longer on. Each of the states in this loop has transition conditions relevant to its activity: the motion states complete when the motor reaches its target position and the **wait** state completes when time is up.

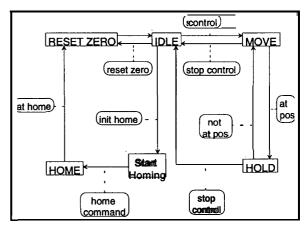

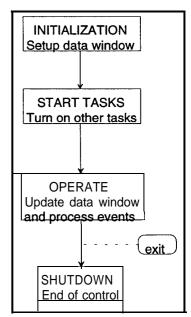

The step generation task, **Figure 6**, operates by interpreting commands that are sent to it. The master task, **Figure** 7, controls the start-up of the other tasks, and, in this case, also implements the operator interface.

#### **10.2** Documentation

The documentation information produced by the transition logic processor follows:

Project: STEPSEQ

Task: Master-opint; Initial State: Initialize Type: Continuous, Priority: 0 Chnl: 0 Data value: 0 **Init** status: 2 State: Initialize [Initialize I/O, variables, etc.] to: **StartTasks** if [Initialization done]

State: **StartTasks** [Start up sequence and position tasks] to: Operate if [Tasks successfully started]

State: Operate [Normal system operation]

to: Shutdown if [Operator request for shutdown] State: Shutdown [Home motor, turn off control]