## UC San Diego UC San Diego Electronic Theses and Dissertations

#### Title

Energy Efficient Integrated Circuits for Low Power Wireless Communication Applications

Permalink https://escholarship.org/uc/item/0ww702v8

Author Lee, Dhon-Gue

Publication Date 2019

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA SAN DIEGO

#### Energy Efficient Integrated Circuits for Low Power Wireless Communication Applications

#### A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

Electrical Engineering (Electronic Circuits and Systems)

by

Dhon-Gue Lee

Committee in charge:

Professor Patrick P. Mercier, Chair Professor Peter M. Asbeck Professor Gert Cauwenberghs Professor Ian A. Galton Professor Laurence B. Milstein

2019

Copyright Dhon-Gue Lee, 2019 All rights reserved. The dissertation of Dhon-Gue Lee is approved, and it is acceptable in quality and form for publication on microfilm and electronically:

Chair

University of California San Diego

2019

#### DEDICATION

To my mother.

| Signature Page                                                                                                                                                                                                                                                                                                                | iii                                          |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--|

| Dedication                                                                                                                                                                                                                                                                                                                    |                                              |  |

| Table of Contents                                                                                                                                                                                                                                                                                                             | v                                            |  |

| List of Figures                                                                                                                                                                                                                                                                                                               | viii                                         |  |

| List of Tables                                                                                                                                                                                                                                                                                                                | xii                                          |  |

| Acknowledgements                                                                                                                                                                                                                                                                                                              | xiii                                         |  |

| Vita                                                                                                                                                                                                                                                                                                                          | XV                                           |  |

| Abstract of the Dissertation                                                                                                                                                                                                                                                                                                  | xvi                                          |  |

| Chapter 1. Introduction         1.1. Link Budgeting         1.2. Low Power RX Architectures         1.3. Clocked Modulator         1.4. Energy/Envelope Detector-based RX         1.5. Super-regenerative Receiver         1.6. Summary of dissertation         1.7. Acknowledgement                                          | 1<br>3<br>5<br>6<br>8<br>8<br>10             |  |

| Chapter 2. A 1.65 mW PLL-free PSK Receiver Employing Super-regenerative         Phase Sampling                                                                                                                                                                                                                                | 11<br>11<br>13<br>15<br>15<br>16<br>16<br>19 |  |

| Chapter 3. Noise Analysis of Phase-Demodulating Receivers Employing Super-Regenerative Amplification         3.1. Introduction         3.2. Overview of General Super-Regenerative Theory         3.2.1. One Port Oscillator Model         3.2.2. Solution of the Differential Equation for the Linear and Time-Variant Model | 22<br>22<br>25<br>25<br>25                   |  |

| 3.2.3. Frequency Domain SRA Noise Model             |                              |

|-----------------------------------------------------|------------------------------|

| 3.3. Sensitivity Analysis of a PSK SRA              |                              |

| 3.3.1. Derivation of the probability density f      | unction of output phase . 30 |

| 3.3.2. Sensitivity analysis of super-regenerat      | ive phase                    |

| 3.3.3. The effect of noise in the saturated osc     | cillation                    |

| regime on the sensitivity of a super-reg            | generative receiver 37       |

| 3.4. Design and Analysis of a Colpitts-based        |                              |

| SRA                                                 |                              |

| 3.5. Measurement Results                            |                              |

| 3.6. Appendix A: Time-Domain Stochastic             |                              |

| Analysis of Super-Regenerative Amplifiers .         |                              |

| 3.6.1. Time-invariant Noise Input                   |                              |

| 3.6.2. Time-Varying White Noise Model               |                              |

| 3.7. Appendix B: Derivation of the pdf of $\Theta$  |                              |

| 3.8. Appendix C: Effect of Phase Noise on the sen   |                              |

| 3.9. Acknowledgement                                |                              |

| C                                                   |                              |

| Chapter 4. Active Mixer Adopted Sub-Sampling Phase- | Locked Loop 61               |

| 4.1. Introduction                                   |                              |

| 4.2. Sources of the Reference Spur in               |                              |

| Conventional Sub-Sampling PLLs &                    |                              |

| Mitigation Strategies                               |                              |

| 4.2.1. Sources of the reference spur                |                              |

| 4.2.2. Prior-art mitigation technique I: VCO        | buffer 65                    |

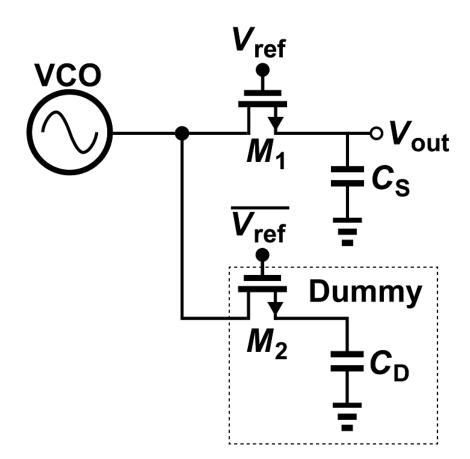

| 4.2.3. Prior-art mitigation technique II: a cor     | nplementary dummy path 66    |

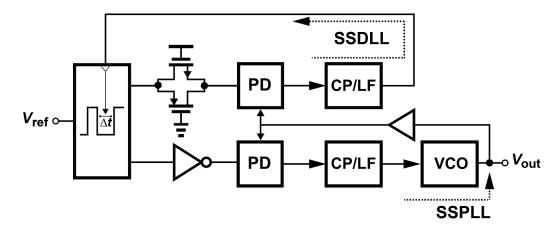

| 4.2.4. Prior-art mitigation technique III: a ter    | tiary delay-locked loop . 67 |

| 4.3. Proposed Active-Mixer Adopted                  |                              |

| Sub-Sampling (AMASS) Phase Detector                 |                              |

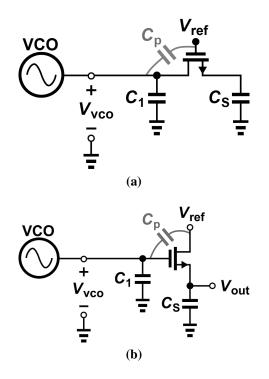

| 4.3.1. Step 1: Rotating the Switch                  |                              |

| 4.3.2. Step 2: Adding a Sampler                     |                              |

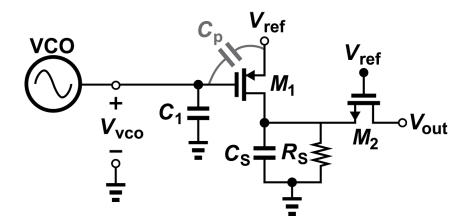

| 4.3.3. Final Phase Detector Circuit                 |                              |

| 4.4. Circuit & System Description                   |                              |

| 4.4.1. Pulse Generator                              |                              |

| 4.4.2. Phase Detector                               |                              |

| 4.4.3. Gm Cell and Loop Filter                      |                              |

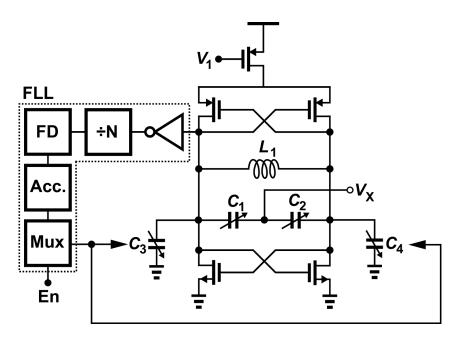

| 4.4.4. Hybrid VCO/DCO and FLL                       |                              |

| 4.5. Phase Domain Model                             |                              |

| 4.6. Measurement Results                            |                              |

| 4.7. Conclusion                                     |                              |

| 4.8. Acknowledgement                                |                              |

| -                                                   |                              |

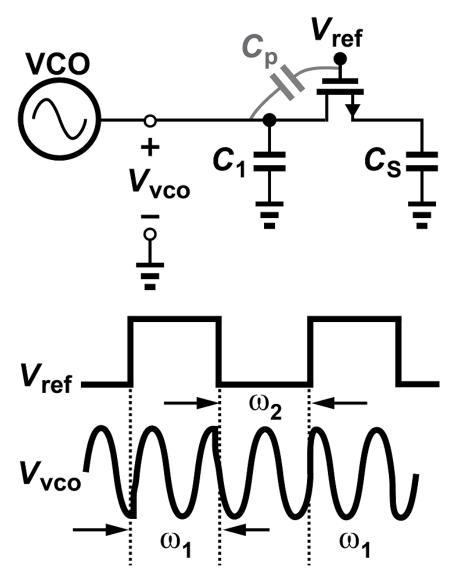

| Chapter 5. Spur Reduction in Sub-Sampling PLLs using Cancellation Varactors . | 91  |

|-------------------------------------------------------------------------------|-----|

| 5.1. Introduction                                                             | 91  |

| 5.2. Proposed Technique                                                       | 91  |

| 5.3. Simulation Result                                                        | 95  |

| 5.4. Design Detail                                                            | 96  |

| 5.5. Conclusion                                                               | 98  |

| References                                                                    | 101 |

#### LIST OF FIGURES

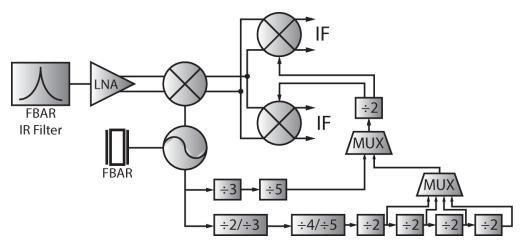

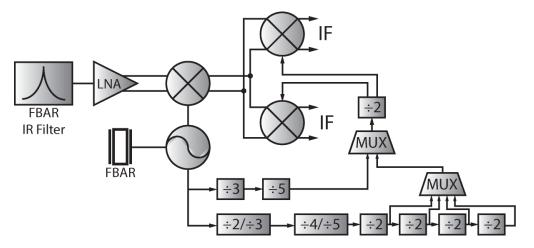

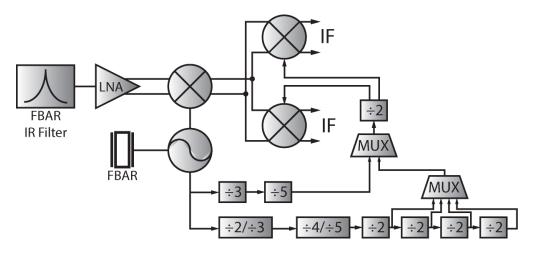

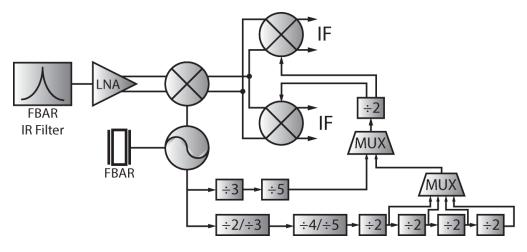

| Figure 1.1. PLL-less FBAR-based Super-heterodyne RX schematics [1]                                              | 6  |

|-----------------------------------------------------------------------------------------------------------------|----|

| Figure 1.2. Schematics of envelope-detector-based RX frontend                                                   | 6  |

| Figure 1.3. Schematics of 2-tone FSK receiver [2]                                                               | 7  |

| Figure 1.4. Schematics of super-regenerative receiver with BW calibration [3]                                   | 9  |

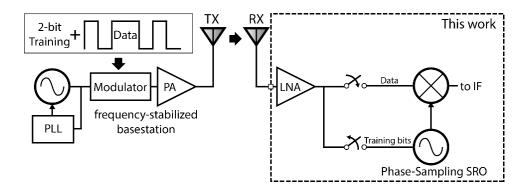

| Figure 2.1. Overview of the proposed phase-sampling system.                                                     | 12 |

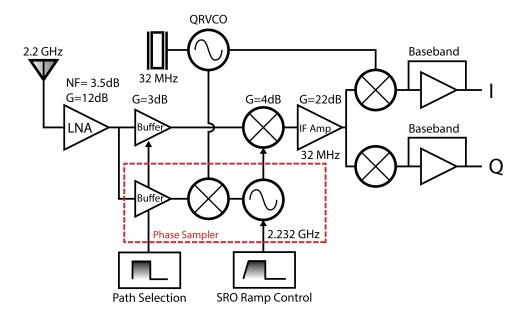

| Figure 2.2. Block diagram of the phase-sampling receiver.                                                       | 14 |

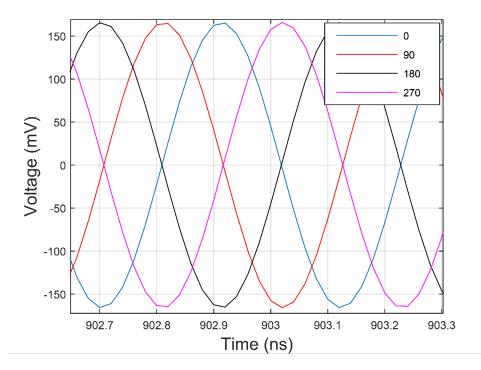

| Figure 2.3. Simulation result of phase sampling SROs output waveform given 100 nA inputs of 4 different phases. | 15 |

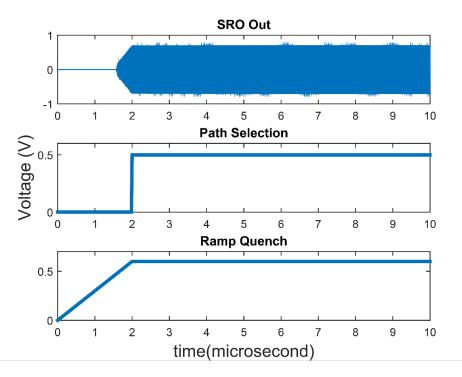

| Figure 2.4. Timing diagram of control signals and the output of the SRO                                         | 16 |

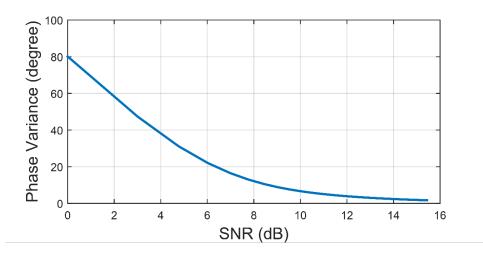

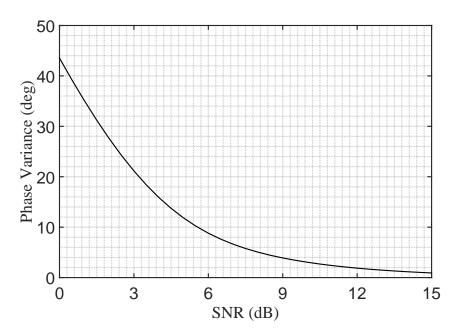

| Figure 2.5. Simulated phase variance versus SNR of the SRO                                                      | 17 |

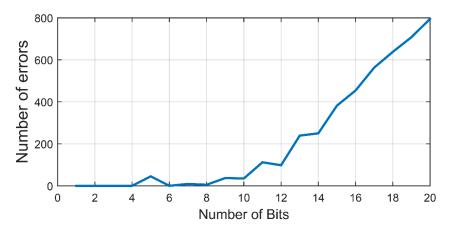

| Figure 2.6. Measured number of errors for each bit after the training bit                                       | 17 |

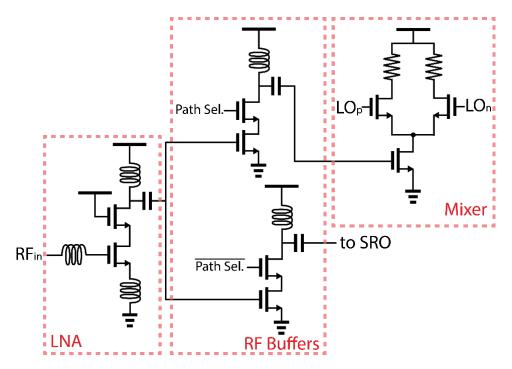

| Figure 2.7. Schematics of LNA, RF buffers, and active down-conversion mixer.                                    | 18 |

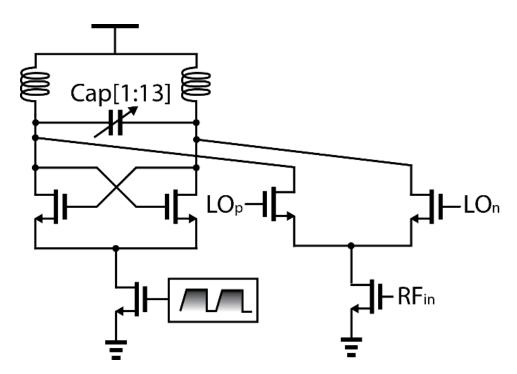

| Figure 2.8. Schematics of the SRO (left) and the up-conversion mixer (right)                                    | 19 |

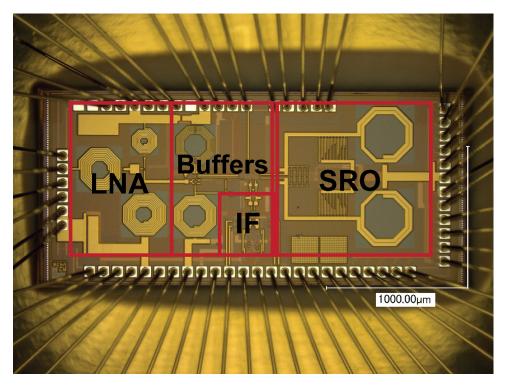

| Figure 2.9. Chip microphotography of the receiver.                                                              | 20 |

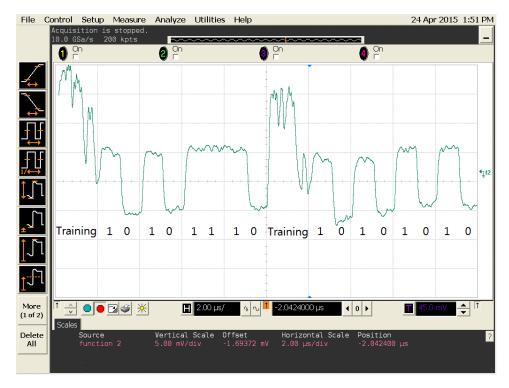

| Figure 2.10. Transient waveform of the receivers I channel output                                               | 20 |

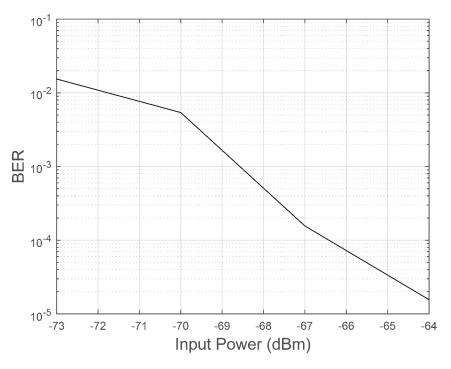

| Figure 2.11. Measured Input Power versus BER                                                                    | 21 |

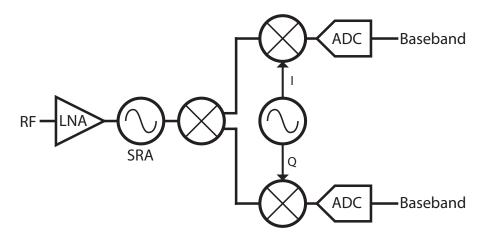

| Figure 3.1. A representative PSK receiver architecture employing super-regenerative amplification.              | 24 |

| Figure 3.2. One port oscillator circuit model of SRAs.                                                          | 25 |

| Figure 3.3. Illustration of the operation of an SRA.                                                            | 26 |

| Figure 3.4. Illustration of the random variables in the constellation diagram                                   | 32 |

| Figure 3.5. SNR vs phase variance of super-regenerative amplifiers                                              | 34 |

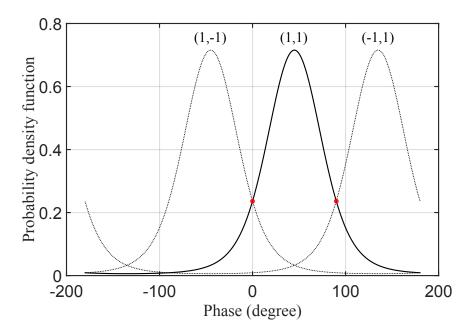

| Figure 3.6. Probability density functions of the phase at the SRA output given two different QPSK input signals at $SNR_{out} = 5 \text{ dB}.$                                                                 | 35 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

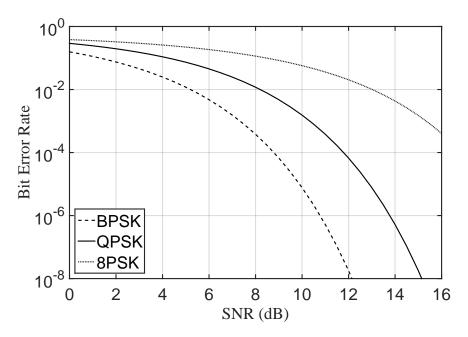

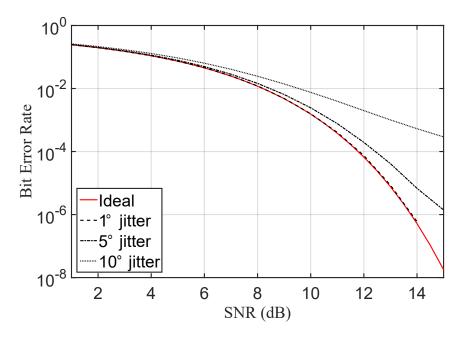

| Figure 3.7. SNR vs. BER for various phase modulation schemes                                                                                                                                                   | 36 |

| Figure 3.8. SNR vs. BER in the presence of phase noise at different RMS jitter values for QPSK modulation.                                                                                                     | 38 |

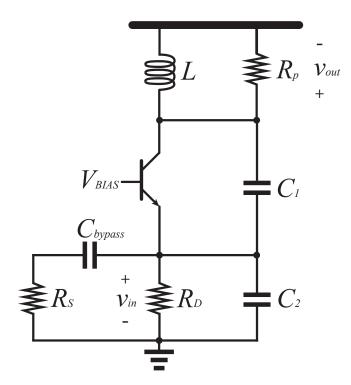

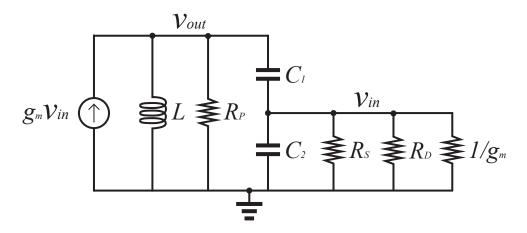

| Figure 3.9. A schematic of Colpitts-based SRA                                                                                                                                                                  | 39 |

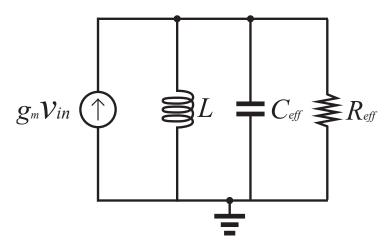

| Figure 3.10. Small-signal model of the Colpitts-based SRA                                                                                                                                                      | 40 |

| Figure 3.11. One-port equivalent model of the Colpitts-based SRA.                                                                                                                                              | 40 |

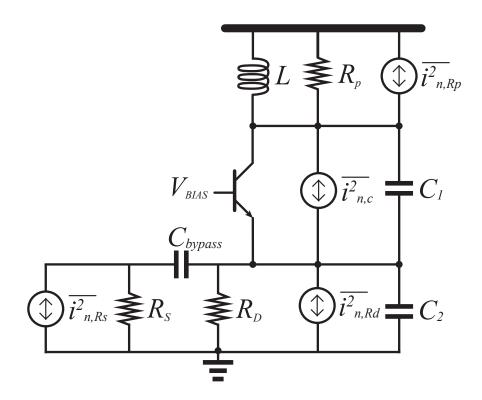

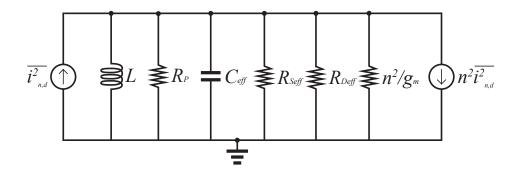

| Figure 3.12. Circuit model of the SRA with noise sources.                                                                                                                                                      | 41 |

| Figure 3.13. Single-port circuit model of the SRA with noise sources.                                                                                                                                          | 42 |

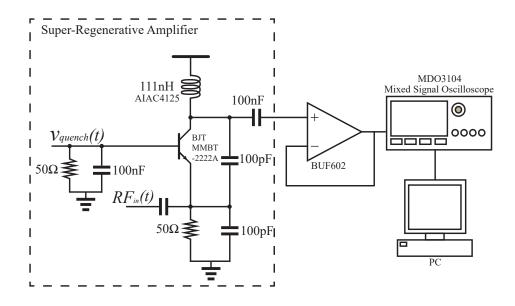

| Figure 3.14. Schematic of a discrete SRA prototype used for experimental verification.                                                                                                                         | 45 |

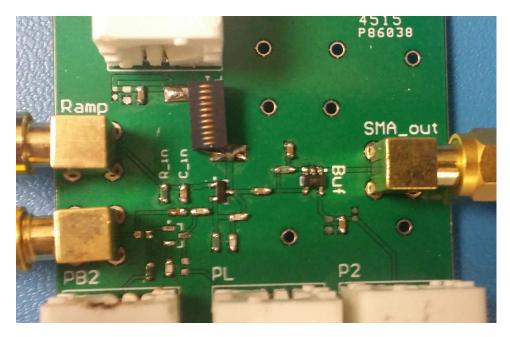

| Figure 3.15. Photograph of the discrete SRA prototype used for experimental verification. Fairchild MMBT-2222a BJT, Abracon Co. AIAC-4125 inductor, and TI BUF602 amplifier have been used in the measurement. | 46 |

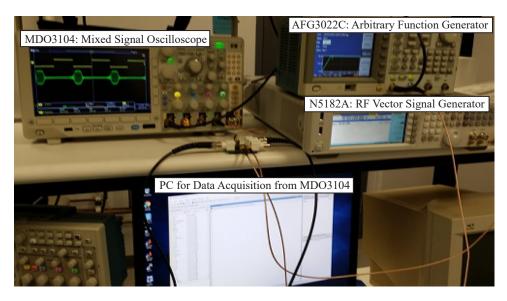

| Figure 3.16. Photograph of the experimental set-up (DC supplies not shown)                                                                                                                                     | 47 |

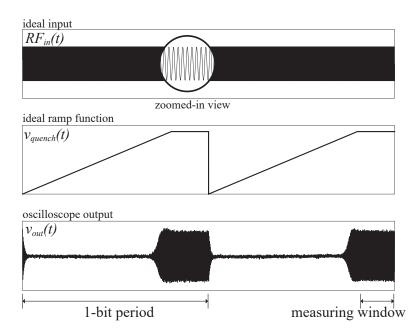

| Figure 3.17. Illustration of important waveforms in the measurement                                                                                                                                            | 48 |

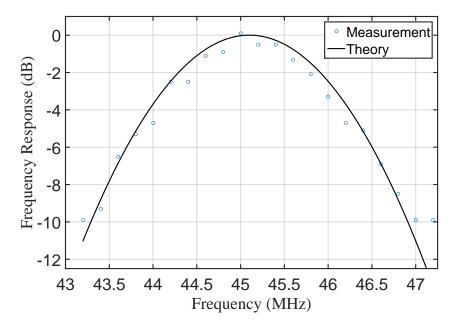

| Figure 3.18. Frequency response of the SRA                                                                                                                                                                     | 49 |

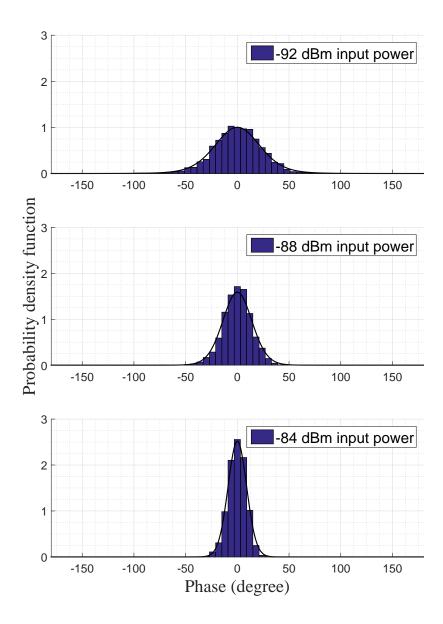

| Figure 3.19. Measured and theoretical probability density function of the output waveform at different input powers.                                                                                           | 58 |

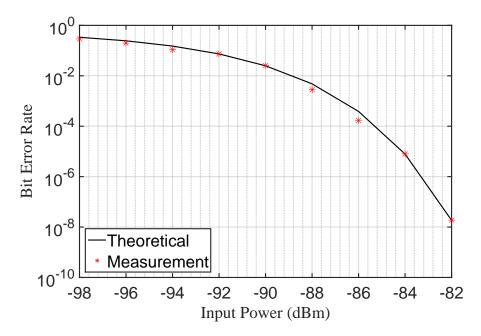

| Figure 3.20. A comparison between the measured and predicted bit error rate for QPSK modulation.                                                                                                               | 59 |

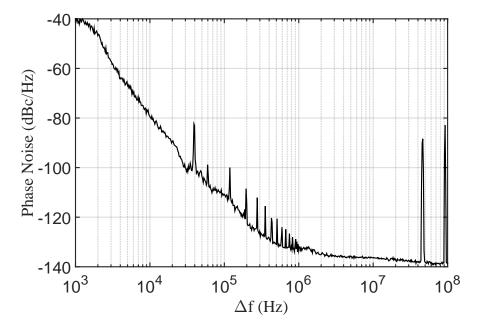

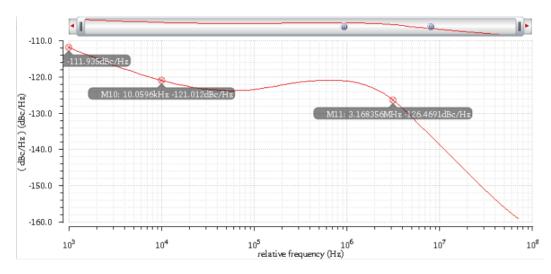

| Figure 3.21. Phase noise measurement of the prototype SRA operating in the oscillatory mode.                                                                                                                   | 59 |

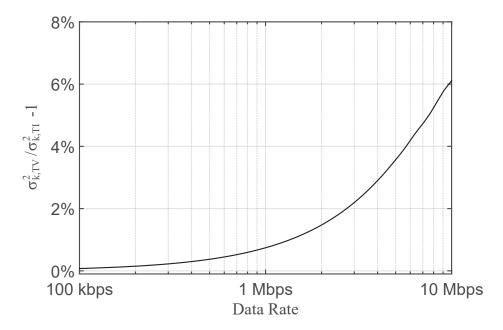

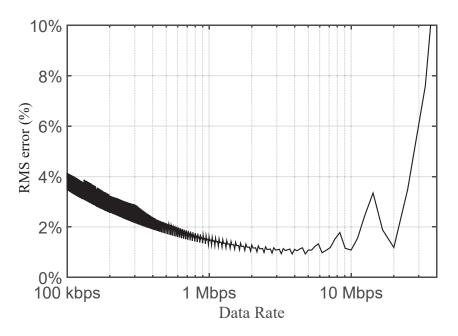

| Figure 3.22. Difference between time-variant analysis and time-invariant analysis plotted versus data rate.                                                                                                    | 60 |

| Figure 3.23. The solution $(3.3)$ to the differential equation $(3.2)$ is compared to the solution of the same differential equation based on numerical analysis                                               | 60 |

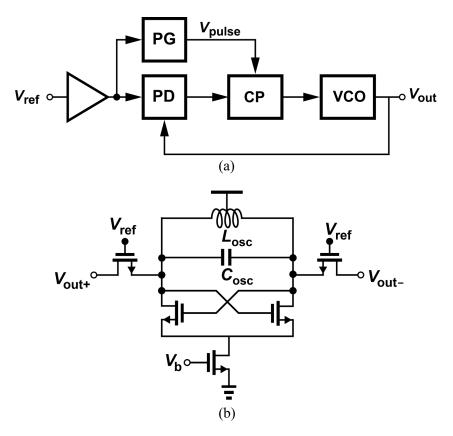

| Figure 4.1. (a) A system diagram of conventional sub-sampling PLL [4] and (b) a detailed schematic of the voltage controlled oscillator (VCO) and the phase detector (PD).     | 63 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 4.2. Illustration of sources of spur caused by the phase detector                                                                                                       | 80 |

| Figure 4.3. A dummy path technique for spur reduction [5]                                                                                                                      | 81 |

| Figure 4.4. A DLL based spur-reduction technique. [6]                                                                                                                          | 81 |

| Figure 4.5. (a) A schematic of a conventional sub-sampling phase detector. (b) A schematic of the sub-sampling phase detector with swapped orientations of input and reference | 82 |

| Figure 4.6. The new phase detector with hold operation.                                                                                                                        | 82 |

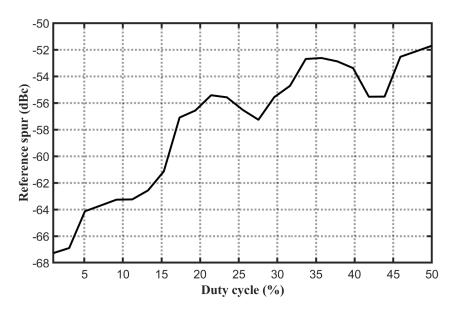

| Figure 4.7. A simulated reference spur versus the duty cycle of reference clock .                                                                                              | 83 |

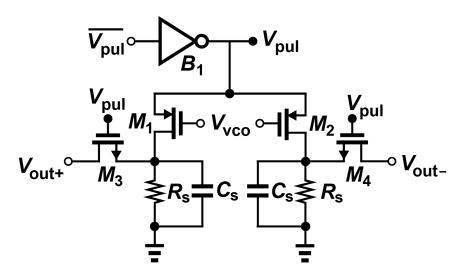

| Figure 4.8. The final implementation of the proposed phase detector                                                                                                            | 83 |

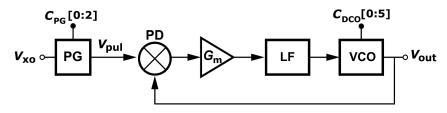

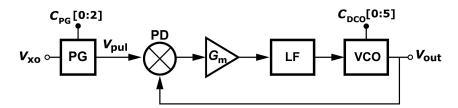

| Figure 4.9. A Schematic of the AMASS-PLL                                                                                                                                       | 83 |

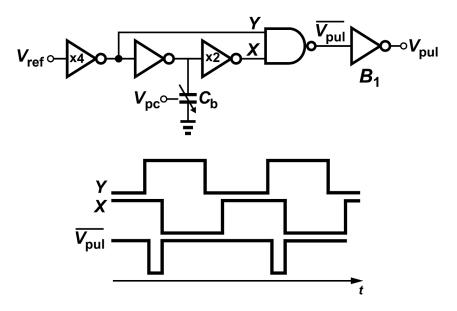

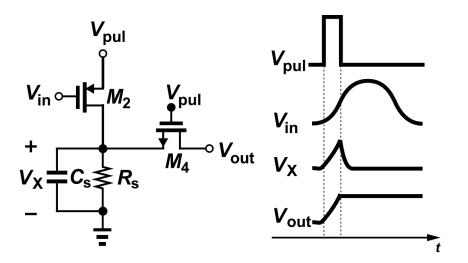

| Figure 4.10. A schematic of the pulse generator and waveforms of interest                                                                                                      | 84 |

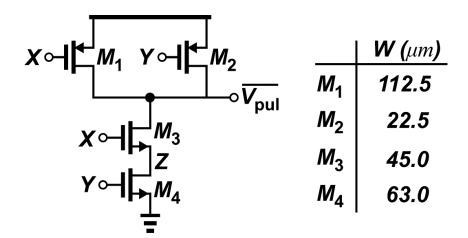

| Figure 4.11. A schematic of the NAND-gate in the pulse generator and the size of each transistor.                                                                              | 84 |

| Figure 4.12. A half circuit schematic of the pulse generator and waveforms of interest.                                                                                        | 85 |

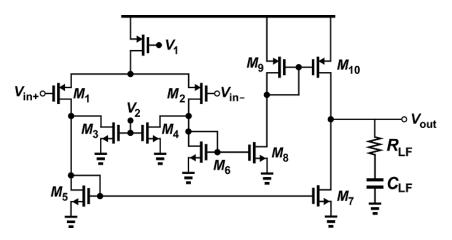

| Figure 4.13. A schematic of the transconductance amplifier.                                                                                                                    | 85 |

| Figure 4.14. A Schematic of the hybrid VCO/DCO                                                                                                                                 | 86 |

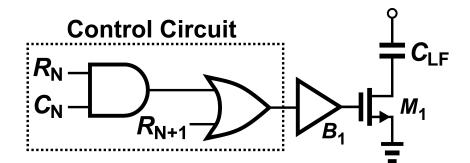

| Figure 4.15. Capacitor Bank for DCO                                                                                                                                            | 86 |

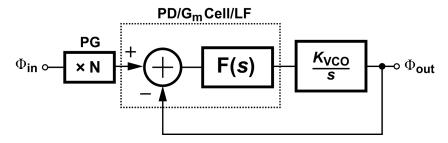

| Figure 4.16. Frequency domain model of the AMASS-PLL.                                                                                                                          | 86 |

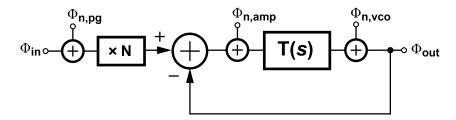

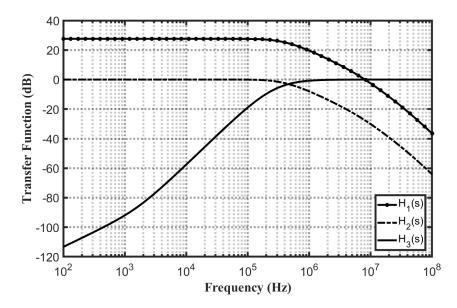

| Figure 4.17. Phase domain model of the AMASS PLL with noise sources of inter-<br>est.                                                                                          | 87 |

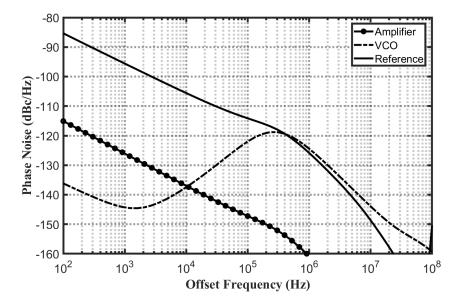

| Figure 4.18. The noise transfer functions of the prototype AMASS-PLL                                                                                                           | 87 |

| Figure 4.19. The simulated phase noise contribution of each block of the prototype AMASS-PLL.                                                                                  | 87 |

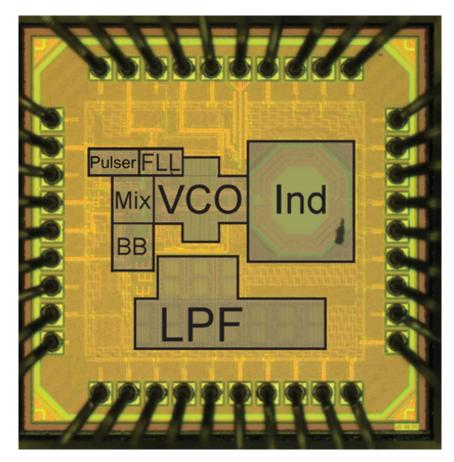

| Figure 4.20. A die photo of AMASS-PLL prototype                                                                                                       | 88  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

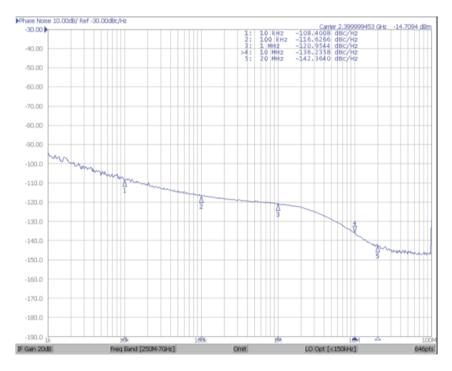

| Figure 4.21. The measured phase noise spectrum from Agilent E5052B Signal Source Analyzer                                                             | 89  |

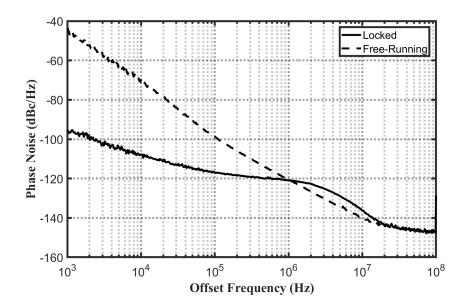

| Figure 4.22. The measured output phase noise under locked and free-running con-<br>ditions                                                            | 89  |

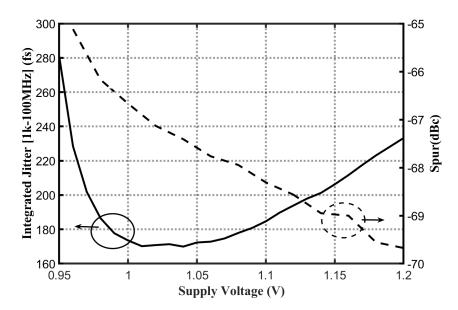

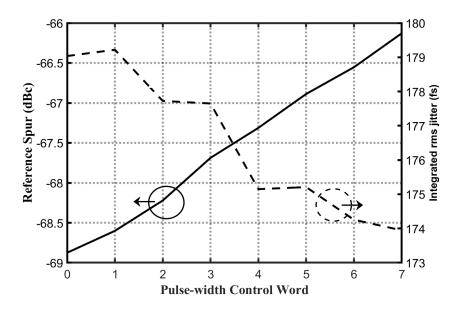

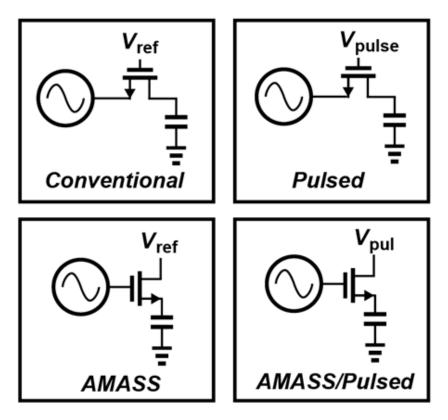

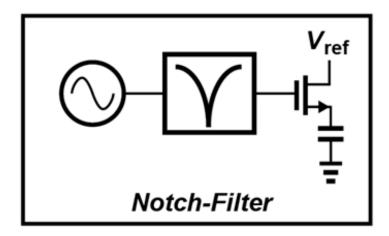

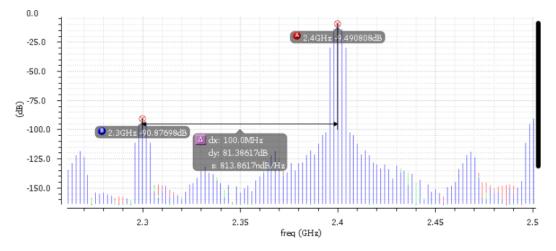

| Figure 4.23. The measured reference spur and integrated jitter versus the supply voltage                                                              | 90  |

| Figure 4.24. The measured reference spur and integrated jitter versus various reference pulsewidths                                                   | 90  |

| Figure 5.1. Illustration of sources of spur caused by the phase detector                                                                              | 92  |

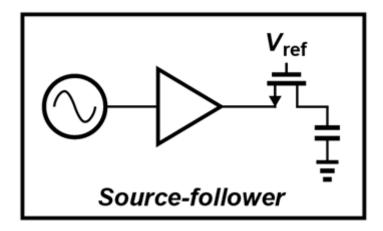

| Figure 5.2. Illustration of notch filter for charge injection mitigation.                                                                             | 93  |

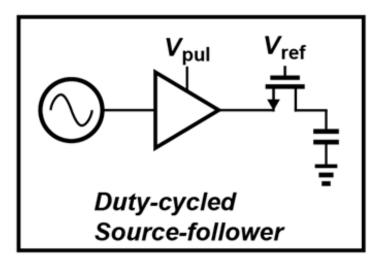

| Figure 5.3. Illustration of source follower to improve the isolation between the phase detector and the VCO.                                          | 94  |

| Figure 5.4. Illustration of duty-cycled source-follower to improve the power effi-<br>ciency of source-follower based isolation.                      | 95  |

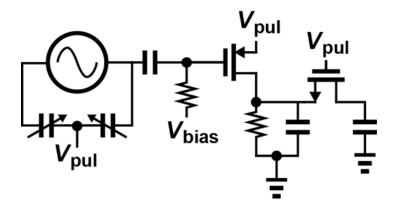

| Figure 5.5. Proposed varactor cancellation.                                                                                                           | 95  |

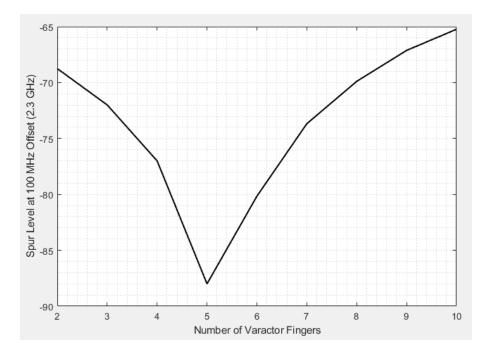

| Figure 5.6. Spur (dBc) versus the number of fingers per each varactor                                                                                 | 96  |

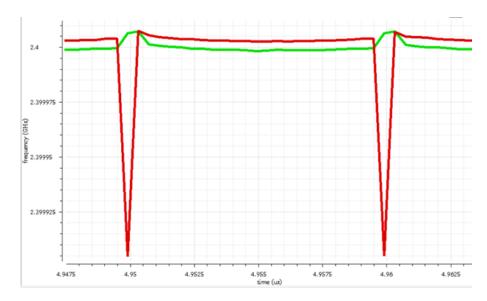

| Figure 5.7. VCO Instantaneous Frequency versus Time. Red curve is without the cancellation varactor and green curve is with the cancellation varactor | 97  |

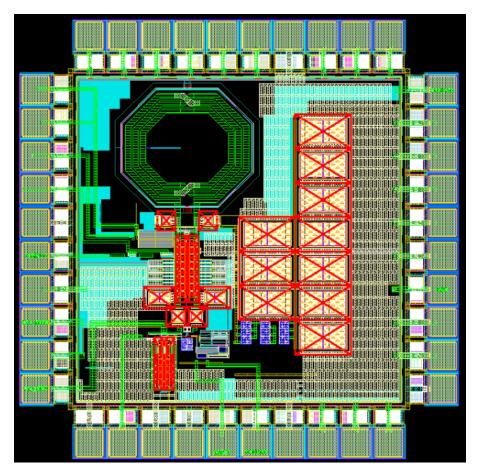

| Figure 5.8. Top level Layout View.                                                                                                                    | 98  |

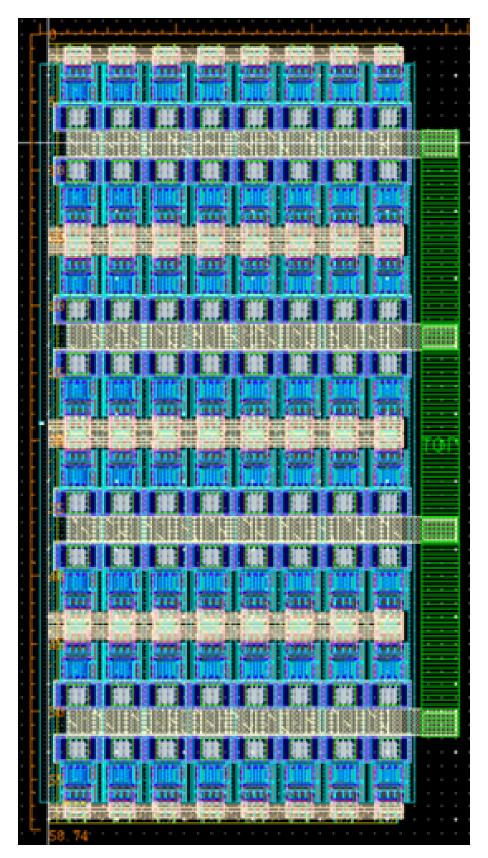

| Figure 5.9. Top level capacitor bank layout                                                                                                           | 99  |

| Figure 5.10. A Schematic of the AMASS-PLL                                                                                                             | 100 |

| Figure 5.11. The simulated output phase noise is shown.                                                                                               | 100 |

| Figure 5.12. DFT of the PLL output shows the simulated spur less than -80 dBc.                                                                        | 100 |

#### LIST OF TABLES

| Table 2.1. Table to test captions and labels                | 21 |

|-------------------------------------------------------------|----|

| Table 4.1. Comparison With State-of-the-Art Integer-N PLLs. | 77 |

#### ACKNOWLEDGEMENTS

I would like to express my sincere gratitude to my advisor Prof. Patrick Mercier for his continuous and unwavering support and guidance during my Ph.D study. His faith in me has resulted in the works presented here.

Besides my advisor, I would like to thank Prof. Laurence Milstein, Prof. Yonghan Kim, and Prof. Ian Galton for their insightful advice related to some of the works presented here.

I thank all of my fellow labmates for all the fun we had during my stay. Particularly, I would like to thank Cooper Levy, Po-yi Wu, Jiwoong Park, Chul Kim, and Hui Wang for their helpful technical discussions.

Last but not least, I would like to thank my parents for all that they have done for me, and my wife for her encouragement throughout my Ph.D study.

Chapter 1, in part, is a reprint of the material as it appears in D. Lee and P. P. Mercier, "Introduction to Ultra Low Power Transceiver Design." The dissertation author was the primary author of this paper.

Chapter 2, in part, is a reprint of the material as it appears in D. Lee and P. P. Mercier, "A 1.65 mW PLL-free PSK receiver employing super-regenerative phase sampling," 2015 IEEE Biomedical Circuits and Systems Conference (BioCAS), Atlanta, GA, 2015, pp. 1-4. The dissertation author was the primary author of this paper.

Chapter 3, in part, is a reprint of the material as it appears in D. Lee and P. P. Mercier, "Noise Analysis of Phase-Demodulating Receivers Employing Super Regenerative Amplification," in IEEE Transactions on Microwave Theory and Techniques, vol. 65, no. 9, pp. 3299-3311, Sept. 2017. The dissertation author was the primary author of this paper.

Chapter 4, in part, is a reprint of the material as it appears in D. Lee and P. P. Mercier, "AMASS PLL: An Active-Mixer-Adopted Sub-Sampling PLL Achieving an FOM of 255.5dB and a Reference Spur of 66.6dBC," 2018 IEEE Symposium on VLSI Circuits, Honolulu, HI, 2018, pp. 181-182. The rest of the chapter that is not part of

the reprint is in revision process for submission to Journal of Solid State Circuits. The dissertation author was the primary author of this paper.

Chapter 5, is a new and unpublished material. The material presented in this chapter is simulation only, and the fabricated silicon prototype is currently being characterized. The dissertation author was the primary author of this work.

#### VITA

| 2011 | B. S. in Electrical and Computer Engineering, Cornell University, Ithaca, NY.                             |

|------|-----------------------------------------------------------------------------------------------------------|

| 2019 | Ph. D. in Electrical Engineering (Electronic Circuits and Systems),<br>University of California San Diego |

#### PUBLICATIONS

D.-G. Lee, P.P. Mercier, AMASS PLL: An Active Mixer Adopted Sub–Sampling PLL with an FOM of –256 dB, in *IEEE Journal of Solid State Circuits*. (*in submission*).

D.-G. Lee, P.P. Mercier, AMASS PLL: An Active Mixer Adopted Sub–Sampling PLL Achieving an FOM of 255.5dB and a Reference Spur of 66.5dBc, in *Proc. IEEE VLSI Symposium*, Jun. 2018.

D.-G. Lee, P.P. Mercier, Noise Analysis of Phase-Demodulating Receivers Employing Super-Regenerative Amplification, *IEEE Transactions on Microwave Theory and Techniques*, vol. 65, no. 9, pp. 3299-3311, Sep. 2017.

D.-G. Lee and P.P. Mercier, A 1.65 mW PLL-free PSK Receiver Employing Superregenerative Phase Sampling, in *Proc. IEEE Biomedical Circuits and Systems Confer*ence, Oct. 2015.

D.-G. Lee, L.G. Salem, P.P. Mercier, Narrowband Transmitters: Ultra-Low-Power Design, *IEEE Microwave Magazine*, vol. 16, no. 3, pp 130-142, Apr. 2015.*Invited paper*.

#### ABSTRACT OF THE DISSERTATION

#### Energy Efficient Integrated Circuits for Low Power Wireless Communication Applications

by

Dhon-Gue Lee

Doctor of Philosophy in Electrical Engineering (Electronic Circuits and Systems)

University of California San Diego, 2019

Professor Patrick P. Mercier, Chair

Low-power wireless receiver design has been an active area of research during the last decade. One of the most difficult part of the design is generating a spectrally pure clock signal for demodulation in an energy efficient manner. The clock generation is usually done through either a phase-locked loop, and the energy cost of implementing a PLL is usually more power expensive than the the rest of the receiver. Therefore, the solutions thus far have been to use a simple modulation schemes such as On-Off-Keying(OOk). However, such modulation schemes are spectrally inefficient, and as the density of wireless devices grow larger, more stringent spectral efficiency will be demanded even for low-power applications. This dissertation presents a search for an alternative to an envelope-detector. We have investigated a PLL-less coherent detection, as well as an ultra-low power PLL for an alternative to an envelope detector. Chapter 1 describes the general link budget required for such low-power applications. Popular low-power receiver architectures are described in this chapter. Chapter 2 presents a PLL-

less receiver architecture that employs a super-regenerative oscillator as a phase storage element. The chapter details the system level and circuit design as well as the measurement results. Chapter 3 presents a mathematical model for super-regenerative reception of phase-modulated signal. The theoretical model needed to build the receiver presented in chapter 2 was not available at the time of the design. The authors investigated the behavior of super-regenerative receivers when it is used to receive phase-modulated signals employing modulations such as phase-shift-keying (PSK). Chapter 4 describes a low-power PLL architecture that is promising enough to meet both the power and the noise requirement of low-power wireless communication applications at 2.4 GHz. The in-band phase noise of sub-sampling PLL can approach the theoretical limit of the reference phase noise. However, SSPLL can suffer from a significant spurious tone. This chapter presents a sub-sampling PLL architecture that can lower the spurious tone significantly without relying on a power-expensive calibration scheme. Furthermore, the entire loop (except the oscillator) consumes less than 500 microwatts of power, and the total power consumption of the PLL is less than 1 mW, suitable for low-power wireless communication applications.

# Chapter 1

# Introduction

Recent advancements in integrated radio design have enabled many new applications ranging from wearable healthcare or fitness monitors to Internet of Things (IoT) devices, structural integrity monitors, and beyond. In many of these applications, device size and battery life are of critical importance. Since radios often consume a significant portion of the power budget in small sensing nodes [7], reducing radio power consumption can be an impactful way to effectively decrease device size or increase operational lifetime. Reducing radio power can, however, be challenging, as there are important tradeoffs between power consumption and performance metrics such as radiated output power, linearity, sensitivity, channelization capabilities, and interference sensitivity. Low-power radio designs often sacrifice one or more of these metrics in the pursuit of low overall power consumption. The purpose of this chapter is to briefly introduce the main challenges facing narrowband ultra-low-power (ULP) RX design.

## **1.1 Link Budgeting**

*Wireless sensor networks* (WSN) and *body area networks* (BAN) are two common areas that generally require short-range ULP transceivers. The purpose of this section is to briefly review path loss models and link budgets for these representative applications to derive minimum required output power.

To come up with a general WSN link budget, consider a representative WSN system operating with a carrier frequency of 2.4 GHz at a communication distance of 10 m. Most WSN nodes operate in peer-to-peer ad-hoc networks, where each node can

potentially act as a relay between other nodes. Consequently, WSN transceivers must balance power specifications evenly between transmit and receive modes in order to optimize system-level energy efficiency. As a result, receivers are typically designed to have an input sensitivity close to -90 dBm. The minimum transmitter output power can then be calculated by preparing a link budget using the Friis equation for free space as a baseline case:

where  $\lambda$  is the carrier wavelength and D is the distance between nodes. This equation tells us that, in free space, a 10 m link suffers from 60 dB of path loss at 2450 MHz. A typical surface-mount antenna at 2450MHz has a gain of 0 dBi, which leads to the minimum transmit power of -30 dBm under ideal condition. However, a WSN transceiver working in a hostile environment could experience as much as 30 dB of additional loss, for a total of 90 dB of path loss [8]. Therefore, a WSN transmitter should have a maximum output power of 0 dBm, our definition of a ULP transmitter.

On the other hand, BAN applications have much lower transmission distances: 1-2 m is often sufficient to communicate information around the human body. This should theoretically result in a lower path loss than in WSNs: 40-46 dB in free space at 2.4 GHz. Unfortunately, the presence of the human body in BANs adds significant attenuation, resulting in a measured path loss that range from 40 to 80 dB [9]. As an added complication, this path loss is highly variable and depends not only on the carrier frequency and the distance between nodes, but also on the relative position of the body and its surrounding environment [9]. Fortunately, the frequency of this variation is limited by the response time of a human (hundreds of milliseconds), enabling relatively lowcomplexity automatic gain control loops to compensate for such variation. Additionally, while the channel itself has high losses, it can generally be modeled as a non-frequency selective channel with no resolvable multipath, eliminating the requirement for complex multipath cancellation schemes [10]. Other studies have shown slightly lower path loss results (by 10-15 dB) at 900 MHz and 400 MHz [11] as a result of lower tissue conductivity and higher relative permeability. Operating at these frequencies, however, reduces the radiation efficiency of electrically small antennas, which may negate the path loss

advantage when computing the system-level energy efficiency. As a result, there is no clear rule-of-thumb regarding carrier frequency selection in BANs, as the available size and location of the antenna affects this decision dramatically.

To calculate the generally required PA output power range in a BAN, we first exploit a natural property of the system: most BAN users will be wearing a smartphone or smartwatch platform that is energy-rich, at least in comparison to a wearable or implantable sensor node. Thus, we can utilize these smart de-vices in an energyasymmetric star topology network, where the smart watch/phone platform acts as a highly-sensitive centralized base-station. Assuming a base-station receiver sensitivity of -100 dBm, as typically encountered in commercial Bluetooth receivers, along with path loss of 40-80 dB and 10 dB link margin, the most efficient PA implementation would dynamically alter its output power between -10 dBm and -50 dBm depending on instantaneous channel conditions; -10 dBm is also the recommended transmit power according to IEEE802.15.6 BAN standard [12].

To put these number in perspective, recall that -10 dBm corresponds to 100 W output power. It is very challenging to design all downstream blocks to consume well under 100 W in order to limit the overall system power con-sumption. The rest of this chapter will thus review architectures and circuits that help address this problem.

### **1.2 Low Power RX Architectures**

The power consumption of a receiver (RX) is highly influenced by the modulation scheme chosen, which then defines the overall receiver architecture. Receivers can be broadly categorized by the following demodulation schemes:

Clocked demodulation. Broadly, RF energy is first mixed down to a lower frequency (or two) before demodulation occurs. In general, a low-phase noise LO is desired, though not strictly required. This category can be further subcategorized into the following architectures:

- (a) Super-heterodyne/heterodyne RX. Although the traditional dual down-conversion architecture is extremely robust, as seen in Figure 1 it requires two LOs and an additional mixer and thus has difficulty achieving ULP operation. Section 1.3 discusses several techniques to minimize the power consumption in such architectures.

- (b) Homodyne (zero-IF) RX. It is generally more energy-efficient to operate at baseband than at RF, and for this reason, homodyne architectures save power by directly down-converting the input signal to baseband. However, homodyne receivers are well-known to suffer from DC offsets, flicker noise, LO leakage, and other issues. Thus, low-power methods to address these issues are required, several of which are also discussed in Section 1.3.

- 2. Energy/Envelope detection. A PLL can be amongst the most power hungry blocks in ULP receivers, and as a result, receiver architectures that eliminate the requirement of a PLL can more easily achieve ULP operation. Eliminating the PLL, however, generally either reduces LO precision, making coherent demodulation difficult, or through high-Q resonators precludes multi-channel operation. Instead, it is possible to perform non-coherent demodulation by observing the signals energy level either directly at RF, or after down conversion to an imprecise intermediate frequency. Naturally, doing so relies on less spectrally efficiency modulation schemes (e.g., OOK), and has difficulty dealing with blockers. Section 1.4 describes methods to perform envelope/energy detection in more detail.

- 3. Super-regenerative receiver. A super-regenerative receiver (SRR) achieves ultrahigh gain using a low-complexity unstable network in an efficient and controlled manner. While most SRRs indeed have envelope/energy detectors, SRRs have sufficiently different requirements to consider them separately. Section 1.5 describes the basic operation of a super-regenerative receiver and presents examples from the recent literature.

# **1.3 Clocked Modulator**

The power consumption of a receiver is normally dominated by frequency synthesis, RF amplification, and the LO buffer. Although the dual down-conversion architecture is very robust for demodulating data while rejecting unwanted signals, the requirement of multiple down-conversion mixers and two reference signals is often prohibitively expensive from a power perspective in ULP applications. Consequently, low-IF and zero-IF architectures have gained popularity in ULP radio design due to their low implementation complexity (i.e., the minimal number of blocks that consume power). Image rejection problems associated with low-IF receiver architectures can be solved by using high-Q resonators as image rejection filters. Furthermore, certain low power standards, such as ZigBee, require very loose specifications of image rejection and channel filter [13], potentially saving implementation complexity, though at the expense of an increased chance of interference. Additional power can be saved by adopting simpler modulation schemes such as OOK, FSK, and low-index PSKs, though at the expense of reduce spectral efficiency. While such system-level simplifications can decrease power consumption, they may not be sufficient to meet ULP power budget constraints. Thus, efforts have been made to further lower the power consumption in such architectures by replacing a PLL with a clever method of frequency synthesis [1], [14], lowering the supply voltage [15], [16], [17], and replacing the LNA with a passive mixer front end [15].

Figure 1.1 shows an example of a representative FBAR-based multi-channel super-heterodyne receiver architecture [1]. Here, multi-channel operation has been achieved by first down-converting the whole channel band to a wideband IF (5 to 80 MHz), while using multiple frequency dividers driven by the resonator in order to define all necessary channels in the 2.4 GHz ISM band, as illustrated in Fig 9.

Figure 1.1: PLL-less FBAR-based Super-heterodyne RX schematics [1]

# **1.4 Energy/Envelope Detector-based RX**

The high power consumption associated with coherent demodulation often steers designers to choose simpler non-coherent modulation scheme such as OOK or FSK at the cost of reduced spectral efficiency. Energy or envelope detector-based receiver architectures further save power consumption by removing the need for an accurate high frequency clock. The key difference between energy and envelope detection is whether using a self-mixer or an envelope detector, where the former implements an actual square operation.

Figure 1.2: Schematics of envelope-detector-based RX frontend

Figure 1.2 shows a schematic of a generic envelope-detector-based receiver. Envelop and energy detectors generally offer extremely low-power operation compared to all other demodulators, though they suffer from poor blocker rejection and SNR due to translation of blockers to DC and minimum detectable signals set by non-linear elements. These problems can potentially be mitigated by using a 2-tone modulation scheme with a high-gain LNA [2], or by using an uncertain-IF architecture [18]. An example 2-tone receiver architecture is shown in Figure 1.3. Unlike a traditional envelope detector that down-converts any signal (potentially including interferers) to DC, in a 2-tone system the signal is transmitted at two separate frequencies with a known frequency offset, such that the intermodulation between these two signals lies at a known-IF, which can then be filtered and demodulated with substantial blocker rejection. The implementation in [2] uses the best phase-aligned LO signal amongst 8 phases in order to demodulate the signal without using a quadrature path.

Figure 1.3: Schematics of 2-tone FSK receiver [2]

An uncertain-IF architecture utilizes an imprecise and thus power-efficient LO (e.g., a ring oscillator) to down-convert the desired signal to a wide, uncertain IF to take advantage of the large gain attainable at such frequencies. However, down-conversion introduces image, and a high-Q RF filter, such as bulk acoustic wave resonators (BAW), must be used as image rejection filters [18], which in some cases may be cost or area prohibitive.

# **1.5 Super-regenerative Receiver**

Super-regenerative receivers (SRR) use an oscillator with a variable bias current to steer the two complex poles of the oscillator from the left half plane s-plane to the right half plane, effectively oscillating and quenching the system in a non-linear fashion. During the start-up of the super-regenerative oscillator (SRO), any small signal and noise in the vicinity of the oscillators natural frequency is exponentially amplified, thereby achieving enormous gain - much higher gain than an open loop amplifier. A representative SRR is shown in Figure 1.4. Most SRRs use an envelope detector to demodulate OOK or other amplitude modulated signals. Unlike other envelope-detector-based receivers, an SRR can have an arbitrarily large gain (limited by the quench period and power supply rail) and does not nominally suffer from an envelope detectors low detection threshold. While super-regenerative amplifiers achieve the largest gain-to-current ratio of any competing amplifier topology by exploiting the positive feedback growth characteristics of a building oscillation, any blocker in a nearby channel can force an oscillation independent of the presence of a signal at the desired band. Consequently, SRR architectures are very susceptible to blockers, and the susceptibility is inversely proportional to the rate at which the transconductance of the oscillator, or the quench signal, grows [19]. An effort has been made to mitigate this problem at the cost of additional complexity and data rate by calibrating the quench signal with a digital feedback loop as shown in Figure 1.4 [3].

## **1.6 Summary of dissertation**

Ultra-low-power narrowband radios can open up many unique applications ranging from Internet-of-Things and industrial sensor networks, to wearable sensors, healthcare devices, and beyond. Achieving ultra-low-power con-sumption while maintaining robust operation involves difficult trade-offs be-tween output power, data rate, bandwidth, channel selectivity, sensitivity, and energy efficiency that must be overcome

Figure 1.4: Schematics of super-regenerative receiver with BW calibration [3]

through a combination of innovative circuit design, novel architectures, and systemlevel considerations. This chapter has introduced typical architectures used in ULP radios, discussed their relative merits, and provided some benchmarking data to help identify what architectures might make the most sense given system-level specifications. While optimal implementations depend strongly on the given application, in general the most efficient radios employ low-complexity modulation schemes (e.g., OOK, FSK, and possibly BPSK), and are run by an efficient LO stabilized without a PLL.

This dissertation consists of two main parts. The first part of the dissertation focuses on super-regenerative receivers. In chapter 2, a novel way to use a super-regenerative amplifier as a phase storage device is presented. In chapter 3, a mathematical analysis of the noise behavior of the non-linear and time-variant system when SRAs are used to demodulate phase rather than amplitude is present to help analyze systems such as shown in chapter 2. In the second part of the dissertation, an energy-efficient way to build a PLL for low-power wireless communication is presented. Chapter 4 describes the analysis and design of a sub-sampling PLL architecture that reduces the reference spur without relying on PVT-sensitive techniques. Chapter 5 describes an improvement of the PLL architecture shown in chapter 4 that further reduces the spur by more than 15 dB in simulation.

# 1.7 Acknowledgement

Chapter 1, in part, is a reprint of the material as it appears in D. Lee and P.P. Mercier, "Introduction to Ultra Low Power Transceiver Design," in: P.P. Mercier and A. Chandrakasan, "Ultra-Low-Power Short-Range Radios. Integrated Circuits and Systems." Springer, 2015. The dissertation author is the primary author of this paper.

# Chapter 2

# A 1.65 mW PLL-free PSK Receiver Employing Super-regenerative Phase Sampling

*Abstract* - This chapter presents a 1.65 mW low-power receiver that uses a superregenerative oscillator (SRO) to replace power hungry phase lock loops (PLLs) that are conventionally required for phase-demodulation. It is shown that operating an SRO in the amplification mode preserves the phase of incoming RF signals, and thus an SRO is used to periodically sample the phase of two incoming training bits, after which the SRO operates as a local oscillator for a super-heterodyne receiver. Operating at 0.5 V in a 0.18 m process, the receiver achieves -70 dBm of sensitivity at BER of 1e-3 when demodulating an 800 kbps BPSK signal without a PLL.

### 2.1 Introduction

The growing interest in wearable health and fitness devices such as smartwatches and medical patches require low power wireless radios that can employ spectrally efficient modulation schemes. For example, a 128- electrode EEG system sampling at 1 kS/s with >16 bits of resolution has a raw data rate requirement of >2 Mbps. In the congested 2.4 GHz band, where channel bandwidths are limited to 1 MHz and interference with other standards should be avoided at all costs, modulation schemes such as PSKs and QAMs are required. While Bluetooth v2.0 support maximum data rate of 3 Mbps for  $\pi$ /4-DQPSK and 8-DPSK, the power consumption of such radios is large in

Figure 2.1: Overview of the proposed phase-sampling system.

part due to the requirement of a phase locked loop (PLL), which have difficulty scaling below 1 mW at 2.4 GHz [20], and further have long start-up times that make aggressive duty-cycling for low average power operation difficult.

On the other hand, most low power radios in the current literature only employ schemes such as OOK and FSK due to their low-complexity/low-power implementations [21]. Unfortunately, such low-order modulation schemes are spectrally inefficient and cannot support the high required data rates in the allocated channel bandwidths at 2.4 GHz. The next generation of wearable and medical applications must thus find a way to support higher order modulation schemes at low instantaneous power.

In this chapter, we propose a new PSK receiver architecture that can demodulate phase information without the use of a PLL, thereby enabling ultra-low-power operation. Here we exploit the fact that many wearable biomedical applications operate in an energy-asymmetric star network where a comparatively energy-rich basestation (e.g., smartphone) can easily afford a highly-accurate frequency synthesizer for its transmitter. Transmitted information is thus frequency-stabilized, which can be leveraged at the receiver for in-time calibration of a low-power LO. While prior work has exploited transmitted frequency-stabilized signals to periodically calibrate a PLL [22], the power and slow start-up drawbacks of PLLs remain.

## 2.2 Architecture Overview

To minimize power and enable rapid duty-cycling, the proposed architecture, shown in Fig. 2.1, utilizes a superregenerative oscillator (SRO) to first amplify two frequency-stabilized training symbols, and then transition to an oscillatory mode where the phase of the oscillator is matched to the incoming training symbols. At this point, the temporarily-stabilized SRO with known phase characteristics acts as an LO for a super-heterodyne receiver. Since the power consumption of an SRO is only marginally higher than a conventional VCO, and no frequency dividers, phase detectors, or loop filters are required, the power overhead of stabilizing the LO can be substantially reduced compared to prior-art.

Naturally, the SRO can only hold its sampled phase and frequency for so long, and thus n training symbols must be transmitted between every m data symbols. It has been shown that the frequency drift of a VCO can be minimized at 2.5 Hz/ $\mu$ s for a low-voltage multi-gigahertz design in modern CMOS processes [23], which is more than sufficient to demodulate upwards of m = 8 symbols of data at 1 MSps with n = 2. As opposed to a free-running oscillator, the phase sampling oscillator is periodically quenched to mitigate the effects of frequency drift and accumulated jitter, which typically limits D-BPSK systems to have m close to 8.

The phase-sampling receiver architecture, illustrated in Fig. 2.2, operates as follows. A low-noise amplifier (LNA) amplifies incoming RF energy at 2.2 GHz, and drives two time-sequenced buffers. During training, the path selection signal is low and the bottom buffer is turned on, mixing incoming RF energy with a 32 MHz reference to generate a 2.232 GHz signal that is injected into the phase-sampling SRO. The SROs bias current is then ramped-up via a linear quenching function, exploiting the positive-feedback properties of super-regenerative architectures to realize enormous gain. Figure 2.3 illustrates timing diagram of the control signals and the output of the SRO. Though SROs are generally used as high-gain blocks in non-coherent radios, it can be shown that an SRO preserves the phase information of a signal that is injected during the start-up

Figure 2.2: Block diagram of the phase-sampling receiver.

of oscillation, as illustrated by simulation results in Fig. 2.4. Thus, when the SROs bias current reaches its maximum value, the SRO enters an oscillatory mode that is phase matched to the incoming RF signal, mixed up by 32 MHz to avoid frequency-pulling.

Figure 2.5 shows the quality of phase sampling as a function of SNR over the bandwidth of the SRO. The bandwidth of the SRO is proportional to the slope of the ramp quenching function. An SNR greater than 13 dB is necessary for good quality phase sampling (i.e., this would result in BER of 1e-4 when demodulating a noiseless signal).

Once the phase of the injected signal is successfully sampled, training is complete and the path selection signal is asserted, turning off the SRO buffer and upconversion mixer, thereby achieving 40 dB of isolation between the LNA and SRO while saving 0.3 mW of power. At this point, the top path is turned on and operated as a super-heterodyne receiver using the SRO as an LO. The quadrature mixer then enables demodulation of BPSK, QPSK, and QAM signals. Once all data symbols following the training symbols are demodulated, the SRO is quenched, and new training symbols are sampled. Figure 2.6 shows that the number of errors begins to rise 8-10 symbols after

**Figure 2.3:** Simulation result of phase sampling SROs output waveform given 100 nA inputs of 4 different phases.

the training symbols. Thus, in this work the system is quenched after demodulating m = 8 symbols.

## 2.3 Circuit Implementation

#### 2.3.1 LNA, RF buffers, and down-conversion mixer

A singled-ended inductively degenerated common source LNA and a singlebalanced active mixer are employed for their low power consumption. The LNAs simulated noise figure is 3.8 dB. Schematics are shown in Fig. 2.7. The gate, source, and load inductors are all implemented with on-chip inductors. The LNA is followed by two parallel cascode RF buffers used to isolate the output of the LNA from frequency pulling the SRO. As mentioned previously, only one of the two buffers is turned on at all times in order to provide maximum isolation and minimum power consumption.

Figure 2.4: Timing diagram of control signals and the output of the SRO.

#### 2.3.2 SRO and Up-conversion Mixer

Figure 2.8 shows the circuit implementation of the SRO and its preceding upconversion mixer. The periodic ramp function is input into the NMOS current bias transistor to control the SROs bandwidth and quenching rate. A 13-bit digital capacitor bank is used to tune the center frequency of the oscillator across approximately 100 MHz of bandwidth. A switch-capacitor-based digital capacitor bank is used to implement the 9 LSBs [24]. In order to save power, the mixers LO is grounded through a digital MUX during the demodulation phase and is only turned on while sampling the phase.

## 2.4 Experimental Results

The phase-sampling receiver was implemented in 0.18  $\mu$ m CMOS SOI process and measured in a Quad Flat Noleads (QFN) package; a die photo is shown in Fig. 2.9. RF performance was characterized by inputting a pseudorandom data sequence into the

Figure 2.5: Simulated phase variance versus SNR of the SRO.

Figure 2.6: Measured number of errors for each bit after the training bit.

chip using a vector signal generator at 2.2 GHz. Due to unintended layout mismatch of the quadrature oscillator, Q channel data was not available during measurement of the fabricated chip. Consequently, while the receiver was intended for demodulating QPSK signals, only BPSK demodulation was tested in this prototype.

The transient waveform of the I-channel during BPSK demodulation is shown in Fig. 2.10. After two symbol periods, the phase is sampled onto SRO, and 8 symbols are subsequently demodulated. The SRO is then quenched after demodulation, and a new 10-symbol cycle is started. Each cycle is 10 microsecond, so that the effective data rate is 800 kbps.

Figure 2.7: Schematics of LNA, RF buffers, and active down-conversion mixer.

The measured BER versus input power is shown in Fig. 2.11, illustrating a -70 dBm sensitivity. Due to a higher than expected parasitics, the super-regenerative oscillator operated at 2.2 GHz instead of its optimal frequency of 2.4 GHz. Consequently, the rest of the RF blocks operated at 2.2 GHz, which led to a degradation in sensitivity due to operation beyond the nominal bandwidth of the designed amplifiers. In order to compensate for the reduced gain, which according to simulations is 6.58 dB away from the nominal tuning range, the power of the LNA and RF was increased: instead of 500  $\mu$ W, the LNA and RF buffers together consumed 1.22 mW in measurement to increase the gain of the LNA by approximately 6 dB. The baseband circuitry consumed 0.2 mW while the phase sampling SRO consumed 0.41 mW. Digital circuits consume 29.5  $\mu$ W. The performances of the phase-sampling SRO receiver are summarized and compared to prior-art in Table 2.1. Even though the gain was degraded via frequency mismatch and power was increased to compensate, the chip still achieves performance comparable to, and in some cases exceeding, prior-art, thereby demonstrating that a phase-sampling SRO can be used as a low power alternative to a PLL for coherent detection while con-

Figure 2.8: Schematics of the SRO (left) and the up-conversion mixer (right).

suming less power.

### 2.5 Acknowledgement

Chapter 2, in part, is a reprint of the material as it appears in D. Lee and P. P. Mercier, "A 1.65 mW PLL-free PSK receiver employing super-regenerative phase sampling," 2015 IEEE Biomedical Circuits and Systems Conference (BioCAS), Atlanta, GA, 2015, pp. 1-4. The dissertation author was the primary author of this paper.

Figure 2.9: Chip microphotography of the receiver.

Figure 2.10: Transient waveform of the receivers I channel output.

Figure 2.11: Measured Input Power versus BER

| Comparison of the Measured Performance of Low Power Receivers |           |              |            |           |

|---------------------------------------------------------------|-----------|--------------|------------|-----------|

|                                                               | TCAS '12  | ISSCC [26]   | ISSCC'14   | This Work |

|                                                               | [25]      | '11          | [27]       |           |

| Technology                                                    | 0.18 μm   | 90 nm        | 90nm       | 0.18 μm   |

| Sensitivity (dBm)                                             | -65       | -75          | -92        | -70       |

| Data Rate (kbps)                                              | 1000      | 5000         | 2000       | 800       |

| Architecture                                                  | Carrier   | Super-       | Sliding-IF | Phase-    |

|                                                               | Recovery  | regenerative | Phase-to-  | Sampling  |

|                                                               | Loop      | Receiver     | Digital    | SRO       |

| Total Power                                                   | 20.4 mW   | 0.534mW      | 2.4 mW @   | 1.6 mW @  |

|                                                               | @ 1.8 V   | @ 1.2 V      | 1 V        | 0.5 V     |

| PLL Power                                                     | None      | 1.098 mW     | 0.550 mW   | None      |

| Receiver Power                                                | 20.4 mW   | 0.534 mW     | 1.85 mW    | 1.6 mW    |

| Modulation                                                    | QPSK      | OOK          | HS-        | DBPSK     |

|                                                               |           |              | OQPSK      |           |

| Energy-per-bit                                                | 20.4 nJ/b | 0.1 nJ/b     | 1.2 nJ/b   | 2 nJ/b    |

| PLL                                                           | None      | For Cali-    | Yes        | None      |

|                                                               |           | bration      |            |           |

Table 2.1: Table to test captions and labels

### Chapter 3

# Noise Analysis of Phase-Demodulating Receivers Employing Super-Regenerative Amplification

*Abstract* - Growing interest in ultra-low-power RF receivers has reinvigorated research in super-regenerative amplifier (SRA) architectures, in part due to their ability to achieve enormous gain at very low power. Conventionally, SRAs have been paired with envelop detectors that demodulate amplitude-modulated signals (e.g., OOK); mathematical models have been developed to predict the performance of such systems. Since modern communication applications require more spectrally-efficiency modulation schemes, this chapter develops a mathematical model that predicts the stochastic behavior of SRAs when used in phase-demodulating receivers. This stochastic model is then used to predict the sensitivity of a phase-demodulating receiver employing a Colpitts-based SRA. Results from the developed model are validated with measurements of a discrete prototype, illustrating that SRAs can be used with I/Q mixing to demodulate quadrature phase-shift keying (QPSK) signals with -88 dBm sensitivity when the SRA consumes 1.2 mA at 1.5 V at 45 MHz.

### **3.1** Introduction

Super-regenerative amplifier (SRAs) are known to have excellent gain and sensitivity while consuming minimal DC power. Invented by Armstrong in 1922 [28], superregenerative radio frequency (RF) receivers were briefly popular due in part to their ability to achieve large gain from a single active element. Until the superheterodyne architecture supplanted SRA-based receivers due to their superior channel selectivity and limited self-radiation, SRAs were conventionally deployed with envelope detectors to demodulate amplitude modulation (AM) signals. The recent demand for low-cost and low-power wireless communication systems has re-energized research and development of SRA-based receivers for the same reasons they were popular in the early 1900s: their ability to attain large gain and high sensitivity at low power. However, most modern designs employ SRAs in essentially the same way they were employed in the 1920s: as a high-gain RF amplifier, followed by envelope detection of amplitude-modulated signals such as on-off keying (OOK) [19, 29–33].

Interestingly, there is no fundamental reason why SRAs can only be used along with amplitude demodulation hardware like envelope detectors. In fact, recent work has shown that SRAs can be used in receivers that demodulate frequency shift keying (FSK) signals [34, 35] or phase shift keying (PSK) signals with a conventional I/Q architecture as depicted in Figure 3.1 [36–39]. This is an important development, as many emerging wireless applications require communication with higher-order modulation schemes such as PSK and quadrature amplitude modulation (QAM) schemes. However, while the general theory of super-regenerative reception of OOK has been well analyzed in [18] and augmented in [40] and [41], noise analysis of SRAs in phase demodulating receivers has not yet been presented in the literature.

As a result, the primary purpose of this chapter is to present and experimentally verify a mathematical model of the noise performance of SRAs when used in phase demodulating systems. Leveraging either a conventional frequency-domain stochastic model [40], or a new time-domain stochastic model developed in Appendix A of this chapter, it is shown that the output noise of an SRA can be translated into the variance of the output phase by deriving the probability density function of the phase of the output waveform. The probability density function is then used to find the relationship between the noise figure of an SRA and the bit error rate when used with an m-ary PSK demodulator. Lastly, a discrete prototype of an SRA based on a Colpitts oscillator is

**Figure 3.1:** A representative PSK receiver architecture employing super-regenerative amplification.

designed in order to validate the theoretical model with experimental results.

The chapter is organized as follows. Section II briefly summarizes the general theory of super-regenerative reception [18] and the result of frequency-domain sensitivity analysis [40]. Section III leverages this prior analysis to develop a model that predicts output phase variance, which is then used to perform sensitivity analysis of QPSK reception. Section IV considers the design of a discrete SRA that can be employed in phase-demodulating receivers, while Section V presents the testbench and measurement result used to validate the developed theoretical work.

The analysis presented in this chapter, along with prior work on this topic, assumes that noise sources in SRAs are time-invariant. Since this is not actually true, this chapter also includes the development of a new time domain model that enables inclusion of time-varying noise sources. This new model is presented in Appendix A, and shows that the time-invariant assumption is indeed satisfactory for most practical data rates.

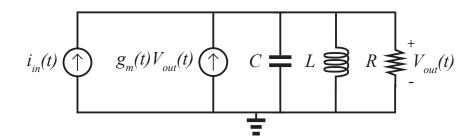

Figure 3.2: One port oscillator circuit model of SRAs.

### **3.2 Overview of General Super-Regenerative Theory**

Much of the work presented in this chapter require a basic understanding of existing SRA theory [18,40]. The primary purpose of this section is to briefly overview general SRA theory and notation that will be used in later sections.

#### **3.2.1** One Port Oscillator Model

A super-regenerative amplifier is, at its core, an oscillator that is periodically switched on and off between a high-gain start-up phase and a steady-state oscillatory phase. An example of a single-port *RLC* model is shown in Figure 3.2, with a timevarying transconductance  $g_m(t)$  modeling an active element that periodically turns on and off.

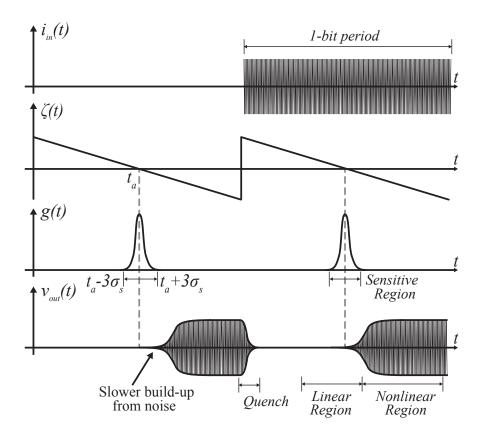

The typical behavior of an SRA is illustrated in Figure 3.3. During a single bit period,  $g_m(t)$  is gracefully modulated from a value below 1/R, where no oscillations should occur, to a value above 1/R, where oscillations should occur at steady state. This modulation is typically described by a *damping function*,  $\zeta(t)$ . In this chapter a ramp damping function is used throughout, and is given by:

$$\zeta(t) = \zeta_0 (1 - g_m(t)R), \qquad (3.1)$$

where  $\zeta_0$  is the *quiescent damping factor*. When the damping function crosses zero, the

Figure 3.3: Illustration of the operation of an SRA.

amplifier becomes unstable, and its output envelope grows exponentially until it reaches non-linear compression and, eventually, steady-state oscillation.

For a critical period of time around the zero crossing of  $\zeta(t)$ , the SRA coherently responds to the input RF waveform, serving as a high-gain amplifier. Thus, if an RF signal is present, the input will help excite resonance, serving to build up oscillation quickly. If no RF signal is present, non-coherent noise is responsible for activating oscillation, which is a process that takes longer. RF amplitude information is thus measured by the time it takes to initiate oscillation. Once the oscillation is well established, the SRA no longer strongly responds to changes in input signal, and thus the SRA is rapidly quenched.

# **3.2.2** Solution of the Differential Equation for the Linear and Time-Variant Model

SRAs can generally be operated in one of two modes: *linear* or *logarithmic* [18,40,42]. When the output of an SRA remains small enough throughout each quench cycle to not be compressed, the SRA is said to be in linear mode. If the SRA output is left on long enough to the point of compression, the SRA is said to be in the logarithmic mode. Fortunately, it has been shown that, when ignoring noise, the phase of the output is nominally preserved in either mode of operation [41]. Since this chapter is focused on using SRAs in phase demodulating receivers, it is thus reasonable to assume a linear and time-variant SRA model without a loss of generality. It is worth noting, however, that non-linearity in the system may cause non-constant envelope signals to affect the output phase slightly. However, the nature of non-constant input power is usually not random (and often changes more slowly than the data rate of the radio), and can be calibrated by a separate circuit if there is a need.

A  $2^{nd}$  order differential equation describes the linear time-variant one-port oscillator model in Figure 3.2:

$$v_{out}''(t) + 2\zeta(t)\omega_0 v_{out}'(t) + \omega_0^2 v_{out}(t) = 2R\zeta_0 \omega_0 i_{in}'(t).$$

(3.2)

The solution to the differential equation is given in [18,40] as:

$$v_{out}(t) = Z_0 \mu(t) k(t), \qquad (3.3)$$

where  $\mu(t)$  and k(t) are the *SRA gain* and the *filtering* term respectively, which are described as follows:

$$\mu(t) = e^{-\omega_0 \int_{t_0}^t \zeta(\lambda) d\lambda}$$

(3.4)

$$g(t) = \mu(t)^{-1} = e^{\omega_0 \int_{t_0}^t \zeta(\lambda) d\lambda}$$

(3.5)

$$k(t) = \int_{t_0}^t i'_{in}(\tau)g(\tau)sin[\omega_0(t-\tau)]d\tau.$$

(3.6)

In this case, time t is defined to be zero at the zero crossing of  $\zeta(t)$  and  $t_0$  is the initial time of a symbol period.

The reciprocal of SRA gain is termed the *sensitivity function*, g(t), which is only measurably non-zero during a finite window of time near the zero-crossing of  $\zeta(t)$ . The SRA is only sensitive to the input signal during the period of time when g(t) is large.

Note that k(t) is the only portion of the output,  $v_{out}(t)$ , that is a function of the input current, whereas the SRA gain  $\mu(t)$  is determined only by the circuit parameters and is independent of input current. For this reason,  $\mu(t)$  can be neglected during SRA noise analysis.

If the damping function  $\zeta(t)$  is a linear ramp function such that:

$$\zeta_{ramp}(t) = -\beta t, \tag{3.7}$$

then the SRA gain and the sensitivity function can be described as follows:

$$\mu_{ramp}(t) = e^{\omega_0 \int_{t_0}^t \beta \lambda \ d\lambda} = e^{\frac{t^2}{2\sigma_s^2}}$$

(3.8)

$$g_{ramp}(t) = e^{-\omega_0 \int_{t_0}^t \beta \lambda \ d\lambda} = e^{-\frac{t^2}{2\sigma_s^2}},\tag{3.9}$$

where  $\sigma_s$  is the *SRA time constant*. Here, g(t) approaches its peak value as the  $\zeta(t)$  tends to zero.

#### **3.2.3 Frequency Domain SRA Noise Model**

The output of an SRA is typically sampled when sufficient time has passed from the sensitivity window in order to benefit from the exponential growth of voltage waveform. Therefore, the filtering term k(t) in (3.6) can be approximated by the following convolution:

$$k(t) \approx \int_{-\infty}^{\infty} i'_{in}(\tau) g(\tau) \sin[\omega_0(t-\tau)] d\tau, \qquad (3.10)$$

or

$$k(t) \approx x(t) * \sin[\omega_0 t], \qquad (3.11)$$

where

$$x(t) = i'_{in}(t)g(t).$$

(3.12)

The output voltage under this approximation is given by:

$$v_0(t) = Z_0 \mu(t) |X(\omega_0)| \sin(\omega_0 t + \angle X(\omega_0)),$$

(3.13)

where  $X(\omega)$  is a Fourier transform of x(t).

The convolution approximation of the SRA model makes it easy to analyze its response to noise in the frequency domain. If the input to the SRA is additive white Gaussian noise (AWGN) with the power spectral density (PSD)

$$I_n(\omega) = \frac{N}{2},\tag{3.14}$$

then according to (3.12), x(t) is a convolution of the derivative of the input noise and the sensitivity function g(t). The Fourier transform of x(t) is then:

$$\overline{|X(\omega)|^2} = \frac{N\omega^2}{4\pi} * |G(\omega)|^2.$$

(3.15)

The overline in (3.15) means *expected value* since  $X(\omega)$  is a random variable in this example. If we assume a ramp damping function, then the convolution above, evaluated at  $\omega_0$ , is given by:

$$\overline{|X(\omega_0)|^2} = \sigma_X^2 = \frac{1}{2} N \omega_0^2 \sigma_s \sqrt{\pi},$$

(3.16)

where  $\sigma_X^2$  is the variance of random process  $X(\omega)$ .

The preceding analysis assumed that the noise in the SRA is AWGN with con-

stant single side band power density  $N_0$ . In practice, however, a portion of noise injected into the SRA's resonant tank is actually time variant: as the damping function  $\zeta(t)$ , and thus the transconductance, changes with time, the noise of the active device, typically implemented with a single transistor, changes as well. The frequency domain model presented here and in [40] is not suitable to include time-varying noise sources. Thus, a time-invariant noise source, whose value is computed by the minimum transconductance necessary to enable oscillation, is typically included in such analysis, though mathematical justification for such an assumption has not been previously given. The interested reader can refer to Appendix A, which introduces a new time domain SRA model that enables inclusion of time-varying noise sources in order to quantify over what range of practical implementation parameters this assumption is reasonable.

### **3.3** Sensitivity Analysis of a PSK SRA

This section develops a stochastic model that enables prediction of the sensitivity of an SRA used in an m-ary PSK demodulating receiver. Since the analysis presented in Appendix A shows that the effect of time variant noise is negligible as long as the data rate is sufficiently small compared to the carrier frequency, which is true in many ramp-damped SRO systems, the analysis presented in this section utilizes the output variance computed in (3.16). Designers interested in wideband systems can follow the same analysis presented below, though starting from (3.84) instead.

# **3.3.1** Derivation of the probability density function of output phase

The output of an SRA used in a phase demodulating receiver is often sampled when the SRA reaches a stable oscillation in order to benefit from the large gain of the regenerative amplifier. Fortunately, the output phase of the SRA is preserved as the SRA transitions from linear mode to logarithmic mode, and to a stable oscillation [39,41]. Therefore, analysis of phase uncertainty in linear mode is valid for all modes of operation.

When the input to the system is a sum of a deterministic input,  $i_{i,signal}(t)$ , and non-deterministic noise,  $i_{i,noise}(t)$ , then the output can be given by:

$$v_{out}(t) = v_{o,signal}(t) + v_{o,noise}(t), \qquad (3.17)$$

where  $v_{o,signal}(t)$  and  $v_{o,noise}(t)$  are outputs due to  $i_{i,signal}(t)$  and  $i_{i,noise}(t)$ , respectively. The amplitude of this equation is only valid in the linear region of the SRA.

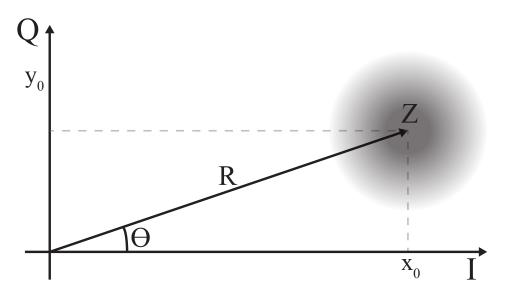

To ease further analysis, define Z as a complex random variable that represents the value of  $v_{out}(t_0)$  at time  $t_0$  when enough time has passed such that the sensitivity function g(t) is practically zero, and yet, the magnitude of the output is sufficiently small for the system to still be linear. When the input is AWGN only, the phase of the output at  $t_0$  should be uniformly distributed from  $-\pi$  to  $\pi$ . Therefore, if Z is written as a sum of its vector component X and Y, such that Z = X + jY, the variance of X and Y must be the same. Thus,  $X \sim N(x_0, \sigma^2)$  and  $Y \sim N(y_0, \sigma^2)$ , and the variance  $\sigma^2$  of X and Y is related to the variance  $\sigma_k^2$  of Z in the following manner:  $\sigma_k^2 = 2\sigma^2$ . The mean of X and Y,  $x_0$  and  $y_0$ , are the vector components of the output due to signal,  $v_{o,signal}$ .

Now, with a convenient mathematical model defined, the the probability density function of the phase of  $v_{out}(t_0)$  can be derived. The magnitude and phase of the random variable Z are then defined by the following, as illustrated in Figure 3.4:

$$R = \sqrt{X^2 + Y^2},$$

(3.18)

and

$$\Theta = \tan^{-1}(\frac{Y}{X}). \tag{3.19}$$

From this model, the pdf of  $\Theta$  represents the output phase of the SRA. Random variables X and Y can be expressed in terms of  $\Theta$  and R:

Figure 3.4: Illustration of the random variables in the constellation diagram.

$$X = R\cos(\Theta), \tag{3.20}$$

$$Y = R\sin(\Theta). \tag{3.21}$$

The joint pdf of R and  $\Theta$  can be expressed as:

$$f_{R,\Theta}(r,\theta) = f_{X,Y}(R\cos(\Theta), R\sin(\Theta))|\Im(r,\theta)|.$$

(3.22)

$\Im(r,\theta)$  is the Jacobian of the transformation such that

$$\Im(r,\theta) = det \begin{bmatrix} \frac{\partial x}{\partial r} & \frac{\partial x}{\partial \theta} \\ \frac{\partial y}{\partial r} & \frac{\partial y}{\partial \theta} \end{bmatrix} = det \begin{bmatrix} \cos(\theta) & -r\sin(\theta) \\ \sin(\theta) & r\cos(\theta) \end{bmatrix} = r$$

(3.23)

Then the joint pdf of X and Y in (3.22) can be expressed as

$$f_{X,Y}(r\cos(\theta), r\sin(\theta)) = \frac{1}{\sigma^2 2\pi} e^{-\frac{(r\cos(\theta) - x_0)^2 + (r\sin(\theta) - y_0)^2}{2\sigma^2}}$$

(3.24)

Substituting (3.24) into (3.22) results in:

$$f_{R,\Theta}(r,\theta) = \frac{r}{\sigma^2 2\pi} e^{-\frac{(r\cos(\theta) - x_0)^2 + (r\sin(\theta) - y_0)^2}{2\sigma^2}}.$$

(3.25)

The terms with r and  $\theta$  can be separated such that

$$f_{R,\Theta}(r,\theta) = \frac{r}{\sigma^2 2\pi} e^{-\frac{r^2 + v_s^2}{2\sigma^2}} e^{\frac{r(x_0 \cos(\theta) + y_0 \sin(\theta))}{\sigma^2}},$$

(3.26)

where  $v_s^2 = x_0^2 + y_0^2$  is the output power due to the deterministic input signal. Lastly, integrating (3.26) with respect to *R* results in the following expression for the marginal pdf of  $\Theta$ :

$$f_{\Theta}(\theta) = \frac{1}{\sigma^2 2\pi} \int_0^\infty r e^{-\frac{r^2 + v_s^2}{2\sigma^2}} e^{\frac{r(x_0 \cos(\theta) + y_0 \sin(\theta))}{\sigma^2}} dr.$$

(3.27)

From this, the output SNR can be defined by taking the ratio of signal power to noise power as:

$$SNR_{out} = \frac{v_s^2}{\sigma_k^2} = \frac{v_s^2}{2\sigma^2}.$$

(3.28)

Note that (3.27) is no longer Gaussian, which is expected as the probability density function is defined from  $-\pi$  to  $\pi$  in Radians, and is uniformly distributed when the SNR is zero (i.e., no signal is present).

While (3.27) has no closed form solution, it can be further simplified:

$$f_{\Theta}(\theta) = \frac{A(\theta)}{\sqrt{2\pi\sigma}} e^{\frac{A(\theta)^2 - v_s^2}{2\sigma^2}} Q(-\frac{A(\theta)}{\sigma}) + \frac{1}{2\pi} e^{-\frac{v_s^2}{2\sigma^2}},$$

(3.29)

where  $A(\theta)$  is defined as

$$A(\theta) = x_0 \cos(\theta_0) + y_0 \sin(\theta_0), \qquad (3.30)$$

and Q(x) is the normalized Gaussian tail probability function which is defined as

$$Q(x) = \frac{1}{\sqrt{2\pi}} \int_{x}^{\infty} e^{-\frac{u^2}{2}} du.$$

(3.31)

Figure 3.5: SNR vs phase variance of super-regenerative amplifiers.

A detailed derivation of (3.29) can be found in Appendix B.