PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0159529

# High mobility wide bandgap amorphous-Gallium Oxide thin-film transistors for NMOS inverters

Yong Zhang, 1 Chi-Hsin Huang, 1 and Kenji Nomura 1,2 a)

<sup>1</sup>Department of Electrical and Computer Engineering, University of California San Diego, 9500 Gilman Dr., La Jolla, California, 92093, USA

<sup>2</sup>Materials Science and Engineering Program, University of California San Diego, 9500 Gilman Dr., La Jolla, California, 92093, USA

a) Corresponding author: Kenji Nomura

E-mail: kenomura@ucsd.edu

Tel: +1-858-246-2349

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0159529

### **ABSTRACT**

Wide bandgap Gallium Oxide thin-film transistor (TFT) is promising for next-generation sustainable energy-efficient power electronics. In particular, amorphous oxide channel exhibits inherent advantages on mass-productions based on a low-temperature processability compatible with cost-effective large-sized glass. Here, we developed hydrogen defect termination to produce amorphous GaO<sub>x</sub> (a-GaO<sub>x</sub>) channel for n-channel oxide-TFT and demonstrated high-mobility a-GaO<sub>x</sub>-TFT exhibiting a high saturation mobility  $(\mu_{\text{sat}})$  of ~31 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, threshold voltage  $(V_{\text{th}})$  of ~3.3 V, a current on/off ratio of ~10<sup>8</sup>, and subthreshold swing value (s-value) of  $\sim 1.17 \text{ V} \cdot \text{dec}^{-1}$ . The study found that oxygen conditions during the channel fabrication process, i.e., oxygen partial pressure during the film deposition and post-thermal annealing atmospheres, were critical for the TFT performances of Gallium Oxide-TFTs, and subgap defects originated from low-valence Ga+ state and excess oxygen rather than oxygen vacancy had a large responsibility for the device performances. The finding explains why the development of Gallium Oxide-TFTs is largely behind the other oxide-TFTs. We also fabricated depletion and enhancement-mode a-GaO<sub>x</sub>-TFTs and developed a full-swing zero-V<sub>GS</sub>-load inverter with high voltage gain ~200, and sufficient noise margins. The presented study demonstrates a high potential of Gallium Oxide channel for lowtemperature processed *n*-channel oxide-TFT for next-generation electronic applications.

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0159529

### **MANUSCRIPT**

### I. INTRODUCTION

Metal-oxide semiconductors consisted of post-transition metals such as In, Ga, Sn etc., are nowadays known as the mainstream of an n-channel material for thin-film transistor (TFT) application and are highly expected to develop next-generation sustainable energy-efficient device applications in the broad fields of electronics. Because of the excellent material properties such as high electron mobility over 10 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> and the low-temperature processability less than 500 °C, it also enables cost-effective "giant microelectronics" using a large-size glass substrate.[1-3] Therefore, n-channel oxide-TFT using amorphous In-Ga-Zn-O (a-IGZO) channel has been intensively investigated and already commercialized as a pixel TFT back-plane in several state-of-art displays such as highresolution active-matrix flat panel display (AMFPD), large-sized liquid-crystal display (LCD) and high-resolution organic light-emitting display (OLED).[4-6] A wide variety of n-type metal-oxide semiconductor materials is so far proposed to improve the TFT device performances and explore new opportunity of device applications for nextgeneration electronics beyond display applications.<sup>[7,8]</sup>

Wide-bandgap nature over 3.0 eV and high permittivity property originating from ionic chemical bonding mainly characterize oxide semiconductor channel materials.  $\beta$ -Gallium Oxide ( $\beta$ -Ga<sub>2</sub>O<sub>3</sub>) is a well-known n-type oxide with wide bandgap  $(E_z)$  of 4.5 – 4.9 eV, high dielectric constant  $(\varepsilon > 10)$ , and high electron mobility (~300 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> in single crystal), and is widely recognized as a promising material for oxide-semiconductor devices.<sup>[9, 10]</sup> The wide bandgap nature provides several benefits such as a high optical transparency through visible-ultraviolet region, a low intrinsic carrier concentration, and a high breakdown electric field of >6 MV·cm<sup>-1</sup>, which also enable to develop a variety of optoelectronics such as deep-ultraviolet sensor, power electronics devices, and novel applications.[9-15]

So far numerous efforts have been devoted for the development of Ga<sub>2</sub>O<sub>3</sub>-based transistors, which are mainly classified into two types of channel forms, i.e., bulk single-crystal and thin-film channel. The recent progress of single crystal (SC) β-Ga<sub>2</sub>O<sub>3</sub>-based field-effect transistor (FET) and TFTs are summarized in Table S1 and S2 (supplementary material). Several high-mobility SC-β-Ga<sub>2</sub>O<sub>3</sub>-FET (~191 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> at the record value) have been demonstrated. [16-19] Because non-doped SC  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> channel shows semi-insulative behavior with high electrical resistivity of >10<sup>6</sup>  $\Omega$ ·cm, the electron doped  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> bulk channels using Si and Sn donors are used for the most

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0159529

reported SC devices. [16] However, the precise control of electron doping level is not established yet and also the doping level is always high with >10<sup>18</sup> cm<sup>-3</sup> for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> channels. [19, 20] Thus these devices operate in only depletion mode with a large negative threshold voltage ( $V_{th}$ ), typically more than -30 V. Moreover, the SC-channels require high-temperature single crystal grown at 800 - 1400 °C and are fabricated by non-massive process such as mechanically exfoliation process.[17-19, 21, 22]

Although TFT device is in general highly preferable for massive production process, on the other hand, the development of  $Ga_2O_3$ -TFTs is largely behind from the SC devices, and the reports regarding  $\beta$ - $Ga_2O_3$ -TFT are currently limited.<sup>[23, 24]</sup> (See Table S2 in supplementary material for the TFT device performances for previously reported Ga<sub>2</sub>O<sub>3</sub>-TFTs including epitaxial film, poly-crystalline film and amorphous film channels) Recently, Lv et al. achieved high mobility of ~90 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> in the epitaxial β-Ga<sub>2</sub>O<sub>3</sub>-TFT fabricated by MOCVD at 750 °C.<sup>[25]</sup> Moreover, nanocrystalline  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> and amorphous GaO<sub>x</sub> (a-GaO<sub>x</sub>) channels are also developed by using several deposition methods such as spray pyrolysis<sup>[26]</sup>, pulsed laser deposition (PLD)<sup>[27, 28]</sup>, and sputtering<sup>[29]</sup>. However, it is still challenging to fabricate high-performance Ga<sub>2</sub>O<sub>3</sub>-TFTs at a low temperature less than 500 °C compatible with glass substrate. [30] To our best knowledge, typical TFT mobility of poly-crystalline Ga<sub>2</sub>O<sub>3</sub>-TFTs is still limited to  $0.1-2 \text{ cm}^2\text{V}^{-1}\text{s}^{-1}.^{[26-29, 31]}$

In this study, we developed high-performance amorphous-GaO<sub>x</sub>-TFTs exhibiting good switching properties such as a large saturation mobility of ~31 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, V<sub>th</sub> of 3.28V, on/off current ratio of ~10<sup>8</sup> by using hydrogen subgap defect termination performing less than 500 °C. We investigated the electronic/defect structures of the GaO<sub>x</sub> channel and explained why the development of Ga<sub>2</sub>O<sub>3</sub>-TFT was more challenging than another oxide-TFTs. In Gallium oxide, the subgap defects originating from low-valence Ga+ state and excess oxygen rather than oxygen vacancy were significant for the TFT performances, and these defects caused the large degradation of the device performances. We also fabricated both depletion mode and enhancement mode a-GaO<sub>x</sub>-TFTs for NMOS inverter application and demonstrated a-GaO<sub>x</sub>-TFT-based-zero-V<sub>GS</sub>-NMOS inverter exhibiting a full-swing inversion action and high voltage gain of ~200.

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0159529

### **II. RESULTS AND DISCUSSION**

Inverted-staggered structure, i.e., bottom gate and top-contact, TFT was fabricated using ~40 nm-thickness Gallium oxide channel (Fig. 1(a) for the schematic of the cross-sectional view for the TFT structure and the optical microscopic image of the channel region). Fig. 1(b) shows the variations of transfer characteristics, i.e., drain current  $(I_D)$  versus gate bias  $(V_{GS})$  at drain-source voltage  $V_{DS} = 20$ V, for the as-deposited (i.e., unannealed)-TFTs prepared at different oxygen partial pressure (PO<sub>2</sub>) during pulsed laser deposition (PLD) at room temperature (RT). The glancing-angle X-ray diffraction (GIXRD) measurement confirmed that no diffraction peak was observed for all the as-deposited films, revealing that these films were amorphous irrespective of the PO<sub>2</sub> conditions during the PLD depositions (Fig. S1 for the GIXRD patterns for the as-deposited films in supplementary material). All the amorphous-GaO<sub>x</sub> (a-GaO<sub>x</sub>) films exhibited semiconducting behavior, and n-channel field-effect transistor actions, i.e., the I<sub>D</sub> current increased with applying positive V<sub>GS</sub>, were confirmed. But the device performances are largely varied by the PO<sub>2</sub> deposition conditions, which suggests that the TFT characteristics are controlled by the channels that involve different defect structures originating from off-stoichiometry.

The variation of TFT characteristics by the PO<sub>2</sub> condition is not straightforward. The lowest PO<sub>2</sub> condition (i.e.,  $PO_2 = 5mTorr$ ) provides relatively good n-channel TFT device with the on/off-current ratio of >10<sup>5</sup> even in the RT device fabrication condition. When the PO2 raises to ~10 mTorr, i.e., oxygen moderately-rich conditions, however, the film becomes highly conductive with the high electrical conductivity (σ) of ~7.1 S·cm<sup>-1</sup> and thus the TFT device only shows very weak field-effect current modulation. On the other hand, the a-GaO $_x$  channel turned out to be semiconducting state with the  $\sigma$  of  $\sim 1.2 \times 10^{-5} \text{ S} \cdot \text{cm}^{-1}$  by furthermore increasing the PO<sub>2</sub> to 20 mTorr and decent nchannel TFT switching was confirmed again. However, the TFT characteristics for the 20 mTorr-device are not as good as the 5 mTorr-devices and quite poor with a small on/off-current ratio of  $\sim 10^3$ .

The important TFT device parameters, i.e., saturation mobility ( $\mu_{sat}$ ),  $V_{th}$ , on/off-current ratio, and subthreshold slope value (s-value) are summarized in Figs. 1(c)-(d). From the measured transfer curve, the  $V_{\rm th}$  is determined from a straight line in a  $(I_{\rm D})^{1/2}$  -  $V_{\rm GS}$  plot to the  $V_{\rm GS}$  axis. At  $V_{\rm DS}=20{\rm V}$ ,  $\mu_{\rm sat}$  is calculated by  $I_{\rm D}=1/2$ ·  $W\cdot\mu_{\rm sat}$ ·  $C_{\rm ox}/L\cdot(V_{\rm GS}-1)$  $(V_{th})^2$ , where W and L are channel width and length, respectively,  $(C_{ox})$  is the gate insulator capacitance per unit area. The s-value is evaluated in the subthreshold region, with  $s = (\partial \log I_D / \partial V_{GS})^{-1}$ . The best TFT characteristics for the

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0159529

as-deposited a-GaO<sub>x</sub> channel were obtained when the channel was deposited at the PO<sub>2</sub> of 5 mTorr, and TFT performances were  $\mu_{sat}$  of ~0.3 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>,  $V_{th}$  of ~12.3 V, current on/off ratio of ~10<sup>6</sup>, s-value of 1.0 V·dec<sup>-1</sup>, which were nearly comparable to the recently reported a-GaO<sub>x</sub>-TFT performances.<sup>[28, 29]</sup>

The role of the deposition PO2 condition of metal-oxide channels has been well investigated for several metal oxides such as a-IGZO, amorphous In-Zn-O (a-IZO), ZnO, In<sub>2</sub>O<sub>3</sub> etc. It is well observed that most oxide channels simply transit from electrically conductive state to highly-resistive state by increasing the PO<sub>2</sub> condition and thus the corresponding  $V_{th}$  changes from negative to positive values, [32] The reason is mainly considered as the change of electron density (N<sub>e</sub>) in the oxide channels by the formation/annihilation of oxygen vacancy (Vo) by the PO<sub>2</sub> conditions. However, the observed variations for the presented a-GaO<sub>x</sub>-TFT are not simple and cannot be understood by the single effect of the N<sub>e</sub> variation. Fig. 1(e) illustrates the variation of film conductivity as the PO<sub>2</sub> increasing, indicating non-linear relation between the film conductivity and the PO2 condition during the RTdeposition. Thus we should consider the channel subgap defects, which also alter the Fermi level (EF) position and vary the  $N_c$  and the conductivity in a-GaO<sub>x</sub> channel, to explain the observed PO<sub>2</sub> dependency.

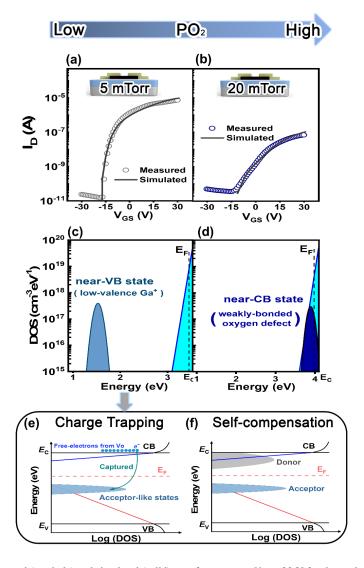

To obtain better insight for subgap density of state (DOS) for the a-GaO<sub>x</sub> channels, Technology Computer-Aided Design (TCAD) device simulation was performed. Figs. 2(a) and 2(b) show the measured and simulated transfer curves for the as-deposited a-GaO<sub>x</sub>-TFTs fabricated by PO<sub>2</sub> deposition at 5 and 20 mTorr, respectively. All the measured transfer curves were well reproduced by optimizing the subgap DOS profile, which was composed of acceptor-like exponential band-tail and Gaussian-distributed subgap defects. This indicates that TFT characteristics are mainly controlled by subgap defects. Especially, the defect density and the energy level of the Gaussiandistributed subgap defects have a large responsibility for the variations of the transfer characteristics for the a-GaO<sub>x</sub>-TFTs.

The exponential tail-like DOS in the vicinity of the conduction band minimum (CBM) is expressed by  $g_{CBa}(E) = g_{ia} \exp[(E - E_C)/W_{ia}]$ , where  $E_C$  is conduction band edge energy,  $g_{ta}$  is acceptor-like states density at  $E = E_{\rm C}$ , and  $W_{\rm ta}$  is characteristic decay energy of conduction band-tail states. Meanwhile, the acceptor-like Gaussian states are assumed by  $g_{Ga}(E) = g_{ga} \exp[-((E_{ga} - E)/W_{ga})^2]$ , where  $g_{ga}$  is the total acceptor-like Gaussian-

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0159529

distributed DOS,  $E_{\rm ga}$  is peak energy distribution measured from  $E_{\rm C}$ , and  $W_{\rm ga}$  is the characteristic decay energy. The subgap defect parameters for the device simulation are summarized in Table S3 (supplementary material).

Figures 2(c) and 2(d) show the corresponding subgap DOS profiles for the a-GaO<sub>x</sub> channel extracted from the TFT device simulation analysis. When the channel is deposited at low PO<sub>2</sub> condition (i.e., 5 mTorr), TFT simulation analysis found that the film involves high  $N_e$  of >  $10^{18}$  cm<sup>-3</sup>. Moreover, the relatively deep acceptor-like defect was found at the energy level of  $E_V + 1.5$  eV, where  $E_V$  is valence band edge energy, i.e., nearly near-valence band (VB) defect (Fig. 2(c)). To explain the observation, two carrier compensation mechanisms: 1) charge trapping mechanism, and 2) self-compensation mechanism, are considered. The observed deep acceptor-like states can capture free electrons, causing to lower the Fermi level due to carrier trap-induced charge compensation, shown as Fig. 2(e). Since the carrier density  $(N_E)$  relates to Fermi level  $(E_F)$  position, it follows the equation,  $N_e = N_C \exp \left[ -(E_C - E_F) / kT \right]$ , where k is the Boltzmann constant, T is room temperature,  $N_C$  is the effective density of states at the conduction band edge  $E_c$ . Thus, the 5 mTorr a-GaO<sub>x</sub> channel has the less  $N_e$  (~10<sup>18</sup> cm<sup>-3</sup>) by the presence of deep acceptor-like states and exhibits decent n-channel TFT action. On the other hand, the selfcompensation mechanism is often used for metal oxide semiconductor to explain the variation of the electron density because most oxides have the electronic structure consisted of a shallow donor and a compensating deep acceptor levels, which is similar to the presented a-GaO<sub>x</sub> channel. [33] In this model, the deep state is treated as acceptor with the density of  $N_A$ , while the near-CBM state is donor with density of  $N_D$ , shown as Fig. 2(f). When the Fermi level is above the acceptor level, the acceptor is negatively charged with  $N_{\Lambda}^{-}$ . On the other hand, the donor states are also nearly completely ionized and charged with  $N_D^+$ . Charge neutrality requires  $N_D^+ = N_e + N_A^-$  for such n-type oxide semiconductor. From the charge neutrality condition,  $N_D^+ = N_e + N_A^-$  for n-type semiconductor, the existence of the deep acceptor states compensates part of the charge and results in the lower electron density.

Soft X-ray photoelectron spectroscopy (XPS) measurements were performed for the as-deposited a-GaO<sub>x</sub> films deposited at different PO2 conditions, as shown in Figs. S2 and S3 in supplementary material. We observed the

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0159529

extra subgap defect states above the VBM. The defect strongly depends on the deposition PO2 condition, and the density increases when the a-GaOx films are deposited at the low PO2 conditions. The near-VB defect is often observed in metal-oxide semiconductors, but the exact origin is not clarified yet. [4, 28, 34, 35] Currently, Vo and lowvalence metal cation state (i.e., Ga+ in Gallium oxide) are considered as possible sources. The bulk-sensitive hard X-ray photoemission spectroscopy (HX-PES) study showed that the amount of Ga contents in a-IGZO channel significantly affected the near VB-defect structure and the VB-defect DOS increased by increasing the Ga content.[36] From the reported HX-PES observation and our experimental fact that near VB-defect is obvious for the low-PO<sub>2</sub> condition, we speculate that low-valence Ga<sup>+</sup> is strong candidate for the formation of the near-VB-defects.

Significant reduction of the  $N_e$  down to ~5×10<sup>17</sup> cm<sup>-3</sup> and the appearance of shallow acceptor-like states near  $E_C$ - 0.2 eV (i.e., near CB-defect) were observed in the highest PO<sub>2</sub>-deposited channel (Fig. 2(d)). This observation allows us to speculate that oxygen-rich deposition condition eliminates oxygen deficient-related defects such as Vo and low-valence metal but is likely to form extra subgap defect, such as weakly-bonded (excess) oxygen defect, which is also often observed in amorphous metal oxide and works as acceptor-like traps. [28, 37] Therefore, the 20 mTorr-deposited a-GaO<sub>x</sub> channel satisfies the TFT operation conditions but exhibits poor performances with a very large s-value and a large hysteresis with the hysteresis window of >25 V.

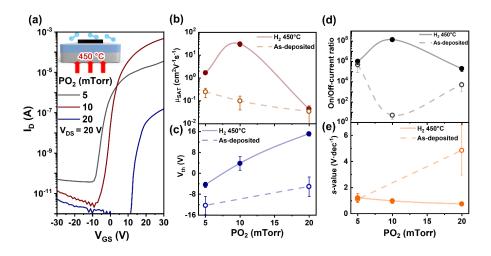

We next examined the effect of post-thermal hydrogen annealing for the a-GaO<sub>x</sub> channel to improve the TFT device characteristics. Fig. 3(a) shows the variation of transfer curves for the devices where the channels were annealed at 450 °C in hydrogen atmosphere. [31] The GIXRD measurement confirmed that the 450 °C-annealed films maintained amorphous phase (Fig. S4 for the GIXRD analysis in supplementary material). We confirmed that  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> was formed after 550 °C-post-annealing. The observation is consistent with previous reports that high temperature annealing above 500 °C is required for the crystallization of Ga<sub>2</sub>O<sub>3</sub>.<sup>[28, 30, 31]</sup>

The variations of fundamental device parameters by hydrogen annealing are summarized in Figs. 3(b)-(e), compared with the corresponding as-deposited devices. The 5mTorr-TFT showed the improvement of TFT mobility, but no apparent improvement of s-value and the on/off current ratio were observed. Large positive shift of  $V_{\rm th}$  was observed in the 20mTorr-devices. Significant improvement was observed only in the channel deposited

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0159529

at PO<sub>2</sub> = 10 mTorr, suggesting that the as-deposited 10mTorr-film has better stoichiometry, i.e., less subgap defect originating from oxygen-related off-stoichiometry. Therefore, the a-GaO<sub>x</sub> film deposition condition is still important to obtain high performance TFT fabricated with post-thermal annealing process. The H concentration was measured by Secondary Ion Mass Spectrometry (SIMS) and was found to be ~ 2×10<sup>19</sup> cm<sup>-3</sup> for the 450 °C-H<sub>2</sub> annealed-a-GaO<sub>x</sub> film (See Fig. S5 for the Hydrogen SIMS depth profile in supplementary material).

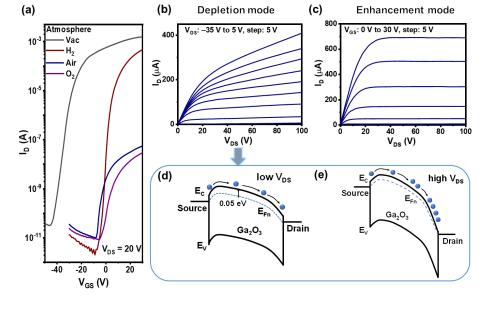

Figure 4(a) also shows the variation of transfer characteristics of the a-GaO<sub>x</sub>-TFTs annealed in different annealing atmospheres such as hydrogen, vacuum, oxygen, and ambient air. All the channel was deposited at 10 mTorr and then annealed at 450 °C for 1 hour. The TFTs performances are also summarized in Table I. The trap state density  $(D_{it})$  can be estimated from the s-value with the following relation:  $s = \ln 10 \cdot k_B T/q \cdot [1 + eD_{it}/C_{ox}]$ , where  $k_B$  is Boltzmann constant, T is the temperature, and e is the elementary charge. We observed that the TFT characteristics were largely affected by the annealing atmospheres. The vacuum annealing and hydrogen annealing produce TFT devices with good switching property such as large on/off-current ratio  $(I_{on}/I_{off})$  over  $10^8$ . The  $\mu_{sat}$ values are ~27 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, and ~31 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> for the vacuum-annealed and hydrogen-annealed TFTs, respectively. It is well known that the mobility is sometimes overestimated due to fringe effect of channel region and the channel length contributed by the peripheral channels. Therefore, it is important to show the accuracy of the mobility and the accuracy is estimated as ~89% for the presented TFTs. The s-values are ~2.5 V·dec<sup>-1</sup> and ~1.0 V·dec<sup>-1</sup>, which correspond to the  $D_{\rm it}$  values of ~5.9×10<sup>12</sup> cm<sup>-2</sup>eV<sup>-1</sup>, and ~2.3×10<sup>12</sup> cm<sup>-2</sup>eV<sup>-1</sup>, respectively. The  $V_{\rm th}$  are -30 V and +3.3 V for the vacuum and hydrogen-annealed TFTs, indicating that these devices are operated in depletion (D) mode (normally-on) and enhancement (E) mode (normally-off) modes, respectively. This is understood by the difference of the  $N_e$  in the a-GaO<sub>x</sub> channels, which are estimated be ~2×10<sup>18</sup> cm<sup>-3</sup> and ~1×10<sup>17</sup> cm<sup>-3</sup> for the vacuumand hydrogen-annealed channels, respectively. Studies regarding native point-defect analysis for crystalline  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> have been done by using density functional theory (DFT) material simulations. These studies predict that the Vo defect<sup>[38, 39]</sup>, impurity hydrogen<sup>[40, 41]</sup>, Gallium interstitials (Ga<sub>i</sub>)<sup>[42]</sup> are considered as the possible sources of electron for Ga<sub>2</sub>O<sub>3</sub>. Several experimental studies also supported the DFT predictions for the carrier generation, but it is still controversial.[43-45] Our experimental observations showed that vacuum-annealing produces one order higher N<sub>e</sub> than hydrogen-annealing, and Vo and Ga<sub>i</sub> defects are more obvious than hydrogen impurity for electron

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0159529

carrier generation. Currently, the exact kind of defect that is terminated by hydrogen annealing is still unclear. Because the defect should be electron trap state, oxygen vacancy is still considered as a strong candidate for the defect. It was reported that hydrogen could be easily incorporated and possibly substitute with oxygen vacancy site for amorphous metal oxide. [46] Another plausible defect relates to a free space in amorphous structure, which causes the formation of shallow unoccupied state below the CBM for oxide-TFT.[47] Since the film density of the presented a-GaO<sub>x</sub> film is only ~ 5.2 g/cm<sup>3</sup>, the amorphous structure is speculated to have a large volume of free space with high density vacancy defects and bond angle distortions, which work as electron trap. Therefore, such free space facilitates fast migration/diffusion of Hydrogen, and Hydrogen helps to terminate electron trap defect sites.

Both the D and E-mode TFT devices showed clockwise-hysteresis, indicating the presence of electron trap. The hysteresis windows for the hydrogen-annealed are ~1.8 V and ~1.5 V at V<sub>DS</sub> = 1 V and 20 V, respectively, which are well suppressed as compared with that in the vacuum-annealed TFTs (~8 V) (See Fig. S6 for the hysteresis characteristics in supplementary material).

On the other hand, oxygen-containing annealing atmospheres such as dry-O<sub>2</sub> and ambient air showed apparent degradation of the device characteristics from the as-deposited device. These annealed devices showed very low mobility of < 5×10<sup>-3</sup> cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> and a small on/off-current ratio of <10<sup>4</sup>, which are the similar device performances as the previously reported Ga<sub>2</sub>O<sub>3</sub>-TFT devices<sup>[27, 31]</sup>, and similar as the as-deposited device fabricated at high PO<sub>2</sub> conditions in this study. In general, oxygen-containing annealing is believed to improve the device characteristics for several n-channel metal oxide-TFTs such as IGZO, ZnO and In<sub>2</sub>O<sub>3</sub>. This is based on the assumption that Vo defect forms electron-trap states and oxygen-containing annealing compensate Vo-defects.<sup>[1, 48, 49]</sup> However, we clearly observed opposite effects of oxygen-containing annealing for the presented a-GaO<sub>x</sub>-TFTs. Since the device performances for the air and oxygen-annealed-TFTs are very similar with the high PO2-deposited TFT device, we speculate that excess oxygen defects that work as acceptor-like defect are introduced by oxygen-containing annealing.

We also analyzed the subgap DOS by microwave-photoconductivity decay (µ-PCD) measurement and found that the subgap DOS profile was significantly altered by the deposition PO2 and post-thermal annealing conditions. For the unannealed films, it was observed that the 10 mTorr and 20 mTorr a-GaO<sub>x</sub> films involved relatively high

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0159529

subgap DOS of > 10<sup>18</sup> cm<sup>-3</sup>eV<sup>-1</sup>, while the subgap DOS for the 5 mTorr film was well suppressed to ~10<sup>17</sup> cm<sup>-3</sup>eV<sup>-1</sup> 1. This observation is consistent with the TCAD simulation analysis, which explains the reason why the 5mTorrchannel TFT shows decent reasonable TFT performances. Moreover, we observed hydrogen annealing significantly reduced the subgap DOS down to ~10<sup>16</sup> cm<sup>-3</sup>eV<sup>-1</sup>. It is also confirmed that vacuum annealed film has a relative low amount of shallow subgap DOS of ~1017 cm<sup>-3</sup>eV<sup>-1</sup>. The air-annealed film involved high-density shallow states with DOS of  $> 10^{18}$  cm<sup>-3</sup>eV<sup>-1</sup>. (See Figs. S7-S10, Table S4 and S5 for  $\mu$ -PCD analysis and extracted subgap DOS profiles in supplementary material) These observations support our claim that oxygen-containing annealing generates extra subgap DOS and does not improve TFT performances for the a-GaO<sub>x</sub>-TFTs. On the contrary, hydrogen annealing produces good n-channel oxide-TFT originating from the reduction of subgap defect.

We measured the bandgap (Eg) for the presented a-GaOx films and confirmed a-GaOx films maintained wide bandgap nature (Fig. S11 for the bandgap and urbach energy for the presented a-GaO<sub>x</sub> films in supplementary material). The Eg values of the as-deposited a-GaOx films are varied by the PO2 conditions and are from ~3.5 to 4.1 eV by increasing the PO<sub>2</sub> condition. Post-annealing also increases the  $E_g$  values, which were ~3.8 eV and ~4.0 eV for vacuum-annealed film, and the hydrogen-annealed film, respectively. The observed  $E_{\rm g}$  is smaller than crystalline  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> but in good agreement with the previously reported amorphous Gallium oxide. [28, 31] The variation of  $E_{\sigma}$ can be mainly understood by the change of the film density (Fig. S12 for the film density analysis in supplementary material). The film density of the a-GaO<sub>x</sub> films has the tendency to be increased by high PO<sub>2</sub> condition and postthermal annealing. The film density was determined as  $\sim 5.2 - 5.4 \text{ g} \cdot \text{cm}^{-3}$  that is  $\sim 12 \%$  lower than that of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> (density ~5.95 g·cm<sup>-3</sup>).

Figures 4(b) and 4(c) show high-voltage output characteristics for the depletion (D-) mode vacuum-annealed and enhancement (E-) mode hydrogen-annealed-TFTs, respectively. The linear output characteristics confirmed the ohmic behavior, indicating that ITO contact made good ohmic contact for both operation modes. We confirm that both devices maintain stable operation under high  $V_{\rm DS}$  DC voltage sweeping up to 100 V, the maximum current density is ~1.4 mA·mm<sup>-1</sup> for the presented D-mode TFT, and ~2.3 mA·mm<sup>-1</sup> for the presented E-mode TFT, which are comparable to the previously reported E-mode epitaxial  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET. [24, 50]

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0159529

The D-mode-TFT exhibits larger linear region than the E-mode device and insufficient pinch-off characteristics. This is due to the effective channel length modulation by high-density accumulated carrier formation near drain region at high  $V_{DS}$ . The band diagrams for the D-mode TFT operations are depicted as Figs. 4(d)-(e). For the low drain-source electric field at low V<sub>DS</sub> condition (< 25 V), band bending structure is not altered (Fig 4(d)). In contrast, at high V<sub>DS</sub> condition (> 40 V), the band bending is largely impacted by large positive drain-source electric field and larger downward bending is formed near drain electrode region. In this case, the EF level is close to the CBM and the accumulated electrons are significantly increased near drain region, and the channel length modulation effect becomes remarkable (Fig 4(e)). The drain-current is modified by the channel modulation factor ( $\lambda$ ), and is expressed by  $I_D = \frac{1}{2} \cdot W \cdot \mu_{sat} \cdot C_{ox}/L \cdot (V_{GS} - V_{th})^2 \cdot [1 + \lambda(V_{DS} - V_{Dsat})]$ , where  $V_{Dsat}$  is the value of  $V_{GS} - V_{th}$ . In the presented D-mode TFT,  $\lambda$  value is ~0.01 V<sup>-1</sup>. The effective channel length (L') becomes shorter compared with the total channel length (L) of 150  $\mu$ m, following the relation  $(L-L')/L = \lambda(V_{DS}-V_{Dsat})$ , and L' is estimated as ~50  $\mu$ m at  $V_{DS} = 100 \text{ V}$ . Therefore, the insufficient pinch-off is observed from the D-mode output characteristics.

On the other hand, the E-mode device exhibits ideal output characteristics with a good pinch-off and current saturation characteristics, which originates from the low  $N_e$  condition in the E-mode channel with ~10<sup>17</sup> cm<sup>-3</sup>. Generally, a low N<sub>c</sub> material system exhibits several advantages such as a less self-heating effect due to low thermal conductivity properties. [51] As compared with the previously reported SC-based  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>-FETs, the presented TFT exhibits comparable device mobility of  $\sim 31 \text{ cm}^2\text{V}^{-1}\text{s}^{-1}$  and a lower operation voltage  $(V_{\text{th}} \sim 0\text{V})$ .

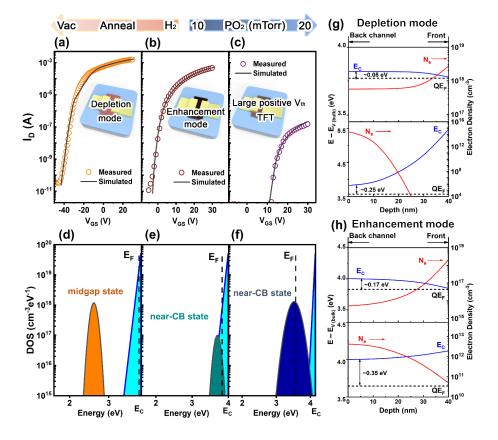

To furthermore understand the TFT operation mode of the D and E-modes a-GaO<sub>x</sub>-TFTs, the electrical characteristics were analyzed by TCAD-TFT device simulation. Figs. 5(a)-(b) show the measured and simulated transfer curves for the above D- and E- mode a-GaO<sub>x</sub>-TFTs, respectively. For the comparison, the device with a large positive V<sub>th</sub>, which was fabricated by 450 °C-hydrogen-annealed a-GaO<sub>x</sub> channel deposited at high PO<sub>2</sub> condition (PO<sub>2</sub> = 20 mTorr), is also included as Fig. 5(c). All the measured transfer curves were well simulated by optimizing the subgap DOS profile in a-GaO<sub>x</sub> channel. The simulation parameters are also summarized in Table S6 (supplementary material).

Figures 5(d)-(f) show the extracted subgap DOS profile for the corresponding a-GaO<sub>x</sub>-TFTs. For the D-mode TFT, high-density midgap-defects with  $\sim 1.2 \times 10^{18}$  cm<sup>-3</sup>eV<sup>-1</sup> located at  $E_C - 1.2$  eV was observed (Fig. 5(d)). When

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0159529

the CB energy is upward bending by large negative  $V_{GS}$ , carrier is depleted and TFT is turned off in the D-mode-TFTs. The surface potential  $(\psi_s)$  is defined as the potential difference between front channel and the bulk, and the sign of  $\psi_S$  is defined as negative for upward band bending. At  $\psi_S = -1.7 \text{ V}$  when  $V_{GS} = -40 \text{ V}$ , the channel depletion width  $(W_d)$ , defined by  $W_d = \sqrt{2\varepsilon |\psi_S|/qN_e}$ , is ~40 nm, which is comparable to the channel thickness and suggests that the device meets the fully-depleted condition. Fig. 5(g) (bottom) shows the corresponding band diagram with bulk VB energy ( $E_{V(bulk)}$ ) as reference, and the electron density map for the D-mode-TFT at  $V_{GS} = -40$ V, confirming that carriers are fully-depleted and total upward band bending is 1.7 eV. Fig. 5(g) (top) is the band diagram and electron density map for the D-mode-TFT at  $V_{\rm GS} = 20$  V, showing a weak carrier accumulation with the  $\psi_s$  of ~0.04 V. The  $E_F$  is located around ~0.05 eV below the CBM for the on-state, while for the off-state the  $E_{\rm F}$  is at  $E_{\rm C} = 0.25$  eV in bulk and is at  $E_{\rm C} = 1.95$  eV near front channel. This indicates that the device requires a large Fermi level sweeping and shift (~1.9 eV) by the gate bias between turn-off and turn-on. Due to the relatively highdensity midgap defect screened by Fermi level during energy band from upward to downward bending, the Dmode-TFT showed a large subthreshold slope property.

In contrast, the extracted E-mode device DOS confirms negligible midgap defect and the device operation is mainly controlled by shallow acceptor-like defect located at E<sub>C</sub> - 0.3 eV (Fig. 5(e)). The observation also indicates that hydrogen annealing significantly suppresses the formation of midgap defect.<sup>[47]</sup> For the accumulation operation mechanism, the  $E_F$  is at  $E_C - 0.35$  eV with  $\psi_S = -0.12$  V at negative bias of  $V_{GS} = -3$  V and no carrier is accumulated (Fig. 5(h) (bottom)). While for the turn-on condition at positive  $V_{GS}$ , the  $E_F$  is shifted up to  $E_C - 0.17$  eV, indicating that carriers are accumulated near the front channel region (Fig. 5(h) (top)).

On the other hand, the TFT simulation analysis for the large positive-V<sub>th</sub>-TFT revealed that the channel involved high-density shallow trap of  $\sim 8.5 \times 10^{17}$  cm<sup>-3</sup>eV<sup>-1</sup> near  $E_C - 0.6$  eV (Fig. 5(f)). The high-density acceptor-like defect generates negatively-charged defects by electron trapping and causes the large positive shift of  $V_{\rm th}$  due to the gate bias screening effect. Moreover, the on-current is largely degraded. Indeed, the most previously reported Ga<sub>2</sub>O<sub>3</sub>-TFTs show very similar performances as such device, i.e., large  $V_{\rm th}$  and low on-current, [26, 52] which can be

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0159529

understood by high-density acceptor-like defect in the Ga<sub>2</sub>O<sub>3</sub>-channels produced by oxygen-rich conditions. It concludes that the development of high performance Ga<sub>2</sub>O<sub>3</sub>-TFT requires the optimal PO<sub>2</sub> condition during film deposition and post-thermal annealing atmosphere.

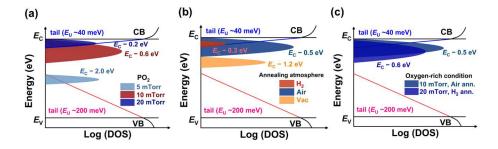

Figure 6 summarizes the electronic/defect structures for the presented a-GaO<sub>x</sub> channels deduced by the presented material characterizations and TFT simulations. Fig. 6(a) depicts the DOS profile for the as-deposited channels. All the as-deposited amorphous channel involves high  $N_c$  of  $\sim 10^{18}$  -  $10^{19}$  cm<sup>-3</sup>, which is consistent with the previous discussion about total donor density  $(N_0)$  of  $\sim 8 \times 10^{19}$  cm<sup>-3</sup> for the RT-PLD-deposited a-GaO<sub>x</sub> channel. [28] Since the donor level  $(E_D)$  forms near the CBM, the  $N_e$  is expressed by  $N_e = N_0 \exp(-(E_C - E_D)/k_B T)$ . However, the observed Ne strongly depends on the subgap defect profiles that are varied by the PO2 deposition conditions. The observations indicate that the  $E_D$  is ~0.1 eV below the CBM for the low PO<sub>2</sub>-film. Instead, highly conductive film can be obtained at optimal PO2 when the deep-level states near-VB are no longer formed, and the corresponding donor level is ~0.05 eV below the CBM. Furthermore, the conductivity drops sharply by further increasing PO<sub>2</sub> due to high-density near-CB electron traps and thus the  $E_{\rm D}$  is shifted to ~0.15 eV below CBM for the high PO<sub>2</sub>-film. On the other hand, post-thermal annealing also alters the Ne into range of 10<sup>17</sup> to 10<sup>18</sup> cm<sup>-3</sup>, and the annealing atmospheres largely modify the subgap defect profiles, as shown in Fig. 6(b). Our observations showed that hydrogen annealing significantly reduced the subgap defects, which is also consistent with the previous report. [47] We also observed that vacuum annealing created midgap states and higher  $N_e$  of the a-GaO<sub>x</sub> channel to fabricate the D-mode TFT. On the other hand, oxygen-containing annealing generated extra high density shallow subgap defect. Similar high density shallow subgap defect was observed in a-GaO<sub>x</sub> channels prepared oxygen rich process conditions such as high PO2 deposition conditions and oxygen-containing annealing and has a large responsibility for the poor TFT performances such as low mobility and very large-positive  $V_{th}$  (Fig. 6(c)). The discussion also clarifies a reason for the poor performance of the previously reported polycrystalline Ga<sub>2</sub>O<sub>3</sub>-TFTs <sup>[26, 28]</sup>. We also performed positive and negative bias stress (PBS and NBS) tests, negative and positive bias illumination stress (NBIS and PBIS) tests for the high mobility a-GaO<sub>x</sub> TFTs (Figs. S13-16 in the supplementary material). Both NBS and PBS showed bias stress-induced  $V_{th}$  instability and the enhanced  $V_{th}$  instability was observed by the lightilluminated bias stress. These observations indicate the presence of high-density subgap defects and developing

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0159529

effective defect termination is strongly required to improve the bias-stability for the a-GaO<sub>x</sub>-TFTs. Since the longterm TFT bias stability is important for practical applications, we preliminary examined a back-channel passivation for a-GaO<sub>x</sub>-TFT and confirmed that the  $V_{th}$  stability in both the PBS/NBS was improved (Figs. S17-18 in the supplementary material). The long-term positive/negative bias illumination stress (PBIS/NBIS) for the passivated devices were also assessed (See Figs. S19-20 in the supplementary material). To further improve the bias stability, the a-GaO<sub>x</sub> TFTs with 30nm-Al<sub>2</sub>O<sub>3</sub> gate dielectric were developed, exhibiting  $\mu_{\text{sat}}$  of 23.3 cm<sup>2</sup>/Vs,  $V_{\text{th}}$  of 0.67 V, and s-value of 0.14 V/dec, and confirmed the improvement of both long-term PBS/NBS and PBIS/NBIS stability (Figs. S21-24 in the supplementary material).

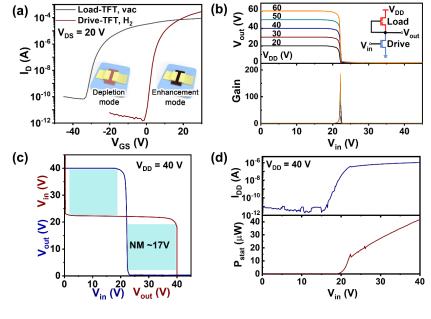

Finally, we fabricated a zero-V<sub>GS</sub>-NMOS inverter composed of the D- and E-mode a-GaO<sub>x</sub>-TFT as load- and drive-TFTs, respectively. Fig. 7(a) shows the corresponding transfer characteristics of the load/drive a-GaO<sub>x</sub>-TFTs. In order to achieve a full-swing inverter property in the voltage transfer characteristics (VTC), i.e., output voltage  $(V_{out})$  vs. input voltage  $(V_{in})$ , the  $I_{on}$  of the drive-TFT should be higher than that of the load device. Thus, we adjusted the  $I_{on}$  level on the load-TFTs. The load-device was fabricated by 450 °C-vacuum-annealing and exhibited  $V_{th}$  of -27 V at  $V_{DS} = 20$  V, s-value of 1.3 V·dec<sup>-1</sup>. For the drive-TFTs, the E-mode TFT with the  $V_{th}$  of 6.6 V at  $V_{DS} = 20$ V, s-value of 0.83 V·dec<sup>-1</sup> was used. Fig. 7(b) represents the VTC and the corresponding voltage gain, defined as  $-dV_{out}/dV_{in}$ , for the zero-V<sub>GS</sub>-load inverter and  $V_{DD}$  is varied from 20 to 60 V. The inset shows the equivalent circuit diagram. The gate and source terminals in the load-TFT are connected, so the load-TFT is always on the "ON" state. At low input voltage  $(V_{in})$ , drive-TFT is on the "OFF" state and the output voltage  $(V_{out})$  is equal to the supplied voltage  $(V_{\rm DD})$ . At high  $V_{\rm in}$ , drive-TFT is on the "ON" state, so the output voltage potential is pulled down to the ground and  $V_{\text{out}}$  becomes 0 V. A full-swing operation with rail-to-rail output was observed in all  $V_{\text{DD}}$  conditions, indicating that the inverter operated in proper NMOS schemes. The voltage gain was ~200, which is nearly comparable as the previously reported oxide-TFT-based zero-V<sub>GS</sub>-NMOS inverters.<sup>[53, 54]</sup> The observed switching threshold voltage  $V_{\text{inv}}$  was 22.2V, which was nearly  $\frac{1}{2}V_{\text{DD}}$  at  $V_{\text{DD}} = 40$  V (Fig. 7(c)). The noise margin is estimated as ~17 V and good noise immunity over 85% is achieved in the present zero- $V_{\rm GS}$ -NMOS inverters. The obtained noise immunity is sufficient for the operation of radio-frequency identification tags and oxide-based logic gates. Note that at this point the D-mode and E-mode TFTs are fabricated in different process of vacuum and hydrogen

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0159529

annealing, respectively, demanding further effort to integrate in the same chip or circuit. The presented device still requires high voltage operations due to a large subthreshold swing characteristics. The use of high-k gate dielectric will improve low power operation. Fig. 7(d) shows the static current ( $I_{DD}$ ), and the static power dissipation ( $P_{stat}$ ) which is defined as  $I_{DD} \cdot V_{DD}$ . At  $V_{DD} = 40 \text{ V}$ , the  $I_{DD}$  was ~3 pA and the corresponding  $P_{\text{stat}}$  was as low as 120 pW before the inversion. During inversion, the  $I_{DD}$  was ~350 nA. Right after inversion, the NMOS inverter reached full swing, where  $I_{\rm DD}$  was ~570 nA and  $P_{\rm stat}$  was ~23  $\mu$ W. Thus, such NMOS inverters exhibit negligible power consumption before inversion, decent gain, sufficient noise margin, and low static current to achieve full swing under high voltage operation. These good inverter characteristics were attributed to the proper switching property of both the D- and E-mode a-GaO<sub>x</sub>-TFTs.

### III. CONCLUSION

We developed a wide bandgap amorphous GaOx-TFT where the channel was fabricated by post-hydrogen thermal annealing at 450 °C, exhibiting good TFT switching characteristics such as high saturation mobility of ~31 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, V<sub>th</sub> of 3.28V, current on/off ratio of ~10<sup>8</sup>, s-value of 1.17 V·dec<sup>-1</sup>, and hysteresis widths of ~1.5 V. The oxygen condition during the channel fabrication process (i.e., PO2 deposition condition and post-annealing atmosphere) was significant for the TFT device performances of the a-GaO<sub>x</sub>-TFTs, because off-stoichiometric defects such as low-valence Ga+ and excess oxygen formed high-density deep near-VB and shallow near-CB subgap defects, respectively. We concluded that these defects hindered the development of high-performance Gallium oxide thin-film electronic devices. We developed hydrogen annealing to effectively reduce the channel subgap defects. Both D-mode and E-mode TFTs were fabricated for oxide-TFT-based NMOS inverter, and the TFT characteristics and the operation mechanisms were analyzed by using TFT device simulation. Finally, the a-GaO<sub>x</sub>-TFT-based zero- $V_{GS}$ -load inverter, composed of D-mode load TFT and E-mode drive TFT, was demonstrated with full-swing VTC, gain of ~200, and noise immunity over 85%. The presented work demonstrated the high potential of Gallium oxide-TFT and NMOS circuit applications, offered the prospects to combine with high-k dielectric technologies for further development, and promised new opportunities in next-generation sustainable cost-effective oxide-TFT technology.

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0159529

# **IV. EXPERIMENTAL SECTIONS**

# A. Film growth and material characterization of amorphous GaO<sub>x</sub> film

The a-GaO<sub>x</sub> films were deposited by pulsed laser deposition (PLD, KrF excimer laser, wavelength of 248 nm, pulsed duration 20 nsec) at RT. The base vacuum pressure of the PLD chamber was <1.8×10<sup>-8</sup> Torr. The commercial sintered body of Ga<sub>2</sub>O<sub>3</sub> (purity: 99.99%) was used as a target. The laser power density was set to ~6 J·cm<sup>-2</sup> at the target surface that yielded a film growth rate of ~10 nm·min<sup>-1</sup>. Oxygen partial pressure (PO<sub>2</sub>) during the deposition was varied from 5 to 20 mTorr. The films were subjected to thermal-annealing at 450 °C for 1 hour in H2 forming gas (5%-H<sub>2</sub> in N<sub>2</sub>), vacuum (~10<sup>-5</sup> Torr), and dry O<sub>2</sub> atmosphere using rapid thermal annealing (RTA) system, and in air using hot plate. For the material characterization, the films were deposited on quartz substrates. The film structure was characterized by grazing incidence X-ray diffraction (GIXRD) with an incident angle of 0.5°. UVvisible spectrophotometer was used to measure the optical transmittance, reflectance spectra and analyze the optical bandgap of the film. The photoconductivity decay curve was measured by microwave-photoconductivity decay (µ-PCD) with yttrium lithium fluoride (YLF) pulsed laser ( $\lambda = 349$  nm) at RT. X-ray reflectivity measurement was performed to determine the film density. X-ray photoemission spectroscopy (XPS) measurements were carried out with Al Kα (hv = 1486.6 eV). No surface treatment was performed for the XPS measurement, and the C 1s core level from the adsorbed carbon was used for binding energy correction. The depth profile of Hydrogen in the annealed films was measured by Secondary-Ion Mass Spectroscopy (SIMS).

### B. Device fabrication and characterization

Top-contact and bottom-gate a-GaO<sub>x</sub>-TFT was fabricated on thermally-oxidized SiO<sub>2</sub> (the thickness of 150 nm)/n<sup>+</sup>-Si substrates where the n<sup>+</sup> Si substrate acted as the common gate electrode. The RT-PLD deposited 40-nmthick a-GaO<sub>x</sub> films were used for a channel layer. The channel and electrode were patterned by shadow mask and the channel width (W) and length (L) were 300 and 150 µm, respectively. The channels are subject to post-thermal annealing in hydrogen, vacuum, dry O2, and air atmospheres at 450 °C for one hour. After the post-thermal annealing, RT-deposited PLD-ITO film (the thickness of 50 nm) was used for source/drain contacts. All electrical DC measurements were performed in the dark ambient environment at RT.

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0159529

### C. TCAD TFT device simulation

TCAD device simulator was used in this study to extract subgap defect DOS profiles of the a-GaO<sub>x</sub> channel. The simulation was conducted by using Silvaco's 2D ATLAS simulator package. Inverted-staggered TFT configuration was employed in the simulator. For the IV characteristics simulation, the following material parameters were used: the relative permittivity values of the silicon oxide as the gate insulator and Ga<sub>2</sub>O<sub>3</sub> as the channel semiconductor were 3.9 and 10, respectively. The electron affinity of Ga<sub>2</sub>O<sub>3</sub> was 4.0 eV and the bandgap  $(E_g)$  was determined by measured value. The measured saturation mobility was used for the electron mobility values for the channel. The effective densities of states in the conduction and valence bands were 3.7×10<sup>18</sup> cm<sup>-3</sup>.

# SUPPLEMENTARY MATERIAL

See the supplementary material for the summary of reported single-crystal Ga<sub>2</sub>O<sub>3</sub> FETs, reported epitaxial, polycrystalline, and amorphous Ga<sub>2</sub>O<sub>3</sub>-TFTs, GIXRD measurements for the a-GaO<sub>x</sub> films under different conditions, XPS measurements for the a-GaO<sub>x</sub> films deposited by different PO<sub>2</sub>, a-GaO<sub>x</sub> TFT simulation parameters, Hydrogen SIMS depth profile, a-GaO<sub>x</sub> TFT hysteresis characteristics, a-GaO<sub>x</sub> thin-film microwave photoconductivity decay measurement, analysis, and extracted subgap DOS, a-GaOx thin-film bandgap and urbach energy analysis, a-GaO<sub>x</sub> film density under different conditions, the positive/negative bias stress and negative/positive bias illumination stress tests for the high mobility a-GaO<sub>x</sub> TFTs, PBS/NBS and PBIS/NBIS for a-GaOx TFTs with back-channel passivation, PBS/NBS and PBIS/NBIS for a-GaOx TFTs with 30nm-Al<sub>2</sub>O<sub>3</sub> gate dielectric, and optical microscope image of the a-GaO<sub>x</sub> TFT.

### **DATA AVAILABLITY**

The data that support the findings of this study are available from the corresponding author upon reasonable request.

### **ACKNOWLEDGEMENTS**

We thank Dr. Keisuke Ide (Tokyo Institute of Technology) for SIMS measurement.

FIG. 1. (a) Schematic of the device structure of a-GaO<sub>x</sub>-TFT and the optical microscope image of the channel region (scale bar:  $200 \,\mu\text{m}$ ). (b) Variation of transfer characteristics at  $V_{DS} = 20 \,\text{V}$  for the a-GaO<sub>x</sub>-TFTs using the unannealed film deposited by different deposition PO<sub>2</sub> at 5, 10, and 20 mTorr at RT. The extracted fundamental TFT parameters (c)  $\mu_{\text{sat}}$  and  $V_{\text{th}}$ , (d) on/off-current ratio and s-value were plotted as a function of the deposition PO<sub>2</sub>. (e) The variation of as-deposited film conductivity as the function of PO<sub>2</sub> during a-GaO<sub>x</sub> channel deposition.

FIG. 2. The measured (symbols) and simulated (solid) transfer curves at  $V_{DS} = 20 \text{ V}$  for the as-deposited a-GaO<sub>x</sub>-TFT fabricated by PO<sub>2</sub> deposition at (a) 5 and (b) 20 mTorr. (c-d) The corresponding subgap defect DOS profiles. The proposed (e) charge trapping and (f) self-compensation mechanisms of carrier compensation for the 5 mTorra-GaO<sub>x</sub> channel device.

AIP Publishing

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset.

FIG. 3. (a) Variation of transfer characteristics at  $V_{\rm DS} = 20$  V for the 450 °C-hydrogen-annealed device with the a- $GaO_x$ -channel deposited at different  $PO_2$  conditions. The variation of fundamental TFT parameters (b)  $\mu_{sat}$ , (c)  $V_{th}$ , (d) on/off-current ratio, and (e) s-value by hydrogen annealing, compared with as-deposited films.

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset. PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0159529

FIG. 4. (a) Variation of the transfer characteristics for the a-GaO<sub>x</sub> TFTs at  $V_{\rm DS}=20~{\rm V}$  by post-annealing with different atmospheres (vacuum, H2, dry O2, and ambient air) at 450 °C. The output characteristics for (b) D-mode device and (c) E-mode device, fabricated by vacuum and hydrogen annealing, respectively. The schematics of band diagram corresponding to D-mode at (d) low and (e) high positive  $V_{DS}$ .

22

FIG. 5. Measured (symbols) and simulated (lines) transfer curves at  $V_{\rm DS} = 20~\rm V$  for (a) depletion-mode (b) enhancement-mode, and (c) large positive  $V_{\rm th}$  TFTs. (d-f) The corresponding extracted DOS distributions near CBM. Conduction band energy diagrams with the corresponding the quasi-Fermi level (QE<sub>F</sub>) and the quasi-electron density ( $N_{\rm e}$ ) for (g) D-mode at  $V_{\rm GS} = -40~\rm V$  (bottom) and +20 V (top), and for (h) E-mode at  $V_{\rm GS} = -3~\rm V$  (bottom) and +20 V (top). The blue and red lines are the conduction band energy ( $E_{\rm C}$ ) and  $N_{\rm e}$ , respectively. The black dashed line denotes the QE<sub>F</sub>.

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset.

FIG. 6. Electronic and subgap defect DOS structures of a-GaO<sub>x</sub> channels for (a) unannealed films under different deposition PO2 at 5, 10, and 20 mTorr at RT, (b) the 10mTorr-PO2 films annealed in different atmospheres of hydrogen, vacuum and air, and (c) the films deposited (PO2 of 20mTorr) or annealed (air annealing) in oxygen-rich conditions.

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0159529

FIG. 7. (a) The transfer characteristics for load-TFT and drive-TFT of the zero- $V_{\rm GS}$ -load inverter. (b) The voltage transfer characteristics (top) with the corresponding voltage gains (bottom) at different  $V_{\rm DD}$  values for the a-GaO<sub>x</sub>-TFT-based inverter. Inset shows the schematic circuit diagram of the zero- $V_{\rm GS}$ -load NMOS inverter composed of load/drive TFTs. (c) Noise margin at  $V_{\rm DD}$  = 40 V of the corresponding inverter. (d) The corresponding static current in log scale ( $I_{\rm DD}$ , top) and static power dissipation ( $P_{\rm stat}$ , bottom).

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0159529

TABLE I. The summary of TFT performances for the a-GaO $_x$ -TFTs annealed in different annealing atmospheres at 450 °C for one hour.

**TABLES**

| Annealing      | $V_{th}$  | $\mu_{\mathrm{sat}}$ | $I_{ m on}/I_{ m off}$ | s-value              | $D_{ m it}$                                       |

|----------------|-----------|----------------------|------------------------|----------------------|---------------------------------------------------|

| atmosphere     | (V)       | $(cm^2V^{-1}s^{-1})$ |                        | $(V \cdot dec^{-1})$ | $(\times 10^{12} \text{ cm}^{-2} \text{eV}^{-1})$ |

| Vacuum         | -38±11    | 27±17                | ~108                   | 2.5±0.9              | 5.88±2                                            |

| $H_2$          | 3.3±3     | 31±7                 | ~108                   | 1±0.18               | 2.27±0.3                                          |

| Air            | -6.2±5    | 2.7×10 <sup>-3</sup> | $\sim 5 \times 10^3$   | 1.94±0.2             | 4.53±0.3                                          |

| O <sub>2</sub> | -0.07±2.5 | 1.5×10 <sup>-3</sup> | $\sim 3.4 \times 10^3$ | 3.35±0.15            | 7.93±0.2                                          |

# PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0159529

accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset

This is the author's peer reviewed,

# **REFERENCES**

- [1] T. Kamiya, K. Nomura, H. Hosono, Sci. Technol. Adv. Mater. 11, 044305 (2010).

- [2] X. Yu, T. J. Marks, A. Facchetti, Nat. Mater. 15, 383 (2016).

- [3] L. Petti, N. Münzenrieder, C. Vogt, H. Faber, L. Büthe, G. Cantarella, F. Bottacchi, T. D. Anthopoulos, G. Tröster, Appl. Phys. Rev. 3, 021303 (2016).

- [4] K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, H. Hosono, Nature 432, 488 (2004).

- [5] D. Kim, Y. Kim, S. Lee, M. S. Kang, D. H. Kim, H. Lee, IEEE J. Electron Devices Soc. 5, 372 (2017).

- [6] H. Zhu, E. Shin, A. Liu, D. Ji, Y. Xu, Y. Noh, Adv. Funct. Mater. 30, 1904588 (2020).

- [7] K. Nomura, J. Inf. Disp. 22, 211 (2021).

- [8] Y. Jeon, D. Lee, H. Yoo, Coatings 12, 204 (2022).

- [9] J. Y. Tsao, S. Chowdhury, M. A. Hollis, D. Jena, N. M. Johnson, K. A. Jones, R. J. Kaplar, S. Rajan, C. G.

- Van de Walle, E. Bellotti, C. L. Chua, R. Collazo, M. E. Coltrin, J. A. Cooper, K. R. Evans, S. Graham, T. A.

- Grotjohn, E. R. Heller, M. Higashiwaki, M. S. Islam, P. W. Juodawlkis, M. A. Khan, A. D. Koehler, J. H.

- Leach, U. K. Mishra, R. J. Nemanich, R. C. N. Pilawa-Podgurski, J. B. Shealy, Z. Sitar, M. J. Tadjer, A. F.

- Witulski, M. Wraback, J. A. Simmons, Adv. Electron. Mater. 4, 1600501 (2018).

- [10] S. J. Pearton, J. Yang, P. H. Cary IV, F. Ren, J. Kim, M. J. Tadjer, M. A. Mastro, Appl. Phys. Rev. 5, 011301 (2018).

- [11] M. H. Wong, K. Sasaki, A. Kuramata, S. Yamakoshi, M. Higashiwaki, IEEE Electron Device Lett. **37**, 212 (2016).

- [12] A. K. Saikumar, S. D. Nehate, K. B. Sundaram, ECS J. Solid State Sci. Technol. 8, Q3064 (2019).

- [13] R. Zhu, H. Liang, S. Hu, Y. Wang, Z. Mei, Adv. Electron. Mater. 8, 2100741 (2021).

- [14] D. Wakimoto, C.-H. Lin, Q.T. Thieu, H. Miyamoto, K. Sasaki, A. Kuramata, Appl. Phys. Express 16, 036503 (2023).

- [15] Y. Yoon, Y. Kim, W.S. Hwang, M. Shin, Adv. Electron. Mater. 9, 2300098, (2023).

- [16] A. T. Neal, S. Mou, S. Rafique, H. Zhao, E. Ahmadi, J. S. Speck, K. T. Stevens, J. D. Blevins, D. B.

- $Thomson, N.\ Moser, K.\ D.\ Chabak, G.\ H.\ Jessen, Appl.\ Phys.\ Lett.\ \textbf{113},\ 062101\ (2018).$

- [17] W. S. Hwang, A. Verma, H. Peelaers, V. Protasenko, S. Rouvimov, H. Xing, A. Seabaugh, W. Haensch, C.

- V. de Walle, Z. Galazka, M. Albrecht, R. Fornari, D. Jena, Appl. Phys. Lett. 104, 203111 (2014).

- [18] Z. Feng, Y. Cai, G. Yan, Z. Hu, K. Dang, Y. Zhang, Z. Lu, H. Cheng, X. Lian, Y. Xu, C. Zhang, Q. Feng, H. Zhou, J. Zhang, Y. Hao, Phys. Status Solidi A **216**, 1900421 (2019).

- [19] X. Wang, S. Yan, W. Mu, Z. Jia, J. Zhang, Q. Xin, X. Tao, A. Song, IEEE Electron Device Lett. 43, 44 (2022).

- [20] H. Zhou, M. Si, S. Alghamdi, G. Qiu, L. Yang, P. D. Ye, IEEE Electron Device Lett. 38, 103 (2017).

- [21] M. Higashiwaki, H. Murakami, Y. Kumagai, A. Kuramata, Jpn. J. Appl. Phys. 55, 1202A1 (2016).

- [22] Z. Li, Y. Liu, A. Zhang, Q. Liu, C. Shen, F. Wu, C. Xu, M. Chen, H. Fu, C. Zhou, Nano Res. 12, 143 (2018).

accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset

This is the author's peer reviewed,

- [23] M. Higashiwaki, K. Sasaki, T. Kamimura, M. H. Wong, D. Krishnamurthy, A. Kuramata, T. Masui, S. Yamakoshi, Appl. Phys. Lett. **103**, 123511 (2013).

- [24] Y. Lv, X. Zhou, S. Long, Y. Wang, X. Song, X. Zhou, G. Xu, S. Liang, Z. Feng, S. Cai, X. Fu, A. Pu, M. Liu, Phys. Status Solidi RRL **14**, 1900586 (2019).

- [25] Y. Lv, X. Zhou, S. Long, X. Song, Y. Wang, S. Liang, Z. He, T. Han, X. Tan, Z. Feng, H. Dong, X. Zhou, Y. Yu, S. Cai, M. Liu, IEEE Electron Device Lett. 40, 83 (2019).

- [26] S. R. Thomas, G. Adamopoulos, Y.-H. Lin, H. Faber, L. Sygellou, E. Stratakis, N. Pliatsikas, P. A. Patsalas, T. D. Anthopoulos, Appl. Phys. Lett. **105**, 092105 (2014).

- [27] K. Matsuzaki, H. Yanagi, T. Kamiya, H. Hiramatsu, K. Nomura, M. Hirano, H. Hosono, Appl. Phys. Lett. **88**, 092106 (2006).

- [28] J. Kim, T. Sekiya, N. Miyokawa, N. Watanabe, K. Kimoto, K. Ide, Y. Toda, S. Ueda, N. Ohashi, H. Hiramatsu, H. Hosono, T. Kamiya, NPG Asia Mater. 9, e359 (2017).

- [29] Z. Han, H. Liang, W. Huo, X. Zhu, X. Du, Z. Mei, Adv. Optical Mater. 8, 1901833 (2020).

- [30] H. Liang, Z. Han, Z. Mei, Phys. Status Solidi A 218, 2000339 (2020).

- [31] D. Purnawati, J. P. Bermundo, Y. Uraoka, Appl. Phys. Express 15, 024003 (2022).

- [32] K. Nomura, A. Takagi, T. Kamiya, H. Ohta, M. Hirano, H. Hosono, Jpn. J. Appl. Phys. 45, 4303 (2006).

- [33] R.A. Street, T.N. Ng, R.A. Lujan, I. Son, M. Smith, S. Kim, T. Lee, Y. Moon, S. Cho, ACS Appl. Mater. Interfaces 6, 4428 (2014).

- [34] S. Narushima, M. Orita, M. Hirano, H. Hosono, Phys. Rev. B 66, 035203 (2002).

- [35] H. Hosono, K. Nomura, Y. Ogo, T. Uruga, T. Kamiya, J. Non-Cryst. Solids 354, 2796 (2008).

- [36] K. Lee, K. Nomura, H. Yanagi, T. Kamiya, H. Hosono, Thin Solid Films 520, 3808 (2012).

- [37] T. Orui, J. Herms, Y. Hanyu, S. Ueda, K. Watanabe, I. Sakaguchi, N. Ohashi, H. Hiramatsu, H. Kumomi, H. Hosono, T. Kamiya, J. Display Technol. 11, 518 (2015).

- [38] K. Yamaguchi, Solid State Commun. 131, 739 (2004).

- [39] M. A. Blanco, M. B. Sahariah, H. Jiang, A. Costales, R. Pandey, Phys. Rev. B 72, 184103 (2005).

- [40] J. B. Varley, J. R. Weber, A. Janotti, C. G. Van de Walle, Appl. Phys. Lett. 97, 142106 (2010).

- [41] J. B. Varley, H. Peelaers, A. Janotti, C. G. Van de Walle, J. Phys.: Condens. Matter 23, 334212 (2011).

- [42] H. Peelaers, J. L. Lyons, J. B. Varley, C. G. Van de Walle, APL Mater. 7, 022519 (2019).

- [43] E. G. Víllora, M. Yamaga, T. Inoue, S. Yabasi, Y. Masui, T. Sugawara, T. Fukuda, Jpn. J. Appl. Phys. 41, L622 (2002).

- [44] M. Yamaga, E. G. Villora, K. Shimamura, N. Ichinose, M. Honda, Phys. Rev. B 68, 155207 (2003).

- [45] M. Yamaga, H. Tsuzuki, S. Takano, E. G. Villora, K. Shimamura, J. Non-Cryst. Solids 358, 2458 (2012).

- [46] J. Bang, S. Matsuishi, H. Hosono, Appl. Phys. Lett. 110, 232105 (2017).

- [47] Y. Hanyu, K. Domen, K. Nomura, H. Hiramatsu, H. Kumomi, H. Hosono, T. Kamiya, Appl. Phys. Lett. 103, 202114 (2013).

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0159529

[48] C.-H. Hsu, X.-P. Geng, W.-Y. Wu, M.-J. Zhao, X.-Y. Zhang, P.-H. Huang, S.-Y. Lien, Molecules **25**, 5043 (2020).

[49] Y. Magari, T. Kataoka, W. Yeh, M. Furuta, Nat. Commun. 13, 1078 (2022).

[50] M. H. Wong, Y. Nakata, A. Kuramata, S. Yamakoshi, M. Higashiwaki, Appl. Phys. Express 10, 041101 (2017).

[51] N. A. Moser, J. P. McCandless, A. Crespo, K. D. Leedy, A. J. Green, E. R. Heller, K. D. Chabak, N. Peixoto, G. H. Jessen, Appl. Phys. Lett. 110, 143505 (2017).

[52] Y. Yoon, M. J. Kim, B. J. Cho, M. Shin, W. S. Hwang, Appl. Phys. Lett. 119, 122103 (2021).

[53] F. H. Alshammari, M. K. Hota, Z. Wang, H. Al-jawhari, H. N. Alshareef, Adv. Electron. Mater. 3, 1700155 (2017).

[54] H. Chang, C.-H. Huang, K. Nomura, ACS Appl. Electron. Mater. 3, 4943 (2021).