## **UC Berkeley**

## **UC Berkeley Previously Published Works**

## **Title**

A Platform-Based Design Methodology With Contracts and Related Tools for the Design of Cyber-Physical Systems

## **Permalink**

https://escholarship.org/uc/item/15r8r6k6

## **Journal**

Proceedings of the IEEE, 103(11)

## **ISSN**

0018-9219

## **Authors**

Nuzzo, Pierluigi Sangiovanni-Vincentelli, Alberto L Bresolin, Davide et al.

## **Publication Date**

2015

## DOI

10.1109/jproc.2015.2453253

Peer reviewed

# A Platform-Based Design Methodology with Contracts and Related Tools for the Design of Cyber-Physical Systems

Pierluigi Nuzzo, Alberto Sangiovanni-Vincentelli, Davide Bresolin, Luca Geretti, Tiziano Villa

Abstract—We introduce a platform-based design methodology that uses contracts to specify and abstract the components of a cyber-physical system (CPS), and provide formal support to the entire CPS design flow. The design is carried out as a sequence of refinement steps from a high-level specification to an implementation built out of a library of components at the lower level. We review formalisms and tools that can be used to specify, analyze or synthesize the design at different levels of abstractions. For each level, we highlight how the contract operations can be concretely computed as well as the research challenges that should be faced to fully implement them. We illustrate our approach on the design of embedded controllers for aircraft electric power distribution systems.

#### I. Introduction

LARGE number of new IT applications are emerging, which go beyond the traditional boundaries between computation, communication and control. The majority of these applications, such as "smart" buildings, "smart" traffic, "smart" grids, "smart" cities, cyber security, and health-care wearables, build on *distributed, networked sense-and-control platforms*, characterized by the tight integration of "cyber" aspects (computing and networking) with "physical" ones (e.g., mechanical, electrical, and chemical processes). In these *cyber-physical systems* (CPS) [1], [2], [3] computational devices monitor and control the physical processes, usually with feedback loops where physics affects computation and *vice versa*.

Intelligent systems that gather, process and apply information are changing the way entire industries operate, and have the potential to radically influence how we deal with a broad range of crucial societal problems. As embedded digital electronics becomes pervasive and cost-effective, codesign of both the cyber and the physical portions of these systems shows promise of making the holistic system more

- P. Nuzzo and A. Sangiovanni-Vincentelli are with the Department of Electrical Engineering and Computer Sciences, University of California, Berkeley, USA. Email: {nuzzo, alberto}@eecs.berkeley.edu.

- D. Bresolin is with the Department of Computer Science and Engineering, University of Bologna, Bologna, Italy. Email: davide.bresolin@unibo.it.

- L. Geretti is with the Department of Electrical Engineering (DIEGM), University of Udine, Udine, Italy. Email: luca.geretti@univr.it.

- T. Villa is with the Department of Computer Science, University of Verona, Verona, Italy, Email: tiziano.villa@univr.it.

This work was supported in part by IBM and UTC via the iCyPhy consortium, by the TerraSwarm Research Center, one of six centers supported by the STARnet phase of the Focus Center Research Program (FCRP), a Semiconductor Research Corporation program sponsored by MARCO and DARPA, and by the EU Commission through the EU project FP7-ICT-223844 CON4COORD.

capable and efficient. However, CPS complexity and heterogeneity, originating from combining what in the past have been separate worlds, tend to substantially increase the design and verification challenges.

A serious obstacle to the efficient realization of CPS is the inability to rigorously model the interactions among heterogeneous components and between the physical and the cyber sides. CPS design entails the convergence of several sub-disciplines, and tends to stress all existing modeling languages and frameworks, which are hardly interoperable today. While in computer science logic is emphasized rather than dynamics, and processes follow a sequential semantics, physical processes are generally represented using continuoustime dynamical models, often expressed as differential equations, which are acausal, concurrent models. It is therefore difficult to accurately capture the interactions between these two worlds. Moreover, a severe limitation in common design practice is the lack of formal specifications. Requirements are written in languages that are not suitable for mathematical analysis and verification. Assessing system correctness is then left for simulation and, later in the design process, prototyping. Thus, the traditional heuristic design process based on informal requirements and designers' experience can lead to implementations that are inefficient and sometimes do not even satisfy the requirements, yielding long re-design cycles, cost overruns and unacceptable delays.

The cost of being late to market or of product malfunctioning is staggering as witnessed by the recent recalls and delivery delays that system industries had to bear. Toyota's infamous recall of approximately 9 million vehicles due to the sticky accelerator problem<sup>1</sup>, Boeing's 787 delay bringing an approximate toll of \$3.3 billion<sup>2</sup> are examples of devastating effects that design problems may cause. If this is the present situation, the problem of designing planetary-scale CPS appears insurmountable unless bold steps are taken to bridge the gap between *system science* and *system engineering*.

Several languages and tools have been proposed over the years to overcome the limitations above and enable model-based development of CPS. However, an all-encompassing framework for CPS design that interconnects different tools, possibly operating on different system representations, is still missing [3]. By reflecting on the history of achievements of electronic design automation in taming the design complexity

<sup>1</sup> see e.g., http://www.autorecalls.us

<sup>&</sup>lt;sup>2</sup>see, e.g., http://en.wikipedia.org/wiki/Boeing\_787

of VLSI systems, we advocate that CPS design automation efforts are doomed to be impractical and poorly scalable, unless they are framed in *structured design methodologies* and in a formalization of the design process in a *hierarchical* and *compositional* way. Hierarchy has been instrumental to scalable VLSI design, where boosts in productivity have always been associated with a rise in the level of abstraction of design capture, from transistor to register transfer level (RTL), to systems-on-chip. On the other hand, designers typically assemble large and complex systems from smaller and simpler components, such as pre-designed intellectual property (IP) blocks. Therefore, compositional approaches offer a "natural" perspective that should inform the whole design process, starting from its earlier stages.

In this paper, we present a path towards an integrated framework for CPS design; the pillars for the framework are a methodology that relies on the platform-based design paradigm (PBD) [4] and the algebra of *contracts* to formalize the design process and enable the realization of systems in a hierarchical and compositional manner. Contracts are mathematical abstractions, explicitly defining the assumptions of each component on its environment and the guarantees of the component under these assumptions. The design is carried out as a sequence of refinement steps from a highlevel specification to an implementation built out of a library of components at the lower level. The high-level specification is first formalized in terms of contracts to enable requirement validation and early detection of inconsistencies. Then, at each step, contracts are refined by combining synthesis, optimization and simulation-based design space exploration methods.

We review formalisms and tools that can be used to specify, analyze or synthesize the design at different levels of abstractions, from the level of discrete systems, to the one of hybrid systems. For each formalism, we highlight how the contract operators can be computed, and expose the main research challenges for their implementation. We conclude by illustrating our approach on the design of embedded controllers for aircraft electric power distribution systems.

# II. PLATFORM-BASED DESIGN WITH CONTRACTS FOR CYBER-PHYSICAL SYSTEMS

We consider in this paper a particular case of CPS that incorporates most, if not all, of the features of general CPSs, to help explain the methodology: a *control system*, composed of a physical *plant*, including sensors and actuators, and an embedded *controller*. The controller runs a *control algorithm* to restrict the behaviors of the plant so that all the remaining (closed-loop) behaviors satisfy a set of *system requirements*. Specifically, we consider *reactive controllers*, i.e. controllers that maintain an ongoing relation with their *environment* by appropriately reacting to it. Our goal is to design the *system architecture*, i.e. the interconnection among system components, and the control algorithm, to satisfy the set of high-level requirements.

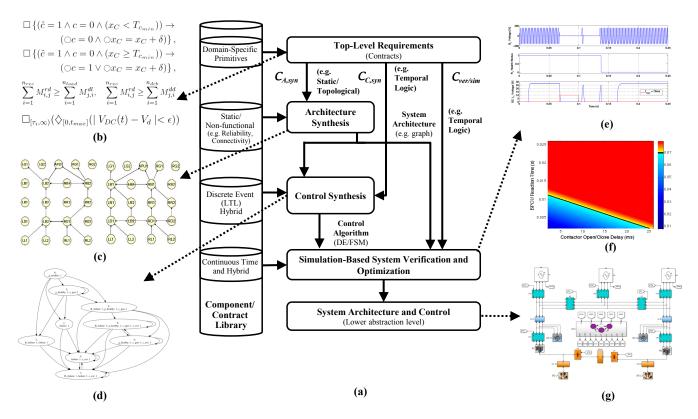

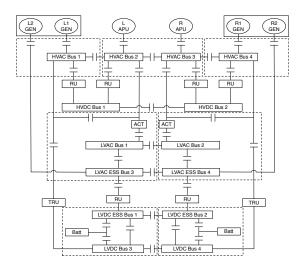

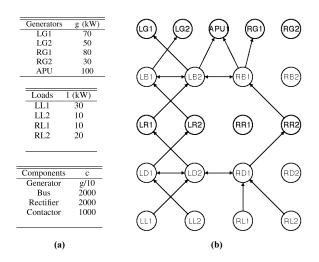

As shown in Fig. 4 (a), the design methodology consists of two main steps, namely, system architecture design and control design. The *system architecture design* step instantiates

system components and interconnections among them to generate an optimal architecture while guaranteeing the desired performance, safety and reliability. Typically, this design step includes the definition of both the embedded system and the plant architectures. The *embedded system architecture* consists of software, hardware, and communication components, while the *plant architecture* depends on the physical system under control, and may consist of mechanical, electrical, hydraulic or thermal components. Sensors and actuators reside at the boundary between the embedded system and the plant [5]. Given an architecture, the *control design* step includes the exploration of the control algorithm and its deployment on the embedded platform.

The above two steps are however connected. The correctness of the controller needs to be enforced in conjunction with the assumptions on the plant. Similarly, performance and reliability of an architecture should be assessed for the plant in closed loop with the controller.

At the highest level of abstraction, the starting point is a set of requirements, predominantly written in text-based languages that are not suitable for mathematical analysis and verification. The result is a model of both the architecture and the control algorithms to be further refined in subsequent design stages. We place this process in the form of Platform-Based Design and we use contracts extensively to verify the design and to build refinements that are correct by construction.

## A. Platform-Based Design

In PBD, at each step, top-down refinements of high-level specifications are mapped onto bottom-up abstractions and characterizations of potential implementations. Each abstraction layer is defined by a design *platform*, which is the set of all architectures that can be built out of a *library* (collection) of *components* according to *composition rules*. In the *bottom-up phase* of each design step, we build and model the component library (including both plant and controller). In the *top-down phase*, we formalize the high-level system requirements and we perform an optimization (refinement) phase called *mapping*, where the requirements are mapped onto the available implementation library components and their composition.

Mapping is cast as an optimization problem, where a set of performance metrics and quality factors are optimized over a space constrained by both system requirements and component feasibility constraints. Mapping is the mechanism that allows to move from a level of abstraction to a lower one using the available components within the library. Note that when some constraint cannot be satisfied using the available library components or the mapping result is not satisfactory for the designer, additional elements can be designed and inserted into the library. For example, when implementing an algorithm with code running on a processor, we are assigning the functionality of the algorithm to a processor and the code is the result of mapping the "equations" describing the algorithm onto the instruction set of the processor. If the processor is too slow, then real-time constraints may be violated. In this case,

a new processor has to be found or designed that executes the code fast enough to satisfy the real-time constraint. In the mapping phase, we consider different *viewpoints* (aspects, concerns) of the system (e.g. functional, reliability, safety, timing) and of the components.

If the design process is carried out as a sequence of refinement steps from the most abstract representation of the design platform (top-level requirements) to its most concrete representation (physical implementation), providing guarantees on the correctness of each step becomes essential. Specifically, we seek mechanisms to formally prove that: (i) a set of requirements are *consistent*, i.e. there exists an implementation satisfying all of them; (ii) an aggregation of components is compatible, i.e. there exists an environment in which they can correctly operate; (iii) an aggregation of components refines a specification, i.e. it implements the specification and is able to operate in any environment admitted by it. Moreover, whenever possible, we require the above proofs to be performed automatically and efficiently, to tackle the complexity of today's CPS. Therefore, to formalize the above design concepts, and enable the realization of system architectures and control algorithms in a hierarchical and compositional manner that satisfies the constraints and optimizes the cost function(s), we resort to *contracts*.

#### B. Contracts: An Overview

The notion of contracts originates in the context of compositional assume-guarantee reasoning [6], which has been used for a long time, mostly for software verification. In a contract framework, design and verification complexity is reduced by decomposing system-level tasks into more manageable subproblems at the component level, under a set of assumptions. System properties can then be inferred or proved based on component properties. Rigorous contract theories have been developed over the years, including assume-guarantee (A/G) contracts [7] and interface theories [8]. However, their concrete adoption in CPS design is still in its infancy, a major challenge being the absence of a comprehensive modeling formalism for CPS, due to their complexity and heterogeneity [9], [10].

In this paper, we adopt the assume-guarantee (A/G) contract framework, as introduced by Benveniste et al. [7], [10], to reason about requirements and their refinement during the design process. Because of the explicit distinction between component and environment, A/G contracts are deemed as a rigorous yet intuitive framework, which directly conforms to the thought process of a designer, aiming to guarantee certain performance figures for the design under specific assumptions on its environment. An integration language incorporating A/G contracts to formalize system requirements and enable the generation of simulation monitors has been proposed within the META research program [11], with the aim to compress the product development and deployment timeline of defense systems. Furthermore, over the last few years, many publications have demonstrated the application of A/G contracts in different domains, such as automotive [12], [13], analog integrated systems [5] and, more recently, synthesis and verification of control algorithms for CPS [14], [15], [16], [17].

Since A/G contracts are centered around *behaviors*, they are expressive and versatile enough to encompass all kinds of models encountered in system design, from hardware and software models to representations of physical phenomena [10], [18]. The particular structure of the behaviors is defined by specific instances of the contract model. This will only affect the way operators in the contract algebra are implemented, since the basic definitions will not vary.

In the sequel, before describing the steps of our methodology, we detail the notions of components and contracts.

#### C. Components and Contracts

Since PBD is based on the composition of components while refining the design, we start our analysis with a formal representation of a component and we associate to it a set of properties that the component satisfies expressed with contracts. The contracts will be used to verify the correctness of the composition and of the refinements.

A component M can be seen as an abstraction representing an element of a design, characterized by the following attributes:

- a set of input U, output Y and internal X variables (including state variables); a set of configuration parameters K, and a set of input, output and bidirectional ports Λ. Components can be connected together by sharing certain ports under constraints on the values of certain variables. In what follows, to simplify, we use the same term variables to denote both component variables and ports;

- a set of behaviors, which can be implicitly represented by a dynamic behavioral model F(u, y, x, κ) = 0, uniquely determining the values of the output (y ∈ Y) and internal (x ∈ X) variables given the values of the input variables (u ∈ U) and configuration parameters (κ ∈ K). Components can respond to every possible sequence of input variables, i.e. they are receptive to their input variables. Behaviors are generic and could be continuous functions that result from solving differential equations, or sequences of values or events recognized by an automata model. In the following, we also use [M] to denote the set of behaviors of a component;

- a set of non-functional models, i.e. maps that allow computing non-functional attributes of a component, corresponding to particular valuations of its input variables and configuration parameters. Examples of non-functional maps include the performance model  $\mathcal{P}(.)=0$ , computing a set of performance figures (e.g. bandwidth, latency) by solving a behavioral model, or the reliability model  $\mathcal{R}(.)=0$ , providing the failure probability of a component.

Components can be hierarchically organized to represent the system at different levels of abstraction. A system can then be assembled by *parallel composition* and interconnection of components at level l, and represented as a new component at level l+1. We denote the composition of two components  $M_1$  and  $M_2$ , when it is defined, as  $M_1 \times M_2$ . Then, the behaviors of the composition can be described, in

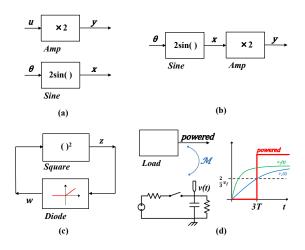

Fig. 1. Pictorial representation of the components and interconnections used to illustrate some of the contract operations and relations: (a) parallel composition, (b) serial composition, (c) feedback composition, (d) heterogeneous refinement.

general, as the intersection of the behaviors of its components, i.e.  $[\![M_1 \times M_2]\!] = [\![M_1]\!] \cap [\![M_2]\!]$ . At each level of abstraction, components are also capable of exposing multiple, complementary *viewpoints*, associated with different design concerns (e.g. safety, performance, reliability) and with models that can be expressed via different formalisms, and analyzed by different tools. Finally, a component M may be associated with a contract, offering a *specification* for it, as further detailed below.

To simplify, in the sequel, we always refer to components with a fixed configuration, i.e. components in which the configuration parameters K are fixed. Then, a contract  $\mathcal C$  for a component M is a triple (V,A,G), where  $V=U\cup Y\cup X$  is the set of component variables, and A and G are assertions, each representing a set of behaviors over V [7]. A represents the assumptions that M makes on its environment, and G represents the guarantees provided by M under the environment assumptions.

A component M satisfies a contract  $\mathcal C$  whenever M and  $\mathcal C$  are defined over the same set of variables, and all the behaviors of M satisfy the guarantees of  $\mathcal C$  in the context of the assumptions, i.e. when  $[\![M]\!]\cap A\subseteq G$ . We denote this satisfaction relation by writing  $M\models \mathcal C$ , and we say that M is an implementation of  $\mathcal C$ . However, a component E can also be associated to a contract  $\mathcal C$  as an environment. We say that E is a legal environment of  $\mathcal C$ , and write  $E\models_E \mathcal C$ , whenever E and  $\mathcal C$  have the same variables and  $[\![E]\!]\subseteq A$ .

As an example, we consider the amplifier component *Amp* represented in Fig. 1 (a), whose amplification gain is two. To specify its operation, we can then formulate a simple (stateless) contract as follows:

$$C_{amp} = (\{u, y\}, \{(u, y) \in \mathbb{R}^2 | |u| \le 1\}, \{(u, y) \in \mathbb{R}^2 | y = 2u\}),$$

where we use |u| to denote the absolute value of u, and constraints (predicates) on the real variables u and y to characterize the sets of assumptions and guarantees of  $C_{amp}$ . For

brevity's sake, when the domain of all the component variables is known, we can also represent assumptions and guarantees directly in terms of predicates, e.g.,  $\mathcal{C}_{amp}=(\{u,y\},|u|\leq 1,y=2u)$ , where we implicitly assume that an assumption predicate  $\phi_A$  and a guarantee predicate  $\phi_G$  are both interpreted over the whole set of contract variables. Moreover, A and G will be, respectively, the set of all the behaviors satisfying  $\phi_A$  and  $\phi_G$ .

The component Amp duplicates the value of any real number u in the interval [-1,1], provided as an input. Because the behavior of Amp is only determined for a specific input range, there is potentially an infinite number of implementations for  $\mathcal{C}_{amp}$ . In particular, a component  $M_{amp}$ , defined over the same set of variables  $\{u,y\}$ , and enforcing y=2u for all  $u\in\mathbb{R}$ , is certainly an implementation for  $\mathcal{C}_{amp}$ , i.e.  $M_{amp}\models\mathcal{C}_{amp}$ . In fact, its set of behaviors  $[\![M_{amp}]\!]=\{(u,y)\in\mathbb{R}^2|y=2u\}$ , coincides with the guarantees of  $\mathcal{C}_{amp}$ , and therefore  $[\![M_{amp}]\!]\cap A_{amp}\subseteq G_{amp}$  trivially holds. On the other hand, let  $M'_{amp}$  be an amplifier with saturation, defined over the same set of variables  $\{u,y\}$ , and characterized by the following behavioral model:

$$M'_{amp}: \begin{cases} y = 2u & \forall u \in \mathbb{R} : -1 \le u \le 1, \\ y = -2 & \forall u \in \mathbb{R} : u < -1, \\ y = 2 & \forall u \in \mathbb{R} : u > 1. \end{cases}$$

(1)

$M'_{amp}$  blocks its output to a constant value when the magnitude of its input exceeds one. However, in the context of the assumptions  $A_{amp}$ , it satisfies  $G_{amp}$ ; therefore, by definition of contract satisfaction,  $M'_{amp}$  is also an implementation of  $\mathcal{C}_{amp}$ .

Any component satisfying the assumptions of  $\mathcal{C}_{amp}$  is a legal environment for it; specifically, a component  $E_{amp}$ , defined over  $\{u,y\}$ , and providing as an output u=0 for all  $y\in\mathbb{R}$  is legal, i.e.  $E_{amp}\models_E\mathcal{C}_{amp}$ . Moreover, given a legal environment  $E_{amp}$ , the composition  $E_{amp}\times M_{amp}$ , for all implementations  $M_{amp}$ , generates a closed system.

Two contracts  $\mathcal C$  and  $\mathcal C'$  with identical variables, identical assumptions, and such that  $G'\cup\overline A=G\cup\overline A$ , where  $\overline A$  is the complement of A, possess identical sets of environments and implementations. Such two contracts are then equivalent. In particular, any contract  $\mathcal C$  is equivalent to a contract in saturated form  $\mathcal C'$ , obtained by taking  $G'=G\cup\overline A$ . For instance, the contract  $\mathcal C'_{amp}=(\{u,y\},|u|\leq 1,|u|\leq 1\to y=2u)$  is equivalent to  $\mathcal C_{amp}$ , since it has the same sets of environments and implementations. However, differently than  $\mathcal C_{amp}$ ,  $\mathcal C'_{amp}$  is in saturated form; its set of guarantees  $G'_{amp}=(\{u,y\},|u|>1\lor y=2u)$  is maximal, and coincides with the union of the behaviors of all its implementations. In what follows, we assume that all contracts are in saturated form.

1) Composition: Contracts associated to different components can be combined according to different rules. Similar to parallel composition of components, parallel composition ( $\otimes$ ) of contracts can be used to construct composite contracts out of simpler ones. Let  $\mathcal{C}_1 = (V, A_1, G_1)$  and  $\mathcal{C}_2 = (V, A_2, G_2)$  be contracts (in saturated form) over the same set of variables V. The composite contract  $\mathcal{C}_1 \otimes \mathcal{C}_2$  is defined as the triple

(V, A, G) where:

$$A = (A_1 \cap A_2) \cup \overline{(G_1 \cap G_2)} \tag{2}$$

$$G = G_1 \cap G_2. \tag{3}$$

The composite contract must satisfy the guarantees of both, which explains the operation of intersection in (3) [10]. Intuitively, the assumptions of the composite contract should also be the conjunction of the assumptions of each contract, since the environment should satisfy all the assumptions. However, in general, part of the assumptions  $A_1$  will be already satisfied by composing  $C_1$  with  $C_2$ , acting as a partial environment for  $C_1$ . Therefore,  $G_2$  can contribute to relaxing the assumptions  $A_1$ , and vice versa.

As an example, let us consider a simple producer-consumer system, where the producer  $M_1$  is interconnected in series with the consumer  $M_2$ , sharing the variable  $y \in \mathbb{R}$ . Let  $\mathcal{C}_1 = (\{y\}, \mathbb{T}, y > 0)$  and  $\mathcal{C}_2 = (\{y\}, y > 0, \mathbb{T})$  be the two contracts specifying the behaviors of  $M_1$  and  $M_2$ , respectively, both in saturated form. In this example, both assumptions and guarantees are expressed as predicates on y, and  $\mathbb{T}$  is the Boolean value True.  $M_1$  guarantees that y is a positive number, which coincides with the assumption made by  $M_2$  on its environment. Then, by applying (2) and (3), we obtain G = (y > 0) and  $A = (y > 0) \vee (y \leq 0) = \mathbb{T}$ , denoting that the composite system is able to operate in any environment, which is intuitive, since the assumptions of  $M_2$  on its environment are relaxed by the guarantees of  $M_1$ .

Specifically, when computing (2), we are interested in the maximum set of behaviors A such that  $A \cap G_2 \subseteq A_1$  and  $A \cap G_1 \subseteq A_2$ , where "maximum" refers to the order of sets by inclusion [10]. This is equivalent to finding:

$$A = \max\{A'|A' \subseteq A_1 \cup \overline{G_2}, A' \subseteq A_2 \cup \overline{G_1}\}$$

$$= (A_1 \cup \overline{G_2}) \cap (A_2 \cup \overline{G_1})$$

$$= (A_1 \cap A_2) \cup (A_1 \cap \overline{G_1}) \cup (A_2 \cap \overline{G_2}) \cup (\overline{G_1} \cap \overline{G_2})$$

$$= (A_1 \cap A_2) \cup \overline{G_1} \cup \overline{G_2},$$

$$(4)$$

which reduces to (2). The last equality in (4) stems from the fact that  $G = G \cup \overline{A}$  holds for a contract  $\mathcal{C} = (V, A, G)$  in saturated form. Contract composition preserves saturated form, that is, if  $\mathcal{C}_1$  and  $\mathcal{C}_2$  are in saturated form, then so is  $\mathcal{C}_1 \otimes \mathcal{C}_2$ . Moreover,  $\otimes$  is associative and commutative and generalizes to an arbitrary number of contracts. We therefore can write  $\mathcal{C}_1 \otimes \mathcal{C}_2 \otimes \cdots \otimes \mathcal{C}_n$ .

For composition to be defined, contracts need to be over the same set of variables V. If this is not the case, then, before composing the contracts, we must first extend their behaviors to a common set of variables using an inverse projection type of transformation, which we call alphabet equalization. Formally, let  $\mathcal{C}=(V,A,G)$  be a contract and let  $V'\supseteq V$  be the set of variables on which we want to extend  $\mathcal{C}$ . The extension of  $\mathcal{C}$  on V' is the new contract  $\mathcal{C}'=(V',A',G')$  where A' and G' are sets of behaviors over V', defined by inverse projection of A and G, respectively. In the sequel, we freely compose contracts  $\mathcal{C}_1$  and  $\mathcal{C}_2$  over arbitrary sets of variables  $V_1,V_2$ , by implicitly first taking their extensions to  $V=V_1\cup V_2$ .

As an example, consider the component Sine shown in Fig. 1 (a), which receives as input an angle  $\theta$  and produces an output proportional to the sine of  $\theta$ . We would like to characterize the contract  $\mathcal{C}_{sin} \otimes \mathcal{C}'_{amp}$ , specifying the parallel composition of Amp and Sine, where  $\mathcal{C}_{sin} = (\{\theta, x\}, \mathbb{T}, x = 2\sin\theta)$ . Moreover, we assume that the components interact by sharing their input variables, which we capture by renaming u as  $\theta$ . Then, to combine correctly the assumptions and guarantees according to (2) and (3), we first need to extend them to the variable set  $\{\theta, x, y\}$ , thus obtaining

$$\begin{aligned} \mathcal{C}''_{amp} &= (\{\theta, x, y\}, |\theta| \leq 1, (|\theta| \leq 1) \rightarrow (y = 2\theta)) \\ \mathcal{C}'_{sin} &= (\{\theta, x, y\}, \mathtt{T}, x = 2\sin\theta). \end{aligned}$$

Finally, we can compute the assumptions and guarantees of the composite contract as follows:

$$\begin{split} G_{\otimes} &:= (x = 2\sin\theta) \wedge ((y = 2\theta) \vee (|\theta| > 1)) \\ A_{\otimes} &:= (|\theta| \le 1) \vee (x \ne 2\sin\theta) \vee ((y \ne 2\theta) \wedge (|\theta| \le 1)) \\ &= (|\theta| \le 1) \vee (x \ne 2\sin\theta). \end{split}$$

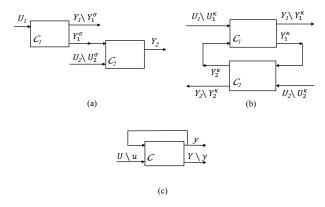

As informally introduced by the producer-consumer example above, both serial and feedback compositions of contracts can be defined using the notion of parallel composition. Feedback composition in the context of contracts has also been investigated in a seminal paper by Benvenuti et al. [19]. Let  $\mathcal{C}_1 = (V_1, A_1, G_1)$  and  $\mathcal{C}_2 = (V_2, A_2, G_2)$  be two contracts, in which the variable sets  $V_1 = U_1 \cup Y_1$  and  $V_2 = U_2 \cup Y_2$ are, respectively, partitioned into finite sets of input  $(U_1, U_2)$ and output variables  $(Y_1, Y_2)^3$ . Moreover, we assume that all sets  $U_1, Y_1, U_2, Y_2$  are pairwise disjoint. Then, a serial interconnection structure  $\sigma$ , defined as a subset of pairs of  $Y_1 \times U_2$ , i.e.  $\sigma \subseteq Y_1 \times U_2$ , generates a renaming on  $\mathcal{C}_2$ where, for each pair  $(y, u) \in \sigma$ , u is renamed as y. Let  $Y_1^{\sigma} = \{y | \exists u : (y, u) \in \sigma\} \text{ and } U_2^{\sigma} = \{u | \exists y : (y, u) \in \sigma\}.$ As represented in Fig. 2 (a), we can then define a renaming operator on  $C_2$ ,  $ren_{\sigma}(C_2)$ , which returns a new contract  $C_2^{\sigma} = (U_2 \setminus U_2^{\sigma} \cup Y_1^{\sigma} \cup Y_2, A_2^{\sigma}, G_2^{\sigma}), \text{ where } A_2^{\sigma} \text{ and } G_2^{\sigma}$ are obtained from  $A_2$  and  $G_2$  after renaming their respective variables according to  $\sigma$ . Finally, we can define the *serial* composition of  $C_1$  and  $C_2$  as  $C_1 \stackrel{\sigma}{\leadsto} C_2 := C_1 \otimes C_2^{\sigma}$ . For example, we compute the cascade composition of  $\mathcal{C}_{sin} \stackrel{\sigma}{\leadsto} \mathcal{C}_{amp}$  for  $\sigma = \{(x, u)\},$  as shown in Fig. 1 (b). After renaming and alphabet equalization, by using (2) and (3), we obtain:

$$G_{\sigma} := (x = 2\sin\theta) \wedge ((y = 2x) \vee (|x| > 1))$$

$$A_{\sigma} := (|x| \le 1) \vee (x \ne 2\sin\theta),$$

where both predicates are now to be interpreted on  $\{\theta, x, y\}$ .

Similarly, a feedback interconnection structure  $\kappa$  can be defined as a subset of pairs  $\kappa \subseteq (Y_1 \times U_2) \cup (Y_2 \times U_1)$ , thus generating a renaming on both  $\mathcal{C}_1$  and  $\mathcal{C}_2$  where, for each pair  $(y,u) \in \kappa$ , u is renamed as y. Let  $Y_1^{\kappa} = \{y \in Y_1 | \exists u \in U_2 : (y,u) \in \kappa\}$ ,  $U_2^{\kappa} = \{u \in U_2 | \exists y \in Y_1 : (y,u) \in \kappa\}$ ,  $Y_2^{\kappa} = \{y \in Y_2 | \exists u \in U_1 : (y,u) \in \kappa\}$ ,

$<sup>^3</sup>$ To simplify, we do not explicitly mention the internal variables X of a contract in our discussion of serial and feedback compositions, since we can assume, without loss of generality, that X is a subset of the output variables Y.

Fig. 2. Pictorial representation of different examples of contract compositions: (a) serial composition, (b) feedback composition of two contracts, (c) feedback composition of one contract.

and  $U_1^\kappa = \{u \in U_1 | \exists y \in Y_2 : (y,u) \in \kappa\}$ . We can then define a *renaming* operator  $ren_\kappa$  on  $\mathcal{C}_1$  and  $\mathcal{C}_2$ , which returns the new contracts  $\mathcal{C}_1^\kappa = (U_1 \setminus U_1^\kappa \cup Y_2^\kappa \cup Y_1, A_1^\kappa, G_1^\kappa)$ , and  $\mathcal{C}_2^\kappa = (U_2 \setminus U_2^\kappa \cup Y_1^\kappa \cup Y_2, A_2^\kappa, G_2^\kappa)$ , as represented in Fig. 2 (b). Finally, we can define the *feedback composition* of  $\mathcal{C}_1$  and  $\mathcal{C}_2$  as  $\mathcal{C}_1 \circ_\kappa \mathcal{C}_2 := \mathcal{C}_1^\kappa \otimes \mathcal{C}_2^\kappa$ .

A special case of feedback interconnection occurs when a set of outputs of a contract is directly connected to a set of its inputs, as represented in Fig. 2 (c). For instance, given a contract  $\mathcal{C} = (V, A, G)$ , in which  $V = U \cup Y$ , with U and Y finite sets of input and output variables, and  $U \cap Y = \emptyset$ , let  $\kappa = (y, u) \in Y \times U$  be a feedback interconnection on C, connecting an output of C to one of its inputs, and let  $C_{id,\kappa} = (\{y,u\}, T, y = u)$  a contract which guarantees that the variables supposed to be connected in  $\kappa$  are set to be equal. To simplify, we express the guarantees of  $C_{id,\kappa}$  by using a stateless constraint over its variable set; however, stateful extensions, including temporal constructs, are straightforward. We can then reduce the feedback connection on a contract to the general case of feedback composition defined above, by redefining the new contract generated by  $\kappa$  as  $\kappa(\mathcal{C}) :=$  $\mathcal{C} \circ_{\kappa} \mathcal{C}_{id,\kappa} = \mathcal{C}^{\kappa}$ . It is then possible to extend the notions of compatibility and consistency of contracts to their serial and feedback compositions as further discussed below.

2) Compatibility and Consistency:  $\mathcal C$  is compatible if there exists a legal environment E for it, i.e. if and only if  $A \neq \emptyset$ . The intent is that a component satisfying contract  $\mathcal C$  can only be used in the context of a compatible environment, to be assured that its behaviors conform with the ones specified by the contract. Similarly, a contract is consistent when the set of implementations satisfying it is not empty, i.e. it is feasible to develop implementations for it. For contracts in saturated form, this amounts to verify that  $G \neq \emptyset$ .

When there is a clear distinction between input (uncontrolled) and output (controlled) variables, different notions of contract compatibility and consistency can be defined [7], [9], [18]. Let  $U \subseteq V$  and  $Y \subseteq V$  be, respectively, the subset of input and output variables of C, with  $U \cap Y = \emptyset$ . Then C is compatible if and only if A is Y-receptive, i.e. if and only if for all behaviors  $\rho'$  restricted to variables in Y, there exists a behavior  $\rho \in A$ , such that  $\rho'$  and  $\rho$  coincide over Y. Intuitively,

an environment has no control on the variables set by an implementation, and therefore A accepts any history offered to the subset Y of its variables. Similarly,  $\mathcal{C}$  is consistent if and only if G is X-receptive.

Based on these definitions,  $\mathcal{C}_{amp}$  and  $\mathcal{C}_{sin}$  are both compatible and consistent, while a contract  $\mathcal{C}_{amp1} = (\{u,y\}, |u| \leq 2, |u| \leq 1 \rightarrow (y = 2u) \land (y > 3))$  is compatible but inconsistent. In fact, compatibility checking amounts to ask whether  $\forall y: |u| \leq 2$  is satisfiable, which is true. On the other hand, consistency checking produces  $\forall u: |u| \leq 1 \rightarrow (y = 2u) \land (y > 3) = \mathbb{F}$  (F being the Boolean value False), since it is impossible to satisfy the guarantees of  $\mathcal{C}_{amp1}$  for any u in the interval  $[-1,1]^4$ .

The definitions above can be lifted to pairs of contracts, so that  $\mathcal{C}_1$  and  $\mathcal{C}_2$  are compatible (consistent) if and only if  $\mathcal{C}_1 \otimes \mathcal{C}_2$  is compatible (consistent). As an example, we show how to derive compatibility and consistency conditions for the cascade of contracts in Fig. 2 (a). To be concrete, we assume that the assumptions and guarantees of  $\mathcal{C}_1$  and  $\mathcal{C}_2$  are represented in terms of predicates or logic formulas on their variables, i.e.  $\mathcal{C}_1 = (U_1 \cup Y_1, \phi_{A1}, \phi_{G1})$  and  $\mathcal{C}_2 = (U_2 \setminus U_2^{\sigma} \cup Y_1^{\sigma} \cup Y_2, \phi_{A2}, \phi_{G2})$ . Moreover, since  $\mathcal{C}_1$  and  $\mathcal{C}_2$  are in saturated form, both  $\phi_{A1} \vee \phi_{G1} = \mathbb{T}$  and  $\phi_{A2} \vee \phi_{G2} = \mathbb{T}$  must hold. We can then compute assumptions and guarantees for the composite contract  $\mathcal{C}_{\sigma} = \mathcal{C}_1 \stackrel{\sigma}{\leadsto} \mathcal{C}_2$  by applying (2) and (3) as follows:

$$\phi_{G\sigma} = \phi_{G1} \wedge \phi_{G2} \tag{5}$$

$$\phi_{A\sigma} = (\phi_{A1} \wedge \phi_{A2}) \vee \neg \phi_{G1} \vee \neg \phi_{G2}, \tag{6}$$

where  $\phi_{G\sigma}$  and  $\phi_{A\sigma}$  must be interpreted as predicates or formulas over the entire set of variables  $U_1 \cup Y_1 \cup U_2 \setminus U_2^{\sigma} \cup Y_2$ . In a general case, we would already conclude that  $\mathcal{C}_1$  and  $\mathcal{C}_2$  are compatible if and only if  $\phi_{A\sigma}$  is satisfiable. Similarly,  $\mathcal{C}_1$  and  $\mathcal{C}_2$  are consistent if and only if  $\phi_{G\sigma}$  is satisfiable. However, to gather more insight into compatibility checking, we will further discuss a special case, which is still relevant to several application domains.

We assume that each component of a system only controls its output ports, while the inputs are assigned by the external environment. In this scenario, the assumptions of each contract will only involve its input variables, since the outputs will be under the responsibility of the implementations. Specifically, for the system in Fig. 2 (a),  $\phi_{A1}$  and  $\phi_{A2}$  will depend, respectively, only on  $U_1$  and  $Y_1^{\sigma} \cup U_2 \setminus U_2^{\sigma}$ , while  $\phi_{G1}$  and  $\phi_{G2}$  will describe relations involving both the input and output variables of each contract. Finally, we assume that the original contracts  $\mathcal{C}_1$  and  $\mathcal{C}_2$  are themselves compatible and consistent. In fact, if any contract is incompatible, then it cannot be used in any context; if any contract is inconsistent, it translates into a specification that generates  $per\ se$  a contradiction, and cannot be implemented.

Our objective is to determine the conditions on the input variables  $U_1 \cup U_2 \setminus U_2^{\sigma}$  that make the composite contract  $\mathcal{C}_{\sigma}$

<sup>&</sup>lt;sup>4</sup>In several practical situations, we are interested in contracts that are compatible and consistent at the same time, i.e. satisfying  $G \cap A \neq \emptyset$ , to discard pathological situations of contracts which are compatible but not consistent, or consistent but not compatible.

compatible. To do so, since the variables in  $Y_1 \cup Y_2$  cannot be controlled by the environment, we derive new assumptions for  $\mathcal{C}_{\sigma}$  as follows, by using universal quantification over the output variables  $Y = Y_1 \cup Y_2$  [18]:

$$\phi'_{A\sigma} := \forall Y : \phi_{A\sigma}$$

$$= \neg \exists Y : (\neg \phi_{A1} \land \phi_{G1} \land \phi_{G2}) \lor (\neg \phi_{A2} \land \phi_{G1} \land \phi_{G2})$$

$$= (\neg \exists Y : \neg \phi_{A1} \land \phi_{G1} \land \phi_{G2}) \land (\neg \exists Y : \neg \phi_{A2} \land \phi_{G1} \land \phi_{G2})$$

$$= (\neg \exists Y : \neg \phi_{A1} \land \phi_{G2}) \land (\neg \exists Y : \neg \phi_{A2} \land \phi_{G1})$$

$$= (\phi_{A1} \lor (\forall Y : \neg \phi_{G2})) \land (\forall Y : \phi_{G1} \rightarrow \phi_{A2}). \tag{7}$$

In the derivations above, we use the fact that quantifiers are commutative and associative to lift them to sets of variables so that  $\forall Y := \forall y_1 : \forall y_2 : \ldots : \forall y_n \text{ when } Y = \{y_1, y_2, \ldots, y_n\}.$  Moreover, we leverage the fact that  $\neg \phi_{A1} \rightarrow \phi_{G1}$  and  $\neg \phi_{A2} \rightarrow \phi_{G2}$  must always hold for contracts in saturated form (implying, e.g.,  $\neg \phi_{A1} \wedge \phi_{G1} \wedge \phi_{G2} = \neg \phi_{A1} \wedge \phi_{G2}$ ). Furthermore, since the contrapositive  $\neg \phi_{G2} \rightarrow \phi_{A2}$  is also true for  $\mathcal{C}_2^\sigma$  (implying  $\neg \phi_{G2} = \neg \phi_{G2} \wedge \phi_{A2}$ ), we obtain

$$(\forall Y : \neg \phi_{G2}) = (\forall Y : \neg \phi_{G2} \land \phi_{A2}) = F, \tag{8}$$

since for any input set satisfying  $\phi_{A2}$ , there always exists a set of outputs  $Y_2$  that satisfies  $\phi_{G2}$ . Given that  $\phi_{A1}$  does not depend on Y, we can then conclude from (7) that

$$\phi'_{A\sigma} = \phi_{A1} \wedge (\forall Y : \phi_{G1} \to \phi_{A2}), \tag{9}$$

and that  $\mathcal{C}_{\sigma}$  is compatible if and only if  $\phi'_{A\sigma}$  is satisfiable. Intuitively, this is equivalent to require that there exists an environment satisfying the assumptions of  $\mathcal{C}_1$ , and capable of driving the guarantees of  $\mathcal{C}_1$  to become a subset of the assumptions of  $\mathcal{C}_2^{\sigma}$  for any possible assignment of the output variables. For example, we apply the result above to the serial composition  $\mathcal{C}_{sin} \stackrel{\sigma}{\leadsto} \mathcal{C}_{amp}$ . Both  $\mathcal{C}_{sin}$  and  $\mathcal{C}_{amp}$  are compatible and consistent contracts. Moreover,  $\phi_{A,sin} = \mathbb{T}$ . However, for their composition to be compatible, we also need to enforce  $(\forall Y: \phi_{G1} \rightarrow \phi_{A2})$ :

$$\forall x : \forall y : (x \neq 2\sin\theta) \lor (|x| \leq 1) =$$

$$= \neg \exists x : (x = 2\sin\theta) \land (|x| > 1)$$

$$= \neg \exists x : (x = 2\sin\theta) \land (2|\sin\theta| > 1)$$

$$= \neg ((2|\sin\theta| > 1) \land (\exists x : x = 2\sin\theta))$$

$$= |\sin\theta| \leq \frac{1}{2} \lor \neg \exists x : (x = 2\sin\theta)$$

$$= |\sin\theta| \leq \frac{1}{2}$$

$$\iff \bigvee_{k \in \mathbb{Z}} \left( -\frac{\pi}{6} + k\pi \leq \theta \leq \frac{\pi}{6} + k\pi \right).$$

In fact, if  $\theta$  violates this condition, there is no way for  $C_{sin}$  to provide a legal environment for  $C_{amp}^{\sigma}$ .

Compatibility and consistency conditions for the feedback composition in Fig. 2 (b) can be determined in a similar way. Computation of the composite contract  $C_{\kappa} = C_1^{\kappa} \circ_{\kappa} C_2^{\kappa}$  generates expressions for the assumptions  $\phi_{A\kappa}$  and the guarantees  $\phi_{G\kappa}$  that are analogous to (5) and (6). However, in the special

case of controlled outputs and uncontrolled inputs, we obtain

$$\phi'_{A\kappa} := \forall Y : \phi_{A\kappa} = \forall Y : (\phi_{G2} \to \phi_{A1}) \land (\phi_{G1} \to \phi_{A2}), \tag{10}$$

stating that  $\mathcal{C}_{\kappa}$  is compatible if and only if there exists an environment such that, for all possible assignments on the output variables, the guarantees of  $\mathcal{C}_1^{\kappa}$  are included into the assumptions of  $\mathcal{C}_2^{\kappa}$ , and *vice versa*. For example, we investigate the feedback composition of a *Square* component, which squares any input value, with a *Diode* component, which propagates its input to the output only if it is larger or equal to zero, as shown in Fig. 1 (c). We assume that the components are formally specified by the contracts  $\mathcal{C}_{square} = (\{w,z\}, \mathtt{T}, z=w^2)$  and  $\mathcal{C}_{diode} = (\{w,z\}, z \geq 0, (z<0) \vee (w=z))$ . Then, since

$$\forall w: \forall z: ((z<0) \lor (w=z) \to T) \land (z=w^2 \to z \ge 0) = T,$$

(11)

we conclude that the two contracts are compatible; moreover, the admitted behaviors can be obtained from the joint guarantees  $\phi_{G,square} \land \phi_{G,diode} := (w = z) \land (z = 0 \lor z = 1)$ .

Finally, for a contract  $\kappa(\mathcal{C}) = (U \cup Y \setminus y, \phi_A, \phi_G)$  as in Fig. 2 (c), compatibility checking reduces to verify that

$$\phi_A' := \forall Y : \phi_A = \forall Y : \phi_A \lor \neg \phi_G = \forall Y : \phi_G \to \phi_A \quad (12)$$

is satisfiable, where we use again the fact that  $\neg \phi_G \rightarrow \phi_A$  is always true for a contract in saturated form. The results in this subsection offer a generalization of the conditions for compatibility of contracts in cascade and feedback compositions that were previously reported in the literature [19].

3) Refinement: Refinement is a preorder on contracts, which formalizes a notion of substitutability. We say that  $\mathcal{C}$  refines  $\mathcal{C}'$ , written  $\mathcal{C} \preceq \mathcal{C}'$  (with  $\mathcal{C}$  and  $\mathcal{C}'$  both in saturated form), if and only if  $A \supseteq A'$  ( $\phi_{A'} \to \phi_A$ ) and  $G \subseteq G'$  ( $\phi_G \to \phi_{G'}$ ). Refinement amounts to relaxing assumptions and reinforcing guarantees, therefore strengthening the contract. Clearly, if  $M \models \mathcal{C}$  and  $\mathcal{C} \preceq \mathcal{C}'$ , then  $M \models \mathcal{C}'$ . On the other hand, if  $E \models_E \mathcal{C}'$ , then  $E \models_E \mathcal{C}$ . We can then replace  $\mathcal{C}'$  with  $\mathcal{C}$ .

As an example, let  $C_{range} = (\{u,y\}, |u| \leq \frac{1}{2}, |y| \leq 1)$  be a contract specifying the input and output ranges for the component Amp; we would like to show that  $C_{amp} \leq C_{range}$ , that is, when operating in the context of the assumptions of  $C_{range}$ ,  $C_{amp}$  produces an output within the range prescribed by the guarantees of  $C_{range}$ . To do this, we apply the definitions above to the saturated versions of the two contracts; then, refinement checking translates into proving the validity of the following two predicates involving, respectively, the assumptions and the guarantees of both contracts:

$$|u| \le 1/2 \to |u| \le 1 \tag{13}$$

$$(y = 2u) \lor (|u| > 1) \to (|y| \le 1) \lor (|u| > 1/2).$$

(14)

While (13) is trivially true, to show the validity of (14), we recall that the antecedent in (14) is true when either (|u| > 1) or (y = 2u) holds, and prove that in both cases the consequent is also true. In fact, in the former case, we also have that (|u| > 1/2) holds and the implication is true; in the latter case, if  $(1/2 < |u| \le 1)$  is true, then the implication is still trivially

true. If instead  $(|u| \le 1/2)$  is true, we can still conclude  $|y| = 2|u| \le 1$ , hence (14) is true.

Alphabet equalization is also needed as a preliminary step to define refinement when  $\mathcal{C}$  and  $\mathcal{C}'$  are defined over a different alphabet. A more general case of refinement occurs when  $\mathcal{C}$  and  $\mathcal{C}'$  are also expressed by using different formalisms (heterogeneous refinement). In this case, before the refinement relation can be defined, we need to map the behaviors expressed by one of the contracts to the domain of the other contract via a transformation  $\mathcal{M}$  (e.g. a type of projection or inverse projection) which is generally more involved than alphabet equalization.

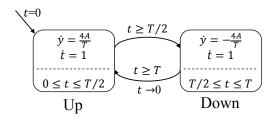

For instance, let  $C_{dis} = (\{powered\}, T, \diamondsuit_{[0,3)}powered)$  be the contract specifying the dynamics of a load in an electrical system, which is powered at startup. We will provide details about the temporal construct used to express the guarantees in Section III. For the moment, we point out that  $C_{dis}$  offers a discrete-time discrete-state abstraction of the dynamics, prescribing that, in all contexts, the Boolean variable powered must be asserted within three time units. On the other hand, let  $C_{con} = (\{v\}, T, v(t) = v_f(1 - e^{-\frac{t}{\tau}}), t \in \mathbb{R}, t \geq 0)$ be the contract describing the voltage level of the electrical load as a continuous function of time t. The load responds as a first order dynamical system with time constant  $\tau$  and steady-state voltage  $v_f$ . Then, we can reason about refinement between  $\mathcal{C}_{con}$  and  $\mathcal{C}_{dis}$  only if we provide a mechanism to map continuous time and voltage levels into discrete ones. In this case, given a time step T, such a mechanism could be provided by the following transformation  $\mathcal{M}$ :

$$\mathcal{M}: \left\{ \begin{array}{cc} powered & := (v \ge \frac{2}{3}v_f) \\ k & := \lfloor \frac{t}{T} \rfloor \end{array} \right., \tag{15}$$

stating that powered is asserted if and only if the voltage is greater or equal to two thirds of the steady-state value, while the discrete time index k is obtained by discretizing t according to the quantization step T. Resting on this mapping, we can then conclude that  $\mathcal{C}_{con} \preceq_{\mathcal{M}} \mathcal{C}_{dis}$  if and only if  $v(3T) > \frac{2}{3}v_f$ , i.e. if and only if the system time constant satisfies  $\tau < \frac{3T}{\ln 3}$ . This condition is illustrated in Fig. 1 (d), where  $v_2(t)$  (in green) satisfies the constraint on  $\tau$  and refines the guarantees of  $\mathcal{C}_{dis}$ , whereas  $v_1(t)$  (in blue) does not, since it reaches the desired value  $\frac{2}{3}v_f$  exactly at time t=3T (k=3), while the interval in the guarantees of  $\mathcal{C}_{dis}$  is rightopen.

4) Conjunction: To compose multiple requirements on the same component, possibly representing different viewpoints that need to be satisfied simultaneously, we can also define the conjunction ( $\wedge$ ) of contracts. Let  $\mathcal{C}_1 = (V, A_1, G_1)$  and  $\mathcal{C}_2 = (V, A_2, G_2)$  be contracts (in saturated form) over the same set of variables V and on the same component M. We would like to combine  $\mathcal{C}_1$  and  $\mathcal{C}_2$  into a joint contract  $\mathcal{C}_1 \wedge \mathcal{C}_2$  so that, if  $M \models \mathcal{C}_1 \wedge \mathcal{C}_2$ , then  $M \models \mathcal{C}_1$  and  $M \models \mathcal{C}_2$ . We can compute the conjunction of  $\mathcal{C}_1$  and  $\mathcal{C}_2$  by taking their greatest lower bound with respect to the refinement relation, i.e. (i)  $\mathcal{C}_1 \wedge \mathcal{C}_2$  is guaranteed to refine both  $\mathcal{C}_1$  and  $\mathcal{C}_2$ , and (ii) for any contract  $\mathcal{C}'$  such that  $\mathcal{C}' \preceq \mathcal{C}_1$  and  $\mathcal{C}' \preceq \mathcal{C}_2$ , we have  $\mathcal{C}' \preceq \mathcal{C}_1 \wedge \mathcal{C}_2$ . For contracts in saturated form and on the same

alphabet, we have

$$C_1 \wedge C_2 = (A_1 \cup A_2, G_1 \cap G_2). \tag{16}$$

As an example, let  $C_{range1}$  and  $C_{range2}$  be two contracts restricting the input and output ranges of an Amp component, and defined as follows

$$C_{range1} = (\{u, y\}, 0 \le u \le 1/2, 0 \le u \le 1/2 \to y \ge u)$$

$$C_{range2} = (\{u, y\}, 0 \le u \le 1, 0 \le u \le 1 \to 0 \le y \le 3u).$$

Then, we can compute the conjunction  $C_{range1} \wedge C_{range2}$  as

$$\begin{split} A_{\wedge} &:= (0 \leq u \leq 1/2) \vee (0 \leq u \leq 1) = 0 \leq u \leq 1 \\ G_{\wedge} &:= (0 \leq u \leq 1/2 \to y \geq u) \wedge (0 \leq u \leq 1 \to 0 \leq y \leq 3u) \\ &= (u \leq y \leq 3u) \vee (u > 1/2 \wedge 0 \leq y \leq 3u) \vee (u < 0) \\ &\vee (u > 1). \end{split}$$

Since  $C_{amp}$  admits a larger set of inputs, the whole interval [-1,1], and promises y=2u for  $u\in[0,1]$ , it clearly refines the conjunction contract, hence it refines both  $C_{range1}$  and  $C_{range2}$ . Therefore, any implementation of  $C_{amp}$ , such as  $M_{amp}$ , will also implement both  $C_{range1}$  and  $C_{range2}$ .

Another form for A/G contracts has also been proposed, which supports reasoning about complex component interactions by avoiding using parallel composition of contracts to overcome the problems that certain models have with the effective computation of the operators [20]. Instead, composition is replaced with the concept of *circular reasoning* [21]: when circular reasoning is sound, it is possible to check relations between composite contracts based on their components only, without taking expensive compositions. However, the notions of compatibility and conjunction, as described above, are not addressed in this theory.

5) Horizontal and Vertical Contracts: Traditionally contracts have been used to specify components, and aggregation of components at the same level of abstraction, as illustrated by the above examples; for this reason we refer to them as horizontal contracts.

We use contracts also to formalize and reason about refinement between two different abstraction levels in the PBD process [5], [10]; for this reason, we refer to this type of contracts as vertical contracts. To illustrate this concept, consider the problem of mapping a specification platform of a system at level l+1 onto an implementation platform at level l. In general, the specification platform architecture (i.e. interconnection of components) may be defined in an independent way, and may not directly match the implementation platform architecture. Such a different architectural decomposition will also reflect on the contracts associated with the components and their aggregations. For instance, the contract describing the specification platform  $C = \bigwedge_{k \in K} (\bigotimes_{i \in I_k} C_{ik})$  may be defined as the conjunction of K different viewpoints, each characterized by its own architectural decomposition into  $I_k$ contracts. On the other hand, the contract describing the implementation platform  $\mathcal{M} = \bigotimes_{j \in J} \left( \bigwedge_{n \in N_j} \mathcal{M}_{jn} \right)$  may be better represented as a composition of J contracts, each defined out of a conjunction of its different viewpoints. Because there may not be, in general, a direct matching between

contracts and viewpoints of  $\mathcal{M}$  and  $\mathcal{C}$ , checking that  $\mathcal{M} \leq \mathcal{C}$  in a compositional way, by reasoning on the elements of  $\mathcal{M}$  and  $\mathcal{C}$  independently, as discussed in Section II-C3, may not be effective.

However, it is still possible to reason about refinement between  $\mathcal{M}$  and  $\mathcal{C}$  by resorting to a contract which specifies the composition of a model and its vertical refinement, even though they are not directly connected, by connecting them indirectly through a mapping, e.g., by synchronizing pairs of events, as if co-simulating a model and its refinement. Informally, this kind of composition captures the fact that the actual satisfaction of all the design requirements and viewpoints by a deployment depends on the supporting execution platform, the underlying physical system, and on the way in which system functionalities are mapped to them. Formally, this composition can be modelled using two alternative methods, based on the specific shapes of  $\mathcal C$  and  $\mathcal M$ :

- The interaction between the specification and the implementation platforms can be modeled using the contract composition  $\mathcal{C}\otimes\mathcal{M}$ . In this case, assumptions made by the specification platform on the implementation platform get discharged by the guarantees of the implementation platform, and *vice versa*, as indicated by (2) and (3). Refinement can then be checked by checking that  $\mathcal{C}\otimes\mathcal{M}$  is compatible, and that  $\mathcal{C}\otimes\mathcal{M}\preceq\mathcal{C}$ , which can be performed compositionally, by matching the elements of  $\mathcal{C}$  with the ones of  $\mathcal{C}\otimes\mathcal{M}$ .

- The interaction between the specification and the implementation platforms can also be modeled using the contract conjunction  $\mathcal{C} \wedge \mathcal{M}$ . In this case, assumptions and guarantees combine as in (16), and  $\mathcal{C} \wedge \mathcal{M}$  is assured to refine  $\mathcal{C}$  by construction. However, being a conjunction, it can still be a source of inconsistencies. Therefore, to guarantee that the design can be implemented, the consistency of  $\mathcal{C} \wedge \mathcal{M}$  must be checked or enforced by the designer.

Composite contracts such as  $\mathcal{C} \otimes \mathcal{M}$  and  $\mathcal{C} \wedge \mathcal{M}$  are both called *vertical contract*, and can be used to formalize mechanisms for mapping a specification over an execution platform, such as the ones adopted in the METROPOLIS [22], METROII [23], and, more recently, the METRONOMY frameworks [24].

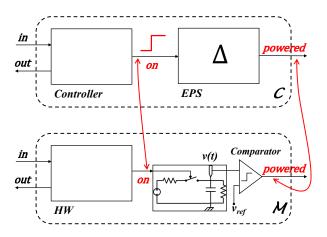

We exemplify the use of vertical contracts by referring to the virtual model of a simple system pictured in Fig. 3. The specification platform architecture, at the top of the figure, consists of two interconnected components. At startup, the *Controller* interacts with an external subsystem through its in and out ports to perform some high-priority task. Then, it switches on a safety-critical electric power system EPS, by asserting its output on, and makes sure that the system is actually powered, i.e. the signal powered is asserted, by the deadline  $t_d$ .

At the application level, to conveniently explore different control strategies, the designer abstracts the physical system *EPS* using a simple delay block, which propagates the value of its input *on* to its output *powered* with a delay  $\Delta$ . We therefore obtain  $t_{pow} - t_{on} = \Delta$ , where  $t_{pow}$  and  $t_{on}$  are, respectively, the times at which *powered* and *on* are asserted, and  $\Delta$  is

Fig. 3. Specification and implementation platform examples used to illustrate vertical contracts.

selected to accommodate the delay of the physical platform. Then, the designer implements the required functionality by allocating the *Controller* to its higher priority task, while guaranteeing a worst case switch-on time  $t_{on}^{max} = t_d - \Delta$  to meet the deadline on the *powered* signal.

While the functional platform described above is very convenient to explore different control strategies, it is not sufficient to determine the correctness of the final design. In fact, the satisfaction of the timing viewpoints heavily relies on the assumptions on the delay of the physical system, which can only be discharged by the implementation platform. The architecture of the implementation platform is shown at the bottom of Fig. 3. The functionality of the *Controller* is mapped to a hardware execution platform HW, while the EPS is modelled by a cascade of a first order filter with time constant  $\tau$ , represented in the figure as an electrical network, and an ideal Comparator block, with reference voltage  $v_{ref}$ . If the filter output voltage v is larger than  $v_{ref}$ , the Comparator asserts its output powered. The reference  $v_{ref}$  corresponds to 90% of the final value  $v_f$  reached by v at steady state.

To show that the implementation platform refines the specification platform, hence satisfies the system requirements, we can formalize the interaction between the two levels in terms of the composition  $\mathcal{C}^t \otimes \mathcal{M}^t$  between two timing contracts:

- $\mathcal{C}^t = (\{\delta_{on}, t_{on}, t_{pow}\}, \delta_{on} \leq \Delta, (t_{on} \leq t_d \Delta) \rightarrow (t_{pow} \leq t_d))$  specifies the timing behavior of the specification platform, by emphasizing its *vertical assumptions* on the implementation platform. If the implementation platform provides a delay  $\delta_{on}$  less than or equal to  $\Delta$  when on is asserted, then the application guarantees to satisfy the requirement on the *powered* signal, if on is asserted by at least an interval  $\Delta$  before the deadline  $t_d$ .

- $\mathcal{M}^t = (\{\delta_{on}, t_{on}, t_{pow}\}, \mathtt{T}, (\delta_{on} = \tau \ln 10) \land (t_{pow} = t_{on} + \delta_{on}))$  exposes the timing behavior of the implementation platform, as derived from the step response of a first-order filter.  $\mathcal{M}^t$  states that, whenever on is asserted, the delay at which v reaches 90% of its steady-state level, hence  $t_{pow}$  is asserted, is  $\delta_{on} = \tau \ln 10$ .

In this simple example, the assumptions and guarantees of both  $C^t$  and  $\mathcal{M}^t$  are assertions over variables denoting the time of occurrence of certain events, or their separation.

Resting on the above contracts, because the assumptions of  $\mathcal{C}^t$  trivially imply the ones of  $\mathcal{M}^t$ , we obtain  $\mathcal{C}^t \otimes \mathcal{M}^t \preceq \mathcal{C}^t$ . Moreover, for the contracts in this example, it is also possible to show that  $\mathcal{M}^t \preceq \mathcal{C}^t \otimes \mathcal{M}^t$  holds. Therefore, checking the correctness of the design finally requires checking that the vertical contract  $\mathcal{C}^t \otimes \mathcal{M}^t$  is compatible. In this case, by applying (9) in Section II-C2, where  $\mathcal{M}^t$  and  $\mathcal{C}^t$  act, respectively, as  $\mathcal{C}_1$  and  $\mathcal{C}_2$ , we conclude that it is enough to check the satisfiability of  $\forall \delta_{on}: \forall t_{pow}: (\delta_{on} = \tau \ln 10) \land (t_{pow} = t_{on} + \delta_{on}) \to (\delta_{on} \leq \Delta)$ , which provides

$$\tau \ln 10 < \Delta. \tag{17}$$

This inequality can also be used at design time, as a practical guideline to dimension either the specification platform, by increasing its margin  $\Delta$ , or the implementation platform, by decreasing its time constant  $\tau$ , to deploy a correct design.

It is also possible to obtain the same result as above, by following an alternative formulation based on contract conjunction. In particular, we suppose that the designer chooses instead to describe the timing behaviors of the system in Fig. 3 using a different contract pair:

- $\tilde{\mathcal{C}}^t = (\{t_{on}, t_{pow}\}, t_{on} \leq (t_d \Delta), t_{pow} \leq t_d)$ , the specification contract, is no longer bound to the implementation platform. It simply states that the requirement on  $t_{pow}$  is satisfied if on is asserted by at least an interval  $\Delta$  before the deadline  $t_d$ .

- $\tilde{\mathcal{M}}^t = (\{t_{on}, t_{pow}\}, \mathbb{T}, t_{pow} = t_{on} + \tau \ln 10)$ , the implementation contract, is also independent of the specification platform (except for being defined on the same variables), and exposes the timing behavior of the *powered* signal.  $\tilde{\mathcal{M}}^t$  states that, whenever *on* is asserted, *powered* will be asserted with a delay  $\tau \ln 10$ , due to the physical system (a first-order filter).

Then, to check the correctness of the refinement, a binding mechanism between the two contracts, each linked to its own platform, can now be provided by the conjunction of  $\tilde{\mathcal{M}}^t$  and  $\tilde{\mathcal{C}}^t$ .  $\tilde{\mathcal{C}}^t \wedge \tilde{\mathcal{M}}^t$  ensures that both contracts are jointly satisfied, and refines  $\tilde{\mathcal{C}}^t$  by construction. Therefore, all we need to check is that  $\tilde{\mathcal{M}}^t$  does not create inconsistencies in  $\tilde{\mathcal{C}}^t \wedge \tilde{\mathcal{M}}^t$ , in the sense that  $(\forall t_{on}: \exists t_{pow}: G_{\tilde{\mathcal{M}}^t} \cap G_{\tilde{\mathcal{C}}^t})$  is true<sup>5</sup>, where  $G_{\tilde{\mathcal{M}}^t}$  and  $G_{\tilde{\mathcal{C}}^t}$  are the guarantees of the two contracts in saturated form. In our case,

$$\forall t_{on}: \exists t_{pow}: (t_{pow} = t_{on} + \tau \ln 10) \land ((t_{on} > t_d - \Delta)$$

$$\lor (t_{pow} \le t_d))$$

$$= \forall t_{on}: (\exists t_{pow}: t_{pow} = t_{on} + \tau \ln 10) \land (t_{on} > t_d - \Delta)$$

$$\lor (t_{on} \le t_d - \tau \ln 10)$$

$$= \forall t_{on}: (t_{on} > t_d - \Delta) \lor (t_{on} \le t_d - \tau \ln 10)$$

$^5\text{We}$  are actually interested in checking consistency  $\forall t_{on}:t_{on}\leq (t_d-\Delta),$  which is the set of legal environments for  $\tilde{\mathcal{C}}^t.$  In fact, we want to show that, for each  $t_{on}$  satisfying the assumptions of the specification contract  $\tilde{\mathcal{C}}^t,$  there exists an implementable  $t_{pow},$  according to the implementation contract  $\tilde{\mathcal{M}}^t,$  which also satisfies the deadline  $t_d,$  as required by  $\tilde{\mathcal{C}}^t.$  When  $t_{on}>(t_d-\Delta),$   $\tilde{\mathcal{C}}^t\wedge\tilde{\mathcal{M}}^t$  is trivially consistent, since the guarantees of  $\tilde{\mathcal{C}}^t$  are vacuously true.

leads to the condition  $\tau \ln 10 \leq \Delta$ , which is the result found in (17). Intuitively, this amounts to requiring that, if  $t_{on}$  and  $t_{pow}$  have to synchronize so that  $\tilde{\mathcal{M}}^t$  refines  $\tilde{\mathcal{C}}^t$  and the overall system satisfies the timing requirement on  $t_{pow}$ , then the delay implemented by the physical system in  $\tilde{\mathcal{M}}^t$  must be smaller than or equal to the one defined by the application platform in  $\tilde{\mathcal{C}}^t$ .

The approach illustrated above has been previously adopted in the design of analog and mixed-signal integrated circuits [25], [5], by leveraging effective approximations of implementation constraints to formulate vertical contracts representing different viewpoints (e.g., timing, energy, noise), and then checking their compatibility or consistency during design space exploration. More recently, a similar approach has also been advocated in the context of AUTOSAR [10]. Alternatively, when vertical assumptions and guarantees cannot be effectively expressed by compact models, compatibility and consistency of vertical contracts can be checked by co-simulation of the application and implementation platforms under a mapping mechanisms, such as the one in the METRONOMY framework [24], in which tuples of signals in the two platforms are synchronized. In the context of our example, this technique can be applied by unifying both occurrences and values of the on and powered signals, as shown in red in Fig. 3, and then checking that the synchronized models satisfy the requirements.

We finally observe that the formal notion of vertical contracts we have presented is general, in that it encompasses other notions of contracts that were previously introduced in a control setting to capture the interactions between the controller and its execution platform [9], [26]. In this scenario, a controller takes as assumptions several aspects that include the timing behavior of the control tasks and of the communication between tasks, e.g., delay, jitter, as well as the accuracy and resolution of the computation (vertical assumptions in  $\mathcal{C}$ ). On the other hand, the controller provides guarantees in terms of the amount of requested computation, activation times and data dependencies (vertical guarantees in C). Vertical contracts can then be effectively used to formalize the agreement between control, software, and hardware engineers, when specifying both system functionality and timing requirements. As a result, several design approaches and guidelines, which have been previously established in the literature in terms of "design contracts" [26], can be derived by formulating vertical contracts for both the software and control layers, and by enforcing their compatibility and consistency as illustrated by the example in Fig. 3.

# III. REQUIREMENT FORMALIZATION AND VALIDATION USING CONTRACTS

We use contracts to formalize top-level requirements, allocate them to lower-level components, and analyze them for early validation of design constraints. Requirement analysis can often be challenging, because of the lack of familiarity with formal languages among system engineers. Moreover, it is significantly different from traditional formal verification, where a system model is compared against a set of

Fig. 4. (a) Structure of the proposed contract-based methodology for CPS design, from top-level requirements to the definition of system architecture and control algorithm. Demonstration of the different design steps on the aircraft electric power system example in Section VI [14]: (b) requirement formalization; (c) plant architecture selection; (d) reactive control synthesis; (e) simulation-based verification; (f) simulation-based design exploration; (g) hybrid power system model in SIMULINK for further refinement.

requirements. Since there is not yet a system at this stage, requirements themselves are the only entity under analysis. By formalizing requirements as contracts, it is instead possible to provide effective tests to check for requirement consistency, i.e. whether a set of contracts is realizable, or whether, in contrast, facets of these are inherently conflicting, and thus no implementation is feasible. Moreover, it is possible to exclude undesired behaviors, e.g. by adding more contracts, by strengthening assumptions, or by considering additional cases for guarantees. Since contracts are abstractions of components, their concrete representations are typically more compact than a fully specified design [15]. The above tests can then be performed more efficiently than traditional verification tasks.

A framework for requirement engineering has been recently developed by leveraging modal interfaces, an automata-based formalism, as the underlying specification theory [10]. However, to retain a correspondence between informal requirements and formal statements, *declarative*, "property-based" approaches using some temporal logic are gaining increasing interest. They contrast *imperative*, "model-based" approaches, which tend to be impractical for high-level requirement validation. In fact, constructing a model to capture all the behaviors allowed by the requirements often entails considering all possible combinations of system variables. Moreover, these models are usually hard to parametrize, and small changes in the requirements become soon hard to map into changes in the corresponding models.

In this paper, we follow an approach based on A/G contracts as introduced in Section II-B, which allows specifying different kinds of requirements using different formalisms, following both the declarative and imperative styles, to reflect the different viewpoints and domains in a heterogeneous system, as well as the different levels of abstraction in the design flow. As shown in Fig. 4 (a), to facilitate reasoning at the level of abstraction of requirement engineers, a viable strategy is to drive engineers towards capturing requirements in a structured form, using a set of predefined high-level *primitives*, or patterns, from which formal specifications can be automatically generated. This approach is similar to the one advocated in the STATEMATE verification environment [27], within the European projects SPEEDS and CESAR [13] (linked to automata-based formalisms), or to the higher-level domainspecific language (DSL) exemplified in Section VI [14].

From a set of high-level primitives, different kinds of contracts can be generated. When specifying the *system architecture*, steady-state (static) requirements, interconnection rules, component dimensions can be captured by static contracts, expressed via *arithmetic constraints on Boolean and real variables* to model, respectively, discrete and continuous design choices. Then, compatibility, consistency and refinement checking translate into checking feasibility of conjunctions or disjunction of constraints, which can be solved via queries to Satisfiability Modulo Theory (SMT) solvers [28], [29] or mathematical optimization software, such as mixed

integer-linear, mixed integer-semidefinite-positive, or mixed integer/non-linear program solvers.

When specifying the control algorithm, representing dynamic behaviors becomes the main concern; safety and realtime requirements can then be captured by contracts expressed using temporal logic constructs. For instance, linear temporal logic (LTL) [30] can be used to reason about the temporal behaviors of systems characterized by Boolean, discrete-time signals or sequences of events (discrete event abstraction in Fig. 4a). Signal temporal logic (STL) [31] can deal with dense-time real signals and continuous dynamical models (continuous abstraction in Fig. 4a). Sometimes, discrete and continuous dynamics are so tightly connected that a discreteevent (DE) abstraction would result inaccurate, while a continuous abstraction would turn out to be inefficient, thus calling for a hybrid system abstraction, mixing discrete and continuous behaviors, such as Hybrid Linear Temporal Logic with Regular Expressions (HRELTL) [32] and hybrid automata [33]. In the sequel, we review the main formalisms for the specification of dynamical systems, and the related tools, which can be used to implement the algebra of contracts and perform requirement analysis within our framework.

#### A. Temporal Logic

Temporal logic is a symbolism for representing and reasoning about the evolution of a system over time. Starting from the '80s it has been successfully applied in formal verification, and a flourishing family of temporal logics has been developed both by academy and industry. Because of its "declarative" flavor, temporal logic seems a "natural" language to formalize high-level requirements in terms of contracts. Moreover, especially for discrete-time, discrete-state system representations, the wealth of results and tools in temporal logic and *model checking* can provide a substantial technological basis for requirement analysis [6].

Classical discrete-time temporal logics like LTL and computation tree logic (CTL) [6], originally developed to state requirements of hardware and software electronic systems, can indeed be effectively used to describe the DE abstraction of CPS. As an example, in the abstraction offered by LTL, a component can be represented as a set of Boolean variables  $S_{DE}$ . Then, the behaviors of a component can be described by the infinite sequences of states of the form  $\sigma = s_0 s_1 s_2 \dots$ satisfying an LTL formula, each state s being a valuation of the Boolean variables in  $S_{DE}$ . A sample requirement expressible by LTL is the property "An alert must be eventually resolved", which can be formalized by the formula  $\Box(alert \rightarrow \Diamond sys\_ok)$ , where alert and  $sys\_ok$  are Boolean component variables. This formula states that every occurrence of the alert event (i.e. when alert is asserted), as denoted by the always  $(\Box)$  operator, must eventually  $(\diamondsuit)$  be followed by an occurrence of a sys ok event.

Discrete-time temporal logics, however, lack the expressiveness needed to capture the continuous aspects of the system in a faithful way. To overcome this limitation, temporal logics have been extended in many ways. A first extension, routinely used in the verification of discrete-time hybrid systems, is to replace Boolean variables with first order atoms, including non-linear arithmetic constraints on real numbers [34]. In this way, LTL can express properties like "If the temperature reaches 90 degrees then it must eventually decrease below 60", using formulas of the form  $\Box(t \geq 90 \rightarrow \Diamond t < 60)$ , which constrains any state where the temperature t is greater or equal to 90 to be followed by a state where the temperature is below t

A second possibility is to add operators to express timing constraints between discrete events. This leads to the development of *real-time temporal logics* such as Metric Temporal Logic (MTL) [35]. For instance, real-time temporal logics can express properties like "An alert must be resolved in 10 seconds", by means of the MTL formula  $\Box(alert \rightarrow \Diamond_{[0,10]} sys\_ok)$ , which forces the  $sys\_ok$  event to occur at most 10 time units after the alert event.

Real-time temporal logics have been further extended by providing a continuous notion of time, and by making them capable of expressing properties of continuous quantities. The most relevant language in this family of *continuous-signal logics* is STL [31], which combines first order atoms with timing constraints and is able to express properties like "If the temperature reaches 90 degrees then it must decrease below 60 in at most 10 seconds". Such a property can be formalized by the formula  $\Box(t \geq 90 \rightarrow \diamondsuit_{[0,10]} \ t < 60)$ , which constrains any time instant  $\tau_0$  where the temperature t is greater or equal to 90 to be followed by a time instant  $\tau_1$  where the temperature is below 60 and such that  $\tau_1 - \tau_0 \leq 10$ .

More recently, some logics for hybrid-systems have been introduced, which can express properties of both the discrete and continuous behaviors of a system. Two relevant members of this class are HRELTL [32], which extends the LTL with regular expressions (RE), and Differential Dynamic Logic (dL) [36], which can specify correctness properties for hybrid systems given operationally as hybrid programs. An example of a hybrid property is "If the temperature reaches 90 then an alert is raised", which can be formalized by the HRELTL formula  $\Box(t > 90 \rightarrow \bigcirc alert)$ , where  $\bigcirc$  is the "next discrete event" operator. On the other hand, the hybrid property "for the state of a train controller train,  $z \le 100$  always holds true when starting in a state where  $v^2 \le 10$  is true", can be expressed by the  $d\mathcal{L}$  formula  $v^2 \leq 10 \rightarrow [train]z \leq 100$ , where z and v are the position and the velocity of the train, respectively.