## **UC San Diego**

## **UC San Diego Electronic Theses and Dissertations**

#### **Title**

Design Techniques for High Data Rates in Microwave and Millimeter-Wave Transmitters /

#### **Permalink**

https://escholarship.org/uc/item/1ck1f76s

#### **Author**

Dabag, Hayg-Taniel

#### **Publication Date**

2014

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA, SAN DIEGO

#### Design Techniques for High Data Rates in Microwave and Millimeter-Wave Transmitters

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy

in

Electrical Engineering (Electronic Circuits and Systems)

by

Hayg-Taniel Dabag

#### Committee in charge:

Peter M. Asbeck, Chair James F. Buckwalter, Co-Chair Prasad S. Gudem, Co-Chair Robert R. Bitmead William S. Hodgkiss Bhaskar D. Rao

Copyright

Hayg-Taniel Dabag, 2014

All rights reserved.

| The dissertation of Hayg-Taniel Dabag is approved, and  |

|---------------------------------------------------------|

| it is acceptable in quality and form for publication on |

| microfilm and electronically:                           |

|                                                         |

|                                                         |

|                                                         |

|                                                         |

|                                                         |

|                                                         |

|                                                         |

| Co-Chair                                                |

|                                                         |

| Co-Chair                                                |

|                                                         |

| Chair                                                   |

University of California, San Diego

2014

## DEDICATION

To my parents.

### TABLE OF CONTENTS

| Signature Pag   | ge .                                     |                                                                                                                                                                            | 111                                                                   |

|-----------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| Dedication .    |                                          |                                                                                                                                                                            | iv                                                                    |

| Table of Cont   | tents                                    |                                                                                                                                                                            | V                                                                     |

| List of Figure  | es .                                     |                                                                                                                                                                            | viii                                                                  |

| List of Tables  | S                                        |                                                                                                                                                                            | xi                                                                    |

| Acknowledge     | ments                                    |                                                                                                                                                                            | xii                                                                   |

| Vita            |                                          |                                                                                                                                                                            | xiv                                                                   |

| Abstract of the | he Dis                                   | ssertation                                                                                                                                                                 | xvi                                                                   |

| Chapter 1       | Intro<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5 | Spectral Efficiency of Digital Modulation                                                                                                                                  | 1<br>2<br>4<br>9<br>12<br>13                                          |

| Chapter 2       |                                          | iver Desensitization in Uplink Carrier Aggregation Due to ng of Two Transmit Signals in Cellular Handsets Background: Cellular Transceivers for Uplink Carrier Aggregation | 155<br>19<br>19<br>21<br>22<br>27<br>31<br>31<br>32<br>34<br>35<br>36 |

|           | 2.5  | Experimental Results                                   | 38 |

|-----------|------|--------------------------------------------------------|----|

|           |      | 2.5.1 Measurement Setup                                | 38 |

|           |      | 2.5.2 Cancellation Results                             | 40 |

|           | 2.6  | Rate of Convergence                                    | 49 |

|           | 2.7  | Computational Effort                                   | 49 |

|           | 2.8  | Conclusions                                            | 52 |

| Chapter 3 | Ana  | lysis and Design of Stacked-FET Millimeter-Wave Power  |    |

| •         |      | plifiers                                               | 54 |

|           | 3.1  | Background: mm-wave Silicon PAs                        | 54 |

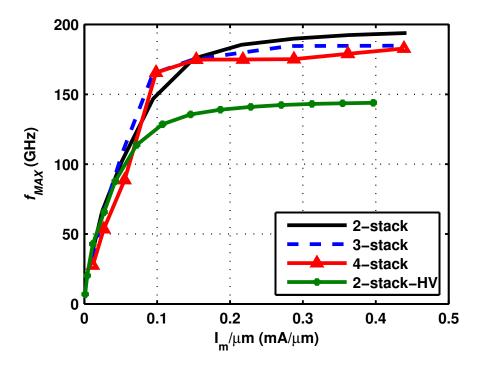

|           | 3.2  | FET Stacking Concept                                   |    |

|           |      | 3.2.1 Prior Work on Stacked-FET PAs                    |    |

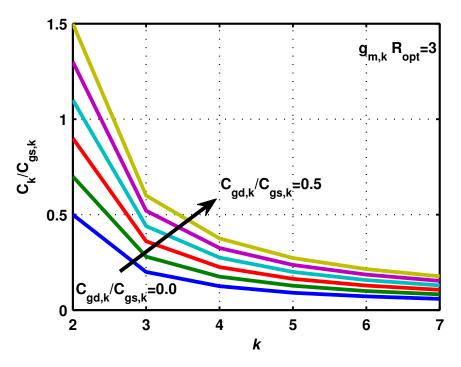

|           |      | 3.2.2 Sizing of the Gate Capacitance $C_k$             | 60 |

|           |      | 3.2.3 Voltage Distribution                             | 63 |

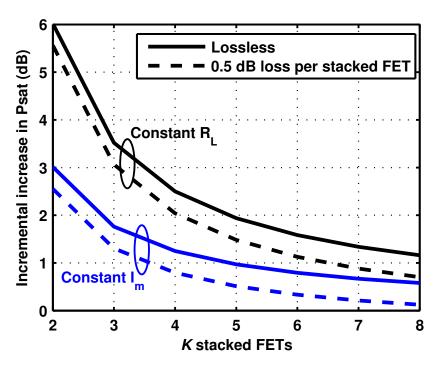

|           |      | 3.2.4 Benefits and Limitations of Stacking             |    |

|           |      | 3.2.5 Comparison of Stacking to Other Power Combin-    |    |

|           |      | ing Techniques                                         | 66 |

|           | 3.3  | Complex Intermediate Node Matching                     | 68 |

|           |      | 3.3.1 Optimal Complex Intermediate Node Impedance      | 69 |

|           |      | 3.3.2 Optimal Intermediate Node Impedance Matching     | 73 |

|           |      | 3.3.3 Verification of Intermediate Node Matching Anal- |    |

|           |      | ysis                                                   | 76 |

|           |      | 3.3.4 Comparison of Intermediate Node Matching Tech-   |    |

|           |      | niques                                                 | 78 |

|           | 3.4  | Technology and Amplifier Implementation                | 79 |

|           |      | 3.4.1 45-nm CMOS SOI Technology                        | 79 |

|           |      | 3.4.2 PA Implementation                                | 79 |

|           | 3.5  | Experimental Results                                   |    |

|           |      | 3.5.1 Measurement Setups                               |    |

|           |      | 3.5.2 Intermediate Node Matching                       | 85 |

|           |      | 3.5.3 Comparing 2-, 3-, and 4-Stack PAs                | 87 |

|           | 3.6  | Conclusions                                            |    |

|           | 3.7  | Appendix 3.A: Optimal Drain Impedance                  |    |

|           | 3.8  | Appendix 3.B: Stacking Efficiency                      | 95 |

| Chapter 4 | High | n Data Rate mm-Wave Wireless Transmission              | 97 |

| -         | 4.1  | Mark E Predistortion System                            | 98 |

|           |      | 4.1.1 DPD Algorithms                                   |    |

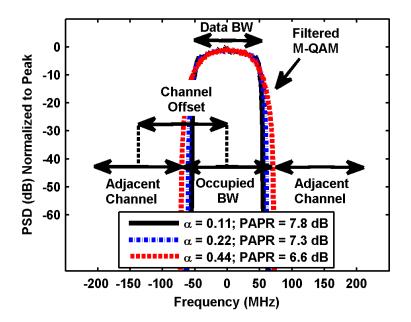

|           |      | 4.1.2 M-QAM Test Signals                               |    |

|           |      | 4.1.3 Predistortion of Mark E "Through" Test           |    |

|           |      | 4.1.4 System Accuracy Limits                           |    |

|           | 4.2  | Spatially Power Combined stacked-FET PAs               |    |

|              | 4.3 DPD Results of Spatially Power Combined stacked-F |          |                              |

|--------------|-------------------------------------------------------|----------|------------------------------|

|              |                                                       | PAs .    |                              |

|              | 4.4                                                   | Conclu   | asions                       |

| Chapter 5    | Cone                                                  | clusions | s and Future Work            |

|              | 5.1                                                   | Disser   | tation Summary               |

|              | 5.2                                                   | Future   | e Work                       |

|              |                                                       | 5.2.1    | Two UL CA and Three DL CA    |

|              |                                                       | 5.2.2    | Silicon mm-Wave Transmitters |

| Bibliography |                                                       |          |                              |

## LIST OF FIGURES

| Figure 1.1:             | 64-QAM constellation for various SNRs                                                                                         | 3   |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 1.2:             | Signal quality requirements for correct data reconstruction                                                                   | 4   |

| Figure 1.3:             | 2011 US frequency allocations chart illustrates the heavy frag-                                                               |     |

|                         | mentation                                                                                                                     | 8   |

| Figure 1.4:             | Possible frequency plan for carrier aggregation                                                                               | 9   |

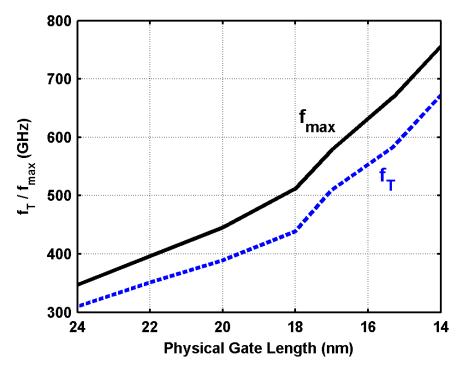

| Figure 1.5:             | 2011 ITRS roadmap for $f_T$ and $f_{max}$ [5]                                                                                 | 10  |

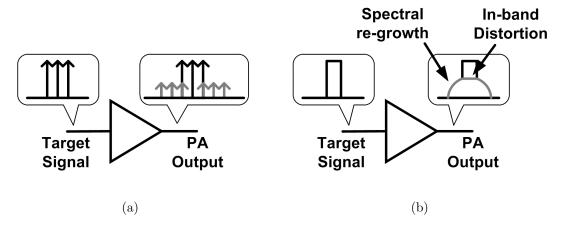

| Figure 1.6:             | Nonlinear PA distorting input signal                                                                                          | 12  |

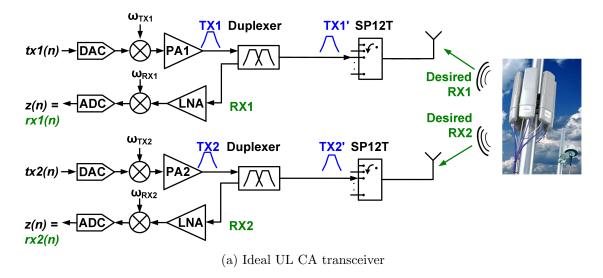

| Figure 2.1:             | Block diagram of two transmitter system for UL CA                                                                             | 16  |

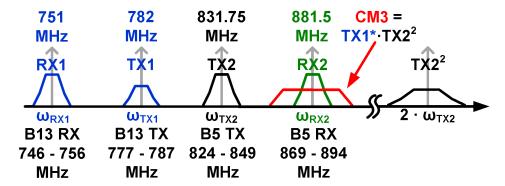

| Figure 2.2:             | Frequency view of third-order cross-modulation product (CM3) created by band 5 and 13 transmit signals across antenna switch. | 17  |

| Figure 2.2.             | ·                                                                                                                             | 20  |

| Figure 2.3: Figure 2.4: | The adaptive noise cancelling concept [12]                                                                                    | 20  |

| rigure 2.4.             | mission [14]                                                                                                                  | 21  |

| Figure 2.5:             | Block diagram of adaptive distortion canceller                                                                                | 22  |

| Figure 2.6:             | Covariance of measured $cm3(n)$ and estimated $cm3'(n)$                                                                       | 24  |

| Figure 2.7:             | Peak of covariance from Fig. 2.6 versus the group-delay difference between TX1" and TX2'                                      | 25  |

| Figure 2.8:             | Block diagram of SISO adaptive distortion canceller                                                                           | 26  |

| Figure 2.9:             | -                                                                                                                             | 28  |

| Figure 2.10:            | Amount of cancellation given $\lambda$ for various received signal powers.                                                    | 33  |

| ~                       | Adaptive MISO filter with digital channel select filter for adja-                                                             |     |

| D: 0.10                 | cent channel jammer suppression                                                                                               | 34  |

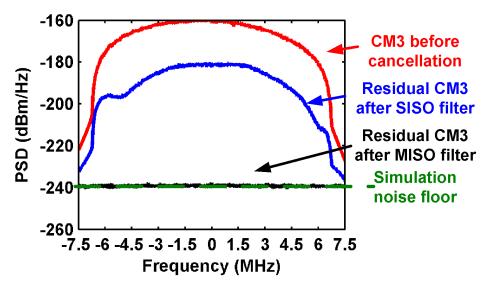

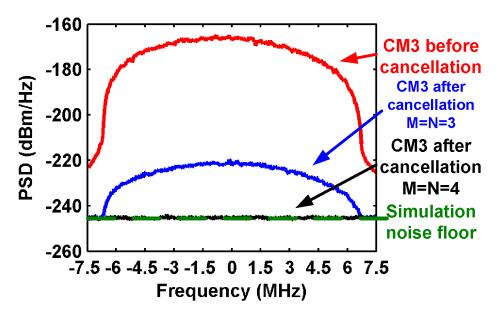

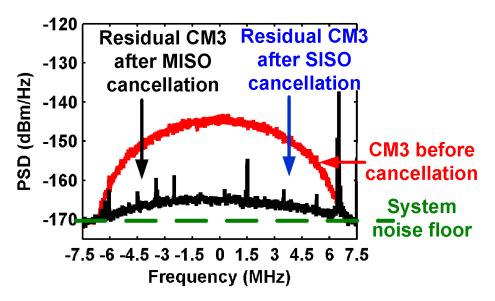

| Figure 2.12:            | Spectral plots of the simulated distortion before and after can-                                                              | 0.0 |

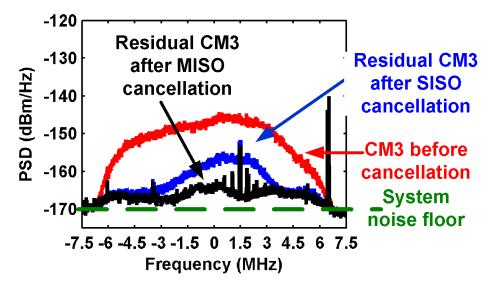

| D: 0.10                 | cellation using the SISO and the MISO filter                                                                                  | 36  |

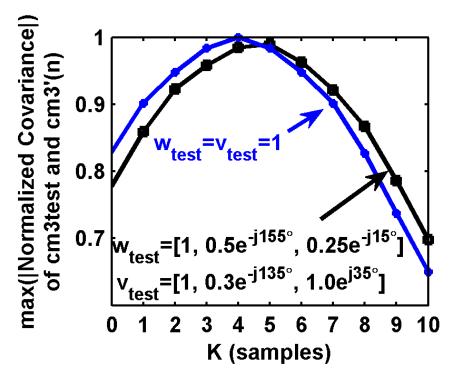

|                         | Peak of covariance of $cm3test$ and for various $K$                                                                           | 37  |

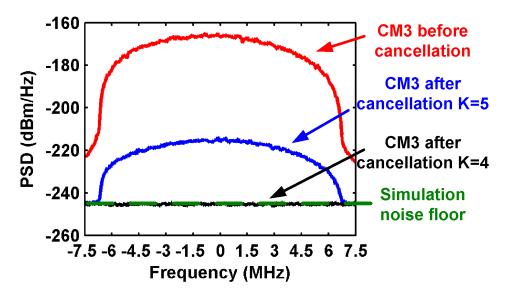

| Figure 2.14:            | Simulated distortion before and after the MISO canceller using                                                                | 0.0 |

| D: 0.15                 | correct and incorrect group delay adjustment of $K$                                                                           | 38  |

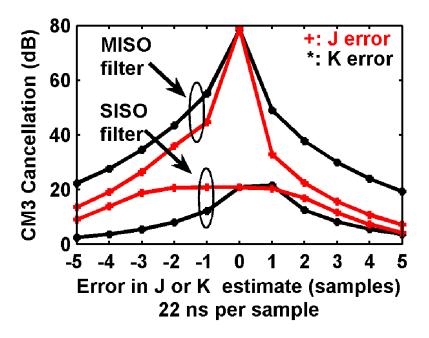

| Figure 2.15:            | Cancellation performance for different filter lengths when $K$ is                                                             | 20  |

| D: 0.16                 | underestimated $(K = 3)$ for the MISO canceller                                                                               | 39  |

|                         | Sensitivity of MISO and SISO filter to errors in time alignment.                                                              | 39  |

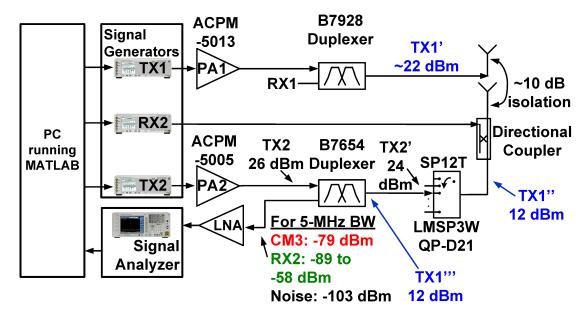

| _                       | Measurement setup mimicking an UL CA handset                                                                                  | 41  |

| Figure 2.18:            | Measured duplexer distortion before and after cancellation using                                                              | 4.0 |

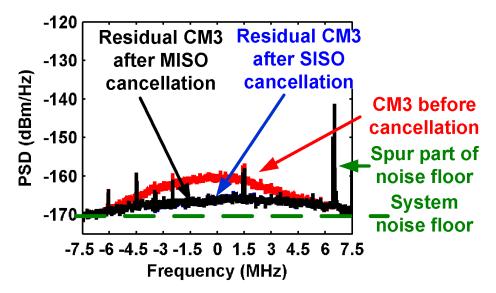

| T. 0.10                 | MISO or SISO filter                                                                                                           | 42  |

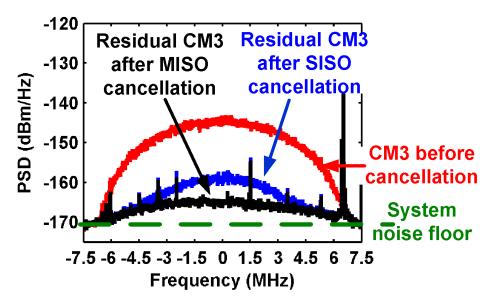

| Figure 2.19:            | Measured switch and duplexer distortion before and after can-                                                                 |     |

| T                       | cellation using either the MISO or the SISO filter                                                                            | 43  |

| Figure 2.20:            | Measured switch and duplexer distortion before and after can-                                                                 |     |

|                         | cellation using the SISO or the MISO filter with $K$ alignment                                                                |     |

|                         | error by minus one sample                                                                                                     | 43  |

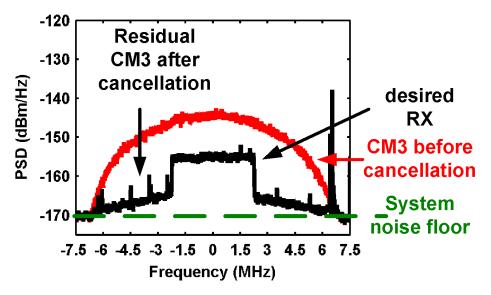

| Figure 2.21:            | Low-power received signal with distortion before and after can-                                                               |     |

|                         | cellation (SINR before/after cancellation $\approx$ -10 dB/ +9.4 dB).                                                         | 44  |

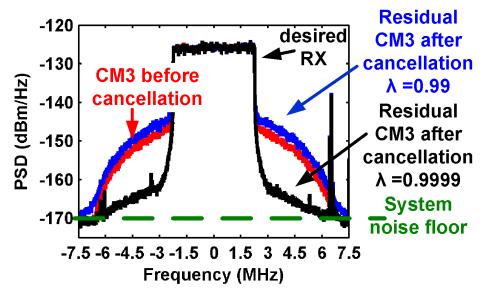

| Figure 2.22:    | High-power received signal with distortion before and after cancellation (SINR before/after cancellation $\approx 20 \text{ dB}/32 \text{ dB}$ ) | 45 |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

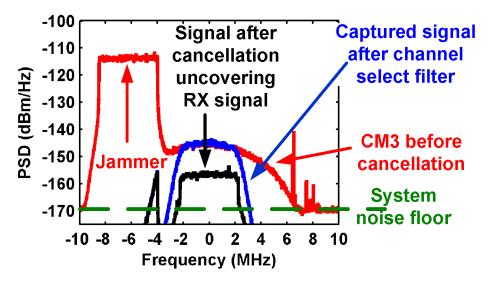

| Figure 2.23:    | Captured signal with out-of-band jammer before and after channel select filtering and after adaptive distortion cancellation                     | 47 |

| Figure 2.24:    | Captured CM3 in experiment using different antennas. Reflections change distortion shape. SISO filter length is 4. MISO filter length is 16      | 48 |

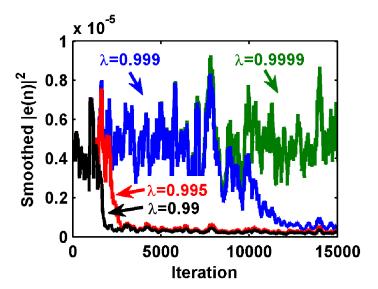

| Figure 2.25:    | Convergence of MISO filter output for various $\lambda$                                                                                          | 50 |

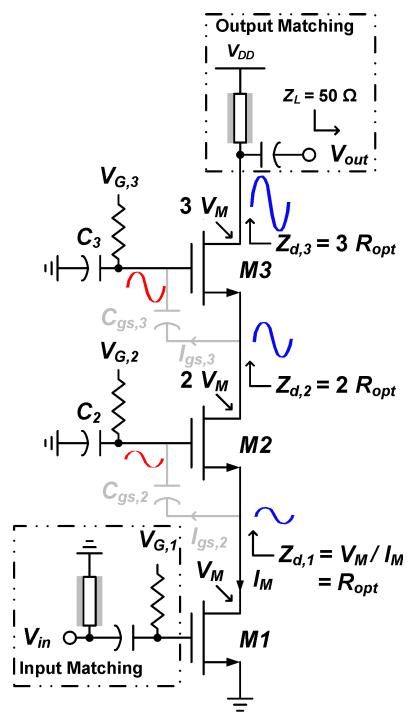

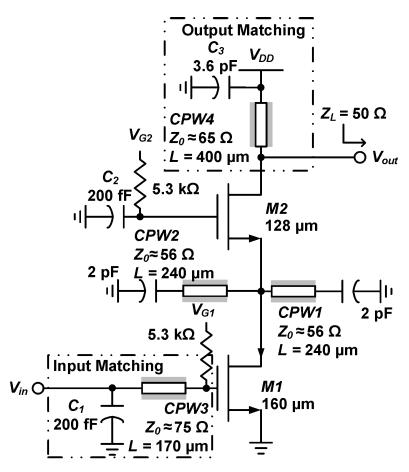

| Figure 3.1:     | 3-stack PA schematic. The rectangular boxes used in the input and output matching network are coplanar waveguides (CPWs).                        | 58 |

| Figure 3.2:     | Hittite high power amplifier [25]                                                                                                                | 59 |

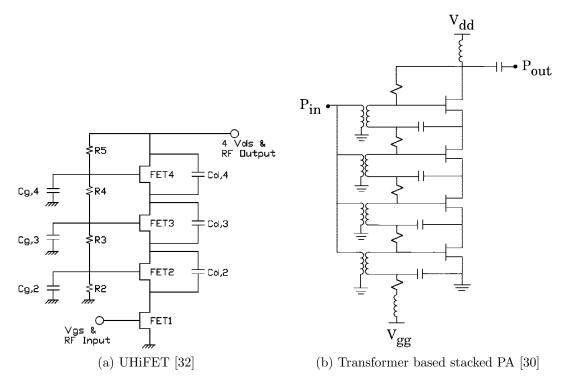

| Figure 3.3:     | Prior stacked-FET PAs                                                                                                                            | 60 |

| Figure 3.4:     | $C_k/C_{gs,k}$ for various $C_{gd,k}/C_{gs,k}$ for $g_{m,k} \cdot R_{opt} = 3. \dots \dots$                                                      | 63 |

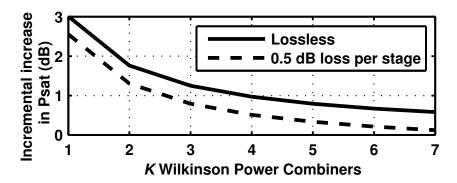

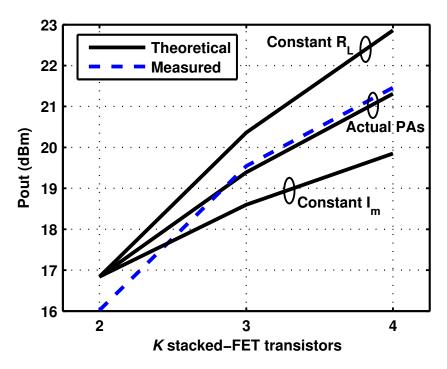

| Figure 3.5:     | Incremental increase in Psat of $k$ th stacked FET                                                                                               | 65 |

| Figure 3.6:     | Comparison of $f_{MAX}$ of two, three, and four stacked FETs using thin-oxide FETs and two stacked thick oxide / high-voltage                    |    |

|                 | (HV) FETs                                                                                                                                        | 68 |

| Figure 3.7:     | Incremental increase in $P_{sat}$ of the $k$ th Wilkinson combiner                                                                               | 69 |

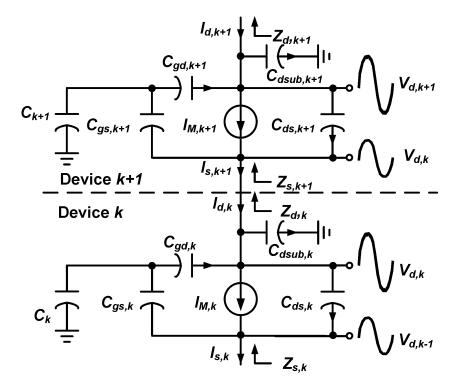

| Figure 3.8:     | Simplified small-signal model of stacked transistors                                                                                             | 70 |

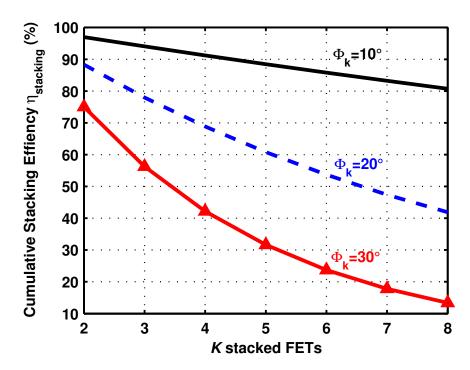

| Figure 3.9:     | Cumulative stacking efficiency for various phase misalignments.                                                                                  | 72 |

| Figure 3.10:    | 2-stack PA schematic with different intermediate node tuning                                                                                     |    |

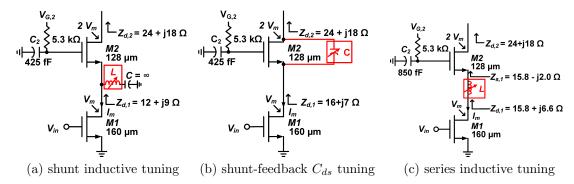

|                 | techniques                                                                                                                                       | 73 |

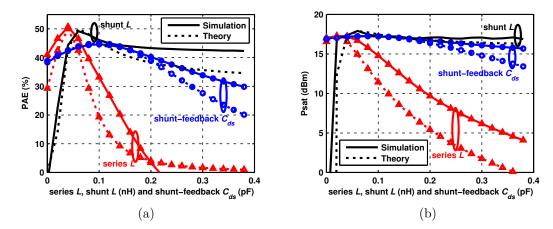

| Figure 3.11:    | PAE (a) and Pout (b) for $P_{in} = 9$ dBm using series $L$ , shunt $L$ , and shunt-feedback $C_{ds}$ intermediate node tuning                    | 77 |

| Figure 3.12:    | Schematic of 2-stack PA with shunt tuning elements between the two transistors                                                                   | 80 |

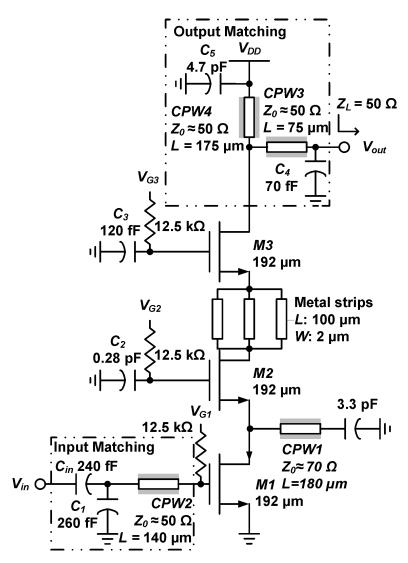

| Figure 3.13:    | Schematic of 3-stack PA with shunt tuning element between $M1$ and $M2$ and series tuning inductance between $M2$ and $M3$                       | 81 |

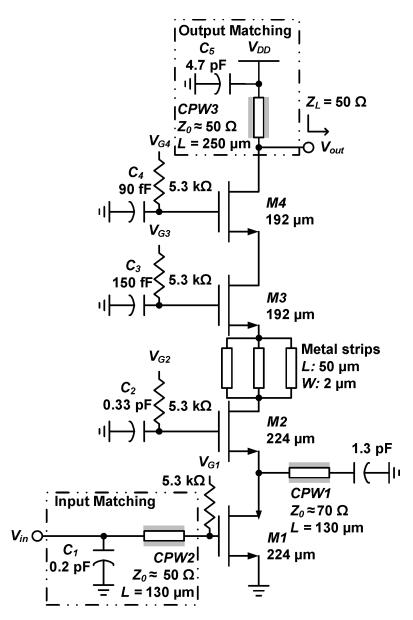

| Figure 3.14:    | Schematic of 4-stack PA with shunt tuning element between $M1$ and $M2$ and series tuning inductance between $M2$ and $M3$                       | 82 |

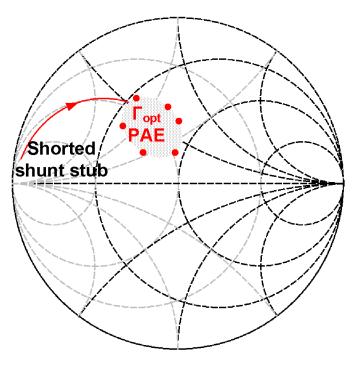

| Figure 3.15:    | $50-\Omega$ load and pad capacitance are transformed by a shunt stub (solid line) to a load impedance for optimal PAE inside the                 | _  |

|                 | highlighted region.                                                                                                                              | 83 |

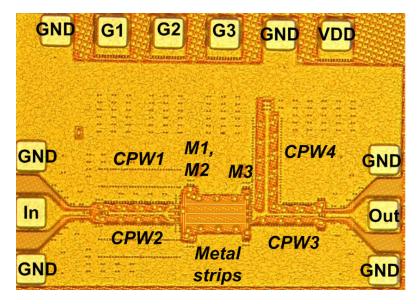

| Figure 3.16:    | Photomicrograph of 3-stack PA occupying 0.6 mm x 0.5 mm                                                                                          |    |

|                 | including pads                                                                                                                                   | 83 |

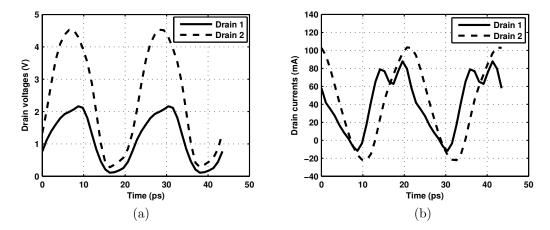

| Figure $3.17$ : | Simulated drain voltages (a) and drain currents (b) of 2-stack                                                                                   |    |

|                 | PA from Fig. 3.12 without $CPW2$                                                                                                                 | 84 |

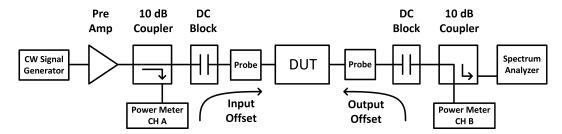

| Figure 3.18:    | Large-signal measurement setup                                                                                                                   | 85 |

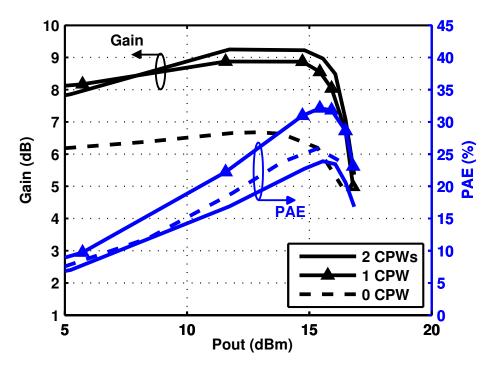

| Figure 3.19:    | Measured gain and PAE as a function of output power at 46                                                                                        |    |

|                 | GHz for the 2-stack PA with two shunt $CPWs$ , with one shunt                                                                                    |    |

|                 | $CPW$ , and no shunt $CPW$ biased at: $V_{G,1}$ 0.2 V, $V_{G,2}$ =1.8 V,                                                                         |    |

|                 | $V_{DD}$ =2.8 V, $I_{DC}$ =8 mA                                                                                                                  | 86 |

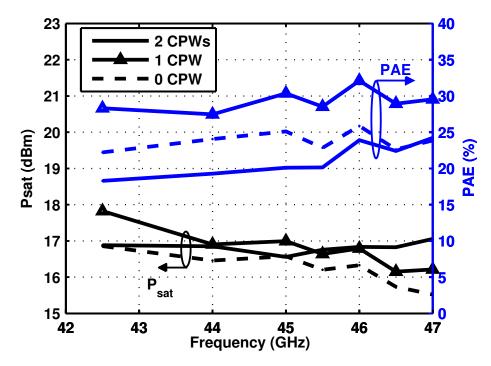

| Figure 3.20:  | Measured PAE and $P_{sat}$ over frequency for 2-stack PA with two shunt $CPWs$ , with one shunt $CPW$ and no shunt $CPW$ | 87         |

|---------------|--------------------------------------------------------------------------------------------------------------------------|------------|

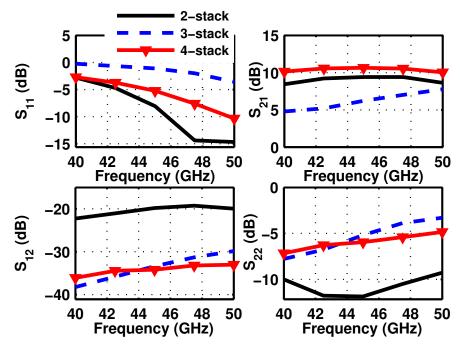

| Figure 3.21:  | Measured S-parameter for 2-stack, 3-stack, 4-stack PA;<br>2-stack: $V_{G,1}$ =0.3 V, $V_{G,2}$ =1.6 V, $V_{DD}$ =2.5 V;  | J 1        |

|               | 3-stack: $V_{G,1}$ =0.2 V, $V_{G,2}$ =1.7 V, $V_{G,3}$ =2.5 V, $V_{DD}$ =3.5 V;                                          |            |

|               | 4-stack: $V_{G,1}=0.3 \text{ V}, V_{G,2}=1.7 \text{ V}, V_{G,3}=2.7 \text{ V}, V_{G,4}=4 \text{ V}, V_{DD}=5 \text{ V}.$ | 88         |

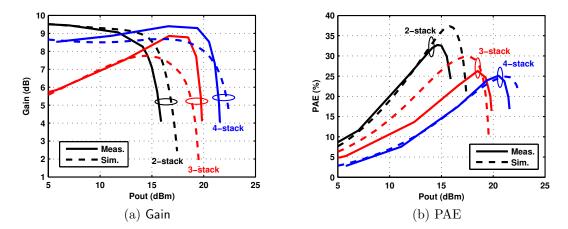

| Figure 3.22:  | Measured gain and PAE versus Pout for 2- and 3-stack PA at                                                               | വ          |

| Figure 2 22.  |                                                                                                                          | 89<br>90   |

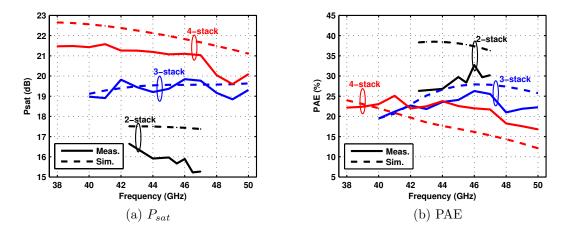

| 0             | Measured peak PAE and Psat versus frequency for 2-, 3-, 4-                                                               | 90         |

| 1 18410 9.21. |                                                                                                                          | 91         |

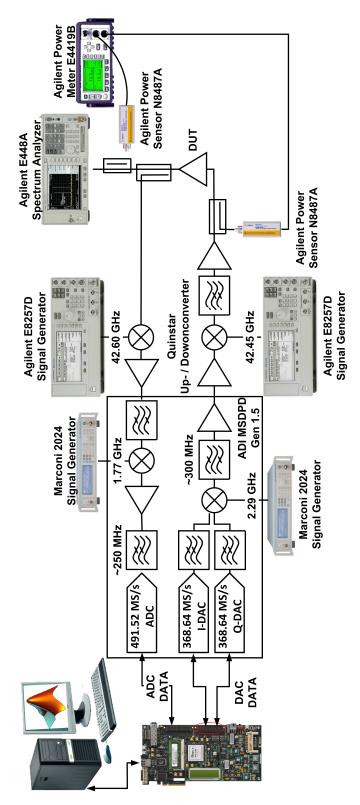

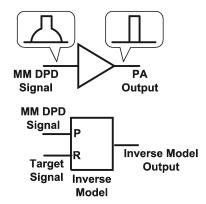

| Figure 4.1:   | Simplified block diagram of mm-wave predistortion system 10                                                              | 00         |

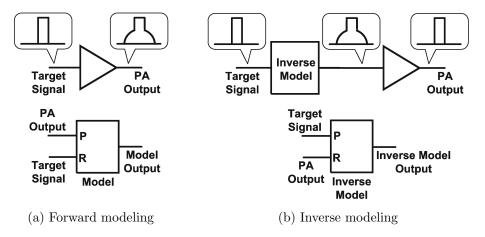

| Figure 4.2:   | Modeling and inverse modeling of PA for DPD                                                                              |            |

| Figure 4.3:   | Inverse modeling of PA using the MM signal as primary input . 10                                                         |            |

| Figure 4.4:   | Spectrum of M-QAM signal after RRC filtering with different $\alpha$ 10                                                  | J5         |

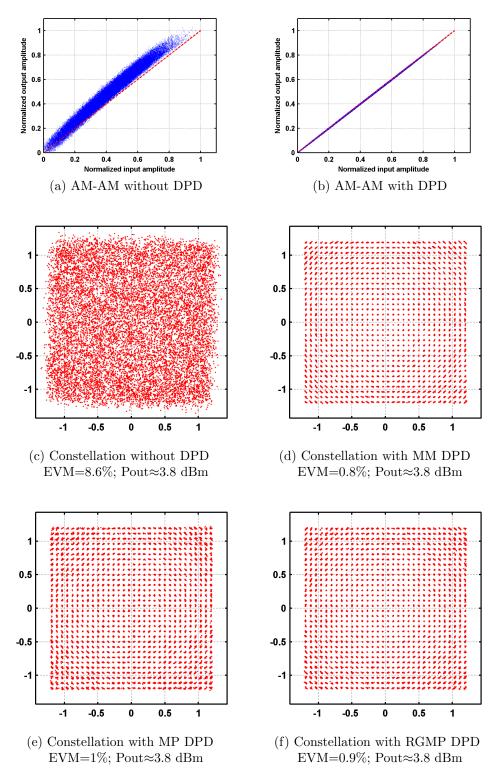

| Figure 4.5:   | Evaluation of linearity and memory of the Mark E system in "through" test. Pout de ambedded to Ovinctor development or   |            |

|               | "through" test; Pout de-embedded to Quinstar downconverter RF input                                                      | US<br>N    |

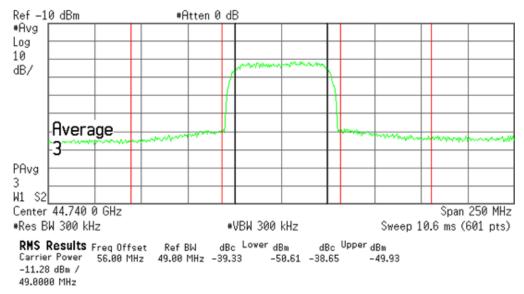

| Figure 4.6:   | Spectral response of system "through" test after the mm-wave                                                             | JO         |

| 118010 1.0.   | driver and after the mm-wave downconverter                                                                               | 10         |

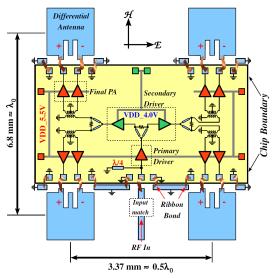

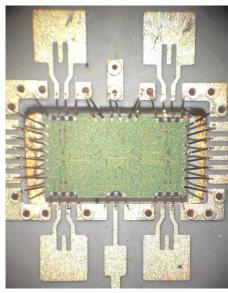

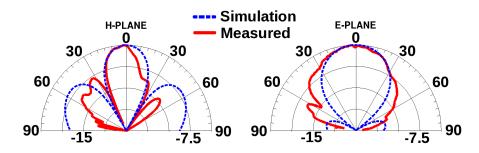

| Figure 4.7:   | Diagram of stacked-FET PA array with differential patch an-                                                              |            |

|               |                                                                                                                          | 13         |

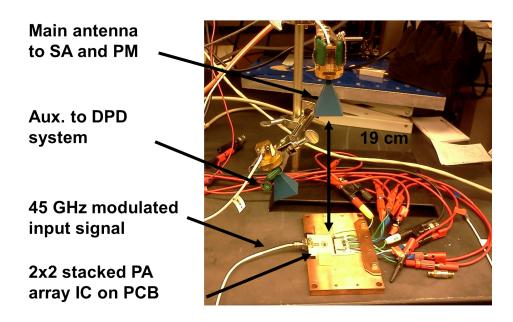

| Figure 4.8:   | Picture of antenna assembly around the PCB with 2x2 antenna                                                              |            |

| FI 4.0        | v                                                                                                                        | 14         |

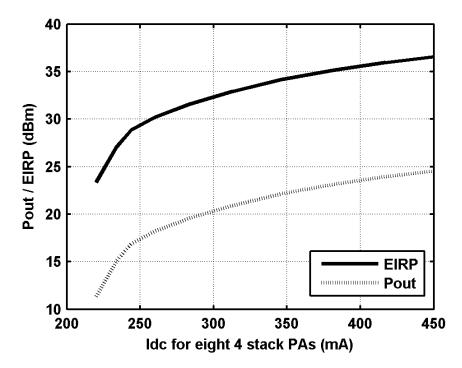

| Figure 4.9:   | Measured EIRP at main antenna and estimated Pout vs. Idc                                                                 | 1 -        |

| Figure 4.10.  | of eight 4-stack PAs for CW excitation                                                                                   | 19         |

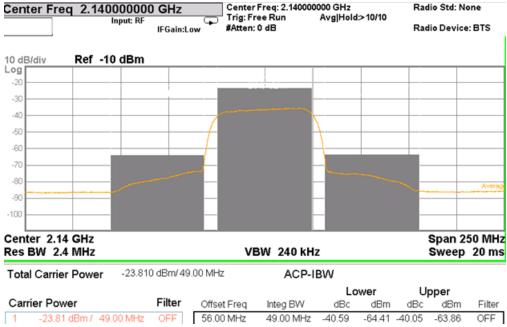

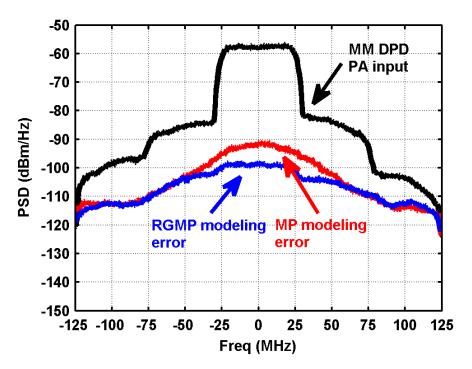

| rigure 4.10.  | <del>-</del>                                                                                                             | 17         |

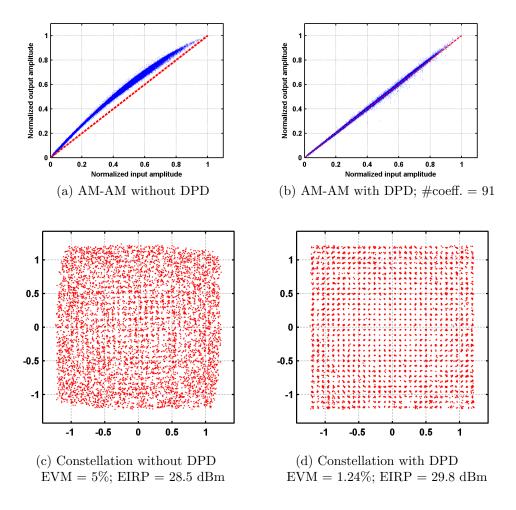

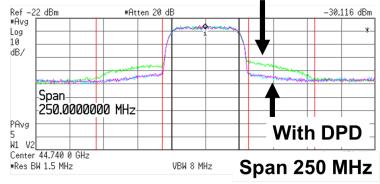

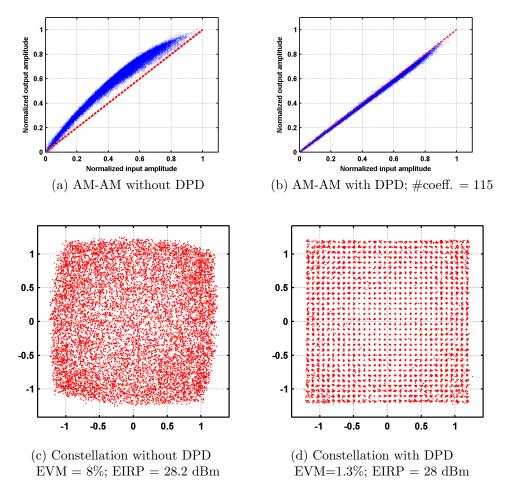

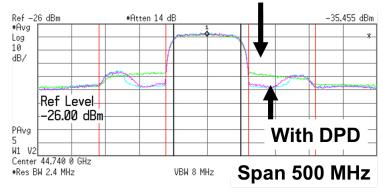

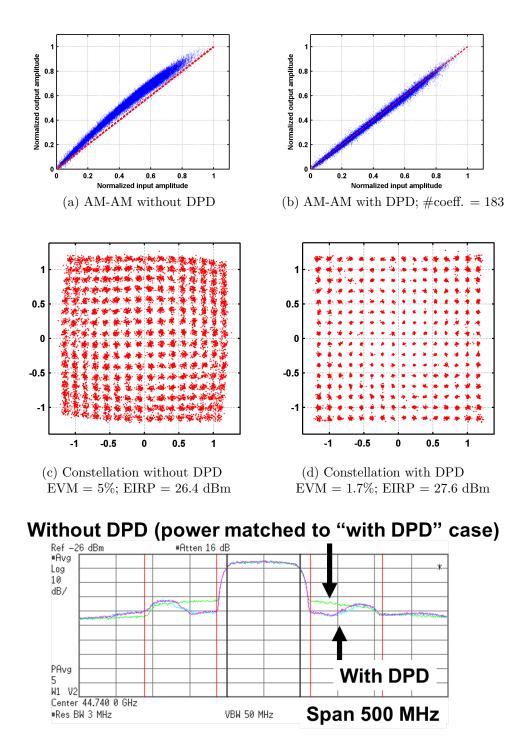

| Figure 4.11:  | PA array output before and after DPD for 49-MS/s, 1024-QAM                                                               |            |

| 0             | signal                                                                                                                   | 21         |

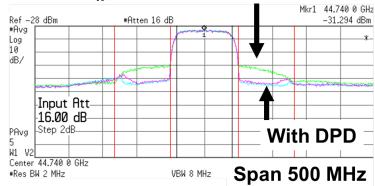

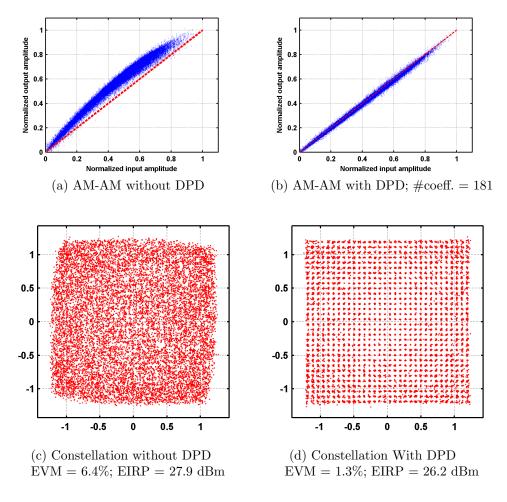

| Figure 4.12:  | PA array output before and after DPD for 82-MS/s, 1024-QAM                                                               |            |

|               | signal                                                                                                                   | 22         |

| Figure 4.13:  | PA array output before and after DPD for 98-MS/s, 1024-QAM                                                               |            |

| D: 4.14       |                                                                                                                          | 23         |

| r igure 4.14: | PA array output before and after DPD for 98-MS/s, 256-QAM signal                                                         | 9 <i>1</i> |

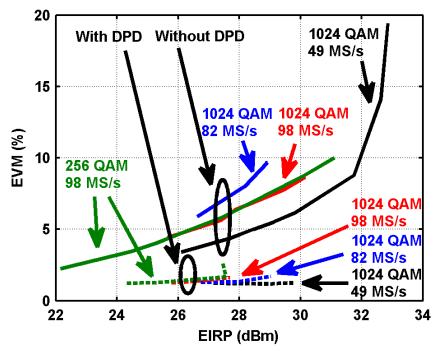

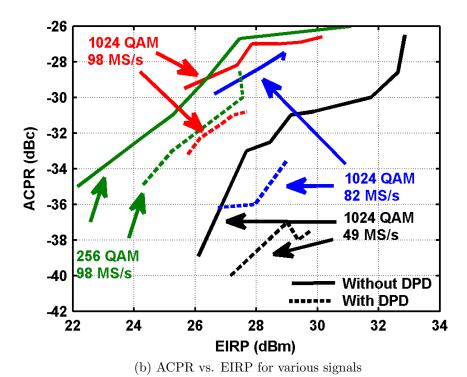

| Figure 4.15   | EVM and ACPR vs. EIRP                                                                                                    | 24<br>26   |

|               |                                                                                                                          |            |

| Figure 5.1:   | 2 UL and 3 DL CA with CM2 desensing on of the receivers 12                                                               | 30         |

## LIST OF TABLES

|                                        | LTE FDD Frequency Bands September 2012 [3] LTE FDD Frequency Bands September 2012 Continued [3] | 6<br>7   |

|----------------------------------------|-------------------------------------------------------------------------------------------------|----------|

| Table 2.1:<br>Table 2.2:               | Cancellation Performance of MISO Filter Order of Complexity of SISO and MISO Filter             | 46<br>52 |

| Table 3.1:<br>Table 3.2:<br>Table 3.3: | Evaluation of Load Impedances in Stacked-FET PA Reactive Intermediate Node Tuning               |          |

| Table 4.1:<br>Table 4.2:               | Specifications of used modulated signals                                                        |          |

| Table 4.3:                             | various filter corner frequencies                                                               |          |

| Table 4.4:                             | mm-wave driver                                                                                  |          |

| Table 4.5:                             | Summary of ACPR and EVM with and without DPD                                                    |          |

| Table 5.1:                             | B3 and B8 TX power at different components of B7 receiver and resulting CM2 power               | 131      |

#### **ACKNOWLEDGEMENTS**

First and foremost, I would like to thank my advisor, Dr. Peter Asbeck, for his support and guidance throughout my graduate studies. I have been very fortunate to have him as my teacher and mentor during my years at UCSD. His technical expertise and guidance were tremendously helpful in achieving my research goals. His endless patience was truly an inspiration and is something I strive to achieve one day for myself. I cannot express my gratitude enough for all his support, and inspiration. Thank you Dr. Asbeck.

I am also exceedingly grateful to my co-advisors Dr. James Buckwalter and Dr. Prasad Gudem. Their assistance and encouragement were tremendously valued especially in regards to the ELASTx project and my distortion cancellation project.

I would also like to thank my dissertation committee: Dr. Bhaskar Rao, Dr. William Hodgkiss, and Dr. Robert Bitmead for providing precious and insightful feedback.

A special acknowledgment is needed for Dr. Byunghoo Jung and Dr. Dongwon Seo whos unwavering support during my undergraduate studies paved the way for my internships at Qualcomm and my doctorate at UCSD.

To my classmates, labmates, and countless others I have had the pleasure to work at UCSD, I would like to thank you all for being part of this journey. In particular Dr. Joohwa Kim for his invaluable training during my early years at the program and my current labmates Bassel Hanafi, Hamed Gheidi, Paul Draxler, Johana Yan, Sataporn Pornpormlikit, for their friendship and support.

On a personal note, I would like to thank my parents, Sona and Mihran, and my brother Tigran. I cannot express enough love for their unconditional support, love, and guidance. Their work ethic, determination, and loving spirit is something I strive to imitate every day.

Lastly, I would like to include a special thanks to my friends in San Diego and Bochum. I will forever cherish the good memories we created over this long and arduous journey. Greg, Willie, Thanh, Chris, Marcel, Khaled, and everyone else who helped me relax, thanks!

The material in this dissertation is based on the following papers. Chapter 2 is mostly a reprint of the material as it appears in "All-Digital Cancellation Technique to Mitigate Receiver Desensitization in Uplink Carrier Aggregation in Cellular Handsets", *Transactions on Microwave Theory and Techniques*, Dec. 2013.

Chapter 3 is mostly a reprint of the material as it appears in "Analysis and Design of Stacked-FET Millimeter-Wave Power Amplifier", *Transactions on Microwave Theory and Techniques*, Apr. 2013.

Section 4.2 is in part a reprint of the material as it appears in 'A CMOS 45 GHz Power Amplier with Output Power >600 mW Using Spatial Power Combining", accepted to 2014 IEEE MTT-S International Microwave Symposium (IMS).

The material in Section 4.3 will in part be used for a publication in preparation with the working title "Digital Predistortion for 1024-QAM of Millimeterwave, Free-space-combined Stacked-FET PAs".

The dissertation author was primary or collaborating author of these materials, and co-authors have approved the use of the material for this dissertation.

#### VITA

| 2008      | Dipl. Ing. in Electrical Engineering, Ruhr University Bochum, Germany |

|-----------|-----------------------------------------------------------------------|

| 2011      | M.S. in Electrical Engineering, University of California, San Diego   |

| 2009-2014 | Graduate Research Assistant, University of California, San Diego      |

| 2014      | Ph. D. in Electrical Engineering, University of California, San Diego |

#### **PUBLICATIONS**

- H.-T. Dabag, H. Gheidi, S. Farsi, P. Gudem, and P. M. Asbeck, "All-Digital Cancellation Technique To Mitigate Receiver Desensitization in Uplink Carrier Aggregation in Cellular Handsets", *Transactions on Microwave Theory and Techniques*, vol. 61, no. 12, pp. 4754-4765, Dec 2013.

- A. Agah, H.-T. Dabag, B. Hanafi, P. M. Asbeck, J. F. Buckwalter and L. E. Larson "Active Millimeter-Wave Phase-Shift Doherty Power Amplifier in 45-nm SOI CMOS", *IEEE Journal of Solid-State Circuits* vol. 48, no. 10, pp. 2338-2350, Oct 2013.

- J. Jayamon, A. Agah, B. Hanafi, H. Dabag, J. Buckwalter, and P. Asbeck, "A W-band stacked FET power amplifier with 17 dBm Psat in 45-nm SOI CMOS", *IEEE 13th Topical Meeting on RF Systems (SiRF)*, 2013.

- H.-T. Dabag, H. Gheidi, P. Gudem, and P. M. Asbeck, "All-Digital Cancellation Technique To Mitigate Self-Jamming In Uplink Carrier Aggregation in Cellular Handsets", *IEEE International Microwave Symposium*, 2013.

- A. Agah, H. Dabag, P. Asbeck, L. Larson, and J. Buckwalter, "High-speed, High-efficiency millimeter-wave transmitters at 45 GHz in CMOS", *IEEE International Microwave Symposium*, 2013.

- H.-T. Dabag, B. Hanafi, F. Golcuk, A. Agah, J. F. Buckwalter, and P. M. Asbeck, "Analysis and Design of Stacked-FET Millimeter-Wave Power Amplifier", *Transactions on Microwave Theory and Techniques*, vol. 61, no. 4, pp. 1543-1556, Apr 2013.

- J. Kim, H. Dabag, P. Asbeck, and J. F. Buckwalter, "Q- and W-band Power Amplifiers in 45-nm SOI CMOS Technology", *IEEE Transactions on Microwave Theory and Techniques*, vol. 60, no. 12, pp. 1870-1877, June 2012.

- H.-T. Dabag, P. M. Asbeck, and J. F. Buckwalter, "Linear operation of high-power millimeter-wave stacked-FET PAs in CMOS SOI", *IEEE International Midwest Symposium on Circuits and Systems*, 2012.

- A. Agah, B. Hanafi, H. Dabag, P. Asbeck, L. Larson, and, J. Buckwalter, "A 45GHz Doherty power amplifier with 23% PAE and 18 dBm output power, in 45nm SOI CMOS", *IEEE International Microwave Symposium*, 2012.

- A. Agah, H. Dabag, B. Hanafi, P. Asbeck, J. Buckwalter, and L. Larson, "A 34% PAE, 18.6dBm 42-45 GHz stacked power amplifier in 45nm SOI CMOS", *IEEE International Microwave Symposium*, 2012.

- S. Pornpromlikit, H.-T. Dabag, B. Hanafi, J. Kim, L. E. Larson, J. F. Buckwalter, and P. M. Asbeck, "A Q-Band Amplifier Implemented with Stacked 45 nm CMOS FETs", *IEEE Compound Semiconductor IC Symposium*, 2011.

- H.-T. Dabag, J. Kim, L. E. Larson, J. F. Buckwalter and P. M. Asbeck, "A 45-GHz SiGe HBT Amplifier with Above 25% Efficiency and 30 mW Output Power", *IEEE Bipolar / BiCMOS Circuits and Technology Meeting*, 2011.

- D. Seo, H. Dabag, Y. Guo, M. Mishra, and G. McAllister, "High-Voltage-Tolerant Analog Circuits Design in Deep-Submicrometer CMOS Technologies", *IEEE Transactions on Circuits and Systems I*, vol. 54, no. 10, pp. 2159-2166, Oct 2007.

- H. Dabag, D. Seo, M. Mishra and J. Hausner, "Electrical Stress-free High Gain and High Swing Analog Buffer Using an Adaptive Biasing Scheme", *IEEE International Symposium on Circuits and Systems*, 2007.

#### ABSTRACT OF THE DISSERTATION

#### Design Techniques for High Data Rates in Microwave and Millimeter-Wave Transmitters

by

#### Hayg-Taniel Dabag

Doctor of Philosophy in Electrical Engineering (Electronic Circuits and Systems)

University of California, San Diego, 2014

Peter M. Asbeck, Chair James F. Buckwalter, Co-Chair Prasad S. Gudem, Co-Chair

In the quest to increase channel bandwidths in wireless communication systems, two important trends are to move towards wider continuous bands at mm-wave frequencies and to aggregate smaller bands at cellular frequencies. In this dissertation a few of the challenges and possible circuit and DSP solutions for efficient high data rate communication using these techniques are described.

First, an issue relating to cellular uplink carrier aggregation is discussed and a DSP based solution developed. Second, the design of a broad band CMOS PA for

mm-wave applications is presented. Third, the design of a mm-wave predistortion system and its use to predistort an array of mm-wave CMOS SOI PAs is described.

In the near term, cellular carriers plan on employing carrier aggregation to increase data rates. This can lead to significant receiver desensitization for a number of LTE band combinations, because of the cross-modulation products created by the nonlinearity of RF front-end components. To mitigate this effect, an all-digital cancellation algorithm is proposed in this thesis that cancelled the cross-modulation product and improved the signal-to-interference-plus-noise ratio (SINR) and error-vector-magnitude (EVM) of the desired received signal by up to 20 dB.

In the second part of the dissertation, the possibility of using mm-wave CMOS PAs for wideband communication is described. The design of CMOS stacked-FET PAs with an emphasis on appropriate complex impedances between the transistors is presented. The stacking of multiple FETs enables the use of higher supply voltages, which in turn allows higher output power and a broader bandwidth output matching network. A 4-stack amplifier design that achieves a saturated output power greater than 21 dBm while achieving a maximum power-added-efficiency (PAE) greater than 20% from 38 GHz to 47 GHz is reported.

Finally, the thesis describes predistortion of an array of stacked-FET PAs after spatial power combining. Predistortion improved the signal quality to a high level, which allowed the use of complex modulation schemes, which in turn allows high data rates in a spectrally efficient manner. After predistortion a 100-MHz wide, 1024-QAM signal was demodulated with an EVM of 1.3%, which corresponds to a data rate of 1 Gb/s.

# Chapter 1

## Introduction

It is just about 40 years ago that the first cellular call from a prototype mobile phone was made and about 30 years when the first commercial mobile phones became available. The initial phones were heavy, bulky, and their talk time was very short. After many iterations of improvements, cellular phones became smaller, had acceptable battery life, and became sufficient for (but limited to) voice calls and text messaging.

More recently, the simultaneous increase in available data rates for wired Internet connections enabled a variety of new Internet based multimedia and business services. The user demand to enjoy these contends in wireless fashion keeps driving the the demand for higher data rates for wireless communication systems. To fill this need, various techniques are under development. The attempted solutions generally center around two approaches: increasing the available bandwidth and increasing the number of bits transmitted in a given bandwidth, or a combination of the two.

In this chapter, a brief overview is provided to review some of the challenges on the path to higher wireless data rates. First, a brief review is given to explain the limitation on obtainable data rates per occupied bandwidth. Second, techniques are discussed to increase the available bandwidth. Third, implementation difficulties focusing on the transmitter, in particular the power amplifier (PA), are described. The fourth and fifth section describe the scope and structure of the dissertation.

## 1.1 Spectral Efficiency of Digital Modulation

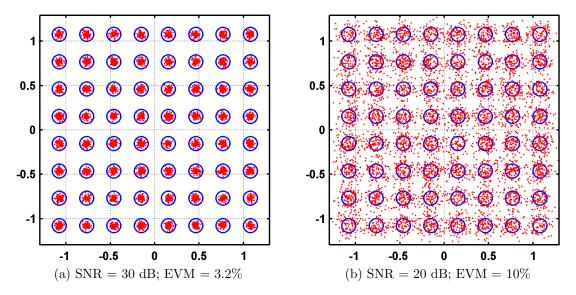

Even though our transmitters radiate signals at gigahertz frequencies the actual information transmitted generally only occupies multiple megahertz of unique user data. The method how the bits are encoded on the carrier in a bandwidth limited signal is called modulation. Earlier wireless communication standards used analog modulation schemes, which have been replaced by their digital counter parts. There exists a wide variety of modulation schemes with different tradeoffs. This section does not try to give a complete overview, but just enough background information to explain the benefits of more complex modulations and the practical challenges they pose. M-ary quadrature amplitude modulation (M-QAM) in some form is the basis of many modern communication standards. Fig. 1.1 shows a 64-QAM constellation with 64 unique symbols. In this constellation log2(M) i.e. 6 bits per symbol can be encoded. Fig. 1.1(a) and Fig. 1.1(b) respectively show an example of received modulations (in I and Q plane) for signal to noise ratio (SNR) of 30 dB and 20 dB. From the figures it is apparent that correct assignment of each received symbol to its target is dependent on the SNR. For example the constellation shown in Fig. 1.1(a) allows error free reception and the signal shown in Fig. 1.1(b) will have a significant number of errors.

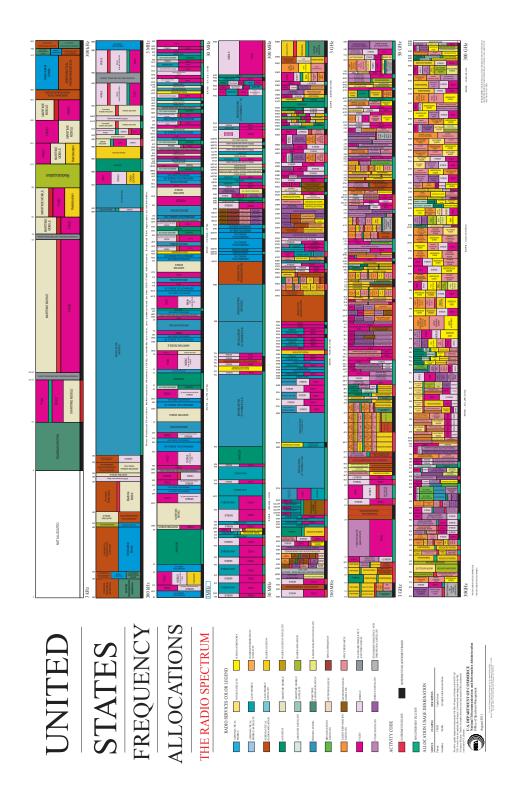

Fig. 1.2(a) plots the required SNR for M-QAM for a targeted bit error rate

Figure 1.1: 64-QAM constellation for various SNRs

(BER), assuming the only disturbance is white Gaussian noise. A BER between  $10^{-3}$  and  $10^{-6}$  are frequently targeted in wireless systems [1]. An alternative representation to SNR is the error vector magnitude (EVM). In the constellation diagram it represents the normalized power difference between the actual received symbol and the ideal symbol. The peak EVM and root-mean-square (rms) average are often specified for a received signal. With (1.1) one can approximate the average EVM for a given SNR. Fig. 1.2(b) plots the BER versus EVM. One can see that for higher order modulation schemes the SNR and EVM requirements increase significantly even though the achieved increase in data rate is not as high.

$$EVM(\%) \approx 10^{-SNR(dB)/20} \cdot 100$$

(1.1)

Another factor and the key motivator to go to higher order modulations is the required signal bandwidth. It is important to note that the bandwidth is independent of the modulation order. This leads to the concept of spectral efficiency, which is defined as the number of transmitted bits per bandwidth. Since higher

**Figure 1.2**: Signal quality requirements for correct data reconstruction; highlighted are the average SNR / EVM for a BER of  $10^{-6}$ .

order modulation occupy the same amount of bandwidth the spectral efficiency increases with increased modulation order. However, the higher modulation order require higher SNR i.e. better EVM for correct demodulation. Achieving the good SNR/EVM over wireless links poses significant implementation challenges in particular in the power amplifier (PA). Some of these challenges are discussed in Section 1.3.

Other techniques such as multiple-input and multiple-output (MIMO) antenna arrays are being developed to further increase the spectral efficiency and orthogonal frequency-division multiplexing (OFDM) modulation is used to increase the effectively achievable data rates. The solutions in the dissertation do not go into issues relating to these techniques, but the achieved results can be used in conjunctions with MIMO and OFDM systems.

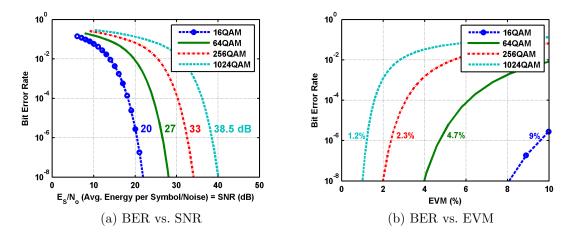

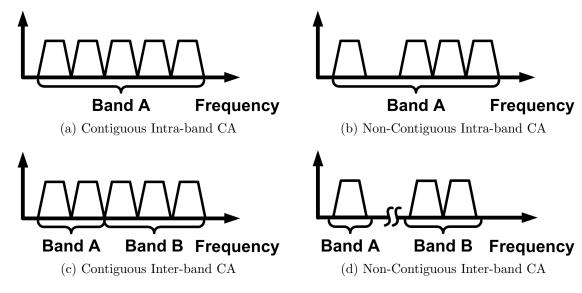

## 1.2 Increasing the Bandwidth

Since increasing the spectral efficiency is becoming increasingly more difficult and the increase in data rates are modest by further increase of the modulation order, a lot of attention is focused on increasing the bandwidths used. In cellular system this is made difficult due to the scarcity of available bandwidth and its fragmentation as shown in Fig. 1.3. Therefore, the upcoming LTE-A standard allows aggregating up to five 20-MHz LTE channels [2]. Fig. 1.4 shows the four possible frequency plans of carrier aggregation. The simplest two would aggregate multiple continuous or non-continuous channels in a single band. The third combines continuous or non-continuous channels across multiple adjacent bands. The fourth combines multiple channels across non-continuous bands. Unfortunately, most bands are significantly smaller than 100 MHz as listed in Table 1.1 and Table 1.2. This regulatory restriction virtually forces the need for inter band carrier aggregation (CA) in cellular systems. Even if cost and power inefficiency in a simplistic implementation of CA with two parallel transceivers is accepted, CA of certain band pairs can cause problems. One specific issue in uplink CA (UL CA) and a potential solution is discussed in Chapter 2 of this dissertation.

$\textbf{Table 1.1:} \ \ \text{LTE FDD Frequency Bands September 2012 [3]}$

| LTE FDD | Uplink Frequency | Downlink Frequency | Width |

|---------|------------------|--------------------|-------|

| Band    | (MHz)            | (MHz)              | (MHz) |

| 1       | 1920 - 1980      | 2110 - 2170        | 60    |

| 2       | 1850 - 1910      | 1930 - 1990        | 60    |

| 3       | 1710 - 1785      | 1805 - 1880        | 75    |

| 4       | 1710 - 1755      | 2110 - 2155        | 45    |

| 5       | 824 - 849        | 869 - 894          | 25    |

| 6       | 830 - 840        | 865 - 875          | 10    |

| 7       | 2500 - 2570      | 2620 - 2690        | 70    |

| 8       | 880 - 915        | 925 - 960          | 35    |

| 9       | 1749.9 - 1784.9  | 1844.9 - 1879.9    | 35    |

| 10      | 1710 - 1770      | 2110 - 2170        | 60    |

| 11      | 1427.9 - 1447.9  | 1475.9 - 1495.9    | 20    |

**Table 1.2**: LTE FDD Frequency Bands September 2012 Continued [3]

| LTE FDD   | Uplink Frequency | Downlink Frequency | Width |

|-----------|------------------|--------------------|-------|

| Band      | (MHz)            | (MHz)              | (MHz) |

| 12        | 698 - 716        | 728 - 746          | 18    |

| 13        | 777 - 787        | 746 - 756          | 10    |

| 14        | 788 - 798        | 758 - 768          | 10    |

| $-15^{1}$ | 1900 - 1920      | 2600 - 2620        | 12    |

| $16^{1}$  | 2010 - 2025      | 2585 - 2600        | 15    |

| 17        | 704 - 716        | 734 - 746          | 12    |

| 18        | 815 - 830        | 860 - 875          | 15    |

| 19        | 830 - 845        | 875 - 890          | 15    |

| 20        | 832 - 862        | 791 - 821          | 30    |

| 21        | 1447.9 - 1462.9  | 1495.9 - 1510.9    | 15    |

| 22        | 3410 - 3490      | 3510 - 3590        | 80    |

| 23        | 2000 - 2020      | 2180 - 2200        | 20    |

| 24        | 1626.5 - 1660.5  | 1525 - 1559        | 34    |

| 25        | 1850 - 1915      | 1930 - 1995        | 65    |

| 26        | 814 - 849        | 859 - 894          | 35    |

| 27        | 807 - 824        | 852 - 869          | 17    |

| 28        | 703 - 748        | 758 - 803          | 45    |

<sup>&</sup>lt;sup>1</sup> Reserved

Figure 1.3: 2011 US frequency allocations chart illustrates the heavy fragmentation

Figure 1.4: Possible frequency plan for carrier aggregation.

Even if all of the challenges posed by CA are solved, the maximum available bandwidth is still limited to 100 MHz. However, for satellite communication and wireless high resolution video transfer even higher data rates are required than available in the relatively low frequency bands around 1-5 GHz. Another effort focuses on cost effective solutions for mm-wave wireless system, in particular in the Q (33 - 50 GHz) and V (40 - 75 GHz) band. In those continuous channels of 1 GHz or larger are possible [4].

## 1.3 Challenges in mm-Wave CMOS PA Design

Due to the aggressive scaling of transistor sizes, reasonable gains are achievable in mm-wave bands. The unity current gain  $(f_T)$  and unity power gain  $(f_{max})$  in today's CMOS process are in the order of 300 GHz and are predicted to continue increasing as illustrated in Fig. 1.5. This makes the use of CMOS transistors viable for mm-wave amplifiers.

Unfortunately, the decreasing feature sizes also reduce the voltage handling

Figure 1.5: 2011 ITRS roadmap for  $f_T$  and  $f_{max}$  [5]

capabilities of the transistor. There are several breakdown mechanisms in CMOS transistors such as the gate oxide breakdown, hot carrier degradation, and punch-through. To avoid these breakdown mechanisms, the drain-source, the gate-drain, and the gate-source voltage need to be kept below certain voltage levels. Unfortunately, those voltage limits decrease with the decreasing feature sizes of the transistor, which is particularly disadvantages for power amplifiers (PA).

In order to achieve high output powers one can either increase the output voltage swing and / or output current swing of the PA. The former is limited by the transistor breakdown voltages. The latter can be increased to some extend by increasing the transistor gate width. However, increasing the transistor width, and hence current, also increases the transistor capacitance, which decreases the transistor gain at high frequencies and makes the input matching more challenging.

In addition, increasing the transistor current also decreases the load line

impedance  $R_L$  as state in (1.2), where  $V_{max}$  is the maximum RF swing the device can tolerate and  $I_{max}$  is the maximum current the device can provide. Loading a PA with  $R_L$  ensures that it operates at its optimal efficiency and highest achievable power [6]. As mentioned before, an increase in current also decreases  $R_L$ , which makes the output matching network more challenging.

$$R_L = V_{max}/I_{max} (1.2)$$

In summary, the reduced feature sizes for CMOS transistors are required to ensure sufficient gain at mm-wave frequencies. Unfortunately, this goes hand in hand with reduced voltage handling capability, which effectively reduces the output power and efficiency.

Since achieving high output powers at mm-wave is a challenge in itself, one should operate the PAs as close as possible to their saturated output power. Unfortunately, the linearity of amplifiers significantly degrades close to saturation. A PA in compression, as any nonlinear system, pass a distorted copy of its input signal to the output. Many of the distortion components land far way from the band of interest and can easily be filtered. However, some of the intermodulation products land very close to the band of interest. This is illustrated in Fig. 1.6. If 3-tones are fed to a PA, which only experiences a third order nonlinearity the output of the PA will generate the original 3-tones and additional tones in- and out-of-band. Fig. 1.6(b) shows the nonlinear PA output for a wideband input signal.

The in-band distortion corrupts the desired signal and reduces its signal to noise and interference ratio (SINR), which reduces the EVM in a similar relationship as the SNR in (1.1).

The out-of-band signal interferes with neighboring channels. The exact

Figure 1.6: Nonlinear PA distorting input signal.

acceptable adjacent channel power leakage (ACP) depends on the used communication standard. But unless it is kept at reasonable low levels e.g. 33 dBm below the main signal, the achievable EVM of the adjacent channel is limited. Alternatively, one would have to place "guard bands" between two channels, which is disadvantageous due to the scarcity of available bandwidth.

## 1.4 Scope of the Dissertation

There are various challenges and potential solutions in the quest for higher data rates. This dissertation focuses on two aspects.

First, an immediate issue in an uplink CA (UL CA) transceiver is studied. The simultaneous data transmission in certain band pairs can cause a self-jamming of the receiver due to nonlinearity of the passive front-end. The nature of the problem allowed a DSP based solution, which has the advantage that cost effective implementations can be realized very quickly.

The second part of the dissertation focuses on the mm-wave communication system. There the availability of low cost and efficient PAs is a major challenge. This is addressed by adapting the "stacked-FET PA" architecture to mm-wave

operation, which resulted in record efficiencies and power for CMOS PAs at mmwaves. In addition digital predistortion is applied to an array of the "stacked-FET PAs" after spatial power combining, which allowed the use of high complexity signals for high spectral efficiency.

## 1.5 Dissertation Organization

In this chapter the critical issues for spectrally efficient high-speed microwave and millimeter wave wireless communication systems have been reviewed.

Chapter 2 considers cell phone transceivers suitable for uplink carrier aggregation (UL CA) to increase transmit data rates. UL CA can lead to significant receiver desensitization for a number of LTE band combinations, because of the cross-modulation products created by the nonlinearity of antenna switches and duplexers in the RF front-end. To mitigate this effect, an all-digital cancellation algorithm is proposed that relies solely on the digital representation of the signals, a peak covariance search for time alignment, and an adaptive distortion canceller.

Chapter 3 discuses stacked-FET CMOS mm-wave PAs with a focus on design of appropriate complex impedances between the transistors. The stacking of multiple FETs allows increasing the supply voltage, which in turn allows higher output power and a broader bandwidth output matching network. Different matching techniques for the intermediate nodes are analyzed and used in 2-, 3- and 4-stack single-stage Q-band CMOS power amplifiers (PAs).

In Chapter 4 a wideband digital predistortion system for mm-wave applications is described. With this system, an ensemble of stacked-FET PAs is predistorted after their output signals are spatially power combined. An auxiliary antenna is used to feed back part of the radiate signal to the digital predistortion

(DPD) system and the main lobe is monitored on a spectrum analyzer to confirm the effectiveness of the DPD.

# Chapter 2

Receiver Desensitization in

Uplink Carrier Aggregation Due

to Mixing of Two Transmit

Signals in Cellular Handsets

# 2.1 Background: Cellular Transceivers for Uplink Carrier Aggregation

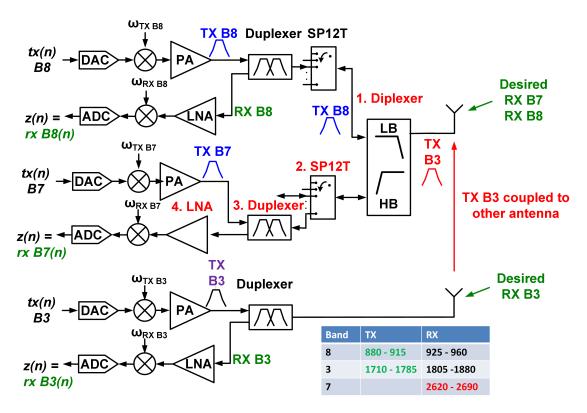

One approach to meet user demands for high data rates in handsets is the use of wider signal bandwidths. This cannot always be directly applied, since many carriers own noncontiguous spectra in various frequency bands. To enable the use of multiple bands, next-generation cellular standards support uplink carrier aggregation (UL CA) [2]. Fig. 2.1(a) shows a block diagram of a two transmitter system used for UL CA, which comprises two separate TX and RX chains as well as two antennas. Since modern cell phones need to cover a wide range of bands, each

tx1(n) DAC

PA1

RX1

Duplexer TX2" TX1' SP12T TX2"

10 dB isolation tx2(n) DAC

PA2

TX2

Duplexer TX1" TX2' SP12T TX1"

Desired RX2 cm3 enerated in switch and duplxer tx2(n) + cm3(n)

(b) UL CA transceiver with cross modulation generated in the front-end

Figure 2.1: Block diagram of two transmitter system for UL CA.

antenna is preceded by a multiport switch, which allows transmitters for different bands to share the same antenna. As shown in Fig. 2.1(b), due to poor antenna isolation in a cell phone, a copy of the first transmitted waveform (TX1) will be received by the second transmitter (and vice versa).

If all system components were perfectly linear, the coupled version of TX1 would only act as an out-of-band jammer. However, nonlinear behavior of switches and duplexers creates cross-modulation distortion products that can land in the receive band for certain band pairings. One can calculate the center frequency of

**Figure 2.2**: Frequency view of third-order cross-modulation product (CM3) created by band 5 and 13 transmit signals across antenna switch.

both third-order cross-modulation products (CM3s) using (2.1):

$$\omega_{CM3.1} = 2 \cdot \omega_{TX1} - \omega_{TX2}, \quad \omega_{CM3.2} = 2 \cdot \omega_{TX2} - \omega_{TX1}$$

(2.1)

where  $\omega_x$  is the center frequency of that particular signal. Fig. 2.2 illustrates this for bands 5 (B5) and 13 (B13). For example, if  $\omega_{TX1}$  is 782 MHz and  $\omega_{TX2}$  is 831.75 MHz, one can calculate with (2.1) that  $\omega_{CM3,2}$  is 881.5 MHz, which is inside of the B5 RX band. Other examples of problematic band pairs for UL CA are as follows: B2 and B4, and B8 and B20. The distortion power can be estimated by:

$$P_{CM3} = 2 \cdot P_{TX1} + (P_{TX1} - \text{path loss}) - 2 \cdot IIP3$$

(2.2)

where  $P_x$  is the power of the particular signal in dBm, and IIP3 refers to the inputreferred third-order intercept points of the component. State-of-the-art antenna switches and duplexers, respectively, have IIP3s of 70 dBm to 80 dBm [7,8]. When the TX power at each antenna is 24 dBm and considering 10-dB antenna isolation, the resulting CM3 power, according to (2.2), is -79 dBm, which is 28 dB above the thermal noise floor for a 5-MHz signal. Despite the high linearity of switches and duplexers, the distortion power is high enough to severely desensitize the receiver. To overcome this, one could reduce the power of both transmitted signals by approximately 10 dB. However, this would severely compromise the link budget for UL CA. Improving the antenna isolation from 10 to 40 dB would also greatly mitigate the receiver desensitization. However, this is challenging due to the limited cavity size dictated by cell phone dimensions.

Alternatively, one could develop components with IIP3s greater than 85 dBm, which are currently not available. Even if such parts with the required linearity become available in the future, replacement of all required passive components with high linearity components would significantly increase the cost. Alternatively, one could take advantage of the deterministic nature of the sources of self-jamming and employ digital cancellation techniques to mitigate the receiver desensitization [9–11]. In this chapter the digital cancellation technique is extend to mitigate receiver desensitization caused by two unrelated transmit signals in UL CA. A multiple-input single-output (MISO) digital filter is added to the receiver DSP to reduce RF front-end hardware cost and complexity. This chapter is divided into eight sections. The previous section described a cellular UL CA transceiver and explains the cause of the desentization of one of the receivers. Section 2.2 goes into the background of adaptive noise cancellation and highlights two exemplary uses of this technique. Section 2.3 describes the modified cancellation algorithm when used to avoid self-jamming in UL CA transmitters. In Section 2.4, the sensitivity of the cancellation algorithms to time alignment errors is studied in representative simulated experiments. Section 2.5 describes laboratory measurements using handset components to demonstrate up to 20 dB of cancellation, by utilizing the proposed algorithm. In Section 2.6, the convergence rate of the algorithm is discussed, and Section 2.7 briefly describes the order of complexity of the algorithms. Section 2.8 summarizes the conclusions of the use of DSP based

cross-modulation cancellation.

## 2.2 Prior Application of Noise/Distortion Cancellation Algorithms

Since UL CA is an upcoming technique, no published worked has focused on the self-jamming issue described in Section 2.1. Therefore, there is no prior cancellation algorithm for this particular case. However, to give a brief overview and explain the origin of adaptive noise cancellation a short summary of the paper "Adaptive Noise Cancelling: Principles and Applications" is provided in this section [12].

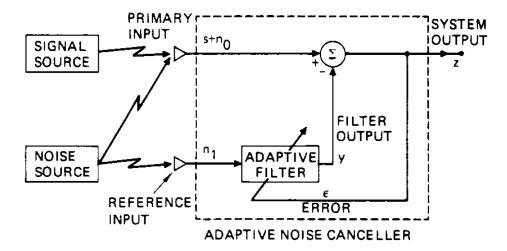

#### 2.2.1 Principle of Adaptive Noise Canceller

Fig. 2.3 illustrates the problem and the adaptive noise canceller. A primary input receives a desired signal (s) contaminated by noise  $(n_0)$ . If one had exact knowledge of  $n_0$  one could simply subtract it from the contaminate received signal. Unfortunately, exact knowledge of  $n_0$  is generally not available. However, in many cases a "reference noise"  $(n_1)$ , which is strongly correlated to  $n_0$  can be obtained. If for example the difference between  $n_0$  and  $n_1$  can be compensated with a filter, one could process the reference input  $n_1$  subtract it from the primary input. The output of the adaptive noise canceller z would equal the desired signal s. Generally, the structure and parameters of the required filter are unknown. However, by feeding back z to the filter and adapting it one can find a close approximation to the ideal solution such that z approximates s.

At first glance it is not clear how z can be used to adapt the filter for optimal performance. Widrow et. al provide a detailed derivation in [12]. The key

Figure 2.3: The adaptive noise cancelling concept [12].

observation is that  $n_1$  and  $n_0$  are strongly correlated to each other and neither of them is correlated to s. Therefore, by subtracting y from the primary input, the power in z can only decrease by cancelling  $n_0$  from the primary input. Various algorithms have been proposed of the past decades on how to quickly and efficiently adapt the filter coefficients such as the least squares method, the least mean square (LMS) algorithm, and the recursive least squares (RLS) algorithm [13].

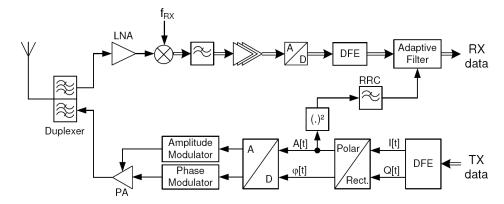

A recent use of the adaptive noise canceller for cell phone applications has been presented in [14]. Fig. 2.4 shows a block diagram of a homodyne transceiver. The duplexer isolates the transmitter from the receiver in system when the transmitter and receiver operate simultaneously. However, due to its finite suppression some of the TX signal leaks into the receiver. This is referred to as TX-leakage. In a homodyne architecture the desired received signal is directly downconverted to baseband, where it is sampled by an ADC. The downconverted TX-leakage can be suppressed with conventional filters in the analog or the digital domain. However, due to nonlinearity of the receiver a second order intermodulation component (IMD2) caused by the TX-leakage lands on top of the desired received signal after downconversion and cannot be suppressed with conventional filters. The authors

**Figure 2.4**: Block diagram of a transceiver using polar modulation for transmission [14].

of [14] propose to use the adaptive noise canceller to suppress the interference caused by the IMD2 of the TX-leakage. In this case the reference signal is easily obtainable by squaring the known TX signal. The adaptive filter compensates for the difference in frequency response of the actual IMD2 and the estimated IMD2. Lederer et al. show that this technique reduced the receiver desense due to even order nonlinearity of the receiver by 3-5 dB.

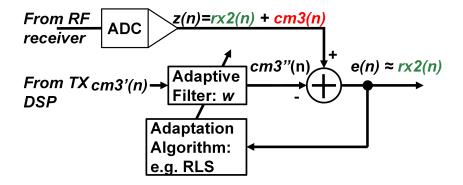

# 2.3 Proposed Cancellation Algorithm for UL CA Handsets

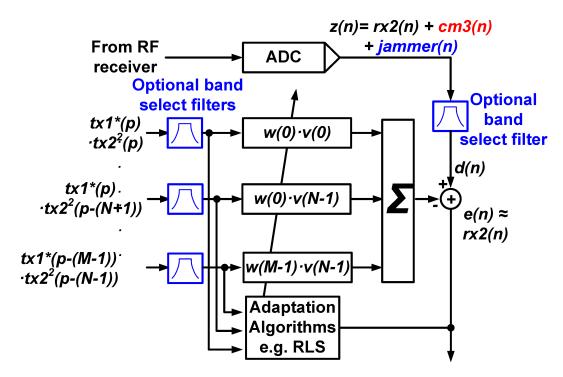

The interference cancellation for the self-jamming for UL CA handsets described in Section 2.1 is based on the adaptive distortion cancellation approach reviewed in the previous section. Fig. 2.5 shows the block diagram of the distortion canceller for the UL CA case, where a desired received signal rx2(n) is contaminated by a deterministic and predictable signal, in this case the cm3(n) created from the switch or other nonlinear components (where n is time sample index). If an estimate (cm3'(n)) of the contaminating distortion can be measured

Figure 2.5: Block diagram of adaptive distortion canceller.

or computed, one can subtract it from the distorted received signal z(n) such that only the desired received signal is left at the output of the filter  $e(n) \approx rx2(n)$ . The distortion estimate can be generated within the transmitter DSP, since both TX1 and TX2 are known. Unfortunately, the distortion estimate (cm3'(n)) does not perfectly match the real distortion, since the latter experiences some filtering in the transmitter, power amplifier, and passive front-end components. An adaptive FIR filter w of length M can be used to modify the reference to compensate for the linear response of the system. The optimal filter weights of w, which minimize the effect of cm3(n) in e(n), can be found either in block fashion using the pseudoinverse method discussed below, or are determined iteratively with algorithms such as recursive least squares (RLS). Since rx2(n) is uncorrelated with cm3'(n), the desired signal is not disturbed by the filtering.

## 2.3.1 Interference Estimation and Single-Input Single-Output Adaptive Distortion Canceller

The major challenge for good cancellation is the computation of a good estimate of the distortion (cm3'(n)). Since RF signals TX1" and TX2' at the ports of the switch are always in the passband of the system, it is a reasonable

approximation that the signals are not noticeably changed from the known digital baseband signals tx1(n) and tx2(n). Note that one only needs to consider one of the cross-modulation products, since the others lie outside of the receive band and are attenuated by the duplexer. One can estimate the baseband equivalent of of the relevant distortion as

$$cm3'(n) \approx tx1^*(n) \cdot tx2^2(n).$$

(2.3)

Unfortunately, this is not a sufficiently accurate estimate, since the transmitted signals and the distortion experience an unknown delay in the transmitter and receiver hardware. The DSP distortion estimate needs to compensate for this delay. This is a common time alignment problem and can be represented as follows:

$$cm3'\{J\}(n) \approx tx1^*(n-J) \cdot tx2^2(n-J)$$

(2.4)

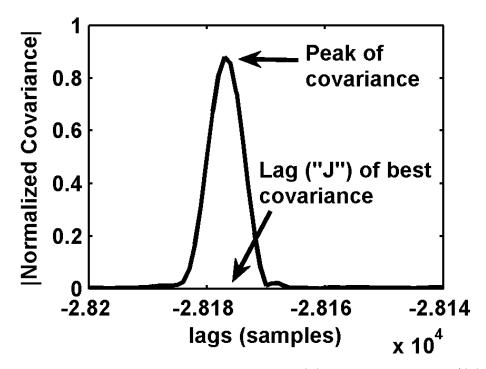

where J corresponds to the number of delay taps required to time align the distortion estimate with the measured distortion in the received signal z(n). Various time alignment algorithms can be applied, such as the early - late algorithm [15] or other covariance-based algorithms. In this case, the covariance of the measured distortion and the distortion estimate is computed, as shown in Fig. 2.6. In a particular hardware implementation, the group delay is fairly constant, and the search space of J is small.

In addition to the general group delay between the distortion estimate and the measured distortion, it is critical to note that the signal TX1" and TX2' experience slightly different group-delay profiles by the time they reach the switch. This group delay difference is critical and has a significant impact on the quality of the distortion estimate, and therefore needs to be compensated.

**Figure 2.6**: Covariance of measured cm3(n) and estimated cm3'(n).

Equation 2.5 includes a new variable K, which can be used to compensate for the group-delay difference of the two signals:

$$cm3'(n)\{J,K\} \approx tx1^*(n-J-K) \cdot tx2^2(n-J).$$

(2.5)

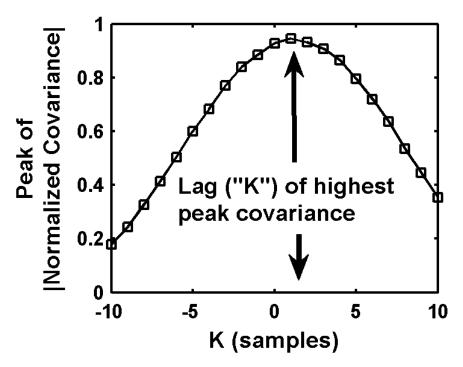

One approach to find a good value for K is based on the covariance. The peak of the covariance shown in Fig. 2.6 depends on K. Fig. 2.7 shows the peak of the covariance of the measured distortion cm3(n) and distortion estimate  $cm3'\{J,K\}$  for various values of K. For a large search space of K, this would be computationally expensive. Fortunately, K is based on known and relatively constant delays of the transmitter components, and only a fine alignment within a few samples is required.

Fig. 2.8 shows the complete diagram of the cancellation algorithm, where

**Figure 2.7**: Peak of covariance from Fig. 2.6 versus the group-delay difference between TX1" and TX2'.

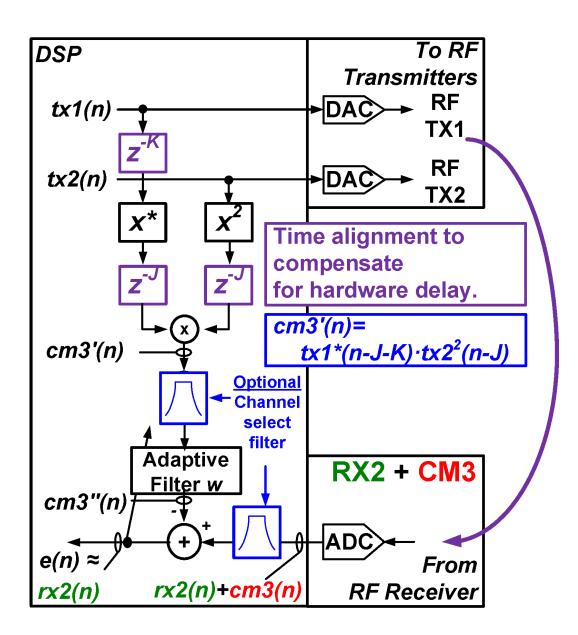

J and K are determined with the methods described above. The adaptive distortion canceller shown in Fig. 2.8 has been presented in [16]. It implements a single-input single-output (SISO) distortion canceller, where cm3'(n) is calculated prior to the adaptive filter. It has been demonstrated to work very effectively in directly coupled transmitters. However, the SISO algorithm does not give the adaptation sufficient degrees of freedom to separately modify tx1(n) and tx2(n). This is required when the two transmitters are coupled through the antenna with strong spectral shaping or in cases where multipath effects are significant or TX2 is reflected by its own transmit antenna due to insufficient matching.

Figure 2.8: Block diagram of SISO adaptive distortion canceller.

#### 2.3.2 Multiple-Input Single-Output Adaptive

#### **Distortion Canceller**

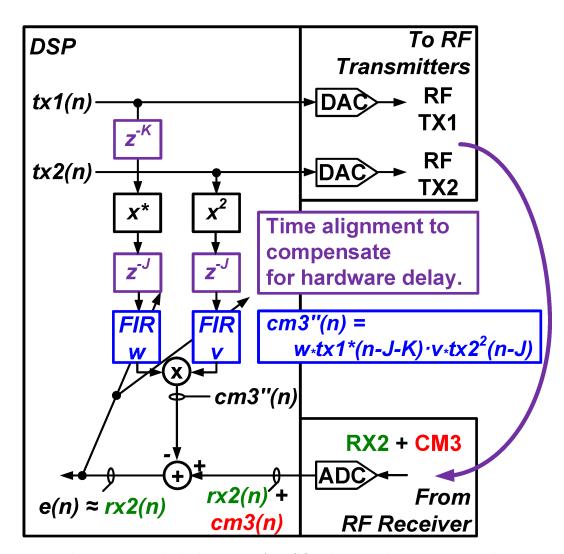

In this section, a multiple-input single-output (MISO) adaptive distortion canceller is proposed as an extension to the SISO canceller. Conceptually,  $tx1^*(n)$ (the complex conjugate of tx1(n)) and  $tx2^2(n)$  pass through their own adaptive FIR filters w and v before they are multiplied to form the estimated cancellation signal cm3''(n). The MISO approach has sufficient degrees of freedom in the adaptation to compensate for the transfer function and multipath effects in antenna coupled transmitters. Fig. 2.9 shows a block diagram of the MISO filter structure. An additional advantage of the MISO algorithm with separate filters for  $tx1^*(n)$  and  $tx2^{2}(n)$  is that it can compensate for incorrect estimation of K if the filter length of v and w is sufficient. This can even be used to skip the search for K using the covariance method explained above. Instead of using a separate search for K, one can take advantage of the fact that in a given hardware environment K will be relatively fixed in a range of  $K_{min}$  to  $K_{max}$ . One can set K to  $K_{min}$  and extend the filter length of w by  $K_{max} - K_{min}$  taps (often one or two taps are sufficient). This has the advantage that no separate covariance based search for K is necessary; however, this increases the order of complexity of the parameter estimation.

Whether or not a separate covariance-based search for K is performed, the challenging part is the optimal estimation of the filters w and v. Unfortunately, direct estimation of the filter M + N coefficients of w and v is difficult due to the nonlinear dependency of the parameters. Following the logic of [17], the input-

Figure 2.9: Block diagram of MISO adaptive distortion canceller.

output relationship of MISO filter can be written as

$$cm3(p) = \left(\sum_{i=0}^{M-1} w_i \cdot tx1^*(p-i)\right) \left(\sum_{j=0}^{N-1} v_i \cdot tx2^2(p-j)\right) + n(p)$$

$$= \sum_{i=0}^{M-1} \sum_{j=0}^{N-1} w_i \cdot v_j \cdot tx1^*(p-i) \cdot tx2^2(p-j) + n(p)$$

(2.6)

where n(p) is the modeling error, e.g., caused by noise. Using the following notation:

$$\theta = \left[ w_0 v_0, ..., w_0 v_{N-1}, ..., w_{M-1} v_0, ..., w_{M-1} v_{N-1} \right]^T$$

(2.7)

$$\phi_p = \left[ tx1^*(p)tx2^2(p), ..., tx1^*(p - (M-1))tx2^2(p - (N-1)) \right]. \tag{2.8}$$

Equation (2.6) can be written as

$$cm3(p) = \phi_p \theta + n(p). \tag{2.9}$$

The latter form has the advantage that the problem is in linear regression form. Given a P-point data set and defining

$$CM3_P \triangleq [cm3(0), cm3(1), cm3(2), \dots, cm3(P-1)]^T$$

(2.10)

$$N_P \triangleq [n(0), n(1), \dots, n(P-1)]$$

(2.11)

$$\Phi_P \triangleq \left[\phi_0, \phi_1, \dots, \phi_{P-1}\right]^T, \tag{2.12}$$

the parameter estimation problem can be written as

$$CM3_P = \Phi_P \theta + N_P. \tag{2.13}$$

The best estimate of the parameters in least-mean-squares sense can be found with the pseudoinverse

$$\hat{\theta} = \left(\Phi_P^T \Phi_P\right)^{-1} \Phi_P C M 3_P. \tag{2.14}$$

The transformed problem with a "combined  $w \cdot v$  filter" instead of two separate filters requires the estimation of  $M \cdot N$  parameters instead of M + N parameters. This, in turn, implies a higher computational cost. However, in this particular application, the order of the filtrs M and N is low enough that the difference in computational effort is not prohibitively high given the capability and efficiency of the DSP in today's cell phones. An alternative to the block computation of the parameters using the pseudoinverse is the RLS algorithm. In each iteration, the RLS algorithm computes an updated estimate of the parameters  $\hat{\theta}$  based on the previous estimate and the current measured data. The RLS algorithm estimates the parameter in the  $\hat{\theta}$  ith iteration as

$$\hat{\theta}_i = \hat{\theta}_{i-1} + P_i \Phi_i \left[ cm3(i) - \Phi_i \hat{\theta}_{i-1} \right]$$

(2.15)

where  $P_i$  is

$$P_{i} = \lambda^{-1} \left[ P_{i-1} - \frac{\lambda^{-1} P_{i-1} \Phi_{i}^{*} \Phi_{i} P_{i-1}}{1 + \lambda^{-1} \Phi_{i} P_{i-1} \Phi_{i}^{*}} \right].$$

(2.16)

Since the RLS algorithm continuously adapts the parameters  $\hat{\theta}_i$ , the algorithm can quickly adapt to the changing external environment, such as the hand position of the user. This is crucial, since the hand position has a significant impact on the coupling between the two transmitters, which, in turn, affects the distortion.

#### 2.3.3 Multiple Nonlinear Components

As mentioned above, there can be multiple sources of nonlinearity such as the duplexer and the switch. Referring to Fig. 2.1, it is important to realize that distortion from the switch is created from TX1" and TX2'. The distortion caused by the duplexer is created from TX1" and TX2, where the apostrophes denote small differences between the signals caused by the switch and the duplexer transfer functions and group delays. In particular, this means that an estimate for each distortion signal should have slightly different values for J and K. Depending on the sampling rate of the system and the components, the differences in J and K might be in the subsample range. An alternate interpretation of this is that TX2 and TX1 experience an echo and multiple copies of the signals create multiple cm3s in a single component. FIR filters are frequently used to model multipath and echo effects. Therefore, the structure of the MISO filter inherently is capable of compensating for distortion created by multiple components.

#### 2.3.4 Cancellation in the Presence of Desired RX Signal

So far, the discussion has focused only on the distortion cancellation. However, the main objective is to achieve good reconstruction of the desired signal received from the base station. The input to the adaptive filter contains the distortion and the desired received signal. The latter behaves like noise to the parameter estimation algorithm. In extreme cases, when the desired received signal is significantly stronger than the distortion, it degrades the cancellation performance of the distortion canceller. The output power of the adaptive filter is

$$e^2 = EMSE + \sigma_{RX2}^2 + \sigma_n^2 (2.17)$$

where  $\sigma_{RX2}^2$  and  $\sigma_n^2$  are the powers in the received signal and the thermal noise floor. EMSE is the power of the residual distortion after cancellation. After the RLS algorithm converges, this can be expressed as

$$EMSE_{RLS} \approx \frac{\left(\sigma_{RX2}^2 + \sigma_n^2\right)\left(1 - \lambda\right)L}{2} \tag{2.18}$$

where L is the number of parameters to be estimated and  $\lambda$  is the forgetting factor [18]. From (2.18), one can determine the amount of distortion cancellation as

$$Cancellation_{CM3} \approx \frac{(\sigma_{RX2}^2 + \sigma_n^2)}{\sigma_{CM3}^2} \cdot \frac{(1 - \lambda) L}{2}.$$

(2.19)

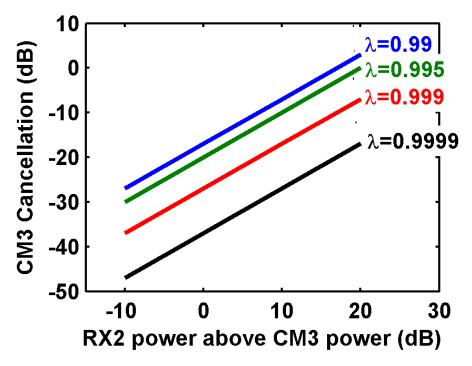

Fig. 2.10 shows the amount the cancellation for a given received signal power above or below the distortion for L equal to 4 and various values of  $\lambda$ . The graph illustrates that, for a strong received signal and  $\lambda$  equal to 0.99, the EMSE is as strong or stronger than the CM3 itself. This means that the adaptive filter would actually degrade the SINR of the desired received signal. To achieve good cancellation for strong received signals, one needs to increase  $\lambda$  to 0.9999. Unfortunately, this also increases the convergence time of the algorithm. However, in those cases, the SINR of the desired received signal is high enough that longer convergence time is acceptable. This will be discussed in more detail in Section 2.6.

## 2.3.5 Cancellation in the Presence of Adjacent Channel Jammers

In addition to the desired received signal, one also has to consider adjacent channel jammers. These can be significantly stronger than the desired received signal and would disturb the cancellation algorithm similar to the RX signal shown

Figure 2.10: Amount of cancellation given  $\lambda$  for various received signal powers.

in Fig. 2.10. However, in the case of adjacent channel jammers, we can benefit from the suppression of the jammer by the digital channel filter at the input of the receiver. This also requires a modification to the cancellation algorithms to include the impact of the channel select filter. In the case of the SISO filter, this is straightforward and illustrated in Fig. 2.8. It is sufficient to insert the channel select filter at the receiver input and after cm3'(n) is generated.

In the MISO distortion canceller, it is slightly more complicated. The adaptive distortion cancellation portion, including channel select filters for the MISO distortion canceller, is shown in Fig. 2.11. The measured received signal z(n) is processed by a channel select filter to suppress the jammer. It also suppresses parts of the cm3(n) signal that lie outside of the band of interest. In the MISO case, each of the vectors of the form  $tx1(p)*tx2^2(q)$  still contains the information outside of the band of interest that are not present at the filter input d(n). These

Figure 2.11: Adaptive MISO filter with digital channel select filter for adjacent channel jammer suppression.

out-of-band components need to be filtered out so as to not interfere with the parameter estimation process. This is similar to the approach presented in [19].

#### 2.4 Simulation Results

In this section, MATLAB simulations are used to prove the robustness of the proposed algorithms under different conditions. The section focuses particularly on aspects relating to the time alignment. The cancellation performances in the presence of received signals and out-of-band jammers are discussed in detail in Section 2.5 using measured data sets and are not included here for brevity.