## UC Berkeley UC Berkeley Electronic Theses and Dissertations

## Title

Tuning Hardware and Software for Multiprocessors

## Permalink

https://escholarship.org/uc/item/1dg4w04b

## Author Mohiyuddin, Marghoob

## Publication Date 2012

Peer reviewed|Thesis/dissertation

Tuning Hardware and Software for Multiprocessors

by

Marghoob Mohiyuddin

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

$\mathrm{in}$

Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor John Wawrzynek, Chair Professor James Demmel Professor Ming Gu

Spring 2012

Tuning Hardware and Software for Multiprocessors

Copyright 2012 by Marghoob Mohiyuddin

#### Abstract

#### Tuning Hardware and Software for Multiprocessors

by

#### Marghoob Mohiyuddin

#### Doctor of Philosophy in Electrical Engineering and Computer Sciences

#### University of California, Berkeley

#### Professor John Wawrzynek, Chair

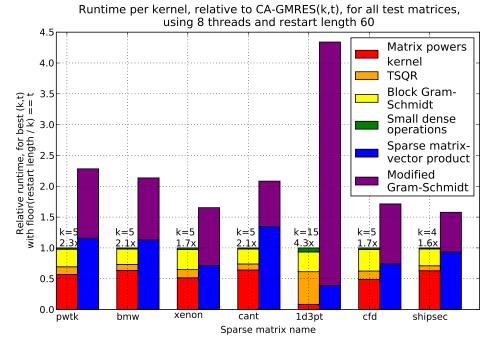

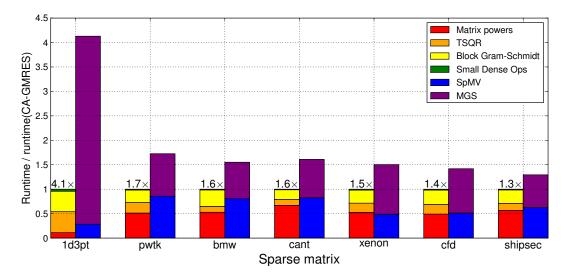

Technology scaling trends have enabled the exponential growth of computing power. However, the performance of communication subsystems scales less aggressively. This means that an application constrained by memory/interconnect performance will not be able to use the available computing power efficiently—in fact, technology scaling will make this efficiency even worse. This problem can be alleviated if algorithms minimize communication. To this end, we describe communication-avoiding algorithms and highly optimized implementations of a sparse linear algebra kernel called "matrix powers". Results show up to  $2.3 \times$  improvement in performance over the naïve algorithms on modern architectures. Our multi-core implementation of matrix powers enables us to develop a communication-avoiding iterative solver for sparse linear systems which is up to  $2.1 \times$  faster than a conventional Generalized Minimal Residual method (GMRES) implementation.

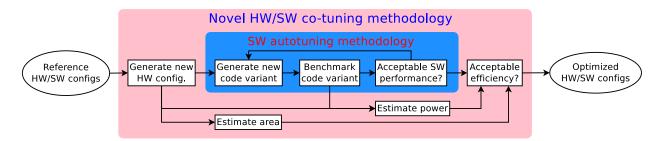

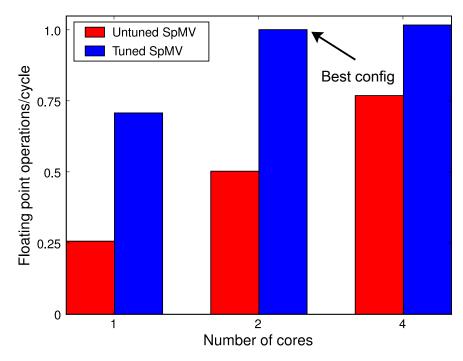

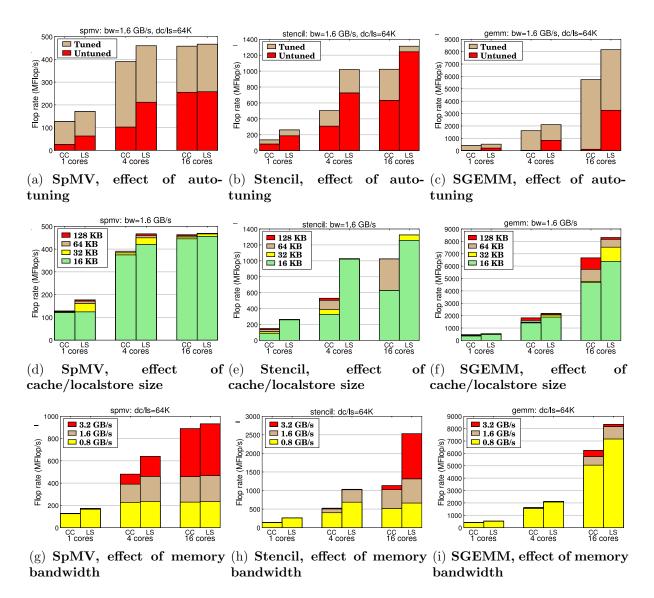

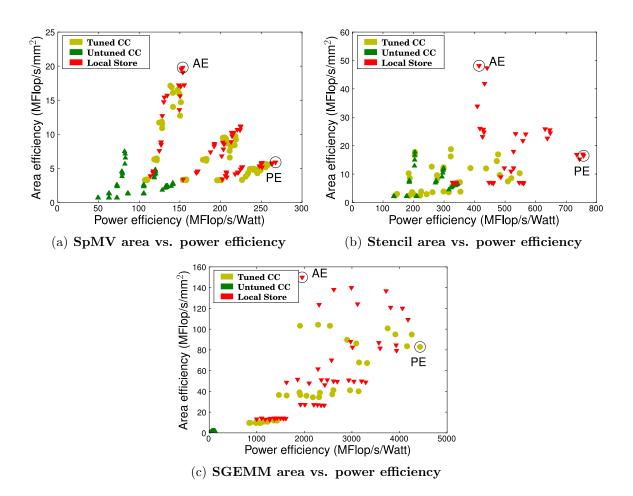

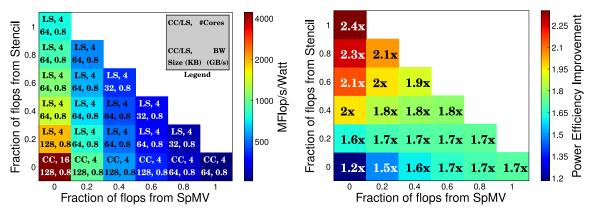

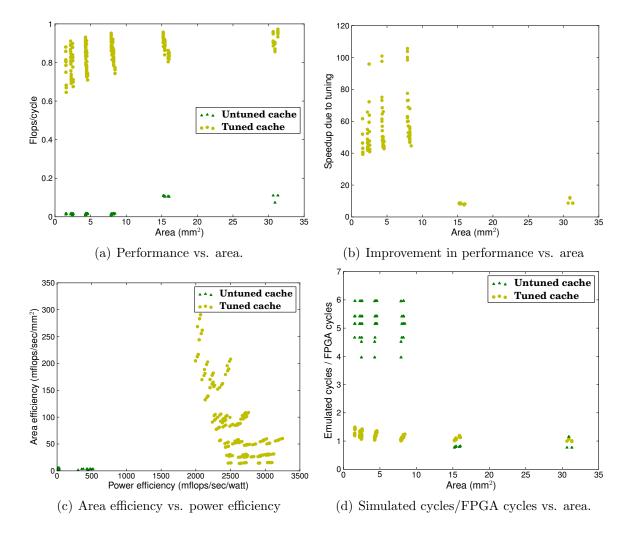

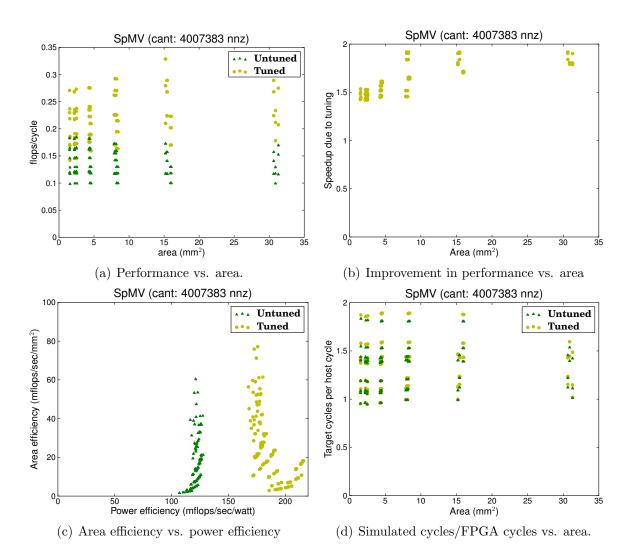

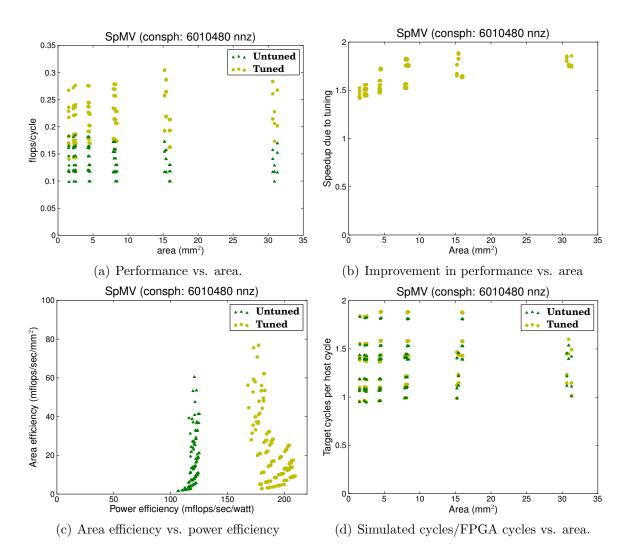

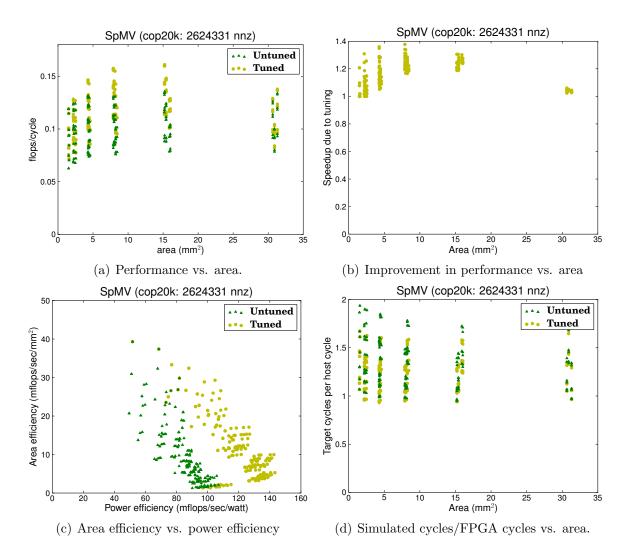

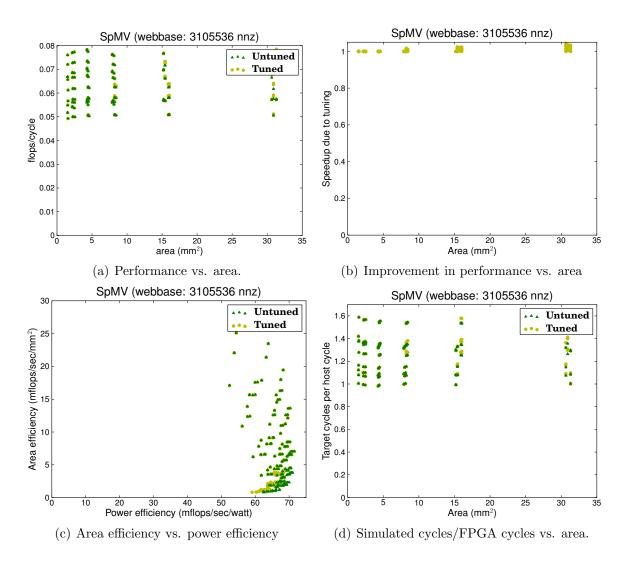

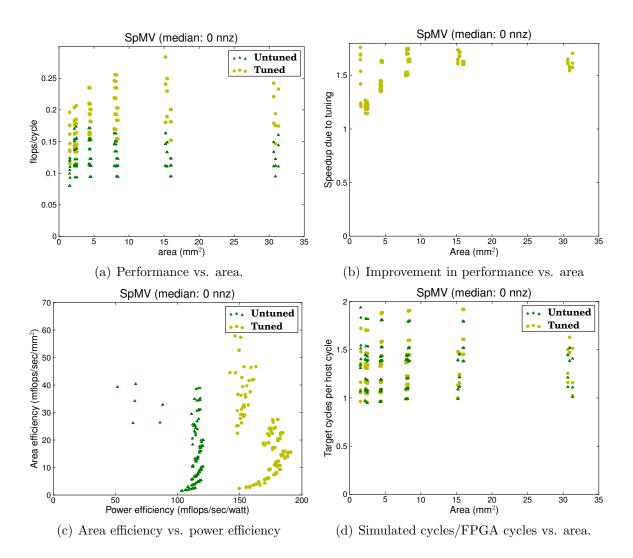

Another problem plaguing the supercomputer industry is the power bottleneck—power has, in fact, become the pre-eminent design constraint for future high-performance computing systems which is why computational efficiency is being emphasized over simply peak performance. Static benchmark codes have traditionally been used to find architectures optimal with respect to specific metrics. Unfortunately, because compilers generate suboptimal code, benchmark performance can be a poor indicator of the performance potential of architecture design points. Therefore, we present hardware/software co-tuning as a novel approach for system design. In co-tuning, traditional architecture space exploration is tightly coupled with software auto-tuning for delivering substantial improvements in area and power efficiency. We demonstrate co-tuning by exploring the parameter space of a Tensilica's Xtensa-based multi-processor running three of the most heavily used kernels in scientific computing, each with widely varying micro-architectural requirements: sparse matrix vector multiplication, stencil-based computations, and general matrix-matrix multiplication. Results demonstrate that co-tuning improves hardware area and power efficiency by up to  $3 \times$  and  $2.4 \times$  respectively.

O Lord, let me emulate the example of the moth! O Lord, let me dote and dart on the candle flame of knowledge! (excerpt from Allama Iqbal's "A Child's Prayer")

To Ammi, Abba, Nana and Shareen

## Contents

| 1        | Intr | ntroduction 1                                            |   |  |  |  |  |  |

|----------|------|----------------------------------------------------------|---|--|--|--|--|--|

|          | 1.1  | Related Work                                             | 2 |  |  |  |  |  |

|          |      | 1.1.1 Communication-Avoiding Algorithms                  | 2 |  |  |  |  |  |

|          |      | 1.1.2 Software Auto-Tuning                               | 3 |  |  |  |  |  |

|          |      | 1.1.3 Hardware Design Space Exploration                  | 6 |  |  |  |  |  |

|          | 1.2  | Contributions of This Work                               | 8 |  |  |  |  |  |

| <b>2</b> | The  | Matrix Powers Kernel 10                                  | ) |  |  |  |  |  |

|          | 2.1  | Background                                               | 0 |  |  |  |  |  |

|          | 2.2  | Related Work                                             | 2 |  |  |  |  |  |

|          | 2.3  | Model Problems                                           | 4 |  |  |  |  |  |

|          | 2.4  | Distributed Memory Parallel Algorithms for Matrix Powers | 7 |  |  |  |  |  |

|          |      | 2.4.1 1D meshes                                          | 3 |  |  |  |  |  |

|          |      | 2.4.2 2D and 3D meshes                                   | 2 |  |  |  |  |  |

|          |      | 2.4.3 Summary of Parallel Complexity on Meshes           | õ |  |  |  |  |  |

|          |      | 2.4.4 General Graphs                                     | 9 |  |  |  |  |  |

|          | 2.5  | Sequential Algorithms 34                                 | 4 |  |  |  |  |  |

|          |      | 2.5.1 1D Meshes                                          | õ |  |  |  |  |  |

|          |      | 2.5.2 2D and 3D Meshes                                   | 3 |  |  |  |  |  |

|          |      | 2.5.3 Summary of Sequential Complexity on Meshes         | 9 |  |  |  |  |  |

|          |      | 2.5.4 General Graphs                                     | C |  |  |  |  |  |

|          |      | 2.5.5 The Ordering Problem in Sequential Algorithms      | 1 |  |  |  |  |  |

|          | 2.6  | Asymptotic Performance Models                            | 7 |  |  |  |  |  |

|          |      | 2.6.1 Parallel Algorithms                                | 7 |  |  |  |  |  |

|          |      | 2.6.2 Sequential Algorithms                              | 9 |  |  |  |  |  |

|          | 2.7  | Detailed Performance Modeling                            | 1 |  |  |  |  |  |

|          |      | 2.7.1 Performance Modeling of PA2                        | 4 |  |  |  |  |  |

|          |      | 2.7.2 Performance Modeling of SA2                        | 7 |  |  |  |  |  |

|          | 2.8  | Implementation of PA1, P2 and Out-Of-Core SA2            | 5 |  |  |  |  |  |

|          | 2.9  | Shared Memory Algorithms for Multi-Cores                 | 7 |  |  |  |  |  |

|          |      | 2.9.1 Parallel Algorithm                                 | 3 |  |  |  |  |  |

|          |      | 2.9.2 Sequential Algorithms                              | 9 |  |  |  |  |  |

|          | 2.10 | Multi-Core Implementation                                | ) |  |  |  |  |  |

|    |        | 2.10.1 Optimizations                                   | 91  |

|----|--------|--------------------------------------------------------|-----|

|    |        | 2.10.2 Auto-tuning Matrix Powers                       | 93  |

|    | 0.14   | 2.10.3 Results                                         | 94  |

|    | 2.11   | 0                                                      | 104 |

|    |        | 0                                                      | 104 |

|    |        |                                                        | 106 |

|    |        | 2.11.3 Performance Results                             |     |

|    | 2.12   | Summary                                                | 108 |

| 3  |        | 8                                                      | 11  |

|    | 3.1    |                                                        | 111 |

|    |        | 3.1.1 Motivating Examples                              | 113 |

|    | 3.2    | Experimental Setup                                     | 116 |

|    |        | 3.2.1 Software Setup                                   | 116 |

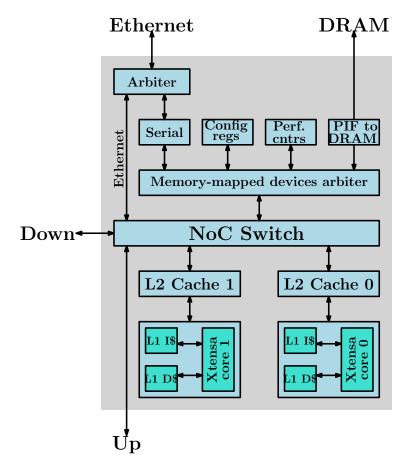

|    |        | 3.2.2 Hardware Setup                                   | 121 |

|    | 3.3    | Modeling Performance and Energy                        | 124 |

|    |        | 3.3.1 Modeling Chip Power                              | 124 |

|    |        | 3.3.2 Modeling Chip Area                               | 124 |

|    |        | 3.3.3 Modeling DRAM                                    |     |

|    | 3.4    | Evaluation Metrics                                     | 125 |

|    | 3.5    | Software-Based Simulation Results                      | 127 |

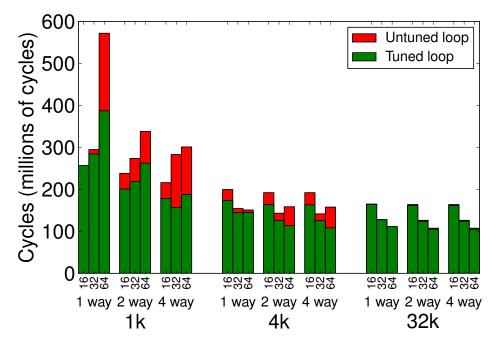

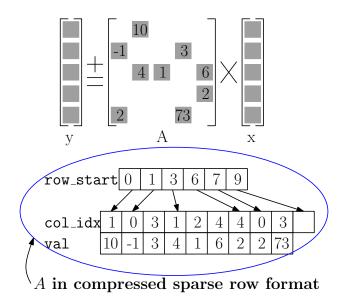

|    |        | 3.5.1 Performance of Design Parameters                 | 127 |

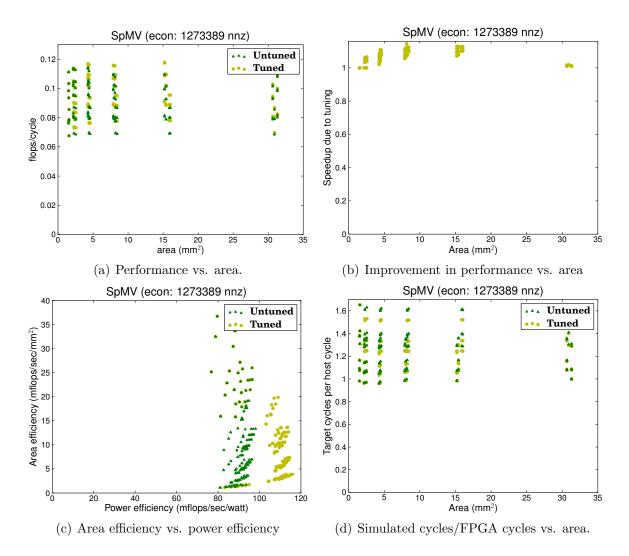

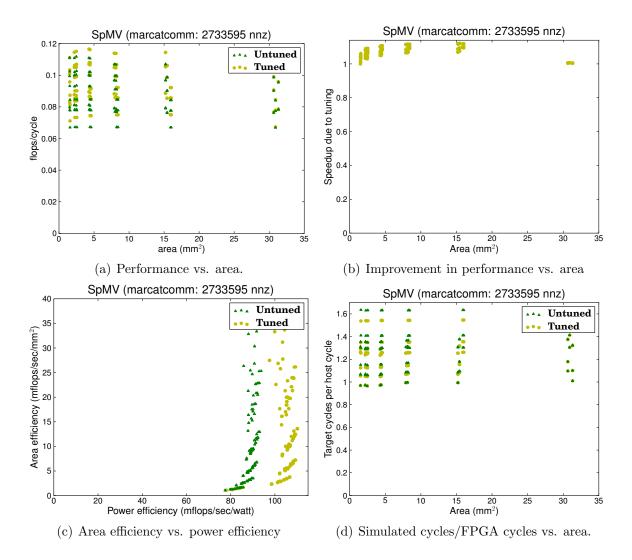

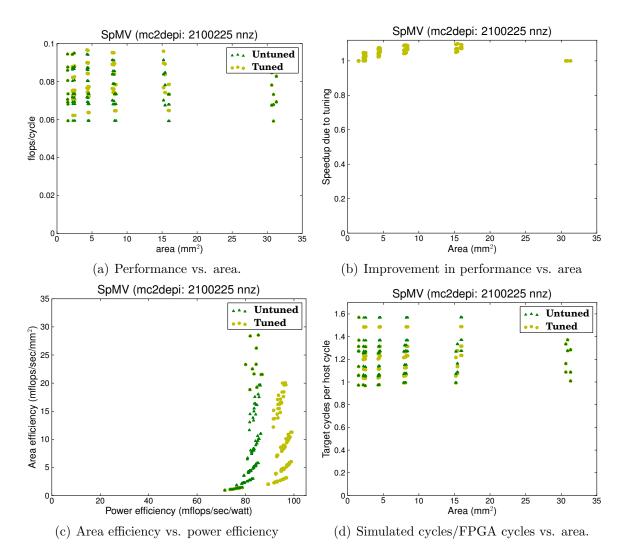

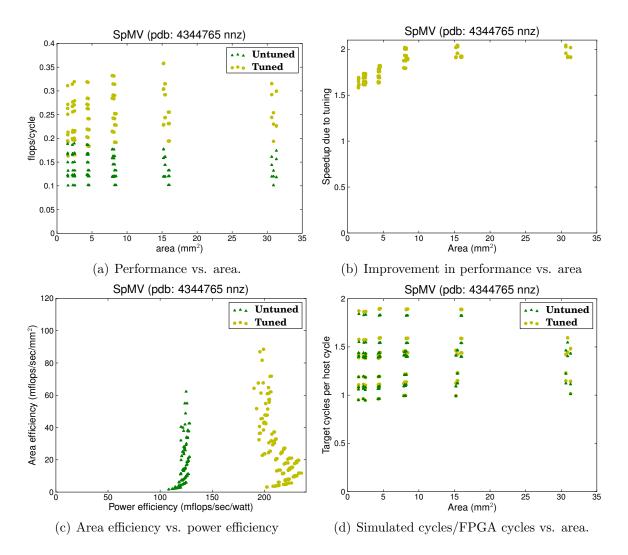

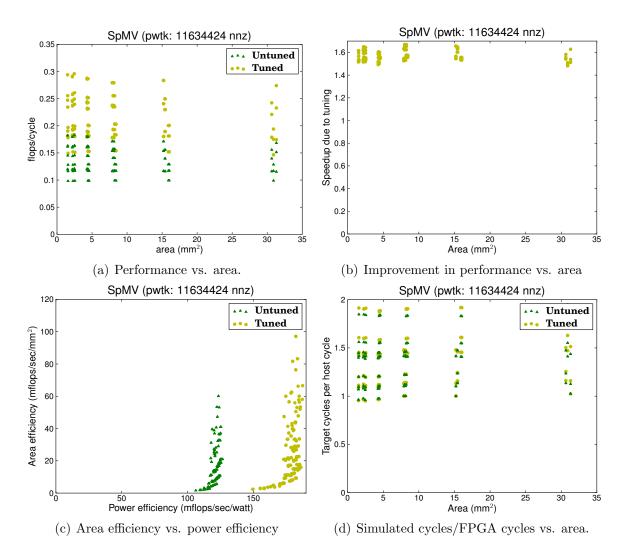

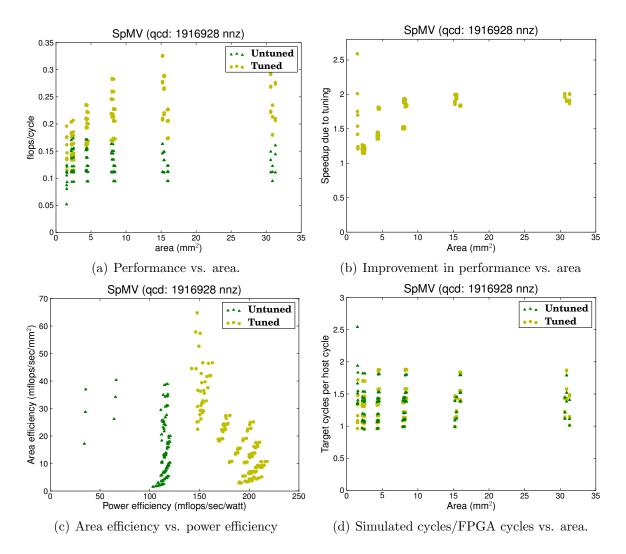

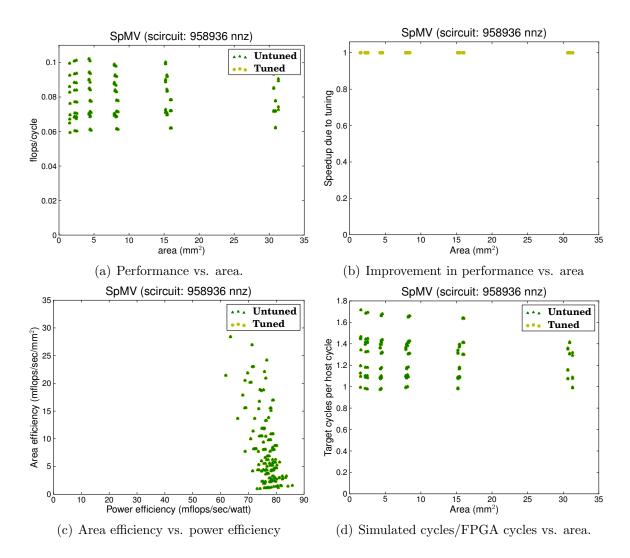

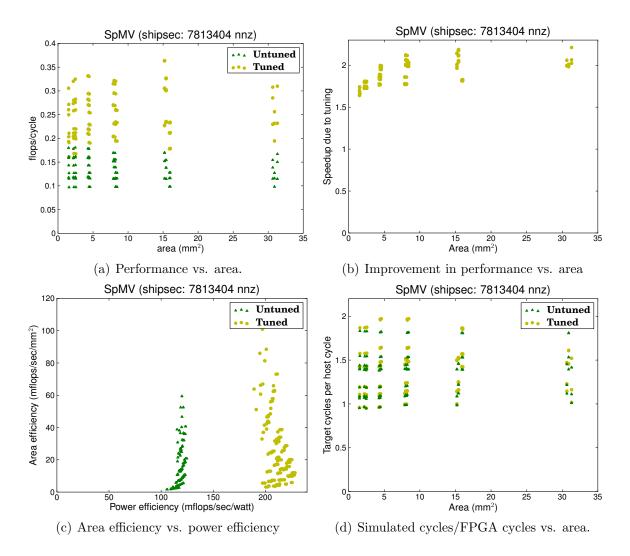

|    |        | 3.5.2 Tuning for Power and Area Efficiency             | 130 |

|    |        | 3.5.3 Co-Tuning for Multi-Kernel Applications          |     |

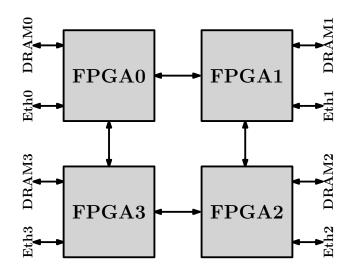

|    | 3.6    | FPGA-Based Simulation                                  |     |

|    |        | 3.6.1 Approaches for Emulation                         |     |

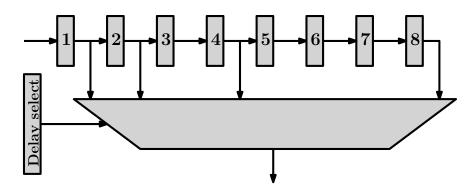

|    |        | 3.6.2 Emulation Details                                |     |

|    |        | 3.6.3 Physical Implementation on a Single FPGA         |     |

|    |        | 3.6.4 Performance Counters and Configuration Registers | 140 |

|    |        | 3.6.5 Software Infrastructure                          |     |

|    | 3.7    | FPGA-based Simulation Results                          |     |

|    |        | 3.7.1 Single Core Emulation                            | 142 |

|    | 3.8    | Summary                                                |     |

| 4  | Con    | clusions and Future Work 1                             | 60  |

| -  | 4.1    |                                                        | 160 |

|    | 4.2    |                                                        | 162 |

|    |        |                                                        | 162 |

|    |        | 4.2.2 Co-Tuning                                        |     |

|    |        |                                                        |     |

| Bi | ibliog | raphy 1                                                | 165 |

#### Acknowledgments

It feels great to acknowledge the contributions of the people who made this thesis possible. First of all, I thank my advisor Professor John Wawrzynek for giving me enough freedom and flexibility in research. He was always very patient and understanding, especially during some tough times in research, and, for this, I am extremely grateful to him. I also thank Professor Jim Demmel and Professor Kathy Yelick for giving me the opportunity to work in the Berkeley Benchmarking and Optimization ("BeBOP") research group—I owe my continued interest in high-performance computing to this great experience. My Ph.D. research has been an amalgamation of ideas from Professor Wawrzynek and Professor Demmel, and I am extremely thankful to them for helping me out with finding an interesting thesis topic. I thank Professor Ming Gu for being on my thesis committee and providing me useful feedback.

I thank Professor Adnan Aziz, who was my M.S. advisor at the University of Texas at Austin, for motivating me to pursue a Ph.D. degree. He has been a great mentor and friend to me and his continued advice and support to this day is always appreciated.

During the course of my graduate studies, I had the opportunity of being a part of multiple research groups—the BeBOP, Reconfigurable, and ParLab research groups on campus. It has been a terrific experience working and interacting with so many talented graduate students and researchers. Among them, I would first like to thank Mark Hoemmen for not just being a great collaborator but a great friend too—working with him is always a pleasure. Special thanks to Dave Donofrio and Greg Gibeling for helping me with the hardware infrastructure—their contributions to GateLib and help with debugging hardware modules were very crucial. Many other students deserve thanks, in particular Grey Ballard, Erin Carson, Jike Chong, Kaushik Datta, Shauki Elassaad, Andrew Gearhart, Ankit Jain, Shoaib Kamil, Alex Krasnov, Nick Knight, Adam Megacz, Mark Murphy, Rajesh Nishtala, and Sam Williams.

I would like to acknowledge the researchers at the Future Technologies Group at Lawrence Berkeley National Laboratory (LBNL) and the National Energy Research Scientific Computing Center (NERSC), especially John Shalf, Leonid Oliker, Michael Wehner, Norman Miller, and Leroy Drummond. It was a great experience working as a Graduate Student Researcher (GSR) at LBNL and I really enjoyed being involved in the "Green Flash" project.

I acknowledge the use of computing facilities at UC Berkeley (the Millennium cluster) and the NERSC center. This research used resources of NERSC center, which is supported by the Office of Science of the U.S. Department of Energy under Contract No. DE-AC02-05CH11231.

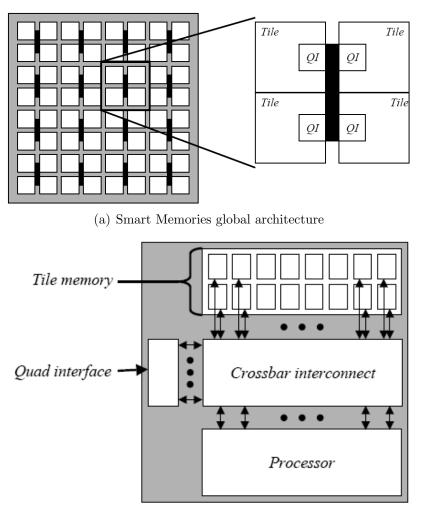

I thank the Stanford Smart Memories research group, led by Professor Mark Horowitz, for letting us use their Smart Memories simulator. Special thanks to Amin Firoozshahian and Alex Solomatnikov for helping us with setting up and running the simulator.

Many thanks to the UC Berkeley staff, especially Ruth Gjerde, Tamille Johnson, La Shana Polaris, Laura Rebusi, and Shirley Salanio, for helping me with the paperwork and meeting the administrative deadlines.

My graduate student life has been a fun and memorable one due to lots of wonderful people: Saurabh Amin, Richa Sharma, Huma Zaidi, Anurag Gupta, Vishnu Narayanan, Kranthi Kiran Mandadapu, Deepthi Aluru, Ambuj Tewari, Anuj Tewari, Aditya Medury, Debanjan Mukherjee, and Sharanya Prasad. I especially thank Saurabh and Richa for being there for me at all times, and Huma for the occasional push and stern advice when necessary. I tremendously enjoyed discussions on anything with Anurag and the visits to the Recreational Sports Facility with Vishnu. These people added the much needed spice to the academically charged environment at Berkeley.

Last of all, but certainly one of the most important, I express my gratitude to my parents, grandfather, and sister, for their love, support, patience and understanding over all these years. I feel truly blessed to have such a wonderful family—I dedicate my thesis to them.

## Chapter 1 Introduction

Although clock scaling stopped almost a decade ago, the semiconductor industry still follows Moore's law by the doubling the computational power per chip every technology generation. However, raw computational power doesn't necessarily translate to actual performance—the software needs to be designed in a way to make an efficient use of the underlying computational power. With a variety of machine configurations available in the market, the software needs to be customized (aka "tuned") for each target to get good performance. Traditionally, manual software-tuning along with using appropriate compiler flags, has been done to optimize the code for a target hardware setup. Due to the generalpurpose nature of commonly available compilers (gcc, icc, llvm), naïve code can perform rather poorly even when using aggressive compiler flags. This makes software tuning a necessity for high-performance codes. However, manual tuning is prohibitively expensive due to the overwhelming number of target machines available today as well as possible in the future. Software auto-tuning is an approach to mitigate the problem of achieving portable performance. It relies on trying out different algorithms, code variants, data structures and empirically measuring the performance on the target machine—in the end, the best performing algorithm, code variant, data structure is chosen. Such an approach has yielded success stories in dense linear algebra (ATLAS [112]), sparse linear algebra (OSKI [106]), and signal processing (SPIRAL [82], FFTW [39]). More recent work has also focused on developing auto-tuning frameworks in order to ease the development of auto-tuned codes. In keeping with this, the unifying theme of this work is "tuning", i.e., adapting the software to the target hardware and, going one step further, we propose "hardware/software co-tuning" as an approach to adapt the software and the hardware to each other for even more efficient hardware/software solutions.

Another problem we note with the scaling trends is that different technology components scale differently—computational power scales more aggressively when compared to memory/network subsystem latency and bandwidth. We refer to the latter as the communication subsystem. Current technology trends show exponentially increasing gaps between computation, bandwidth and latency costs. A study [92] of high performance computing showed floating point speeds increasing historically at 59%/year, but interprocessor bandwidth improving only 26%/year, and interprocessor latency improving only 15%/year. Indeed, on certain very large, distributed computing platforms (like the Grid) latencies are already speed-of-light limited and on the order of milliseconds, as opposed to fractions of nanoseconds for floating point operations. Similarly, memory (DRAM) bandwidth is improving only at 23%/year, and memory latency at 5.5%/year. For out-of-core algorithms, with disk bandwidth and latency limited by the rotational speed of disks, the gaps are even larger. Another study [78] observed that latency improves much more slowly than bandwidth across many technologies. These trends suggest that algorithms should be designed not to minimize arithmetic operations, as is traditional, but to minimize communication both within a local memory hierarchy and between processors. In this work, we consider the computations that arise in the communication-intensive Krylov subspace methods (KSMs) used to solve large sparse linear systems or large sparse eigenvalue problems. On current machines, KSMs are limited by memory and network performance, because they execute only a small constant number of arithmetic operations per communicated data value. We replace conventional KSMs with "communication avoiding" versions that send fewer messages and read data less frequently from slow memory at the cost of slightly more arithmetic.

## 1.1 Related Work

## 1.1.1 Communication-Avoiding Algorithms

There are two costs to implementing algorithms: "computation" and "communication". "Computation" is the useful work done and it involves processing of data. "Communication" is the movement of data across the system—this data movement can be between different levels of the memory hierarchy, between different processors in a parallel machine and between processors and coprocessors. Furthermore, the communication between different processors can be through the memory subsystem, an on-chip interconnect network or an inter-node interconnect. The cost of communication manifests as a hit on performance as well as energy consumption. Thus, it is desirable to minimize the cost of communication for an application. In fact, given the current technology scaling trends and the lag between communication and computation costs for units of data, it may even make sense to perform more computation if it cuts down the communication significantly. Thus, applications must be communication-avoiding, especially if communication can be a significant part of performance.

At a high-level, communication-avoidance has been a key component of software-tuning. A very good example of communication-avoidance strategies in software design is cache blocking optimization commonly seen in key scientific computing kernels [112, 106, 43, 96]. Cache blocking optimizations try to reuse data in the cache as much as possible which amounts to avoiding data movement across the memory subsystem as much as possible. Another low-level optimization which can be considered communication-avoiding is register tiling, which is performed in both dense and sparse linear algebra codes. In the case of dense linear algebra, register tiling improves register reuse while keeping the same computational complexity. As for sparse codes, register tiling may result in more computation being performed but cut down the memory footprint (and, hence, communication cost) to result in an overall improvement in performance. Although, "cache blocking" and "register tiling" are optimizations commonly used in different computational kernels, they mean different low-level optimizations depending on the kernel.

There has been theoretical work in bounding the cost of communication [47] and developing communication-efficient algorithms [9]. The authors in [47] were able to bound the communication cost of a cache-blocked dense matrix-matrix multiplication as a function of the cache size. It was shown that the multiplication of two dense  $n \times n$  matrices using the conventional  $\Theta(n^3)$  algorithm on a machine with a fast memory of size M, requires  $\Omega(n^3/\sqrt{M})$  words of data movement between fast and slow memories. This lower bound is tight as "blocked" algorithms were shown which attain the aforementioned lower bound. Irony et al. [51] extended the communication bounds to parallel machines and showed that the lower bound can be expressed as  $\Omega\left(\frac{\#\text{arithmetic operations}}{\sqrt{M}}\right)$ , where M is the size of fast memory for the sequential machine model and size of the local memory for the parallel machine model. Ballard et al. [9] extended the communication lower bound results to all direct methods of linear algebra—examples include LU factorization, Cholesky factorization, QR factorization, etc. It is also interesting to note that some of the these bounds for dense and sparse linear algebra operations easily translate to related graph algorithms, e.g., all-pairs shortest paths. In addition, Ballard et al. [9] list algorithms which attain the lower bounds.

### 1.1.2 Software Auto-Tuning

Software tuning is usually required for high-performance codes because general-purpose compilers are usually unable to generate good machine code due to their general nature. Traditionally, careful hand-tuning of software [54] and hand-coded assembly have been used to get high-performance for critical sections of high-performance applications. Hand-tuning software is not only time consuming but also does not scale well as applications need to be deployed on new machines. Furthermore, with the complex interplay between software and the underlying hardware, it is often difficult to predict performance on a target machine given a particular piece of code. Auto-tuning has emerged as an approach to mitigate this problem of tuning software. The idea is fairly simple: write code which automatically adapts to the target hardware. This necessitates that tuning "knobs" be built into the code—the values of these "knobs" which result in high performance, are determined empirically by actually trying out different values and choosing the best performing one. In a way, autotuning of software aims to achieve portable performance using minimal writing of code. An auto-tuned software performs part of the tuning at install-time (done once per target machine) and the rest at run-time (which depends on the inputs to the software). A typical auto-tuner achieves its goal of performance portability by employing the following:

• Parameterized code generators: Given that there may be several ways of writing the code for the same computations and different code variants may perform well on different target machines, code generators are used to generate the different possibilities. At install-time, these code generators are used to generate different code variants and the

performance of these code variants is empirically measured to determine the best one. A very prominent example of such a code generator is from ATLAS [112], which is an auto-tuned library for dense linear algebra. ATLAS's code generator generates different variants for the dense matrix-matrix computational kernel. The code generator is heavily parameterized—examples of some parameters include the matrix dimensions, loop unroll factor, number of matrix entries to keep in registers, and matrix data layout (row major or column major format).

- Parameterized routines: While code generators account for different ways of writing code, parameterized routines are used to account for making run-time decisions for performance. These run-time decisions may include the choice of data structures, algorithms, core computational codes, etc. As with code generators, the right parameters are determined empirically by trying out different parameter values at run-time or at install-time. One good example of such a run-time parameter is the data structure used to represent a sparse matrix in memory—this is a key decision to be make in case of a sparse linear algebra library like OSKI [106]. A sparse matrix can be represented in many ways and the optimal representation (with respect to performance) depends on the sparsity pattern of the matrix which is only known at runtime.

- Search heuristic: An auto-tuned software may have several tuning knobs built into it and an exhaustive exploration of the parameter space can be impractical and more so if the exploration has to be performed at run-time. This necessitates the integration of an efficient search strategy in the auto-tuner. The search heuristic must be able to find parameter values yielding good performance in as little time as possible.

There are several success stories involving high-performance libraries which make use of auto-tuning and, in fact, address a variety of computations:

- Dense linear algebra: One of the early success stories for auto-tuned software has been ATLAS [112], which can be seen as a successor to PHiPAC [11, 12]. ATLAS aims to provide a set of high-performance routines for dense linear algebra. At the heart of ATLAS is a high-performance routine for multiplying two dense matrices (General Matrix Multiply or GEMM). ATLAS uses an auto-tuner to figure out a good performing implementation of GEMM on a target machine. It is interesting that while the simplest implementation of GEMM (which is basically three nested loops in C) performs very poorly due to low data reuse, auto-tuned implementations can achieve close to machine peak performance. Almost all the tuning in for GEMM is done at install-time as the performance only depends on the matrix dimensions.

- Sparse linear algebra: The OSKI library [106] attempts the same by targeting sparse linear algebra. One of the key computational kernels in OSKI is Sparse Matrix Vector Multiplication (SpMV) which is really hard to optimize as the performance is determined heavily by the sparsity pattern of the matrix [30]. OSKI performs part of the tuning at install-time and the remaining is done at run-time when the matrix structure is known.

- Discrete Fourier Transforms: FFTW [39] is one of the most popular libraries for computing the DFT (Discrete Fourier Transform). Given the dimensions of the DFT, FFTW explores possible ways of computing the DFT—this includes the different ways the FFT recursion can be done. Since the DFT dimensions are known at run-time, the first call to the DFT computation can be expensive as auto-tuning is performed to try out different alternatives and measure their performance. Since an exhaustive exploration of the search space can be expensive, FFTW includes a fast mode where a reasonably performing DFT solution is computed quickly. Note that FFTW performs all of its tuning at run-time.

- Signal processing: SPIRAL [82] is one example of a library targeting signal processing applications. Given a digital signal processing (DSP) computation expressed as a formula, SPIRAL uses auto-tuning to generate target-optimized code implementing the DSP computation. These formulas are expressed in a special "tensor-product" language and all the tuning is done at compile-time. Like FFTW, SPIRAL can also be used to compute the DFT but unlike FFTW, it can handle a wider range of DSP computations.

In addition to the above mentioned libraries, significant efforts have been made in advancing the state of the art for auto-tuning for individual kernels. Independently of OSKI, auto-tuned SpMV implementations have been developed targeting multi-cores [113, 114, 16] and, more recently, GPUs [20]. In a similar vein, Volkov et al. [103] implemented several key linear algebra kernels on GPUs and use auto-tuning and overlapping CPU and GPU computations to achieve near peak performance. The PLASMA (Parallel Linear Algebra for Scalable Multi-core Architectures) and MAGMA (Matrix Algebra on GPU and Multics Architecture) projects [1] are recent collaborative efforts to develop auto-tuned frameworks for dense linear algebra on multi-cores as well as hybrid systems involving both multi-cores as well as GPUs. Datta et al. [25] performed an extensive study comparing auto-tuned implementations of the 7-point stencil from the heat equation on structured meshes, on several platforms ranging from multi-cores, IBM Cell to GPUs. Kamil et al. [55] generalize the stencil optimization work to develop a framework for generating auto-tuned implementations of arbitrary stencils specified in a high-level language—this approach is similar to the SPIRAL framework. Performance comparison against the naïve implementations on several platforms showed up to  $22 \times$  speedups.

There has also been work towards developing general frameworks for auto-tuning:

- The POET (Parameterized Optimizations for Empirical Tuning) language [121] was developed to specify code and the allowed transformations. This lets developers write domain-specific source code generators which simplifies auto-tuner design. The output source code generated by the POET compiler can be fed to a low level compiler as part of the auto-tuning process.

- The ROSE compiler project [88] allows one to be able to build custom source-to-source generators—this is achieved by ROSE allowing the user to manipulate the abstract syntax tree (AST) of the source code and then using the AST to generate ("unparse")

the source code. This can be used to target whole applications instead of limiting to specific kernels. As a proof of concept, ROSE was used as part of PERI [67] to identify performance bottlenecks and auto-tune the SMG2000 [15] (Semicoarsening Multigrid Solver) benchmark from DOE which contains about 28k lines of code—the application was sped up by  $1.8 \times$  after a bottleneck stencil kernel was auto-tuned.

- CHiLL [19] (Composing High-Level Loops) is a compiler framework for describing and loop transformations. Polyhedral representations of nested loops are used along with scripts describing the set of allowed transformations in order to generate the loop code variants to test for performance tuning. Example loop transformations include loop unrolling, loop nest permutation, tiling, loop splitting, and copy of data to temporary locations. As a demonstration, CHiLL scripts were used to auto-tune different dense linear algebra kernels, e.g., matrix matrix multiplication, LU factorization, and triangular solve. Performance improvements close to hand-tuned code were reported.

- PERI (Performance Engineering Research Institute) [7] is a major collaborative effort to automate the process of tuning whole applications (in contrast to just tuning specific kernels and providing them as libraries). In a way, PERI integrates code profilers, source code generators, source-to-source translators, and search heuristics to formalize and implement a methodology for systematic tuning of whole applications.

- The SEJITS (Selective Embedded Just-In-Time Specialization) [17] project is an attempt to bridge the gap between writing productive code in high level languages like Python and Ruby and the performance of auto-tuned codes written in low level languages like C. One of the key ideas in SEJITS is providing *specializers* which describe source code transformations from a high level language to a low level language. The specializers, if provided, accelerate the critical portions of the high level code by generating and executing auto-tuned low level implementations.

As we can see, although auto-tuning is still an emerging field, significant progress has been made from the initial work involving custom auto-tuners for specific computational kernels, to more recent work involving developing frameworks which enable development of auto-tuners in a more systematic way. Since our goal was simply to demonstrate the effectiveness of our communication-avoiding algorithms, for the purpose of this work, we use an almost exhaustive search in our auto-tuned implementation of matrix powers.

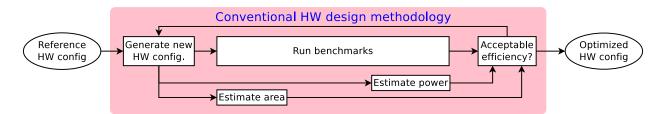

## 1.1.3 Hardware Design Space Exploration

Hardware design space exploration (DSE) is typically performed to determine the optimal hardware parameters for a given set of benchmark applications [23, 6, 117]. In fact, most of the work in computer architecture evaluates hardware design points using benchmark codes [75, 66, 64, 76]. Figure 1.1 shows a high-level view of such DSE studies—different hardware configurations are evaluated using a set of benchmark applications. The DSE may be constrained (by chip area, cost, power, energy) in order to study the trade-offs involved and answer questions like:

- Should more chip area be devoted to caches?

- Should more money be spent on memory bandwidth?

- Should low voltage be used to trade off speed for power?

Kumar et al. [60] showed that cores, caches and interconnect need to be *co-designed* in order to get good performance or energy efficiency. This is due to the non-negligible cost of the interconnect in terms of area, performance and energy. Interestingly, due to the high cost of the interconnect for sharing caches, the authors found that the theoretical performance benefits go away when constraints of area and power are applied. Thus, it is better to simulate the system as a whole rather than independent components.

Li et al. [66] performed a DSE study under thermal (temperature) and physical (pin bandwidth, chip area, power) constraints. To cut down the simulation time, the authors decoupled core simulation from interconnect and memory subsystem simulation. Single core simulations were used to generate traces which were used for the interconnect and memory simulations. Thus, multi-core simulation results were actually an extrapolation of results from single core simulations and interconnect and memory subsystem simulations. As expected, CPU-bound workloads favored a higher core count while memory-bound workloads favored larger cache area on chip. Interestingly, thermal constraints dominated physical constraints and simpler core designs were found to be favorable for more power-efficient solutions.

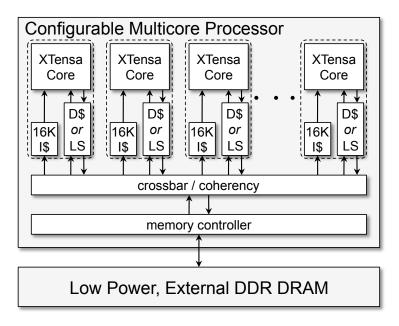

Leverich et al. [64] performed a DSE study to compare cache-based multiprocessors with local store-based ones with respect to energy consumption and performance. The multiprocessor was designed using Tensilica's embedded processor XTensa [98] with VLIW features. Multiple parameters like core counts, bandwidth, and frequency were varied. It was found that with features like hardware prefetching and non-allocating stores enabled, cachebased configurations performed close to local store-based configurations. Given that local store-based configurations require extra programming effort, cache-based configurations had an overall advantage. The authors hand-tuned some of the benchmarks and found significant improvement in performance, thus demonstrating the effectiveness of software tuning.

Musoll et al. [76] used DSE to compare multi-threaded with out-of-order single-threaded superscalar architectures. Hardware multi-threading was shown to be effective at reducing power consumption as well as area when compared to a superscalar for the same performance.

Seo et al. [89] proposed a new software-managed cache design called the extended setindex cache (ESC). The cache design attempts to have the tag search performance of a setassociative cache and the miss rate of a fully-associative cache. Interestingly, the hardware adapts the cache parameters depending on the code being run—this can depend on which part of which application is being run. It was found that the hardware adaptation at runtime improved performance significantly for the benchmark applications as there was no one size fits all solution for the cache parameters.

In a study closest to co-tuning, Shrivastava et al. [90] perform DSE for horizontally partitioned cache architectures. The compiler used the hardware configuration information to

Figure 1.1: Traditional hardware design space exploration

generate code tuned to minimize energy consumption. The authors found that incorporating the compiler to generate target specific code gave much better results when compared to the traditional approach of using fixed codes for all hardware design points.

One major issue with DSE studies is the size of the design space [27, 49, 36, 3, 62, 52]. especially since software simulation of hardware is traditionally used to perform such studies. To cut down the simulation time, various techniques have been tried to make the DSE tractable, ranging from relying on "industry experience, intuition and literature surveys" [27] to statistical sampling for creating trained models using artificial neural networks [49], or cubic splines [62]. Random sampling of the design space is used to train the statistical models. Dubach et al. [36] use linear regression to predict the performance of a new application using the trained model and performance on a few sampled design points. More recently, Azizi et al. [3] use posynomial<sup>1</sup> functions for the trained models. Given these statistical techniques, only a small part of the design space need to be actually simulated for training the statistical model. Once the training is done, the model can be used to predict the performance over the design space. Since our work explored limited design spaces, we employed an exhaustive search rather than the sophisticated statistical modeling techniques currently used in exploring large design spaces. We note that hardware design spaces can be explored more quickly using FPGA<sup>2</sup>-acceleration [97, 22]-the acceleration can easily be two orders of magnitude. This speeding up of hardware simulation also enables exploration of the larger design space which can also include the software design space. Using hardware to accelerate also has ramifications with respect to the power consumption-with the speedups involved, a single FPGA board can easily replace a cluster of machines and yet achieve the same simulation throughput for a much lower power consumption. Chapter 3 covers FPGA-acceleration of hardware simulation in more detail.

## 1.2 Contributions of This Work

In light of the key issues discussed previously, two major contributions are made in this thesis:

• We describe communication-minimizing algorithms, models and implementation of

<sup>&</sup>lt;sup>1</sup>A posynomial is a function of the form  $f(x_1, x_2, \ldots, x_n) = \sum_{k=1}^{K} c_k x_1^{a_{1,k}} \cdots x_n^{a_{n,k}}$  where the coordinates  $x_i$  and coefficients  $c_k$  are positive real numbers, and the exponents  $a_{i,k}$  are real numbers.

<sup>&</sup>lt;sup>2</sup>An FPGA (Field Programmable Gate Array) is a configurable hardware and can be used to quickly implement a digital circuit

"matrix powers"—a linear algebra kernel. Furthermore, in keeping with the overarching theme of tuning, our implementation of the "matrix powers" kernel is auto-tuned. We also demonstrate the effectiveness of the matrix powers implementation in an iterative solver for large sparse systems—results (see Section 2.11) show that performance improves by up to 2.2 over the naïve implementation. Parts of this work have appeared in [31, 32, 73].

• We describe "hardware/software co-tuning" (henceforth, referred to as simply cotuning) as a methodology for hardware design and demonstrate its effectiveness on a set of well-known kernels from scientific computing and a hardware architecture results (see Sections 3.5 and 3.7). Parts of this work have appeared in [74, 111]— Sections 3.6-3.7, however, are new.

The rest of the thesis describes the aforementioned contributions (see Section 1.2) in detail. Chapter 2 covers the matrix powers kernel in detail. Chapter 3 discusses co-tuning. Finally, Chapter 4 covers conclusions and future work.

# Chapter 2 The Matrix Powers Kernel

## 2.1 Background

Krylov subspace methods (KSMs) are iterative methods for computing solutions of sparse linear systems (solving for x in Ax = b) and eigenvalue problems (solving for x in  $Ax = \lambda x$ ), particularly when the problems are large. Formally, the Krylov subspace for a matrix A and a vector v is the following subspace:

$$\mathcal{K}_k(A, v) = \operatorname{span}\{v, Av, \dots, A^k v\}, \qquad k \in \mathbb{N}.$$

A KSM minimizes the residual ||Ay - b|| by computing better approximations to the solution every iteration. At every iteration, the KSM expands the set of basis vectors for the Krylov subspace—the basis is used to approximate the solution or the eigenvalues and eigenvectors. Conventional algorithms for KSMs spend most of the time in communication-limited kernels like sparse matrix-vector multiply (SpMV), vector dot products and sums. Given the data dependencies in each iteration, only limited performance gains can be made by overlapping communication with computation. Given that KSMs are an important component of scientific and engineering applications, making them communicate less can have significant impact in improving the performance of those applications.

Conventional implementations of KSMs involve the following computational kernels:

- SpMVs (sparse matrix-vector products): given a sparse matrix A, a vector x, compute  $A \cdot x$  or  $A^T \cdot x$ .

- AXPYs (vector-vector sums): given vectors x and y, scalar  $\alpha$ , compute  $\alpha \cdot x + y$ .

- Dot products: given vectors x and y, compute  $y^* \cdot x^1$

A typical implementation would alternate SpMV with AXPYs and dot products. Note that all the above mentioned kernels are communication-limited as they perform very few computations per data word read from memory. Therefore, both the computation and communication cost of k iterations grows at least proportionally to k.

<sup>&</sup>lt;sup>1</sup>For a vector v of complex values,  $y^*$  denotes the conjugate transpose of v.

The Generalized Minimal Residual method (GMRES) of Saad and Schultz [86] is a Krylov subspace method for solving a non-symmetric square system of linear equations Ax = b. The standard implementation of GMRES alternates between using a sparse matrix-vector product to generate a new Krylov basis vector, and using BLAS 1<sup>2</sup> - based Modified Gram-Schmidt to orthogonalize that vector against all the previously generated and orthogonalized basis vectors. A number of authors proposed performing GMRES in a different way [108, 28, 53, 4, 38]. Begin with a starting vector  $v_1$ , and then generate k more vectors  $v_2, \ldots, v_{k+1}$  so that they form a basis of the Krylov subspace

$$\operatorname{span}\{v_1, v_2, \dots, v_{k+1}\} = \operatorname{span}\{v_1, Av_1, A^2v_1, \dots, A^jv_1\}$$

for  $j = 1, \dots, k$

Then, use a QR factorization<sup>3</sup> to orthogonalize the basis vectors. They become therefore identical to the basis vectors that standard GMRES would generate (modulo a unitary column scaling). Finally, use the R factor to reconstruct the k + 1 by k upper Hessenberg matrix<sup>4</sup> from standard GMRES, compute a new approximate solution, and restart if the desired accuracy is not yet reached. Other authors developed similar algorithms, generally called "s-step Krylov methods," for conjugate gradient iteration and other Krylov iterations for symmetric matrices [21, 100]. The above variants of GMRES all require restarting after each group of k steps.

In this work, we reorganize KSMs so that the communication cost is nearly as small as theoretically possible. Specifically, we implement a communication-avoiding version of GMRES called CA-GMRES (communication-avoiding GMRES) to demonstrate the effectiveness of our approach. To this end, communication-avoiding analogues of some computational kernels were introduced:

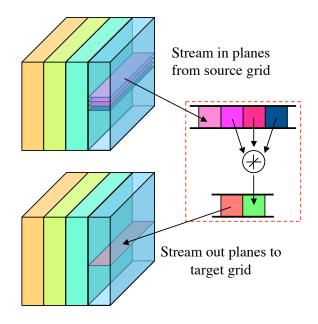

- Matrix powers: Given a matrix A in sparse format, a vector x, an integer k > 0, compute the k vectors  $[p_1(A)x, p_2(A)x, \ldots, p_k(A)x]$ , where  $p_i(A)$  is a polynomial of degree  $i, 1 \leq i \leq k$ . This kernel replaces the SpMV kernel and performs multiple iterations instead of one iteration at a time which is the case with SpMV.

- Tall Skinny QR (TSQR): Perform the QR factorization of an  $m \times n$  dense matrix A with  $m \gg n$ .

- *Block Gram-Schmidt* (BGS): Perform Modified Gram-Schmidt (MGS) orthogonalization but instead of processing a column at a time, process a block of columns at a time to improve performance. It is not really a new kernel but its use in combination with TSQR is the novel idea here.

In related work [46], we describe numerically stable reorganizations of typical KSMs, such as GMRES and CG, that leverage a matrix powers kernel (or small variations) to

<sup>&</sup>lt;sup>2</sup>The Basic Linear Algebra Subprograms (BLAS) [61], an interface for dense linear algebra computations, such as dot products (BLAS 1), vector sums (BLAS 1), matrix-vector multiply (BLAS 2), and matrix-matrix multiply (BLAS 3).

<sup>&</sup>lt;sup>3</sup>Given a matrix A, its QR factorization is matrices Q and R such that A = QR, Q is orthogonal and R is upper triangular.

<sup>&</sup>lt;sup>4</sup>An upper Hessenberg matrix has zero entries below the first sub-diagonal.

advance k steps in one iteration. That work also describes support for preconditioning, which is essential to KSMs in practice.

We focus here on the matrix powers kernel with nearly minimal communication time. On a parallel computer, this means with latency costs that are independent of k. In fact if the sparse matrix has a suitable (and common) sparsity structure described below, we will see that the latency cost of matrix powers is just O(1). On a sequential computer, this means that latency and bandwidth costs are independent of k. Said another way, both the matrix A and k output vectors will need to be moved between fast and slow memory just 1 + o(1) times (1 time is obviously the minimum), not k times. Since bandwidth is always the bottleneck in the sequential case, our approach is always an improvement. Our communication *avoiding* approach complements and is more powerful than communication *overlap* techniques, which can at best halve the running time. Avoiding communication can achieve up to k-fold speedups when communication is dominant, and can be combined with overlap for an additional performance boost.

Specifically, we consider two flavors of the matrix powers kernel:

- Given a matrix A, a vector x, a positive integer k, compute  $[x, Ax, A^2x, \ldots, A^kx]$ . This is a simplification of the general form. When the basis vectors of the Krylov subspace are computed in this way, we refer to it as the monomial basis. For the purpose of illustration and explanation, this flavor will be used throughout this chapter.

- Given a matrix A, a vector x, a positive integer k, compute  $[p_1(A)x, \ldots, p_k(A)x]$ , where  $p_i(A) = (A - \lambda_1 I) \cdots (A - \lambda_i I)$ . When this form is used, we refer to it as the Newton basis. Our multi-core implementation of CA-GMRES uses this form.

## 2.2 Related Work

The optimizations described in this work belong to a collection of techniques for improving the performance of applying a stencil repeatedly to a regular discrete domain, or multiplying a vector repeatedly by a sparse matrix. They, in turn, are a subset of various methods known as *tiling* or *blocking*. They all involve decompositions of the *d*-dimensional domain into *d*-dimensional sub-domains, and rearranging the order of arithmetic operations in order to exploit the parallelism and/or temporal locality implicit in those sub-domains.

Tiling research falls into three general categories. The first encompasses performanceoriented implementations and practical performance models. See, for example, [81, 79, 50, 115, 84, 71, 93, 116, 35, 95, 34, 119, 104, 57, 56]. The second category consists of theoretical algorithms and asymptotic performance analyses. These are based on sequential or parallel processing models which account for the memory hierarchy and/or inter-processor communication costs. Works that specifically discuss stencils or more general sparse matrices include [47], [63], and [100]. The third category contains suggested applications that call for repeated application of a stencil (resp. sparse matrix) to a domain (resp. vector). See, for example, [102, 85, 21, 28, 4, 95].

The idea of using redundant computation to avoid communication or slow memory accesses in stencil codes may be as old as out-of-core (OOC) stencil codes themselves. Leiserson

et al. cite a reference from 1963 [63, 81]. Nevertheless, many tilings do not involve redundant computation. For example, Douglas et al. describe a parallel tiling algorithm that works on the interiors of the tiles in parallel, and then finishes the boundaries sequentially [35]. Many sequential tilings do not require redundant computations [56]; our SA1 algorithm does not.

However, at least in the parallel case, tilings with redundant computation have the advantage of requiring only a single round of messages, if the stencil is applied several times. The latency penalty is thus independent of the number of applications, though the bandwidth requirements increase. Furthermore, Strout et al. point out that the sequential fill-in of boundary regions suggested by Douglas et al. suffers from poor locality [95]. Most importantly, redundant computation to save messages is becoming more and more acceptable, given the exponential divergence in performance between latency, bandwidth, and floatingpoint rate.

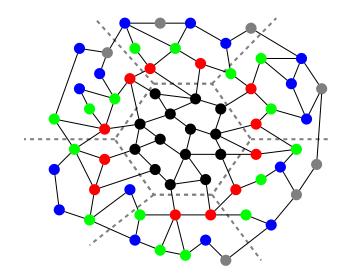

Extensions of stencil tiling to more general sparse matrices require runtime analysis of the sparse matrix structure, often using a graph partitioner. Finding an optimal partition is an NP-complete problem which must be approximated in practice, at nontrivial cost. Theoretical algorithms for the out-of-core sequential case already existed (see e.g., [63]), but Douglas et al. were apparently the first to attempt an implementation of parallel tiling of a general sparse matrix, in the context of repeated applications of a multigrid smoother [35]. This was extended by Strout et al. [94] into a sequential cache optimization which resembles our SA1 (discussed in Section 2.5) algorithm.

Our work differs from existing approaches in many ways. First, we developed our methods in tandem with an algorithmic justification: communication-avoiding or "s-step" Krylov subspace methods [46]. Toledo had suggested an s-step variant of conjugate gradient iteration, based on a generalization of algorithm PA1 (discussed in Section 2.4), but he did not supply an implementation for matrices more general than tridiagonal matrices [100]. We have a full implementation of PA1 for general sparse matrices, and have detailed theoretical models showing performance increases on a wide variety of platforms.

Douglas et al. and Strout developed their matrix powers kernel for classical iterations like Gauss-Seidel [35, 95]. However, these iterations' most common use in modern linear solvers are as multigrid smoothers. The payoff of applying a smoother k times in a row decreases rapidly with k; this is, in fact, why multigrid is used, rather than classical iterations such as Jacobi or Gauss-Seidel. Douglas et al. acknowledge that usually  $1 \le k \le 5$  [35]. In contrast, communication-avoiding Krylov subspace methods are potentially much more scalable in k. Saad also suggested applying something like a matrix powers kernel to polynomial preconditioning, but here again, increasing the degree of the polynomial preconditioner has a decreasing payoff, in terms of the number of CG iterations required for convergence [85].

We have also expanded the space of possible algorithms by including algorithms PA2 (see Section 2.4) and SA2 (see Section 2.5). PA2 avoids some redundant computation, but offers less opportunity for overlapping communication and computation. SA2 extends SA1 for the case in which the vectors (as well as the matrix) do not fit entirely in fast memory. As far as we can tell, PA2 and SA2 are novel. In addition, we compose the parallel algorithms with sequential algorithms to implement matrix powers on multi-cores (discussed in Section 2.9).

## 2.3 Model Problems

Our techniques work for general sparse matrices, but the case of regular d-dimensional meshes with  $(2b+1)^d$ -point stencils illustrates potential performance gains for a representative class of matrices. By a *regular mesh*, we mean a simply connected domain in  $\mathbb{R}^d$  (d = 1, 2, 3, ...) where the vertices are evenly spaced at the grid points. The connectivity pattern of a regular mesh is described by the *stencil*, which shows for each point in the mesh, how it is connected to its neighbors. For example, on a 2D mesh, a 5-point stencil means that each point is connected to its east, south, west, and north immediate neighbors. A 9-point stencil for a 2D mesh means that each point is connected to its 8 immediate neighbors, i.e., east, southeast, south, southwest, west, northwest, north, and northeast neighbors. In these cases, we say that the bandwidth b of the stencil is 1, since each point is only connected to its immediate neighbors. Generalizing this, we can have  $(2b + 1)^d$ -point stencils where each point is connected to neighbors within a radius of b points. Since a sparse matrix can be thought of as representing a directed graph, we use the terms sparse matrix and graphs interchangeably. When meshes are being discussed, we may also refer to them simply by their stencil pattern.

Here, we assume a symmetric pattern (but arbitrary non-symmetric matrix entries) and describe the pattern in terms of its undirected graph.

We consider the following model problems:

- 1. 1D mesh with n unknowns and (2b+1)-point stencil;<sup>5</sup>

- 2. 2D mesh with  $n^2$  unknowns and  $(2b+1)^2$ -point stencil, in nested dissection<sup>6</sup> ordering;

- 3. 3D mesh with  $n^3$  unknowns and  $(2b+1)^3$ -point stencil, in nested dissection ordering.

We call the *surface* of a mesh the number of points on the partition boundary. For an  $n \times n$  (2D) mesh partitioned in to p equal sized squares with a 5-point stencil, the surface is  $4\frac{n}{p^{1/2}}$ . For an  $n \times n \times n$  (3D) mesh partitioned in to p equal sized cubes with a 7-point stencil, the surface is  $6\frac{n^2}{p^{2/3}}$ . The *volume* of a mesh is the total number of points in each processor's partition, namely  $\frac{n^2}{p}$  and  $\frac{n^3}{p}$  in the 2D and 3D cases. The *surface-to-volume ratio* of a mesh is therefore  $4\frac{p^{1/2}}{n}$  in the 2D case and  $6\frac{p^{1/3}}{n}$  in the 3D case. We assume all the above roots (like  $p^{1/3}$ ) and fractions (like  $\frac{n}{p^{1/2}}$ ) are integers, for simplicity.

The surface-to-volume ratio of a partition of a general sparse matrix is defined analogously. All our algorithms work best when the surface-to-volume ratio is small, as is the case for meshes with large n and sufficiently smaller p.

In the parallel case, we use the usual mapping where row blocks j of A, x and y = Ax are all assigned to processor j. As stated above, the latency cost of our version of a KSM will be *independent* of k, requiring just 1 message between each processor and its "neighbors",

$<sup>^{5}</sup>$ We consider tridiagonal matrices in order to illustrate our techniques most clearly, not because they are computationally challenging for computing products.

<sup>&</sup>lt;sup>6</sup>Nested dissection is a heuristic for partitioning a sparse matrix [41, 69, 42]—the corresponding graph is partitioned recursively to minimize the number of vertices connecting different partitions.

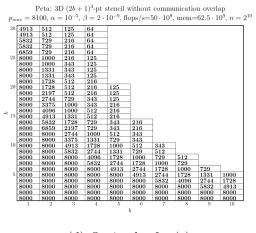

i.e., those processors owning components of x needed to compute the local components of y = Ax. The bandwidth and computation costs will be nearly minimal, increasing only by lower order terms (depending on the surface-to-volume ratio) compared to a conventional implementation. For example, suppose that the sparsity pattern of our matrix is that of a 27 point stencil operating on an  $n \times n \times n$  mesh, and that we assign  $\frac{n}{p^{1/3}} \times \frac{n}{p^{1/3}} \times \frac{n}{p^{1/3}}$  "cubes" of mesh points to each of p processors. Then using our approach drops the number of messages per processor from 26k to 26, while only increasing the number of words communicated per processor from  $\frac{6kn^2}{p^{2/3}}$  to  $\frac{6kn^2}{p^{2/3}} \cdot (1 + \frac{2kp^{1/3}}{n})$  and arithmetic operations per processor from  $\frac{53kn^3}{p} \cdot (1 + \frac{1.5kp^{1/3}}{n})$ . In both cases, the factor  $\frac{p^{1/3}}{n}$  is proportional to the surface-to-volume ratio, which will be small for problems of interest.

In the sequential case, our algorithm will mimic the parallel algorithm, processing the matrix block by block. As stated above, all the data (matrix and vectors) will only have to move from slow to fast memory 1 + o(1) times in order to implement k steps of a KSM, not move k times. In other words the number of slow memory accesses (the latency cost) and the bandwidth cost will exceed their minimal values by this 1 + o(1) factor. The o(1) term will be proportional to the surface-to-volume ratio.

We contrast our approach of *avoiding* communication with the complementary approach of *overlapping* communication and computation. The latter approach can at best halve the running time, whereas avoiding communication can potentially achieve up to k-fold speedups when communication is dominant. Furthermore, we can use overlapping to accelerate our algorithms as well.

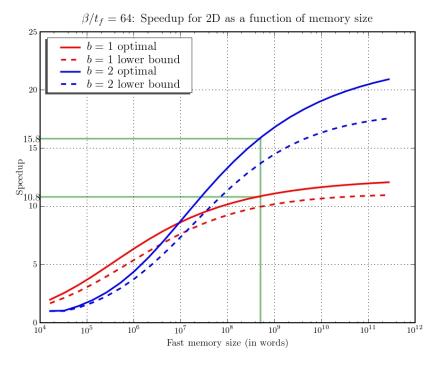

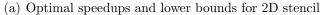

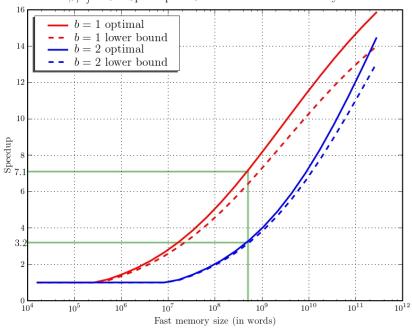

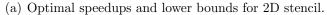

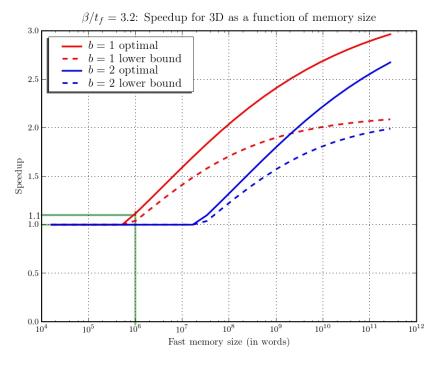

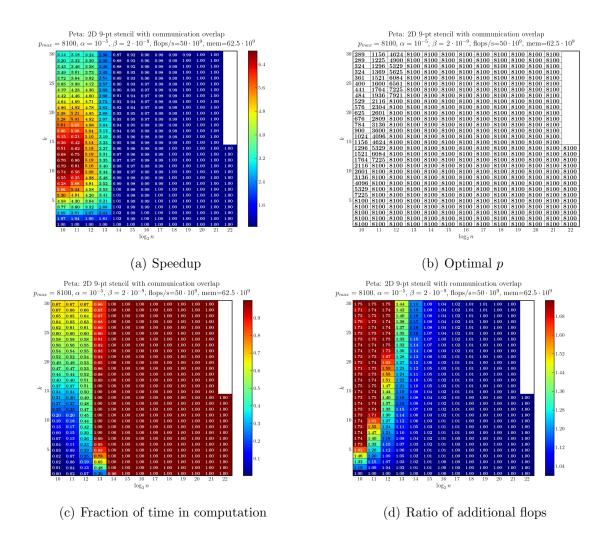

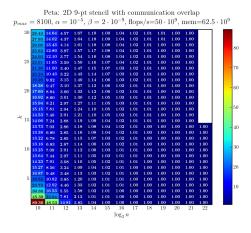

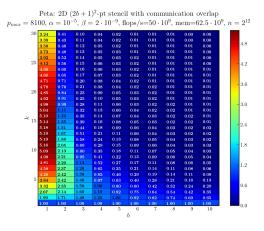

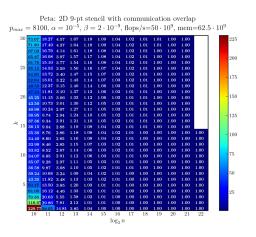

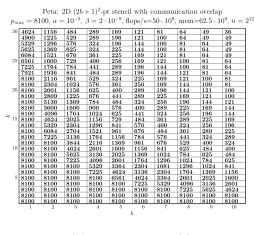

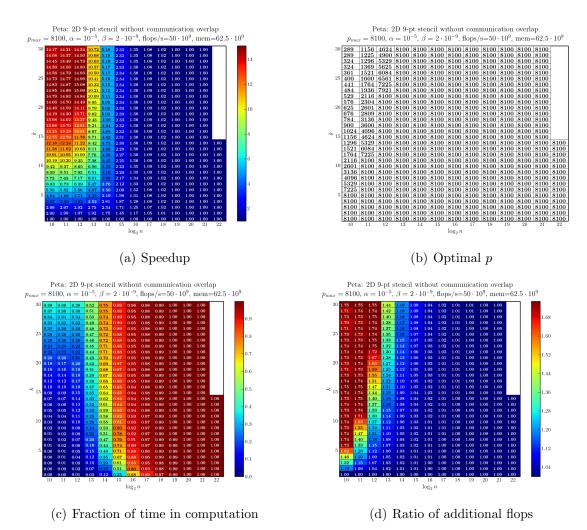

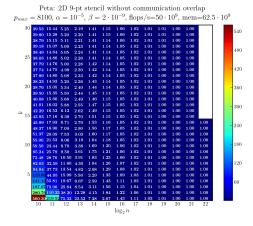

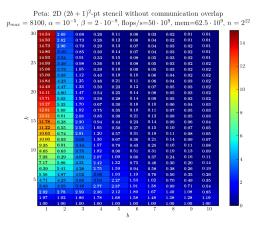

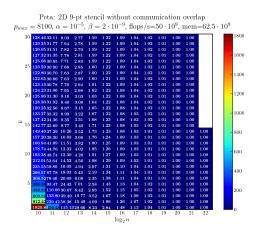

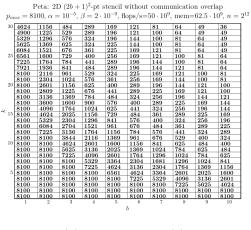

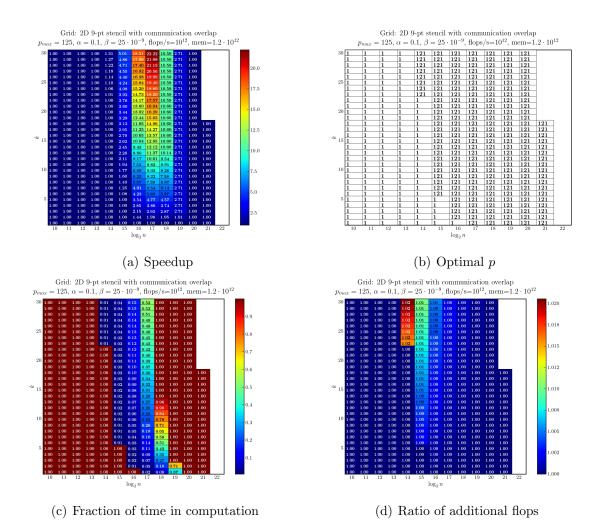

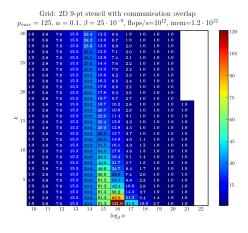

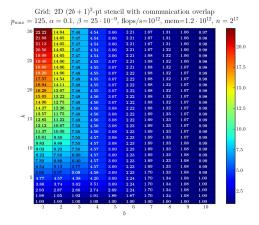

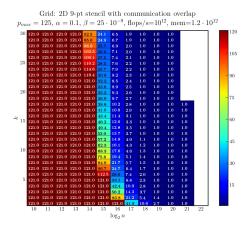

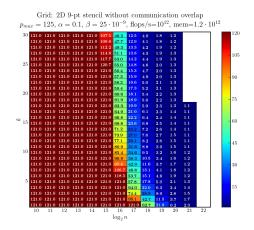

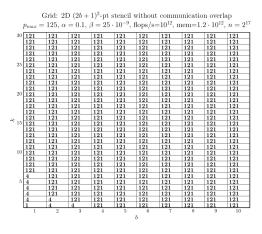

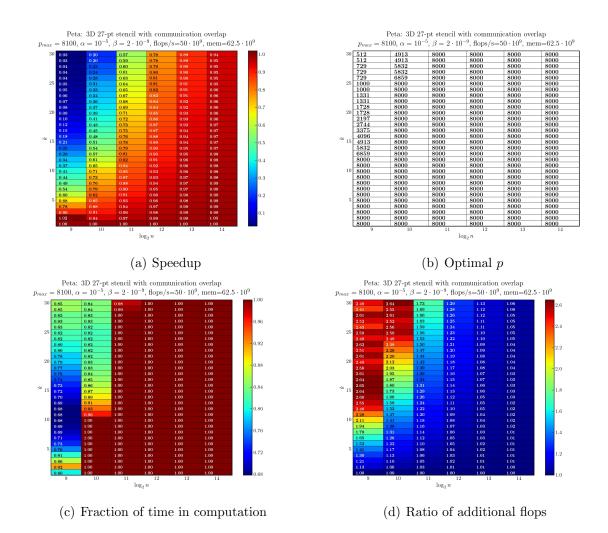

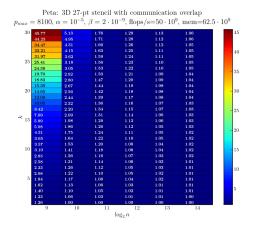

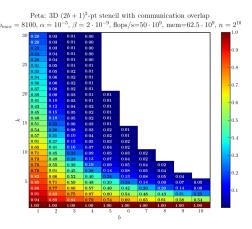

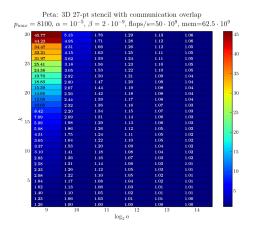

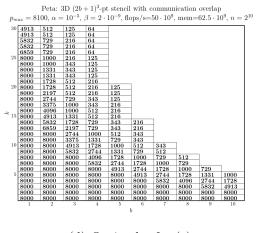

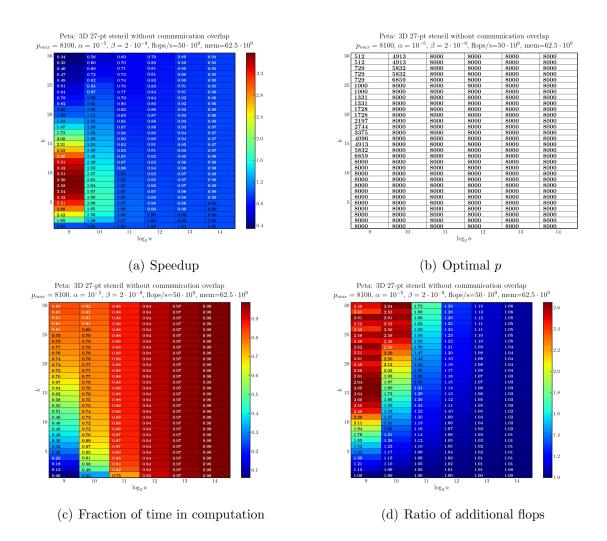

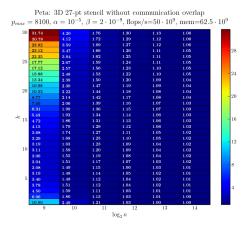

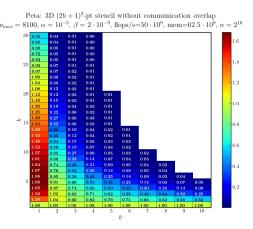

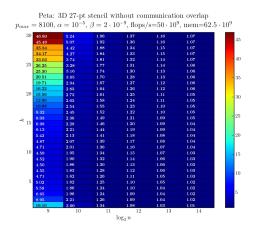

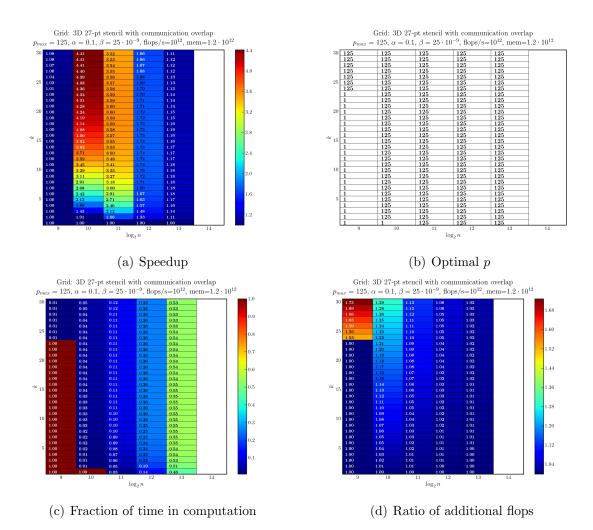

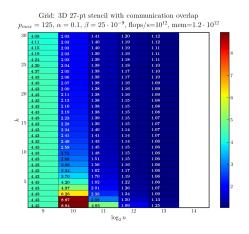

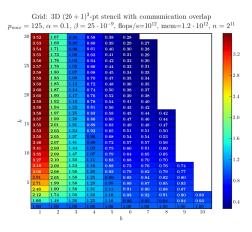

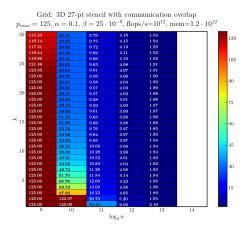

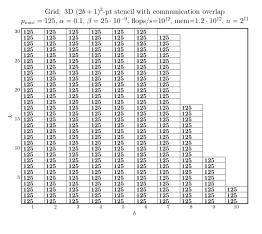

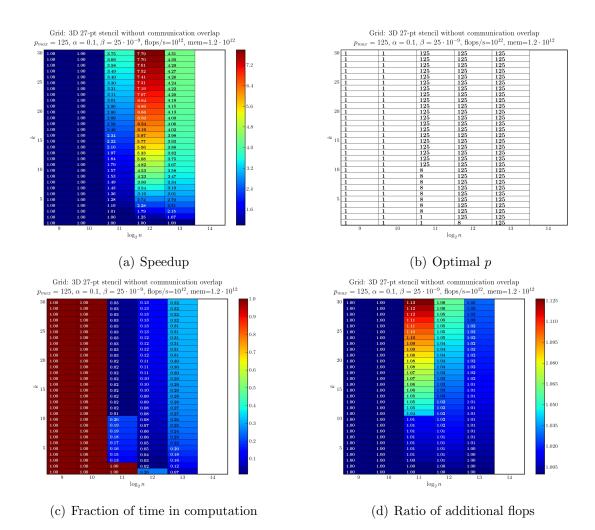

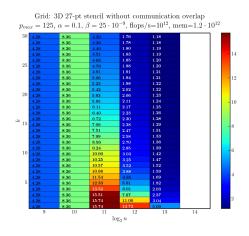

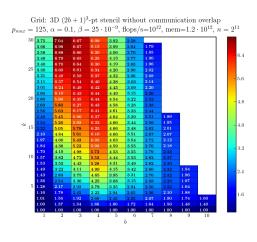

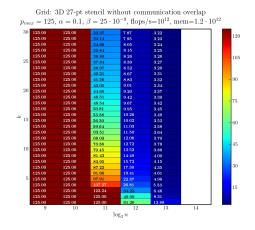

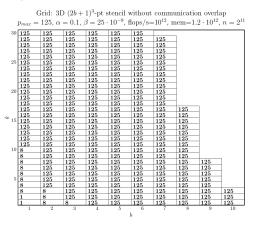

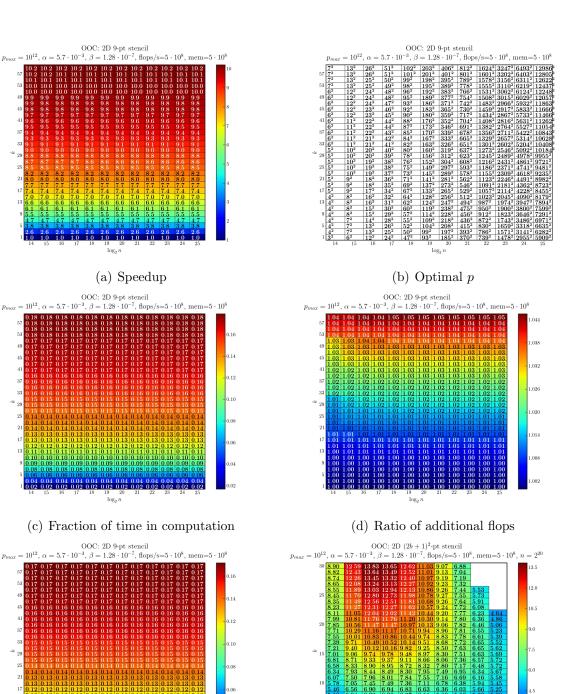

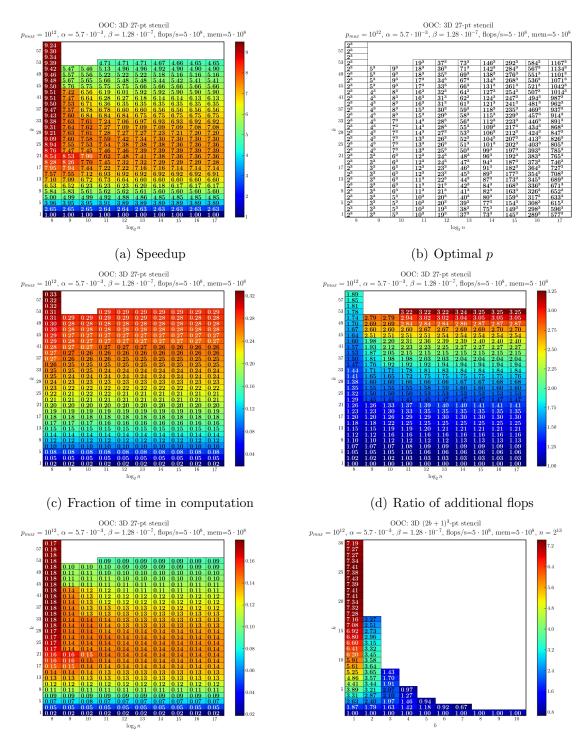

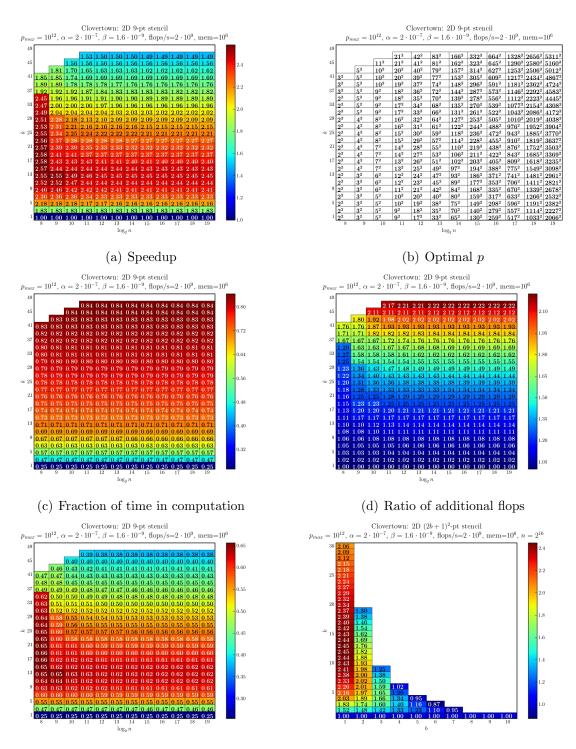

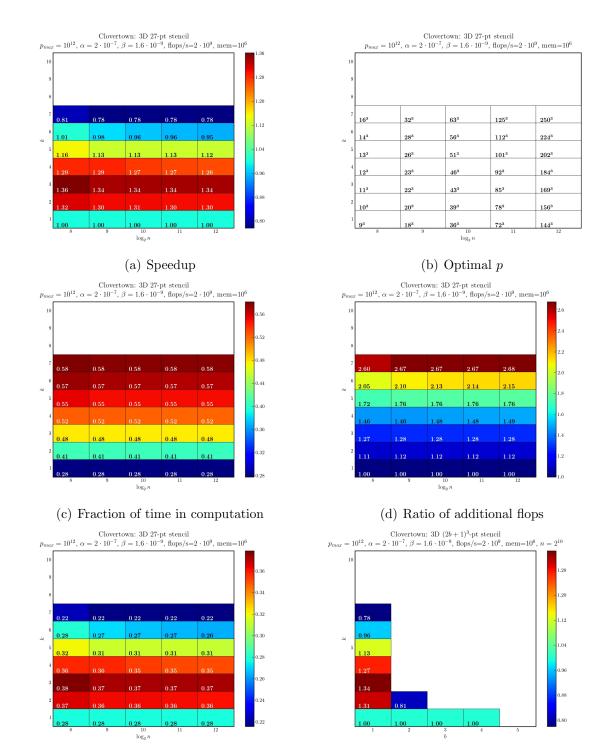

We present both detailed performance models and measurements from different implementations. We model matrices with the sparsity patterns of both a 2D and 3D stencil on a variety of parallel and sequential computers. The two parallel computers modeled are a Petaflop machine consisting of 8100 50 GFlop/s processors connected over a fast network, and a Grid consisting of 125 1 TFlop/s processors connected over the internet. The speedup over a conventional algorithm depends on whether it is a 2D or 3D problem, the width of the stencil (e.g., 5 point, 9 point etc.), the problem size, and how much computation and communication can be overlapped. Table 2.1 summarizes the maximum speedups modeled below for matrices whose graphs are 9 point 2D stencils and 27 point 3D stencils (but stored as general sparse matrices). For Peta, the best speedups were for smaller n in the range studied, because communication was more dominant; maximum speedups fell as n increased and the problem became computation bound. Also for Peta, non-overlapping computation made latency more important, and so our approach to avoiding latency yielded larger speedups. On the Grid, for the lower n in the range modeled, it was fastest to use just one processor because communication was so expensive. But as n grew, it eventually became effective to use parallelism, and close to this transition point our approach yielded large speedups.

The two "sequential" machines modeled are:

- 1. Uniprocessor with DRAM as fast memory and a single disk as slow memory (called OOC for Out-Of-Core).

- 2. A multi-core chip with on-chip cache as fast memory and DRAM as slow memory (called "CacheBlocked"). Although the machine is parallel, we only address how to

| Machine | Matrix               | Range of $n$         | Overlap | Max Modeled Speedup |

|---------|----------------------|----------------------|---------|---------------------|

|         | 2D                   | $2^{10}$ to $2^{22}$ | Yes     | 6.9                 |

| Peta    |                      |                      | No      | 15.1                |

| reta    | 3D                   | $2^9$ to $2^{14}$    | Yes     | 1.02                |

|         |                      |                      | No      | 3.56                |

|         | 2D                   | $2^{10}$ to $2^{22}$ | Yes     | 22.22               |

| Grid    |                      |                      | No      | 15.63               |

| Gilu    | 3D $2^9$ to $2^{14}$ | $2^9 + 2^{14}$       | Yes     | 4.41                |

|         |                      |                      | No      | 7.79                |

Table 2.1: Performance modeling summary for parallel machines. "Overlap" indicates whether communication is overlapped with computation.

| Machine      | Matrix | Range of $n$         | Modeled Speedup | % Peak      |

|--------------|--------|----------------------|-----------------|-------------|

| OOC          | 2D     | $2^{14}$ to $2^{25}$ | 10.2            | 17%         |

|              | 3D     | $2^8$ to $2^{17}$    | [7.39, 9.51]    | [14%, 18%]  |

| CacheBlocked | 2D     | $2^8$ to $2^{19}$    | [2.45, 2.58]    | [62%,  65%] |

| Cacheblocked | 3D     | $2^8$ to $2^{12}$    | [1.34, 1.36]    | 38%         |

Table 2.2: Performance modeling summary for sequential machine model.

avoid off-chip latency and bandwidth to DRAM.

We only modeled the non-overlapping case, with modeled speedups as shown in the table below. In contrast to the last table, Table 2.2 shows the range of speedups attained over all problem sizes n, since bandwidth is always the bottleneck, so significant speedups were attained for all problems sizes. Here, "% Peak" is the ratio of the (modeled) running time of the algorithm on a zero latency / infinite bandwidth machine to the (modeled) true time. The closer this is to 100%, the more completely the algorithm masks the cost of slow memory access. On OOC, we see that we get high speedups, though we are not near peak. On CacheBlocked our speedups are more modest, but still good, and we are closer to peak.

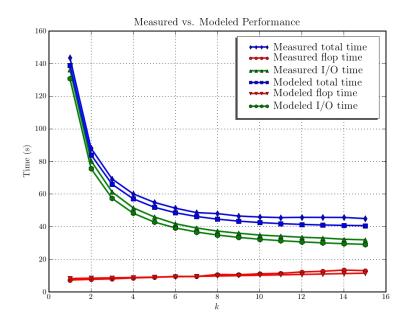

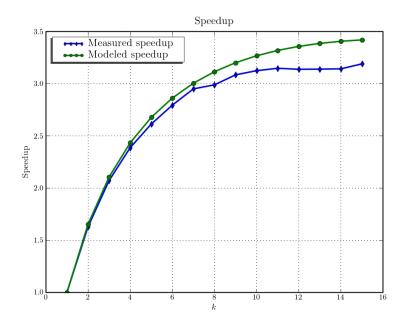

We now describe the organization of the rest of the chapter. Section 2.4 describes parallel algorithms for distributed memory systems, whereas Section 2.5 covers sequential algorithms. We discuss the results of asymptotic analysis of our proposed algorithms in Section 2.6. Section 2.7 covers the results of performance modeling for different machine models. Section 2.8 describes an actual out-of-core implementation, which achieves a speedup of  $3.2\times$ , and is 16% as fast as it would be if run on a machine with zero disk latency and infinite disk bandwidth, up from 5%. This is both a good speedup, and shows that we are within 16% of peak. We also describe our performance model, which uses measured machine parameters and agree with measured performance closely. Section 2.9 adapts the parallel and sequential algorithms for shared memory multi-core machines and Section 2.10 describes a multi-core implementation of matrix powers. Section 2.11 describes the integration of matrix powers in communication-avoiding GMRES (CA-GMRES) and performance results.

## 2.4 Distributed Memory Parallel Algorithms for Matrix Powers

We consider the conventional parallel algorithm, as well as our two new approaches:

- **Conventional Parallel Approach (PA0).** The algorithm runs in k steps, where step j computes  $x^{(j)} = A^j x$  from  $x^{(j-1)} = A^{j-1} x$  by each processor receiving messages with the needed remotely stored entries of  $x^{(j-1)}$  and computing its local components of  $x^{(j)}$ .

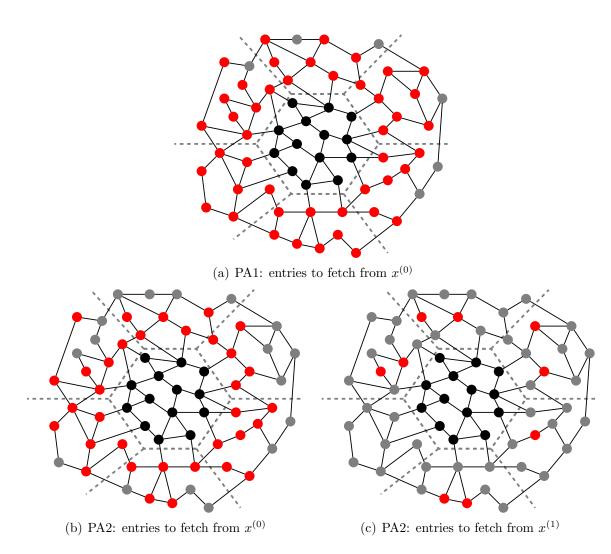

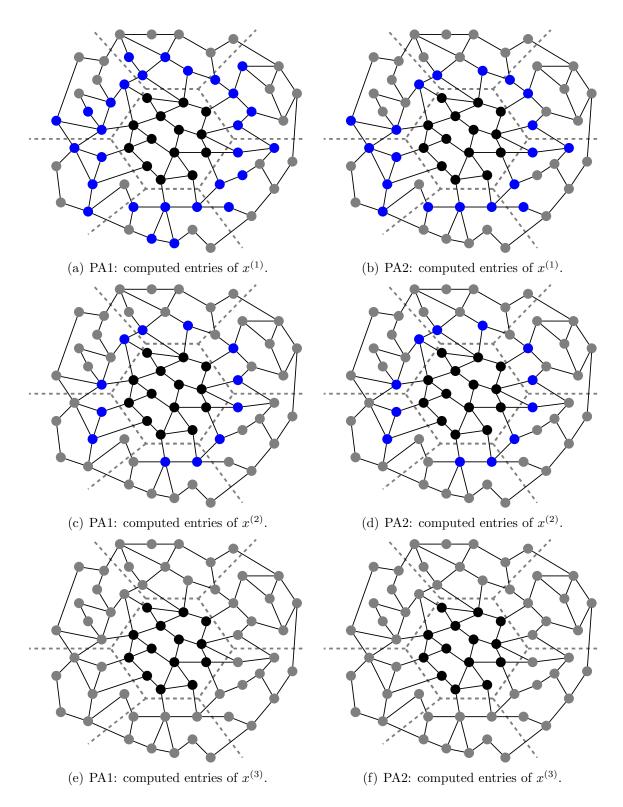

- **Parallel Approach 1 (PA1).** We begin the computation of all *locally computable* components of  $[Ax, ..., A^kx]$ , and simultaneously begin sending all the components of x needed by the neighboring processors to compute the remaining components of  $[Ax, ..., A^kx]$ . Locally computable entries are ones which can be computed locally without needing any entry from any other processor. When the locally computable components are complete, we block until the remote components of x arrive. This maximizes the potential overlap of computation and communication, but does not minimize redundant work, as we will see in PA2.

- **Parallel Approach 2 (PA2).** We compute the set of local values of  $[Ax, ..., A^kx]$  needed by the neighboring processors, so as to minimize redundant computation. Then we send these values to the neighboring processors, and simultaneously compute the remaining locally computable values. When all the locally computable values are complete, we block until the remote components of  $[Ax, ..., A^kx]$  arrive, and complete the work. This minimizes redundant work, but permits slightly less overlap of computation and communication.

The difference between PA1 and PA2 will become clearer when we explain them for the 1D mesh.

We will estimate the cost of our parallel algorithms by measuring five quantities:

- 1. number of floating point operations per processor

- 2. number of floating point numbers communicated per processor (the "bandwidth cost")

- 3. number of messages sent per processor (the "latency cost"),

- 4. total memory required per processor for the matrix, and

- 5. total memory required per processor for the vectors.

Now we argue informally why either approach PA1 or PA2 approximately minimizes communication. We assume that there is no cancellation in any of the powers  $A^j$  or  $A^j x$ that would make them sparser than if all their nonzero entries were nonnegative, and that there are no algebraic relations among entries of A and/or x. Thus the complexity only depends on the sparsity pattern, and for simplicity of notation we assume all the nonzero entries of A and x are positive. In particular the set  $\mathcal{D}$  of processors owning entries of x on which block row i of  $[Ax, A^2x, ..., A^kx]$  depends may be described as the set of processors owning those  $x_j$  where block row i of  $A + A^2 + \cdots + A^k$  has a nonzero j-th column. In both algorithms PA1 and PA2, the processor owning row block i receives exactly one message from each processor in  $\mathcal{D}$ , which minimizes latency. Furthermore, PA1 only sends those entries of x in each message on which the answer depends, which minimizes the bandwidth cost. PA2 sends the same amount of data although different values so as to minimize redundant computation.

The rest of this section is organized as follows:

- Subsection 2.4.1 describes PA1 and PA2 in more detail for 1D meshes (band matrices).

- Subsection 2.4.2 describes PA1 and PA2 in more detail for 2D and 3D meshes.

- Subsection 2.4.3 presents a tabular summary of all the operation counts for meshes, and discusses how they specialize to stencil matrices, where each row of the matrix has identical nonzero entries (modulo boundaries).

- Subsection 2.4.4 describes PA1 and PA2 on general sparse matrices.

#### 2.4.1 1D meshes

We begin by considering a tridiagonal matrix (i.e., with bandwidth b = 1). In the conventional parallel algorithm each processor executes the code in Algorithm 2.1 in order to compute  $x^{(j)} = A^j x^{(0)}$  for j = 1 to k.

#### Algorithm 2.1 PA0: conventional parallel approach for 1D mesh with b = 1

{processor q owns  $x_{s_q}^{(0)}, \dots, x_{e_q}^{(0)}$ , boundaries q = 1 and q = p ignored} for  $j = 1, 2, \dots, k$  do start sending  $x_{s_q}^{(j-1)}$  to processor q - 1start sending  $x_{e_q}^{(j-1)}$  to processor q + 1start receiving  $x_{s_q-1}^{(j-1)}$  from processor q - 1start receiving  $x_{e_q+1}^{(j-1)}$  from processor q + 1compute  $x_{s_q+1}^{(j)} = (Ax^{(j-1)})_{s_q+1}, \dots, x_{e_q-1}^{(j)} = (Ax^{(j-1)})_{e_q-1}$ wait for messages to arrive compute  $x_{s_q}^{(j)} = (Ax^{(j-1)})_{s_q}$  and  $x_{e_q}^{(j)} = (Ax^{(j-1)})_{e_q}$

The computational cost is clearly 2k messages, 2k words sent, and  $5k\frac{n}{p}$  flops (3 multiplies and 2 additions per vector component computed). The memory required per processor is  $3\frac{n}{p}$  matrix entries and  $(k+1)\frac{n}{p}+2$  vector entries (for the local components of  $[x, Ax, ..., A^kx]$ and for the values on neighboring processors).

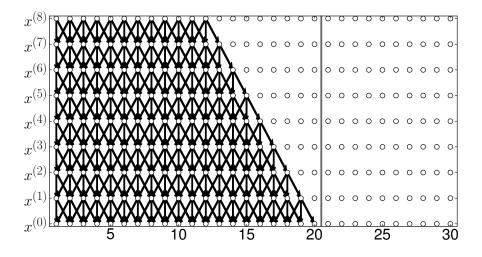

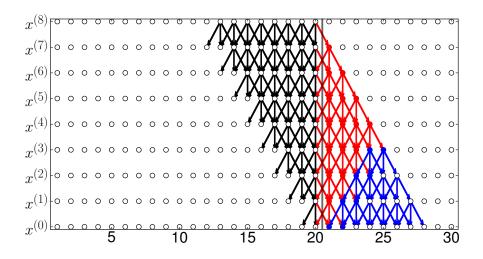

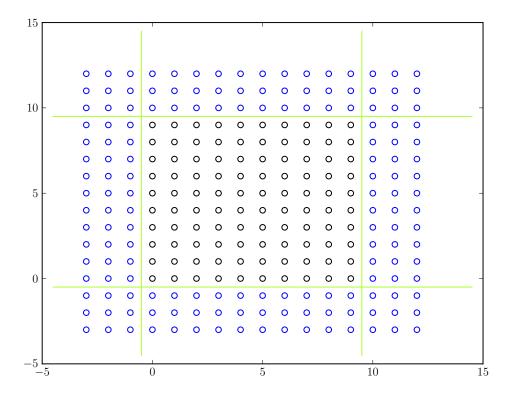

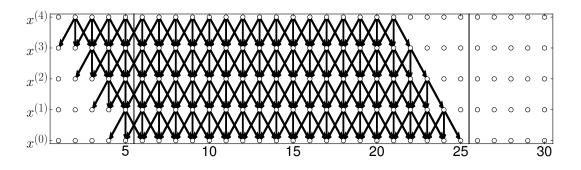

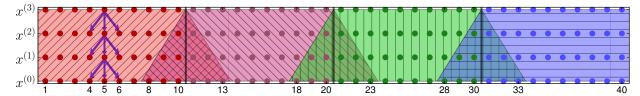

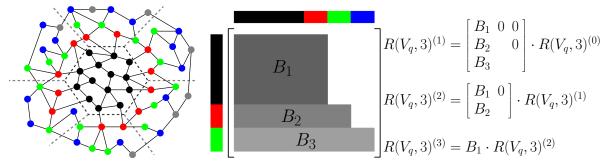

To explain PA1, consider Figure 2.1. Each row of circles represents the entries of  $A^{j}x$ , for j = 0 to j = 8. A subset of 30 components of each vector is shown, owned by 2

Figure 2.1: Locally Computable components of  $[Ax, ..., A^8x]$  for tridiagonal matrix

processors, one to the left of the vertical gray line, and one to the right. (There are further components and processors not shown, to the left and to the right of the ones in the figure). The diagonal and vertical lines show the dependencies: the three lines below each circle (component *i* of  $A^{j}x$ ) connect to the circles on which its value depends (components i - 1, *i* and i + 1 of  $A^{j-1}x$ ). Figure 2.1 shows the local dependencies of the left processor, i.e., all the circles (vector components) that can be computed without communicating with the right processor. The remaining circles without attached lines to the left of the vertical gray line require information from the right processor to be computed.

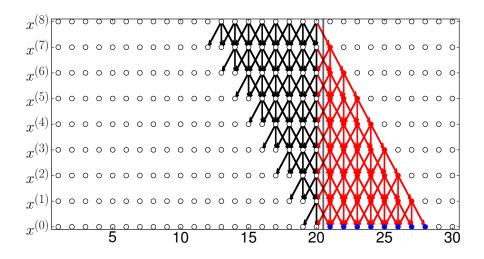

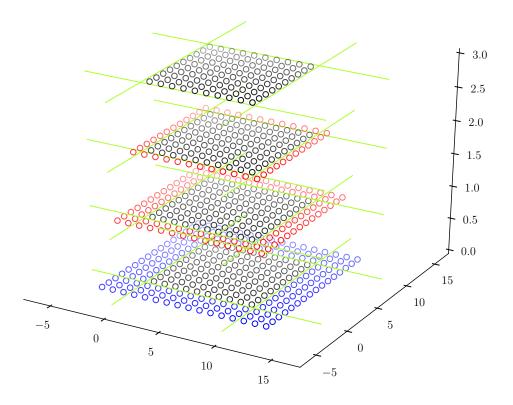

Figure 2.2 shows how to compute these remaining circles using PA1. The dependencies are again shown by diagonal and vertical lines below each circle, but now dependencies on data formally owned by the right processor are shown in red. All these values in turn depend on the k = 8 leftmost value of  $x^{(0)}$  owned by the right processor, shown as blue circles in the bottom row. By sending these values from the right processor to the left processor, the left processor can compute all the circles whose dependencies are shown in Figure 2.2. The black circles indicate computations ideally done only by the left processor, and the red circles show redundant computations, i.e., ones also done by the right processor. Algorithm 2.2 summarizes this discussion.

The memory required by PA1 is  $(k + 4)\frac{n}{p}$  as in PA0 plus 2k more words for vector entries plus 6(k-1) more words for matrix entries, altogether 8k-6 more than PA0. PA1's other costs are 2 messages (versus 2k for the conventional method), 2k words sent (same as the conventional method), and  $5k\frac{n}{p} + 5k(k-1)$  flops, or roughly  $5k^2$  more flops than the conventional method. This can also be described as an increase in flops by a factor  $1 + k/(\frac{n}{p})$ .

Note that we are assuming that  $k < \frac{n}{p}$ , so that only data from neighboring processors is needed, rather than more distant processors. Indeed, we expect that  $k \ll \frac{n}{p}$  in practice, which will mean that the number of extra flops (not to mention extra memory) will be negligible. We continue to make this assumption later without repeating it, and use it to

Figure 2.2: Remote dependencies in PA1 for  $[Ax, ..., A^8x]$  for tridiagonal matrix

#### Algorithm 2.2 PA1: Parallel Approach 1 for 1D mesh with b = 1

{processor q owns  $x_{s_q}^{(0)}, \ldots, x_{e_q}^{(0)}$ ; ignore boundaries as in PA0} start sending  $x_{s_q}^{(0)}, \ldots, x_{s_q+k-1}^{(0)}$  to processor q-1start sending  $x_{e_q-k+1}^{(0)}, \ldots, x_{e_q}^{(0)}$  to processor q+1start receiving  $x_{s_q-k}^{(0)}, \ldots, x_{s_q-1}^{(0)}$  from processor q-1start receiving  $x_{e_q+1}^{(0)}, \ldots, x_{e_q+k}^{(0)}$  from processor q+1for  $j = 1, \ldots, k$  do compute locally dependent components of  $A^j x^{(0)}$  as shown in Figure 2.1 wait for receives to finish for  $j = 1, \ldots, k$  do compute remaining red and black components of  $A^j x^{(0)}$  as shown in Figure 2.2

simplify some expressions in Table 2.3 in Section 2.4.3.

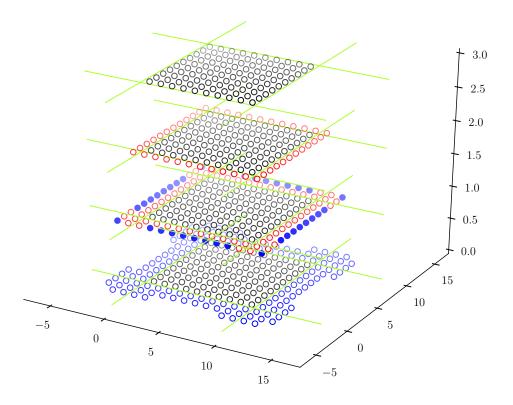

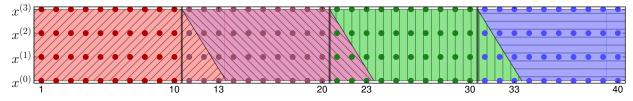

Now consider PA2, illustrated in Figure 2.3. We note that the blue and black circles owned by the right processor and attached to blue lines can be computed locally by the right processor. The 8 solid blue circles can then be sent to the left processor to compute the remaining circles connected to black and/or red lines. This saves the redundant work represented by the blue circles, but leaves the redundant work to compute the red circles, about half the redundant work of PA1. Algorithm 2.3 summarizes this discussion.

The memory required by PA2 is  $(k+4)\frac{n}{p}$  as in PA0 plus 2k more words for vector entries plus  $6\lfloor \frac{k}{2} \rfloor$  more words for matrix entries, altogether roughly 5k more words than PA0. The other costs of PA2 are 2 messages (versus 2k for the conventional method), 2k words sent (same as the conventional method), and  $5k\frac{n}{p} + 10\lfloor \frac{k}{2} \rfloor (\lfloor \frac{k}{2} \rfloor + odd(k))$  flops, where odd(k) = 1if k is odd and odd(k) = 0 if k is even. In other words, PA2 takes roughly  $\frac{5}{2}k^2$  more flops than the conventional method, half as many extra flops as PA1.

We will not always draw the corresponding detailed pictures or algorithms for the other

Figure 2.3: Remote dependencies in PA2 for  $[Ax, ..., A^8x]$  for tridiagonal matrix

meshes, but the same kinds of analyses apply. Nor will we compute the exact expressions for the number of extra flops, but rather approximate the number of mesh points in the black red and blue regions (pyramids, triangles, tetrahedra, and higher dimensional polyhedra) that arise by computing the leading terms of the volumes of these geometric objects. The next sections will sketch these results, and Section 2.4.3 will summarize all the results in a table.

Now we briefly address 1D meshes with bandwidth b > 1, i.e., band matrices. The work per mesh point is 2b + 1 multiplications and 2b additions, or 4b + 1 flops in all per mesh point, or (4b + 1)nk/p flops for the conventional method. A total of 2kb words are communicated with processors to the left and right, in 2k messages. The memory required per processor is  $(k + 1)\frac{n}{p} + 2b$  words for the vectors and  $(2b + 1)\frac{n}{p}$  words for the matrix entries, or  $(2b + k + 2)\frac{n}{p} + 2b$  words in all. Now consider PA1. To compute the extra flops, we must count the number of mesh

Now consider PA1. To compute the extra flops, we must count the number of mesh points in the region corresponding to the red triangle in Figure 2.2, namely bk(k-1)/2. To get the number of extra flops, this is multiplied by 4b + 1. The number of messages is again 2, containing 2kb words in all. The number of words of memory required is  $(k+1)\frac{n}{p} + 2kb$

for the vectors and  $(2b+1)(\frac{n}{p}+2kb)$  for the matrix entries, or  $(2b+k+2)\frac{n}{p}+kb(4b+4)$  words in all.

Now consider PA2. The region corresponding to the blue region in Figure 2.3 has again about half the number of mesh points as the region corresponding to the red region in Figure 2.2, roughly bk(k-1)/4. To get the number of extra flops, this is again multiplied by 4b+1, and by 2, for the right and left boundaries. The number of words of memory required for vectors is the same as PA1, and slightly smaller for matrix entries,  $(2b+1)(\frac{n}{p}+kb)$ .

### 2.4.2 2D and 3D meshes

#### 2D mesh with a 5 point stencil graph

We consider multiplying by a matrix whose graph is the 5-point stencil, i.e., with North, South, East, West (NSEW) connections on an *n*-by-*n* grid of unknowns partitioned on  $p^{1/2}$ by- $p^{1/2}$  grid of processors. We assume  $p^{1/2}|n$ , so that each processor owns a  $\frac{n}{p^{1/2}}$ -by- $\frac{n}{p^{1/2}}$ square of grid points (vector components), and their corresponding matrix rows, and that  $k < \frac{n}{p^{1/2}}$ . We expect that  $k \ll \frac{n}{p^{1/2}}$  in practice.

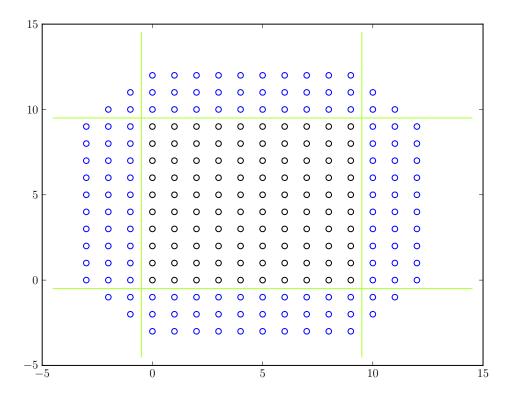

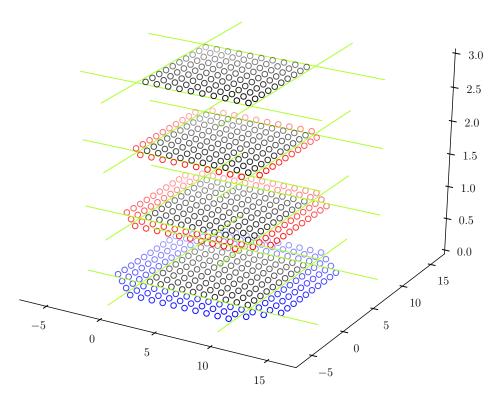

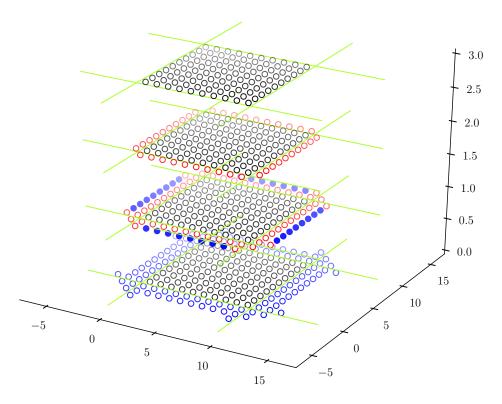

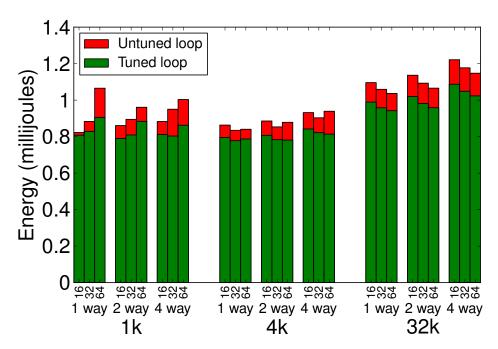

Figure 2.4 shows the remote domain of dependence for a single processor (demarcated by green lines as before) owning a 10-by-10 grid of unknowns (the black circles). When k = 3, the results of  $[Ax, ..., A^kx]$  will depend on the remote values shown by blue circles (the same notation as Figure 2.2). Unlike Figure 2.2, Figure 2.4 does not show circles for components of  $A^jx$  for j > 0, but rather a projected view. Figure 2.5 shows a 3D view analogous to Figure 2.2.

The number of messages decreases from 4k for the conventional algorithm to 8 instead of to 4 for PA1, because communication is required with the corner neighbors (NW, SW, NE and SE), as well as side neighbors (N, S, E and W). The volume of communication also grows slightly to include the triangles of size k - 1 owned by the 4 corner neighbors. The number of flops grows roughly by the factor  $1 + 2k/(\frac{n}{p^{1/2}})$ . When  $k \ll \frac{n}{p^{1/2}}$ , this increase is quite small. It is a little harder to visualize the regions of redundant computations than in the 1D mesh case: In the side neighbors, the red circles denoting redundant computations form a prism with triangular cross section and volume (and number of contained points) proportional to  $k\frac{n}{p^{1/2}}$ , and in the corner neighbors the red circles form a pyramid with volume (and number of contained points) proportional to  $k^3$ . The memory requirement for the conventional algorithm is  $(k+1)\frac{n^2}{p} + 4\frac{n}{p^{1/2}}$  vector entries and  $5\frac{n^2}{p}$  matrix entries; for PA1 it increases by an additional  $4k\frac{n}{p^{1/2}} + 2k^2$  vector entries and 5 times as many matrix entries. Figure 2.6 shows the dependencies for PA2 applies to the 2D mesh with a 5 point stencil

Figure 2.6 shows the dependencies for PA2 applies to the 2D mesh with a 5 point stencil graph. As in Figure 2.3, there are black circles that are the desired (or initial) values, red circles representing redundant work, blue circles denoting work that was redundant in PA1 but saved by PA2, and solid blue circles that are to be communicated. In the side processors, the regions of redundant computations again form prisms with triangular cross sections, with half the cross sectional area of PA1. Thus, like the 1D case, this means about half the redundant work is saved. It is somewhat more difficult to see what is happening in the corner processors. The pyramid of redundant operations from PA1 has a smaller

Figure 2.4: Remote dependencies in PA1 for  $[Ax, ..., A^3x]$  for 2D mesh with 5 point stencil, projected view

tetrahedron of locally computable components subtracted from it; geometrical symmetry considerations indicate that this saves about 1/3 of the redundant operations in the corners. The number of extra words of memory required for matrix entries decreases by nearly a factor of 2.

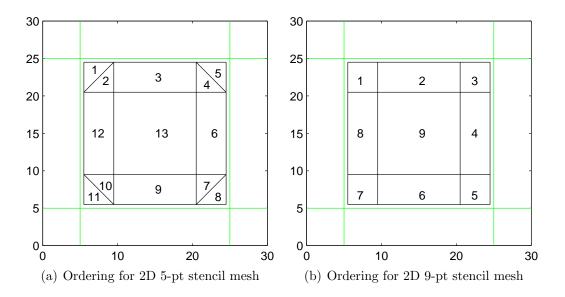

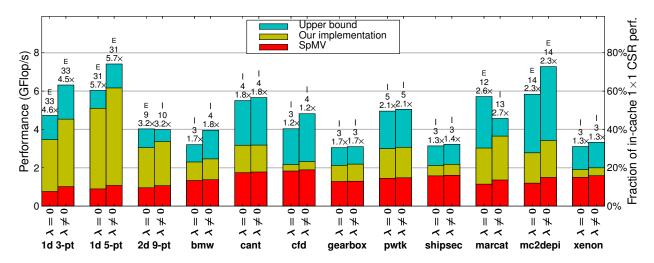

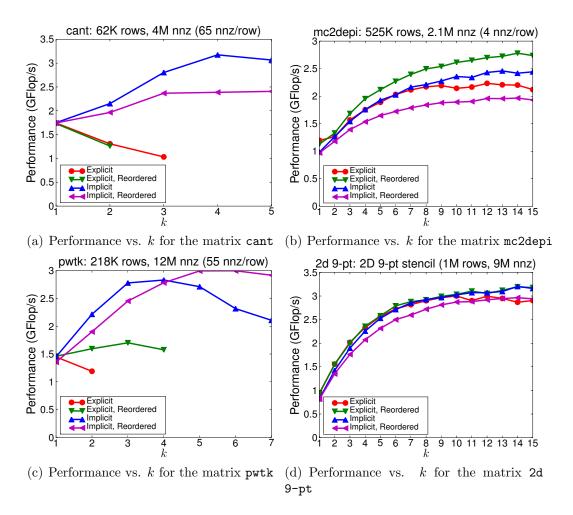

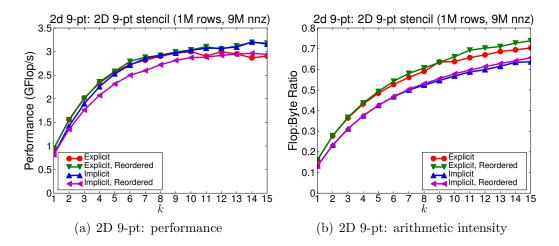

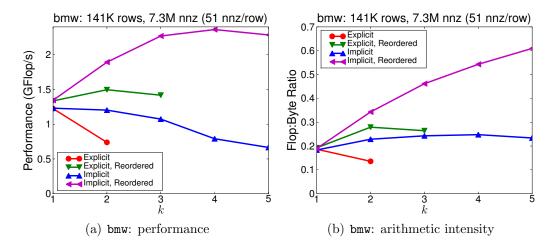

#### 2D mesh with 9 point stencil graph