# UCLA UCLA Electronic Theses and Dissertations

**Title** Performance Debugging Frameworks for FPGA High-Level Synthesis

**Permalink** https://escholarship.org/uc/item/1f19x5nc

**Author** Choi, Young-kyu

Publication Date 2019

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA

Los Angeles

Performance Debugging Frameworks for FPGA High-Level Synthesis

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Computer Science

by

Young-kyu Choi

2019

© Copyright by Young-kyu Choi 2019

#### ABSTRACT OF THE DISSERTATION

Performance Debugging Frameworks for FPGA High-Level Synthesis

by

Young-kyu Choi Doctor of Philosophy in Computer Science University of California, Los Angeles, 2019 Professor Jingsheng Jason Cong, Chair

Using high-level synthesis (HLS) tools for field-programmable gate array (FPGA) design is becoming an increasingly popular choice because HLS tools can generate a high-quality design in a short development time. However, current HLS tools still cannot adequately support users in understanding and fixing the performance issues of the current design. That is, current HLS tools lack in performance debugging capability. Previous work on performance debugging automates the process of inserting hardware monitors in low-level register-transfer level (RTL) languages which limits the comprehensibility of the obtained result. Instead, our HLS-based flows offer analysis on a function or loop level and provide more intuitive feedback that can be used to pinpoint the performance bottleneck of a design. In this dissertation, we present a collection of HLS-based debugging frameworks for various purposes and characteristics of the design. First, we address the problem in the HLS synthesis step, where an inaccurate cycle estimation is provided if the program has input-dependent behavior. We propose a new performance estimator that automatically instruments code that models the hardware execution behavior and interprets the information from the HLS software simulation. However, the performance estimation result of this flow may not be accurate for a type of designs that cannot be simulated correctly by existing HLS software simulators. To handle such cases, we propose a new software simulator that provides cycle-accurate result based on the HLS scheduling information. If the input dataset is not available for software simulation or high-level models do not exist for all components of the FPGA design, we also present an on-board monitoring flow for automated cycle extraction and stall analysis. Finally, we address the needs of HLS programmers to automatically find the best set of directives for FPGA designs. We propose a design space exploration (DSE) framework to optimize applications with variable loop bounds in Polybench benchmark. A quantitative comparison among the proposed frameworks is shown using the sparse matrix-vector multiplication benchmark. The dissertation of Young-kyu Choi is approved.

William Hsu

Miryung Kim

Anthony John Nowatzki

Jingsheng Jason Cong, Committee Chair

University of California, Los Angeles

2019

For my wife, Hyejin, my two daughters, Jiho and Jimin, my parents, and my in-law parents

# 기나긴 박사과정 중에 항상 저를 사랑해준 아내와 딸들, 그리고 항상 격려하고 기도해주신 부모님과 장인 장모님께 감사 드립니다.

## TABLE OF CONTENTS

| Li | st of l | Figures       |                                                                | X            |

|----|---------|---------------|----------------------------------------------------------------|--------------|

| Li | st of [ | <b>Fables</b> |                                                                | iii          |

| A  | cknow   | vledgme       | ents x                                                         | vi           |

| Vi | ta.     |               |                                                                | 7 <b>iii</b> |

| 1  | Intr    | oductio       | <b>n</b>                                                       | 1            |

| 2  | Rela    | nted Wo       | rks                                                            | 7            |

|    | 2.1     | Perform       | mance Analysis Tools in CPU and GPU                            | 7            |

|    | 2.2     | Relate        | d Works on Performance Estimation                              | 7            |

|    | 2.3     | Relate        | d Work on Simulation                                           | 8            |

|    | 2.4     | Relate        | d Works on FPGA Hardware Debugging                             | 9            |

|    | 2.5     | Relate        | d Works on HLS Design Space Exploration                        | 10           |

| 3  | Perf    | ormanc        | e Debugging with Fast and Accurate HLS Performance Estimator 1 | 12           |

|    | 3.1     | Perform       | mance Debugging Framework: HLScope                             | 13           |

|    |         | 3.1.1         | Scope and Overall Tool Structure                               | 13           |

|    |         | 3.1.2         | Performance Debugging Parameters                               | 17           |

|    |         | 3.1.3         | Performance Debugging for Quicksort                            | 20           |

|    | 3.2     | Perform       | mance Estimator for HLS                                        | 22           |

|    |         | 3.2.1         | Introduction                                                   | 22           |

|    |         | 3.2.2         | Background: Cycle Estimation of Loops                          | 24           |

|   |     | 3.2.3   | Improving Cycle Estimation Accuracy for Loops and Conditional Statements | 25 |

|---|-----|---------|--------------------------------------------------------------------------|----|

|   |     | 3.2.4   | External Memory Access Model for HLS Software Simulation                 | 31 |

|   |     | 3.2.5   | Experimental Results                                                     | 38 |

|   |     | 3.2.6   | Software Simulation Flow Overhead                                        | 40 |

|   |     | 3.2.7   | Comparison with Related Work                                             | 41 |

|   |     | 3.2.8   | Conclusion                                                               | 42 |

| 4 | Cyc | le-Accu | rate Software Simulator for HLS                                          | 43 |

|   | 4.1 | Introdu | ction                                                                    | 43 |

|   | 4.2 | Proble  | m Description and Motivating Examples                                    | 48 |

|   |     | 4.2.1   | Data Ordering Problem                                                    | 48 |

|   |     | 4.2.2   | Artificial Deadlock and Stall                                            | 50 |

|   |     | 4.2.3   | Missing Data from Feedback Path                                          | 52 |

|   | 4.3 | Proble  | m Statement and Challenges                                               | 53 |

|   | 4.4 | Autom   | ated Code Generation for Rapid Cycle-Accurate Simulation                 | 57 |

|   |     | 4.4.1   | FIFO Communication Cycle-Accurate Simulation                             | 57 |

|   |     | 4.4.2   | Simulation of Parallelism                                                | 65 |

|   |     | 4.4.3   | Loop and Function Simulation                                             | 69 |

|   | 4.5 | Optimi  | zation of Pipelined Loops Simulation                                     | 70 |

|   |     | 4.5.1   | Cycle-Based Variable Liveness Analysis                                   | 70 |

|   |     | 4.5.2   | Pointer-Based Variable Access                                            | 71 |

|   | 4.6 | Overal  | l Flow                                                                   | 72 |

|   | 4.7 | Source  | -Level Correctness Debugging and Performance Debugging                   | 73 |

|   |     | 4.7.1   | Live Capture                                                             | 74 |

|   |     | 4.7.2   | Source-Level Event Trigger and Performance Measurement                   | 75 |

|   |      | 4.7.3   | Large Data Debugging                                               | 76 |

|---|------|---------|--------------------------------------------------------------------|----|

|   | 4.8  | Experi  | mental Results                                                     | 76 |

|   |      | 4.8.1   | Experimental Setup                                                 | 76 |

|   |      | 4.8.2   | Execution Time                                                     | 77 |

|   |      | 4.8.3   | Accuracy                                                           | 80 |

|   | 4.9  | Conclu  | Iding Remarks                                                      | 80 |

| 5 | On-  | Board N | Monitoring for Performance Debugging                               | 82 |

|   | 5.1  | Introdu | uction                                                             | 82 |

|   | 5.2  | Cycle   | Extraction Based on In-FPGA Monitoring                             | 82 |

|   | 5.3  | In-FPC  | GA Stall Analyzer for FIFO-based Dataflow Application              | 85 |

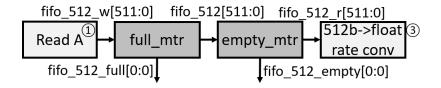

|   |      | 5.3.1   | Code Instrumentation for Module Under Analysis                     | 85 |

|   |      | 5.3.2   | Code Instrumentation for FIFOs                                     | 86 |

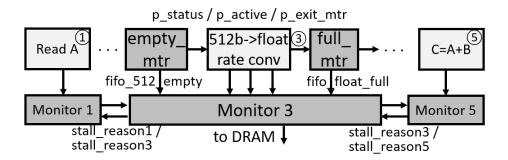

|   |      | 5.3.3   | Monitor for Stall Analysis Network                                 | 87 |

|   | 5.4  | Experi  | mental Results                                                     | 89 |

|   |      | 5.4.1   | Experimental Setup                                                 | 90 |

|   |      | 5.4.2   | Logic Overhead                                                     | 90 |

|   | 5.5  | Compa   | arison with Related On-board Debugging Work                        | 91 |

|   | 5.6  | Conclu  | Iding Remarks                                                      | 91 |

| 6 | Fast | Design  | Space Exploration for Applications with Dynamic Behavior           | 93 |

|   | 6.1  | Introdu | action                                                             | 93 |

|   | 6.2  | HLS C   | Code Transformation for Variable-Bound Loops                       | 95 |

|   |      | 6.2.1   | Loop Pipelining and Loop Unrolling Based on the Maximum Loop Bound | 95 |

|   |      | 6.2.2   | Partial Unrolling with Pipelining                                  | 96 |

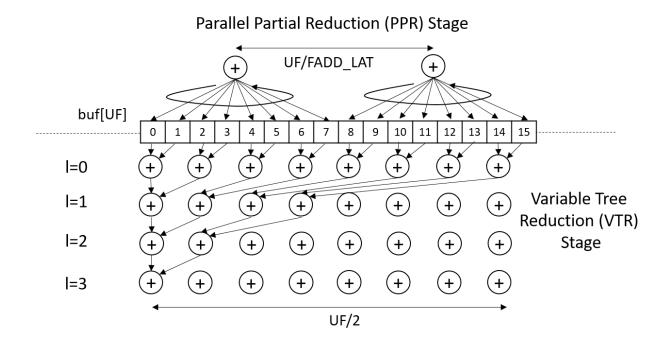

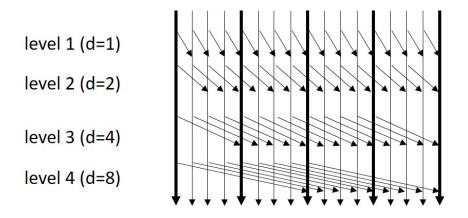

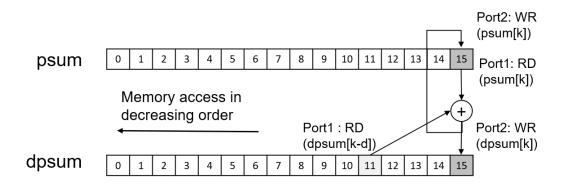

|      |      | 6.2.3    | Transformation for Variable Reduction                                    |

|------|------|----------|--------------------------------------------------------------------------|

|      |      | 6.2.4    | Transformation for Variable Prefix Sum                                   |

| 6    | 5.3  | Cycle    | Resource Estimation                                                      |

|      |      | 6.3.1    | Resource Estimation                                                      |

|      |      | 6.3.2    | Cycle Estimation                                                         |

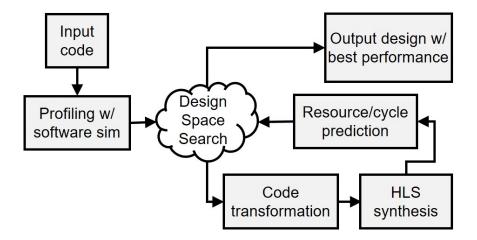

| 6    | 5.4  | Overal   | l Flow and the Design Space Exploration                                  |

| 6    | 5.5  | Experi   | mental Result                                                            |

|      |      | 6.5.1    | Experimental Setup                                                       |

|      |      | 6.5.2    | Performance                                                              |

|      |      | 6.5.3    | Exploration Speed and Prediction Accuracy                                |

| 6    | 6.6  | Compa    | arison with Related Work                                                 |

| 6    | 6.7  | Conclu   | usion                                                                    |

| 7 (  | Dua  | ntitativ | e Comparison among Proposed Frameworks and Concluding Remarks 117        |

|      | 7.1  |          | tative Comparison with Sparse Matrix-Vector Multiplication Benchmark 117 |

| /    | 1.1  | -        |                                                                          |

|      |      | 7.1.1    | Sparse Matrix-Vector Multiplication                                      |

|      |      | 7.1.2    | Comparison of the Proposed Performance Debugging Frameworks 120          |

|      |      | 7.1.3    | Comparison with GPU and Multithreaded CPU Implementation 123             |

| 7    | 7.2  | Conclu   | Iding Remarks and Future Work                                            |

| Refe | eren | ces .    |                                                                          |

## LIST OF FIGURES

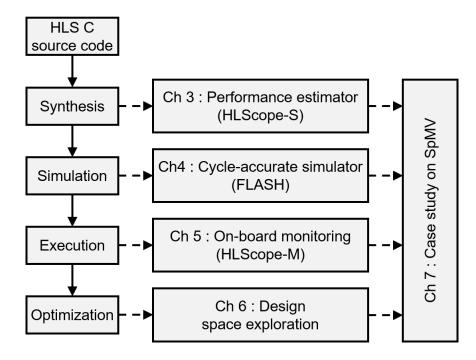

| 1.1  | HLS development steps and the proposed performance debugging frameworks                    | 3  |

|------|--------------------------------------------------------------------------------------------|----|

| 3.1  | Initial unoptimized C code of non-recursive quicksort (modified from [49])                 | 14 |

| 3.2  | Dependency graph for $qsort\_comp()$ given in Fig. 3.1 (c). The dotted line denotes        |    |

|      | synchronization barriers, and $t$ denotes time frames divided by synchronization barriers. | 15 |

| 3.3  | Quicksort code and corresponding dependency graph after applying double buffering          |    |

|      | and unrolling. $loadstore()$ function combines the $load()$ and $store()$ function given   |    |

|      | in Fig. 3.1, and <i>qsort_comp()</i> function is the same as that of Fig. 3.1.             | 16 |

| 3.4  | Performance debugging parameters collected from the initial unoptimized version of         |    |

|      | quicksort. Parameter derived from HLScope-S result. (batch_num=128, n_per_batch=1024)      | 4, |

|      | 'dram': external DRAM port, 'lmem': local BRAM).                                           | 20 |

| 3.5  | Performance debugging parameters after unrolling qsort_comp() function 32 times.           |    |

|      | Some PEs not shown for brevity.                                                            | 21 |

| 3.6  | Performance debugging parameters after applying double buffering optimization              | 21 |

| 3.7  | C code of non-recursive quicksort [49]                                                     | 23 |

| 3.8  | Loop pipelining parameters                                                                 | 24 |

| 3.9  | Code instrumentation to find dynamic loop bound for loop 1.1.1 in Fig. 3.7. Instru-        |    |

|      | mented code is in bold.                                                                    | 25 |

| 3.10 | Quicksort code after pragma insertion                                                      | 27 |

| 3.11 | Quicksort code after inserting cycle estimation code                                       | 28 |

| 3.12 | Dependency graph for $qsort\_comp()$ given in Fig. 3.11. The dotted line denotes syn-      |    |

|      | chronization barriers, and $t$ denotes time frames divided by synchronization barriers.    |    |

|      | Reproduced from Fig. 3.2.                                                                  | 30 |

| 3.13 | Random memory access example in HLS. Variable bram is a float-type local memory                      |    |

|------|------------------------------------------------------------------------------------------------------|----|

|      | and variable dram is an external port. Local memory addr has been pre-initialized                    |    |

|      | with random memory location.                                                                         | 33 |

| 3.14 | Code example for external memory access from multiple PEs, where <i>load()</i> , <i>qstore_comp(</i> | ), |

|      | <i>store()</i> have no dependency with double buffering                                              | 36 |

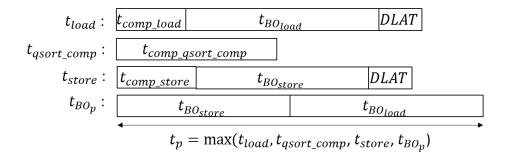

| 3.15 | Computing cycle estimate (Eq. 3.18 and Eq. 3.19) for the example given in Fig. 3.14,                 |    |

|      | in the for loop that contains <i>load()</i> , <i>qsort_comp()</i> , <i>store()</i> PEs               | 36 |

| 4.1  | Molecular dynamics simulation [33]                                                                   | 45 |

| 4.2  | HLS design steps [40] and simulation flows                                                           | 46 |

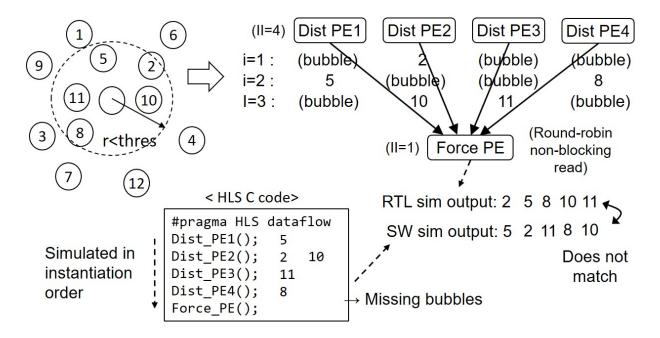

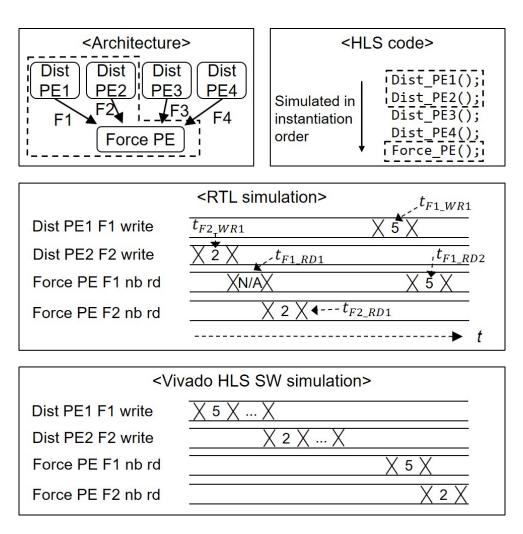

| 4.3  | Timing diagram of the molecular dynamics simulation in Fig. 4.1 (FIFO transactions                   |    |

|      | among only Dist PE1, Dist PE2, and Force PE are shown)                                               | 49 |

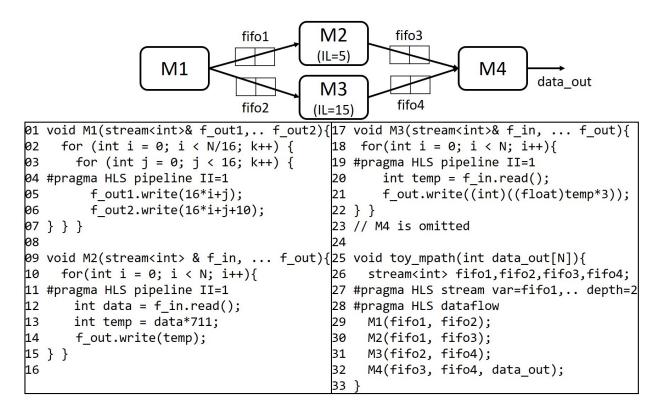

| 4.4  | Structure and code for motivating example toy_mpath                                                  | 51 |

| 4.5  | Modified code of M2 in Fig. 4.4 to avoid artificial deadlock                                         | 52 |

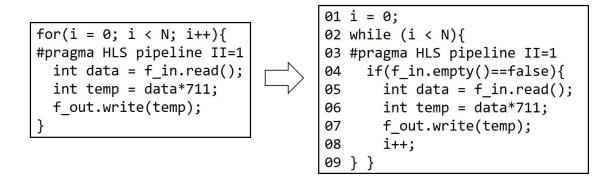

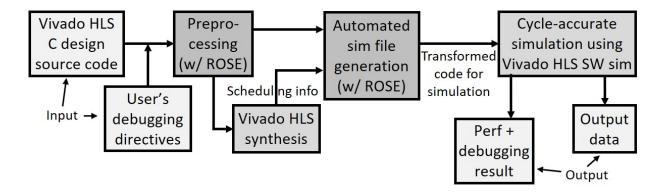

| 4.6  | Matrix multiplication with linear systolic array architecture                                        | 53 |

| 4.7  | Vivado HLS scheduling report for M2 of Fig. 4.5                                                      | 58 |

| 4.8  | Simulation function structure for selective simulation of an FSM state (M2_SIM is                    |    |

|      | simulated at line 9 of Fig. 4.10)                                                                    | 59 |

| 4.9  | Simulation code that models pipelined loop parallelism for M2 of Fig. 4.5 (provides                  |    |

|      | details for line 9 of Fig. 4.8)                                                                      | 66 |

| 4.10 | Module/FIFO simulation scheduler to model task-level parallelism                                     | 68 |

| 4.11 | FIFO simulation code for fifo3 (F3_SIM is simulated at line 11 of Fig. 4.10) $\ldots$                | 69 |

| 4.12 | Loop condition and update for flattened loop in M1 of Fig. 4.4                                       | 70 |

| 4.13 | The code after applying pointer-based variable access optimization to the initial code               |    |

|      | provided in Fig. 4.9                                                                                 | 71 |

| 4.14 | Overall simulation framework of FLASH                                                                | 73 |

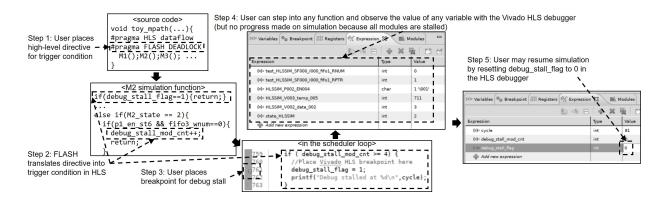

| 4.15 | An example debugging session for deadlock detection using FLASH                        |

|------|----------------------------------------------------------------------------------------|

| 5.1  | Code instrumentation for in-FPGA monitoring (instrumented code in bold) 84             |

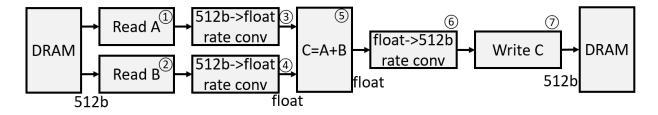

| 5.2  | Dataflow vector add connected through FIFO. Circled number is the module ID 85         |

| 5.3  | Code instrumentation for <i>Read A</i> module. Instrumented code in bold               |

| 5.4  | Instrumentation of <i>full_mtr</i> and <i>empty_mtr</i> for FIFO                       |

| 5.5  | Code for <i>full_mtr</i> logic                                                         |

| 5.6  | Distributed stall analysis network                                                     |

| 6.1  | Variable loop bound example in LU benchmark                                            |

| 6.2  | Loop unrolling for loop 2 of baseline LU code (Fig. 6.1) based on the maximum loop     |

|      | bound found in profiling                                                               |

| 6.3  | Code after applying the proposed partial unrolling and pipelining techniques to loop 2 |

|      | of Fig. 6.1                                                                            |

| 6.4  | Variable reduction example in Cholesky benchmark                                       |

| 6.5  | The computation pattern of variable reduction                                          |

| 6.6  | HLS code for loop 4 of Fig. 6.4 after transformation                                   |

| 6.7  | Baseline code for rotated integral image computation [81] used in face recognition 102 |

| 6.8  | Kogge-Stone prefix sum algorithm [73]                                                  |

| 6.9  | Proposed transformation of variable prefix sum in loop L2_2 of rotated integral image  |

|      | computation (Fig. 6.7)                                                                 |

| 6.10 | Proposed computation pattern for variable prefix sum (UF=1, d=4)                       |

| 6.11 | Overall DSE framework                                                                  |

| 7.1  | The SpMV kernel                                                                        |

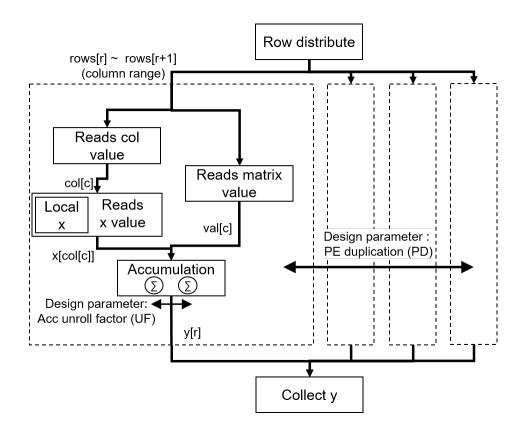

| 7.2  | Overall architecture for SpMV computation                                              |

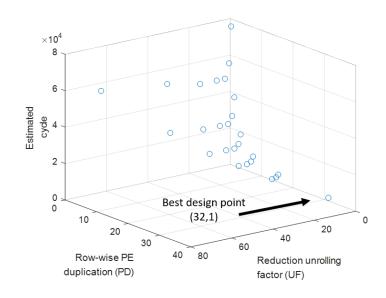

| 7.3  | Design space exploration result of SpMV (cycles per sample)                            |

### LIST OF TABLES

| 1.1  | Comparison of the proposed performance debugging frameworks                                                                    | 5  |

|------|--------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1  | Vivado HLS report for the computation part of quicksort code given in Fig. 3.1. IL, II, and TC are explained in Section 3.2.2. | 13 |

| 3.2  | List of performance debugging parameters                                                                                       | 17 |

| 3.3  | Vivado HLS report for the quicksort code given in Fig. 3.7. IL, II, and TC are explained                                       |    |

|      | in Section 3.2.2                                                                                                               | 22 |

| 3.4  | HLS report for quicksort after code modification                                                                               | 29 |

| 3.5  | Cycle estimation and simulation time for quicksort                                                                             | 31 |

| 3.6  | Read and write bandwidth and latency measured from ADM-PCIE-7V3 and ADM-                                                       |    |

|      | PCIE-KU3 using the methodology in [22]                                                                                         | 32 |

| 3.7  | External bandwidth modeling for ADM-PCIE-7V3 and ADM-PCIE-KU3                                                                  | 35 |

| 3.8  | Average cycle estimation error (absolute difference between on-board cycle measure-                                            |    |

|      | ment and HLScope-S cycle estimation) for ADM-PCIE-7V3 and ADM-PCIE-KU3                                                         |    |

|      | boards                                                                                                                         | 39 |

| 3.9  | Cycle estimation error rate of the most time-consuming among parallel DRAM-bound                                               |    |

|      | submodules for ADM-PCIE-7V3 and ADM-PCIE-KU3 boards.                                                                           | 40 |

| 3.10 | Time overhead of SW simulation flow. Consists of code instrumentation and additional                                           |    |

|      | SW simulation time (unit:s).                                                                                                   | 41 |

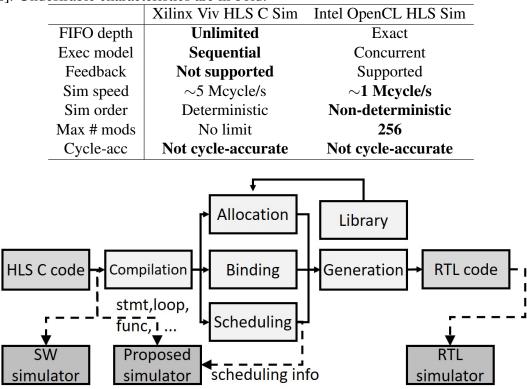

| 4.1  | Comparison of the software simulation of Xilinx Vivado HLS [130] and Intel OpenCL                                              |    |

|      | HLS [62]. Undesirable characteristics are in bold                                                                              | 46 |

| 4.2  | The FIFO communication in the C source code, the corresponding FIFO IP RTL ports                                               |    |

|      | and C variables, and the corresponding FLASH simulation code (Vivado HLS FIFO                                                  |    |

|      | APIs [130] and FIFO IP RTL ports [127] are in monospace font)                                                                  | 54 |

| 4.3 | FIFO IP behavior (assumes all FIFO APIs are evaluated at $t$ )                                 | 59  |

|-----|------------------------------------------------------------------------------------------------|-----|

| 4.4 | Debug directives for FLASH                                                                     | 73  |

| 4.5 | Simulation preparation time breakdown (preprocessing, HLS synthesis, and simulation            |     |

|     | file generation: Fig. 4.14)                                                                    | 77  |

| 4.6 | Speedup after applying optimizations (cumulative spedup shown)                                 | 78  |

| 4.7 | Simulation time comparison among Vivado HLS C simulation, Vivado HLS RTL sim-                  |     |

|     | ulation, Verilator, and FLASH simulation                                                       | 79  |

| 4.8 | Total execution cycle estimated by Vivado HLS synthesis report and FLASH, and its              |     |

|     | error rate compared to the RTL-simulated result                                                | 81  |

| 5.1 | List of probes for module under analysis                                                       | 86  |

| 5.2 | List of states in the SAN monitor 3                                                            | 89  |

| 5.3 | Overhead of in-FPGA debugging flow for various versions of quicksort.                          | 90  |

| 5.4 | Logic overhead of monitors for in-FPGA flow.                                                   | 90  |

| 5.5 | Logic overhead of instrumented FIFO                                                            | 91  |

| 5.6 | Logic overhead of SAN monitor                                                                  | 91  |

| 6.1 | Comparison of the execution cycles and the PE efficiency for loop pipelining (Sec-             |     |

|     | tion 6.2.1), loop unrolling based on the maximum bound (Section 6.2.1), and the pro-           |     |

|     | posed partial unrolling with pipelining (Section 6.2.2)                                        | 97  |

| 6.2 | Comparison of the total execution cycles, resource consumption, and latency of various loop    |     |

|     | bounds (for cases min=1, max=512) for the proposed variable-bound reduction scheme with        |     |

|     | conventional pipelining, dependence-free pipelining [62, 142], and conventional unrolling, for |     |

|     | loop 4 of the Cholesky benchmark                                                               | 102 |

| 6.3 | Comparison of the total execution cycles, resource consumption, and latency of various loop |  |  |

|-----|---------------------------------------------------------------------------------------------|--|--|

|     | bounds (for cases min=1, max=512) for the proposed variable-bound prefix sum scheme with    |  |  |

|     | conventional pipelining, unrolling [69], and Kogge-Stone algorithm [57] for loop L2_2 of    |  |  |

|     | rotated integral image                                                                      |  |  |

| 6.4 | FF/LUT estimation error rate for various R for LU benchmark                                 |  |  |

| 6.5 | Design parameters evaluated in DSE                                                          |  |  |

| 6.6 | Effect of the proposed code transformations (unit: cycles)                                  |  |  |

| 6.7 | Comparison of the performance, design space exploration speed, and the prediction           |  |  |

|     | accuracy among proposed, COMBA, and AutoAccel flows (the performance and the                |  |  |

|     | prediction error rates are that of the final output design)                                 |  |  |

| 7.1 | FPGA resource consumption of the design with the best performance                           |  |  |

| 7.2 | Comparison of the proposed performance debugging frameworks for the best SpMV               |  |  |

|     | design space (100,000 samples, FIFO depth set to 2)                                         |  |  |

| 7.3 | Performance comparison of SpMV among CPU, GPU, and FPGA implementations 123                 |  |  |

#### ACKNOWLEDGMENTS

I would like to thank, first and foremost, my advisor Professor Jason Cong for guiding me through the long journey of PhD degree. Although I have made many mistakes during the process, Professor Cong have always shown patience to lead me to the right path. Professor Cong took time to teach many things to me from topic selection, experimentation, paper writing, and presentation. It has been an unforgettable experience, and I will always try to remember his valuable lessons throughout my career.

I gratefully acknowledge the funding received from Intel and NSF (CCF-0903541, CCF-0926127, CCF-1436827, CCF-1723773, #20134321). I also thank the CDSC partners (especially Baidu, Fujitsu, Google, NEC, and VMWare) and the CAPA collaborators (from Intel and Cornell University) for the financial support and the feedback during the regular meetings. I also greatly appreciate the FPGA boards and the software donation from Xilinx.

I would like to thank the defense committee members, Professor William Hsu, Professor Miryung Kim, and Professor Tony Nowatzki, for their encouragement and the research guidance. I thank Professor Hsu for his advice on the 3D CT reconstruction acceleration work in my early PhD days. I thank Professor Kim for the insights on the concept of performance debugging in this dissertation. I thank Professor Nowatzki for his feedback on differentiating HLScope from other works.

I am grateful to Falcon Computing for providing me with a core infrastructure that I used throughout the works in my dissertation. Without the support of Falcon members, I would not have been able to implement my frameworks. I am especially grateful to Dr. Peng Zhang (formerly a post-doctoral researcher in UCLA) for teaching me how to use the ROSE and Merlin Compiler APIs. Dr. Zhang was one of my role model as a researcher and an engineer, and I was lucky to have the opportunity to learn from his eagerness and efficiency in doing research. I also thank Dr. Peichen Pan and Dr. Cody Hao Yu (also a former labmate) for the discussions and the lessons on the FPGA tools.

I would also like to thank the former and current lab members. I thank Yuze Chi for always helping me with tools, servers, and board installation. I thank Dr. Di Wu for teaching me the steps that is needed to go through the PhD course. I thank Jie Wang, Dr. Peng Wei, and Dr. Peipei Zhou for the frequent discussions and sharing tips for the research. I thank Dr. Peng Li for teaching me many functionalities of Vivado HLS and ROSE. I thank Dr. Yu-ting Chen, Dr. Zhe Chen, Professor Zhenman Fang, Nazanin Farahpour, Licheng Guo, Dr. Karthik Gururaj, Dr. Yuchen Hao, Dr. Hui Huang, Dr. Muhuan Huang, Farnoosh Javadi, Hassan Kianinejad, Jason Lau, Professor Jie Lei, Sen Li, Karl Marrett, Hyunseok Park, Weikang Qiao, Zhenyuan Ruan, Atefeh Sohrabizade, Dr. Bingjun Xiao, Xinfeng Xie, Mo Xu, and Bo Yuan for their feedback and discussion. The PhD life would have been much more difficult if it were not for your help and kindness.

I am grateful to Janice Wheeler for carefully editing all of my conference and journal submissions. I also thank Alexandra Luong for her administrative support.

I would also like to express my gratitude to my former advisors, Professor Wonyong Sung and Professor In Kyu Park, and my former mentor, Dr. Kisun You, for their lessons and guidance. They have given me the opportunity to take down this fascinating journey as a researcher. VITA

2008 Master of Science in Electrical Engineering and Computer Science, Seoul National University, Korea.

2006 Bachelor of Science in Electrical Engineering, Seoul National University, Korea.

#### PUBLICATIONS

Young-kyu Choi, J. Cong, Z. Fang, Y. Hao, G. Reinman, and P. Wei, "In-depth analysis on microarchitectures of modern heterogeneous CPU-FPGA platforms," ACM Trans. Reconf. Tech. and Syst. (TRETS), vol. 12, no. 1, Feb. 2019.

Y. Chi, Young-kyu Choi, J. Cong, and J. Wang, "Rapid cycle-accurate simulator for high-level synthesis," ACM/SIGDA Int. Symp. Field-Programmable Gate Arrays (FPGA), Seaside, pp. 178-183, Feb. 2019.

Young-kyu Choi and J. Cong, "HLS-based optimization and design space exploration for applications with variable loop bounds," in Proc. IEEE/ACM Int. Conf. Computer Aided Design (ICCAD), San Diego, Nov. 2018.

Young-kyu Choi, P. Zhang, P. Li, and J. Cong, "HLScope+: Fast and accurate performance estimation for FPGA HLS," in Proc. IEEE/ACM Int. Conf. Computer Aided Design (ICCAD), Irvine, pp. 691-698, Nov. 2017.

Young-kyu Choi and J. Cong, "HLScope: High-level performance debugging for FPGA designs," in Proc. IEEE Int. Symp. Field-Programmable Custom Computing Machines (FCCM), Napa, pp. 125-128, May 2017.

Young-kyu Choi, J. Cong, Z. Fang, Y. Hao, G. Reinman, and P. Wei, "A quantitative analysis on microarchitectures of modern CPU-FPGA platforms," in Proc. Design Automation Conference (DAC), Austin, pp. 109-114, Jun. 2016.

Young-kyu Choi and J. Cong, "Acceleration of EM-based 3D CT reconstruction using FPGA," IEEE Trans. Biomedical Circuits and Systems (TBCAS), vol. 10, no. 3, pp. 754-767, Jun. 2016.

Young-kyu Choi, J. Cong, and D. Wu, "FPGA implementation of EM algorithm for 3D CT reconstruction," in Proc. IEEE Int. Symp. Field-Programmable Custom Computing Machines (FCCM), Boston, pp. 157-160, May 2014.

# **CHAPTER 1**

## Introduction

With multicore scaling coming to an end [47], customization is often considered to be a promising solution that delivers high performance with low power consumption [30]. The efficiency of customized architectures has been demonstrated in various applications including convolution [103], medical imaging [107], neural network [135], and speech processing [56]. However, it is not practical to provide a customized solution for every application with an application-specific integrated circuit (ASIC), because ASIC manufacturing incurs high non-recurring engineering (NRE) cost. As an alternative solution, field-programmable gate array (FPGA) has gained much interest as a choice of customized acceleration platform because it provides near-ASIC performance and energy efficiency while offering reconfigurability. FPGA allows engineers to easily update and improve their designs even after initial deployment. In datacenters, FPGA can be used to hardware accelerate different needs of customers with homogeneous platforms [102]. Due to its popularity, FPGA is now being offered in various cloud computing services such as Amazon Web Service [5] and Microsoft Azure [88].

However, the low-level programming environment of FPGA often created barrier for those who did not have previous hardware design experience. FPGA designs were typically written in register-transfer level (RTL) languages such as Verilog or VHDL, which require behavior of all signals to be specified for every clock cycle. Design, verification, and optimization of applications written in low-level RTL languages became complex tasks that required expertise of experienced engineers. This naturally lead to increased development cost and prolonged time-to-market.

In order to solve this problem, high-level synthesis (HLS) tools such as Xilinx Vivado HLS [31,

130] and Intel OpenCL HLS [62] were introduced.<sup>1</sup> The HLS tools allow programmers to design FPGA applications with high-level languages such as C and OpenCL and automatically transform them into low-level FPGA designs. This reduces the programmers' burden of determining the micro-architectural details of an FPGA design and increases their productivity. It also becomes easier to change the clock frequency or port an existing design into a new platform. Moreover, the verification is simplified because HLS tools allow C-level simulation of FPGA designs.

However, one of the obstacles that prevented more widespread use of HLS can be found in the lack of performance analysis tools. Even if an initial FPGA accelerator design does not meet the required performance, it is difficult to identify the cause of the problem. In contrast, CPU and GPU programmers may use established tools like VTune [64] and NSight [94]. These tools exploit the built-in hardware performance counters and provide line-by-line profiling result. Also, detailed analysis of the performance bottleneck is provided for the programmers.

The process of identifying the performance bottleneck and finding an optimization to fix the problem is called performance debugging. Previous work on FPGA performance debugging relies on instrumenting hardware monitors into DRAM/inter-module FIFO communication channels [42, 45, 62, 71, 76, 108] or into the finite-state machine of a loop pipeline [42, 108] to measure their active/idle cycle ratios. However, their instrumentation is performed from the viewpoint of an individual module with low-level hardware description language (HDL). Such limited scope makes it difficult to identify the FPGA module that is causing another module to be idle (stalled). Instead, we propose a performance debugging methodology based on HLS. Our high-level analysis allows tracing the cause of stalls on a function or loop level, which provides more intuitive feedback to the programmers by pinpointing the bottleneck of an FPGA design.

However, the difficulty in performing performance debugging on HLS tools arises from the fact that HLS tools abstract away the hardware execution model from the programmers to shorten the learning curve and to allow quick modification of various design parameters. As a result, performance-related details such as the execution cycles of individual processing elements or the list of modules that cause other modules to stall are unavailable to the users. A programmer can

<sup>&</sup>lt;sup>1</sup>For a comprehensive list of the off-the-shelf HLS tools, the readers are referred to [75, 84, 93].

Figure 1.1: HLS development steps and the proposed performance debugging frameworks only observe a brief synthesis report and machine-generated output code, which is almost impossible to comprehend. If a programmer wanted to analyze the output code for further performance improvement, the person often has to spend many hours to identify the performance bottleneck.

In this dissertation, we propose a collection of HLS-based performance debugging frameworks for FPGA as shown in Fig. 1.1. Each debugging framework is intended to be used at a different place of the design process. The first framework is the performance estimator for HLS. Typically, an HLS user would synthesize a design and obtain the performance estimation in the HLS synthesis report, so that the user can quickly identify the performance bottleneck and restructure the code without the time-consuming bitstream generation process. However, we will show in Chapter 3 that the HLS-reported performance estimate may be inaccurate when the program has input-dependent behavior or external memory access. To solve this problem, we propose a simulation-based modeling (SBM) approach named HLScope-S. HLScope-S automatically instruments code that models the hardware-execution behavior. The model includes the external memory access behavior (e.g., DRAM bandwidth) and the loop execution behavior (e.g., initiation interval and iteration latency). The instrumentation is performed in the granularity of loops and functions to minimize the esti-

mation overhead. Next, we run the HLS software simulation on the instrumented code to reflect the input-dependent behavior on the performance estimation. This performance estimation flow is presented in Chapter 3. We also provide a detailed description of the performance debugging process in this chapter.

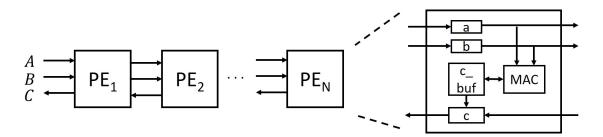

The performance estimation flow described in Chapter 3 depends on the software simulator of HLS to reflect the input-dependent behavior of the design. However, we found that the current FPGA HLS commercial software simulators sometimes produce incorrect results (details provided in Chapter 4). This results in HLScope-S to provide an inaccurate performance estimate. To solve this problem, we propose a new HLS simulation flow named FLASH. The main idea behind FLASH is to extract scheduling information from the HLS tool and automatically construct an equivalent cycle-accurate simulation model while preserving C semantics. We show that correctness of the simulation and accurateness of the performance estimation codes in loops or functions, FLASH simulates in a finer granularity of C statements. In order to accelerate the simulation speed compared to the RTL simulation, we abstract away the allocation, binding, and library information, which were found to be unnecessary for solving the incorrect result problem. The experimental result shows that FLASH runs three orders of magnitude faster than the RTL simulation. The details of the proposed framework is explained in Chapter 4.

The simulation-based flows in Chapters 3 and 4 provide reliable performance estimation when representative input dataset exists. However, in the case where the input may change at the time of FPGA deployment, on-board monitoring becomes necessary. Another problematic case is where high-level models do not exist for all components of the FPGA design. For example, a design may have an RTL sub-component or DRAM with unknown characteristics. In order to provide performance debugging capability for these cases, we propose a HLS-based on-board performance monitoring framework named HLScope-M in Chapter 5. The instrumented monitoring code is described in pure HLS C without involving RTL code, so that the integration process is simplified. In addition to the cycle extraction, we also propose a stall analysis network (SAN) that enables each module to trace the root cause of stall in on-board execution and find the performance bottleneck.

|             | HLScope-S   | FLASH          | HLScope-M      | DSE          |

|-------------|-------------|----------------|----------------|--------------|

|             | (Chapter 3) | (Chapter 4)    | (Chapter 5)    | (Chapter 6)  |

| Purpose     | Performance | Simulation     | On-board       | Design space |

| Turpose     | estimation  | Sillulation    | monitoring     | exploration  |

| Accuracy    | Approximate | Cycle-accurate | Cycle-accurate | Approximate  |

| Accuracy    | (~5% error) | Cycle-accurate | Cycle-accurate | (~5% error)  |

| Time        | 1-10 mins   | 1-10 mins      | 1-10 hours     | 0.1-1 secs   |

| Time        | 1-10 11113  | 1-10 11113     | 1-10 110013    | (per design) |

| Coverage    | FPGA+DRAM   | FPGA only      | FPGA+DRAM      | FPGA only    |

| Publication | [24]        | [18]           | [23]           | [25]         |

Table 1.1: Comparison of the proposed performance debugging frameworks

Based on the information collected from performance debugging, an FPGA designer would perform optimization. However, many different combinations of HLS directives exist, and it is difficult for designers to manually find the best configuration. Several design space exploration (DSE) frameworks for HLS tools have been recently proposed [37, 72, 100, 111, 137, 138] to solve this problem. However, one of the common limitations found in these tools is that they cannot find a design point with large speedup for applications with variable loop bounds. The reason is that loops with variable loop bounds cannot be efficiently parallelized or pipelined with simple insertion of HLS directives. Also, making highly accurate prediction of cycles and resource consumption on the entire design space becomes a challenging task because of the inaccuracy of the HLS tool cycle prediction and the wide design space. To address these challenges, we propose code transformations that increase the utilization of the compute resources for variable loops, including completely parallel computational pattern and computational patterns with loop-carried dependency (floating-point reduction and prefix sum patterns). In order to rapidly perform DSE with high accuracy, we describe a model that predicts the resource usage from the information obtained from a small number of actual HLS synthesis runs. The cycle estimation model has been derived from HLScope-S. Experiments on applications with variable loop bounds in Polybench benchmarks show that our framework outperforms current state-of-the-art DSE frameworks. This is presented in Chapter 6.

The comparison among the proposed debugging frameworks are provided in Table 1.1. As shown in the table, FLASH and HLScope-M provide cycle-accurate result. In contrast, HLScope-

S and the DSE framework are based on approximated prediction of the execution time so that the cycle estimation process is accelerated. For the time taken to apply these frameworks, HLScope-M takes most amount of time because it involves the bitstream generation process. The rest of the frameworks take similar time in the order of minutes, because they involve code transformation using ROSE infrastructure [106] and a software simulation run. Note that since the DSE process reuses the software simulation for cycle estimation of multiple design points, the time taken per design point is in the order of seconds. In terms of coverage, HLScope-S models the behavior of FPGA modules, DRAM controllers, and DRAM. Similarly, HLScope-M can monitor any type of modules. FLASH and the DSE framework are currently limited to modules that only perform computation and intra-FPGA communication, and it remains as a future work to generalize these frameworks that also model the DRAM access latency.

In order to perform quantitative comparison among the proposed frameworks, we provide a case study on sparse matrix-vector multiplication (SpMV) benchmark. This will be presented in Chapter 7. Also, concluding remarks and future work are provided in this chapter.

# **CHAPTER 2**

## **Related Works**

## 2.1 Performance Analysis Tools in CPU and GPU

Performance analysis tools have been widely used for CPUs and GPUs to help programmers with analyzing the performance bottlenecks of their programs. For example, Intel's VTune [64] is a performance analysis tool for x86 CPUs. VTune collects the profiling result on each line of code, so that the users can identify and optimize the most frequently used portion of the code. VTune also provides utilization analysis of CPU microarchitecture—such as the that of the instruction fetch and the execution units of CPU. The experience is enhanced with a graphical timeline view of the utilization. The users can also identify memory-related issues with parameters such as the cache miss rate and the effective DRAM bandwidth.

NVIDIA's NSight [94] provides a profiling result for GPU programs with details similar to that of VTune. NSight provides utilization analysis on components specific to GPUs—such as the number of warps [95] per multiprocessor or the effective shared memory bandwidth. If the performance is lower than expected, the users can refer to NSight's detailed analysis on the reason for stall—such as the memory dependency or the synchronization problems. NSight also provides a general advice on how to remove each type of stall and improve the performance.

#### 2.2 Related Works on Performance Estimation

FPGA performance estimation models are used in design space exploration (DSE) tools such as Lin-analyzer [138] and COMBA [137] to find the best design point among possible candidates. Their models predict the performance for common optimizations such as unrolling, pipelining, and array partitioning. Also, DSE flows such as Aladdin [111] can provide cycle estimation for programs with dynamic behavior using the instruction trace from simulation. However, we will explain in Section 3.2.7 why their models have limitations in accurately predicting the performance of designs actually generated by HLS tools. We will also demonstrate that HLScope-S provides the estimation result faster than the trace-based flows.

For external memory modeling, Aladdin [111] links a cycle-accurate trace-based DRAM simulator to a performance estimator, but cycle-accurate simulation takes a long time compared to the high-level modeling we propose in Section 3.2.4. Work in [9, 13] describes approximately timed transactional-level SystemC simulation with instruction set simulator (ISS), but we would like to raise the level of abstraction to a level of function call or loops, which speeds up the simulation process compared to modeling individual external memory requests. A simple high-level model for a single external memory accessor has been provided in [97], but FPGA typically has multiple processing elements competing for the shared external memory resource. Our model for multiple PE contention will be explained in Section 3.2.4.2. The work in [72] uses a statistical model to estimate the external memory latency of fetching a block, but it is uncertain that such predefined template models for block access can be generalized for arbitrary access patterns.

#### **2.3 Related Work on Simulation**

As will be explained in Chapter 4, FLASH is a software-based HLS simulator that provides cycleaccurate result. Previous work on software-based HLS simulation includes LegUp HLS [14], which provides a speedup prediction based on the profiling result of the source code and the execution cycle from its synthesis result. FlexCL [80] takes OpenCL code as input and performs dynamic profiling with a control data flow graph (CDFG) simulation for performance and power estimation. These works, however, do not guarantee cycle-accuracy like FLASH.

There are several SystemC simulators (e.g., [28, 92, 109]) that can achieve cycle-accuracy for the source code that has explicit scheduling information specified by the programmer. However, such code transformation may be too difficult for non-experts. Our flow, on the other hand, achieves cycle-accuracy for an HLS C source code without requiring user-defined scheduling information.

FLASH has a similar high-level optimization approach with transaction-level modeling (TLM) works [9, 13, 54] in a sense that both FLASH and TLM works accelerate the simulation speed by abstracting unnecessary implementation details. However, even if one tries to apply a similar strategy to optimize the HLS simulation, several issues remain. One of the issue is that, among various type of information created by HLS (e.g., allocation, binding, and scheduling information), it is unclear which one should be kept or abstracted. Another issue is how to automate the abstraction process so that even non-expert users can benefit from this approach. We address both issues in Chapter 4.

There is a class of work that accelerates the simulation of an HLS tool's output RTL code by converting the RTL code into a cycle-accurate C model [83, 113]. Mahapatra, et al. [83] report a speedup of 5X after removing the core computation and only maintaining the IO timing, but such approach cannot be used for data-dependent benchmarks. Verilator [113], on the other hand, can be used to provide a functionally correct and cycle-accurate HLS simulation as our work. Some of the techniques Verilator uses are removal of time delays, randomized unknown value, and creation of table lookups. However, the speedup in Verilator is limited because it is very difficult to *completely* remove allocation and binding information from the RTL code—whereas our approach is free from this overhead since it was never added in the first place. A quantitative comparison is presented in Section 4.8.

## 2.4 Related Works on FPGA Hardware Debugging

Commercial FPGA vendors provide logic analyzers that can be synthesized into the FPGA to extract logic values. Examples include Xilinx's Chipscope [126] and Altera's SignalTap [4]. These tools typically require users to specify the monitored signals and the trigger conditions from the RTL signal list. Trace buffers are then attached to the monitored signals. Next, the original FPGA design and the monitoring logic are synthesized into a bitstream. The bitstream is executed until

the triggering condition is met, and the content of the trace buffer is offloaded for analysis. One of the problems of using these synthesizable logic analyzers is that the manual selection from the low-level netlist may be too difficult for novice FPGA programmers.

Whereas the synthesizable logic analyzers are typically used for RTL designs, there are FPGA debugging works that target HLS designs [51–53, 89, 90]. These works maintain mapping between the variables in the C source code and the hardware registers so that the programmers can select the variables to be debugged in high-level. Similar to Chipscope and SignalTap, they store the content of the variables in trace buffers (called Event Observability Buffer in [89, 90])—however, they perform further optimizations such as storing only the data value that has changed [51] and reconstructing the data value from other variables offline [53]. After offloading the recorded data from the trace buffer, the program may be replayed as the user steps through the source code [51].

Chipscope, SignalTap, and works in [51–53, 89, 90] aim to provide correctness debugging capability. However, these work do not provide insight on solving the performance problems of an FPGA design. To address this problem, some performance debugging tools have been proposed in literature. Work in [71] profiles heterogeneous system consisting of CPUs and FPGAs to identify the bottleneck nodes with high usage rate. Intel's OpenCL HLS tool [62] profiles the communication channel between computation modules as well as the external memory ports. HwPMI [108] provides comprehensive infrastructure of performance monitors for FIFOs, bus, BRAMs, and finite-state machines (FSMs). Work in [42] targets the FSMs derived from if, while, and for statements (written in C), and measurement modules are inserted in VHDL to collect the statistics of the FSMs. Work in [120] is based on OpenCL and stores events' timestamp and their sequence numbers which can be used to measure the stall latency and monitor the memory access patterns. We will explain the difference of HLScope-M compared to these previous works in Section 5.5.

## 2.5 Related Works on HLS Design Space Exploration

The automated DSE framework for HLS is described in several published works. The work in [72] and [100] take high-level parallel patterns such as *map* and *reduce* and generate an FPGA

design based on the predefined templates and the statistical performance model. Aladdin [111] omits synthesis and RTL generation and reuses optimization across a large design space for fast exploration among ASIC accelerators. Lin-analyzer [138] takes a similar approach and further considers the FPGA-specific resources (*e.g.*, DSP, BRAM) during its scheduling. MPSeeker [139] uses Gradient Boosted Machine (GBM) technique for resource modeling and explores trade-off between fine-grain and coarse-grain parallelism. Most recently, COMBA [137] and AutoAccel [37] have been proposed. COMBA explores a comprehensive set of HLS optimization directives and finds the best configuration based on their metric-guided search. AutoAccel presents a push-button flow based on their composable, parallel, and pipeline micro-architecture. These works, however, do not guarantee finding an efficient design for applications with variable loop bounds. A quantitative comparison will be provided in Section 6.5.

## **CHAPTER 3**

# Performance Debugging with Fast and Accurate HLS Performance Estimator

In this chapter, we will first present the scope and the overall structure of our performance debugging tool, HLScope. We will describe how HLScope performs analysis in high-level semantics such as functions of loops, which is more intuitive than providing feedback from DRAM/intermodule FIFO communication channels [42, 45, 62, 71, 76, 108] or finite-state machine of a loop pipeline [42, 108]. We will next explain the performance debugging parameters that is provided by HLScope. Based on the collected parameters, HLScope evaluates the level of application optimization to identify potential performance bottleneck. This is followed by three sample debugging sessions for various versions of quicksort.

HLScope requires cycle count of each module for its analysis. It is possible to obtain this information from an on-board performance monitoring flow (HLScope-M). However, a drawback of such approach is that the FPGA bitstream generation typically takes many hours. An alternative approach is to use the performance estimate provided in the HLS tool's synthesis report. However, we will show that the synthesis report may become incomprehensible when the program has input-dependent behavior. To solve this problem, we will describe a fast and accurate HLS-based cycle estimation flow (HLScope-S) in this chapter. A high-level modeling of the hardware behavior is inserted into the C source code, and the cycle information is extracted by running a software simulation. We will describe an automated code transformation to enable this process.

#### **3.1 Performance Debugging Framework: HLScope**

#### 3.1.1 Scope and Overall Tool Structure

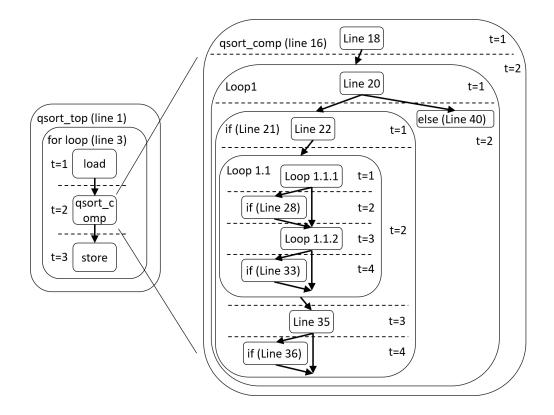

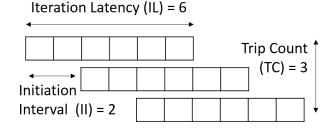

Performance debugging is a process of identifying the performance bottleneck and finding an optimization to fix the problem. We illustrate our performance debugging framework with Vivado HLS [130] because of its widespread use in FPGA designs [20, 21, 23, 32, 34, 78, 79, 79, 105, 135, 138]. Similar to the level of information given in Vivado HLS report, we expect the HLS tool to provide iteration latency (IL), initiation interval (II), and trip count (TC) (will be defined in Section 3.2.2) of loops and the latency of functions. An example of the expected cycle information for the *qsort\_compute()* function of the quicksort (Fig. 3.1 (c)) is shown in Table 3.1. We do not expect the HLS tool to provide cycle information about every line of code; for example, in the graph representation of the quicksort code in Fig. 3.2, the cycle information for the else statement in line 40 is not given in Table 3.1. Instrumentation methods to recover the missing cycle information ('?' in Table 3.1) will be extensively discussed in Section 3.2.3.

Table 3.1: Vivado HLS report for the computation part of quicksort code given in Fig. 3.1. IL, II, and TC are explained in Section 3.2.2.

| Name       | IL | II | TC |

|------------|----|----|----|

| qsort_comp | ?  | -  | -  |

| Loop 1     | ?  | -  | ?  |

| Loop 1.1   | ?  | -  | ?  |

| Loop 1.1.1 | 4  | 4  | ?  |

| Loop 1.1.2 | 4  | 4  | ?  |

As an input, HLScope takes a C code that may have Vivado HLS directives. Our tool will analyze all modules in the top function as a default – or user may specify a particular submodule of interest. Using the APIs in the ROSE compiler infrastructure [106], HLScope first transforms the input code into a tree of nested code blocks. A code block consists of multiple operations with a single program execution path. For the quicksort example in Fig. 3.1, the resulting graph is shown in Fig. 3.2. Vivado HLS will schedule functions without true data dependency to be executed in parallel– thus, HLScope analyzes the variables used in each function for data dependency detection to match Vivado HLS's schedule.

```

void qsort_top(float* dram, int batch_num, int n_per_batch ){

float lmem[LMEM_MAX];

for( int i = 0 ; i < batch_num ; i++ ){

load(dram, lmem, n_per_batch, i);

gsort_comp(lmem, n_per_batch);

store(dram, lmem, n_per_batch, i);

}</pre>

```

(a) Top C function (batch\_num=128, n\_per\_batch=1024, LMEM\_MAX=1024, `dram': external DRAM port, `lmem': local BRAM)

```

8 void load(float* dram, float lmem[LMEM_MAX],

9 int n_per_batch, int i ){

10 memcpy(lmem,dram+i*n_per_batch, n_per_batch*sizeof(float));

11 }

12 void store(float* dram, float lmem[LMEM_MAX],

13 int n_per_batch, int i ){

14 memcpy(dram+i*n_per_batch,lmem, n_per_batch*sizeof(float));

15 }

```

(b) Load and store function

```

16 void qsort_comp( float lmem[LMEM_MAX], int n_per_batch ){

17

int beg[M], end[M], i=0, L, R; float piv, swap;

18

beg[0]=0; end[0]=n_per_batch;

19

while (i>=0) { // Loop 1

//one round of reordering

20

L=beg[i]; R=end[i]-1;

// init L & R ptr

21

if (L<R) {

22

piv=lmem[L];

23

while (L<R) { // Loop 1.1

// swap until L & R meets

24

while (lmem[R]>=piv && L<R){ // Loop 1.1.1</pre>

25

#pragma HLS pipeline // decrement R until an element

26

// Less than pivot is found

R--;

27

}

28

if (L<R) { lmem[L++]= lmem[R]; }</pre>

// copy it to L

29

while (lmem[L]<=piv && L<R){ // Loop 1.1.2</pre>

30

#pragma HLS pipeline // increment L until an element

31

// Less than pivot is found

L++;

32

}

33

if (L<R) { lmem[R--]= lmem[L]; }

// copy it to R

34

}

35

lmem[L]=piv;beg[i+1]=L+1;end[i+1]=end[i];end[i++]=L;

36

if (end[i]-beg[i]>end[i-1]-beg[i-1]) { //swap qsort order

37

swap=beg[i]; beg[i]=beg[i-1]; beg[i-1]=swap;

38

swap=end[i]; end[i]=end[i-1]; end[i-1]=swap;

39

}}

40

else {

41

i--;

```

(c) Computation function

Figure 3.1: Initial unoptimized C code of non-recursive quicksort (modified from [49])

Figure 3.2: Dependency graph for  $qsort\_comp()$  given in Fig. 3.1 (c). The dotted line denotes synchronization barriers, and t denotes time frames divided by synchronization barriers.

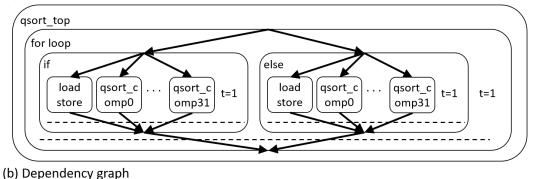

For simplified execution control, Vivado HLS will schedule all submodules to wait for the completion of other submodules executed in parallel. In the example dependency graph for a modified version of the quicksort in Fig. 3.3 (optimization will be explained in Section 3.1.3), loadstore()function (combines load() and store() of Fig. 3.1) and unrolled functions of  $qsort\_comp()$  execute in parallel. After finishing execution, they will wait for all other functions to terminate as well. This is similar to the barrier synchronization in GPU [95], and from now on, we will simply refer to it as *synchronization*. Synchronization is expressed in the dependency graph with the dotted lines as in Fig. 3.2 and Fig. 3.3. To keep track of the execution order, we also assigned time frames t to the groups of blocks that execute in parallel.

In order to avoid the overhead of waiting for other modules to complete (*synchronization overhead*), the user may use the dataflow pragma (*#pragma HLS dataflow* [130]) and FIFO communication channel (*hls::stream<variable type>* [130]). This will allow modules with data dependency

```

void qsort_top(float* dram, int batch_num, int n_per_batch ){

float lmem0[UNROLL_FACTOR][LMEM_MAX];

//partitioned BRAM for parallel

float lmem1[UNROLL_FACTOR][LMEM_MAX];

//access, UNROLL_FACTOR=32

#pragma HLS ARRAY_PARTITION variable="lmem0" complete dim='1'

#pragma HLS ARRAY_PARTITION variable="lmem1" complete dim='1'

for( int i = 0 ; i < batch_num ; i++ ){</pre>

if (i\%2 == 0) //in even i, Lmem0 for memory access and Lmem1 for compute

loadstore(dram, lmem0, n_per_batch, i);

for( int j = 0; j < UNROLL FACTOR; j++ ){

#pragma HLS unroll // 32 duplicated compute PEs

qsort_comp(lmem1[j], n_per_batch);

} }

else{

// in odd i, Lmem1 for memory access and Lmem0 for compute

loadstore(dram, lmem1, n_per_batch, i);

for( int j = 0 ; j < UNROLL_FACTOR ; j++ ){</pre>

#pragma HLS unroll // 32 duplicated compute PEs

qsort_comp(lmem0[j], n_per_batch);

```

Figure 3.3: Quicksort code and corresponding dependency graph after applying double buffering and unrolling. loadstore() function combines the load() and store() function given in Fig. 3.1, and  $qsort\_comp()$  function is the same as that of Fig. 3.1.

to continue with the execution as soon as the input data is available and the output buffer is not full. From now on, we will refer to this module dependency as *parallel by dataflow*. In the dependence graph, we place no barrier between the modules and assume they are executed in the same time frame.

After converting the program into a graph structure, HLScope-S (Section 3.2) measures the number of cycles for each block. HLScope-M (to be presented in Chapter 5), on the other hand, measures the number of cycles only at a function level because of the monitoring logic overhead (Table 5.4). Note that the measurement can be performed at a finer granularity in HLScope-S, because the simulation time overhead is small (~4%, as shown in Table 3.10). In addition to the cycle measurement, HLScope also record the number of DRAM transactions in bytes using the Vivado HLS software simulation with a real input testbench. Based on these measurements, HLScope computes several performance debugging parameters that will be explained in the next subsection.

#### **3.1.2** Performance Debugging Parameters

HLScope provides three groups of performance debugging parameters as shown in Table 3.2. The first group indicates a module's importance for performance debugging.

| Table 3.2: List of performance debugging parameters |                                                      |  |  |  |  |

|-----------------------------------------------------|------------------------------------------------------|--|--|--|--|

| Probe name                                          | Description                                          |  |  |  |  |

| cycle                                               | Execution cycle of each module                       |  |  |  |  |

| PCP                                                 | Is this module on performance critical path?         |  |  |  |  |

| LUT/DSP/BRAM                                        | LookUp Table / DSP48 / Block RAM                     |  |  |  |  |

| stall rate                                          | 1 - usage rate of computational resource             |  |  |  |  |

| DBW                                                 | DRAM bandwidth                                       |  |  |  |  |

| ADBW                                                | Aggregate DBW among all modules executed in parallel |  |  |  |  |

| Reason for stall                                    | Stall type & the name of module causing stall        |  |  |  |  |

Parameter *cycle* is the total execution cycle of each module. Cycle information is obtained from the in-FPGA flow (Section 5.2 and Section 5.3) or the simulation flow (Section 3.2.3 and Section 3.2.4). We exclude the period when the module has been stalled due to other modules. Assuming a hierarchical structure of code blocks such as Fig. 3.2 and Fig. 3.3, HLScope will

add the cycle estimate for a child block to its parent block depending on the static dependency analysis of the code. There are three possibilities: serial, parallel, and parallel by dataflow. If true dependency exists between blocks, they can be executed in a serial manner and will be assigned to a different time frame. The execution time of the child blocks  $c(t_c)$  will be added to its parent  $p(t_p)$  as:

$$t_p = \sum_c t_c \tag{3.1}$$

If there is no dependency, the blocks can execute in parallel and will be assigned to the same time frame. The execution time is the maximum of the parallel blocks:

$$t_p = \max_c \left( t_c \right) \tag{3.2}$$

For the modules running in parallel by dataflow (explained in Section 3.1.1), the execution time is also bounded by the slowest block (Eq. 3.2). The difference is that they do have dependency between them, so it takes  $\sum_{c} IL_{c}$  for data to traverse from beginning to end:

$$t_p = \max_c \left( t_c \right) + \sum_c I L_c \tag{3.3}$$

Also, the modules will be assigned to the same time frame.

Using the module dependency and the cycle information, we mark each module as to whether it has an effect on the overall performance or not. We refer to this parameter as *performance critical path (PCP)*. The serially-executing modules are classified 'yes' in PCP. If there are several parallel-executing modules in a time frame, a module with the longest execution time will be classified 'yes' in PCP. Also, going top-down hierarchically, submodules of a module marked 'yes' will be further analyzed in a similar way for the critical path analysis; submodules in all other modules are marked 'no'. For the modules running in parallel by dataflow, we only mark the module with the longest execution time in a time frame as 'yes' and the rest as 'no'.

Next, HLScope report shows compute resource (LUT/BRAM/DSP) for each function. This is obtained from the HLS synthesis report. A function with large LUT/BRAM/DSP consumption and

a large stall rate can be identified as wasting the compute resource. This could be problematic if the application is compute-intensive.

The next group of parameters provided by HLScope indicates the usage rate of resources. The first parameter is *stall rate*. The stall rate  $stall_i$  of each module is computed by:

$$stall_i = 1 - t_i / t_{tot} \tag{3.4}$$

where  $t_i$  is each module *i*'s execution time and  $t_{tot}$  is the total execution time of all modules. This rate shows the usage rate of FPGA computational resources.

Next, we determine DRAM bandwidth (DBW). It is computed by dividing the amount of data written to or read from the external memory. The number of transferred bytes is obtained from the software simulation that will be explained in Section 3.2.4. We also provide the aggregated DRAM bandwidth (ADBW) which computes the combined DRAM bandwidth among all modules executed in parallel. Note that the DRAM access is only measured in the software simulation flow, HLScope-S. Thus, the performance debugging based on the on-board flow, HLScope-M, does not provide DBW and ADBW parameter values.

Finally, we provide the reason for the stall and the name of the module that is causing the stall. If a module is waiting for data from another module, it is classified as a dependency stall. It includes stalls due to other modules executed in serial or stalls in inter-module communication among parallel-executing modules by dataflow. If a module is waiting for other parallel-executing modules to finish, the stall is classified as a synchronization stall. A module could have multiple stall reasons depending on its place in HLS module hierarchy– an example will be shown in Fig. 3.5, where *qsort\_comp* PE0 has 2.2% synchronization stall waiting for *qsort\_comp* PE27 to finish. It also has 25.2% dependency stall for both *load* and *store* because *qsort\_comp* PE 0-31, *load*, and *store* are executed in serial.

Based on the reason for stall provided by HLScope, the programmer can decide which module to focus his/her attention on for further optimization. An example performance debugging session will be presented in the next section.

# 3.1.3 Performance Debugging for Quicksort

In this section, we will demonstrate performance optimization steps for the quicksort example based on HLScope. We assume that we have 128 sets of 1024 single-precision floating-point numbers to be sorted.

Fig. 3.4 lists the performance debugging parameters collected from initial unoptimized quicksort (code: Fig. 3.1a, dependency graph: Fig. 3.2). The cycle information has been collected from the software simulation flow, HLScope-S. The most obvious performance problem that we can identify from the report is that *qsort\_comp()* takes most (96.5%) of the execution time, and probably should be the target for optimization. Note that the stall rate is very high (98.2%/98.3%) for load() and store(), but does not cause too much computation resource to remain idle since the LUT and DSP usage is small (481/445 and 4/4).

| <pre>for( int i = 0 ; i &lt; batch_num ; i++ ){</pre> | Cycle PCP  LUT  BRAM DSP Stall DBW  ADBW Reason for stall           |

|-------------------------------------------------------|---------------------------------------------------------------------|

| <pre>load(dram,lmem,n_per_batch,i);</pre>             | 145k  Yes  481  0  4  98.2  724M 724M comp(96.5,dep),store(1.7,dep) |

| <pre>qsort_comp(lmem, n_per_batch);</pre>             | 7.75M Yes  2538 3  0  3.5  0  0  load(1.8,dep),store(1.7,dep)       |

| <pre>store(dram,lmem,n_per_batch,i);</pre>            | 140k  Yes  445  0  4  98.3  748M 748M comp(96.5,dep),load(1.8,dep)  |

| }                                                     |                                                                     |

Figure 3.4: Performance debugging parameters collected from the initial unoptimized version of quicksort. Parameter derived from HLScope-S result. (batch\_num=128, n\_per\_batch=1024, 'dram': external DRAM port, 'lmem': local BRAM).

Based on the analysis from the initial version, we apply unrolling on the compute PEs. The result is shown in Fig. 3.5. We can confirm that the *qsort\_comp()* function indeed takes a considerably shorter time—from 7.75M cycles to 231–258k cycles. For the nodes on the time-critical path (*load()*, *qsort\_comp()* PE 27, *store()*), however, the analysis shows that the proportion of *load()* and *store()* increased to 25.2%, respectively. This suggests that memory access has now become a major stall reason. A hint for solution can be found in the aggregate DRAM BW. During *qsort\_comp()*, the ADBW is 0, which means that DRAM is not being utilized at all. This suggests that modules that do use the DRAM, *load()* and *store()*, can probably be overlapped in *qsort\_comp()*.

For memory and compute overlapping, we perform double buffering optimization. The code after optimization was shown in Fig. 3.3, and the corresponding report is presented in Fig. 3.6.

| float local data[UNROLL FACTOR]; //partitioned BRAM for parallel access, UNROLL_FACTOR=32 |                                                      |      |      |     |       |      |      |                                            |

|-------------------------------------------------------------------------------------------|------------------------------------------------------|------|------|-----|-------|------|------|--------------------------------------------|

| #pragma HLS ARRAY PARTITION variable="lmer                                                | #pragma HLS ARRAY PARTITION variable="lmem" complete |      |      |     |       |      |      |                                            |

|                                                                                           | ,<br>ycle PCP                                        | LUT  | BRAM | DSP | Stall | DBW  | ADBW | Reason for stall                           |

| <pre>for( int i = 0 ; i &lt; batch_num ; i++ ){</pre>                                     |                                                      |      | 1    | Í   |       | 1    |      |                                            |

| load( dram, 1mem,);   13                                                                  | 32k Yes                                              | 3017 | 0    | 4   | 74.8  | 797M | 797M | comp27(49.5,dep),store(25.2,dep)           |

| <pre>for( int j = 0 ; j &lt; UNROLL_FACTOR ; j++</pre>                                    | + ){                                                 |      |      |     |       |      |      |                                            |

| <pre>#pragma HLS unroll // 32 duplicated comput</pre>                                     | te PEs                                               |      | 1    | 1   |       |      |      |                                            |

| <pre>qsort_comp(lmem[j]); //PE0   24</pre>                                                | 47k  No                                              | 2538 | 3    | 0   | 52.6  | 0    | 0    | ld(25.2,dep),comp27(2.2,sync),st(25.2,dep) |

| //PE7   23                                                                                | 31k  No                                              | 2538 | 3    | 0   | 55.7  | 0    | 0    | ld(25.2,dep),comp27(5.3,sync),st(25.2,dep) |

| //PE27   25                                                                               | 58k  Yes                                             | 2538 | 3    | 0   | 50.5  | 0    | 0    | ld(25.2,dep),st(25.2,dep)                  |

| }                                                                                         |                                                      |      |      |     |       |      |      |                                            |

| store( dram, lmem,);   13                                                                 | 31k  Yes                                             | 5809 | 0    | 4   | 74.8  | 798M | 798M | comp27(49.5,dep),load(25.2,dep)            |

| }                                                                                         |                                                      |      |      |     |       |      |      |                                            |

Figure 3.5: Performance debugging parameters after unrolling qsort\_comp() function 32 times. Some PEs not shown for brevity.