## $\begin{array}{c} \text{UNIVERSITY OF CALIFORNIA,} \\ \text{IRVINE} \end{array}$

# Resilient On-Chip Memory Design in the Nano Era ${\bf DISSERTATION}$

submitted in partial satisfaction of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

in Computer Science

by

Abbas BanaiyanMofrad

Dissertation Committee: Professor Nikil Dutt, Chair Professor Alex Nicolau Professor Alex Veidenbaum

### **DEDICATION**

$\label{eq:constrain} \textit{To my wife Marjan}$  whom provided me the necessary strength to pursue my dreams.

### TABLE OF CONTENTS

|               | Pag                                                 | zе |

|---------------|-----------------------------------------------------|----|

| LIS           | T OF FIGURES                                        | vi |

| LIS           | T OF TABLES                                         | ix |

| AC            | KNOWLEDGMENTS                                       | x  |

| CU            | RRICULUM VITAE                                      | ii |

| $\mathbf{AB}$ | STRACT OF THE DISSERTATION x                        | V  |

| 1 l           | Introduction                                        | 1  |

| 1             | 1.1 Nano Era Design Trends and Challenges           | 1  |

|               | 1.1.1 Technology Trend                              | 1  |

|               | 1.1.2 Chip Design Trend                             | 2  |

|               | 1.1.3 Application Trend                             | 2  |

| 1             | 1.2 Memories and Errors                             | 3  |

| 1             | 1.3 State-of-the-art Research Efforts               | 5  |

| 1             | 1.4 Motivation                                      | 7  |

| 1             | 1.5 Thesis Contributions                            | 10 |

| ]             | 1.6 Thesis Organization                             | 14 |

| 2 1           | Flexible and Low-Cost Fault-tolerant Cache Design 1 | .5 |

| 2             | 2.1 Introduction $\dots$ 1                          | 15 |

| 2             |                                                     | 19 |

|               | 1                                                   | 19 |

|               | O I                                                 | 20 |

|               | 1                                                   | 21 |

| 2             |                                                     | 23 |

|               | 2.3.1 Proposed Architecture                         | 23 |

|               | 2.3.2 Evaluation                                    | 32 |

| 2             | 2.4 EEC: Embedded Erasure Coding                    | 11 |

|               | 2.4.1 Preliminaries                                 | 11 |

|               | 2.4.2 Proposed EEC                                  | 13 |

|               | 2.4.3 Evaluation                                    | 18 |

| 2             | 2.5 Summary                                         | 55 |

| 3 | Sca  | able Fault-tolerant Cache Design in CMPs 56             |

|---|------|---------------------------------------------------------|

|   | 3.1  | Introduction                                            |

|   | 3.2  | Related Work and Motivation                             |

|   | 3.3  | RESCUE                                                  |

|   |      | 3.3.1 Baseline Architecture                             |

|   |      | 3.3.2 RESCUE Overview                                   |

|   |      | 3.3.3 RESCUE Remapping Policies                         |

|   |      | 3.3.4 Evaluation                                        |

|   |      | 3.3.5 Quantitative Comparison to Alternative Techniques |

|   |      | 3.3.6 Experimental Results                              |

|   | 3.4  | Summary                                                 |

| 4 | Inte | rconnect-aware Resilient Cache Design 94                |

|   | 4.1  | Introduction                                            |

|   | 4.2  | Related Work                                            |

|   |      | 4.2.1 Fault-tolerant Cache Design                       |

|   |      | 4.2.2 Fault-tolerant NoC design                         |

|   |      | 4.2.3 Memory Reliability in Multi/Many-cores            |

|   | 4.3  | NoC-based Fault-tolerance of LLC                        |

|   | 1.0  | 4.3.1 Basic Idea and Baseline Architecture              |

|   |      | 4.3.2 Proposed Architecture                             |

|   |      | 4.3.3 Evaluation                                        |

|   |      | 4.3.4 Results                                           |

|   | 4.4  | CoDEC                                                   |

|   | 7.7  | 4.4.1 Background and Motivation                         |

|   |      | 4.4.2 CoDEC Overview                                    |

|   |      | 4.4.3 Evaluation                                        |

|   |      | 4.4.4 Experimental Results                              |

|   | 4.5  | Summary                                                 |

| 5 | Dal  | exing Error Resiliency in On-chip Memories 143          |

| 9 |      | Introduction                                            |

|   | 5.1  | 5.1.1 Cost of Guard-banding                             |

|   |      |                                                         |

|   |      | 11 0                                                    |

|   |      | 9                                                       |

|   | r 0  |                                                         |

|   | 5.2  | Related Work                                            |

|   |      | 5.2.1 Exploiting Memory Variability                     |

|   | - 0  | 5.2.2 Approximate Computing                             |

|   | 5.3  | Relaxed Cache                                           |

|   |      | 5.3.1 Hardware Support                                  |

|   | - 1  | 5.3.2 Software Support                                  |

|   | 5.4  | Experimental Evaluation                                 |

|   |      | 5.4.1 Experimental Setup                                |

|   |      | 5.4.2 Benchmarks                                        |

|    |       | 5.4.3 Results                                         | 160 |

|----|-------|-------------------------------------------------------|-----|

|    | 5.5   | Summary                                               | 163 |

| 6  | Syst  | tem-wide Memory Resiliency Design Space Exploration 1 | 64  |

|    | 6.1   | Introduction                                          | 164 |

|    | 6.2   | Background                                            | 167 |

|    |       | 6.2.1 Reliable Memory Design                          | 167 |

|    |       | 6.2.2 Design Space Exploration                        | 168 |

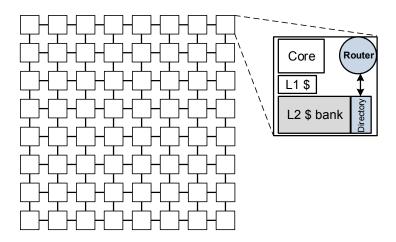

|    |       | 6.2.3 Exemplar Many-core Architecture                 | 169 |

|    |       |                                                       | 169 |

|    | 6.3   |                                                       | 172 |

|    |       | 6.3.1 Reliability Clustering                          | 172 |

|    | 6.4   |                                                       | 173 |

|    |       | 6.4.1 Experimental Setup                              | 174 |

|    |       | 6.4.2 Design Space Exploration Studies                | 175 |

|    |       |                                                       | 176 |

|    | 6.5   |                                                       | 183 |

| 7  | Con   | nclusion and Future Work                              | 84  |

|    | 7.1   | Conclusion                                            | 184 |

|    | 7.2   | Future Work                                           | 185 |

| Bi | bliog | graphy 1                                              | 89  |

### LIST OF FIGURES

|            |                                                                                                                    | Page    |

|------------|--------------------------------------------------------------------------------------------------------------------|---------|

| 1.1<br>1.2 | Memory Abstractions, Errors, and Opportunities                                                                     | 4<br>10 |

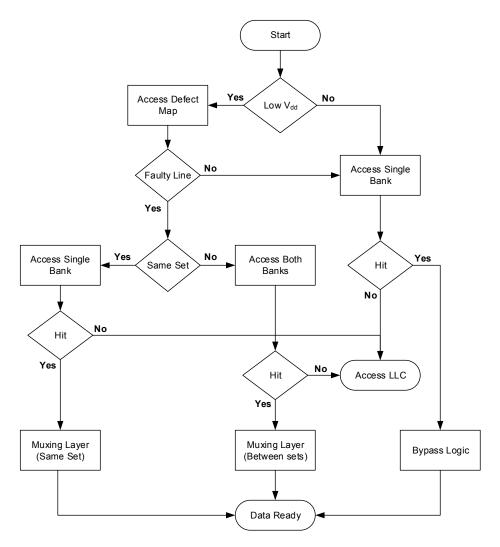

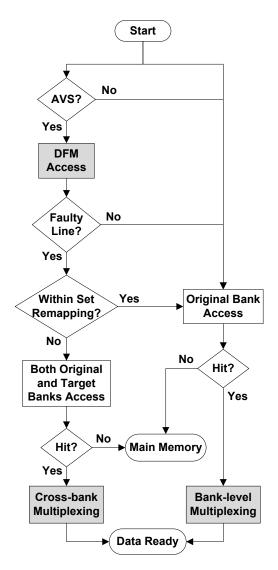

| 2.1        | FFT-Cache Access Flowchart                                                                                         | 25      |

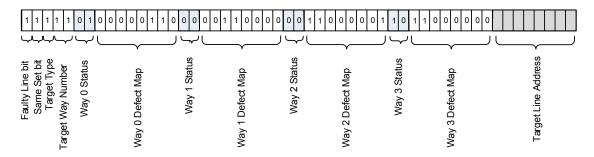

| 2.2        | Details of a row of FDM                                                                                            |         |

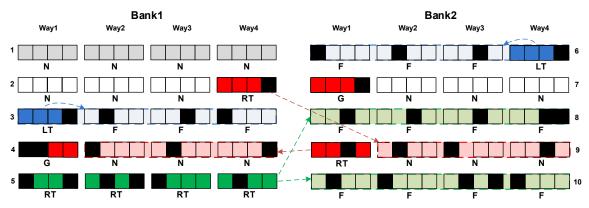

| 2.3        | An example of FDM configuration and remapping for a given distribution of faults in a 4-way set associative cache  | 30      |

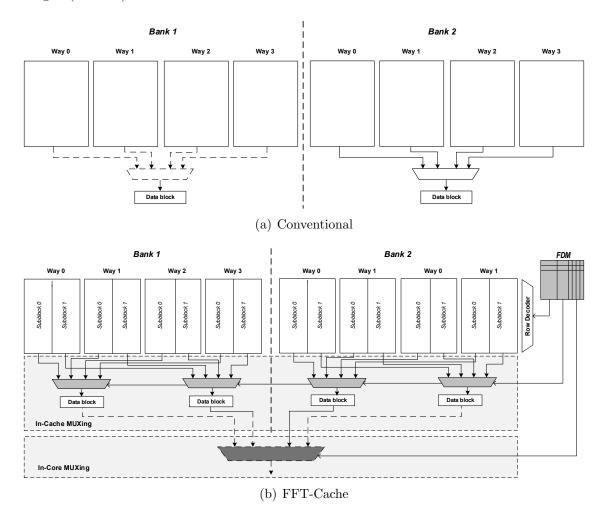

| 2.4        | Architecture details of (a) a conventional 4-way set associative cache, (b) the                                    | 30      |

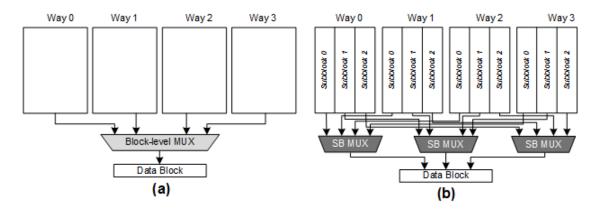

|            | proposed FFT-Cache with FDM and 2 sub-blocks per block                                                             | 31      |

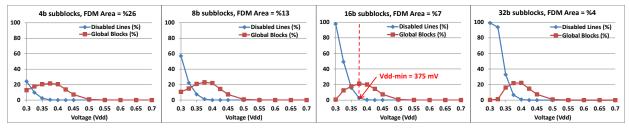

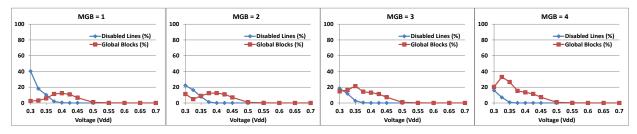

| 2.5        | The effect of changing one design parameter of L1 FFT-Cache while fixing                                           |         |

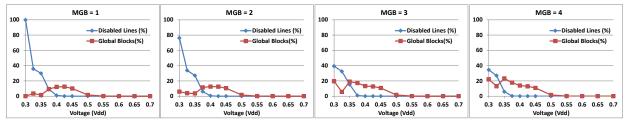

| 2.0        | other parameters for different Vdd values.                                                                         | 35      |

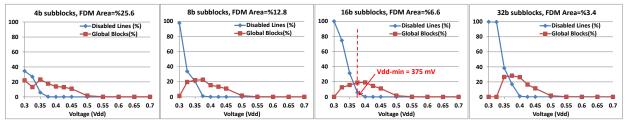

| 2.6        | The effect of changing one design parameter of L2 FFT-Cache while fixing other parameters for different Vdd values | 36      |

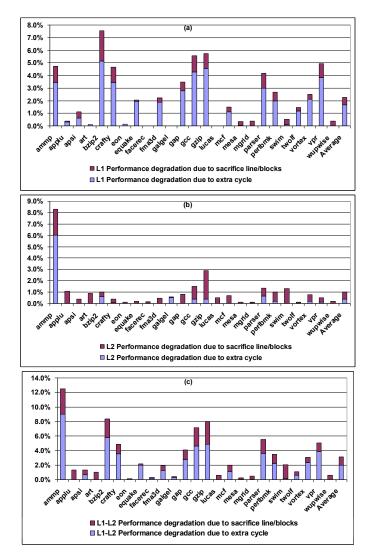

| 2.7        | Processor performance degradation when applying FFT-Cache for (a) L1 (b)                                           | 50      |

|            | L2 and (c) L1 and L2 at the same time                                                                              | 37      |

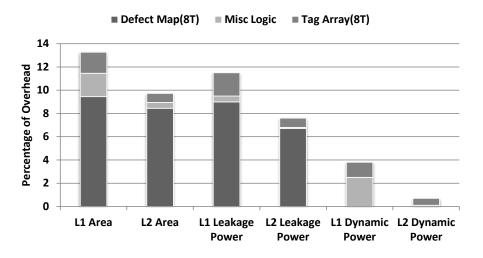

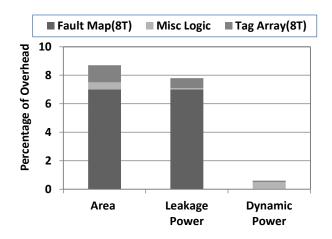

| 2.8        | Power and Area overheads of FFT-Cache                                                                              | 38      |

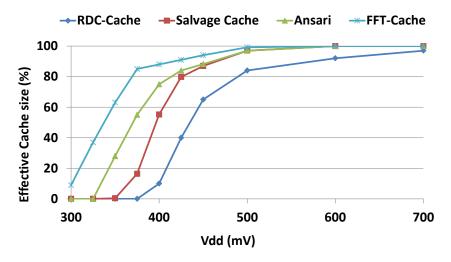

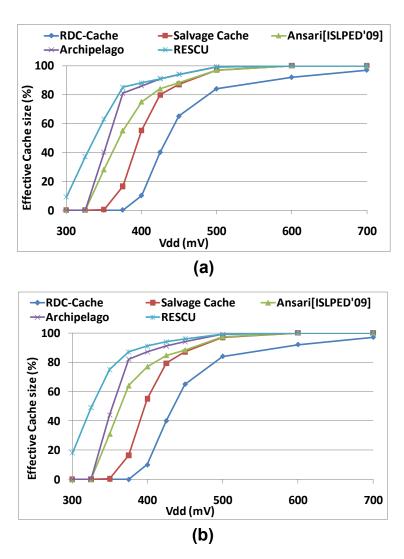

| 2.9        | Comparison of effective cache size for different fault-tolerant techniques                                         | 39      |

| 2.10       |                                                                                                                    | 10      |

| 9 11       | ities in a 45 nm SRAM Array                                                                                        |         |

|            | A sample parity-based erasure code with one redundant block                                                        |         |

|            | A 4-way L1 cache architecture protected with EEC that shows the updated                                            | 10      |

|            | write operation in three steps                                                                                     | 46      |

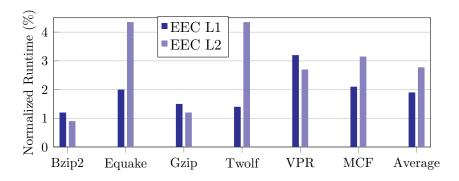

| 2.14       | Performance overhead of EEC for L1 and L2 caches on Alpha processor                                                | 51      |

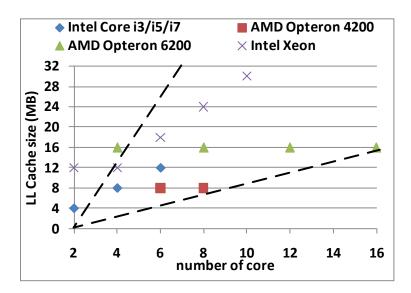

| 3.1        | Empirical data for the cache size per core across various CMP architecture                                         | 62      |

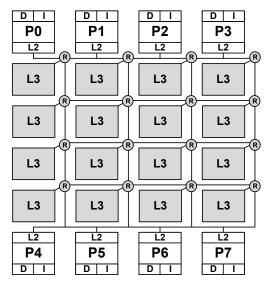

| 3.2        | Baseline 8 processor CMP structure                                                                                 |         |

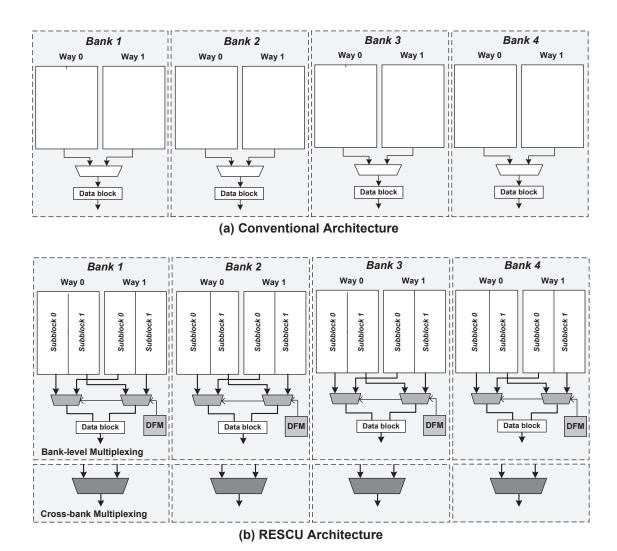

| 3.3        | Architecture details of (a) a conventional 4-banked 2-way set associative cache,                                   |         |

|            | (b) the proposed RESCUE with DFM and 2 sub-blocks per line                                                         | 66      |

| 3.4        | RESCUE cache access flowchart                                                                                      |         |

| 3.5        | DFM initialization algorithm.                                                                                      |         |

| 3.6        | DFM configuration algorithm.                                                                                       | 70      |

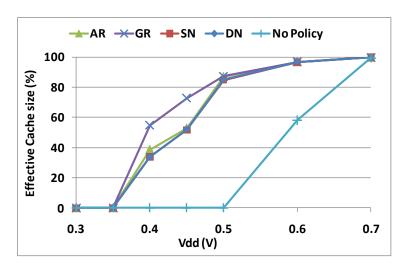

| 3.7        | Effective cache size for different techniques with the (a) two banks and (b) four banks LLC                        | 74      |

|            |                                                                                                                    | 14      |

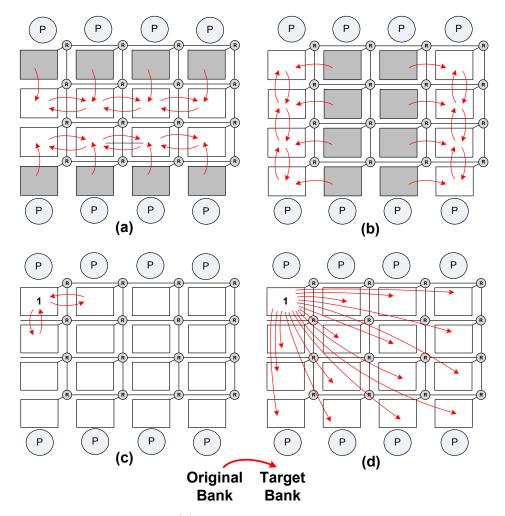

| 3.8   | Example showing the (a)DNUCA optimized scheme with remapping limited to one bank with 1 hop (b)SNUCA optimized scheme with remapping limited    |          |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|       | to one bank with 1 hop (c)Adjacent mapping scheme (d)Global mapping scheme.                                                                     | 76       |

| 3.9   | Area, leakage, and dynamic power overheads of RESCUE for an 8-core CMP                                                                          |          |

|       | with 16 LLC banks in 45nm                                                                                                                       | 82       |

| 3.10  | Effective cache size after applying RESCUE policies                                                                                             | 85       |

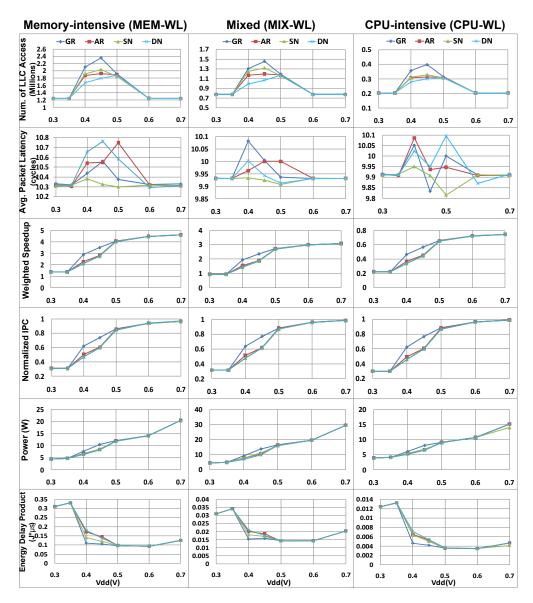

| 3.11  | Sensitivity studies of RESCUE policies across various workloads                                                                                 | 86       |

| 3.12  | v O                                                                                                                                             |          |

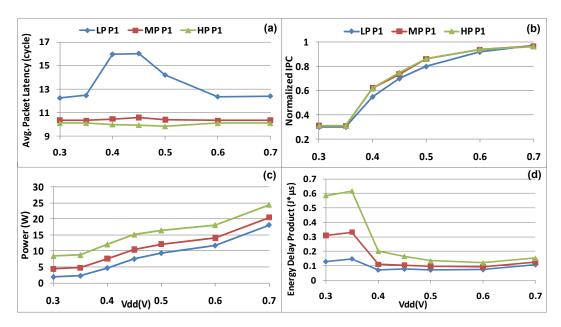

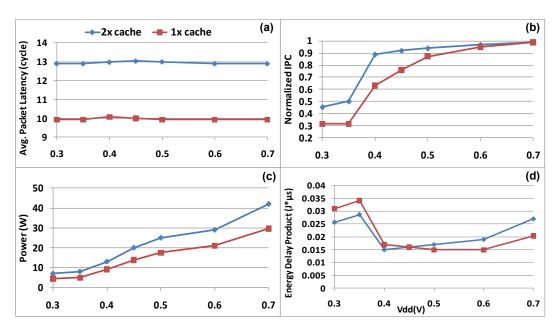

|       | Latency (a), Normalized IPC (b), Total Power (c), and EDP (d)                                                                                   | 88       |

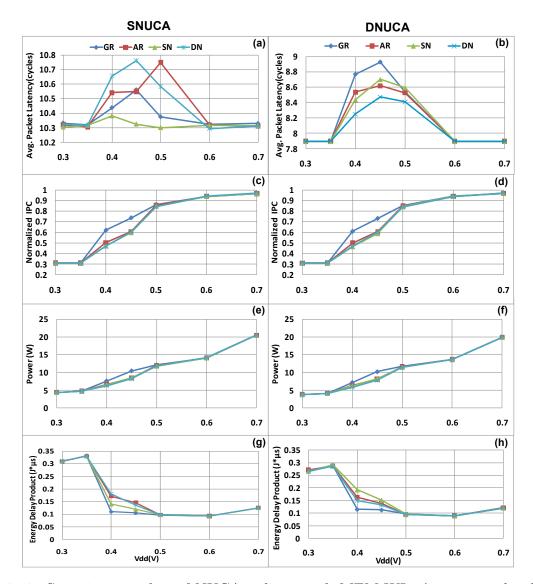

| 3.13  | Sensitivity studies of NUCA policies with MEM-WL; Average packet latency (1st row), normalized IPC (2nd row), total power consumption(3rd row), |          |

| 0.4.4 | EDP(4th row).                                                                                                                                   | 89       |

| 3.14  | Sensitivity studies of Cache size over-provisioning with MIX-WL; Average                                                                        |          |

|       | packet latency (a), normalized IPC (b), total power consumption (c), and                                                                        | 0.0      |

| 0.15  | EDP (d)                                                                                                                                         | 90       |

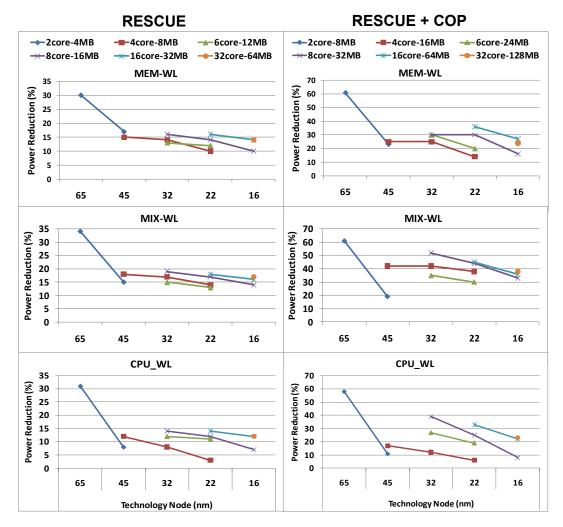

| 3.15  | Power reduction across process technology nodes over all organizations and policies with MEM-WL, MIX-WL, and CPU-WL when applying RESCUE        |          |

|       | (left) and RESCUE+COP (right)                                                                                                                   | 91       |

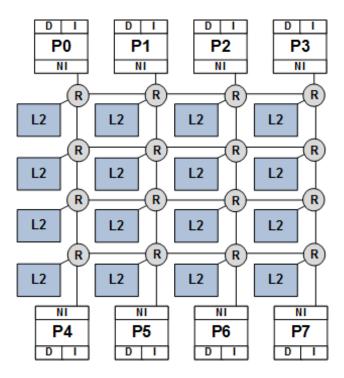

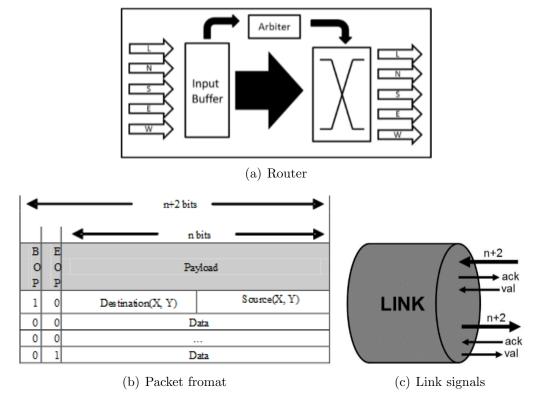

| 4.1   | Baseline NoC architecture                                                                                                                       | 102      |

| 4.2   |                                                                                                                                                 | $10^{2}$ |

| 4.3   |                                                                                                                                                 | 107      |

| 4.4   |                                                                                                                                                 | 11(      |

| 4.5   |                                                                                                                                                 | 111      |

| 4.6   |                                                                                                                                                 | 112      |

| 4.7   | Cache bank architecture: (a) A conventional 4-way set-associative cache bank;                                                                   |          |

|       |                                                                                                                                                 | 112      |

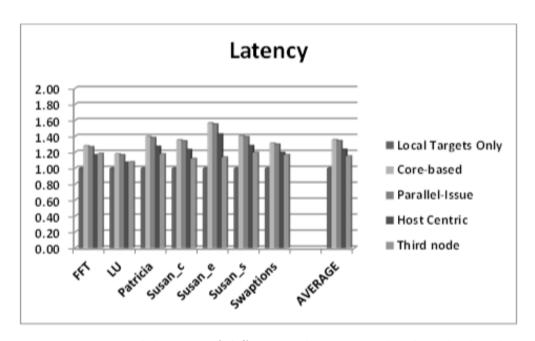

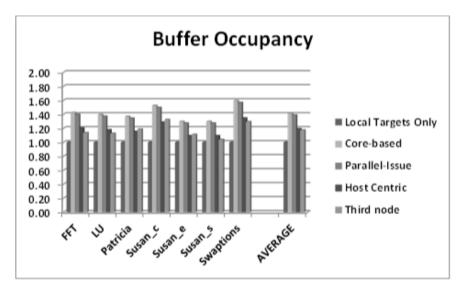

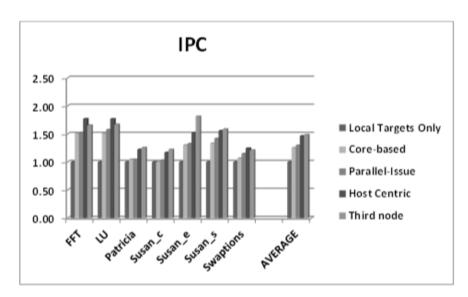

| 4.8   | Network latency of different policies normalized to the baseline                                                                                | 117      |

| 4.9   |                                                                                                                                                 | 118      |

| 4.10  | Network latency of different policies normalized to the baseline                                                                                | 119      |

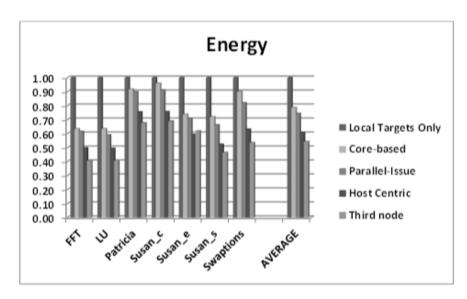

| 4.11  | Energy of different policies normalized to the baseline                                                                                         | 120      |

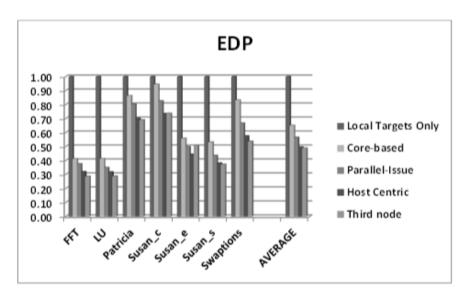

| 4.12  | Energy-delay product of different polices normalized to the baseline                                                                            | 121      |

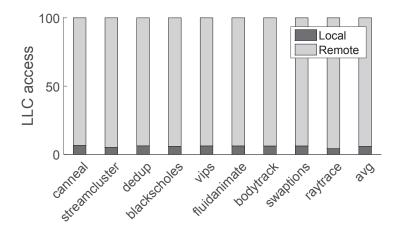

| 4.13  | Percentage of LLC remote vs local accesses in a 16 MB shared LLC                                                                                | 124      |

|       | Ų į                                                                                                                                             | 124      |

|       | 1                                                                                                                                               | 125      |

|       |                                                                                                                                                 | 127      |

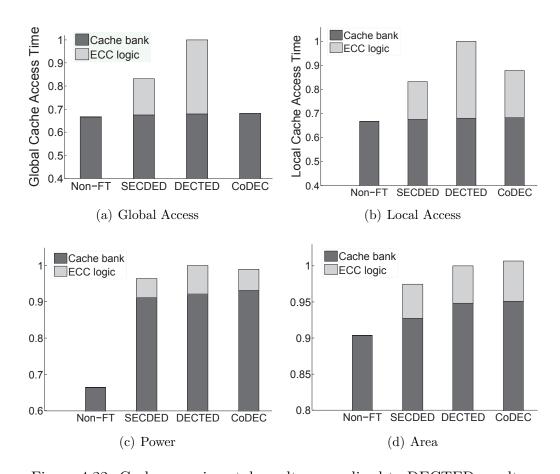

| 4.17  | The architecture of an ECC-protected LLC bank in the Conventional and                                                                           |          |

|       | 11                                                                                                                                              | 129      |

| 4.18  | Data flow of LLC block through the network in Conventional vs. CoDEC approach                                                                   | 130      |

| 4.19  |                                                                                                                                                 | 132      |

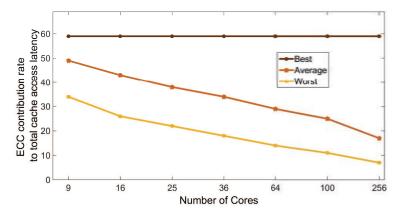

|       | <u>*</u>                                                                                                                                        | 134      |

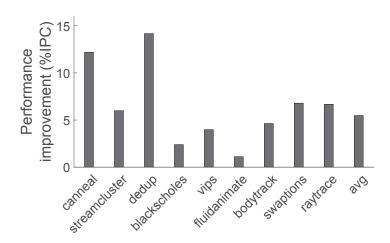

|       | Performance (IPC) improvement of a system with CoDEC LLC, normalized                                                                            |          |

|       |                                                                                                                                                 | 137      |

| 4.22  | Cache experimental results normalized to DECTED results                                                                                         | 137      |

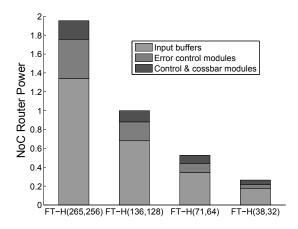

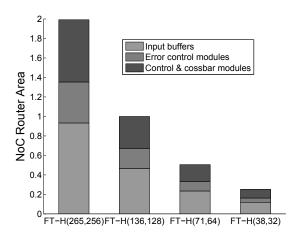

|                   | Power consumption of NoC router's major blocks for various ECC sizes Area of NoC router's major blocks for various ECC sizes                                                                                                                                                                                                                                                                                                          | 139<br>140 |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

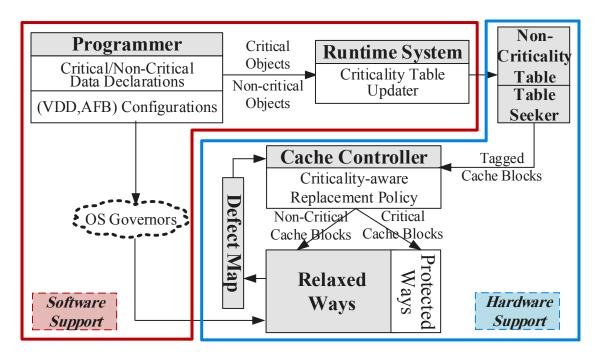

| 5.1               | High-level diagram showing HW/SW components of Relaxed Cache and their                                                                                                                                                                                                                                                                                                                                                                |            |

|                   | interactions                                                                                                                                                                                                                                                                                                                                                                                                                          | 151        |

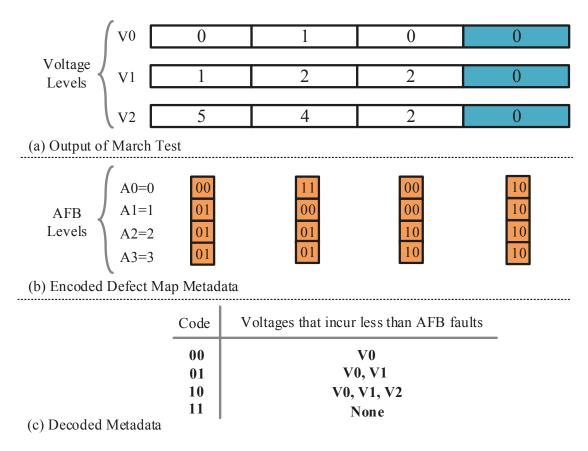

| 5.2               | A Sample 4-way Cache with VDD=580mV and AFB=4                                                                                                                                                                                                                                                                                                                                                                                         | 152        |

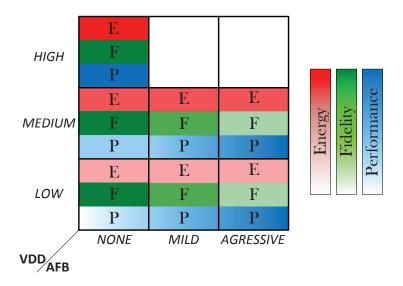

| 5.3<br>5.4        | Encoding and decoding defect map info in Relaxed Cache Abstracting Relaxed Cache knobs up to metrics familiar to a software programmer (i.e., performance, fidelity, and energy consumption). Note that (VDD = High, AFB = Mild) and (VDD = High, AFB = Aggressive) combi-                                                                                                                                                            | 153        |

|                   | nations are sub-optimal, hence not applicable                                                                                                                                                                                                                                                                                                                                                                                         | 157        |

| 5.5               | A sample code showing programmer's data criticality declarations and cache                                                                                                                                                                                                                                                                                                                                                            | 150        |

| 5.6               | configurations to be used by Relaxed Cache                                                                                                                                                                                                                                                                                                                                                                                            | 158        |

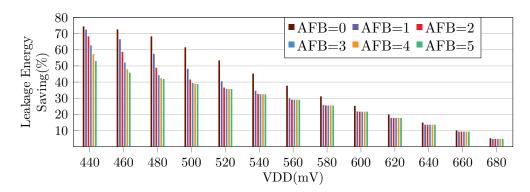

| 5.0               | savings are normalized to a baseline cache that uses 700mV.)                                                                                                                                                                                                                                                                                                                                                                          | 160        |

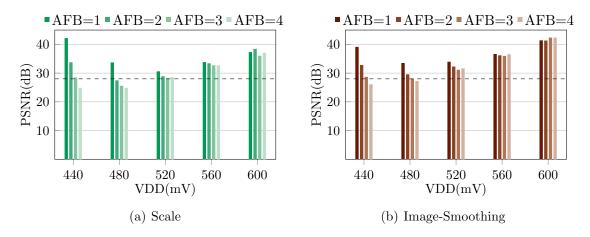

| 5.7               | Fidelity results for (a) Scale and (b) Image-Smoothing benchmarks                                                                                                                                                                                                                                                                                                                                                                     | 161        |

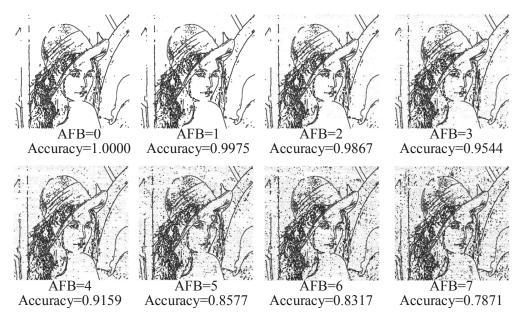

| 5.8               | Fidelity results for Edge-Detection benchmark (VDD=480mV)                                                                                                                                                                                                                                                                                                                                                                             | 162        |

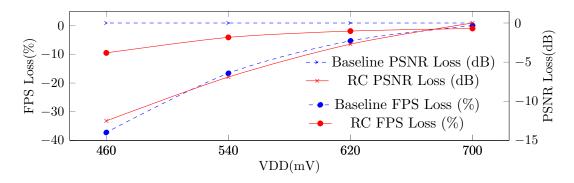

| 5.9               | FPS-PSNR trade-offs w/ and w/o Relaxed Cache scheme (AFB=4)                                                                                                                                                                                                                                                                                                                                                                           | 163        |

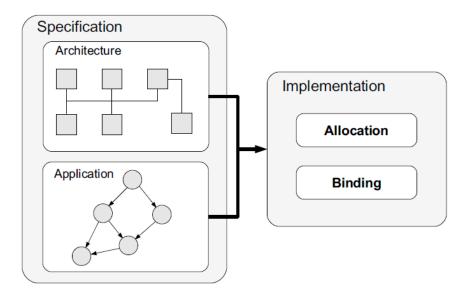

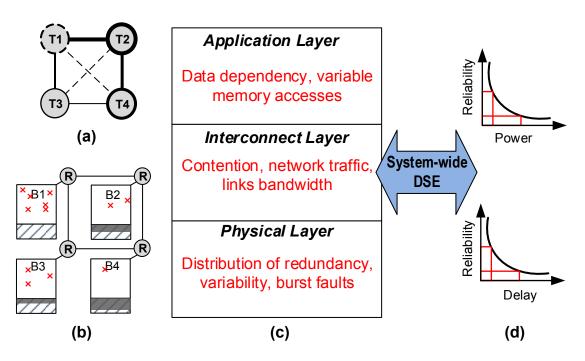

| 6.1<br>6.2<br>6.3 | A general system-level design space exploration problem [101] Exemplar Many-core Architecture with an 8x8 mesh NoC A sample case of a 2 × 2 NoC and four tasks mapped on its cores; a)a sample task mapping; b)uniform distribution of faults vs non-uniform distribution of faults (shaded areas represent redundancy resources and cross signs represent faulty blocks); c)cross-layer design methodology; d)DSE and Pareto-optimal | 168<br>169 |

| a 4               | solution                                                                                                                                                                                                                                                                                                                                                                                                                              | 170        |

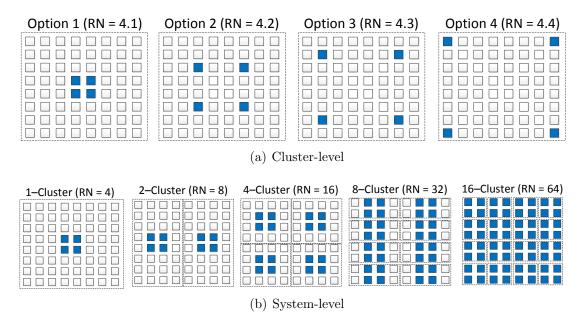

| 6.4               | Possible redundancy configuration patterns in (a) cluster-level and (b) system-level models with four redundancy nodes per cluster                                                                                                                                                                                                                                                                                                    | 177        |

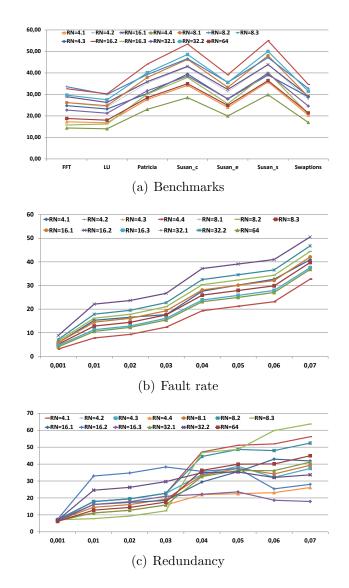

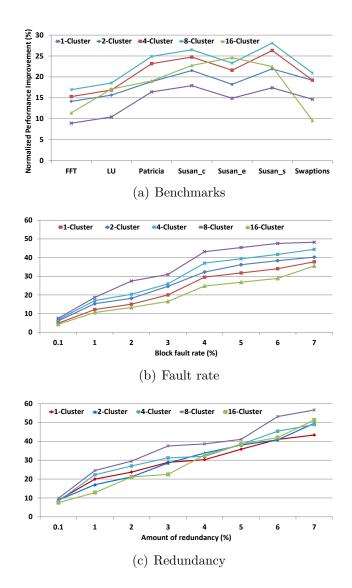

| 6.5               | Normalized performance improvement of different cluster-level configurations                                                                                                                                                                                                                                                                                                                                                          |            |

|                   | across different a) benchmarks, b)<br>fault rates, c)<br>amount of redundancy                                                                                                                                                                                                                                                                                                                                                         | 179        |

| 6.6               | Normalized performance improvement of different system-level configurations across different a) benchmarks, b)fault rates, c)amount of redundancy                                                                                                                                                                                                                                                                                     | 181        |

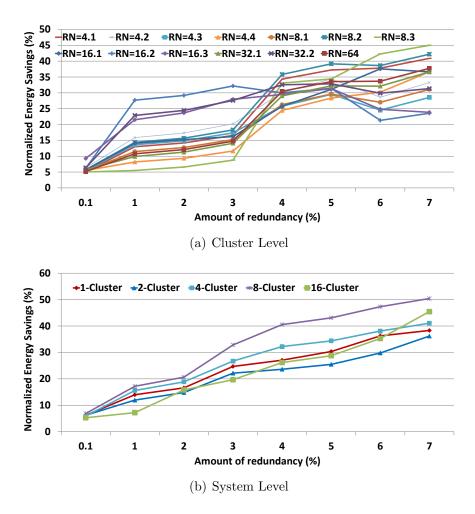

| 6.7               | Energy results across different amount of redundancy for (a) Intra-cluster, (b)                                                                                                                                                                                                                                                                                                                                                       | 101        |

|                   | Inter-cluster (system-level) configurations                                                                                                                                                                                                                                                                                                                                                                                           | 182        |

### LIST OF TABLES

|     |                                                                | Page  |

|-----|----------------------------------------------------------------|-------|

| 2.1 | Processor Configuration                                        | . 33  |

| 2.2 | Comparison of different cache protection schemes               |       |

| 2.3 | Simulated System Parameters                                    | . 50  |

| 2.4 | Reliability and coding area comparison of different techniques | . 53  |

| 3.1 | Architectural Specification                                    | . 63  |

| 3.2 | Workload Mix, Spec2006 benchmarks are denoted with _06         | . 80  |

| 3.3 | Comparison of different cache protection schemes               | . 83  |

| 4.1 | Simulation Configuration                                       | . 113 |

| 4.2 | Benchmarks Description                                         | . 115 |

| 4.3 | RDB Remapping Results                                          | . 118 |

| 4.4 | Power and Area Overhead Results                                | . 122 |

| 4.5 | Simulation Configuration                                       | . 133 |

| 4.6 | Overhead and improvements comparison                           | . 140 |

| 5.1 | A sample criticality table for Relaxed Cache                   | . 154 |

| 5.2 | gem5 Common Parameter Settings                                 |       |

| 6.1 | Simulation Configuration                                       | . 175 |

#### ACKNOWLEDGMENTS

First of all, I would like to express my gratitude to my advisor, Professor Nikil Dutt, for his support and mentorship in these past years. He gave me the freedom to choose my research topic, always interacted with me to make my ideas concrete, constantly kept me motivated during the formative years of my graduate student tenure, and has consistently inspired me to do quality research. I am extremely grateful towards him for all his advices, guidance, and support throughout this journey. During these years, I learned a lot of lessons from him which helped me to be more successful in my research, career, and more importantly in my life. I also owe thanks to my candidacy and dissertation committee, Professor Ahmed Eltawil, Professor Tony Givargis, Professor Alex Nicolau, and Professor Alex Veidenbaum for their time and feedback. Their valuable comments and feedback immensely improved the quality of my dissertation.

I would also like to express my gratitude to all my past mentors and collaborators including Prof. Houman Homayoun, Dr. Luis Bathen, Dr. Gustavo Giro, Majid Shoushtari, Mark Gottscho, Ashkan Eghbal, Pooria Yaghini, Dr. Fabian Oboril and Mojtaba Ebrahimi for their great feedback, guidance, and collaborations, which resulted in an excellent research with many successful publications. They have all at some point in my life made an enormous impact, encouraged me to follow my dream, and to not give up. Especially, Prof. Houman Homayoun, who helped me to start a good research and gave me the words I needed to hear to keep moving forward.

I would like to mention special thanks to my friends and colleagues at UCI. In particular, I thank Arup Chakraborty, Dr. Hesam Kooti, Dr. Amirhossein Gholamipour, Dr. Luis (Danny) Bathen, Dr. Kazuyuki Tanimura, Codrut Stancu, Dr. Gustavo Giro, Hossein Tajik, Dr. Jun Yong Shin, Santanu Sarma, Dr. Trent Lo, Majid Shoushtari, Jurngyu Park, Bryan Donyanavard, Roger Chen-Ying Hsieh, Tiago Mck, Ashkan Eghbal, and Pooria Yaghini. They all made a great impact in my life.

I would like to thank Professor Alex Nicolau, Professor Dean Tullsen, Professor Puneet Gupta, Professor Nader Bagherzadeh, and Professor Mehdi Tahoori for their great advices, feedback, and willingness to collaborate with me.

My research at UCI has been supported in part by the National Science Foundation under NSF Variability Expedition Grant Number CCF-1029783.

Most importantly, my family deserve major gratitude. I would like to thank my parents for all their unconditional love and support, for having faith in me and unconditionally supporting me in every step I take. I would also like to thank my wife's parents for all their support. I would also like to thank my extended family members including my siblings and siblings of my wife for being a great cheering team and constantly fueling my aspirations. I feel blessed to have a family who has given me all the opportunities to succeed in life.

I am very grateful for the support, encouragement and patience of the love of my life, Marjan,

throughout the long years I worked toward my Ph.D. She made a lot of sacrifices and provided me the necessary strength to pursue my dreams, I will be forever in her dept. I also owe my son Nickan, a debt of gratitude for being such a nice and lovely boy who gave me the energy to enjoy the life and work hard.

Finally, thank God, whom I respect and thank for the opportunities I was given and placing so many wonderful people in my path.

### CURRICULUM VITAE

### ${\bf Abbas} \ {\bf Banaiyan Mofrad}$

#### **EDUCATION**

| Doctor of Philosophy in Computer Science<br>University of California, Irvine                               | <b>2015</b> <i>Irvine, California</i>      |

|------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| Master of Science in Computer Engineering<br>University of Tehran                                          | <b>2006</b> <i>Tehran, Iran</i>            |

| Bachelor of Science in Computer Engineering Isfahan University of Technology                               | <b>2003</b> <i>Isfahan, Iran</i>           |

| RESEARCH EXPERIENCE                                                                                        |                                            |

| Graduate Research Assistant<br>University of California, Irvine                                            | <b>2010–2015</b> <i>Irvine, California</i> |

| Visiting Researcher Karlsruhe Institute of Technology (KIT)                                                | <b>2014</b> Karlsruhe, Germany             |

| Graduate Research Assistant<br>University of Tehran                                                        | <b>2003–2006</b> <i>Tehran, Iran</i>       |

| SELECTED HONORS AND AWARDS                                                                                 |                                            |

| Yahoo! Best Dissertation Student Award<br>University of California, Irvine                                 | 2014                                       |

| Karlsruhe House of Young Scientists (KHYS) scholarship<br>Karlsruhe Institute of Technology (KIT), Germany | 2014                                       |

| SIGDA-DAC PhD Forum Travel Award<br>University of California, Irvine                                       | 2014                                       |

| Design and Automation Conference (DAC) Young Student University of California, Irvine                      | Award 2011, 2012                           |

| ICS Dean's Fellowship for 4 years of support<br>University of California, Irvine                           | 2010–2014                                  |

| Deans honored graduate University of Tehran, Iran                                                          | 2003                                       |

#### TEACHING EXPERIENCE

| Teaching Assistant University of California, Irvine                                                                                                   | 2012–2013<br>Irvine, California |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Teaching Assistant                                                                                                                                    | 2005–2006                       |

| University of Tehran                                                                                                                                  | Tehran, Iran                    |

| REFEREED JOURNAL PUBLICATIONS                                                                                                                         |                                 |

| RESCUE: Fault-tolerant Design of NUCA Caches at<br>Near-Threshold Voltages<br>ACM Transaction on Architecture and Code Optimization (TACC             | <b>2015</b> (under review)      |

| DPCS: Dynamic Power/Capacity Scaling for SRAM Caches in the Nanoscale Era ACM Transaction on Architecture and Code Optimization (TACC                 | <b>2015</b> (second stage)      |

| Exploiting Partially-Forgetful Memories for Approximate Computing IEEE Embedded Systems Letters (IEEE-ESL)                                            | 2015                            |

| Using a Flexible Fault-Tolerant Cache to Improve Reliability for Ultra Low Voltage Operation ACM Transaction on Embedded Computing Systems (TECS)     | 2015                            |

| NoC-Based Fault-Tolerant Cache Design in Chip Multiprocessors  ACM Transaction on Embedded Computing Systems (TECS)                                   | 2014                            |

| REFEREED CONFERENCE PUBLICATIONS                                                                                                                      |                                 |

| Protecting Caches Against Multiple Bit Upsets Using<br>Embedded Erasure Coding<br>IEEE European Test Symposium (ETS)                                  | May 2015                        |

| Partially-Forgetful Memories: Relaxing Memory<br>Guard-bands for Approximate Computing<br>Workshop on Approximate Computing Across the System Stack ( | Feb <b>2015</b> WACAS)          |

| Power / Capacity Scaling: Energy Savings with Simple Fault-Tolerant Caches ACM/IEEE Design Automation Conference (DAC)(Invited)                       | Jun 2014                        |

| Multi-Layer Memory Resiliency ACM/IEEE Design Automation Conference (DAC)                                                                             | Jun 2014                        |

REMEDIATE: A Scalable Fault-tolerant Architecture

Aug 2013

for Low-Power NUCA Cache in Tiled CMPs

International Green Computing Conference (IGCC)

Modeling and Analysis of Fault-tolerant Distributed Mar 2013

Memories for Networks-on-Chip

IEEE Design, Automation, and Test in Europe (DATE)

A Novel NoCBased Design for Fault-Tolerance of Last-Level Caches in CMPs

IEEE/ACM International Conference on Hardware-Software Codesign and System Synthesis, (CODES+ISSS)

FFT-Cache: A Flexible Fault-Tolerant Cache Architecture for Ultra Low Voltage Operation

Oct 2011

International Conference on Compilers, Architectures, and Synthesis of Embedded Systems (CASES)

#### **SOFTWARE**

FFT-Cache framework https://github.com/abanaiya/fft-cache C simulation framework for fault-tolerant cache design

#### ABSTRACT OF THE DISSERTATION

Resilient On-Chip Memory Design in the Nano Era

By

Abbas BanaiyanMofrad

Doctor of Philosophy in Computer Science

University of California, Irvine, 2015

Professor Nikil Dutt, Chair

Aggressive technology scaling in the nano-scale regime makes chips more susceptible to failures. This causes multiple reliability challenges in the design of modern chips, including manufacturing defects, wear-out, and parametric variations. By increasing the number, amount, and hierarchy of on-chip memory blocks in emerging computing systems, the reliability of the memory sub-system becomes an increasingly challenging design issue. The limitations of existing resilient memory design schemes motivate us to think about new approaches considering scalability, interconnect-awareness, and cost-effectiveness as major design factors. In this thesis, we propose different approaches to address resilient on-chip memory design in computing systems ranging from traditional single-core processors to emerging many-core platforms. We classify our proposed approaches in five main categories: 1) Flexible and lowcost approaches to protect cache memories in single-core processors against permanent faults and transient errors, 2) Scalable fault-tolerant approaches to protect last-level caches with non-uniform cache access in chip multiprocessors, 3) Interconnect-aware cache protection schemes in network-on-chip architectures, 4) Relaxing memory resiliency for approximate computing applications, and 5) System-level design space exploration, analysis, and optimization for redundancy-aware on-chip memory resiliency in many-core platforms. We first propose a flexible fault-tolerant cache (FFT-Cache) architecture for SRAM-based on-chip cache memories in single-core processors working at near-threshold voltages. Then, we extend the technique proposed in FFT-Cache, to protect shared last-level cache (LLC) with Non-Uniform Cache Access (NUCA) in chip multiprocessor (CMP) architectures, proposing REMEDIATE that leverages a flexible fault remapping technique while considering the implications of different remapping heuristics in the presence of cache banking, non-uniform latency, and interconnected network. Then, we extend REMEDIATE by introducing RES-CUE with the main goal of proposing a design trend (aggressive voltage scaling + cache over-provisioning) that uses different fault remapping heuristics with salable implementation for shared multi-bank LLC in CMPs to reduce power while exploring a large design space with multiple dimensions and performing multiple sensitivity analysis. Considering multibit upsets, we propose a low-cost technique to leverage embedded erasure coding (EEC) to tackle soft errors as well as hard errors in data caches of a high-performance as well as an embedded processor. Considering non-trivial effect of interconnection fabric in memory resiliency of network-on-chip (NoC) platforms, we then propose a novel fault-tolerant scheme that leverages the interconnection network to protect the LLC cache banks against permanent faults. During a LLC access to a faulty area, the network detects and corrects the faults, returning the fault-free data to the requesting core. In another approach, we propose CoDEC, a Co-design approach to error coding of cache and interconnect in many-core architectures to reduce the cost of error protection compared to conventional methods. Proposing a system-wide error coding scheme, CoDEC guarantees end-to-end protection of LLC data blocks throughout the on-chip network against errors. Observing available tradeoffs among reliability, output fidelity, performance, and energy in emerging error-resilient applications in approximate computing era motivates us to consider application-awareness in resilient memory design. The key idea is exploiting the intrinsic tolerance of such applications to some level of errors for relaxing memory guard-banding to reduce design overheads. As an exemplar we propose Relaxed-Cache, in which we relax the definition of faulty block depending on the number and location of faulty bits in a SRAM-based cache to save energy. In this part of thesis, we aim at cross-layer characterization and optimization of on-chip memory resiliency over the system stack. Our first contribution toward this approach is focusing more on scalability of memory resiliency as a system-level design methodology for scalable fault-tolerance of distributed on-chip memories in NoCs. We introduce a novel reliability clustering model for effective shared redundancy management toward cost-efficient fault-tolerance of on-chip memory blocks. Each cluster represents a group of cores that have access to shared redundancy resources for protection of their memory blocks.

### Chapter 1

### Introduction

### 1.1 Nano Era Design Trends and Challenges

We categorize the general trends and challenges of design in the Nano era in three major groups of *Technology*, *Chip Design*, and *Application* that we briefly describe in below.

### 1.1.1 Technology Trend

Aggressive technology scaling in Nano era coupling with environmental issues make CMOS circuits more susceptible to various sources of failures from soft errors to hard errors [118]. Hence, there are major trends and challenges in circuit reliability with many evolving techniques for dealing with them [48]. The main sources of hard faults in deep sub-micron technology nodes include manufacturing defects, process variation, and wearout induced failures [48].

#### 1.1.2 Chip Design Trend

As semiconductor manufacturers continue to push for Chip-Multiprocessor technology in recent platforms such as IBM cell processor [70], Intel's 48-core IA-32 processor [72], Intel Larrabee many-core [140], Teraflops Research Chip [151], Single-chip Cloud Computer (SCC) [64], Intel Xeon Phi [78], NVIDIA Tesla [97], and Tilera TILE64 processor [31], many-core architectures are become one of the major design options of next-generation large-scale systems. Since reliability and efficiency are challenges of large-scale system design [149], new challenges emerge in terms of effective and reliable design of different components in recent platforms [37]. Furthermore, since memory system constitutes a majority of the silicon in a large-scale system, the memory subsystem has become vulnerable to a host of manufacturing, environmental, and operational failure/degradation mechanisms that affect the overall resiliency of the system. By increasing the number, amount, and hierarchy of on-chip memory blocks in emerging large interconnected many-core architectures, reliability of memory sub-system becomes an increasingly challenging issue in the design of such platforms [69].

### 1.1.3 Application Trend

On the other hand, most of the applications in emerging domains such as big data, cyber physical systems, social networks and so on are memory-intensive. Also, there exist some class of applications such as embedded, multimedia, and Recognition, Mining and Synthesis (RMS), are inherently resilient to some level of errors [92]. Traditional fault-tolerant approaches which try to protect the memories against all existing faults and errors, are not efficient for such applications. Hence, techniques for effective memory protection needed to be addressed in the design of emerging computing systems. (From this point forward, an emerging computing system is a large-scale platform such as many-core which is running new class of applications such as memory-intensive benchmarks.)

#### 1.2 Memories and Errors

Figure 1.1 shows the typical hardware/software abstraction layers for computing systems. Each row of Figure 1.1 describes the system abstraction layer, the memory abstraction at that level, and typical manifestations of memory errors that can compromise system resiliency. The last column of Figure 1.1 describes mitigation schemes in the face of memory error manifestations at that level of abstraction. Memory errors manifest themselves in different ways across abstraction stack. For instance, an unstable memory cell at the circuit/device level can cause a bit failure at the memory logic level, which in turn might propagate up the abstraction stack as a faulty memory access at the architecture level, a wrong function call or system halt at OS-level, and finally an output error or an exception at application layer. Figure 1.1 represents a symbolic abstraction of memory errors over the entire hardware/software system stack. Traditionally, memory resilience has been addressed via disparate techniques at each level of design abstraction, while newer efforts attempt to couple strategies across layers with the goal of improving system efficiency for energy, heat dissipation, lifetime, cost, etc. Furthermore, efforts in relaxed and approximate computing attempt to create designs that can trade off application quality for these system efficiency goals. To understand memory faults, we can classify them by their temporal behaviors (persistence) as well as their causes. With respect to persistence, a memory fault can be permanent or transient. Permanent faults persist indefinitely in the system after occurrence, while transient faults manifest for a relatively short period of time after occurrence. Furthermore, causes of memory faults can be hard or soft. Hard faults are static and caused by device failure or wear-out failure. In contrast, soft faults are dynamic and are typically caused by the operating environment.

In general, memories suffer from different sources of unreliability that can be classified into three main groups:

| System<br>Abstraction | Memory<br>Abstraction                                        | Error<br>Manifesta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | tion                                                          | Mitigation                                        |

|-----------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------|

| Application           | Program,<br>Data Structures,<br>Files,<br>Libraries          | ERROR!                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Incorrect Output,<br>Infinite Loop,<br>Crash                  | TMR,<br>Recomputing,<br>Information<br>Redundancy |

| System<br>(OS)        | Main Memory,<br>File System<br>Address Space,<br>Heap, Stack |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Wrong Pointer,<br>Erroneous System<br>Call, Trap              | Error Check,<br>Assertion,<br>Exception           |

| Architecture<br>(ISA) | Buffers,<br>Register File,<br>L1\$, L2\$, SPM                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Faulty Word,<br>Cache Block,<br>Way                           | ECC, Spare<br>Elements,<br>Disabling              |

| Logic                 | Memory Cells,<br>Bit Arrays                                  | 0 1010100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Bit flip,<br>Stuck @ 0/1                                      | Adding Parity,<br>Spare Cells                     |

| Circuit/<br>Device    | Voltage,<br>Current,<br>Transistor,<br>Cell                  | Process & variation & variation & Formula & Process & Variation & | Low Noise  Margin,  Unstable Cell,  V <sub>th</sub> Variation | Larger transistors,<br>More transistors           |

Figure 1.1: Memory Abstractions, Errors, and Opportunities.

- 1. Manufacturing. Worsening manufacturing imperfections in nanoscale technologies result in increasing variability of device and circuit-level parameters. This process variation particularly affects transistor threshold voltages through random dopant fluctuation (RDF), increasing the likelihood of memory cells failing permanently due to insufficient noise margins at a given supply voltage.

- 2. Environmental. Alpha particle radiation coming from the operating environment can cause single event upsets (SEU). Combined with weakened noise margins from manufacturing effects, memory cells are also becoming more susceptible to SEU, impacting their soft error resilience [2]. Noise stemming from variations in the supply voltage and thermal effects can also cause memory faults exhibiting dynamic and random behavior.

- 3. Aging and Wearout. Depending on the type of technology used, memory cells can age, reducing their performance, data retention capability, and power consumption. Aging can

lead to memory wearout, resulting in permanent faults.

Different memory technologies suffer from various sources of unreliability. Volatile memories such as SRAM and DRAM mostly suffer from manufacturing defects and environmental issues that lead to hard and soft errors, respectively. Endurance is not an issue in SRAM and DRAM. In contrast, different nonvolatile memories (NVMs) have their own sources of unreliability. For flash and phase change memory (PCM), wearout is the primary source of unreliability due to limited write endurance. PCMs also suffer from hard and soft errors [162]. Other emerging NVMs such as MRAM and its newer cousin STT-RAM also suffer from hard and soft errors. However, for these devices, wearout is not as great of a reliability threat, because they have large write endurances similar to that of SRAM.

The design of reliable computer systems has a rich history spanning several decades: variants of spatial, temporal, and information redundancy have been exploited to improve reliability. Memory systems also deploy these forms of redundancy to achieve resilience across various layers of system abstraction. Additionally, memory designers have leveraged a variety of other memory-specific techniques.

In next section, we provide a sampling of common techniques used for reliable memory design at the architectural level. A significant body of research exists on the design of a reliable memory hierarchy comprising multiple levels of caches and main memory.

### 1.3 State-of-the-art Research Efforts

A significant amount of literature targets the memory reliability concerns due to different aspects of vulnerability including transient errors, manufacturing defects, process variation, wearout, and stability in near/sub-threshold operation [54]. We briefly review the prior related work in three major categories including: Reliable and fault-tolerant cache design,

memory reliability concerns in multi/many-core platforms, and techniques for approximate computing on memories or application-aware memory resiliency.

Reliable and Fault-tolerant Cache/Memory design A significant body of research exists on the design of a reliable memory hierarchy comprising multiple levels of caches and main memory [54]. We can categorize resilient SRAM cache design efforts into three main groups of Cell/Circuit-Level Techniques, Error Coding Techniques, and Architecture-Level Techniques. Many of these have the common property of fault-tolerant voltage-scalable (FTVS) design, because low voltage operation while critical for achieving power and energy savings is the primary driver behind unreliable memories. In general, regardless of whether the fault-tolerant design is done at the cell, circuit, coding, or architecture level, there is a trade-off in terms of memory capacity and area. This may be due to larger memory cells, spare or redundant cells, error correction logic, or a reduced amount of reliable memory available for use by the application.

Fault-tolerant memory designs have often used simple techniques such as adding redundant rows/columns to the memory array [139] or applying memory down-sizing techniques by disabling a faulty row or cache line (block) [122]. Many recent architecture-level schemes deploy more complicated redundancy or capacity downsizing techniques to improve the reliability of cache memories. Information redundancy via error coding is also commonly used to improve the reliability of memory components. Wide ranges of error detection and correction codes (EDC and ECC, respectively) have been used [96]. Typically, EDCs are simple parity codes, while the most common ECCs use Hamming [67] or Hsiao [73] codes. ECC is proven as an effective mechanism for handling soft errors. For NVMs that have limited write endurance, various wear-leveling approaches have been proposed to mitigate aging and extend memory lifetime. In the domain of embedded systems, design of reliable software-controlled scratchpad memories (SPMs) has also received great attention recently, including efforts that address the reliability of SPMs for chip-multiprocessors (E-RoC [25] and SPMVisor [27]), or

for hybrid memories (FTSPM [110]).

Memory reliability in multi/many-cores There is a large body of previous work on fault-tolerant design of on-chip memories and caches, mostly focused on either single bank or multi-bank caches with uniform access latency in single-core processors [54]. However, they face severe limitations when applied to emerging multi-core/many-core architectures where the number of access points (cores) and memory banks are increasing, large on-chip memories are shared and distributed via interconnected network among all cores, memory access latencies are not unified, interconnect backbone is also erroneous and affects memory resiliency, and cost of uniform fault-tolerance is very high [19]. Hence, most of the current fault-tolerant schemes are not modular, scalable, and cost-efficient enough to be applied to these architectures. Only a few efforts somehow addressed on-chip memory reliability in CMP or NoC platforms [7, 154, 25, 5, 16].

Memory Reliability Relaxation A significant amount of work has proposed different hardware and software techniques that trade-off reliability or application fidelity to gain benefits in energy, performance, lifetime, or yield for applications that can tolerate some level of error in exchange for loss of quality (e.g., RMS applications). Many studies on approximate computing era have shown that a variety of applications have a high tolerance to errors [51, 45, 92, 109, 95]. While most of the previous efforts on approximate computing have focused on the computational part, there exist only a few works that have addressed relaxing reliability in memories which mainly focused on off-chip memories [100, 135].

### 1.4 Motivation

In this section, we first define some general as well as introduced terminology we leverage throughout the thesis.

- Resiliency: The power or ability to recover from or adjust easily to a bad/unlikely situation.

- Reliability: The ability to be relied on or depended on, as for accuracy, honesty, or achievement.

- System Reliability: The ability of a system or component to perform its required functions under stated conditions for a specified period of time.

- System Resiliency: The ability of a system to continue to function correctly, sometimes in a degraded fashion, in the presence of faults, errors, or other variation.

Resilience is a measure of a system's ability to bounce back from a failure to continue to offer some level of performance (possibly not the original level of performance).

Design for Resiliency is a way of achieving Reliability by trading off other system metrics like performance. The reliability issues and limitations of common schemes mentioned above motivate us to think about new approaches that address cost-efficient resilient design of on-chip memory in emerging multi/many-core platforms. We consider all limiting factors of traditional and current approaches as well as emerging technology/architecture/application requirements and challenges in design of our new approaches. Some of the key resiliency design features that are either missed or addressed inefficiently in previous approaches, considered in design of our novel approaches and include: flexibility, scalability, interconnect-awareness, multi-layer design, cost-efficiency, non-uniformity, redundancy-awareness, and application-awareness.

By reviewing the previous approaches as well as current efforts and design trends, we gain multiple important observations. We summarize the key observations as follows:

• Inefficiency of previous fault-tolerant cache/memory design approaches for emerging applications and platforms

- Cost-efficient resilient memory design becomes a major challenge in design of emerging platforms

- For many application domains, it is acceptable to trade some design metrics (performance, yield, fidelity, etc.) to increase the efficiency.

- New approaches required to provide memory resiliency in emerging computing systems

The key missed resiliency features as well as our observations mentioned above, motivates us to approach to memory resiliency in a different way. Our key idea in this thesis is that we propose novel approaches with the goal of *Design for Memory Resiliency or Resilient Memory Design* other than traditional design for Reliability or fault-tolerance memory design. That is, we try to address most of the key required resiliency features in our new approaches to memory resiliency to make it more efficient and reduce the costs by considering different design parameters such as possible design trade-offs, multi-layer design possibilities, platform features (resources and constraints), and application features (requirements and constraints).

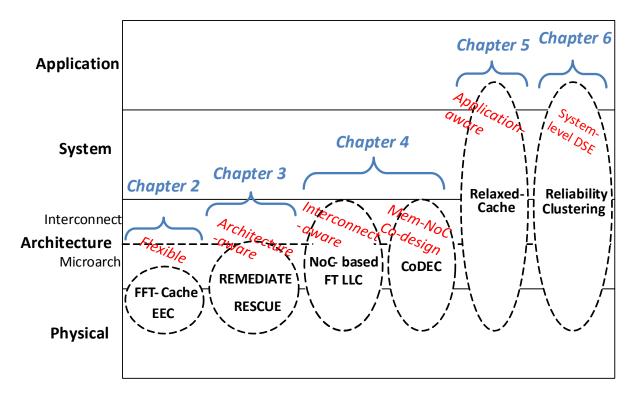

Figure 1.2: Summary of the thesis main contributions.

#### 1.5 Thesis Contributions

In this thesis, we make multiple contributions and propose novel approaches in different layers of system hierarchy to address resilient memory design issues in computing systems ranging from traditional single-core processors to emerging many-core platforms as indicated in Figure 1.2. We classify our proposed approaches in five main categories: 1) Flexible low-cost Cache Design (Chapter II), 2) Scalable Resilient Cache Design (Chapter III), 3) Interconnect-aware resilient cache design (Chapter IV), 4) Application-aware Memory Resiliency (Chapter V), and 5) System-level Memory Resiliency Design Space Exploration and Optimization (Chapter VI).

In this thesis, we make the following contributions:

• Proposing two flexible and low-cost approaches to protect cache memories in single-core

processors against permanent and transient faults, respectively.

- FFT-Cache, a flexible cache architecture, presented to protect regular SRAM structures against high degree of process variation, we arout induced failures, and manufacturing defects. Furthermore, we propose a methodology to model the collision pattern in the cache as a graph problem. Given this model, a graph coloring scheme is employed to minimize the amount of additional redundancy.

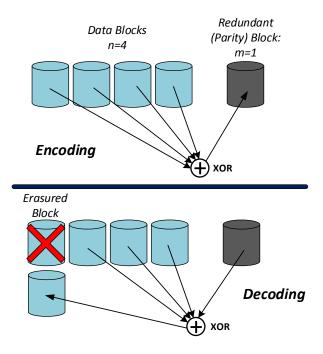

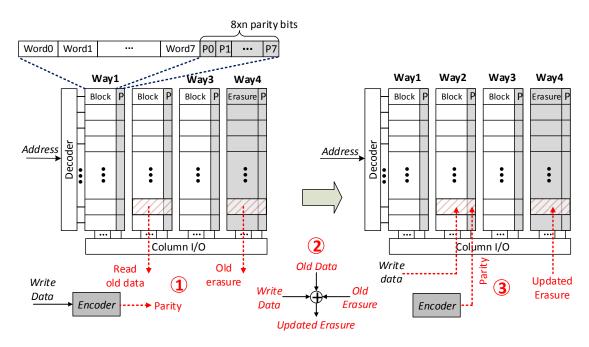

- EEC, an embedded erasure coding approach to protect cache memories against multi-bit upsets. The EEC scheme employs fast bit-interleaved parity coding as error detection in combination with optimal parity-based erasure coding as error correction over set-associative cache memories. Reserving a part of cache (e.g., one way) as erasure storage, EEC trades cache capacity for fast and low-cost error correction.

- Proposing two scalable fault-tolerant approaches to protect last-level cache (LLC) with non-uniform cache access (NUCA) in chip multiprocessors (CMPs).

- REMEDIATE to protect shared NUCA caches in tiled-based multicore platforms. REMEDIATE achieves fault-tolerance through redundancy from multiple banks to maximize the amount of fault remapping, and minimize the amount of capacity lost in the cache when the failure rate is high.

- RESCUE extends REMEDIATE to enhance fault-tolerant voltage-scalable design of shared NUCA caches in multi/many-core core platforms. While the main goal in REMEDIATE is to develop a remapping-based fault-tolerant scheme for protection of shared LLC in Tile-based CMPs while operating in low voltages, the main goal in RESCUE is to propose a design trend (aggressive voltage scaling + cache over-provisioning) that uses different fault remapping heuristics with salable implementation for shared multi-bank LLC in non-tiled-based CMPs to reduce power while exploring a large design space with multiple dimensions and

performing multiple sensitivity analysis.

- Proposing two interconnect-aware LLC protection schemes in many-core platforms.

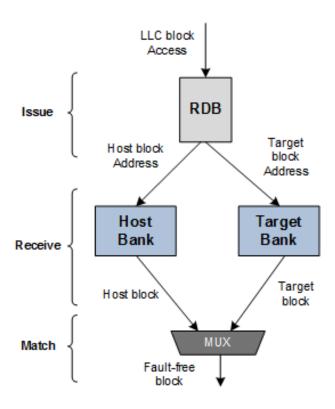

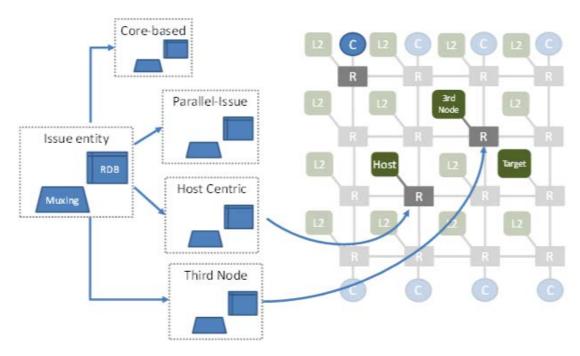

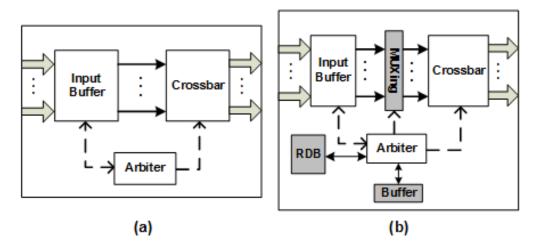

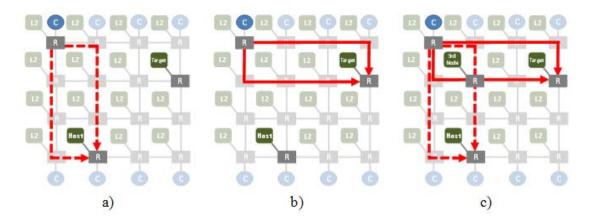

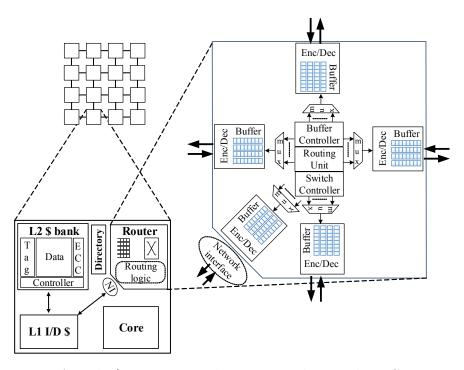

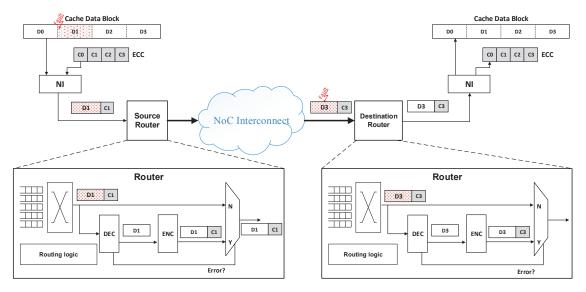

- FT-LLC, NoC-based fault-tolerance of LLC in mesh-based CMPs. This approach leverages the NoC fabric to implement a remapping-based fault-tolerant scheme protecting the LLC cache banks against permanent faults in a scalable and efficient way with minimal overhead. In this approach, during an LLC access to a faulty block, the components inside the network (routers) are responsible for detecting and correcting the faults and then returning the fault-free data to the corresponding core.

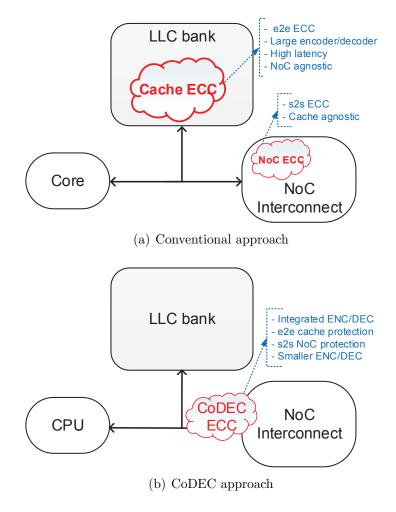

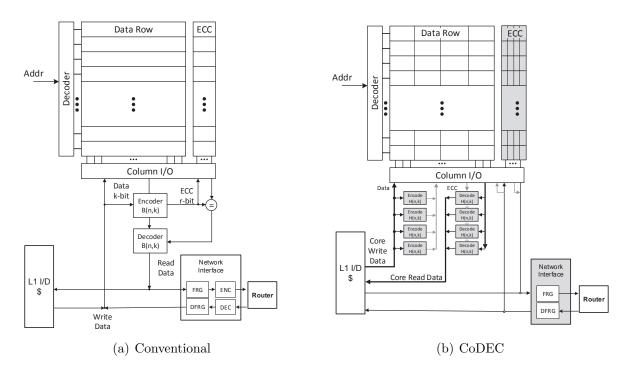

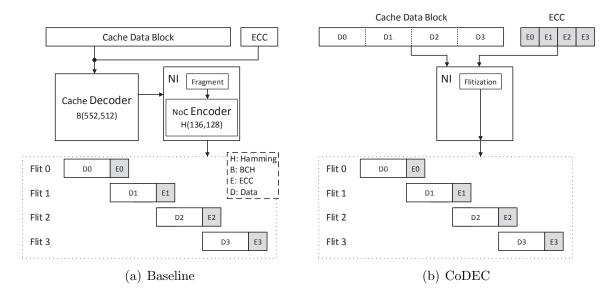

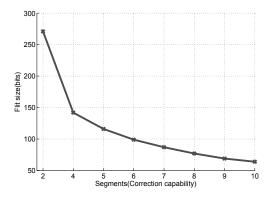

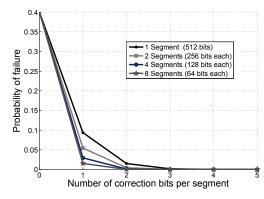

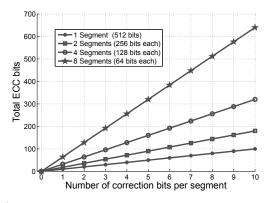

- CoDEC, a Co-design of error coding in cache and interconnect in many-cores.

CoDEC deploys a united error coding scheme that guarantees the end-to-end protection of LLC data blocks throughout the on-chip network against both hard and soft errors. CoDEC integrates strong multi-bit ECC in cache banks with s2s error coding of interconnect while removing their overlapped redundancy.

- Introducing Partially-Forgetful Memory (PFM) as an application-aware Memory Resiliency relaxation approach.

- Relaxed-Cache as an exemplar to address memory variability and approximate computing challenges for employing partially-forgetful SRAM caches. Relaxed Cache lets the application programmer adjust the cache guard-banding knobs and therefore adapt its reliability and capacity to the application's demands. Accordingly, the application programmer needs to identify critical memory objects as well as major criticality and computational phases of the application.

- Proposing approaches to system-level Design Space exploration, analysis, and optimization for on-chip memory resiliency.

- System-level Memory Resiliency, We propose a system-level design methodology for scalable fault-tolerance of distributed on-chip memory blocks in manycore platforms.

- Reliability Clustering, to model distribution of shared redundancy resources. A novel approach to manage shared redundancy resources for distributed fault-tolerance of on-chip memory components in many-cores. Each cluster represents a group of cores that have access to shared redundancy resources for protection of their own memory blocks which include LLC banks in our approach.

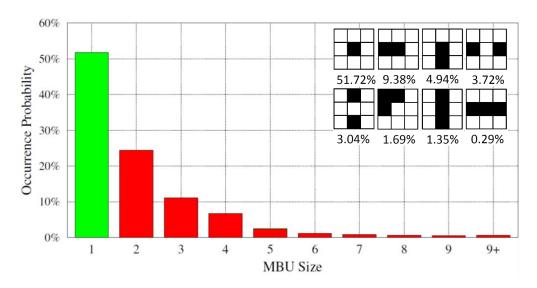

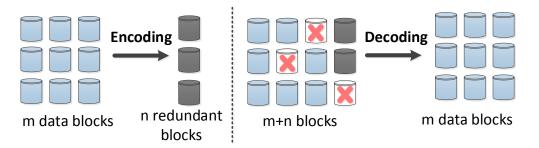

### 1.6 Thesis Organization