# UC Santa Cruz

**UC Santa Cruz Electronic Theses and Dissertations**

### Title

Voltage Stacking and Timing Speculation with an SRAM Focus

### Permalink

https://escholarship.org/uc/item/1hj7d74m

**Author** Ebrahimi, Elnaz

Publication Date 2017

### **Copyright Information**

This work is made available under the terms of a Creative Commons Attribution License, available at <a href="https://creativecommons.org/licenses/by/4.0/">https://creativecommons.org/licenses/by/4.0/</a>

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA SANTA CRUZ

### VOLTAGE STACKING AND TIMING SPECULATION WITH AN SRAM FOCUS

A dissertation submitted in partial satisfaction of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

in

### COMPUTER ENGINEERING

by

### Elnaz Ebrahimi

March 2017

The Dissertation of Elnaz Ebrahimi is approved:

Professor Jose Renau, Chair

Professor Matthew Guthaus

Professor Jishen Zhao

Tyrus Miller Vice Provost and Dean of Graduate Studies Copyright © by

Elnaz Ebrahimi

2017

# **Table of Contents**

| Li | st of I | Figures       |                                          | vi   |

|----|---------|---------------|------------------------------------------|------|

| Li | st of ] | <b>Fables</b> |                                          | x    |

| Al | bstrac  | t             |                                          | xi   |

| De | edicat  | ion           |                                          | xiii |

| A  | cknow   | ledgme        | ents                                     | xiv  |

| 1  | Intr    | oductio       | n                                        | 1    |

| 2  | Leve    | el Shifte     | ers for Voltage Stacked Architectures    | 6    |

|    | 2.1     | Introdu       | uction                                   | 6    |

|    | 2.2     | Overvi        | iew of Level Shifter designs             | 8    |

|    |         | 2.2.1         | Capacitive-Coupling-based (Conventional) | 8    |

|    |         | 2.2.2         | Two-Stage Cross-Coupled (TSCC)           | 9    |

|    |         | 2.2.3         | Wilson Current Mirror (WCM)              | 10   |

|    |         | 2.2.4         | Stacked WCM                              | 11   |

|    |         | 2.2.5         | Tong                                     | 12   |

|    |         | 2.2.6         | Modified Tong                            | 12   |

|    | 2.3     | Charac        | cterization                              | 13   |

|    |         | 2.3.1         | Transistor Sizing                        | 13   |

|    |         | 2.3.2         | PVT Variation Effect                     | 16   |

|    | 2.4     | Conclu        | usion                                    | 20   |

| 3  | Volt    | 0             | cking in SRAMs                           | 22   |

|    | 3.1     | Introdu       | uction                                   | 22   |

|    | 3.2     |               | d Work                                   | 24   |

|    | 3.3     | SRAM          | 1 Stacking Model                         | 25   |

|    | 3.4     | Setup         |                                          | 27   |

|    | 3.5     | Evalua        | ution                                    | 29   |

|    | 3.6     | Conclu        | usion                                    | 33   |

| 4 | GPU        | <b>UNTC Process Variation Compensation with Voltage Stacking</b>              | 34 |

|---|------------|-------------------------------------------------------------------------------|----|

|   | 4.1        | Introduction                                                                  | 34 |

|   | 4.2        | Related Work                                                                  | 37 |

|   | 4.3        | GPU Stacking                                                                  | 39 |

|   |            | 4.3.1 Process Variation                                                       | 40 |

|   |            | 4.3.2 High Level Idea of Process Variation Compensation                       | 40 |

|   |            | 4.3.3 Detailed Analysis of Process Variation Compensation with Voltage Stack- |    |

|   |            | ing                                                                           | 42 |

|   |            | 4.3.4 General Purpose GPU                                                     | 45 |

|   |            | 4.3.5 Process Variation Model                                                 | 46 |

|   |            | 4.3.6 Which Lanes to Stack?                                                   | 47 |

|   |            | 4.3.7 Divergence and Extreme Conditions                                       | 51 |

|   |            | 4.3.8 Final Design                                                            | 53 |

|   | 4.4        | Experimental Setup                                                            | 54 |

|   |            | 4.4.1 Process Variation Modeling                                              | 55 |

|   |            | 4.4.2 Simulation Framework                                                    | 56 |

|   |            | 4.4.3 Power Delivery Network                                                  | 57 |

|   | 4.5        | Near Threshold Computing and Baseline Choice                                  | 59 |

|   |            | 4.5.1 Power-Performance Trade-off                                             | 59 |

|   |            | 4.5.2 GPU Sizing for NTC                                                      | 60 |

|   | 4.6        | Evaluation                                                                    | 63 |

|   |            | 4.6.1 Main Results of GPU Stacking on NTC                                     | 63 |

|   |            | 4.6.2 Load Mismatch                                                           | 65 |

|   |            | 4.6.3 Stacking FinFETs vs. Planar CMOS                                        | 67 |

|   |            | 4.6.4 Lateral Current                                                         | 72 |

|   |            | 4.6.5 GPU stacking Practicality Issues                                        | 73 |

|   |            | 4.6.6 Other advantages of GPU stacking                                        | 75 |

|   | 4.7        | Conclusion                                                                    | 76 |

| _ |            |                                                                               |    |

| 5 |            | ing Speculative SRAM                                                          | 78 |

|   | 5.1        | Introduction                                                                  | 78 |

|   | 5.2        | Related Work                                                                  | 79 |

|   | 5.3        | Time Speculative SRAM                                                         | 83 |

|   |            | 5.3.1 Protecting from Read Time Failures                                      | 84 |

|   |            | 5.3.2 Protecting from Incorrect Writes                                        | 85 |

|   |            | 5.3.3 Sense Amplifier                                                         | 86 |

|   | 5.4        | Experiment Setup                                                              | 87 |

|   |            | 5.4.1 Tool Flow                                                               | 87 |

|   | 5.5        | Evaluation                                                                    | 88 |

|   |            | 5.5.1 Energy Efficiency                                                       | 89 |

|   |            | 5.5.2 Area                                                                    | 89 |

|   | <b>.</b> - | 5.5.3 Process Variation Effects                                               | 91 |

|   | 5.6        | Conclusion                                                                    | 94 |

| 6  | Con    | clusion and Future Work | 95 |

|----|--------|-------------------------|----|

|    | 6.1    | Conclusion              | 95 |

|    | 6.2    | Future Work             | 96 |

| Bi | bliogr | aphy                    | 98 |

# **List of Figures**

| 2.1 | Capacitive-Coupling-based (Conventional)                                              | 9  |

|-----|---------------------------------------------------------------------------------------|----|

| 2.2 | (a) Cross-Coupled (CC) (b) Two-Stage Cross-Coupled (TSCC)                             | 10 |

| 2.3 | (a) Wilson Current Mirror (WCM) (b) Stacked Wilson Current Mirror (Stacked)           | 11 |

| 2.4 | (a) Tong (b) Mod-Tong                                                                 | 13 |

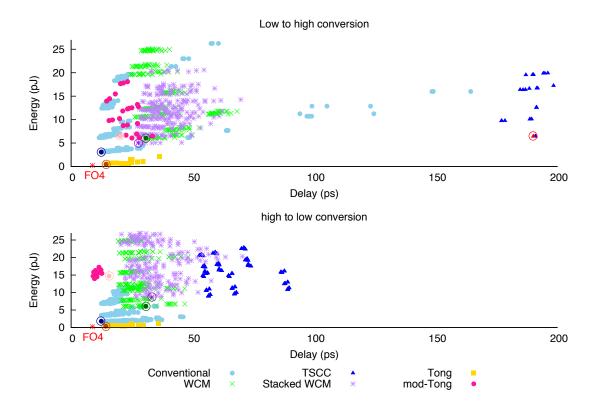

| 2.5 | Level-up shifters active energy-delay with different transistor widths                | 14 |

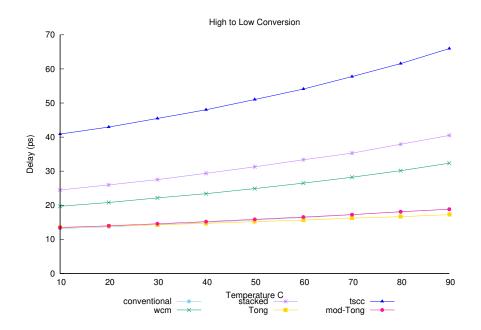

| 2.6 | Delay vs. temperature. In high to low conversion, as the temperature rises, the       |    |

|     | average propagation delay will increase. Tong is the least sensitive and TSCC         |    |

|     | is the most sensitive to temperature variation.                                       | 17 |

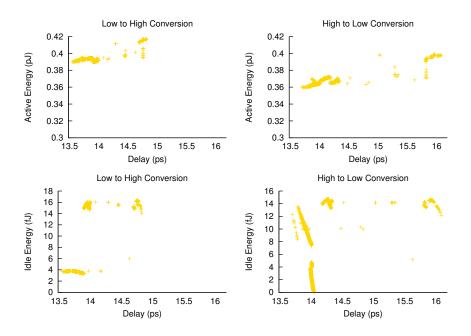

| 2.7 | Active energy-delay: +/-6% Vth variation MC simulations                               | 18 |

| 2.8 | Active energy-delay: +/-5% $V_{dd}$ variation MC simulations                          | 19 |

| 2.9 | Active and idle energy-delay: +/-5% capacitance variation MC simulations $\therefore$ | 20 |

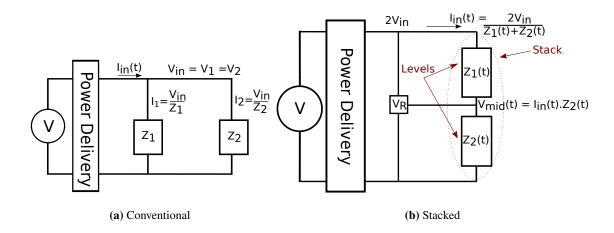

| 3.1 | Conventional vs. stacked power delivery mode                                          | 26 |

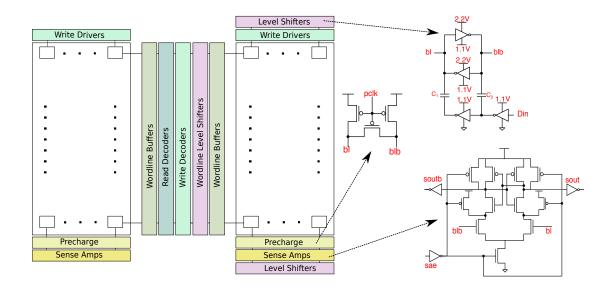

| 3.2 | Voltage stacked SRAM                                                                  | 28 |

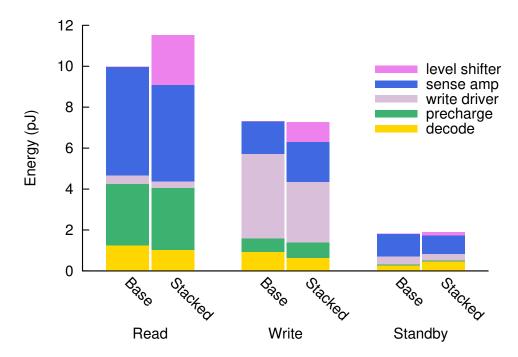

| 3.3 | Energy breakdown in voltage stacked SRAM vs. non-stacked                              | 29 |

| 3.4 | Current breakdown in voltage stacked SRAM vs. non-stacked                             | 31 |

| 3.5 | Stacking introduces a 60ps delay in the top stack output bitline, which is equiv-            |    |

|-----|----------------------------------------------------------------------------------------------|----|

|     | alent to 6% performance hit.                                                                 | 32 |

| 3.6 | Voltage noise for stacked SRAM is within acceptable levels, even without a                   |    |

|     | voltage regulator.                                                                           | 32 |

| 4.1 | Example of how the case study inverters are used in the stacked logic. The blue              |    |

|     | inverters are the devices under test.                                                        | 43 |

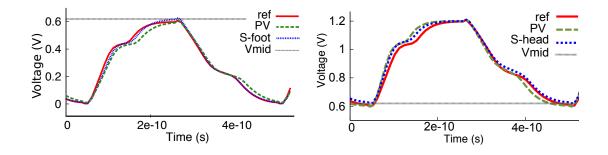

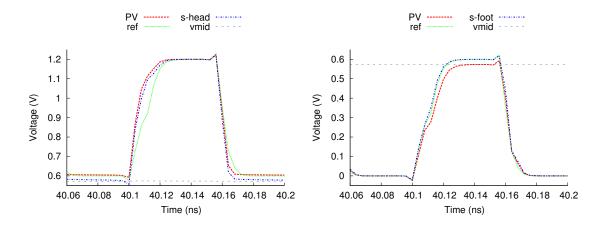

| 4.2 | Stacked configuration $(S - foot \text{ and } S - head)$ intrinsically mitigates the varia-  |    |

|     | tion effects. These signals are closer to the case without process variation $ref$ ,         |    |

|     | than the non-stacked baseline $PV$ . Since $V_{mid}$ has shifted, there is more voltage      |    |

|     | available for the slower part of the design.                                                 | 44 |

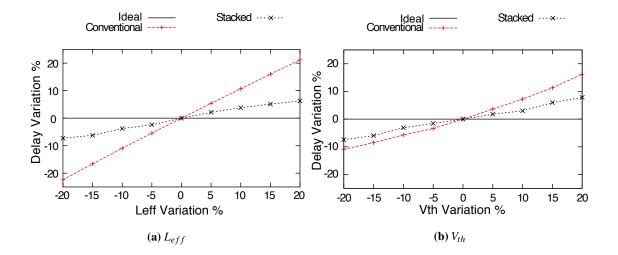

| 4.3 | Mitigation of the variation effects compared to conventional configuration                   | 45 |

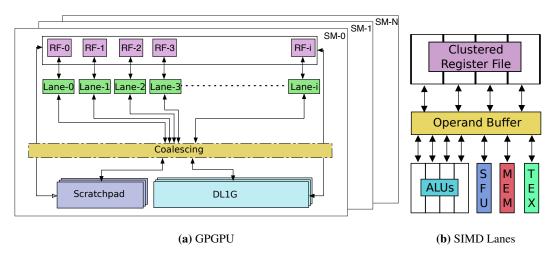

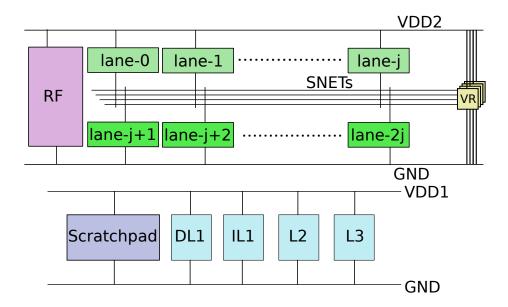

| 4.4 | GPGPUs present a large number of identical SIMD lanes, ideal for stacking                    | 46 |

| 4.5 | Sample die with 4 <i>lanes</i> and different variations                                      | 47 |

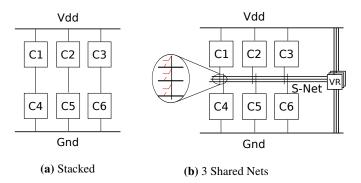

| 4.6 | Shared Net configuration simplifies stacking and supports post-fabrication con-              |    |

|     | figurability.                                                                                | 49 |

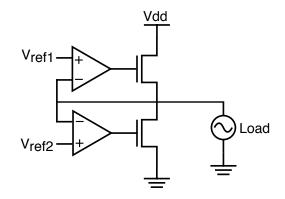

| 4.7 | The proposed dual VR based on the Low Dropout Linear VR design [67]                          | 52 |

| 4.8 | GPU stacking allows a more fine-grained voltage adjustment per lane                          | 53 |

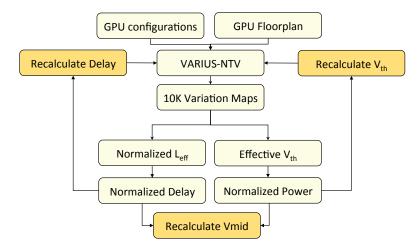

| 4.9 | Experimental setup with VARIUS-NTV process variation modeling flow. VARIUS                   | -  |

|     | NTV generates GPU variation maps and then calculates the normalized $L_{eff}$ and            |    |

|     | effective $V_{th}$ for each map. $V_{mid}$ value changes after process variation effects and |    |

|     | is calculated and fed back to VARIUS-NTV for compensated delay and power                     |    |

|     | calculations                                                                                 | 56 |

|     |                                                                                              |    |

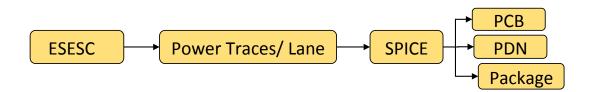

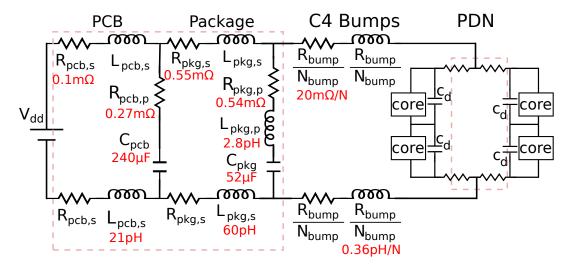

| 4.10 | The power delivery model tool flow.                                                | 57 |

|------|------------------------------------------------------------------------------------|----|

| 4.11 | The complete power delivery model used for simulations                             | 58 |

| 4.12 | Designs with more SMs become more efficient in terms of energy-delay prod-         |    |

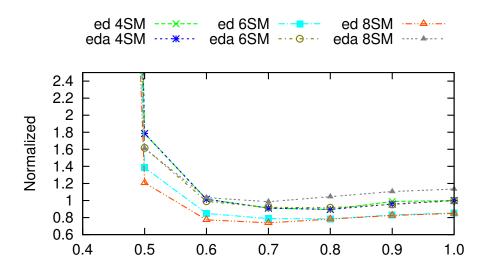

|      | uct, as well as energy-delay-area product as $V_{dd}$ decreases                    | 62 |

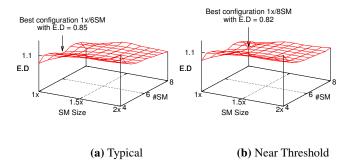

| 4.13 | The optimized baseline in near threshold region is different from the typical su-  |    |

|      | per threshold region. Larger structure sizes for cache or register file or number  |    |

|      | of lanes could become more desirable in near threshold. This demands recon-        |    |

|      | sidering the architectural parameters to obtain the best energy efficiency, rather |    |

|      | than just lowering the voltage.                                                    | 63 |

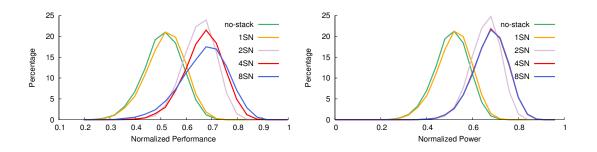

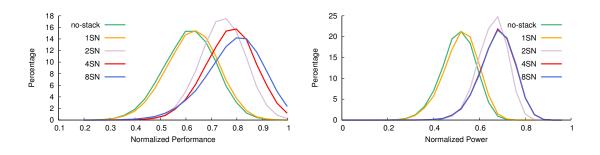

| 4.14 | The proposed techniques shift the performance and power towards the ideal          |    |

|      | scaling with no process variation                                                  | 64 |

| 4.15 | When multi-clock domain architecture is used, GPU stacking shifts the perfor-      |    |

|      | mance further towards the ideal scaling with no process variation                  | 65 |

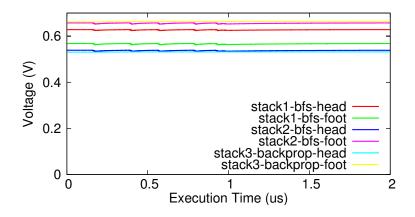

| 4.16 | It is possible to maintain the voltage in each level of the stacks with on package |    |

|      | decoupling capacitors                                                              | 68 |

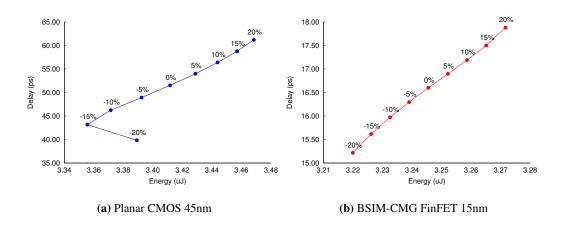

| 4.17 | The intrinsic compensation of PV effects seen for planar devices is not observed   |    |

|      | for FinFET devices due to the inverted ED trend between those two technolo-        |    |

|      | gies                                                                               | 69 |

| 4.18 | Delay increases more rapidly for Planar CMOS than FinFET as we vary $L_{eff}$ .    | 69 |

| 4.19 | The proposed techniques shift the performance and power towards the ideal          |    |

|      | scaling with no process variation.                                                 | 71 |

| 4.20 | When multiclock domain architecture is used, GPU stacking shifts the perfor-       |    |

|      | mance further towards the ideal scaling with no process variation                  | 71 |

| 4.21 | GPU stacking reduces the IR drop by reducing the total current flowing through     |    |

|------|------------------------------------------------------------------------------------|----|

|      | $V_{dd}$                                                                           | 73 |

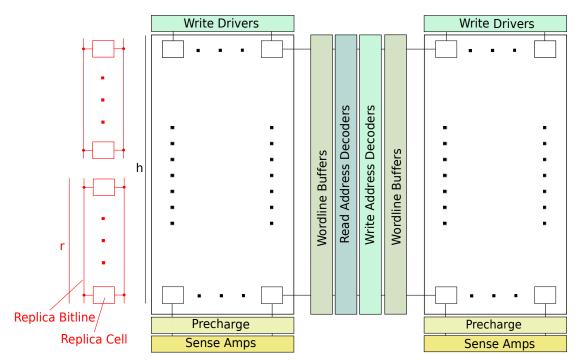

| 5.1  | Replica-based SRAM [4]. $r$ is the height of Replica cells that are active and $h$ |    |

|      | is the height of the SRAM core.                                                    | 80 |

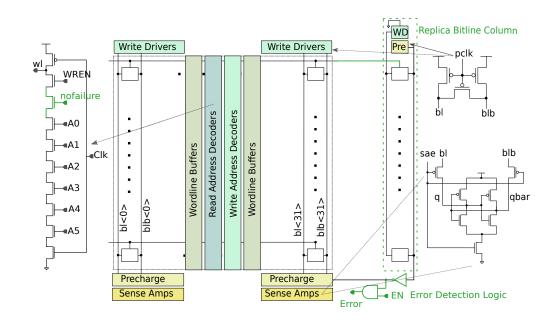

| 5.2  | Timing Speculative SRAM                                                            | 83 |

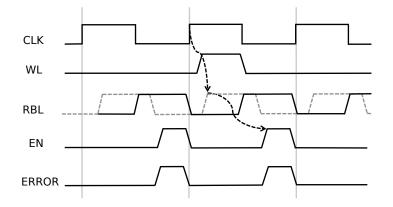

| 5.3  | RTS error signal generation                                                        | 85 |

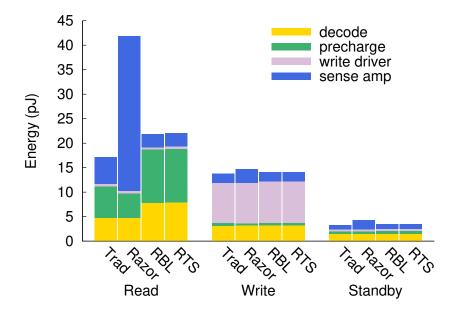

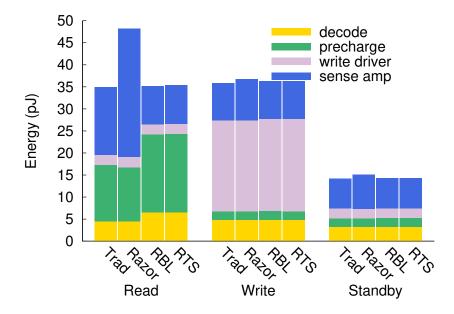

| 5.4  | Energy breakdown in <i>small</i> SRAMs                                             | 90 |

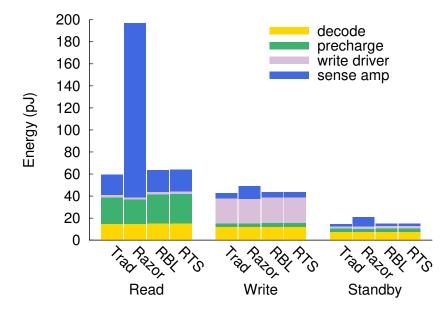

| 5.5  | Energy breakdown in <i>medium</i> SRAMs                                            | 91 |

| 5.6  | Energy breakdown in <i>large</i> SRAMs                                             | 92 |

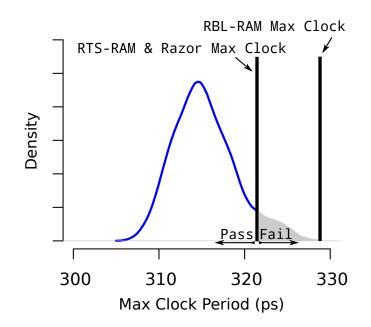

| 5.7  | RBL and Razor achieve similar results, both allow protection from infrequent       |    |

|      | failures                                                                           | 93 |

## **List of Tables**

| 2.1 | Minimum ED Pareto frontier points                                                 | 15 |

|-----|-----------------------------------------------------------------------------------|----|

| 4.1 | Simulation parameters                                                             | 61 |

| 4.2 | GPU stacking delivers better performance and power than a non-stacked config-     |    |

|     | uration under process variation. It also allows better VR efficiency, and reduced |    |

|     | number of power pins.                                                             | 76 |

| 5.1 | Experimental SRAM configurations model three typical processor SRAMs              | 87 |

| 5.2 | Experimental SRAM types                                                           | 88 |

| 5.3 | RTS overhead is mainly due to Replica Bitline Column. The Razor sense am-         |    |

|     | plifier is 5.5x RBL bitcell area and 7.4x the traditional sense amplifier. Units  |    |

|     | are in $\mu m^2$                                                                  | 91 |

| 5.4 | The area overhead percentage difference of RTS and Razor with RBL                 | 92 |

### Abstract

### Voltage Stacking and Timing Speculation with an SRAM Focus

by

### Elnaz Ebrahimi

Power consumption and delivery have emerged as one of the major challenges facing modern SoC design. As chip designs become more complex with aggressive architectures, pressure on efficient power delivery mechanisms is increasing.

Designing efficient voltage regulators gets harder due to increased current as power increases and voltage scales down. Off-chip voltage regulators can be made more efficient due to fewer restrictions on capacitor sizes but need to take into account parasitics on pads. Process variation further exacerbates the problem, because the design needs to take into account the worst case. As technology scales towards nano-scale and with the prevalence of having multiple voltage domains on the chip, voltage stacking offers an alternative in Power Delivery Network (PDN) design that alleviates conventional power delivery inefficiencies.

The first part of this dissertation explores different types of existing level shifters suitable for a voltage stacked logic, their optimal sizing, and the effect of PVT variation on delay and energy consumption.

In the second part of the dissertation, instead of inserting an SRAM into a voltage domain, as it is the common case, the SRAM logic itself is divided into multiple domain. The symmetric logic of SRAM is leveraged for a stacking technique and is divided into two logic domains, and the supply voltage  $V_{dd}$  is doubled. The supply voltage  $2V_{dd}$  will distribute evenly

between the stacks and the current demand will decrease up to half. Hence, the same amount of power is delivered, but with half the current.

The third part of this dissertation builds upon the idea of a floating voltage level in a voltage stacked system and on the observation that slower transistors have higher impedance in the presence of process variation. This chapter offers a GPU stacking method based on voltage stacking to manage the effects of process variation and improve the power delivery simultaneously. The evaluation conducted in this dissertation considers Near Threshold Computing (NTC), because the effects of process variation are more severe in this scenario, however, the technique can be applied without the use of NTC. Using GPU Stacking brings the chip distribution closer to the nominal, *i.e.*, no process variation, and is shown to be better than simply using multiple clock domains, which is the current state-of-the-art.

The final contribution of the dissertation looks at SRAM design, specifically into reducing voltage and timing margins. I propose a timing speculative SRAM that extends the existing Replica Bit-Line (RBL) technique to detect read timing failures. And to protect it from incorrect write operations, the SRAM decode logic is extended. The Replica-based Timing Speculative SRAM (RTS) is evaluated as an energy and area efficient design alternative to prior techniques such as Razor-enabled SRAMs.

Dedicated to my parents, Maryam and Hossein

### Acknowledgments

The journey of my doctoral studies has been one of the most demanding and yet transformative and rewarding phases of my life. It truly enriched both my academic and my personal life and there are number of people I would like to thank for their immeasurable support and guidance.

Doctoral studies are known to be inherently challenging, and there were many times when I lacked inspiration and energy, however, I was surrounded with family and friends who inspired me and encouraged me to stay positive and continue with persistence. My sincere thanks goes to my advisor, Professor Jose Renau, who never fails to inspire, motivate, and provide guidance. His vast knowledge of computer architecture and his multi-angle research interest opened the door for me to pursue various projects which helped me learn different languages, design techniques, and problem solving skills.

I would like to express my gratitude to my committee members, Professor Matthew Guthaus and Professor Jishen Zhao, who kindly accepted to serve on my dissertation committee. Professor Guthaus has provided me with valuable feedback and research guidance throughout the years. Taking his VLSI courses and seminars has helped me immensely in my research.

During my time as a Ph.D. student, I have been involved in various projects, some of which are not included in this dissertation, yet they have been a product of collaborative efforts with MicroArchitecture Santa Cruz (MASC) laboratory colleagues whom I would like to acknowledge. Rafael Trapani and I have collaborated on a few projects related to "Fluid Pipelines", a repipelining idea applied to retry-based or elastic pipelines and we have published our results in IWLS'16 [80] and ICCD'16 [79], and presented a poster in DAC'15 [78]. Our most recent collaboration on "Level Shifter Design for Voltage Stacking" will be presented at ISCAS'17. I would like to thank Dr. Ehsan Ardestani and Dr. Gabriel Southern with whom I have collaborated on a "Thermal Sampling" project which resulted in multiple peer-reviewed publications: ISLPED'12 [33] and TCAD'13 journal [34]. These projects have strengthened my knowledge of VLSI design and architecture design. And I will be forever grateful to them for such rich joint efforts.

To all my dear colleagues in the MASC Laboratory, Gabriel, Rafael, Ehsan, Daphne, Michael, Ian, Sina, David, Raj, Jason, Tom, Alamelu, Ethan, Blake, Akash, and Ramesh, thank you for the stimulating discussions, for the sleepless nights we were working together before deadlines, and for the positive environment you helped create which made the long working hours untiring.

The continued love and support that I have received from my family over the course of my doctoral studies has been an integral part of my journey. I am thankful to my husband, Mehdi, for always encouraging me to focus my full energy on my research and for always being patient and compassionate when I worked long hours for days and months. Last but not least, I am thankful to my brother and sister for continuously sending me positive energy. I could not have made this journey without all of your help.

## **Chapter 1**

### Introduction

The power delivery network is an integral part of the chip design where it has to be robust enough to ensure every device on the chip accesses stable voltage, and meets the timing and functionality requirements. One of the challenges in current SoC design is that there is not a single power domain on the chip, and the number of domains continues to grow as the technology node scales down. As these voltage domains are sharing the same piece of silicon and routed through the same package, they need to be optimized without jeopardizing the voltage drop [72].

One of the most effective techniques for reducing the power consumption is dynamic voltage scaling [86]. Since the dynamic power dissipation in a digital circuit is cubically proportional to the supply voltage, lowering the supply voltage will decrease the dynamic and short-circuit power dissipation [31]. However, it will increase the propagation delay of the circuit and require slowing down of the clock frequency of the circuit, leading to an overall quadratic reduction in the energy to complete a task [86]. As a result, the supply voltage of the components present in the critical path cannot be modified due to speed constraints of the de-

sign. One way to overcome this problem is to use multi-VDD systems [49], where components present in the critical path will work with the standard supply (VddH) and those present in the non-critical path will work with the scaled-down supply voltages (VddL). This leads to different voltage islands, and in order to communicate among each other, an interface circuit is required for voltage level conversion. These circuits are called level converters or level shifters [31, 63]. Also, in a chip with multiple supply voltages, there is need for extra voltage regulators, either on-chip or off-chip DC-DC converters suffer from slow voltage transition times, while the high board-level footprint and system cost limit the number of voltage domains that can be implemented. On-chip voltage regulators enable fast voltage transition times and facilitate multiple voltage domains, but such regulators suffer from low conversion efficiency, especially for high step-down ratios [52].

In addition to adding propagation delay, lowering the supply voltage leads to a rapid increase in the supply current requirements. With increasing current transients and average current levels, more on-chip decoupling capacitance is required while the resistance and inductance of the power distribution network (including on-chip wiring, pins, sockets and connectors) must be kept stringently low for supply integrity. High current requirements also exacerbate on-chip electromigration concerns [66,81], reduce efficiency of voltage regulators [7,53], increase voltage noise and losses due to parasitics [25, 52], and increase the number of dedicated power pins [87].

Voltage stacking is an alternative to delivering power in a multi-VDD system that mitigates the aforementioned challenges [25, 52, 87]. Voltage stacking uses the concept of charge recycling [66] and delivers power to logic blocks "stacked" or connected in series as opposed to the usual parallel scheme. A high voltage is applied to the system and divided to deliver power to each of the logic blocks by charge recycling. Using the stacking technique draws less current to the stacks (voltage domains) without altering the original power budget. Voltage stacking greatly reduces the amount of current drawn. However, it presents a challenge in stack load balancing. If there is current mismatch between the stacks, voltage noise will be introduced in the stacked architecture. Hence, it is a challenge to keep the loads in stacks balanced. Prior approaches for voltage stacking relied on extra voltage regulators to deliver stable voltage to each level [25, 52]. This is mainly required because those approaches applied voltage stacking to full cores that were often running different applications.

Voltage stacking can be applied to SRAMs. SRAM is an indispensable part of most modern Very-Large-Scale Integration (VLSI) designs and dominates silicon area in many applications. 20% of chip area is taken by SRAMs and that is when up to 60% of the total active chip area is taken by memories, which translate to a large amount of chip power consumption [2, 64]. In SRAM voltage stacking the logic can be divided into stacks with a much better balancing than what is observed in a full core. If the activity and power consumption in the voltage stacks are balanced, the shared voltage rails are less susceptible to noise. I leverage the SRAM structure to show how the stacking technique benefits memory subsystems.

The second proposal for voltage stacking application is to use it to compensate for process variation. Process variation affects transistors so that slower transistors will present higher impedance. I will show that assuming balanced activity, and a floating rail between stacking levels, stacking transistors with opposite variation would create a "natural compensation mechanism, because the slower transistor would have higher voltage drop. The challenge in such a scenario would be to guarantee the balanced activity. GPUs parallelize the workload and maintain the performance level across multiple processing units (PEs), and thus are an ideal

candidate for this application.

Power dissipation can be reduced by other techniques in SRAMs such as removing the timing guardbands with the support of an error detection logic. SRAMs are failure prone due to PVT variations and timing guardbands keep SRAMs less sensitive to such variations. However, strict guardbands make it more challenging to meet the frequency requirements, and in that regard SRAMs are overdesigned. There is a demand for architectural alterations which ease the frequency margin without requiring large area or power overhead. We leverage the existing RBL technique to detect timing errors and offer power savings without additional area overhead and design complexity.

In this thesis, I present two different applications and evaluations of voltage stacking, first as a way to reduce overall current in SRAMs operating in nominal voltage levels, with good activity balancing across stack levels and then using GPUs at the near threshold region, to compensate for process variation. I also present a power efficient Replica Bitline Column-based timing speculative technique for SRAMs.

Chapter 2 surveys existing research on level shifter designs suitable for voltage stacked systems. The analysis includes a Pareto optimal plot of existing designs (considering performance, power, and area) and evaluates the robustness of designs while undergoing process variation such as variation of effective length, width, and threshold voltage.

Using one of the level shifters in Chapter 2, I propose a novel voltage stacking technique for SRAMs in Chapter 3. The typical solution to has been to avoid stacking SRAMs or stack the whole SRAM without leveraging the internal structure which happens to be suitable for voltage stacking. This chapter presents the design process of a voltage stacked SRAM, the implementation of the level shifters in the design, and the evaluation of stacked versus nonstacked SRAMs in terms of energy consumption. This is the first work to propose voltage stacking with a floating voltage rail.

Chapter 4 uses the efficiently stacked SRAM design from Chapter 3 in a GPU environment operating at near threshold voltage. For the first time, this voltage stacking technique is used to compensate for process variation in GPUs. This chapter includes details on how to stack with uneven voltage levels, how to mitigate process variation in NTC, and how to configure the design, post-silicon.

Chapter 5 presents the final contribution of the thesis, a novel timing error detection scheme with minimal area and power overhead. It shows how to leverage an existing RBL technology to detect read timing errors due to process variation with minimal area and power overhead.

Finally, Chapter 6 concludes how power consumption limitations in current architecture design leave researchers in search of methods to design in a power-aware fashion, while the complex and intensive computations will not allow them to compromise performance. This chapter recapitulates elements from previous chapters to further emphasize the need for simple yet novel ideas such as stacked architectures to ease the power delivery and management in chip power network design cycle.

5

## **Chapter 2**

# Level Shifters for Voltage Stacked

## Architectures

### 2.1 Introduction

Using a multi-VDD system is an alternative to voltage scaling technique. It counteracts the negative impact on performance, because the critical path components will continue running at  $V_{dd}$  level while non-critical components run at a scaled down  $V_{dd}$  [63]. In a multi-VDD system, when the DC current flows from a low voltage gate to a high voltage gate, the voltage is not sufficient to turn the PMOS "ON" and therefore, the PMOS in the high voltage gate is weakly "ON" conducting static current from the power supply to the ground. The level shifters will remove the static current and restore the full voltage swing from VddL to VddH [31].

Designing a multi-VDD system is inherently complex as there are a few challenges in using a Level Shifter (LS) in the system. They dissipate power and add propagation delay. It is

necessary to optimize the LS circuit for minimum energy-delay product to obtain the potential benefit of using multiple power supply domains. As an LS includes both high voltage and low voltage gate, it will require more area and routing resources. For example, when each functional block on a die needs a different voltage for its desired performance, the number of level shifters can easily grow and become a design area overhead. Techniques such as Dynamic Voltage scaling (DVS) have been widely used in digital signal processing elements for reducing energy consumption [86]. And future low-power systems-on-chips (SoCs) are likely to consist of many scalable voltage domains. This requires level shifters to be able to perform at a high speed with low power [63,91].

As in the case of multi-VDD systems, voltage stacked systems require level shifters for inter-level communication [25, 53]. Traditional level shifters are inserted to translate or shift the logic levels from the level supplied by one domain to another level supplied by the second domain. In the context of voltage stacking, the level shifters will have a primary voltage rail which sits at the top and a secondary voltage rail which sits in the middle. When placed in a voltage stacked design, they will shift the both rails, either from GND-midrail to midrail-toprail (low to high level shifters) or from midrail-toprail to GND-midrail (high to low level shifters). Although many designs for level shifters exist, an evaluation of different designs in the context of voltage stacking has not been made, so the trade-offs of different designs are not clear. As the starting point for our research, we evaluate existing approaches of LSs for voltage stacking applications. We are especially interested in delay and power, but area and sensitivity to PVT (Process, Voltage and Temperature) variations are also considered. Each of those parameters may have different importance in different designs. For instance, CoreUnfolding [7] allows an entire clock cycle for level shifting, thus delay is less important. However, it requires a large amount of shifters, which makes area a critical design factor. On the other hand, a voltage stacked SRAM [20] requires minimal impact on timing, but due to the small number of shifters, can tolerate more area overhead per shifter.

The contributions of this chapter are as follows:

- Overview of current level shifter designs.

- Comparison of level shifters in terms of energy, delay, and area.

- Comparison of level shifters in terms of PVT tolerance.

### 2.2 Overview of Level Shifter designs

This section explores some of the level shifter designs that are suitable for a stacked architecture and their operational behavior. Figure 2.1 to Figure 2.4 include the schematics for a mix of LS designs used in this study and each circuit diagram shows how the LS converts Vin "low" to Vout "high". Note that all of the chosen level shifters are bidirectional. This exploration focuses on converting in a stacked architecture where the primary/top voltage rail is 2V and the middle voltage rail is 1V. The signals are shifted from 0-1V voltage domain to operate in 1-2V voltage domain and vice versa.

### 2.2.1 Capacitive-Coupling-based (Conventional)

Gu *et al.* designed the capacitive-coupling-based LS shown in Figure 2.1 for a multistory or voltage stacked power delivery scheme as they did not see the traditional level shifters a good fit for such systems. This LS has a driving inverter, a coupling capacitor, and a receiver with gain stages. Two diodes are connected back to back in order to constrain the voltage swing at the output node of the coupling capacitor (gate and drain are shorted in the NMOS transistors). Since it always settles near the inverter trip point, a signal transition takes place with a minimal size coupling capacitor [25].

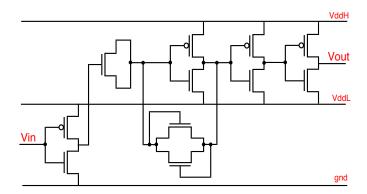

Figure 2.1: Capacitive-Coupling-based (Conventional)

### 2.2.2 Two-Stage Cross-Coupled (TSCC)

The conventional level shifter shown in Figure 2.2(a), is a differential cascade voltage switched logic gate, using a cross-coupled PMOS half latch operating at the higher supply voltage. To overcome the leakage of weakly conducting PMOS transistors, drive strength of NMOS transistor is enhanced. Low Vin input voltage turns mn1 on, which discharges node A to ground and activates mp2. Node B will be pulled up to VddH and the output voltage will be low. Subsequently, when Vin is asserted, mn2 and mp1 are activated shifting the output voltage up to VddH. The drive of the pull-down transistors needs to be much larger than the PMOS transistors to overcome the PMOS latch action driven with a higher supply voltage. It is a simple design suited for super-threshold conversion [26, 32, 58].

In order to achieve full voltage swing, two cross-coupled level-shifting stages are cascaded. The diode-connected NMOS transistor is employed to weaken the pull-up network

in the 2.2(b) structure which expands the convertible input voltage. The operating range is determined by the transistor size and the threshold voltage. As this is a two-stage cross-coupling structure, the area automatically increases in comparison with Cross-Coupled LS [32, 46, 91].

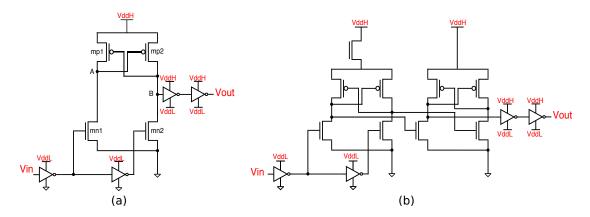

Figure 2.2: (a) Cross-Coupled (CC) (b) Two-Stage Cross-Coupled (TSCC)

### 2.2.3 Wilson Current Mirror (WCM)

Wilson Current Mirror design is based on the topology of another conventional LS called Current Mirror (CM). CM is a unity gain current amplifier which provides output current proportional to its input current at its high impedance output node. It also maintains the output current constant regardless of the load [3, 58]. The high drain-to-source voltage of PMOS transistors facilitates the construction of a stable current mirror, which offers an effective on-off current comparison at the output node. However, for super-threshold input voltage, a high amount of quiescent current occurs. Because of this high power consumption limits the use of the CM [32]. Figure 2.3(a) shows the schematic of the WCM. It uses a feedback PMOS (mp3) to cut off the static current flowing through mn1 and mp1 after switching. This reduces the standby power in the Current Mirror. However, as the source current is cut off, the mirror

current flowing through mp2 is largely reduced, resulting in weakened pull-up strength and a voltage drop at node A. Although the voltage drop increases the source current through the feedback control, the current increase is too small to pull the voltage at node A back to VddH. The output finally stabilizes at a voltage below VddH, which causes large static current and standby power in the output buffer of the LS [91].

### 2.2.4 Stacked WCM

Figure 2.3(b) is an enhancement to the WCM design [48] and uses a stacking technique to reduce the leakage power consumption. There is an addition of 3 NMOS transistors in the pull-down network.

Figure 2.3: (a) Wilson Current Mirror (WCM) (b) Stacked Wilson Current Mirror (Stacked)

### 2.2.5 Tong

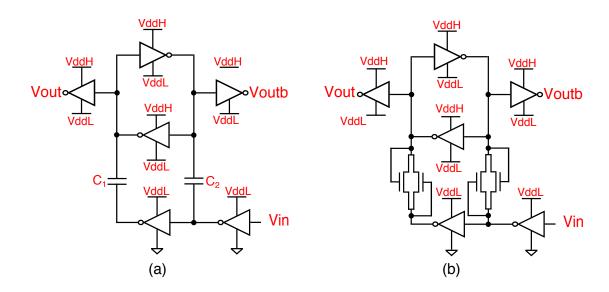

Figure 2.4(a) shows a capacitive-coupled LS that has been used in a 16-core voltagestacked system [53]. The voltage across the coupling capacitor depends on the difference between the two voltage domains but it can be up to  $\approx 2.7$ V, much higher than the gate-oxide breakdown voltage of the transistors available. Hence, this approach requires the use of metaloxidemetal (MOM) capacitors [77]. The original design has one 25fF capacitor on each side of the back to back inverters. If we translate each fF to  $\approx 1 um^2$ , the LS area is considerably large. Our experiments show that the 25fF capacitors are over-designed for an LS, and we were able to reduce that number to  $\approx 2.6$ fF (details in the experimental section), taking into consideration a 30% margin over the minimum operation point. Even with this size reduction, the overall area is still large.

### 2.2.6 Modified Tong

Since the capacitors occupy a large area in Tong LS (Figure 2.4(a)), utilizing it in a stacked domain can be problematic. We have modified it by replacing each capacitor with two NMOS transistors connected back to back, where the drain and gate are shorted (Figure 2.4. This reduces the area, but is expected to increase the power consumption due to the resistive effect added.

Figure 2.4: (a) Tong (b) Mod-Tong

### 2.3 Characterization

### 2.3.1 Transistor Sizing

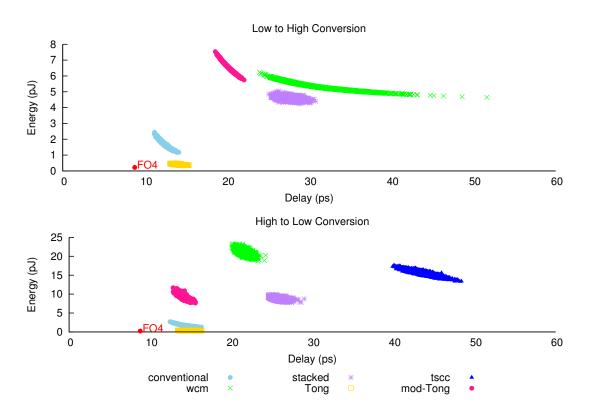

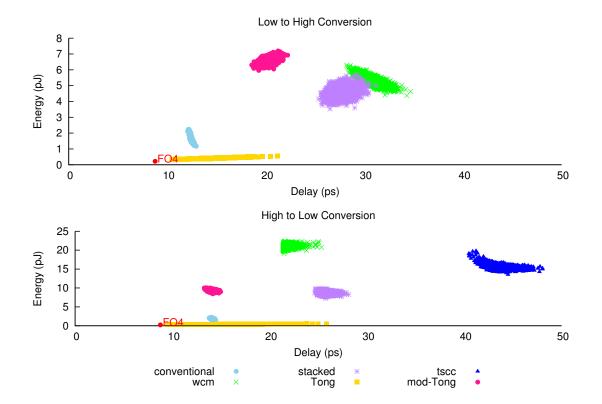

To setup the level shifters for energy, delay, and area comparison, we begin by determining the optimal size for each LS. Our experiments use the NCSU FreePDK, the Open-Access-based PDK for the 45nm technology node [73]. For each CMOS transistor in an LS circuit, SPICE is run while varying the width from 90nm to 720nm. Energy and average propagation delay for an input signal with 5% slew rate are calculated. The resulting points are plotted in 2.5. Since each LS operates bidirectionally, the same experiment is repeated for level down shifters (Figure 2.5).

There is a Pareto frontier for each LS in Figure 2.5 and any of the frontier points could be of interest for a specific LS depending on its application. The minimum energy-delay product (ED) point is our point of interest for optimal sizing of an LS (It is circled in the plot and listed in Table 2.1. The power and delay are measured for a 1GHz input pulse as *active* energy

and *idle* energy, *i.e.*, when the input voltage is kept constant. We estimate the area considering it is proportional to the sum of widths of transistors in the design and the area of one transistor (45nmx90nm).The capacitors in Tong LS dominate the area, 7x the area of Mod-Tong. The top Pareto point is not shown for TSCC down shifter in Figure 2.5, because the delay is more than 250ps.

Figure 2.5: Level-up shifters active energy-delay with different transistor widths

Looking at the Pareto points in table 2.1, there is not a single level shifter that is superior in area, delay, and energy. For instance, if minimum delay in the level up shifters is the main design concern, Conventional and Tong are best choices, however, they impact the area significantly as Tong uses two 2.6fF capacitors and Conventional uses a decoupling capacitor and a diode [10]. Also, when down converting, Mod-Tong presents the best delay, but Tong has the best Energy. Thus, it is not possible to pick a "winner" although Tong, Conventional and Mod-Tong have overall best numbers. TSCC has by far the worst delay in this case.

| name        | Area | Delay (ps) | Active Power (pW) | Idle Power (pW) |

|-------------|------|------------|-------------------|-----------------|

| Conv        | 2790 | 12.37      | 3.07              | 0.53            |

| TSCC        | 2250 | 190        | 6.42              | 0.53            |

| WCM         | 2610 | 30.69      | 6.04              | 0.41            |

| Stacked WCM | 3060 | 27.64      | 5.04              | 0.37            |

| Tong        | 2430 | 14.36      | 0.48              | 0.001           |

| Mod-Tong    | 3330 | 20.09      | 6.57              | 0.75            |

|             |      |            |                   |                 |

### Low to high conversion

### High to low conversion

| name        | Area | Delay (ps) | Active Power (pW) | Idle Power (pW) |

|-------------|------|------------|-------------------|-----------------|

| Conv        | 2790 | 13.99      | 1.79              | 0.24            |

| TSCC        | 1980 | 56.39      | 8.89              | 1.11            |

| WCM         | 2610 | 21.51      | 6.04              | 0.41            |

| Stacked WCM | 1980 | 26.72      | 8.69              | 1.43            |

| Tong        | 2160 | 14.13      | 0.36              | 0.01            |

| Mod-Tong    | 3690 | 9.06       | 14.7              | 3.40            |

### 2.3.2 PVT Variation Effect

An integral deciding factor is LS robustness in presence of Process, Voltage, and Temperature (PVT) variation. To see how temperature affects the delay and energy consumption, we perform an SPICE temperature sweep from 10°C to 90°C. Figure 2.6 shows the trend when converting from high to low.

When shifting down, Tong delay line has a slope of  $0.046ps/^{\circ}C$  and there is less than 5ps difference in delay as the temperature rises up to 90°C. Conventional and mod-Tong have close slopes of 0.068 and  $0.072ps/^{\circ}C$  respectively which translates to less than 10ps delay difference across different temperatures. WCM and Stacked WCM each have 3.4x and 4.3x the slope of Tong LS which is equivalent to delay range of up to 16ps and up to 13ps respectively. When shifting up, as the temperature increases, so does the average propagation delay, however, the delay increase is minimal for Conventional, Tong, and mod-Tong: 0.065, 0.053, and  $0.082ps/^{\circ}C$ . TSCC follows an inverse trend of decreasing delay (22 times the slope of Tong's), where rise and fall delay vary  $\approx$  100ps from start to finish. The delay itself is large as the whole circuit is slower when up shifting than it is when down shifting (Table 2.1). WCM and Stacked WCM each have a slope twice as steep compared to Tong which translates to 10ps delay range.

Active energy has a small decreasing trend during the up and down conversion in all the level shifters except for Tong where the line slope is  $\approx 0pJ/^{\circ}C$ . For up conversion, Tong and Conventional with slopes of 0.003 and  $-0.058pJ/^{\circ}C$  are the best candidates and mod-Tong has the highest slope,  $-0.023pJ/^{\circ}C$ . However, for all the level shifters the range that energy varies is less than 2pJ. During the down conversion as temperature increases, TSCC and Stacked WCM are affected the most with slopes of -0.065 and  $0.093pJ/^{\circ}C$  which translates to an energy range

**Figure 2.6:** Delay vs. temperature. In high to low conversion, as the temperature rises, the average propagation delay will increase. Tong is the least sensitive and TSCC is the most sensitive to temperature variation.

of 7pJ and 8pJ. The least sensitive to varying temperature are Tong and Conventional with slopes of 0 and  $-0.006pJ/^{\circ}C$ . Overall, as the temperature increases up to 90°C, taking delay sensitivity into consideration takes priority over the power sensitivity.

Continuing the PVT variation effect analysis, we use an HSpice Gaussian distribution function with absolute variation to vary the threshold voltage +/-6% with  $3\sigma$  value or 99.7% yield and run 5000 Monte Carlo simulations. In this experiment, we vary NMOS and PMOS threshold voltage by +/-6% and measure delay and energy in the *active* mode. Figure 2.7 is the final plot and an FO4 delay point has been included as a point of reference. When up shifting, the energy variation is a few *pJ*s for all the level shifters , however, the delay variation is not small. For example, WCM delay varies  $\approx$ 30ps. TSCC points have been removed from the up shifters plot, where the delay varies from 100ps to 450ps whereas energy varies from 4.3pJ to 6pJ and is comparable to that of WCM and Mod-Tong. Tong seems to be the least sensitive to the Vth variation due to having capacitances. There is an energy-delay trade-off between Mod-Tong and Stacked WCM. Mod-Tong has a smaller delay variation whereas Stacked WCM power consumption varies less. When downshifting, the energy variation for all is less than 5pJ. And again, TSCC is the most sensitive with the largest delay range of  $\approx$ 10ps. TSCC is a two-stage LS, and therefore, is affected by variation differently. Other LS types have nearly half the number of transistors as TSCC and therefore, their delay range is almost half as TSCC.

Figure 2.7: Active energy-delay: +/-6% Vth variation MC simulations

We repeat the same experiment and vary the supply voltages by +/-5% (Figure 2.8). Unlike previous experiment, Tong seems to be sensitive as the delay varies both in up conversion and down conversion with an 11ps and 18ps range respectively. In up conversion, mainly the delay difference separates the choices. The most unpredictable delay belongs to TSCC, 100ps, and Tong comes in second. However, the energy variation is less than 2pJ for TSCC. Conventional or Mod-Tod might be better choices for down conversion as both energy and delay vary a few units. When downshifting, WCM and Stacked WCM are more sensitive to variation as their energy consumption differs from their Pareto frontier values (Table 2.1). Devices based on capacitance have lower variation on energy, since they tend to not dissipate power.

Figure 2.8: Active energy-delay: +/-5%  $V_{dd}$  variation MC simulations

Since Tong uses two capacitors, variation could affect the operational behavior of the LS. We repeat the experiment by applying variation to the capacitors. Similar to  $V_{dd}$ , the transient sweep is done by using +/-5% variation with  $3\sigma$ . However, it hardly has any effect on

the delay and energy consumption of the LS (Figure 2.9).

Figure 2.9: Active and idle energy-delay: +/-5% capacitance variation MC simulations

### 2.4 Conclusion

In this study, we discussed the trade-offs between different designs of level shifters existing in the literature, focusing on the applications in voltage stacked systems. The performance, power, and area of those designs greatly vary depending on the transistor sizing. To find the optimal sizing for each LS, we run experiments varying transistor widths and obtain a Pareto frontier of delay vs. energy. We choose the minimum energy-delay product point as the optimal point for each LS. In terms of power and delay, Tong [77] offers the best design points, but requires large MOM capacitors, that may make it unsuitable for applications where a considerable number of shifters may be required, therefore, we analyze various designs to show how critical each design factor becomes in different contexts.

# **Chapter 3**

# **Voltage Stacking in SRAMs**

## 3.1 Introduction

Delivering power to the logic in a chip is one of the major challenges in current chip design [52]. As technology scales, the reduction in voltage supply has led to a sharp increase in the total current that needs to be delivered to a chip. Increased current has several draw-backs: reduced efficiency of voltage regulators [53], increase in voltage noise and losses due to parasitics [25,52], increase in the number of pins dedicated to power [87], and electromigration.

Voltage stacking is an alternative method to deliver power to components that are placed in series, rather than in parallel. The charge between the layers is recycled, *i.e.*, it passes through multiple components [66]. Thus, for the same power budget, voltage stacking allows for delivering less current at an increased voltage level. This effectively reduces the total chip current by n, where n is the number of stack levels used in the design [53]. Voltage stacking of CPU and GPU cores has been proposed by several groups to mitigate these problems [25, 52, 87, 88] and it will be further discussed in Chapter 4. In this study we focus on voltage stacking

in the context of SRAMs.

Previous work has focused on the voltage stacking of cores and logic components of a chip, however, chips dedicate a large portion of their area to SRAMs and cache blocks [2], and thus SRAMs account for a considerable amount of the chip power. Research groups have been able to reduce the current drawn from on-chip SRAMs by focusing on reducing their total power consumption [2, 28, 68]. Although reducing the power consumption is a goal by itself, it has limited impact when it comes to reducing the total current. Voltage stacking mitigates such problem by reducing the current drawn by a factor of n, where n is the number of voltage stacks.

The main challenge in voltage stacking is to balance the activity between the stack levels to maintain the voltage at each level roughly constant [52]. This is a challenge that we will address similarly in Chapter 4. An additional Voltage Regulator (VR) can be used in the intermediate node to guarantee that the voltage stays within specified values [53]. SRAMs have fairly predictable activity during operation, making them ideal candidates for voltage stacking. Voltage stacking SRAM banks has been proposed as a technique to reduce the stand-by power of those components [2]. In this approach, when the banks are not in use, power switches change the banks to a stacked configuration where only half  $V_{dd}$  is applies to each bank. This reduces the leakage power during the stand-by mode.

We propose applying voltage stacking to the SRAM structure. To guarantee that the activity is the same across the stack levels, the stacking is done by splitting each word and stacking the word parts which guarantees that the access to both stack levels occurs in the same cycle. Besides the RAM core, sense amplifiers and prechargers are also stacked. Level converters are used where needed to guarantee that each component receives the appropriate voltage level.

Our experiments show that SRAM stacking is able to reduce the current drawn by the SRAM by 40% during write, 36% during read and 44% during standby mode. We will explain that on a circuit level, stacking has multiple benefits such as reducing the IR drop and decreasing number of power rails which has a linear impact on the number of power delivery pins.

To the best of our knowledge, this is the first study that proposes voltage stacking in SRAMs at all times. It reduces the pressure of on-chip power grid design, by reducing the current, especially when combined with core voltage stacking.

## 3.2 Related Work

Voltage stacking has been proposed in the context of CPU cores to increase the efficiency of voltage regulators as it reduces the high current demands for current chips [52, 66]. Voltage stacking does not reduce the power consumption in the chip, but rather allows for operation at higher voltage and lower current, which is beneficial for VR design both by reducing power losses in the VR and reducing its area [52].

Voltage stacking has also been proposed to reduce the number of pins dedicated to power in a chip [87]. Since the number of power pins is roughly proportional to the current, reducing the current by a factor of n (in a n stacked configuration) would result in a reduction in the number of power pins by the same factor.

Gu *et al.* [25] note that voltage stacking can reduce voltage noise (*IR* and  $L\frac{dt}{dt}$ ) and *IR* drop in the power grid, which can ultimately lead to the reduction of power in the parasitics of the system. We also observe that with the reduced noise it is possible to reduce voltage margins,

and increase power savings, although we do not evaluate this scenario in this manuscript, as it would require a parasitics characterization to obtain meaningful results.

Cabe *et al.* [2] proposed to dynamically stack SRAM blocks while they are inactive. This allows for a reduction in leakage power during the stand-by phase of the banks. The technique uses power switches that choose between the stacked mode when in stand-by or regular mode when in regular operation. However, this technique provides a constant  $V_{dd}$ , regardless of the circuit state (stacked or not), which means when stacked, half the  $V_{dd}$  is applied to each stack level, with doubled  $V_{dd}$ , thus the full  $V_{dd}$  is applied to each level at all times. We propose maintaining the circuit stacked during all phases of operation. This allows for a reduction in leakage during all times, as well as other benefits of voltage stacking, such as power pin reduction, VR efficiency increase, and voltage noise reduction.

#### **3.3 SRAM Stacking Model**

Voltage stacking helps reduce the current draw while applying a higher power-supply voltage to the logic blocks in the design. To take advantage of the charge recycling, instead of running the SRAM at  $V_{dd}$ , we divide it into two logic domains connected in series, and apply  $2V_{dd}$ . If each logic domain consumes the same amount of power, the voltage will distribute evenly between them. The logic domain loads however have to be selected in such way that they have well-balanced charge utilization for achieving a high efficiency [66]. If the power consumption of the two stacks is the same, as the voltage supply is multiplied by n, where n is the number of stacks, the current draw will be reduced to  $\frac{1}{n}$ . Two stacks are used and Equation 3.1 shows that theoretically this leads to 50% reduced current in the SRAM.

$$p1 = p2$$

$$V_1 \times I_1 = V_2 \times I_2$$

$$V_1 \times I_1 = 2 \times V_1 \times I_2$$

$$I_2 = \frac{I_1}{2}$$

(3.1)

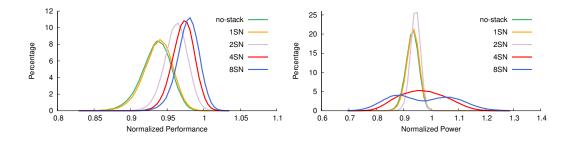

In terms of circuit design, Figure 3.1 shows how the conventional model differs from the stacking model. In Figure 3.1a, the two circuits are running in parallel and the same voltage differential is applied to each, the total current drawn from the power source is then the summation of the current of all the components in the circuit. In Figure 3.1b, the stacks run in series and the configuration reduces the current draw, and the IR drop across the stacked components is reduced by a factor of n where n is the number of circuits in series. The current is recycled through the stacks connected in series.  $V_{mid}$  will fluctuate depending on the load and impedances present in each stack. If the impedances are similar, the  $V_{mid}$  balances in the middle and is the most efficient stacked configuration.

Figure 3.1: Conventional vs. stacked power delivery mode

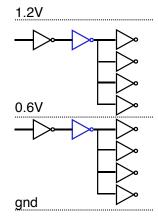

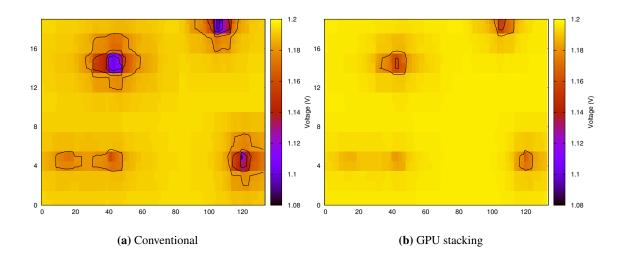

Figure 3.2 shows a high level view of stacked SRAM. The SRAM size is 1Kb, 32 32-bit words, and it has 2 read ports and 1 write port. In order to divide it into two vertical logic domains, we cut the 32-bit wordline in two, which leaves 16 bit for each stack. Bits 0-15 go to the bottom stack and bits 16-31 go to the top stack. Consequently, each stack will have 16x32 bitcells, 16 precharge circuits, 16 write drivers and 3x32 wordline buffers.

The two stacks operate at 0- $V_{dd}$  and  $V_{dd}$ - $2V_{dd}$  where  $V_{dd}$  is 1.1V. The voltage level of all the signals entering the top stack (2.2V) will need to be shifted; hence, level shifters are placed in 3 locations. First, the input data to write drivers has to be converted to the same voltage level as the top stack. The wordlines will pass both stacks in a row of bitcells, therefore, each decoder will drive two wordlines. Second, the top stack wordline voltage level is shifted. To avoid having the wordline be driven by the level shifters, we placed them before the read and write address buffers. Third, the sense amplifier outputs exiting the top stack will have to be converted back to the  $V_{dd}$ ; hence, level shifters are placed right after the sense amplifiers. The read and write address decoders, placed in the middle of the RAM core, are the only components which are not part of the stacked architecture.

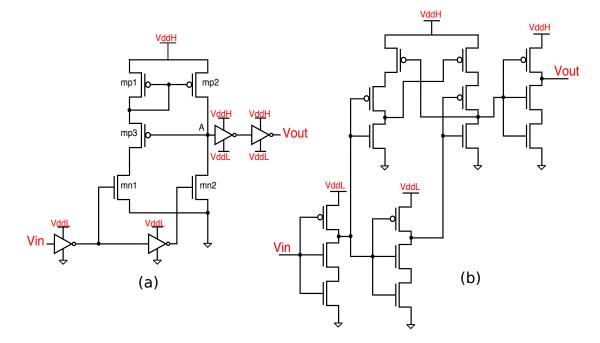

The schematic of the level shifter used throughout the SRAM is shown in Figure 3.2. There are two capacitors C1 and C2 ,which are sized 15fF each. The design is adopted from Lee's 16-core design [53].

#### 3.4 Setup

We implemented our voltage stacking technique on SRAMs generated by FabMem. FabMem is a multiported RAM and CAM compiler for design space exploration and given

Figure 3.2: Voltage stacked SRAM

the configuration it can generate netlists and layouts and estimate read/write delay and energy consumption [71]. FabMem uses the NCSU FreePDK, the Open-Access-based PDK for the 45nm technology node [73].

Using FabMem, we generated an SRAM with a configuration that is similar to the size of a typical Register File: A 2-read 1-write 1Kb consisting of 32 32-bit words. We use one RF for the base case SRAM and another for the stacked version.

A few alterations had to be made to some of the SRAM components such as the sense amplifier and the precharge circuits. In our experiments, we use current latch mode sense amplifier [60] as opposed to the FabMem default voltage controlled sense amplifier circuitry, because the current latch mode works with the stacked SRAM design. The precharge circuitry used is shown in Figure 3.2.

All the energy related measurements were taken using Synopsys HSpice version I-2013.12-1.

# 3.5 Evaluation

In this section, we discuss the overall results and share insights as how effective SRAM voltage stacking is.

The two SRAM netlists are simulated using HSpice at  $V_{dd} = 1.1V$  with frequency of 500MHz. The simulation results compare the stacked SRAM against the non-stacked SRAM, which we refer to as the base case in this section. Figure 3.3 shows the energy consumption breakdown. Each colored section of the histogram bar shows the total energy consumption of a particular component. The energy numbers pertain to the logic that is stacked. For instance, the level shifters are placed before the buffers driving the wordlines, therefore, these buffers are part of the stacked logic and the read and write address decoders are not. We refer to the read and write wordline buffers as "decoder".

Figure 3.3: Energy breakdown in voltage stacked SRAM vs. non-stacked.

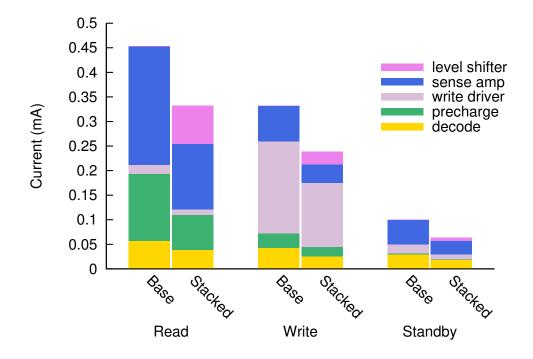

The simulation includes periods of initialization, write, read, followed by standby. Each write or read period consists of 10 write or read operations. Overall, the power consumption increases by 20%, 23%, and 13% during write, read, and standby modes respectively. During the read operations, the stacked SRAM consumes a bit more energy than the base case, however, looking at the breakdown, the excess energy usage is due to having the level shifters in the top stack. For instance they draw 8% more current during the read operation than the precharge circuits. The other components such as sense amplifier, precharger, decoder, and write drivers almost consume the same amount of energy. As the SRAM size increases, the overhead of level shifters will become less of an issue. The standby energy consumption is the same meaning at  $2V_{dd}$  the SRAM has the same leakage as operating at  $V_{dd}$ . Figure 3.4 shows the current consumption in the top stack of the stacked SRAM versus the base SRAM. Overall, stacked components draw 40%, 36% and 44% less current than the base components during the write, read, and standby modes. Comparing the current and energy breakdown plots for the write operation, we notice that that the write drivers do not have a balanced load, leading to less than expected current savings. For larger SRAMs however, we would expect that this gap will decrease, since the relative power of write drivers are smaller.

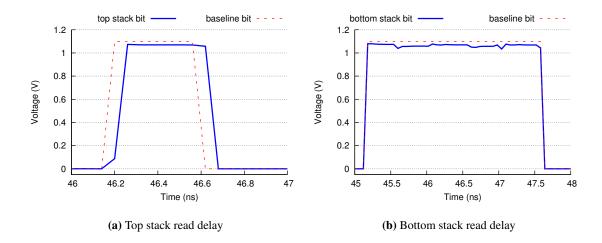

We also evaluate the impact of stacking on the SRAM performance. For bitline transitions shown in Figure 3.5, we simulated both SRAMs with 1GHz frequency. Two read output bits, are selected from the top and bottom stacks to show how level conversion affects the SRAM read speed in each stack. As Figure 3.5b shows, there is no delay for the bottom stack bit, however, Figure 3.5a shows the stacked bit has some delay when transitioning from 0 to 1. It is a 60*ps* delay which translates to 6% frequency hit. In reality, the performance hit should be even smaller, because the stacking can be applied to the slower part of the SRAM. We did not

Figure 3.4: Current breakdown in voltage stacked SRAM vs. non-stacked.

perform this optimization, because it is layout dependent. Thus, SRAM stacking has limited impact on performance.

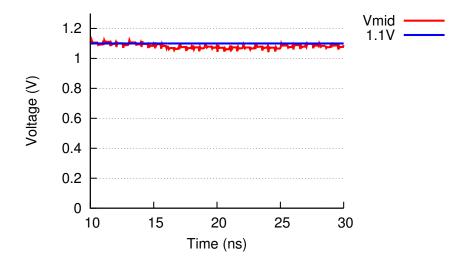

Finally, we evaluate the voltage noise level in the  $V_{mid}$  due to the fluctuation in the load. One of the challenges in voltage stacking is load balancing. As expected in a stacked architecture  $V_{mid}$  fluctuates and introduces noise to the power deliver network. Since we have used an SRAM architecture, the nature of the circuitry allows for a division of stacks in such way that the  $V_{mid}$  is maintained within an acceptable range. Figure 3.6 shows the stability of  $V_{mid}$  during initialization, write, and read operations. In the case of  $V_{mid}$  noise, one option is to place a voltage regulator at  $V_{mid}$  to guarantee that  $V_{mid}$  stays at  $V_{dd}$  which is 1.1V. In our designed SRAM, the fluctuations observed are within the acceptable range and thus there is no need for an extra voltage regulator, as it is used in stacking for cores [52].

**Figure 3.5:** Stacking introduces a 60ps delay in the top stack output bitline, which is equivalent to 6% performance hit.

Voltage stacked SRAMs have a small area impact; the level shifter is the main source of overhead. Even in a small SRAM, such as the one we evaluate, the level shifters represent less than 6% of the transistors.

Figure 3.6: Voltage noise for stacked SRAM is within acceptable levels, even without a voltage regulator.

# 3.6 Conclusion

As the technology scales, and power supply is reduced, delivering power to the logic on a chip becomes a major challenge as its current demand increases drastically. Increased current has many drawbacks [25,52,53,87]. Voltage stacking is an alternative method to deliver power to components on a chip that is stacked or placed in series. A large portion of the chip area belongs to SRAMs and caches. In this research study, we focus on SRAMs and stack an SRAM the size of a typical Register File. Our design keeps the SRAM in stacked mode at all times. Other research work have been proposed where they keep the SRAM banks in stacked mode during the standby mode [2]. We divide the SRAM words into 2 stacks and are able to reduce current by 36%-44% while not letting energy consumption be more than 23%. In addition, doubling  $V_{dd}$  and reducing the current could save as much as 10% power from the increased VR efficiency [52], but this was not considered in this paper.

# **Chapter 4**

# **GPU NTC Process Variation Compensation** with Voltage Stacking

## 4.1 Introduction

Near Threshold Computing (NTC) can improve energy efficiency by further reducing the operating voltage [19]. It has been shown that the performance impact resulting from NTC can be mitigated through parallelism. An ideal candidate for such operation is a GPU [9, 19]. Nonetheless, NTC complicates power delivery. It requires more current to flow at a lower voltage [52] and the increased current flow reduces the efficiency of the power delivery circuitry. It also makes the system more sensitive to process variation [39].

To manage the additional sensitivity to process variation (PV) introduced by NTC, some researchers have proposed frequency scaling or having multiple voltage domains. Having multiple voltage domains requires additional power rails which will further exacerbate the current delivery problem. Frequency scaling [40] addresses some of the issues regarding our proposal model which we will address in detail in Section 4.3.

In Chapter 3, we discussed why voltage stacking is a beneficial alternative power delivery mechanism and how on a circuit level it reduces the current drawn from the main Voltage Regulator (VR) that makes it more efficient taking less area. Not only has it been applied to SRAMs, but also it has been proposed in the context of CPU cores [52], and GPU cores [88].

Voltage stacking can be analyzed from another interesting angle that it can compensate for the process variation effects. The proposed GPU stacking methodology lets the voltage node between the stacked elements ( $V_{MID}$ ) float<sup>1</sup>. This floating node is the key to process variation compensation. GPU stacking alleviates the current delivery challenges, and intrinsically mitigates process variation effects without requiring multiple voltage domains. GPU stacking automatically creates a voltage domain per level in the stack without the cost of multiple power rails. We build on top of this premise, and discuss how it can be leveraged for managing process variation. To the best of our knowledge, this is the first time that voltage stacking has been utilized in NTC GPUs.

Voltage stacking of many cores has its own challenges, among which is the load mismatch between the stacked cores [7]. Cores go through different phases while running applications, which can result in transient impedance mismatch of the stacked cores, and yield timing failures. As a result, stacking is successful when the cores have a matching workload. GPGPUs are instances of such designs. Not only are the cores identical, but the applications running on them are roughly homogeneous<sup>2</sup>.

<sup>&</sup>lt;sup>1</sup>For safeguarding reasons, a few voltage regulators are used to cap the maximum and minimum levels of voltage but the voltage does float between maximum and minimum values.

<sup>&</sup>lt;sup>2</sup>Even though divergence exists in modern GPUs, the amount of load mismatch observed in traditional GPGPUs benchmarks can be handled by our technique, as it will be shown in our evaluation.

The evaluation of GPU stacking is carried out in the near threshold region. Although the use of this method in the near threshold region is proposed, it is not a requirement. The use of NTC in this research study is justified by the increased sensibility of NTC to process variation effects. The first part of this experiment consists of finding the ideal GPU configuration for the NTC region. By carefully sizing the GPU to NTC, power consumption is reduced by 43% with only 4.8% performance degradation compared to the baseline.

Based on our experiments, there is a potential for self balancing in the stacked configuration. We observe that stacking of cores with opposing process variation trends is a better choice to gain the best self balancing results. This is more likely to happen when there is a certain distance between the stacks. This study proposes the stacking of SIMD Lanes, because having a large number of lanes provides more opportunities for PV compensation. Analyzing several PV maps, GPU stacking shows that it is able to deliver, on average,  $\approx 80\%$  of the nominal performance in a multi-frequency domain scenario (as opposed to  $\approx 60\%$  in a non-stacked configuration).

The floating  $V_{mid}$  node could be a source of problems in cases of extreme load mismatch, or high temperatures. Thus, we propose the use of Dummy Activity (DA), and a small voltage regulator to keep the voltage within safe operational margins (*i.e.*, to avoid voltage starvation in one of the levels). We use SPICE simulations to verify the reliability of the power delivery network (PDN), and show that GPU stacking does not incur extra voltage noise. In our simulations, DA and the additional VR were not required, given the stability of the operational voltage.

The following lists the contributions of this research study:

• The first study to show how voltage stacking alleviates process variation effects.

- The first study proposing stacking with an uneven voltage division  $(V_{MID})$ .

- A study to propose a technique to make the post-silicon configuration of the design feasible.

The remainder of this chapter is organized as follows: We start by presenting the related work in Section 4.2, then in Section 4.3, we investigate, with an example case, how Voltage Stacking can mitigate the effects of process variation, and discuss the application of this technique in a GPU architecture. In Section 4.5, the trade-offs of designing a GPU at near threshold are discussed, and the baseline architecture is defined. Section 4.4 and 4.6 present the evaluation setup and the results for the conducted experiments. And finally, Section 4.7 concludes the findings of this study.

### 4.2 Related Work

**GPU Stacking:** As supply voltage decreases, the efficiency of power delivery components degrades. On-chip voltage regulators [44] have been proposed to increase the PDN efficiency, as well as the series configurations of units rather than parallel [25, 52, 66]. Such configurations are known as Multi-Story Power Delivery [25], charge recycling [66], or mainly as voltage stacked systems [52]. Our proposed technique depends on a series configuration of cores, yet for a different purpose. Such configuration is referred to as GPU stacking throughout this dissertation. Note that no previous research on voltage stacking exploits the stacking method to control or neutralize process variation effect.

**Process Variation:** Process variation increases as feature size shrinks. And lowering  $V_{dd}$ , as a power management technique, further exacerbates the effects of process variation.

Karpuzcu *et al.* [39] built a model on top of the VARIUS [70] tool which models process variation for logic and memory cells, while targeting NTC [9, 19], called VARIUS-NTV. They observed significant variation in core frequency, and power consumption as a result of process variation.

Lee *et al.* study the impact of frequency variation on the throughput of a GPGPU [50]. Adaptive Body Bias (ABB) leverages the power-performance trade-off to manage process variation effects [84]. Slower devices due to process variation, can run faster by consuming more power, and vice versa. Adaptive Supply Voltage (ASV) is another technique in managing process variation [12]. Supply voltage of a region in the design can be adjusted to compensate for performance loss due to variation. ABB and GPU stacking are orthogonal techniques, and could be used together, although ABB efficiency is expected to reduce with technology scaling [40]. Our proposed technique intrinsically performs ASV.

**NTC:** An extensive amount of research targets increasing the power/energy efficiency of processors. Apart from the many proposed techniques of how to reduce the utilization of resources [18, 59], or how to promote the use of more power efficient structures [13, 15], there are a significant number of proposals that attempt to utilize the power-performance trade-off. DVFS and Power Gating are among the techniques widely studied at an architectural level, for the same purpose [29, 30]. Intel Turbo Boost technology is another example of utilizing voltage and frequency scaling to adapt to runtime conditions.

Dreslinski *et al.* [19] study devices for near threshold operation, and Chang *et al.* propose the optimization of device parameters for NTC [9]. They propose a slightly modified SRAM cell to address the stability challenges introduced in near threshold regions. Lower  $V_{dd}$ exacerbates the effects of process variation. In the context of NTC, again we refer to VARIUS- NTV model built by Karpuzcu *et al.* [39] which models process variation. The same team published another study of NTC in many cores where they argued in favor of fine-grained core assignment and DVFS [40].

**Energy efficiency in GPGPUs:** With the rising popularity of GPGPUs, several research groups discuss strategies to make them more energy efficient [24, 51, 69, 89]. Lee *et al.* study the impact of frequency variation on the throughput of a GPGPU [50]. This methodology, however, is the first to extend the evaluation to NTC trade-offs and it is an extension of previous research addressing NTC challenges. Massive data parallelism and extremely repetitive nature of the GPGPU applications is leveraged to adapt the operational region and configuration to the runtime application demand.

# 4.3 GPU Stacking

Revisiting Figure 3.1, if the GPU core units in the stack consume the same amount of power, the voltage across each GPU core will be equal to  $V_{dd}$ . Because as less current flows through the system, the power delivery subsystem could operate more efficiently. However, in the context of GPUs, balancing the overall load across the stacked elements, is not as easily manageable as SRAMs. This is because a change in behavior of one core directly affects the other core. If these changes have significant magnitude, they could result in timing failures as one core could throttle the power delivery to the other. Nonetheless, stacking exhibits promising behavior in the presence of process variation that can be leveraged towards more variation resilient designs.

Before presenting the final model, we formulate the high level effects of process vari-

ation expected in a circuit and explain the high level mechanisms by which voltage stacking can compensate for the effects of process variation. Then, an example case is presented that quantifies how much PV is compensated under simplistic and idealized scenarios. We conclude our preliminary findings and apply them to the GPGPU architecture to mitigate the PV effects. The section ends with a discussion of the architectural choices made for managing extreme cases.

#### 4.3.1 Process Variation

VARIUS-NTV uses Equation 4.1 formulates the gate delay for a MOS transistor, where  $V_{dd}$  is the supply voltage to the core,  $L_{eff}$  is the effective channel length, *K* and *M* are fabrication constants [39].

$$delay \propto \frac{V_{dd} \times L_{eff}}{K \times ln^2 (e^{M \times (V_{dd} - V_{th})} + 1)}$$

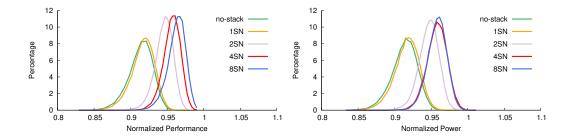

(4.1)