## **Lawrence Berkeley National Laboratory**

#### **Recent Work**

#### Title

PROPOSED THIN FILM ELECTRONICS FOR A-SI:H PIXEL DETECTORS

#### **Permalink**

https://escholarship.org/uc/item/1kb3q106

#### **Authors**

Perez-Mendez, V. Cho, G. Fujieda, I.

#### **Publication Date**

1989-04-01

# Lawrence Berkeley Laboratory

UNIVERSITY OF CALIFORNIA

## Physics Division

RECEIVED

LAWRENCE

BERKELEY LABORATORY

OCT 9 1989

LIBRARY AND DOCUMENTS SECTION

Proposed Thin Film Electronics for a-Si:H PIXEL Detectors

V. Perez-Menáez, G. Cho, I. Fujieda, S.N. Kaplan, S. Qureshi, and R.A. Street

**April 1989**

## TWO-WEEK LOAN COPY

This is a Library Circulating Copy which may be borrowed for two weeks.

#### DISCLAIMER

This document was prepared as an account of work sponsored by the United States Government. While this document is believed to contain correct information, neither the United States Government nor any agency thereof, nor the Regents of the University of California, nor any of their employees, makes any warranty, express or implied, or assumes any legal responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by its trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof, or the Regents of the University of California. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof or the Regents of the University of California.

# Proposed Thin Film Electronics For a-Si:H PIXEL Detectors

V. Perez-Mendez, G. Cho I. Fujieda, S.N. Kaplan, S. Qureshi

Lawrence Berkeley Laboratory, University of California Berkeley, California 94720

and R.A. Street

Xerox Palo Alto Research Center, Palo Alto, California 94305

This work was supported by the Director, Office of Energy Research, Office of High Energy and Nuclear Physics, Division of High Energy Physics, of the U.S. Department of Energy under Contract No. DE-AC03-76SF00098.

## Content

| I   | Prop   | osed    | System    |             |           |           | 3   |

|-----|--------|---------|-----------|-------------|-----------|-----------|-----|

|     | A.     | Detec   | tor       |             |           |           |     |

|     | В.     | Ampli   | ifier     |             |           |           |     |

|     |        | Noise   |           |             |           |           |     |

| II  | Desc   | ription | of T      | FTs         |           |           | 1 5 |

|     | Α.     | A-Si:I  | H TFT     | with reduc  | ed lithog | raphy     |     |

|     | В.     | High    | Temperat  | ure Polysi  | licon MC  | SFET      |     |

|     |        | _       | al a-Ŝi:H | •           |           |           |     |

| ш   | Me     | asurem  | ients of  | n a-Si:H    | TFTs      |           | 17  |

|     | A.     | Insula  | ator Thic | ckness      |           |           |     |

|     |        |         |           | nsconductar | nce       |           |     |

|     |        |         |           | Rise Time   |           |           |     |

|     |        | Noise   |           |             |           |           |     |

| IV  | Co     | nclusio | n         |             |           |           | 23  |

| Re  | feren  | ces     |           |             |           | . <b></b> | 25  |

| Api | pendi  | x A     | Notatio   | on          |           |           | 27  |

|     | pendi: | х В     | Noise     | Equations   |           |           | 29  |

#### I Proposed System

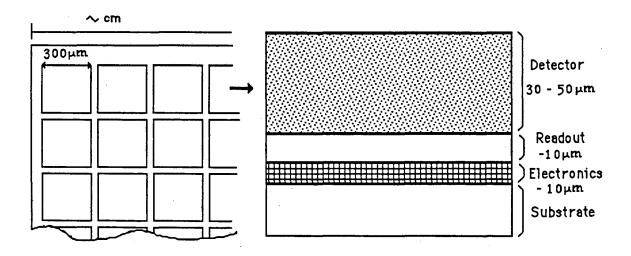

We describe a proposed 2-D PIXEL detector and its electronic circuit. The dimensions of each PIXEL are  $300 \times 300 \ \mu m^2$ . Signal-to-noise ratio is in excess of 8 when connected to an a-Si:H TFT with  $g_m = 3$ , and 10 when a polysilicon PMOSFET with  $g_m = 50$  is used. For both cases we assume an RC-CR shaping time of 1  $\mu$ sec. [1] The signal amplification and readout circuit will be placed under the detector and can consist of 5 or 6 FETs and some passive elements. For these amplifiers we consider the following 3 choices.

- 1. A-Si:H TFTs with advanced lithographic technique (4 μm)

- a) 4 A-Si:H FET Amplifier

- b) 5 A-Si:H FET Amplifier

- 2. High temperature polysilicon MOSFETs (4 FETs)

- 3. Vertical a-Si:H TFTs

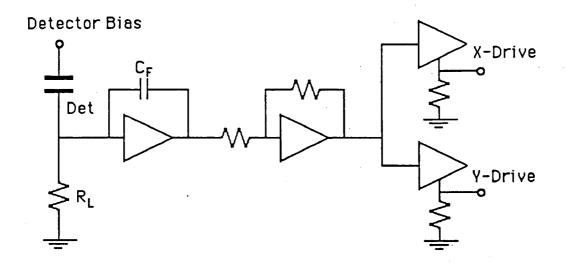

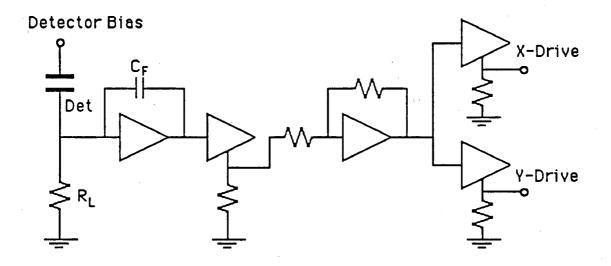

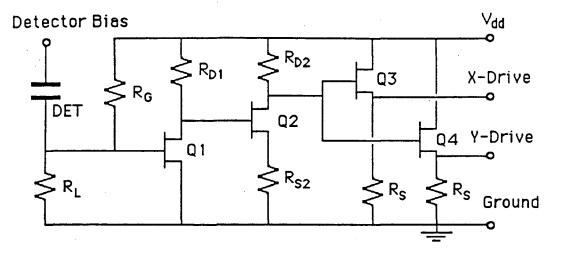

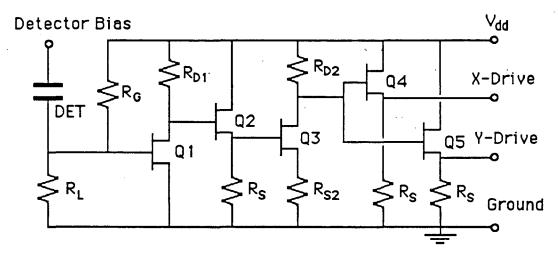

Table 1 is a summary of the properties of several noncrystalline-Si TFTs. Figure 1 shows a schematic diagram of the 2-D PIXEL array. Figure 2 shows a schematic diagram of the electronics.

Fig. 1. Schematic Diagram of 2-D PIXEL Array

Table 1 Estimated Properties of Thin-Film-Transistors (TFTs)

| Type of T.F.T.                | Electron<br>Mobility<br>(cm <sup>2</sup> /Vsec) | W/L          | g <sub>m</sub><br>(Υ\ΑΨ) | Frequency<br>Limit (3db)<br>(MHz) | Noise * (1 µsec) (electrons)   | Rediation<br>Resistesnce |

|-------------------------------|-------------------------------------------------|--------------|--------------------------|-----------------------------------|--------------------------------|--------------------------|

| a-Si:H<br>10 µm Tech.         | 0.3 - 0.8                                       | 2-20         | 2 - 4                    | 1-3                               | <b>&gt;</b> 350                | Excellent                |

| a-Si:H<br>4 µm Tech.          | 0.3 - 0.8                                       | 2-50         | 2 - 5                    | 3-10                              | <b>&gt;</b> 350                | Excellent                |

| a-Si:H<br>Vertical            | 0.3 - 0.8                                       | 100-<br>1000 | 30-300                   | 5-10                              | ≥1000                          | Unknown                  |

| Polysilicon<br>400°Anneal     | 10-20                                           | 2-20         | 3-30                     | 10-20                             | ≥ 500<br>(expected)            | Unknown                  |

| Polysilicon<br>900°Anneal     | 50-100                                          | 2-20         | 15-150                   | 50-100                            | 300<br>(PMOS)<br>480<br>(NMOS) | Unknown                  |

| c-Si on<br>Insulator<br>(SOI) | 1000-<br>1500                                   | 2-20         | 1000-<br>2000            | <b>&gt;</b> 100                   | Same as<br>c-Si FET            | Excellent                |

<sup>\*</sup> Noise values are given for a typical size of each TFT with 1  $\mu$ sec CR-RC shaping amplifiers. However these measurements are preliminary because we have not measured enough samples.

#### PROTOTYPE AMPLIFIERS

a) 4 FET Amplifier

b) 5 FET Amplifier

Fig. 2. Schematic Circuit Diagram of PIXEL Electronics

a) 4 FET Amplifier

b) 5 FET Amplifier

Fig. 3. Amplification Stage for 4 and 5 FET Electronics

#### A. Detector

The proposed PIXEL detector has characteristics as shown in table 2. Signal and charge collection are assumed to be generated by minimum ionizing particles.[1]

Table 2 Characteristics of the Proposed PIXEL Detector

| Size             | (μm²)       | 300x300 |

|------------------|-------------|---------|

| Thickness        | (µm)        | 50      |

| $C_{ m DET}$     | (pF)        | 0.2     |

| S <sub>SIG</sub> | (electrons) | 3000    |

#### B. Amplifier

Amplification of the signal charge in the 4-FET amplifier is performed by two FETs. Both FETs are operated in the saturation mode which gives a high output impedance,  $r_0$ , and a low gate-to-drain capacitance,  $C_{\rm gd}$ , which is mainly due to the overlaping area of the gate electrode over the drain contact.<sup>[2]</sup> The first FET is used as a charge sensitive preamplifier by using this inherent gate-to-drain capacitance,  $C_{\rm gd}$ , as a feed-back capacitance,  $C_{\rm F}$ . The equivalent circuit of the amplifier stage is shown in Figure 3-a).

The input voltage signal, V<sub>i</sub>, without the feed-back loop is

$$V_{i} = \frac{Q_{SIG}}{C_{T}}$$

(1)

where  $Q_{SIG}$  is the total signal charge (=  $q*S_{SIG}$ ) and  $C_T$  is the total input capacitance of the first stage amplifer.<sup>[3]</sup>

$$C_{T} = C_{DET} + C_{gs}$$

(2)

A<sub>v</sub> is open loop voltage gain given by

$$A_{v} = -g_{m} * (r_{o} /\!\!/ R_{D1})$$

(3)

and the gain of the first stage (charge sensitive) preamplifier with a capacitive feed back loop is

$$G_1 = \frac{C_T}{C_T + (1 + |A_v|) * C_F} * A_v$$

(4)

The output voltage signal of the first stage, V1, is

$$V_{1} = \frac{Q_{SIG}}{C_{F}} * \left(\frac{A_{v} * C_{F}}{C_{T} + (1 + |A_{v}|) * C_{F}}\right) \sim \frac{Q_{SIG}}{C_{F}} \text{ when } |A_{v}| * 1$$

(5)

The charge-to-voltage conversion gain  $(G_1/C_T)$  can be increased by two methods.

- 1. By decreasing C<sub>F</sub>

- 2. By increasing output resistance

Basically  $C_{gd}$  is determined by the overlapping area between gate and drain of the FET, and its value can be made less than 0.02 pF by 0.5  $\mu m$  overlapping. Also if we underlap the drain, as used in High Voltage TFT designs, then we can expect  $C_{gd}$  to be in the range of a few femto farad.

The second method is limited by the frequency response (RC time constant) of the device which is determined either by the transit time of electrons in the FET channel or the RC value of the output stage. In our case the transit time is of the order of a few tens of nano seconds, so the latter determines the time response. Since the load capacitance from the next stage is the sum of the gate-to-source capacitance and the Miller capacitance of the 2nd FET, selecting the output resistance of the 1st stage is an optimization problem between gain and frequency response.

In the second stage, the voltage gain, G<sub>2</sub>, is<sup>[4]</sup>

$$G_2 = \frac{-(g_o + g_m) * R_{D2}}{1 + (g_o + g_m) * R_{S2}}$$

(6)

where  $g_0$  is the reciprocal of  $r_0$ .

Again,  $G_2$  is limited by the frequency constraint of the entire circuit because it increases the Miller capacitance.

Finally the total output signal is

$$V_o = G_1 * G_2 * V_i$$

(7)

The RC time constant of the amplifier,  $\tau$ , is a product of the total output resistance of the first stage and total capacitance at that point.

$$\tau = (r_o // R_{D1}) * \{ C_{gs} + (1 + |G_2|) * C_{gd} \}$$

(8)

where the second component of the capacitance is increased due to Miller effect at the second stage amplifier.

As a 2nd choice, we propose the 5-FET amplifier scheme shown in Fig. 2-b) and 3-b). In this case we can decrease the RC time constant by a factor of 10 or more because the input capacitance of the 2nd stage (source follower) is only  $C_{\rm gd}$ .

$$\tau = (r_o // R_{D1}) * \{ C_{gs} + C_{gd} \}$$

(9)

The 3rd choice is to use a polycrystalline MOSFET amplifier consisting of 4-FETs. In Table 3 we summarize the design parameters for these three choices of FETs and the calculations of the voltage output and RC time constant,  $\tau$ .

Table 3 Design and Calculated Data for PIXEL Electronics

| Parar              | neters                       | a-Si:H(4FETs)                         | a-Si:H(5FETs)   | Polysilicon(4FETs)    |

|--------------------|------------------------------|---------------------------------------|-----------------|-----------------------|

| L                  | <br>(μm)                     | 8                                     | 8               | 1 2                   |

| W                  | (µm)                         | 250                                   | 250             | 70                    |

| $L_{o}$            | (µm)                         | 0.5                                   | 0.5             | 0.5                   |

| $d_i$              | $(\mu m)$                    | 0.5 (Si <sub>3</sub> N <sub>4</sub> ) | $0.5 (Si_3N_4)$ | $0.1 \text{ (SiO}_2)$ |

| $C_{gd}$           | (pF)                         | 0.015                                 | 0.015           | 0.012                 |

| $C_{gs}$           | (pF)                         | 0.18                                  | 0.18            | 0.21                  |

|                    | $I_{\mathrm{T}}(\mathrm{V})$ | 10.                                   | 10.             | 10.                   |

| $I_D$              | (µA)                         | 15.                                   | 15.             | 207.                  |

| $\mu_{\mathbf{e}}$ | (cm <sup>2</sup> /V)         | s) 0.8                                | 0.8             | 20.                   |

| gm                 | $(\mu A/V)$                  | 3.1                                   | 3.1             | 41.                   |

|                    | en Loop Gai                  | n) 8.8                                | 8.8             | 11.0                  |

| $G_1$              | _                            | 8.5                                   | 8.5             | 10.4                  |

| $G_2$              |                              | 12.                                   | 12.             | 10.                   |

| ro                 | $(M\Omega)$                  | 10.                                   | 10.             | 2.0                   |

| $R_{D1}$           | $(M\Omega)$                  | 4.0                                   | 4.0             | 0.3                   |

| $R_{D2}$           | $(M\Omega)$                  | 4.0                                   | 4.0             | 0.3                   |

| R <sub>S2</sub>    | (ΜΩ)                         | 0.1                                   | 0.1             | 0.01                  |

| $V_i$              | (mV)                         | 1.3                                   | 1.3             | 1.2                   |

| $V_{o}$            | (mV)                         | 130                                   | 130             | 125                   |

| τ                  | (µsec)                       | 1.0                                   | 0.44            | 0.08                  |

Vertical types of a-Si:H TFT can be considered as another choice. The advantage of these devices are their high transconductance,  $g_m$ , and short transit time,  $T_t$ . Here using 7-10  $\mu m$  lithography, channel lengths of 0.3 - 0.5  $\mu m$  can be created by depositing the gate, source and drain metal contacts over each other with spacings determined by the deposition process. Transconductance values higher than 100  $\mu A/V$  have been reported. [5-7] We did not consider this alternative here since the values of  $C_{gd}$ ,  $C_{gs}$ , channel resistance and other parameters were not given completely in the reports available to us.

#### C. Noise

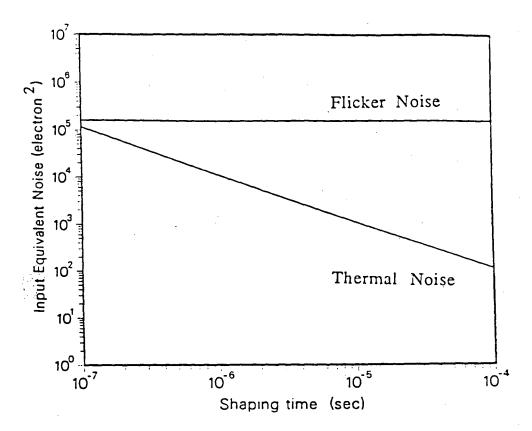

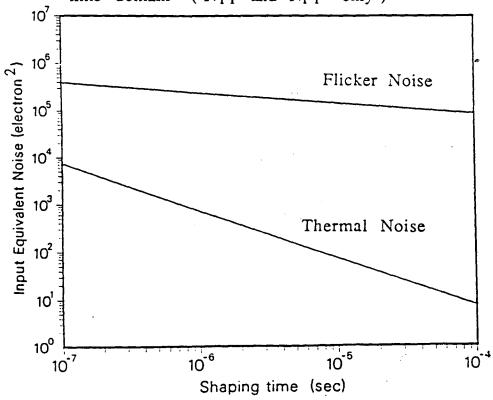

The proposed detector and amplifier system has primarily six noise sources as shown in figure 4. The current noise sources,  $i_{LD}^2$ ,  $i_{SD}^2$  and  $i_{FD}^2$  are called parallel noise and they are respectively the thermal noise of detector load resistance ( $R_L$ ), the shot noise due to detector leakage current ( $I_L$ ) and the flicker noise in the detector. The voltage noise sources,  $v_{LT}^2$ ,  $v_{TT}^2$  and  $v_{FT}^2$  are called series noise and they are also respectively the thermal noise of the amplifier load resistance ( $R_{D1}$ ), the thermal noise of the equivalent channel resistance of TFT and the 1/f noise or flicker noise of the TFT. These noise sources have spectra in the frequency domain and they are summarized in appendix B.

Fig. 4. Six Noise Sources in the Detector and Preamplifier System in the frequency domain when  $R_LC_T >> \tau_o$

When a simple RC-CR shaping amplifier with a peaking time,  $\tau_0$ , is used at the output stage, these noise sources are conveniently expressed by the equivalent input noise charge in the time domain. The procedure is as follows; (1) find the equivalent input noise voltage spectrum of all six noise sources. (2) take an integral of a convolution of the noise spectrum and the transfer functions of the first and second and shaping amplifiers from zero to infinity. (3) divide by the output voltage signal voltage squared from single electron-hole pair which is

$$v_{out}^2 = \left(\frac{q}{eC_T}\right)^2 * (G_1 * G_2)^2$$

(10)

where e is the base of natural logarithm and q is an electronic charge. The results are shown in the following equations.

$$N_{i}^{2} = \left(\frac{e C_{T}}{q}\right)^{2} * \int_{0}^{\infty} \frac{i_{i}^{2}(f)}{(2\pi f C_{T})^{2}} * G^{2}(f) df$$

$$i = LD, SD \text{ or } FD \qquad (11)$$

$$N_j^2 = \left(\frac{e C_T}{q}\right)^2 * \int_0^\infty v_j^2(f) * G^2(f) df$$

$j = LT, TT \text{ or } FT$  (12)

where the amplifier gain  $G_1$  and  $G_2$  are cancelled out and the transfer function of the shaping amplifier, G(f) for simple RC-CR is

$$G(f) = \frac{2\pi f \tau_o}{1 + (2\pi f \tau_o)^2}$$

(13)

In the time domain  $N_{SD}$  and  $N_{TT}$  are called Step Noise and  $\Delta$  Noise respectively.<sup>[1,8]</sup> All results are summarized in appendix B. The total input equivalent noise in units of electrons is

$$N_{TOT} = \left(N_{LD}^2 + N_{SD}^2 + N_{FD}^2 + N_{LT}^2 + N_{TT}^2 + N_{FT}^2\right)^{1/2}$$

(14)

Finally the signal-to-noise ratio is

$$S/N = \frac{S_{SIG}}{N_{TOT}}$$

(15)

Table 4 shows the estimated noise of the system when a RC = CR = 1 µsec shaping time is used.

Table 4 Noise of the Detector and Preamplifier System for 1 usec CR-RC shaping amplifier

| Noise (e)       |                          | a-Si:H TFT                     | Poly-NMOS(900°C) Poly-PMOS       |                         |

|-----------------|--------------------------|--------------------------------|----------------------------------|-------------------------|

| K <sub>f</sub>  | (V <sup>2</sup> /F)      | 1.3 x 10 <sup>-21</sup><br>1.0 | 1.95 x 10 <sup>-22</sup><br>0.78 | 7.0 x 10 <sup>-23</sup> |

| NLD             | (Thermal noise of RL)    | 77                             | 77                               | 77                      |

| NSD             | (Shot noise of detector) | 72                             | 72                               | 72                      |

| $N_{\text{FD}}$ | (1/f noise of detector)  | 7                              | 7                                | 7                       |

| NLT             | (Thermal noise of RD1)   | 24                             | 5                                | 5                       |

| NTT             | (Thermal noise of TFT)   | 107                            | 27                               | 3 3                     |

| NFT             | (1/f noise of TFT)       | 340                            | 480                              | 280                     |

| NTOT            | (Total noise)            | 370                            | 490                              | 300                     |

| S/N             |                          | 8.1                            | 6.1                              | 10.                     |

Among the six noise sources, the amplifier flicker noise turns out to be the dominant one. In order to reduce this 1/f type noise, other types of shaping amplifiers may be used. For example, 1/f noise will be reduced by 10 % when we use a CR- (RC)<sup>n</sup> filter for n > 4 which simulates gaussian type shaping.<sup>[8]</sup> Also it will be further reduced by using a time variant active filtering network such as correlated double sampling network which was originally used in charge coupled devices and showed a 6 dB decrease in 1/f noise of FETs.<sup>[9-10]</sup>

The equivalent noise voltage spectrum from a single TFT is analyzed as a sum of two different noise sources as in the crystalline MOSFET case. The first one is the Nyquist noise ( or the equivalent thermal noise ) due to the finite channel resistance which is expressed as  $2/(3g_m)$ . The second one is the flicker noise ( or 1/f noise ) which is generally inversely proportional to the frequency with some power  $\alpha$ . [11]

$$v_{TFT}^{2}(f) = 4 kT \left(\frac{2}{3 g_{m}}\right) \Delta f + \frac{K_{f}}{C_{i} WL f^{\alpha}} \Delta f$$

(16)

Following the process described earlier to express these terms in the time domain we obtain

$$N_{TFT}^{2} = \left(\frac{e C_{T}}{q}\right)^{2} * \frac{kT}{3 g_{m}} * \frac{1}{\tau_{o}} + \left(\frac{e C_{T}}{q}\right)^{2} * \frac{K_{f}}{2 C_{i} WL} * F(\alpha, \tau_{o})$$

(17)

where  $F(\alpha,\tau_0)$  is between 0 and 1. When  $\alpha$  is 1,  $F(\alpha,\tau_0)$  is 1 and the flicker noise is independent of the shaping time,  $\tau_0$ . See the formula in Appendix B.

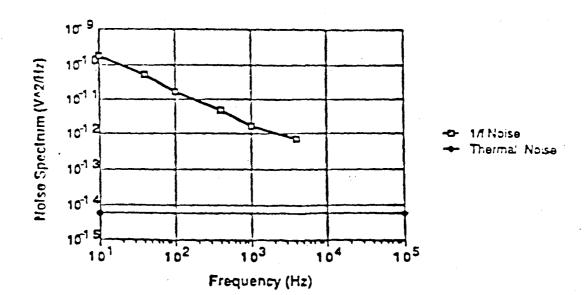

Figures 5 and 6 is the calculation of these two noise contributions in the time domain for a simple CR-RC shaping amplifier for the proposed detector amplifier system. In the calculation,  $K_f$  and  $\alpha$  for a-Si:H TFT are extrapolated from the noise measurements done on the large sized XEROX a-Si:H TFT shown in section III-D. For the poly-Si MOSFET, the data are taken from our measurements and from a recently published paper by A.G. Lewis. [12] They are shown in table 4. As expected these TFTs were not optimally designed for low noise.

The flicker noise in a-Si:H TFT can be explained by the fluctuations of the density of electrons due to the interaction with the interface states between a-Si:H and Si<sub>3</sub>N<sub>4</sub> layers and with the gap states in the channel region. The fact that the field effect electron mobility is lower than the bulk mobility is also attributed to these states. This phenomenon is also present in crystal Si MOSFETs. Better TFT can be possibly made in the future as the deposition techniques improve. A reduction of 1/f noise and an increase of the field effect electron mobility can be expected when the density of these states is decreased.

Fig. 5. Input equivalent noise of a-Si:H TFT amplifier in time domain (N<sub>TT</sub> and N<sub>FT</sub> only)

Fig. 6. Input equivalent noise of poly-Si TFT amplifier in time domain (NTT and NFT only)

#### II Description of TFTs

#### A. A-Si:H TFT with reduced lithography

One of the differences between TFTs and crystalline Si MISFETs is that these devices are generally operated in the accumulation mode of electrons and the drain and source contacts are on the opposite side of the channel from the gate. Due to this geometry and the low mobility of the electrons, these devices have high channel resistance which allows appreciable open loop gains even though the transconductance is small. Furthermore the drain contact can be underlapped relative to the gate so that the gate-to-drain capacitance can be minimized. This type of structure is used for high voltage TFT.

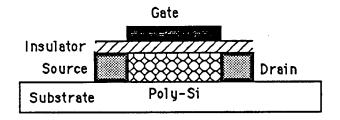

#### B. High Temperature Polysilicon MOSFET

Polysilicon TFTs are under developed now; NMOS, PMOS and CMOS techniques were been achieved recently at XEROX. [12] Polysilicon is annealed at two different temperatures, 900 °C (high temperature) and 400 °C (low temperature). [13-14] The only advantage of low temperature polysilicon TFT is the diverse choice of the substrate material. For high temperature anneal polysilicon, a highly thermal resistant substrate, such as quartz, is required. High temperature polysilicon TFT has the following advantages compared to the low temperature variety. 1) Higher mobility gives higher  $g_m$ , larger voltage gain and faster time reponse. 2) better insulators can be made. (SiO<sub>2</sub> or  $Ta_2O_5^{[15]}$ ) 3) Lower noise is expected due to the larger grain size. For the proposed PIXEL system, the high temperature polysilicon TFT array would be fabricated on the substrate and then a-Si:H detector would be deposited at about 250 °C.

#### C. Vertical a-Si:H TFT

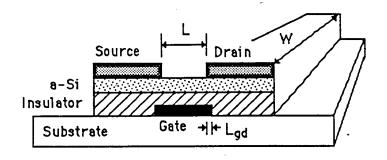

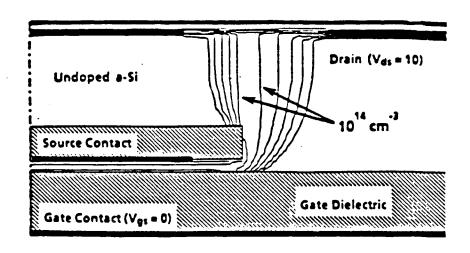

Some of the pioneering a-Si:H vertical TFTs have been designed by M. Hack, et al., at Xerox Palo Alto. [5] Their transconductances vary from 30 to a few hundred and can give high gains. We do not have enough information concerning their dynamic characteristics such as  $C_{gd}$  to have considered them in our amplifier design. Figure 7, 8 and 9 show typical configurations for the three types of TFTs.

Fig. 7. Configuration of a-Si:H TFT

Fig. 8. Configuration of typical poly-Si MOSFET (Courtesy of A. Lewis)

Fig. 9. Configuration of vertical TFT (Courtesy of M. Hack)

#### III Measurements on a-Si:H TFTs

We received and tested some a-Si:H TFTs from Xerox, which have large channel lengths and widths and were designed for switching purpose.

#### A. Insulator Thickness

We measured the thickness of the gate insulator,  $Si_3N_4$ , indirectly by measuring the gate-to-drain capacitance.

$$d_{i} = \varepsilon_{i} * \varepsilon_{o} * \frac{W * L_{GD}}{C_{gd-Max}}$$

(18)

using the value  $\varepsilon_i = 7$  for amorphous silicon nitride.

Table 5 Dimensions of XEROX a-Si:H TFT (1986)

|              |      | <u> </u> |

|--------------|------|----------|

| W            | (µm) | 350      |

| L            | (µm) | 20       |

| W/L          |      | 17.5     |

| $L_0$        | (µm) | 1 2      |

| $C_{gd-Max}$ | (pF) | 1.2      |

| $d_i$        | (µm) | 0.22     |

|              |      |          |

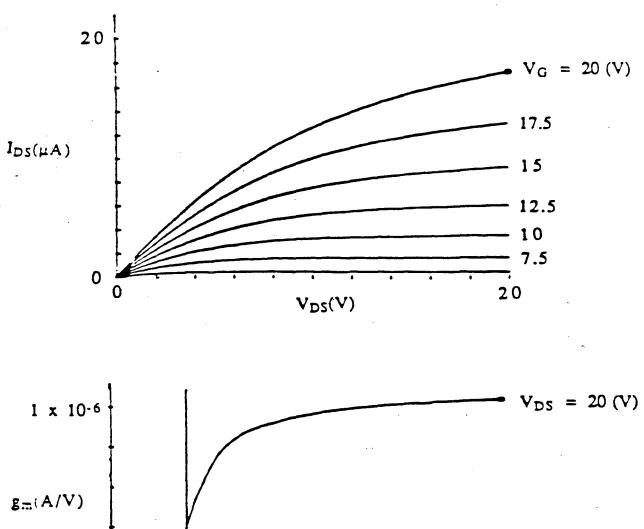

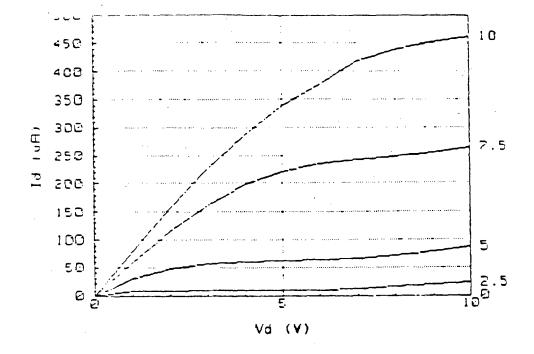

#### B. I-V and Transconductance

We also measured the I-V characteristics and small signal parameters (  $g_m$ ,  $r_o$  etc ) of these TFTs. The measured transconductance and drain current are compared with the calculated values by using the following equations.<sup>[16]</sup>

$$g_{m} = \mu_{e} * \frac{\varepsilon_{i} * \varepsilon_{o}}{d_{i}} * \frac{W}{L} * (V_{G} - V_{T})$$

$$I_{DS} = \frac{g_{m} * (V_{G} - V_{T})}{2}$$

(20)

Figure 10 shows the I-V curves and the transfer curve for a typical a-Si:H TFT of Xerox.

As we see from Table 6, the equations originally used for crystalline MOSFET, describe the static characteristics of a-Si:H TFT very well. For calculating  $g_m$  and  $I_{DS}$ , we assumed only one fitting parameter, which is the electron field effect mobility,  $\mu_e$ , which is within the accepted value in the literature. This channel mobility is 2-3 times smaller than the bulk mobility as measured by the time of flight method. A lower channel mobility is also found in crystalline silicon FETs and is assumed to be due to additional trapping by the surface states between the a-Si:H and the insulator.

Table 6 Static Parameters of XEROX a-Si:H TFT

| V <sub>DS</sub>  | (V)                     | 20   | = |

|------------------|-------------------------|------|---|

| $V_G$            | (V)                     | 17.5 |   |

| $V_{T}$          | (V)                     | 3.5  |   |

| $I_{DS}$         | (μΑ)                    | 112  |   |

| $r_o$            | $(M\Omega)$             | 7.7  |   |

| $g_{\mathbf{m}}$ | $(\mu A/V)$             | 1.7  |   |

| μ <sub>e</sub>   | (cm <sup>2</sup> /Vsec) | 0.25 |   |

#### C. Output Pulse Rise Time

We measured the output pulse rise time of the Xerox TFTs by using various load resistances. We biased the drain at 20 volt through a passive probe with the load resistance directly connected to the probe tip in order to reduce the stray capacitance, and applied 15 volt to the gate. A square wave input pulse was applied to the gate and the output pulse signal was measured by an active probe (Input capacitance = 0.1 pF) capacitively coupled to the drain.

For a load resistance of  $1M\Omega$ , an RC time constant of 1.7 µsec is measured; we estimate the stray capacitance at the drain in this set-up to be about 1.5 - 2.0 pF. Using a 100 k $\Omega$  resistance we observed an RC time constant of 0.178 µsec. Since the transit time of the charge carriers of the TFT is shorter than the RC time, we conclude that the output pulse rise time is dominated by the measured RC time constant.

#### D. Noise

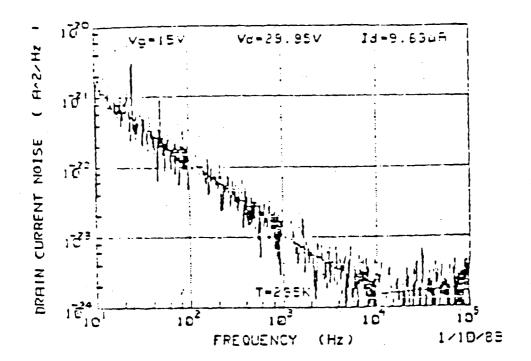

Finally we measured the equivalent input-referred voltage noise of a-Si:H TFT as shown in Figure 11. The measurement system is described in reference [17]. We measured the drain current fluctuations directly and calculated the input equivalent noise voltage by the following equation.

$$v_{TFT}^2(f) = \frac{i_D^2(f)}{g_m^2} \Delta f$$

(21)

The noise spctrum is measured only up to 500 kHz due to the limitation of the probe station system noise. For a typical XEROX TFT the flicker noise constant,  $K_f$  is 1.2 x  $10^{-21}$  V<sup>2</sup>/Farad and  $\alpha$  is about unity. The measurement was done for a TFT which had input capacitance of 1.7 pF and  $g_m = 1.6 \ \mu A/V$ .

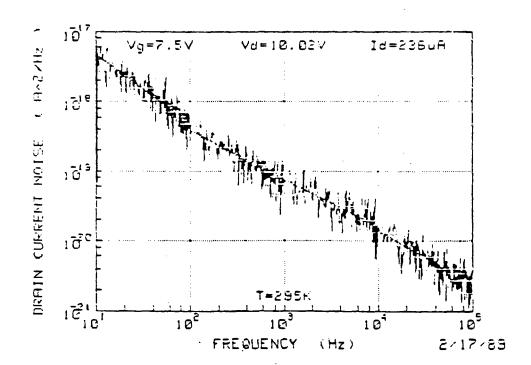

With the courtesy of XEROX, we measured I-V curves and the drain current fluctuations for high temperature polysilicon NMOS as shown in figure 12. The measured  $K_f$  is 2 x  $10^{-22}$   $V^2$ /Farad and  $\alpha$  is about 0.78.

$g_{m}(A/V)$   $L = 20 \mu m$   $W = 350 \mu m$   $V_{G}(V)$

Fig. 10. I-V Curves and Transfer Curve of XEROX a-Si:H TFT

Fig. 11. Typical Input Noise Voltage Spectrum of a-Si:H TFT

(a) Measured drain current noise (the flat part above

10 kHz is due to the limit of system noise.)

(b) Equivalent input voltage noise

Fig. 12. Measurements on Polisilicon NMOS (After A.Lewis) (W/L = 50/10, Annealing at 900 °C)

- (a) I-V Curves

- (b) Drain current noise (at  $V_g = 7.5 \text{ V}$ )

#### IV Conclusion

This paper is intended only as a design consideration for a proto-type a-Si:H PIXEL array for medical applications and high energy particle track detectors. Various types of thin-film transistors are suggested as electronics candidates. A final design, however, should be made by considering several points which are not known yet like radiation resistance, reliability, yield, and convenience of manufacturing.

In this paper, three sample amplifier configurations are proposed with respect to three important design criteria; amplifier gain, time response and noise. No effort has been made to reduce the power dissipation for the sample system. However, the load resistance  $R_d$  could be less than 4  $M\Omega$  for a-Si:H TFT when the operating drain current is less than 10  $\mu A$ . For poly-Si TFT, the resistance could be less than 1  $M\Omega$  because the channel resistance is small. We even do not make use of the fact that CMOS techniques are possible for poly-Si TFTs amplifier systems. One additional FET to reset the PIXEL detector is required in the high energy application, which is not shown in figures 2 and 3, but may not be needed in medical imaging applications because of the slow data rate.

As we see, all three proposed amplifier systems have sufficient gain and have acceptable frequency responses. The five a-Si:H TFTs amplifier system has almost the equivalent gain and frequency response as the four polysilicon TFTs amplifier system. Reduced lithography TFTs are available now and the other two techniques are being developed. By extrapolating the RC time constant measurements done on the Xerox TFT (L =  $20~\mu m$ ) to the proposed a-Si:H TFT (L =  $4~\mu m$ ) at the same electric field strength, the transit time of charge carriers in the proposed TFT becomes at least a factor of 5 less than  $0.18~\mu sec$ , ie., less than 360~nsec. In polysilicon TFT (L =  $8~\mu m$ ), the transit time is less than 100~nsec. So the output pulse rise time is dominated by the RC time constant that we used for the model design.

The noise measurement of the individual TFTs show that the flicker (1/f) noise will be the dominant noise source in

the designed PIXEL amplifier system. The noise data shown in table 4 are the estimated values when a simple RC-CR shaping amplifier with 1  $\mu$  sec shaping time is used. In this case the true 1/f noise is independent of shaping time as is well known. It may be reduced by 10 - 30 % by using more advanced shaping amplifiers such as gaussian shaping or time variant active filters such as correlated double sampling networks.

Signal-to-noise ratios of 6 - 10 are estimated with the current technology a-Si:H and with 900 °C poly-Si TFTs. Due to the larger grain size, high temperature poly-Si TFT (900 °C) is considered the better choice than low temperature poly-Si TFT (400 °C). Since PMOS devices show lower noise than NMOS,[12] the future design of PIXEL amplifiers is possible by using CMOS poly-Si technique with a PMOS input stage. A reduction of flicker noise and an increase of the field effect mobility of both a-Si and poly-Si TFTs can hopefully be achieved in future because the process technique is still new and undergoing improvements.

We want to thank Dr. M. Hack and Dr. A. Lewis from Xerox at Palo Alto for sending sample TFTs to test. We also would like to thank K. Lee, D. Landis, F. Kirsten, and S. Parker for useful discussions on PIXEL amplifiers. This work was supported by the Director, Office of Energy Research, O. H. E. R., Nuclear and High Energy Physics of the U. S. Dept. of Energy under contract # DE-AC03-76SF00098.

#### References

- [1] V. Perez-Mendez, et al., "Hydrogenated Amorphous Silicon Pixel Detectors for Minimum Ionizing Particles" Nucl. Instr. Methods, 127-134 A273 (1988)

- [2] P. R. Gray & R. G. Meyer, 'Analysis and Design of Analog Integrated Circuits', P.70 (1977)

- [3] P. W. Nicholson, 'Nuclear Electronics', P.174 (1974)

- [4] R. Boylestand & L. Nashelsky, 'Electronic Devices and Circuit Theory', ch 8 (1982)

- [5] M. Hack, et al. "Novel a-Si TFTs for Use in Large-Area Microelectronics", Mat. Res. Soc. Symp. Proc. vol 118 (1988)

- [6] H. Okada, et al., "Improved Off-Characteristics of a-Si Vertical-Type MOSFETs", Mat. Res. Soc. Symp. Proc. vol 118 (1988)

- [7] Y. Uchida, et al., "Vertical-Type a-Si FETs with Small Parasitic Elements", Jpn. J. Appl. Phys. L798, vol 25 (1986)

- [8] F. S. Goulding & D. A. Landis, "Signal Processing for Semiconductor Detectors", IEEE. Trans. Nucl. Sci., 1125, vol NS-29 (1982)

- [9] G. R. Hopkinson et al., "Noise Reduction Techniques for CCD Image Sensors", J. of Phys. E., 15, 1214 (1982)

- [10] E. Odat et al., "A CCD Image Sensor with 768 x 490 Pixels " IEEE Trans. on Electron Devices, ED-32, 1457 (1985)

- [11] P. R. Gray & R. G. Meyer, 'Analysis and Design of Analog Integrated Circuits', P.666 (1977)

- [12] A. G. Lewis, et al., "Polysilicon Thin Film Transistors for Analogue Circuit Applications", IEDM 264 (1988)

- [13] Y. Shiraki, et al., "Polys-Si TFTs and Their Applications to LCD", 'Amorphous Semiconductor Technoligies and Devices', 266, vol. 6 (1983)

- [14] W. G. Hawkins, "Polycrystalline-Silicon Device Technology for Large-Area Electronics", IEEE Trans. on ED., 477, ED-33 (1986)

- [15] S. Seki et al., "High Transconductance Si-TFT's Using Ta<sub>2</sub>O<sub>5</sub> Films as Gate Insulators", 16 th Conf. on Solid State devices and Materials", P.563 (1984)

- [16] S. M. Sze, 'Physics of Semiconductor Devices', P.442 (1981)

- [17] K. K. Hung, P. K. Ko et al., "Flicker Noise Characteristics of Advanced MOS Technologies", 88-IEDM, P.34 (1988)

## Appendix A

### Notation

| ADET                                                 | detector area                                                                                | $[\mu m^2]$             |

|------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------|

| $A_{\mathbf{v}}$                                     | open loop gain of TFT                                                                        |                         |

| α                                                    | frequency dependence factor of flicker noise in TFT                                          | •                       |

| CDET                                                 | detector capacitance                                                                         | [pF]                    |

| $c_{F}$                                              | feedback capacitance of preamplifier = $C_{gd}$                                              | [pF]                    |

| $C_{in}$                                             | input capacitance of $= C_{gs} + C_{gd}$                                                     | [pF]                    |

| $\mathbf{c}_{\mathbf{r}}$                            | sum of detector and input capacitance = $C_{DET} + C_{gs}$                                   |                         |

| Ci                                                   | insulator capacitance per unit area of channel                                               | [pF]                    |

| C <sub>gs</sub><br>C <sub>gd</sub>                   | capacitance between gate and source                                                          | [pF]                    |

| $C_{\mathrm{gd}}$                                    | capacitance between gate and drain                                                           | [pF]                    |

| $C_{ds}$                                             | capacitance between drain and source                                                         | [pF]                    |

| d <sub>DET</sub>                                     | a-Si detector thickness                                                                      | [µm]                    |

| d <sub>i</sub>                                       | insulator thickness                                                                          | [µm] .                  |

| d <sub>a</sub>                                       | a-Si thickness in TFT                                                                        | [mm]                    |

| e<br>e:                                              | basis of logarithm = $2.718$<br>dielectric constant of insulator ( $Si_3N_4 = 7$ , $SiO_2 =$ | 4)                      |

| $egin{array}{c} eta_{ m i} \ eta_{ m S} \end{array}$ | dielectric constant of a-Si = $12$                                                           | 7)                      |

| $\epsilon_0$                                         | dielectric constant of air = $8.854 \times 10^{-14}$                                         | [F/cm]                  |

| f                                                    | frequency                                                                                    | [Hz]                    |

| $G_1$                                                | gain of the 2nd stage = $V_1/V_i$                                                            | ()                      |

| $G_2$                                                | gain of the 2nd stage = $V_0/V_1$                                                            |                         |

| $G_{\Gamma}$                                         | total gain of preamplifier = $G_1G_2$                                                        |                         |

| G(f)                                                 | transfer function of RC-CR shaping amplifier                                                 |                         |

| gm                                                   | transconductance of TFT                                                                      | $[\mu A/V]$             |

| go                                                   | channel conductance of TFT                                                                   | [μA/V]                  |

| ID                                                   | drain-to-source current                                                                      | [μ <b>A</b> ]           |

| IDET                                                 | detector leakage current = $J_L * A_{DET}$                                                   | [μ <b>A</b> ]           |

| $i_D^2$                                              | drain current noise sspectrum                                                                | $[A^2/Hz]$              |

| i <sub>i</sub> 2                                     | input current noise sources                                                                  | [A <sup>2</sup> /Hz]    |

| $i_{ m FD}^2$                                        | flicker noise in the detector                                                                | $[A^2/Hz]$              |

| i <sub>LD</sub> <sup>2</sup>                         | thermal noise due to the detector load resistance, R <sub>L</sub>                            |                         |

| $i_{SD}^2$                                           | shot noise of the detector leakage current, IL                                               | [A <sup>2</sup> /Hz]    |

| $J_{L}$                                              | detector leakage curent density                                                              | [A/cm <sup>2</sup> ]    |

| k                                                    | Boltzmann constant = $8.614 \times 10^{-5}$                                                  | [eV/°K]                 |

| $K_d$                                                | flicker noise constant of the detector = $2 \times 10^{-18}$                                 | [Am]                    |

| $\mathbf{K_f}$                                       | flicker noise constant of TFT                                                                | $[V^2/F]$               |

| Ĺ                                                    | channel length                                                                               | [µm]                    |

| $L_{o}$                                              | gate-to-drain or source overlapping length                                                   | [µm]                    |

| μe                                                   | field effect electron mobility in a-Si:H                                                     | [cm <sup>2</sup> /Vsec] |

| Ni                                                   | input equivalent noise from parallel noise source                                            | [electrons]             |

| $N_j$                                                | input equivalent noise from series noise source                                              | [electrons]             |

| $N_{\mathrm{FD}}$                                    | flicker noise in the detector                                                                | [electrons]             |

| $N_{LD}$                                             | thermal noise due to detector load resistance, RL                                            | [electrons]             |

```

shot noise due to detector leakage current, IL

NSD

[clcctrons]

NFT

flicker noise in the TFT

[electrons]

thermal noise of load resistance, RD1

NLT

[electrons]

NTT

thermal noise due to 1/gm in the TFT

[electrons]

NTOT

total noise

[clectrons]

N<sub>TFT</sub><sup>2</sup>

input equivalent noise from TFT = N_{TT}^2 + N_{FT}^2

[electrons<sup>2</sup>]

charge on electron = 1.602 \times 10^{-19}

[Coul]

electron-hole pairs produced in the detector

[Coul]

QSIG

drain load resistance of the 1st stage amplifier

R_{D1}

[M\Omega]

drain load resistance of the 2nd stage amplifier

[M\Omega]

R_{D2}

gate bias control resistance

R_{G}

[M\Omega]

detector load resistance

R_{L}

[M\Omega]

source load resistance of source follower

[M\Omega]

R_S

source load resistance of the 2nd stage amplifier

[M\Omega]

R<sub>S2</sub>

output resistance of TFT

[M\Omega]

ro

electron-hole pairs produced in the detector

[electrons]

SSIG

signal-to-noise ratio

S/N

[°K]

T

temperature

T_t

electron transit time in the channel of TFT

[µsec]

RC time constant of the 1st stage amplifier

τ

[µsec]

peaking time constant of RC - CR shaping amplifier [usec]

\tau_{o}

V_{\rm D}

drain voltage

[V]

V_{dd}

bias supply voltage

[V]

V_{G}

gate bias voltage

[V]

threshold voltage

V_{T}

[V]

v_i

input voltage signal

[mV]

voltage signal after 1st stage amplifier

V_1

[mV]

output voltage signal

V_{o}

[mV]

output voltage signal from single electron-hole pair [V]

Vout

v_j^2

input equivalent voltage noise sources

[V^2/Hz]

v_{FT}^2

flicker noise in the TFT

[V^2/Hz]

vLT<sup>2</sup>

thermal noise due to load resistance, RD 1

[V^2/Hz]

vTT^2

thermal noise due to channel

[V^2/Hz]

resistance

input equivalent noise from TFT = v_{TT}^2 + v_{FT}^2

v<sub>TFT</sub><sup>2</sup>

[V<sup>2</sup>/Hz]

W

channel width

[um]

```

## Appendix B

#### Noise Equations

| Spectrum in Freq. Domain                                 | Eqv. Noise in Time Domain                                                                  |

|----------------------------------------------------------|--------------------------------------------------------------------------------------------|

| $i_{LD}^2(f) = \frac{4 kT}{R_L} \Delta f$                | $N_{LD}^2 = \left(\frac{e}{q}\right)^2 * \frac{kT}{2R_L} * \tau_o$                         |

| $i_{SD}^2(f) = 2 q I_{DET} \Delta f$                     | $N_{SD}^2 = \frac{e^2 I_{DET}}{4 q} * \tau_o$                                              |

| $i_{FD}^2(f) = \frac{K_d I_{DET}}{d_{DET} f} \Delta f$   | $N_{FD}^2 = \left(\frac{e}{q}\right)^2 * \frac{K_d I_{DET}}{d_{DET}} * \tau_o^2$           |

| $v_{LT}^{2}(f) = \frac{4 kT}{R_{D1} g_{m}^{2}} \Delta f$ | $N_{LT}^2 = \left(\frac{e C_T}{q}\right)^2 * \frac{kT}{2 R_{D1} g_m^2} * \frac{1}{\tau_o}$ |

| $v_{TT}^2(f) = \frac{8 kT}{3 g_m} \Delta f$              | $N_{TT}^2 = \left(\frac{e C_T}{q}\right)^2 * \frac{kT}{3 g_m} * \frac{1}{\tau_o}$          |

| $v_{FT}^2(f) = \frac{K_f}{C_i WL f^{\alpha}} \Delta f$   | $N_{FT}^2 = \left(\frac{e C_T}{q}\right)^2 * \frac{K_f}{2 C_i WL} * F(\alpha,$             |

$$F(\alpha, \tau_0) = 1$$

if  $\alpha = 1$

$$F(\alpha,\tau_o) = (2\pi\tau_o)^{\alpha-1} * \frac{\left(\frac{(\alpha-1)\pi}{2}\right)}{\sin\left(\frac{(\alpha-1)\pi}{2}\right)} \quad \text{if } \alpha \neq 1$$

LAWRENCE BERKELEY LABORATORY

TECHNICAL INFORMATION DEPARTMENT

1 CYCLOTRON ROAD

BERKELEY, CALIFORNIA 94720