# UC Santa Barbara

**UC Santa Barbara Electronic Theses and Dissertations**

### Title

Variation-Aware Modeling and Design of Nanophotonic Interconnects

### Permalink

https://escholarship.org/uc/item/1nb7s9dc

# Author

Wu, Rui

# Publication Date 2017

Peer reviewed|Thesis/dissertation

University of California Santa Barbara

# Variation-Aware Modeling and Design of Nanophotonic Interconnects

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy in Electrical and Computer Engineering

by

Rui Wu

Committee in charge:

Professor Kwang-Ting (Tim) Cheng, Chair Professor John E. Bowers Doctor Raymond G. Beausoleil Professor Yuan Xie

June 2017

The Dissertation of Rui Wu is approved.

Professor John E. Bowers

Doctor Raymond G. Beausoleil

Professor Yuan Xie

Professor Kwang-Ting (Tim) Cheng, Committee Chair

March 2017

### Variation-Aware Modeling and Design of Nanophotonic Interconnects

Copyright  $\bigcirc 2017$

by

Rui Wu

To my parents and all my family.

#### Acknowledgements

During the long journey of pursing the Ph.D., I have been receiving numerous support from many people. Firstly, I would be grateful forever to my advisor, Professor Kwang-Ting (Tim) Cheng for his kind guidance and insightful advises that are usually full of wisdom. Professor Cheng is a true role model of mine not only in academics but also in professional, leadership, and life. I would like to thank my committee members Professor John Bowers, Doctor Ray Beausoleil, and Professor Yuan Xie for their patient guidance on photonics, generous support on collaborations, and valuable feedback on my research.

I would like to thank Dr. Jock Bovington and Dr. Chong Zhang, two of my collaborators and mentors in Femto Lab at ECE, UCSB. They taught me a lot on photonics theories and experiments and helped me a lot during the close collaborations. Zeyu Zhang, Dr. Sudha Srinivasan, and all the Femto Lab members are so kind and warmhearted.

I am deeply grateful to the great mentorship from Dr. Chin-Hui (Janet) Chen and Dr. Ashkan Seyedi from Hewlett Packard Labs. Without the valuable opportunities of three internships and close collaborations there, I would not have successfully reached this Ph.D. milestone. Dr. Tsung-Ching (Jim) Huang, Dr. Wayne Sorin, Dr. Zhihong Huang, and all the LSIP group members at Hewlett Packard Labs always offer selfless help and valuable discussions.

The CADLAB and the office labmates are always there willing to help. I would like to thank Yuyang Wang, one of my collaborators, Dr. Di-An Li, Dr. Xiang Qiu, Dr. Amirali Ghofrani, Dr. Chun-Kai Hsu, Miguel Lastras, Dr. Nicole Fern, Dr. Fan Lin, Dr. Yi-Chu Wang, Dr. Xin Yang, Dr. Zhong Guan, Chong Huang, and Leilai Shao.

Grateful thanks to dear Xiaoran (Sharon) Guo for her deep love and support. I have always been feeling lucky that I have a number of friends at Santa Barbara: my 3-year roommates Junkai Jiang, and Zhen Bi, and Runsheng Song, Yifan Shen, Mingquan Chen, Honglei Liu, and all other friends around. I would like to thank them for their care and help.

A special acknowledgment goes to Professor Hong Wang, Professor Shiyuan Yang, and Dr. Yan Zheng at Tsinghua University for their guidance during my undergraduate research and trust and recommendations for the Ph.D. program.

Finally, I would like to thank my parents and all my family who have always been my strong support and motivation for fighting.

### Curriculum Vitæ Rui Wu

### Education

| 2017 | Ph.D. in Electrical and Computer Engineering (Expected),<br>University of California, Santa Barbara, United States. |

|------|---------------------------------------------------------------------------------------------------------------------|

| 2015 | M.S. in Electrical and Computer Engineering,<br>University of California, Santa Barbara, United States.             |

| 2012 | B.S. in Automation,<br>Tsinghua University, Beijing, China                                                          |

#### Work Experience

| 2012 - 2017      | Graduate Research Assistant,<br>University of California, Santa Barbara, CA, United States. |

|------------------|---------------------------------------------------------------------------------------------|

| 2014, 2015, 2016 | Summer Research Intern,<br>Hewlett Packard Labs, Palo Alto, CA, US.                         |

| 2011             | Summer Intern,<br>Siemens (China) Corporate Technology, Beijing, China                      |

### Honors and Awards

| 2016       | ACM DAC PhD Forum Travel Grant                                    |

|------------|-------------------------------------------------------------------|

| 2016       | UCSB PhD Student Travel Grant                                     |

| 2010, 2011 | National Scholarship for Encouragement (top $5\%$ )               |

| 2010       | Second Prize in Electronic Design Competition in Tsinghua Univer- |

|            | sity                                                              |

| 2007       | First Prize in China Physics Olympiad                             |

### Publications

- R. Wu, Y. Wang, Z. Zhang, C. Zhang, C. L. Schow, J. E. Bowers, and K.-T. Cheng, "Compact modeling and circuit-level simulation of silicon nanophotonic interconnects", in *Design, Automation and Test in Europe (DATE)*, 2017.

- [2] F. Lan, R. Wu, C. Zhang, Y. Pan, and K.-T. Cheng, "DLPS: Dynamic laser power scaling for optical network-on-chip", in Asia and South Pacific Design Automation Conference (ASP-DAC), 2017.

- [3] R. Wu, C.-H. Chen, M. A. Seyedi, T.-C. Huang, M. Fiorentino, R. G. Beausoleil, and K.-T. Cheng, "Large-signal model for small-size high-speed carrier-injection silicon microring modulator" in OSA Integrated Photonics Research, Silicon, and Nano-Photonics Conference (IPR), 2016.

- [4] A. M. Seyedi, R. Wu, C.-H. Chen, M. Fiorentino, and R. G. Beausoleil, "15 Gb/s transmission with wide-FSR carrier injection ring modulator for Tb/s optical links" in *Conf. on Lasers & Electro-Optics (CLEO)*, 2016.

- [5] R. Wu, C.-H. Chen, T.-C. Huang, R. G. Beausoleil, and K.-T. Cheng, "Spatial pattern analysis of process variations in silicon microring modulators" in *IEEE Optical Interconnect Conf.*, 2016.

- [6] R. Wu, C.-H. Chen, T.-C. Huang, K.-T. Cheng, and R. G. Beausoleil, "20 Gb/s carrier-injection silicon microring modulator with SPICE-compatible dynamic model" in *Int'l Conf. on Photonics in Switching (PS)* (Post Deadline Paper), 2015.

- [7] R. Wu, C.-H. Chen, C. Li, T.-C. Huang, F. Lan, C. Zhang, Y. Pan, J. E. Bowers, R. G. Beausoleil, and K.-T. Cheng, "Variation-aware adaptive tuning for nanophotonic interconnects" in *IEEE/ACM Int'l Conf. On Computer Aided Design (ICCAD)*, 2015.

- [8] R. Wu, C.-H. Chen, J. Fedeli, M. Fournier, K.-T. Cheng, and R. Beausoleil, "Compact models for carrier-injection silicon microring modulators", *Optics Express*, 2015.

- [9] S. Feng, K. Shang, J. Bovington, R. Wu, B. Guan, K.-T. Cheng, J. E. Bowers, and S.J.B. Yoo, "Athermal silicon ring resonators clad with titanium dioxide for 1.3 μm wavelength operation", Optics Express, 2015.

- [10] R. Wu, C.-H. Chen, J.-M. Fedeli, M. Fournier, R. G. Beausoleil, and K.-T. Cheng, "Compact modeling and system implications of microring modulators in aanophotonic interconnects", in *International Workshop on System-Level Interconnect Prediction* (SLIP), 2015.

- [11] T. C. Huang, C. Li, R. Wu, C. H. Chen, M. Fiorentino, K.-T. Cheng, S. Palermo, and R. G. Beausoleil, "DWDM nanophotonic interconnects: toward Terabit/s chip-scale serial link", in *International Midwest Symposium on Circuits and Systems (MWSCAS)*, 2015.

- [12] J. Bovington, **R. Wu**, K.-T. Cheng, and J. E. Bowers, "Thermal stress implications in athermal TiO<sub>2</sub> waveguides on a silicon substrate", *Optics Express*, 2014.

- [13] S. Feng, K. Shang, J. Bovington, R. Wu, K.-T. Cheng, J. E. Bowers, and S.J.B. Yoo, "Athermal characteristics of TiO2-clad silicon waveguides at 1.3 um", in *IEEE Photonics Conference (IPC)*, 2014.

- [14] J. Bovington, R. Wu, K.-T. Cheng, and J. E. Bowers, "Role of thermal stress in athermal waveguide design using TiO2 waveguides on a silicon substrate", in *IEEE Photonics Conference (IPC)*, 2013.

#### Abstract

#### Variation-Aware Modeling and Design of Nanophotonic Interconnects

by

#### Rui Wu

Optical interconnects have started to replace electrical interconnects in the communications between racks and circuit boards with potential benefits in bandwidth, delay, power efficiency, and crosstalk. Silicon photonics has emerged to be a highly promising enabling technology for the short-reach nanophotonic interconnects because it offers favorable CMOS compatibility and high integration level. The fast-growing complexity of photonic integrated circuit (PIC) and close electro-optical integration call for computeraided design (CAD) for integrated photonics, and electronic-photonic design automation (EPDA) including accurate behavior models and efficient simulation methodologies for integrated electro-optical systems. Also, the nanophotonic devices are highly sensitive to fabrication process variation and thermal variation effects, which requires proper modeling, optimization, and management schemes. To address these problems, this thesis is dedicated to the following two tasks: (1) compact modeling and circuit-level simulation of nanophotonic interconnects, and (2) power-efficient management of the variation effects in nanophotonic interconnects.

The first part of the thesis develops compact models for key components in nanophotonic interconnects including silicon microring modulators, diode lasers, electro-absorption modulators (EAM), photodetectors, etc. These compact models are developed based on their electrical and optical properties, and are then extensively validated by measurement data. The model parameters are extracted from common electrical and optical tests. Implemented in Verilog-A, the models are used in SPICE simulations of optical links, whose results again agree well with measurement data. The compact model library and the simulation methodology enable electro-optical co-simulations and optical device design explorations in the circuit-level.

In the second part of the thesis, we propose modeling methods and power-efficient management schemes for the process and thermal variations in optical interconnects. The proposed adaptive tuning technique performs on-chip self-tests and adaptively allocates just enough power for link operations. The technique saves significant amount of power compared to worst-case based conservative designs, and scales well w.r.t. variations and network size. We also design power-efficient pairing algorithms for microring-based optical interconnects. Our algorithms optimally mix-and-match microring-based devices to minimize the power consumption for tuning. The algorithms are tested on both measured and synthetic data sets, demonstrating promising results of power reduction and scalability for handling a large number of devices. Lastly, we decompose and analyze wafer-scale spatial patterns of process variations in microring modulators. We further investigate the correlations between the spatial patterns and fabrication process steps, which is valuable for understanding process variation sources and improving fabrication processes for uniformity.

# Contents

| Cı            | rriculum Vitae                                                                                                                                                                                                                            | vii                                                 |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| Al            | stract                                                                                                                                                                                                                                    | ix                                                  |

| Li            | t of Figures                                                                                                                                                                                                                              | xiii                                                |

| $\mathbf{Li}$ | t of Tables                                                                                                                                                                                                                               | xvii                                                |

| 1             | Introduction         1.1       Background and Motivation         1.2       Overview of Optical Interconnects and Devices         1.3       Literature Review         1.4       Thesis Outline                                             | <b>1</b><br>1<br>5<br>10<br>12                      |

| 2             | Compact Models for Silicon Microring-based Modulators and Filters2.1Introduction2.2Device Designs and Fabrications2.3Device Design Space Model2.4Electro-Optic Modulation Model2.5Electrical Model2.6Large-Signal Dynamic Model2.7Summary | <b>14</b><br>14<br>16<br>17<br>21<br>27<br>30<br>33 |

| 3             | Compact Models for Other Common Silicon Photonic Devices3.1 Introduction3.2 Overview of the ONoC3.3 Device Modeling and Parameter Extraction3.4 Summary                                                                                   | <b>36</b><br>36<br>37<br>39<br>48                   |

| 4             | Circuit-Level Simulations and Design Space Explorations of Nanophotonic Interconnects 4.1 Introduction                                                                                                                                    | <b>49</b><br>49                                     |

|          | 4.2              | Optical Transceiver based on Silicon Microring Resonators       | 50        |

|----------|------------------|-----------------------------------------------------------------|-----------|

|          | 4.3              | Optical NoC on III-V/Silicon Heterogeneous Platform             |           |

|          | 4.4              | Summary                                                         | 58        |

| <b>5</b> | Var              | iation-Aware Adaptive Tuning Technique                          | <b>59</b> |

|          | 5.1              | Introduction                                                    | 59        |

|          | 5.2              | Background                                                      | 61        |

|          | 5.3              | Variation Challenges                                            | 63        |

|          | 5.4              | Adaptive Tuning Approach                                        | 66        |

|          | 5.5              | Evaluations                                                     | 71        |

|          | 5.6              | Summary                                                         | 77        |

| 6        | Opt              | timal Pairing of Microring-based Optical Transceivers           | 79        |

|          | 6.1              | Introduction                                                    | 79        |

|          | 6.2              | Background                                                      | 80        |

|          | 6.3              | Optimal Assignment of Transmitters and Receivers                | 86        |

|          | 6.4              | Optimal Pairing of Transceivers                                 | 88        |

|          | 6.5              | Summary                                                         | 93        |

| 7        | Spa              | tial Pattern Analysis of Process Variations in Silicon Microrin | ıg        |

|          | Mo               | dulators                                                        | 94        |

|          | 7.1              | Introduction                                                    | 94        |

|          | 7.2              | Spatial Pattern Decomposition and Analysis                      | 95        |

|          | 7.3              | Implications on Fabrication Process Steps                       | 98        |

|          | 7.4              | Summary                                                         | 98        |

| 8        | Cor              | nclusions and Future Work                                       | 100       |

| Bi       | Bibliography 102 |                                                                 |           |

# List of Figures

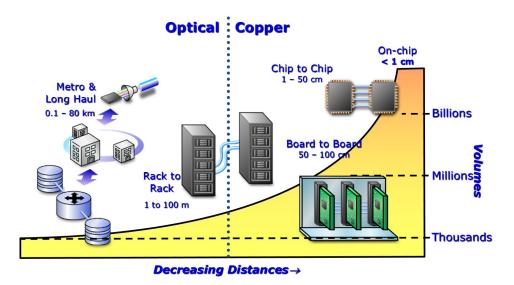

| 1.1 | The evolvement of optical interconnect distance and production volume.                                                                                                                                                                                                                      |    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | (Courtesy of Intel)                                                                                                                                                                                                                                                                         |    |

| 1.2 | IBM's silicon photonic chip. (Courtesy of IBM)                                                                                                                                                                                                                                              |    |

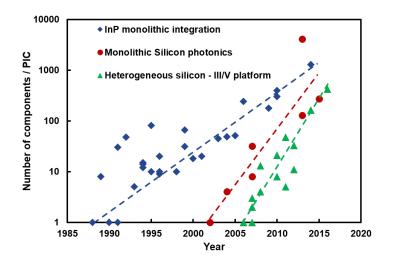

| 1.3 | Number of photonic components integrated on one photonic chip over the past decades for three integrated photonics technology platforms. (Courtesy of J. Hulme)                                                                                                                             | ,  |

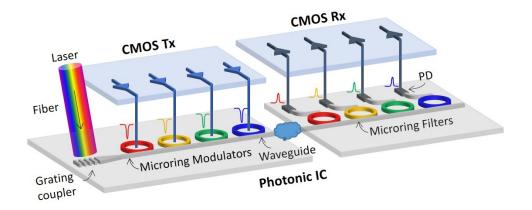

| 1.4 | A silicon photonics based optical interconnect structure.                                                                                                                                                                                                                                   |    |

| 1.5 | Cross section of a silicon waveguide and its optical mode illustration                                                                                                                                                                                                                      |    |

| 1.6 | 3D view of in-plane and microring heterogeneous silicon lasers $[1, 2]$                                                                                                                                                                                                                     |    |

| 1.7 | (a) Microring resonator, (b) microring modulator, (c) an SEM image of a microring resonator [3]                                                                                                                                                                                             |    |

| 2.1 | <ul> <li>(a) A microscopic image of a microring modulator with 10 μm diameter;</li> <li>(b) Transmission spectra sequence with bias current ranging from 0 to 0.5 mA.</li> </ul>                                                                                                            | 1  |

| 2.2 | A subsection of design space of the microring resonators, with microring spectrum fitting, and the separation of critical, over, and under coupled conditions.                                                                                                                              | 1  |

| 2.3 | Extracted (a) $\delta_1$ and (b) $\delta_{2a}$ from the measured Q and ER                                                                                                                                                                                                                   | 2  |

| 2.4 | Average (a) $\delta_1$ and (b) $\delta_{2a}$ with fitting results of coupling coefficient model, where circles are measured data, and red lines are fitting results                                                                                                                         | 2  |

| 2.5 | Model prediction relative error of the $Q$ and $ER$ , where $ER$ is represented<br>by $A = 1 - 1/ER$ to avoid the large $ER$ values close to critical coupling.<br>The 7 × 7 matrix represents the design variants of the microring modulator<br>with different $G_{thru}$ and $G_{drop}$ . | 2  |

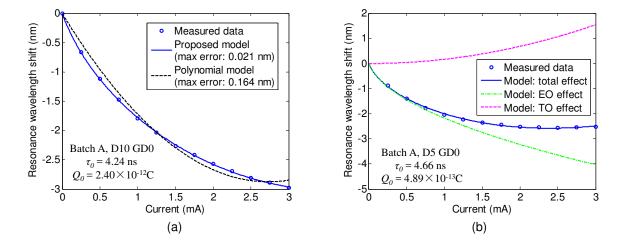

| 2.6 | (a) Measured resonance wavelength shift with fitting results using our                                                                                                                                                                                                                      | Δ. |

| 2.0 | proposed model and empirical polynomial model; (b) Decomposition of                                                                                                                                                                                                                         |    |

|     | wavelength shift to eletro-optic and thermo-optic effect.                                                                                                                                                                                                                                   | 2  |

| 2.7 | Resonance wavelength shift of modulators with model fitting: (a) Batch<br>A with different diameters (D in µm) and guard distances (GD in µm);                                                                                                                                              | 2  |

|     | (b) Batch B with different slab heights (in nm) and GDs (in µm)                                                                                                                                                                                                                             | 2  |

|     |                                                                                                                                                                                                                                                                                             |    |

| 2.8  | Fitting results of the resonance wavelength model for devices with differ-<br>ent fabrications, diameters (D), and slab heights: (a) EO effect (metric:                                                                                                                                                              |          |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|      | $a/\sqrt{I_0}$ ; (b) TO effect (metric: c)                                                                                                                                                                                                                                                                           | 25       |

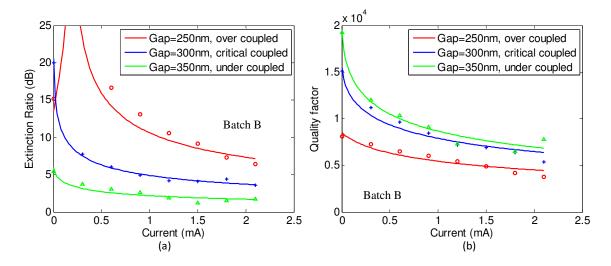

| 2.9  | Measured data (circles) and model fitting results (lines) for (a) extinction<br>ratio and (b) quality factor of devices with different coupling gaps and                                                                                                                                                             |          |

|      | coupling cases.                                                                                                                                                                                                                                                                                                      | 27       |

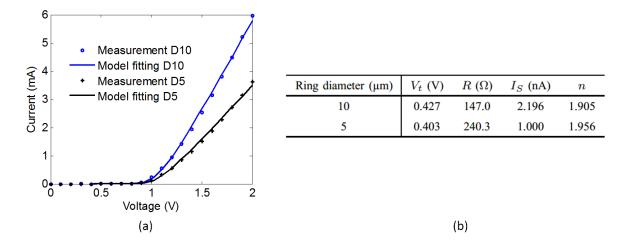

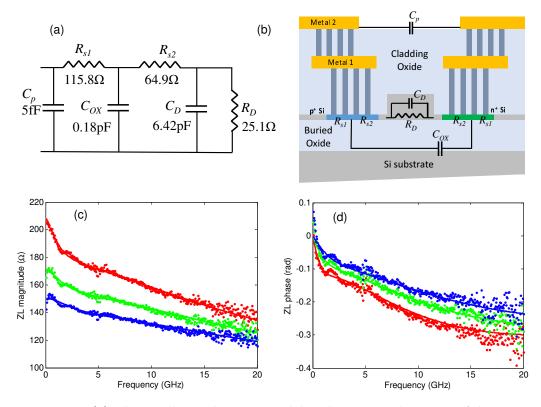

|      | Measured and model fitted I-V curves of modulators with different diameters.<br>(a) The small-signal circuit model with circuit values at 1mA bias points;<br>(b) The cross-section of the microring waveguide; (c)(d) Curve-fitting of<br>the measured load impedance $Z_L$ of the modulator with a 10 µm diameter. | 28       |

| 0 10 | (bias points: red 1 mA, green 2 mA, blue 3 mA)                                                                                                                                                                                                                                                                       | 29       |

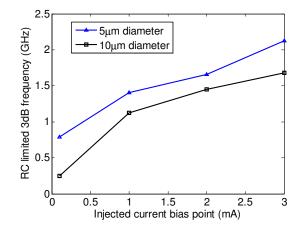

| 2.12 | The RC limited 3dB frequency predicted by the small-signal circuit model for devices with diameter of 5 $\mu$ m and 10 $\mu$ m at different bias points                                                                                                                                                              | 30       |

| 2.13 | The large-signal model framework of the microring modulator                                                                                                                                                                                                                                                          | 31       |

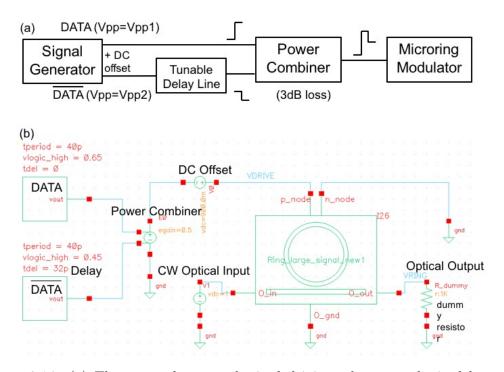

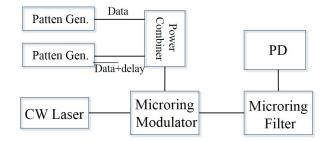

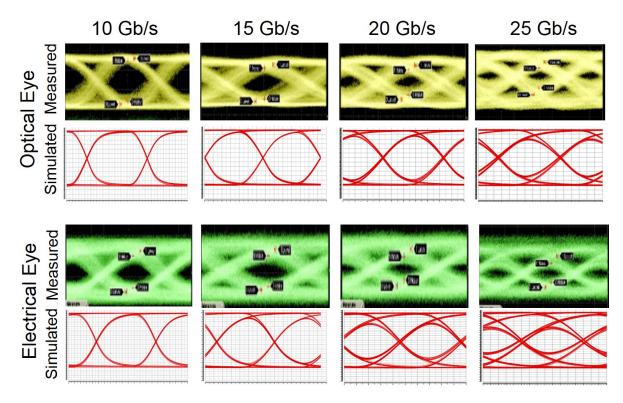

|      | (a) The external pre-emphasized driving scheme synthesized by combining DATA and delayed DATA. (b) The Cadence simulation schematic for the                                                                                                                                                                          |          |

|      | modulator with a pre-emphasized driving signal.                                                                                                                                                                                                                                                                      | 32       |

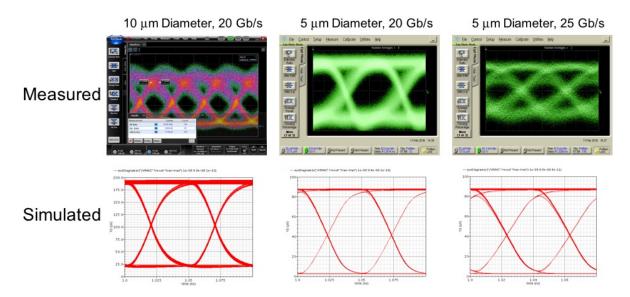

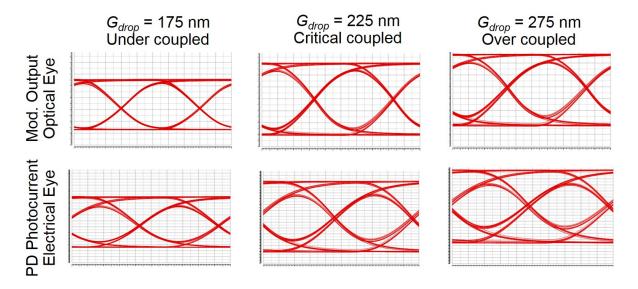

| 2.15 | The experimentally measured and model simulated high-speed eye dia-                                                                                                                                                                                                                                                  |          |

|      | grams of microring modulators                                                                                                                                                                                                                                                                                        | 33       |

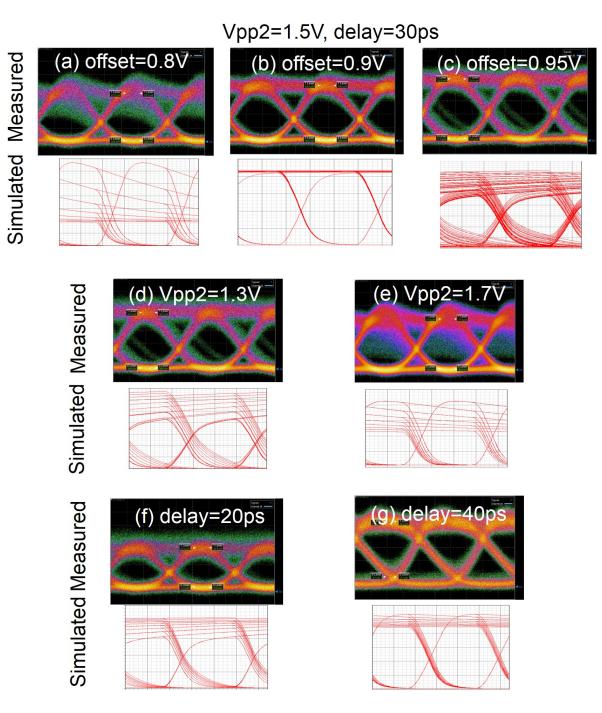

| 2.16 | Measured and simulated eye diagrams with optimal and several sub-optimal driving conditions                                                                                                                                                                                                                          | 34       |

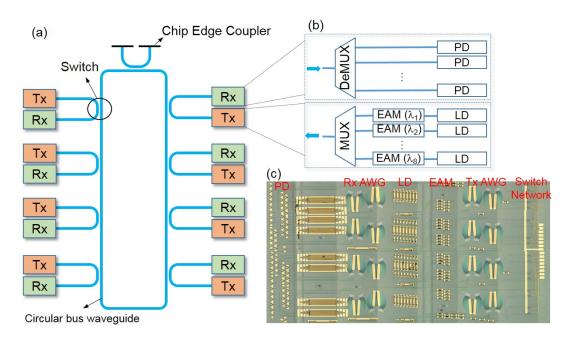

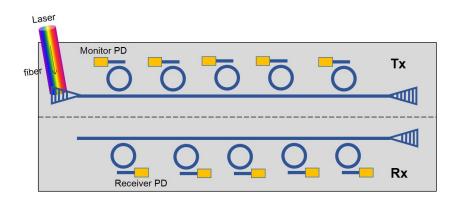

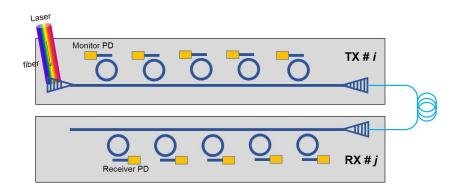

| 3.1  | (a)(b) Our ONoC architecture with a zoom-in of a transmitter (Tx) and a receiver (Rx), where LD: laser diode, EAM: electroabsorption modulator, PD: photodetector, $\lambda_{1\sim8}$ : channel wavelengths; (c) The microscopic image of the fabricated ONoC including 8 transceiver nodes                          | 38       |

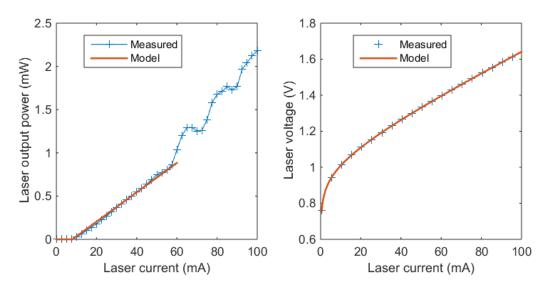

| 3.2  | Measured and model simulated single facet light-current (LI) and voltage-<br>current (IV) curves of the DFB laser                                                                                                                                                                                                    | 40       |

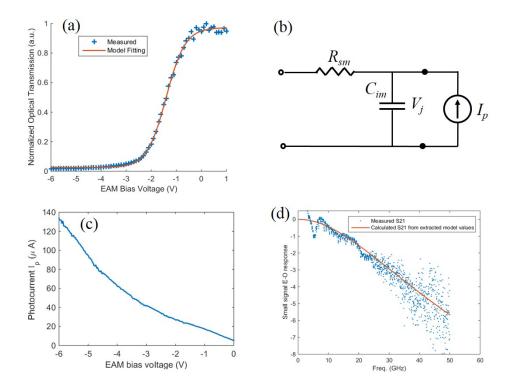

| 3.3  | EAM: (a) Measured and model fitted optical transmission at 1550 nm wavelength; (b) Equivalent circuit model; (c) Measurement photocurrent generated by the absorbed optical power (input optical power = $316 \mu$ W); (d) Directly measured and model calculated small-signal E-O (electrical-                      |          |

| 94   | to-optical) responses                                                                                                                                                                                                                                                                                                | 42       |

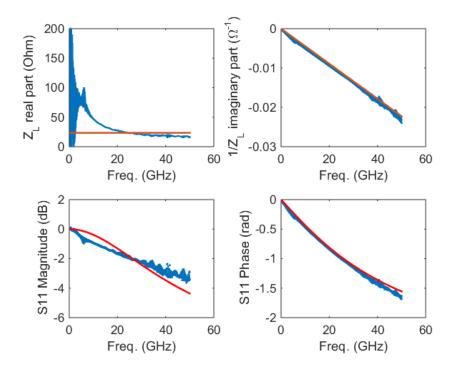

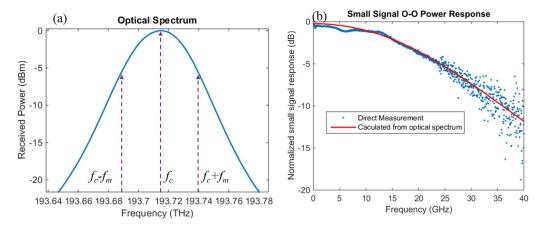

| 3.4  | measurement data and red lines show model results                                                                                                                                                                                                                                                                    | 43       |

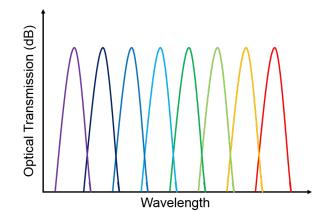

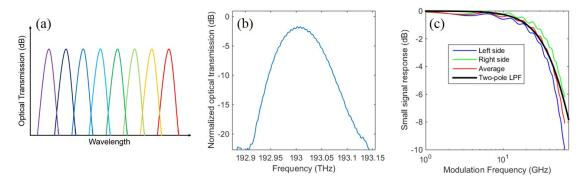

| 3.5  | A typical optical spectrum of AWG.                                                                                                                                                                                                                                                                                   | 40<br>44 |

| 3.6  | (a) Measured optical spectrum of a commercial bandpass filter (BPF); (b)                                                                                                                                                                                                                                             |          |

|      | Measured and calculated small signal responses of the BPF                                                                                                                                                                                                                                                            | 45       |

| 3.7  | (a) Measured single channel optical spectrum of the AWG; (b) The calculated frequency response using AWG's optical spectrum, with an approx-                                                                                                                                                                         |          |

|      | imation by a low pass filter (black line)                                                                                                                                                                                                                                                                            | 46       |

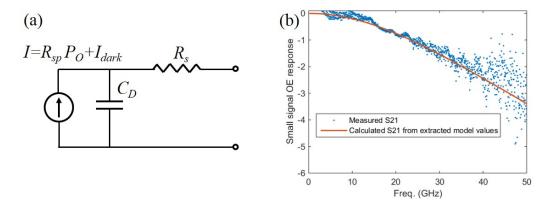

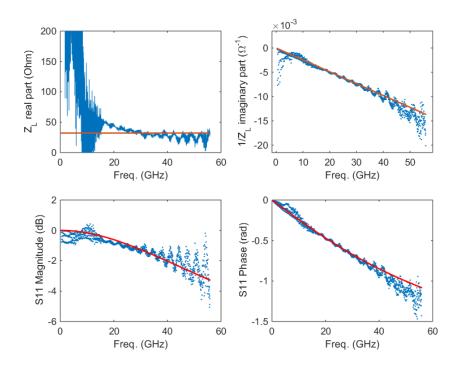

| 3.8        | (a) PD's equivalent circuit model; (b) Directly measured and model cal-<br>culated small-signal O-E (optical-to-electrical) responses of the PD at -3V                                                                                                                                                                       |          |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|            | bias                                                                                                                                                                                                                                                                                                                         | 47       |

| 3.9        | S11 and device impedance data of the PD at -3V bias, where blue dots represent measurement data and red lines show model results                                                                                                                                                                                             | 47       |

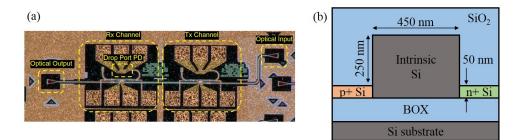

| 4.1        | (a) Microscopic image of our back-to-back optical transceiver; (b) Cross section view of the microring waveguide.                                                                                                                                                                                                            | 50       |

| 4.2<br>4.3 | Cadence simulation schematic for the back-to-back optical transceiver<br>Measured and simulated optical and electrical eye diagrams of the back-                                                                                                                                                                             | 51       |

| 4.4        | to-back transceiver                                                                                                                                                                                                                                                                                                          |          |

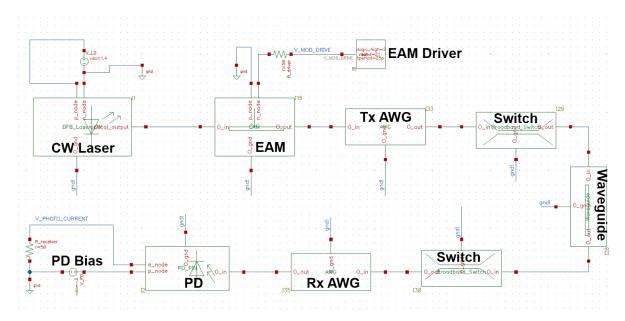

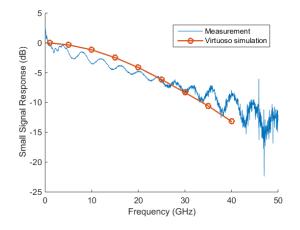

| 4.5        | with respect to microring modulators with different $G_{\text{drop}}$ The Virtuoso simulation schematic of the entire transceiver link using our developed models.                                                                                                                                                           | 53<br>54 |

| 4.6        | developed models                                                                                                                                                                                                                                                                                                             | 55       |

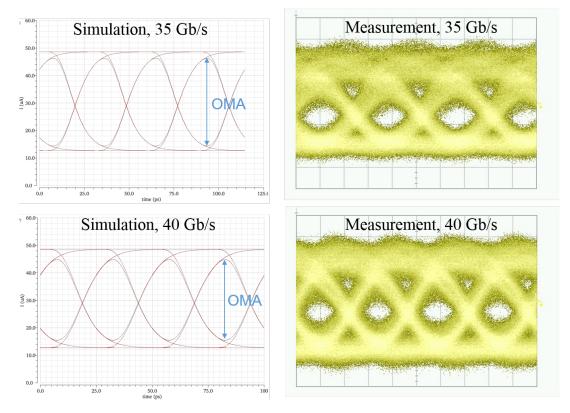

| 4.7        | Simulated eye diagrams of the PD current, and measured eye diagrams of<br>the RF amplifier that connects to the PD for a single channel transceiver                                                                                                                                                                          | 00       |

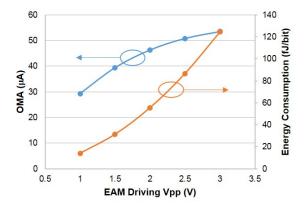

| 4.8        | link                                                                                                                                                                                                                                                                                                                         | 56       |

|            | EAM driving Vpps                                                                                                                                                                                                                                                                                                             | 58       |

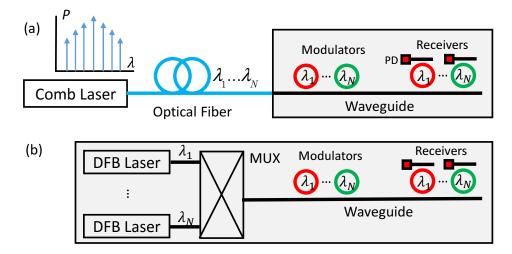

| 5.1        | Schematics of wavelength-division multiplexing (WDM) nanophotonic in-<br>terconnects using (a) an off-chip comb laser or (b) an on-chip DFB laser                                                                                                                                                                            | 69       |

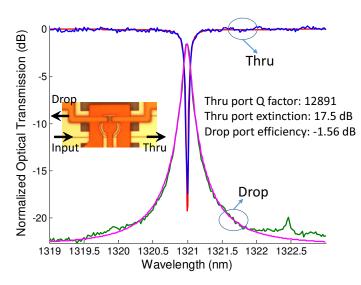

| 5.2        | array                                                                                                                                                                                                                                                                                                                        | 62       |

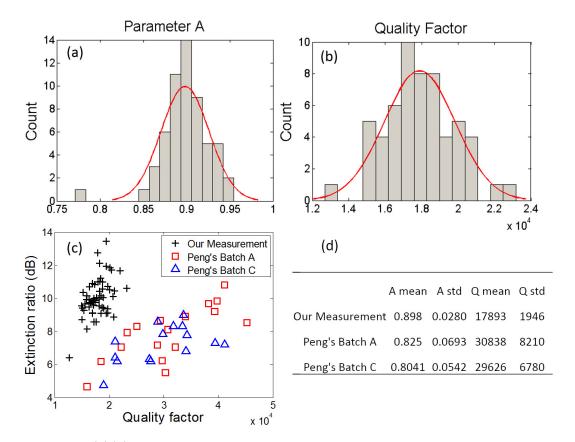

| 5.3        | scopic image of a fabricated microring modulator. $\dots \dots \dots \dots \dots \dots$<br>(a)(b) Histograms of parameters $A$ and $Q$ of our inter-die measurement<br>results; (c) Scatter plot of our inter-die measurement and Peng's intra-die<br>measurement in [4]; (d) Mean and standard deviation (std) of the three | 63       |

|            | measured data sets                                                                                                                                                                                                                                                                                                           | 65       |

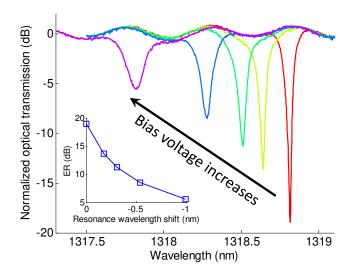

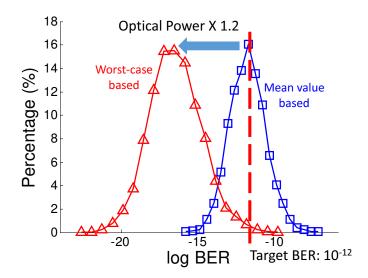

| 5.4        | The measured spectra series of a microring modulator at different bias voltages                                                                                                                                                                                                                                              | 65       |

| 5.5        | The BER distribution in the presence of process variations and the elec-<br>trical tuning. The blue line represents the link configuration based on the<br>means of the device parameters. The red line enhances the link optical                                                                                            |          |

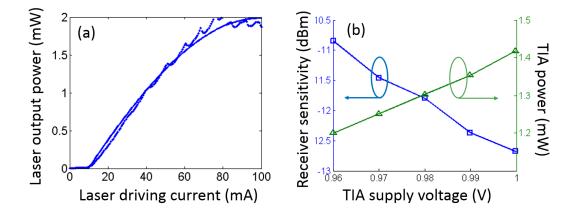

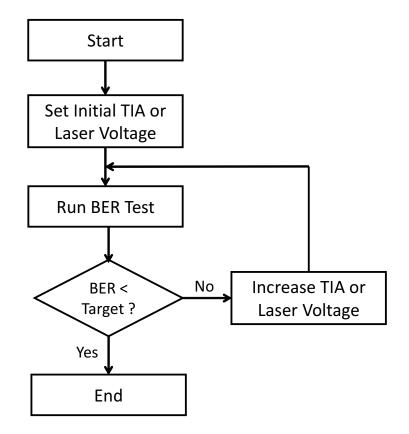

| 5.6        | power by 1.2X                                                                                                                                                                                                                                                                                                                | 66<br>68 |

| 5.7        | The adaptive flow.                                                                                                                                                                                                                                                                                                           | 69       |

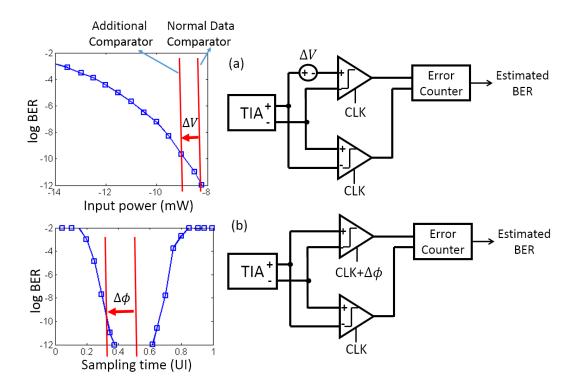

| 5.8  | The two fast BER estimation methods: (a) offset the voltage; (b) offset                        |     |

|------|------------------------------------------------------------------------------------------------|-----|

|      | the sampling time. The data in the left two figures are from $[5]$                             | 70  |

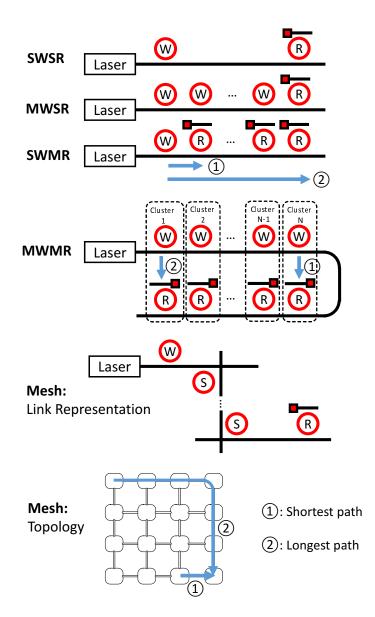

| 5.9  | Five types of link structures. Notions: W: writer or photonic modula-                          |     |

|      | tor; R: reader or photonic receiver; S: photonic switch or router. In a                        |     |

|      | WDM system, the laser represents a multi-wavelength light source; each                         |     |

|      | microring represents a microring array for multiple wavelength channels .                      | 72  |

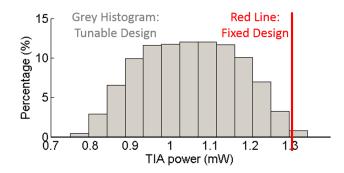

| 5.10 | The simulated TIA power consumption for the fixed design and the tunable                       |     |

|      | design                                                                                         | 74  |

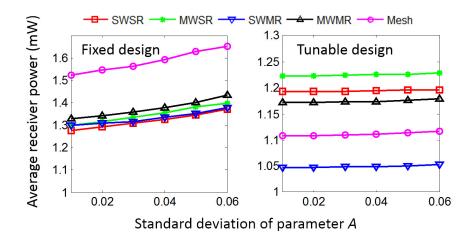

| 5.11 | The average receiver power consumption at different process variations                         |     |

|      | and for different link structures with 16 communication nodes                                  | 75  |

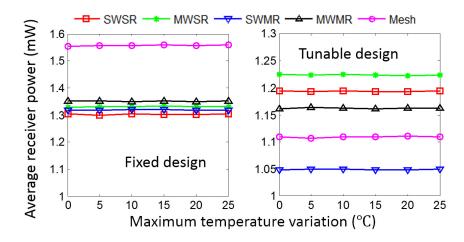

| 5.12 | The average receiver power consumption at different temperature varia-                         |     |

|      | tions and for different link structures with 16 communication nodes                            | 75  |

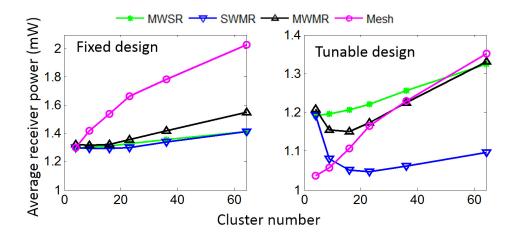

| 5.13 |                                                                                                |     |

| 0.20 | and for different link structures                                                              | 76  |

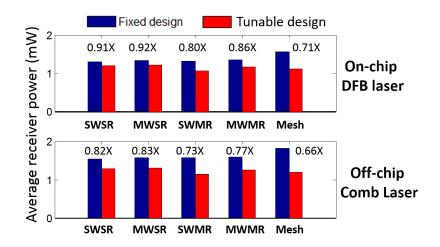

| 5.14 | The average receiver power consumption for different laser types and for                       | ••• |

| 0.11 | different link structures. The numbers denote the ratios of the average                        |     |

|      | receiver power by the tunable design to the fixed design                                       | 77  |

|      | receiver power by the tunable design to the fixed design                                       |     |

| 6.1  | Schematic of the WDM optical transceiver                                                       | 81  |

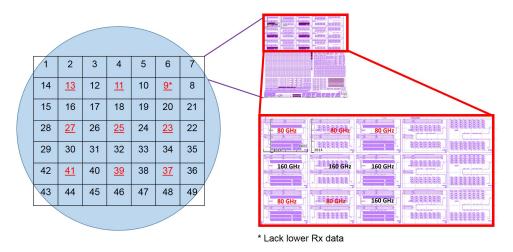

| 6.2  | The silicon photonic transceiver wafer.                                                        | 82  |

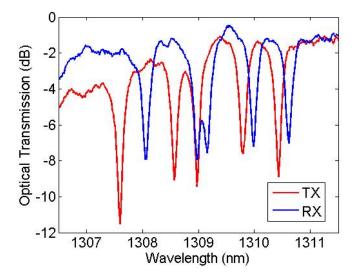

| 6.3  | Measured optical spectrum of a transceiver                                                     | 83  |

| 6.4  | Illustration of the thermal tuning of 10 microrings in a transceiver, where                    |     |

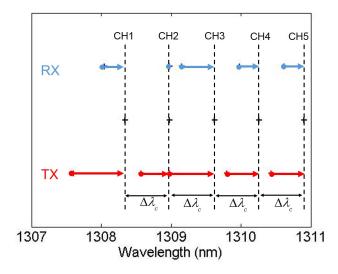

|      | $\Delta \lambda_c = 0.64 \text{ nm}.$                                                          | 84  |

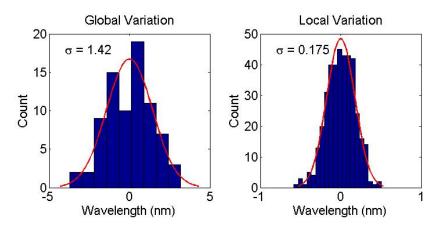

| 6.5  | The distribution of random variables of global and local variations for our                    |     |

|      | 80 GHz data set.                                                                               | 85  |

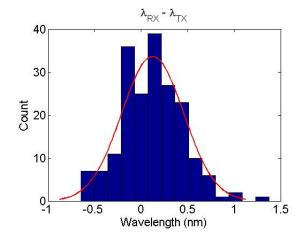

| 6.6  | The distribution of random variables of $\lambda_{RX} - \lambda_{TX}$ for our 80 GHz data set. | 86  |

| 6.7  | A schematic of an individual Tx connected to an individual Rx                                  | 87  |

| 6.8  | A schematic of two connected transceivers in a P2P link                                        | 89  |

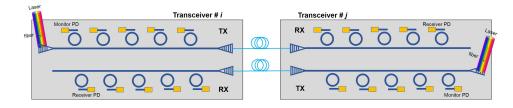

| 6.9  | The results of SA and greedy algorithm on two realistic data sets                              | 91  |

| 0.0  | The results of STI and Greedy algorithm on two realistic data sets                             | 01  |

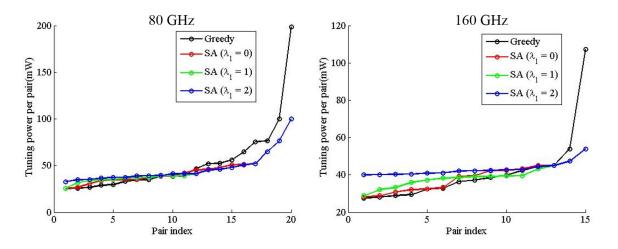

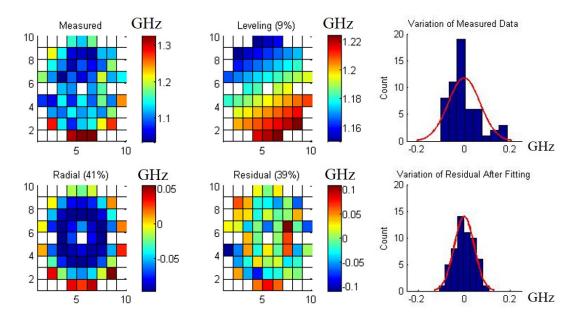

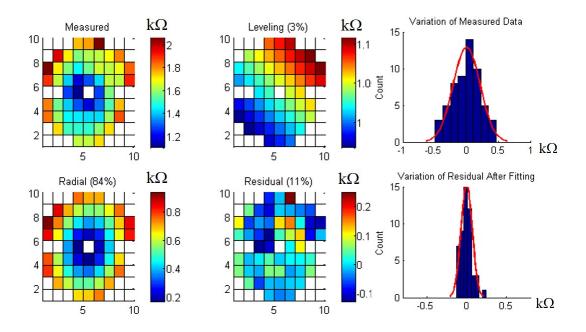

| 7.1  | Measured value and decomposition results of the diode resistance $R_D$ . The                   |     |

|      | center die is burnt. The radial component is not rotationally symmetric                        |     |

|      | with respect to the wafer center since the DUT deviates from the die center.                   | 96  |

| 7.2  | Measured value and decomposition results of the wafer-scale RC-limited                         |     |

|      | bandwidth.                                                                                     | 97  |

| 7.3  | Measured value and decomposition results of the wafer-scale heater resis-                      |     |

|      | tance.                                                                                         | 97  |

|      |                                                                                                |     |

# List of Tables

| PD Design Space and Simulated OMA                    | 57                                |

|------------------------------------------------------|-----------------------------------|

| Optimal Assignment of Tx to Rx using Realistic Data  | 88                                |

| Optimal Assignment of Tx to Rx using Synthetic Data  | 88                                |

| Optimal Pairing of Transceivers using Realistic Data | 92                                |

| Optimal Pairing of Transceivers using Synthetic Data | 93                                |

|                                                      | PD Design Space and Simulated OMA |

# Chapter 1

# Introduction

The fast increasing complexity of optical interconnects and its sensitivity to process and thermal variations pose the great demand for compact modeling, efficient simulation, and variation management schemes. This chapter introduces background of optical interconnects, motivations of the thesis work, and summary of some related work.

### **1.1** Background and Motivation

Optical communication posses high bandwidth, high data rate capacity, small propagation delay, low power consumption, small crosstalk, and high tolerance of electromagnetic interference over traditional electrical communication. With the development of optical fibers with low loss, and semiconductor lasers in the 1970s, optical interconnects started to replace electrical interconnects. In the past several decades, the deployment of optical communications has been spread from long-haul backbone networks to metropolitan area networks (MAN) and local area networks (LAN). In recent years, fiberto-the-home (FTTH) infrastructure are being deployed to address the bottleneck of last mile to customer. Nowadays, optical interconnects are starting to penetrate into the the short-reach datacom regime [6]: Intel just rolled out its silicon photonics based optical transceivers for data center applications [7]. IBM has been devoted to bringing electrical-optical interfaces closer to processors and memories for over a decade through the development of photonic device and packaging technologies [8]. Oracle's 3D macrochip system enables intimate integration and co-manufacturing of photonic chip and electronic chip [9]. Already achieving the success in rack-to-rack communications, optical interconnects are highly promising for the board-to-board, chip-to-chip, and eventually core-to-core communications. The evolvement of the optical interconnect applications is illustrated in Fig. 1.1.

Figure 1.1: The evolvement of optical interconnect distance and production volume. (Courtesy of Intel)

As the distances of optical interconnects decrease, the production volumes grow rapidly, calling for smaller optical device size and higher integration level, and driving the need for nanophotonic devices. Meanwhile, smaller interconnection distances require closer integration of electronics and photonics. Silicon photonics is emerging to meet these demands because of its CMOS process compatibility, manufacturing cost efficiency, and some good optical properties. By sharing the same material with CMOS circuits, silicon photonic devices can be fabricated side-by-side with electronic circuits (a.k.a. monolithic integration) [10]. Meanwhile, the legacy of the mature CMOS processes could greatly reduce the production cost of silicon photonics. Additionally, silicon/silica material system has high refractive index contrast and is transparent in optical communication wavelengths, enabling silicon waveguide with low propagation loss and low bending loss even for small bending radii [11]. The electro-optical effect (a.k.a. plasma dispersion effect) [12] in silicon makes some silicon based electro-optical modulators available, such as silicon microring modulators [13] and Mach-Zehnder modulators [14] that are based on silicon-on-insulator (SOI) substrates, and are all CMOS process compatible. Though it is hard to develop light emitting and amplifying devices on silicon due to its indirect band gap, several workarounds have been developed to wafer bond or directly grow III-V materials on silicon [15, 16].

With the CMOS friendly silicon photonics technology, the paradigm for future chip would likely be a hybrid electronic-photonic integrated circuit (EPIC) consisting electronic processor and memory parts, and optical transmission part. Fig. 1.2 shows a 3D view of a silicon photonic chip including photonic modulators, waveguides and detectors. These photonic components are fabricated with electronic transistors back-to-back.

The ever increasing integration level in short-reach optical interconnects drives more and more components integrated on one photonic integrated circuit (PIC). Fig. 1.3 shows the number of components on one PIC grows exponentially over time, which somewhat follows the Moore's Law of the microelectronics regime. The fast growing complexity of photonic integrated circuits (PICs) drives the need for photonics design automation tools, including trustworthy photonic circuit level models and simulators, photonics propertyaware automatic floor planning [17], layout and routing [18], design rule checking (DRC), and logic vs. schematic (LVS) [19]. Photonics designers need circuit and link level PIC design, layout, and simulation tools. Meanwhile, electronic circuit designers need

Figure 1.2: IBM's silicon photonic chip. (Courtesy of IBM)

accurate compact models of photonic devices to design the complex PIC drivers. All of these demands call for proper computer-aided design (CAD) tools for photonics and electronic-photonic design automation (EPDA) softwares.

Thermal variation and fabrication process variation problem significantly arise in short-reach optical interconnects. The performance and characteristics of optical devices can highly depend on its operational temperature. In conventional long-range optical interconnects, optical devices or modules can be individually cooled by dedicated temperature controllers because the conventional optical modules are individually packaged, and the long-range communications can afford the expense and power of the temperature controllers. In contrast, the nanophotonic components in short-reach optical interconnects are highly integrated and are even closely placed with electronic devices, which makes dedicated temperature controllers impossible. Therefore, it is desired to accurately model and manage the device performance with complicated temperature fluctuations in a electro-optical integrated system.

Fabrication process variation is another sever problem for nanophotonic devices, since

Figure 1.3: Number of photonic components integrated on one photonic chip over the past decades for three integrated photonics technology platforms. (Courtesy of J. Hulme)

the photonic device dimension enters the hundred of nanometers regime, and the absolute process variation amount takes a large portion of the device dimension. The process variations can cause performance degradation or even failure of the optical devices and systems, and therefore need to be modeled and managed effectively and efficiently.

In summary, silicon photonics based short-reach optical interconnect raises problems in CAD for photonics, and management of thermal and process variation effects. This dissertation focuses on these two problems.

# **1.2** Overview of Optical Interconnects and Devices

Fig. 1.4 illustrates an optical interconnect structure including one transmitter (Tx) and one receiver  $(Rx)^1$ . The CMOS die consists modulator driver, and receiver circuits. Processor cores or memories could be placed on the CMOS die in on-chip or chip-to-chip interconnects. In this scheme, light is generated by an off-chip multi-wavelength

<sup>&</sup>lt;sup>1</sup>It can be easily extended to multi-Tx/multi-Rx structure or network using optical switches.

light source, and then coupled onto chip by a grating coupler. To avoid the coupling loss, on-chip heterogonously integrated III-V on silicon lasers could be utilized [1], while the heterogonously integration will increase the process complexity. The light propagates through the silicon waveguide, and is modulated by an array of silicon microring modulators. The microring modulator is capable of modulating the light at a specific wavelength. The colors of the microrings in Fig. 1.4 represents various wavelengths. Similarly, in the receiver side, light at a corresponding wavelength is routed by a microring filter to a photodetector (PD). These wavelength selective microring structures implement wavelength-division multiplexing (WDM) without dedicated (de)multiplexers. The Tx and Rx could be on the same chip, on different chips, or different boards, connecting by on-chip waveguides, on-board polymer fibers, or optical fibers to achieve on-chip, chip-to-chip, or board-to-board communications.

Figure 1.4: A silicon photonics based optical interconnect structure.

Here we introduce the SOI-based silicon photonics platform, and several selected photonic components.

#### 1.2.1 SOI Platform and Silicon Waveguide

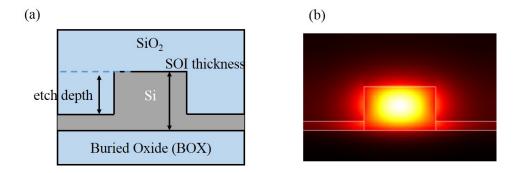

Silicon photonics usually utilize SOI wafers to fabricate photonic components, since the light confinement needs a high refractive index core and low index claddings, and the buried oxide (BOX) under the silicon layer in the SOI wafer can server as the lower cladding. The upper cladding could be either air or SiO<sub>2</sub>. Fig. 1.5 (a) shows a silicon waveguide fabricated on the SOI platform, which serves as a basic building block for other complex silicon photonic components. The waveguide is defined by partially or fully etching the silicon layer, constructing wire<sup>2</sup> or rib waveguide. The partially etched rib waveguide needs careful control of etch depth, while it has the advantages that the rib could serve as the current path in active devices, and it is more tolerant to sidewall roughness and less likely to have resonance splitting in microrings than the fully etched waveguide. SOI wafers with various silicon thicknesses are being used, for example: 220 nm in [20], 250 nm in [21], and 500 nm in [1].

Figure 1.5: Cross section of a silicon waveguide and its optical mode illustration

Fig. 1.5 (b) illustrates the optical mode profile (or the optical power distribution) of the silicon waveguide. Silicon wire or rib waveguide could support certain number of discrete optical modes, depending the waveguide index profile and geometry [22]. Each mode has its effective refractive index  $n_{eff}$ , from which the propagation constant could

<sup>&</sup>lt;sup>2</sup>a.k.a strip waveguide

be calculated. Usually on-chip waveguides are designed to be single-mode such that it supports only the fundamental mode.

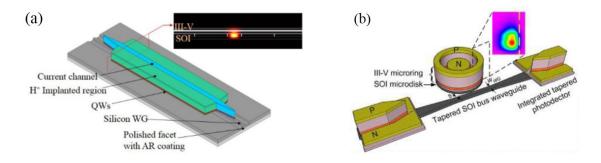

#### 1.2.2 Laser

Silicon is not suitable for light generation due to its indirect band gap. III-V materials, the traditional material to provide optical gain, could be bonded to SOI wafers. Fig. 1.6 shows a heterogenous III-V on silicon distributed feedback (DFB) in-plane laser and a microring laser. III-V material pieces are bonded to pre-patterned SOI substrates through low temperature bonding process[1, 2]. An InP layer helps the crystal transition between the III-V quantum wells and SOI. The III-V material layers generate optical gain when current is injected into the quantum wells. Optical taper structures allow the light to be evanescently coupled into the III-V layers from SOI waveguides (i.e. the optical mode appears both in the III-V and the silicon regions). In this way, light is generated in the III-V region and transferred to the silicon waveguide.

Figure 1.6: 3D view of in-plane and microring heterogeneous silicon lasers [1, 2].

Researchers also grow III-V quantum dots on SOI substrate [16, 23]. Quantum dots are investigated for direct growth because they could mitigate the unwanted dislocations caused by material difference between compound semiconductors and III-V and silicon. Additionally, quantum dot lasers promise high temperature stability and low threshold current density due to three dimensional carrier confinement compared to quantum well lasers.

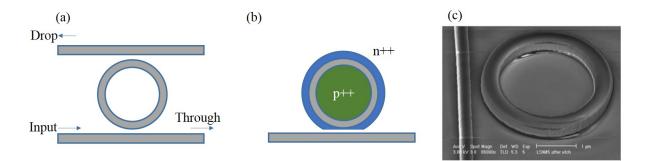

### 1.2.3 Microring-based Modulator, Filter and Switch

A basic microring resonator consists of a silicon microring waveguide and one or two straight waveguides. Fig. 1.7 (a) shows microring resonator with an input waveguide and a drop waveguide. The light is injected into the input port and is coupled into the microring waveguide. When the the optical path length around the microring is an integer number of the light wavelength (i.e. the resonance condition is met), the constructive interference lets the light energy build up within the microring. Consequently, the through port energy reaches a minima and and the drop port energy reaches a maxima. This wavelength selectivity property could be used to realize a modulator: In Fig. 1.7 (b), current is injected into the microring waveguide by p and n doping, such that the silicon index is changed and resonance wavelength is shifted, achieving on-off keying modulation. Additionally, the routing property of microring resonator makes it very suitable as the building block for complex optical switches [24, 25].

Figure 1.7: (a) Microring resonator, (b) microring modulator, (c) an SEM image of a microring resonator [3].

#### 1.2.4 Photodetector

Silicon photonic interconnects usually use CMOS process-compatible Ge or SiGe photodetectors to convert optical light to photocurrent [26, 27]. In p-i-n based photodiodes, input light could generate electrons and holes in the intrinsic region. With negative bias on the diode, the photocurrent is approximately proportional to the input light energy. The weak photocurrent is usually amplified by receiver circuit.

### 1.3 Literature Review

There have been a number of prior studies on device-level modeling, and link- or system-level design space exploration of optical interconnects. This section summarizes selected work on device-level and system-level.

### **1.3.1** Compact Modeling of Photonic Devices

Similar to transistor models, compact photonic device models are needed for accurate link-level simulations of complex optical interconnects. Kononov [28] presented several simple photonic device models. These models were further implemented in Verilog-A by defining new optical natures to describe the optical magnitude and phase. Verilog-A is a analog hardware description language, and can be accepted by many modern versions of SPICE simulators (e.g. Synopsys HSPICE, and Cadence Spectre). Verilog-A photonic device models can be co-simulated with electronic circuits, and has been more and more attract for photonic device modeling: Christen *et al.* implemented a model of vertical-cavity surface-emitting laser (VCSEL) for efficient simulation of optical links [29]. Zhu *et al.* developed a detailed Verilog-A model for a traveling-wave silicon Mach-Zehnder modulator, successfully capturing its optical and distributed electrical properties, and simulating optical eye diagrams [30]. The carrier-depletion based silicon microring modulator was modeled in Verilog-A by describing its optical and electrical behaviors [31]. In [32], the authors developed basic and composite models in Verilog-A, and simulated a WDM interconnect system and a frequency stabilization system. Many photonic foundry service providers are also developing their device models in Verilog-A, such as IMEC [33], and CEA-Leti [34].

### **1.3.2** System-Level Design of Optical Interconnects

Optical interconnects have been proposed to be used in network-on-chip (NoC) architectures (a.k.a. optical NoC). The unique properties of optical interconnect call for system-level design and management strategies. In the architectural design aspect, Vantrease *et al.* proposed Corona structure based on a fully-connected  $64 \cdot 64$  optical crossbar, and a all optical, token-based arbitration scheme. A Clos optial network was proposed in [35] that used point-to-point optical links for state-to-stage communication and electrical routers for routing. Pan *et al.* proposed Firefly architecture that used hybrid electrical and optical interconnects for intra-cluster and inter-cluster communications, respectively [36].

System-level simulation and analysis of optical NoCs are done in many work: Chan *et al.* presented PhoenixSim, a system-level simulator for optical NoC taking into accounts of many photonic device features [37]. Sun *et al.* developed NoC modeling tool called DSENT that could accommodate both electrical and optical networks [38]. Authors in [39] performed systematic crosstalk noise analysis of various optical NoC architectures.

Microring-based optical interconnect suffers from sever thermal and process variation effects: The full system simulation with realistic applications in [40] demonstrated that process and thermal variation poses significant reliability challenges for nanophotonic on-chip networks. The authors further modeled the reliability and proposed run-time thermal management guidelines regulating the peak temperature and the thermal gradient [41]. Similarly, Zhang *et al.* proposed a job allocation technique that minimizes the temperature gradients among the microring modulators/filters [42]. Cross-layer and thermal aware placement and floorplanning for optical NoC chips are performed in [43, 17]. To address the wavelength mismatch issue in an energy efficient manner, Zheng *et al.* proposed several techniques which greatly saved the total tuning power consumption [44, 45, 17]. The techniques include channel remapping, sub-channel redundant rings, transceiver-based network, fabricating fewer rings, and tuning fewer rings. Observing the fact that power consumption of an optical link scales with its data rate, authors in [46].

### 1.4 Thesis Outline

This thesis mainly consists two parts: Chapter 2-4 presents our work on compact modeling and link-level simulation of optical interconnects. Chapter 5-8 discusses modeling and management techniques of process and thermal variations in silicon photonic interconnects.

Chapter 2 presents compact models for various characteristics of microring-based modulators and filters. Several other common photonic devices are modeled in Chapter 3 including their optical and electrical models, forming a device model library together with Chapter 2. Chapter 4 demonstrates circuit-level simulation results of two fabricated links based on the well validated device library.

In Chapter 5, an adaptive tuning technique is proposed to save power consumption by allocating *just enough* power for each link through on-chip self tests. Chapter 6 designs optimization algorithms that pair microring-based optical transceivers so that their thermal tuning power is minimized. Spatial patterns of wafer-scale process variations are decomposed and analyzed in Chapter 7. Lastly, this thesis is concluded by Chapter 8.

# Chapter 2

# Compact Models for Silicon Microring-based Modulators and Filters

In this chapter, we developed compact models for silicon microring modulators, an important and versatile component in silicon photonic platform, in several important aspects including its design space, spectra at bias, electrical properties and large-signal dynamic behavior. The model is extensively validated by measurement data and then implemented in Verilog-A that is compatible with CMOS simulators.

# 2.1 Introduction

In silicon photonic interconnects, microring modulators are of great importance. The carrier-injection p-i-n type and the carrier-depletion p-n type are widely reported [47, 48, 49, 50, 51, 52, 53]. The carrier-depletion type has a high intrinsic bandwidth, as it does not rely on slow diffusion of minority carriers [51, 52]. However, the carrier-

injection type outperforms the carrier-depletion one in modulation depth and insertion loss due to the large change of refractive index [53, 47]. Meanwhile, the speed of the carrier-injection microring modulator can be greatly enhanced by a pre-emphasis driving scheme [47, 48, 49, 50].

Integrating silicon photonic devices into modern CMOS-VLSI design flows requires co-design of electronic and photonic integrated circuits, in which compact models for nanophotonic devices are needed. Researchers have proposed Verilog-A compact models for the Mach-Zehnder modulator [30], the VCSEL [33], and the pulsed optical source and the photodetector [34]. The carrier-depletion microring modulator has also been compactly modeled in many photonic link simulators (e.g., Lumerical Interconnect [54], RSoft OptSim Circuit [55], and DSENT [38]). Sacher *et al.* proposed a dynamic model for microring modulator, e.g., the resonance wavelength shift with respect to bias conditions, have not been accurately modeled. In this work, we develop compact DC and smallsignal models for carrier-injection modulators to provide physical insights to the device performance for a variety of designs.

The resonance wavelength shift in the microring modulator is essential for the on-off keying modulation. Therefore, we derive a theoretical equation for the resonance wavelength shift. The equation is capable of distinguishing the electro-optical blueshift effect and the thermo-optic redshift effect, enabling the analysis of the device design parameters' impact on the modulator's DC performance. Additionally, the quality factor  $\mathbb{Q}$  and the extinction ratio ER are important to determine the link power budget and signal quality [4]. Meanwhile, the  $\mathbb{Q}$  and the ER of the carrier-injection microring modulator change significantly with injected current. Therefore, we quantify the dependence of the  $\mathbb{Q}$  and the ER on the injected current.

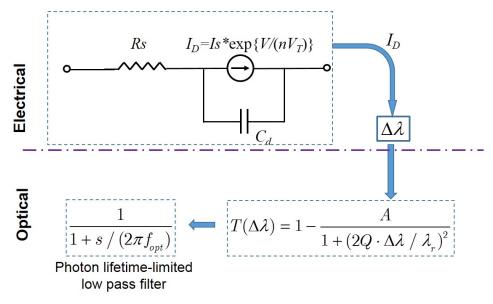

In order to characterize the high-speed behavior of the carrier-injection microring

modulator, we propose a small-signal circuit model. The small-signal circuit parameters are extracted from S11 measurements. The small-signal circuit matches the device structure and provides insights to the dependence of small-signal capacitances and resistances on bias points and design parameters. The small-signal model, together with the DC spectrum model, is implemented in Verilog-A to facilitate co-simulations of photonic and electronic circuits.

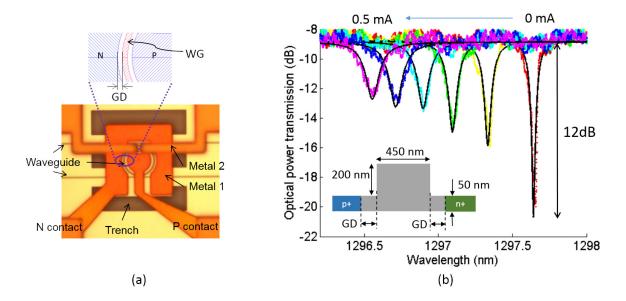

# 2.2 Device Designs and Fabrications

Fig. 2.1(a) shows a microscopic image of a microring modulator fabricated in CEA-LETI's silicon photonic SOI process. The rib section of the microring waveguide is 250 nm x 450 nm, and a slab section of 50 nm is used to inject carriers from the p-doped  $(3 \times 10^{19} \text{ cm}^{-3})$  and n-doped  $(3 \times 10^{19} \text{ cm}^{-3})$  regions, as shown in the Fig. 2.1(b) inset. There are several device design variants including microring diameter, guard distance (GD) between the boundary of doped region and rib waveguide, and the coupling gap between the ring waveguide and the bus waveguide. As part of process development, 25 wafers are used for engineering purposes. A set of short-loop wafers (Batch B) are processed through some subset of the total process steps to provide a snapshot of process reliability and modulators performance before the final delivery. We find that the contact resistance in this batch is significantly higher than the expected value due to miscalculation of the via etch depth. This contact resistance error has been corrected in the final delivery (Batch A).

In the experimental setup, vertical fiber-to-chip grating couplers are used to provide optical input and output access. Using a tunable laser, a DC voltage source, and an optical power meter, we measure the transmission spectra sequence of a microring modulator with respect to different bias current as shown in Fig. 2.1(b), where the colorful

Figure 2.1: (a) A microscopic image of a microring modulator with 10 µm diameter;

(b) Transmission spectra sequence with bias current ranging from 0 to 0.5 mA. The guard distance (GD) is 0, 0.2 µm, and 0.4 µm in our device designs.

dots represent measurement results, the black lines represent model results, and the inset shows the cross section of the microring waveguide. The microring modulator has a quality factor of 12,000 at zero injection, and achieves an on/off extinction ratio of 12 dB.

### 2.3 Device Design Space Model

In order to model the Q and ER of microrings in the device design space, we first model the dependence of Q and ER on coupling coefficient and optical loss in the microring, and then model the relationship between coupling coefficient and coupling gap. Here we define  $\delta_1$  as the through port coupling ratio, and  $\delta_{2a}$  as the sum of ring cavity loss and drop port coupling ratio (both in terms of power):

$$\delta_1 = \kappa_t^2, \quad \delta_{2a} = \kappa_d^2 + \alpha L \tag{2.1}$$

Where  $\kappa_t$  (or  $\kappa_d$ ) is through (or drop) port coupling coefficient in terms of field amplitude ratio; and  $\alpha L$  is the round trip loss of optical power in the microring.

Bogaerts *et al.* presented equations for Q and ER of microring resonators in [57]. We simplify their expressions based on the approximation that both  $\delta_1$  and  $\delta_{2a}$  are close to zero:

$$Q = \frac{2\pi\lambda_r}{FSR\cdot(\delta_1 + \delta_{2a})}, \quad ER = \left(\frac{\delta_1 + \delta_{2a}}{\delta_1 - \delta_{2a}}\right)^2 \tag{2.2}$$

In these expressions, FSR is the free spectral range of the microring spectrum. From the measured optical spectra of the microring resonator, we can extract Q and ER, and then  $\delta_1$  and  $\delta_{2a}$ . By defining  $\delta_c = \delta_1 + \delta_{2a}$ , we have:

$$\delta_c = \frac{2\pi\lambda_r}{Q\cdot FSR} \tag{2.3}$$

When the microring is under-coupled:

$$\delta_1 = \frac{\delta_c}{2} (1 - \frac{1}{\sqrt{ER}}), \quad \delta_{2a} = \frac{\delta_c}{2} (1 + \frac{1}{\sqrt{ER}})$$

(2.4)

And when the microring is over-coupled:

$$\delta_1 = \frac{\delta_c}{2} (1 + \frac{1}{\sqrt{ER}}), \quad \delta_{2a} = \frac{\delta_c}{2} (1 - \frac{1}{\sqrt{ER}})$$

(2.5)

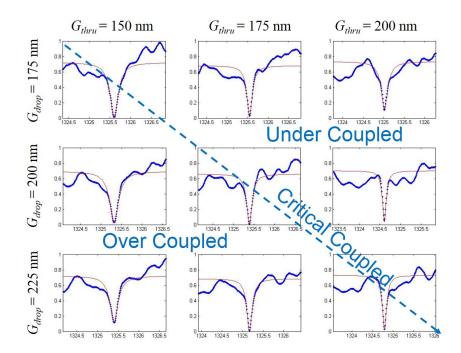

From Eqs. (2.4) and (2.5) we can see that the calculation of  $\delta$  values depends on the coupling condition. Fortunately, we have 7×7 devices where the microring test structures were fabricated with different  $G_{thru}$  and  $G_{drop}$  as shown in Fig. 2.2. Some of the gap combinations lead to critical coupling indicated by high extinction ratios. Then we can identify under coupled devices with a larger  $G_{thru}$  and a smaller  $G_{drop}$  than the critical coupled devices, and vice versa (dot line and label in Fig. 2.2).

Figure 2.2: A subsection of design space of the microring resonators, with microring spectrum fitting, and the separation of critical, over, and under coupled conditions.

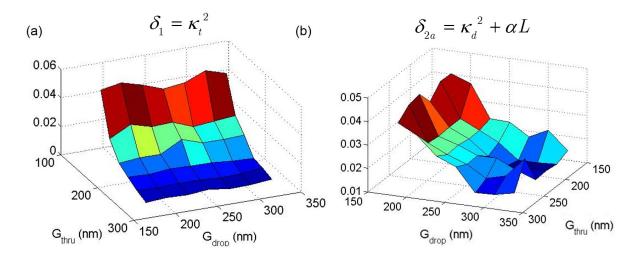

We first extract Q and ER from measured spectra of the microring resonators, and then extract  $\delta$  values from Q and ER based on Eqs. (2.4) and (2.5). The extraction results in Fig. 2.3 show that  $\delta_1$  mainly depends on  $G_{thru}$ , and  $\delta_{2a}$  mainly depends  $G_{drop}$ . These dependency trends are consistent with the definitions of  $\delta_1$  and  $\delta_{2a}$ . The measured data of the microrings with  $G_{thru} = 300$  nm is not included because of the weak coupling and unclear resonance dips.

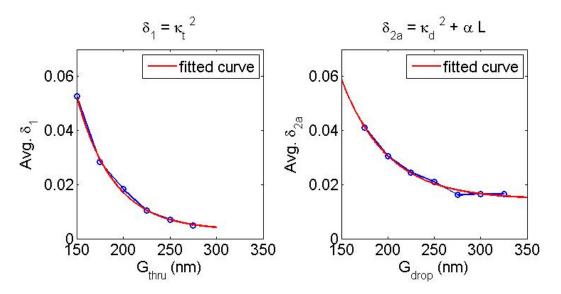

Since there are some fluctuation errors in Fig. 2.3, we calculate the average  $\delta_1$  (or  $\delta_{2a}$ ) for different  $G_{drop}$  (or  $G_{thru}$ ) and replot the data in Fig. 2.4. It can be seen that the values of  $\delta_1$  and  $\delta_{2a}$  are close to zero, which confirms our previous approximation. Based on both the experimental data trend and theoretical analysis [22], we propose an exponential model for the two  $\delta$  as shown in Eq. (2.6), where a, b, and c are fitting

Figure 2.3: Extracted (a)  $\delta_1$  and (b)  $\delta_{2a}$  from the measured Q and ER.

parameters. Fig. 2.4 shows that this exponential model can fit the measured data well.

$$\delta_1 = a_1 \cdot \exp\left(-b_1 \cdot G_t\right) + c_1$$

$$\delta_{2a} = a_2 \cdot \exp\left(-b_2 \cdot G_d\right) + c_2$$

(2.6)

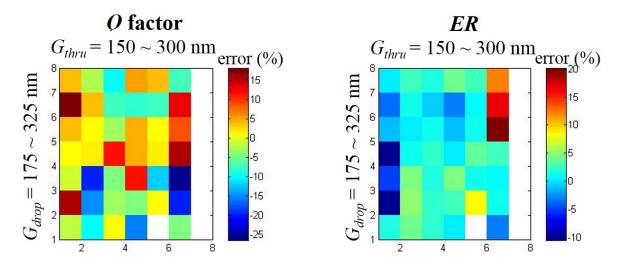

In summary, Eq. (2.6) can be used to calculate the coupling coefficients, and Eq. (2.2) to calculate the Q and ER. To validate our model, we compare the Q and ER values predicted by the model with the ones extracted from experiments, as shown in Fig. 2.5. The low relative errors indicate that our analytical model can accurately predict the Q and ER of the microring resonators. Also, this design space model is developed for passive microring structures, and therefore is valid to both microring-based modulators and filters.

Figure 2.4: Average (a)  $\delta_1$  and (b)  $\delta_{2a}$  with fitting results of coupling coefficient model, where circles are measured data, and red lines are fitting results.

# 2.4 Electro-Optic Modulation Model

The electro-optic modulation of microring resonators utilizes the plasma dispersion effect, in which the refractive index and optical loss of silicon are altered by changing the carrier concentration [12]. As the silicon index changes, the resonance wavelength shifts. Meanwhile, the quality factor and extinction ratio also change due to the increase of the optical loss. we derive theoretical models for the resonance wavelength, the extinction ratio, and the quality factor.

#### 2.4.1 Resonance Wavelength Shift

The electro-optic (EO) effect changes the silicon refractive index, the mode effective index, and in turn the resonance wavelength. The relationship between the EO effect induced resonance wavelength shift  $\Delta \lambda_r^{EO}$  and the carrier concentration change  $\Delta N$  is given by:

$$\Delta \lambda_r^{EO} = -\frac{\lambda_r}{n_g} \Gamma n_f \Delta N \tag{2.7}$$

Figure 2.5: Model prediction relative error of the Q and ER, where ER is represented by A = 1 - 1/ER to avoid the large ER values close to critical coupling. The 7 × 7 matrix represents the design variants of the microring modulator with different  $G_{thru}$ and  $G_{drop}$ .

where  $n_g$  is the group index of the optical mode;  $\Gamma$  is the mode confinement factor [58, 59];  $n_f \approx 2.13 \times 10^{-21} \text{cm}^3$  is the ratio between the change of silicon index and the change of carrier concentration when  $\Delta N \sim 10^{18} \text{cm}^{-3}$  [47, 12, 22].

The steady state injected charge  $Q_{inj}$  in the p-i-n junction can be described by the following nonlinear equation [60]:

$$Q_{inj} = I\tau_c = I \frac{\tau_0}{1 + Q_{inj}/Q_0} \Rightarrow Q_{inj} = \frac{Q_0}{2} \left( \sqrt{1 + \frac{4I\tau_0}{Q_0}} - 1 \right)$$

(2.8)

where  $\tau_0$  is the carrier lifetime at a low carrier density;  $Q_0$  is a fitting parameter describing the dependence of carrier lifetime on the carrier density [60]. Considering the carrier concentration change  $\Delta N = Q_{inj}/q\mathbb{V}$  where  $\mathbb{V}$  is the junction volume, we can derive the lumped equation for the EO effect induced resonance wavelength shift:

$$\Delta \lambda_r^{EO} = -\frac{\lambda_r \Gamma}{n_g} n_f \frac{Q_0}{2q \mathbb{V}} \left( \sqrt{1 + \frac{4I\tau_0}{Q_0}} - 1 \right) \triangleq -a \cdot \left( \sqrt{1 + I/I_0} - 1 \right)$$

(2.9)

In a practical carrier-injection modulator, the thermo-optic (TO) effect caused by the self-heating of the injected current is non-negligible. The silicon index increases with the temperature:

$$\Delta n_{Si} = \frac{\mathrm{d}n_{Si}}{\mathrm{d}T} \cdot \Delta T \tag{2.10}$$

The temperature rise  $\Delta T$  can be characterized as  $\Delta T = \theta I^2 R$ , where  $\theta$  is the thermal impedance of the p-i-n junction. Therefore, the TO effect induced resonance wavelength shift is:

$$\Delta \lambda_r^{TO} = \frac{\lambda_r \Gamma}{n_g} \frac{\mathrm{d}n_{Si}}{\mathrm{d}T} \theta R \cdot I^2 \triangleq c \cdot I^2$$

(2.11)

Consequently, the total resonance wavelength shift is given by:

$$\Delta \lambda_r^{total} = \Delta \lambda_r^{EO} + \Delta \lambda_r^{TO} = -a \cdot \left(\sqrt{1 + I/I_0} - 1\right) + c \cdot I^2 \tag{2.12}$$

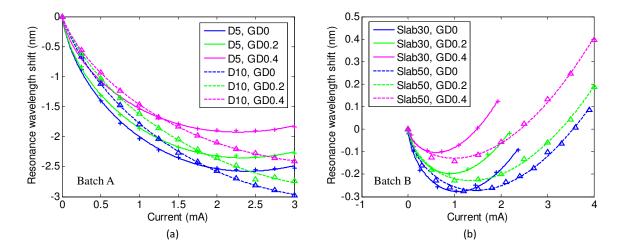

The  $\Delta\lambda_r$  model in Eq. (2.12) results in excellent fitting with the measured data from different device designs and fabrication batches, as shown in Fig. 2.6 and Fig. 2.7, where symbols represent measured data, and lines represent model fitting results. It should be noted that though the injection current in the testing experiments goes up to 3 or 4 mA, the actual bias of the device is usually limited in order to avoid the excess  $I \cdot V$  power consumption and severe degradation of  $\mathbb{Q}$  and ER. For comparison, the measured  $\Delta\lambda_r$ is also fitted using the empirical polynomial model ( $\Delta\lambda_r = -a \cdot I + b \cdot I^2$ ) in [61]. The fitting results demonstrate that the maximum fitting errors using our proposed model are only about 10% for Batch A and about 20% for Batch B of those using the polynomial model. Overall, our model provides a much better fitting accuracy than the polynomial model, since out model captures the nonlinear dependence of the EO effect on the injected current.

Our model can decompose  $\Delta \lambda_r$  to electro-optic (EO) effect and thermo-optic (TO)

Figure 2.6: (a) Measured resonance wavelength shift with fitting results using our proposed model and empirical polynomial model; (b) Decomposition of wavelength shift to eletro-optic and thermo-optic effect.

Figure 2.7: Resonance wavelength shift of modulators with model fitting: (a) Batch A with different diameters (D in  $\mu$ m) and guard distances (GD in  $\mu$ m); (b) Batch B with different slab heights (in nm) and GDs (in  $\mu$ m).

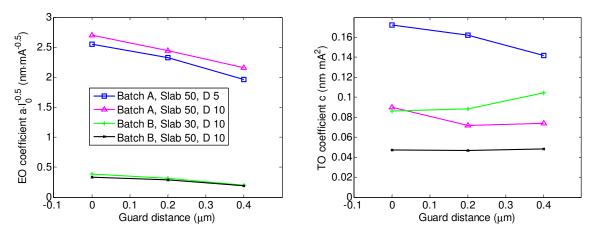

effect separately as shown in Fig. 2.6 (b). The EO and TO effect coefficients summarized in Fig. 2.8 have several implications on the device design parameters: (1) The modulators with a 5 µm diameter have a slightly smaller EO effect than that of 10 µm diameter in terms of the metric  $a/\sqrt{I_0}$ , while D5's TO effect (in terms of c) is about twice as that of D10. (2) For all devices, as the guard distance increases, the EO effect decreases while the TO effect fluctuates irregularly. (3) The devices with a 30 nm slab height have slightly greater EO effect and about two times TO effect than those of a 50 nm slab height. (4) By comparing the modulators with a 10 µm diameter and a 50 nm slab height from Batches A and B, one can see that Batch A's EO effect is much greater than that of Batch B, because the process error has been corrected in Batch A and the injection efficiency is greatly improved.

Figure 2.8: Fitting results of the resonance wavelength model for devices with different fabrications, diameters (D), and slab heights: (a) EO effect (metric:  $a/\sqrt{I_0}$ ); (b) TO effect (metric: c).

#### 2.4.2 Change of Extinction Ratio and Quality Factor

When carriers are injected into a microring modulator, ER and  $\mathbb{Q}$  change since the optical loss within the microring increases. The dependence of ER and  $\mathbb{Q}$  on the intra-

microring optical field loss coefficient  $\alpha$  can be derived from Yariv's transmission relation in [62]:

$$T(\lambda) = 1 - \frac{(1 - t^2)(1 - e^{-2\alpha l})}{(1 - te^{-\alpha l})^2 + (2t^{1/2}e^{-\alpha l/2}\sin(\pi n_{eff}l/\lambda))^2}$$

(2.13)

where t is the through-coupling coefficient that is related to the cross-coupling coefficient  $\kappa$  by  $t^2 + \kappa^2 = 1$ ; l is the microring circumference. The transmission spectrum around a resonance wavelength ( $\lambda_r = n_{eff}l/m$ ) can be approximated by:

$$T(\Delta \lambda) = 1 - \frac{A}{1 + (2\mathbb{Q} \cdot \Delta \lambda / \lambda_r)^2}$$

(2.14)

with

$$A = 1 - \left(\frac{t - e^{-\alpha l}}{1 - t e^{-\alpha l}}\right)^2, \quad \mathbb{Q} = m\pi \frac{t^{1/2} e^{-\alpha l/2}}{1 - t e^{-\alpha l}}$$

(2.15)