### **UC Santa Barbara**

### **UC Santa Barbara Electronic Theses and Dissertations**

### **Title**

Analysis and Design of Precision Timing Circuits using Pulse Mode Event Signaling

### **Permalink**

https://escholarship.org/uc/item/1nt961wz

### **Author**

Mukim, Prashansa

### **Publication Date**

2020

Peer reviewed|Thesis/dissertation

### University of California Santa Barbara

# Analysis and Design of Precision Timing Circuits using Pulse Mode Event Signaling

A dissertation submitted in partial satisfaction of the requirements for the degree

$\begin{array}{c} {\rm Doctor~of~Philosophy} \\ {\rm in} \\ {\rm Electrical~and~Computer~Engineering} \end{array}$

by

Prashansa Mukim

### Committee in charge:

Professor Forrest Brewer, Chair Professor James Buckwalter Professor Luke Theogarajan Professor Yuan Xie

| The Dissertation of Prashansa Mukim is approved. |

|--------------------------------------------------|

|                                                  |

| Professor James Buckwalter                       |

|                                                  |

| Professor Luke Theogarajan                       |

| Professor Yuan Xie                               |

| Professor Forrest Brewer, Committee Chair        |

December 2020

Analysis and Design of Precision Timing Circuits using Pulse Mode Event Signaling

Copyright © 2021

by

Prashansa Mukim

### Acknowledgements

First and foremost, I would like to express my deepest gratitude towards my advisor Professor Forrest Brewer for the innumerable ways in which he has supported me over the last five years. He decided to take me on as his student even when I was unsure about my goals and took the time to teach me everything ranging from the subtleties of designing chips to analysis strategies to writing better code to deconstructing large problems, and most importantly how to be creative in my thinking. Not only has Forrest been a wealth of knowledge, he has also been patient, supported me when I have struggled and given me ample opportunity to learn from my mistakes. Discussing crazy research ideas with Forrest was one of the most enjoyable parts of grad school, and I am extremely grateful for how generous he has been with his time.

I would also like to thank my committee members, all of whom I have been fortunate to work with and learn from during different stages of my PhD. Professor Luke Theogarajan, whose inspiring classes I have taken more than once and learnt how important it is to get the fundamentals right in order to succeed in any endeavor. I also am thankful for his encouragement, trust in me when I was his TA and his valuable feedback on my research. I could not have done without Professor Yuan Xie's support when I first started my PhD. I thank him for the opportunity to work on the CHIPS project and helping me identify important research directions. Working with the SEAL team taught me one of my first lessons on doing collaborative research and inspired me to have a strong work ethic. I also could not have completed my research without Professor Jim Buckwalter's support, who very generously provided me with access to his measurement lab and an opportunity to tapeout in 22nm. The time that he has taken to review my research and provide feedback has also been greatly valuable. I would also like to thank Professor Peng Li for all the stimulating discussions related to Spiking Neural Networks that have

helped me discover future research interests.

I am extremely thankful for the support of all my lab-mates during the course of my PhD. It was a pleasure to work with David, who was my lab neighbor and co-TA on several occasions and always inspired me with his thoroughness. I thank him for all his work on finishing chip tapeouts, help with resolving IT issues (that had a way of appearing at the most inopportune moments) and being a friend. I also would like to thank Aditya, Merritt, Carrie, Joseph, Di and Matt for guiding me when I first joined the lab and making HFH 2164 a fun place to be. I would like to express my gratitude towards Val, for all her guidance, helping make paperwork less daunting and giving the best advice. Thanks also to Avery, Bear and Paul for all their support and always being prompt with renewing key accesses.

Thanks to all my friends in Santa Barbara (Kruthika, Ravi, Akshar, Leah, Bharat, Bharath, Anna, Sadia) for their support and camaraderie over all these years and all the potlucks and game nights, Padma, Divya and Shubhra, who were my companions while taking classes when we spent all our time being at CSIL and my friends in India (Sameeksha, Richa, Meenal, Vasu, Shireen, Nidhi, Rajni) for always being there for me. I will be forever grateful to my parents Archana and Anil Mukim for all their love, for always encouraging me to make my own choices, being proud of the littlest of my achievements and for being my biggest pillars of strength. I also would like to thank my sister Priyanka for being my constant companion and my brother-in-law Ayush for all the good times while visiting India.

My sincere gratitude to Professor Ramesh Gaonkar who encouraged me to come to the US to pursue a PhD and has always looked out for me. Finally, I would like to thank the almighty for the events that led me to be at a place as beautiful as Santa Barbara, pursue my dreams, acquire knowledge, form personal connections with so many wonderful people and have the opportunities to make a difference.

### Curriculum Vitæ Prashansa Mukim

#### Education

| 2020 | Ph.D. in Electrical and Computer Engineering, University of Cali-                              |

|------|------------------------------------------------------------------------------------------------|

|      | fornia, Santa Barbara.                                                                         |

| 2017 | M.S. in Electrical and Computer Engineering, University of California, Santa Barbara.          |

| 2013 | B.E. in Electronics and Communication, Netaji Subhas Institute of Technology, New Delhi, India |

#### **Publications**

- P. Mukim and F. Brewer, "Multi-Wire Phase Encoding: A Signaling Strategy for High Bandwidth, Low Power Data Movement", IEEE Transactions on Very Large Scale Integration (VLSI) Systems (under review)

- P. Mukim, A. Dalakoti, D. McCarthy, C. Segal, M. Miller, J. F. Buckwalter and F. Brewer, "Design and Analysis of Collective Pulse Oscillatots", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2020

- P. Mukim, A. Dalakoti, D. McCarthy, B. Pon, C. Segal, M. Miller, J. F. Buckwalter and F. Brewer, "Distributed Pulse Rotary Traveling Wave VCO: Architecture and Design", IEEE Computer Society Annual Symposium on VLSI (ISVLSI), 2019

- M. Miller, A. Dalakoti, **P. Mukim** and F. Brewer, "Low Phase Noise Pulse Rotary Wave Voltage Controlled Oscillator", International SoC Design Conference (ISOCC), 2017

- M. Miller, C. Segal, D. McCarthy, A. Dalakoti, P. Mukim and F. Brewer, "Impolite High Speed Interfaces with Asynchronous Pulse Logic", Great-Lakes Symposium on VLSI (GLSVLSI), 2018

- P. Gu, D. Stow, **P. Mukim**, S. Li and Y. Xie, "Cost-efficient 3D Integration to Hinder Reverse Engineering During and After Manufacturing", Asian Hardware Oriented Security and Trust Symposium (AsianHOST), 2018

- J. Mekie, **P. Mukim** and K. Kale, "Impact of Process Variations on Synchronizer Performance: An Experimental Study", IEEE International Conference on VLSI Design and Embedded Systems (VLSID), 2018

# List of Figures

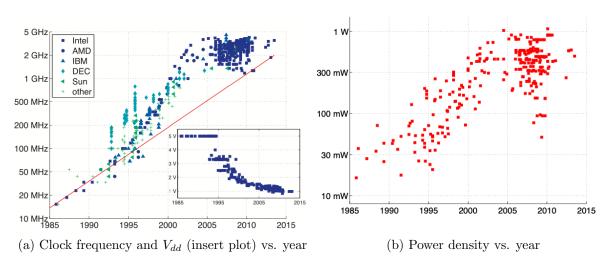

| 1.1 | Processor clock frequency and power density trends over the last 30 years [1]   |

|-----|---------------------------------------------------------------------------------|

|     | (a) Clock frequency and $V_{dd}$ (insert plot) vs. year                         |

|     | (b) Power density vs. year                                                      |

| 1.2 | Evolution of integration techniques                                             |

|     | (a) Multi-chip module. Source: [2]                                              |

|     | (b) Silicon-in-package. Source: [3]                                             |

|     | (c) AMD Radeon $^{TM}$ Fury graphics card with the "Fiji" GPU and High          |

|     | Bandwidth Memory. Source: [4]                                                   |

|     | (d) Xilinx Virtex-7 H580T 3D FPGA based on stacked silicon intercon-            |

|     | nect. Source: [5]                                                               |

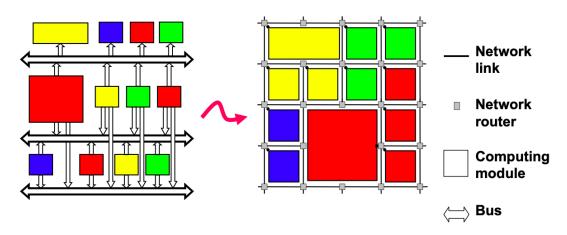

| 1.3 | Comparison of bused-based and NoC based communication. Source: [6] . 4          |

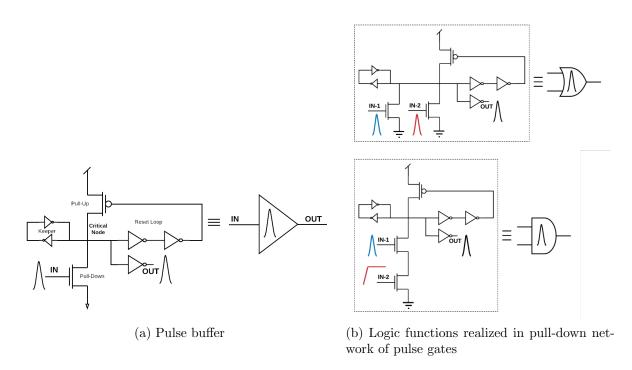

| 2.1 | Pulse gate circuits                                                             |

|     | (a) Pulse buffer                                                                |

|     | (b) Logic functions realized in pull-down network of pulse gates 12             |

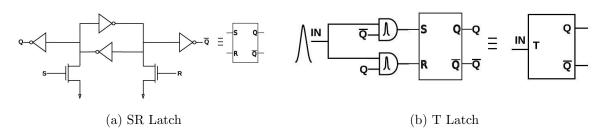

| 2.2 | Pulse latches                                                                   |

|     | (a) SR Latch                                                                    |

|     | (b) T Latch                                                                     |

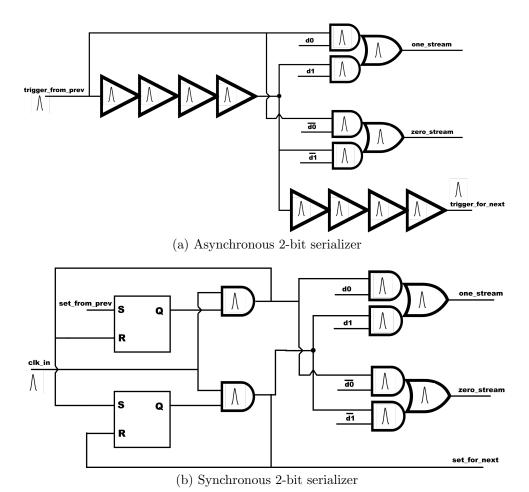

| 2.3 | 2-bit serializer implementations                                                |

|     | (a) Asynchronous 2-bit serializer                                               |

|     | (b) Synchronous 2-bit serializer                                                |

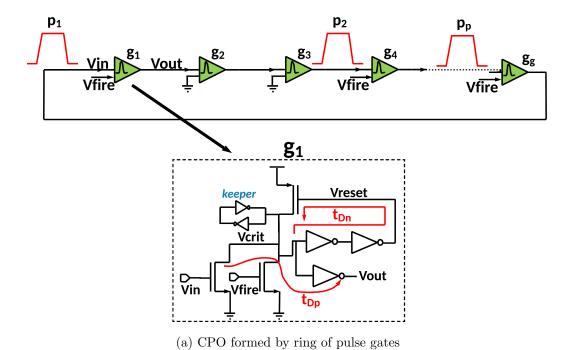

| 2.4 | CPO: Construction and Timing                                                    |

|     | (a) CPO formed by ring of pulse gates                                           |

|     | (b) Voltage at pulse gate nodes during pulse generation                         |

| 2.5 | Delay-separation dynamics                                                       |

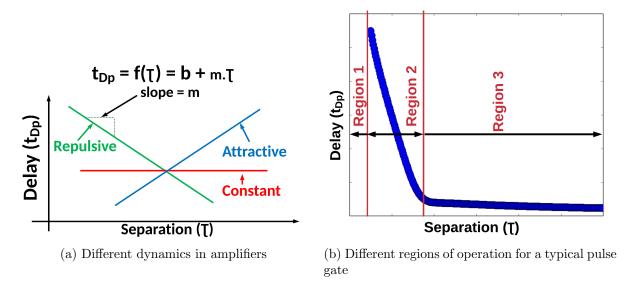

|     | (a) Different dynamics in amplifiers                                            |

|     | (b) Different regions of operation for a typical pulse gate                     |

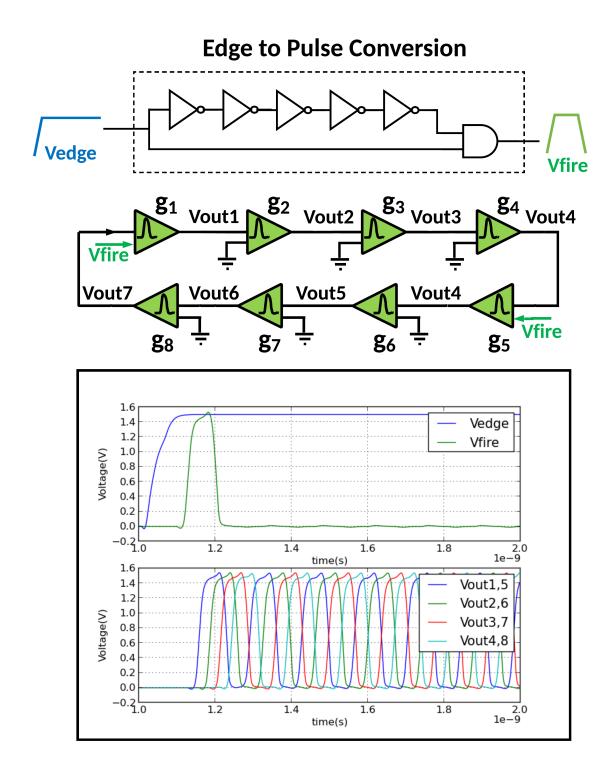

| 2.6 | Start-up circuit and waveforms for $g = 8, p = 2$ CPO                           |

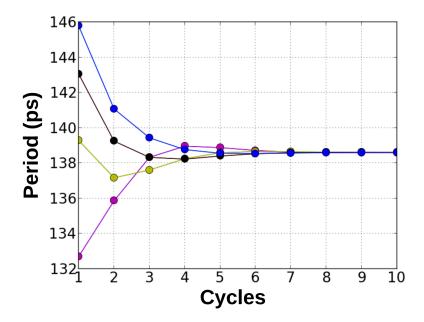

| 2.7 | Period of pulse arrival at different gates of $g = 8, p = 2$ CPO after start-up |

|     | settles to a constant value in less than 10 cycles                              |

| 3.1<br>3.2<br>3.3 | 1-pulse travelling in a 1-pulse-gate loop                                                                                                                                              |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.4               | Normalized phase error obtained from analytical solutions                                                                                                                              |

|                   | (b) Weakly repulsive dynamics                                                                                                                                                          |

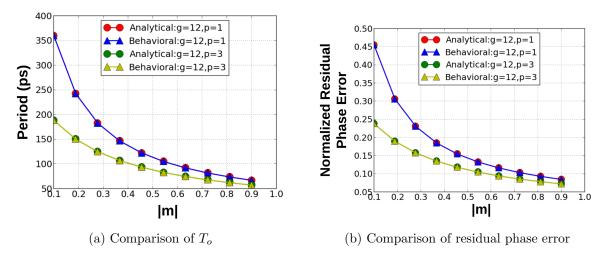

| 4.1               | Comparison of values obtained from the general analytic solution and be-                                                                                                               |

|                   | havioral simulations                                                                                                                                                                   |

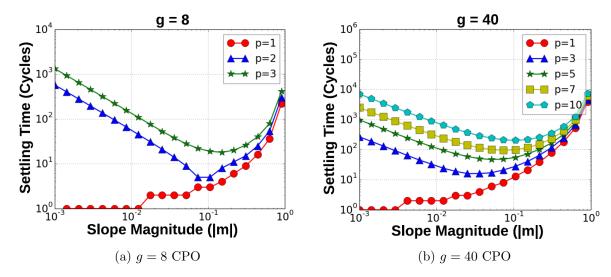

| 4.2               | Effect of $m$ on settling time with impulse-noise injection obtained from                                                                                                              |

|                   | behavioral simulator                                                                                                                                                                   |

|                   | (a) $g = 8 \text{ CPO}$                                                                                                                                                                |

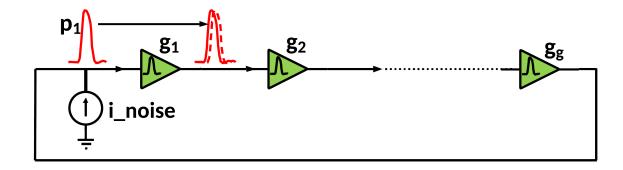

| 4.3               | Impulse noise simulation setup in Hspice                                                                                                                                               |

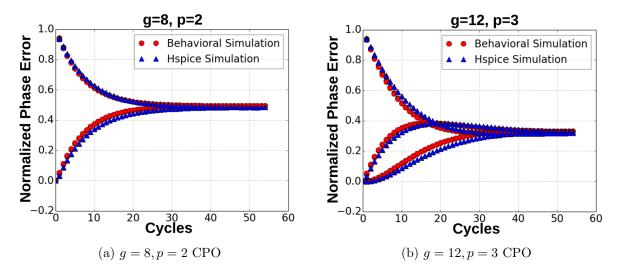

| 4.4               | Comparison of normalized residual (impulse) phase error obtained from behavioral and Hspice simulations                                                                                |

|                   | (a) $g = 8, p = 2$ CPO                                                                                                                                                                 |

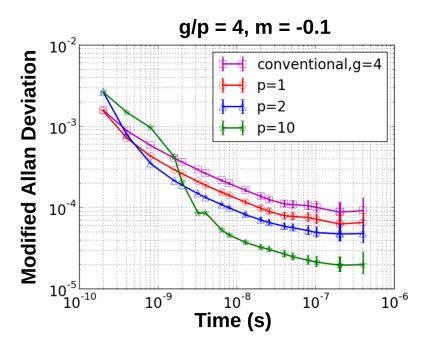

| 4.5               | Improvement in frequency stability of CPOs as a function of $p$ for fixed                                                                                                              |

|                   | g/p and $m$ obtained from behavioral simulations                                                                                                                                       |

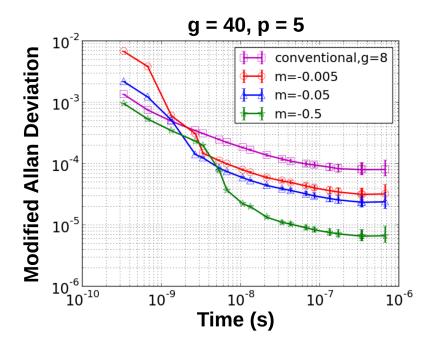

| 4.6               | Improvement in frequency stability of CPOs as a function of $m$ for fixed                                                                                                              |

|                   | $g, p \text{ and } T_o \text{ obtained from behavioral simulations} \dots \dots$ |

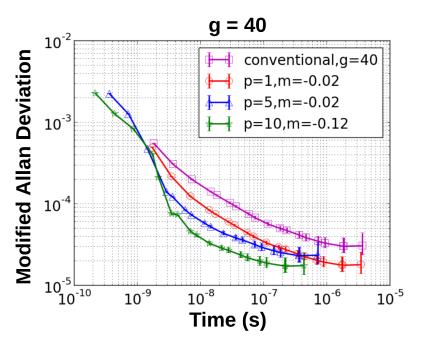

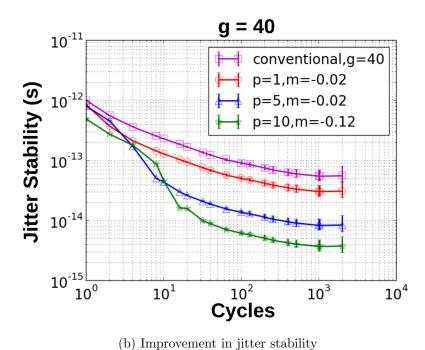

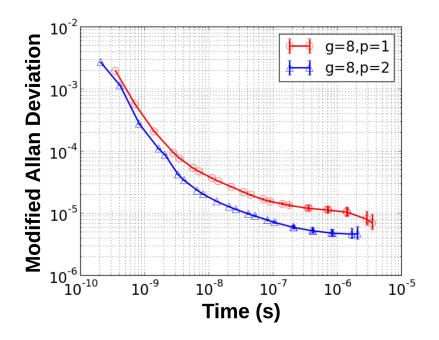

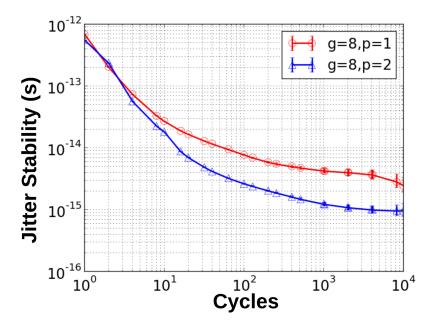

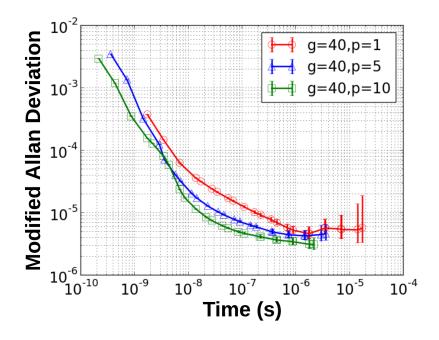

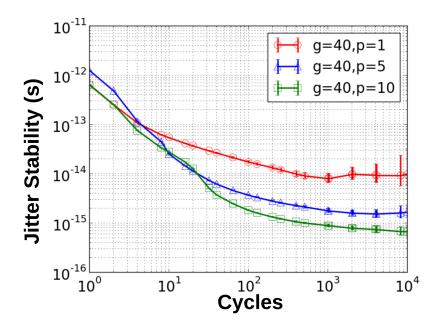

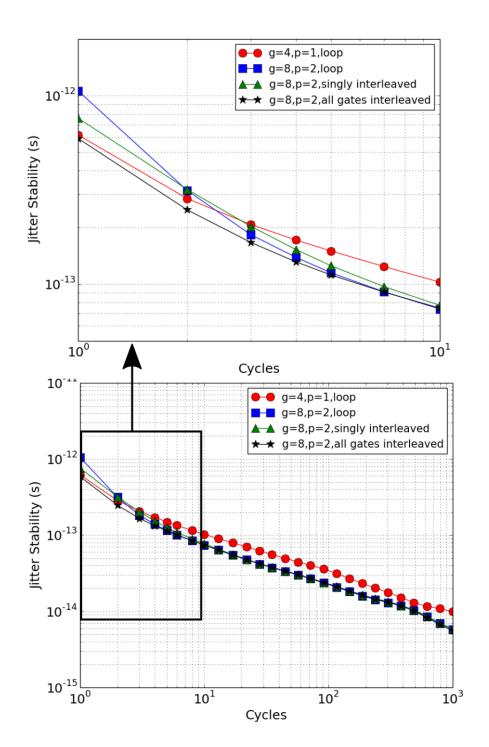

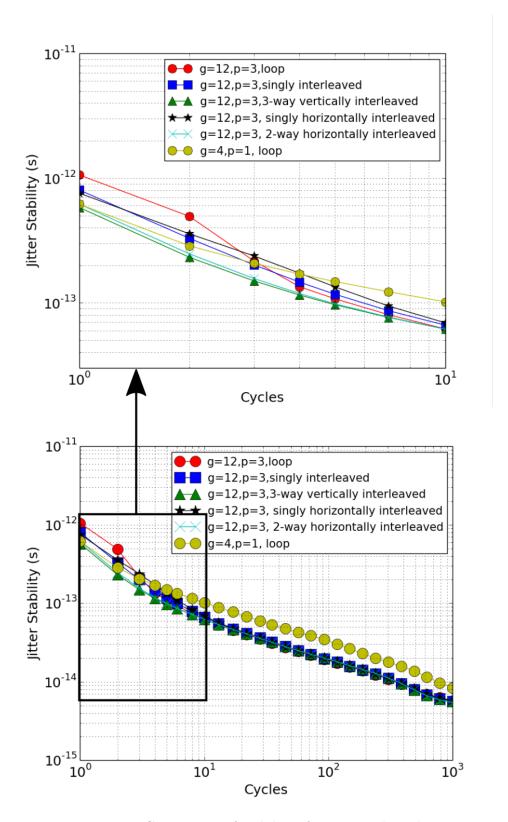

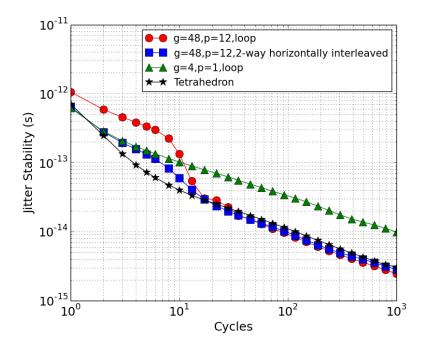

| 4.7               | Improvement in stability of CPOs as a function of $p$ for fixed $g$ obtained                                                                                                           |

|                   | from behavioral simulations                                                                                                                                                            |

|                   | (b) Improvement in jitter stability                                                                                                                                                    |

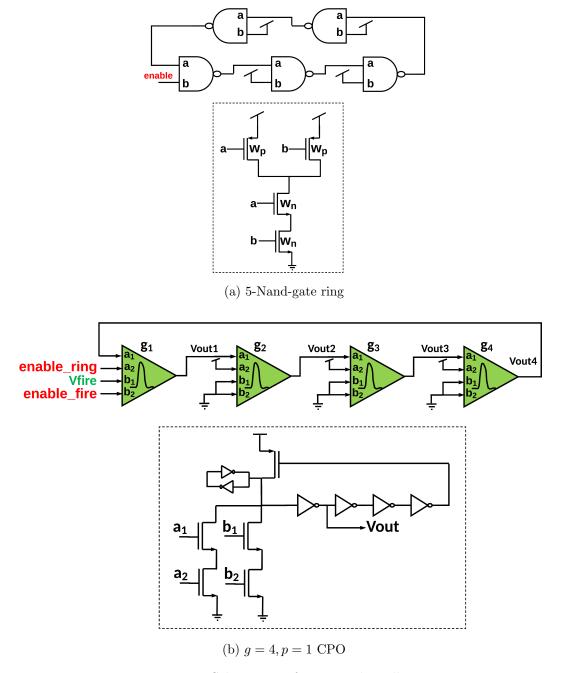

| 4.8               | Schematics of compared oscillators                                                                                                                                                     |

|                   | (a) 5-Nand-gate ring                                                                                                                                                                   |

|                   | (b) $g = 4, p = 1 \text{ CPO} \dots 4$                                                                                                                                                 |

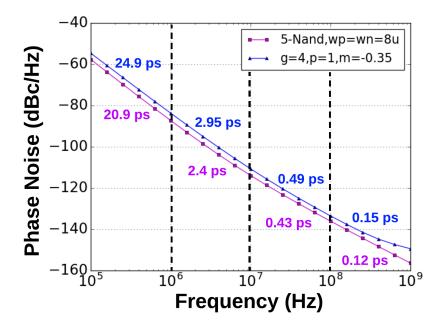

| 4.9               | Simulated phase noise and RMS phase jitter obtained by integrating phase                                                                                                               |

|                   | noise                                                                                                                                                                                  |

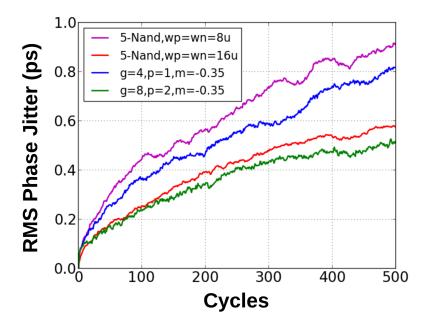

|                   | RMS phase jitter obtained from transient noise simulations                                                                                                                             |

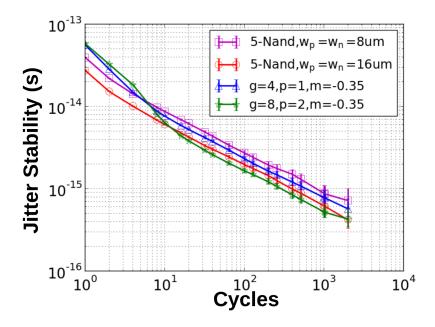

|                   | Jitter stability obtained from transient noise simulations                                                                                                                             |

| 4.12              | Simulated normalized phase error of CPOs and ring oscillators with im-                                                                                                                 |

| 1 10              | pulse noise injection                                                                                                                                                                  |

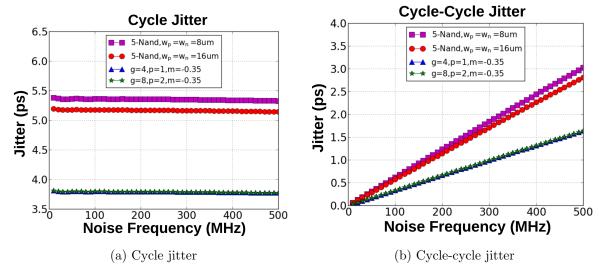

| 4.13              | Comparison of CPOs and ring oscillators with power-coupled noise 5                                                                                                                     |

|                   | (a) Cycle jitter                                                                                                                                                                       |

| 111               | (b) Cycle-cycle jitter                                                                                                                                                                 |

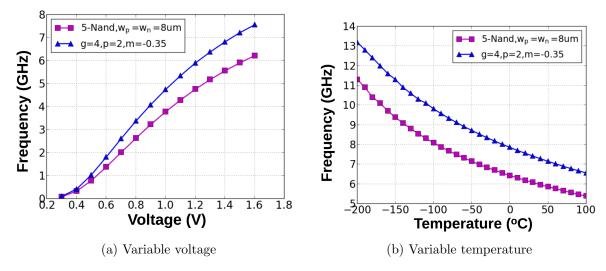

| 4.14              | Trequency for 3-Namu-gate ring oscillator and $q = 4, p = 1$ of $Q = 1, \dots, Q$                                                                                                      |

|      |                                                                           | 51<br>51 |

|------|---------------------------------------------------------------------------|----------|

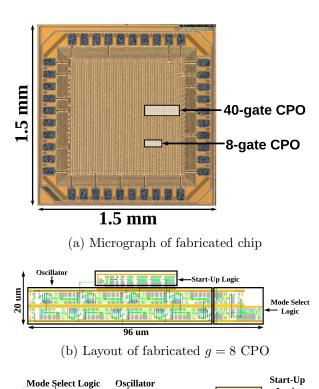

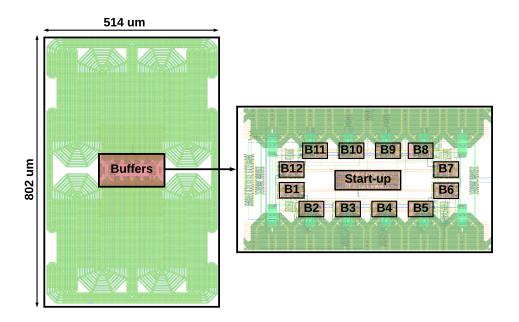

| 5.1  | Chip in GFUS8RF (130 nm)                                                  | 53       |

|      |                                                                           | 53       |

|      |                                                                           | 53       |

|      |                                                                           | 53       |

| 5.2  |                                                                           | 54       |

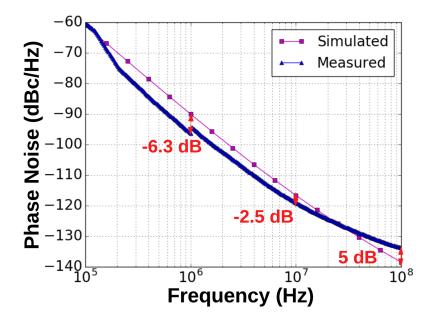

| 5.3  |                                                                           | 56       |

| 5.4  |                                                                           | 56       |

| 5.5  |                                                                           | 57       |

| 5.6  |                                                                           | 58       |

| 5.7  |                                                                           | 58       |

| 5.8  |                                                                           | 59       |

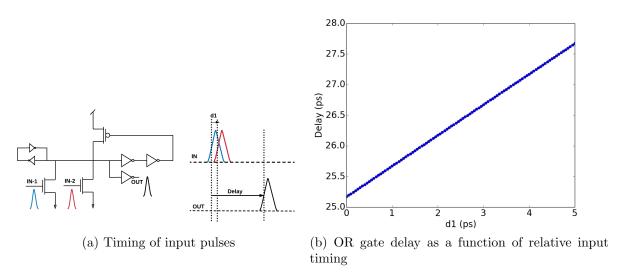

| 6.1  | Pulse OR timing                                                           | 63       |

|      |                                                                           | 63       |

|      |                                                                           | 63       |

| 6.2  |                                                                           | 63       |

| 6.3  | ~                                                                         | 65       |

| 6.4  |                                                                           | 66       |

| 6.5  |                                                                           | 66       |

| 6.6  |                                                                           | 68       |

| 6.7  |                                                                           | 69       |

| 6.8  |                                                                           | 69       |

| 6.9  |                                                                           | 70       |

| 6.10 |                                                                           | 71       |

|      | 9 - 9                                                                     | 71       |

|      |                                                                           | 71       |

| 6.11 |                                                                           | 72       |

|      |                                                                           | 75       |

|      | •                                                                         | 75       |

|      |                                                                           | 75       |

| 6.13 |                                                                           | 75       |

|      |                                                                           | 77       |

|      |                                                                           | <br>77   |

|      | -                                                                         | <br>77   |

| 6.15 | Pulse amplifier with added resistive feedback, fire input and fine tuning | •        |

| 5.10 |                                                                           | 78       |

| 6.16 | •                                                                         | 78       |

| 5.10 |                                                                           | 78       |

|      |                                                                           | 78       |

| 6 17 |                                                                           | 70<br>80 |

|      | (a) Start-up circuit                                                         | 80  |

|------|------------------------------------------------------------------------------|-----|

|      | (b) Transients at start-up                                                   | 80  |

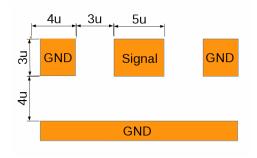

|      | Transmission line structure                                                  | 81  |

| 6.19 | Oscillator layout: transmission line loop and buffers                        | 81  |

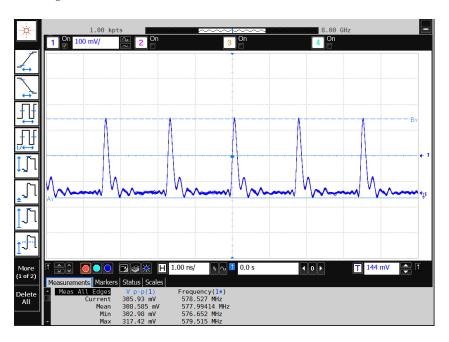

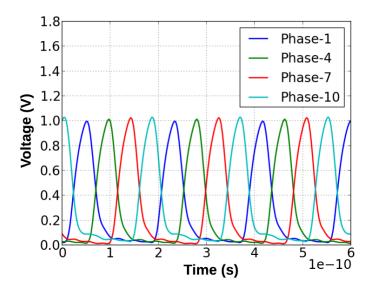

| 6.20 | Waveform showing 4 of 12 clock phases, duty cycle = $27\%$                   | 83  |

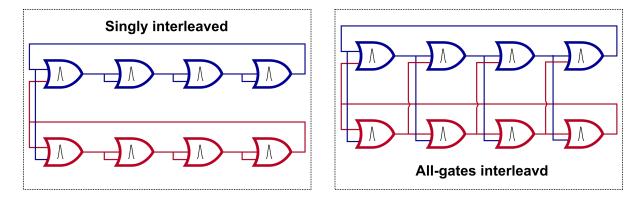

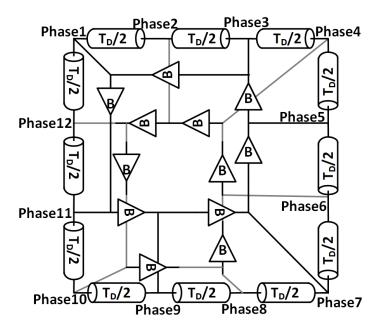

| 6.21 | Interleaved 12 phase pulse RTWO                                              | 83  |

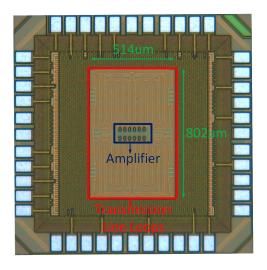

| 6.22 | Die micrograph                                                               | 85  |

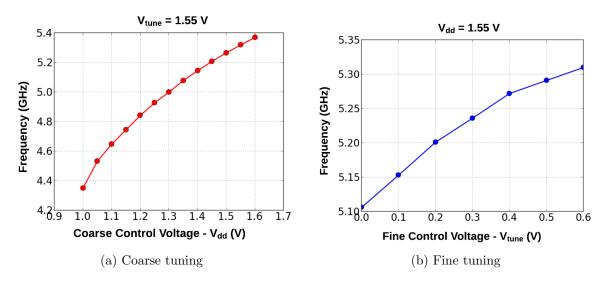

| 6.23 | Measured voltage controlled frequency                                        | 85  |

|      | (a) Coarse tuning                                                            | 85  |

|      | (b) Fine tuning                                                              | 85  |

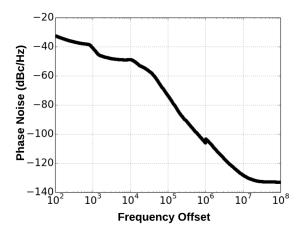

| 6.24 | Phase noise measurements                                                     | 86  |

|      | (a) Measured Phase Noise at $V_{dd} = 1.55V$ , $V_{tune} = 1.55V$            | 86  |

|      | (b) Phase Noise as a function of operating frequency                         | 86  |

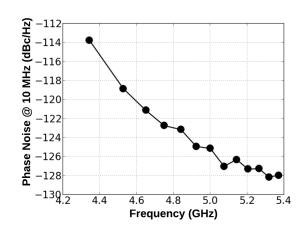

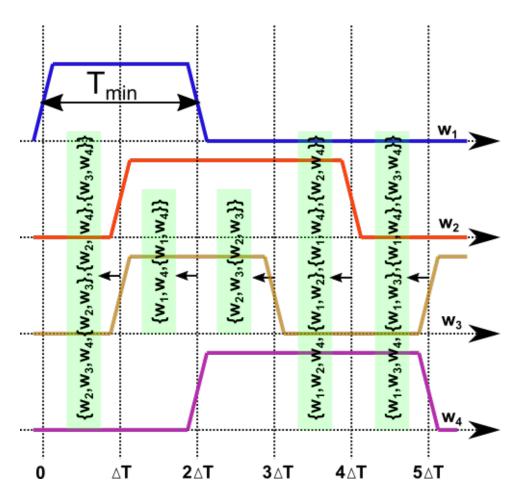

| 7.1  | Transitions on an $n = 4, k = 2$ S-MWPE link                                 | 91  |

| 7.2  | Transitions on an $n = 4, k = 2$ M-MWPE link                                 | 92  |

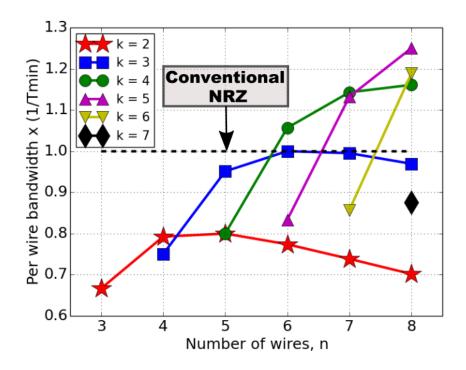

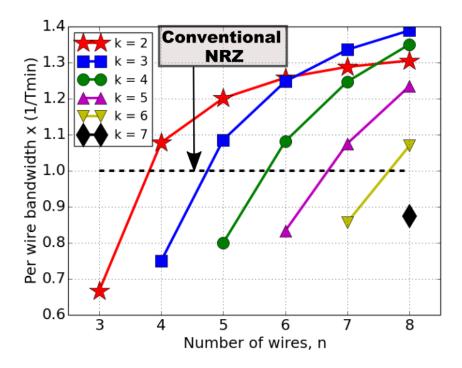

| 7.3  | Bandwidth comparisons of S-MWPE with conventional NRZ links                  | 99  |

| 7.4  | Bandwidth comparisons of M-MWPE with conventional NRZ links                  | 99  |

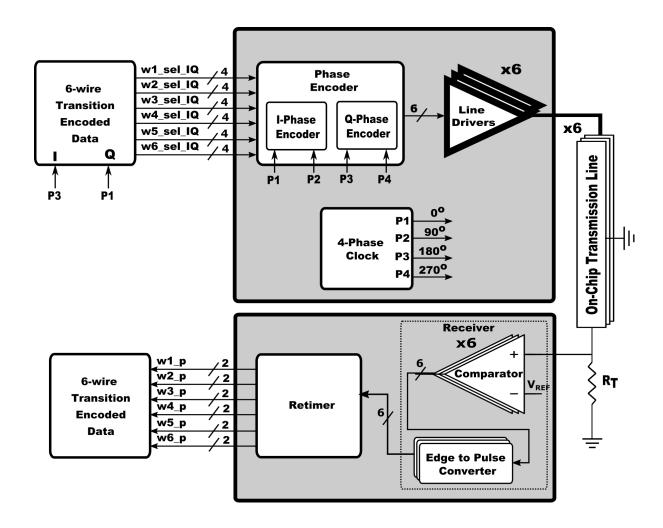

| 7.5  | 6-wire MWPE Link Architecture                                                | 101 |

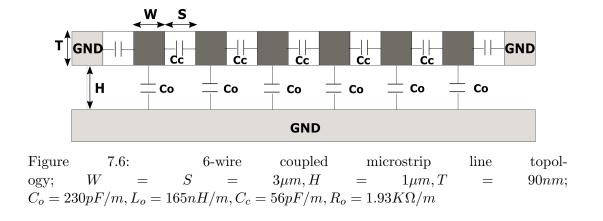

| 7.6  | 6-wire coupled microstrip line topology; $W = S = 3\mu m, H = 1\mu m, T =$   |     |

|      | $90nm; C_o = 230pF/m, L_o = 165nH/m, C_c = 56pF/m, R_o = 1.93K\Omega/m$ .    | 101 |

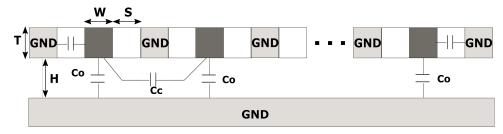

| 7.7  | 6-wire shieldied coplanar waveguide line topology; $W = S = 3\mu m, H =$     |     |

|      | $1\mu m, T = 90nm; C_o = 230pF/m, L_o = 160nH/m, C_c = 8.5pF/m, R_o =$       |     |

|      | $1.93K\Omega/m$                                                              | 102 |

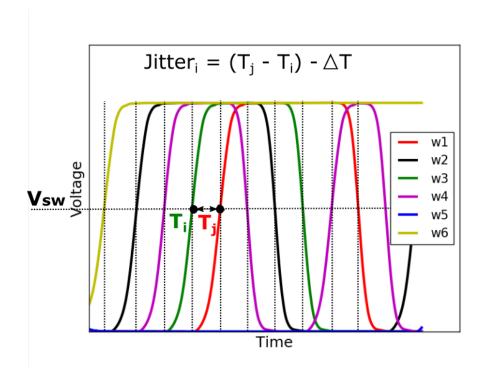

| 7.8  | Jitter for a Phase Encoded link computed from timing of relative transitions | 102 |

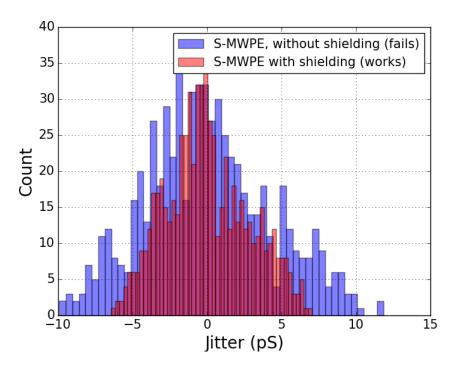

| 7.9  | Jitter for $n = 6, k = 2, T_{min} = 60$ ps S-MWPE links of length $4mm$      | 103 |

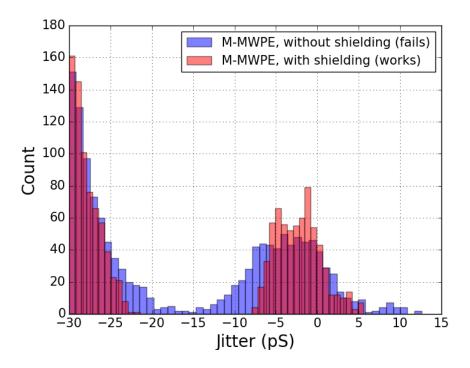

| 7.10 | Jitter for $n = 6, k = 2, T_{min} = 60$ ps M-MWPE links of length $4mm$      | 104 |

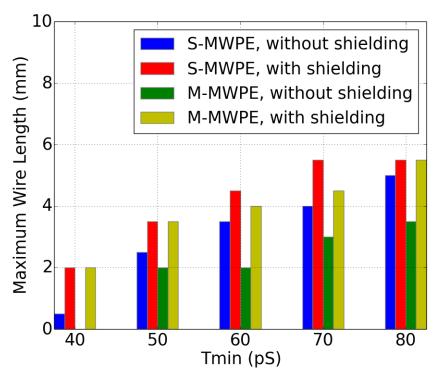

| 7.11 | Maximum link length for which $n = 6, k = 2$ MWPEs are successful for        |     |

|      | the given channel for different $T_{min}$                                    | 105 |

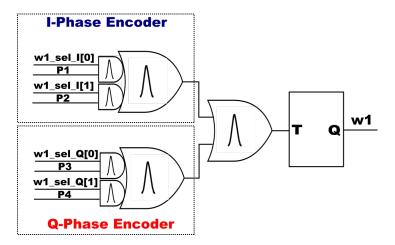

|      | Phase Encoder Circuit                                                        | 107 |

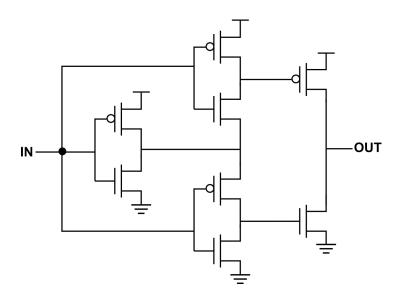

| 7.13 | Driver Circuit                                                               | 107 |

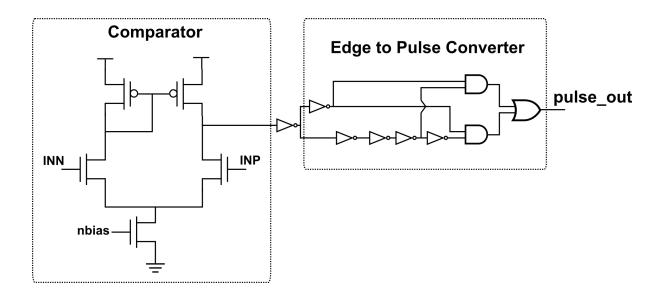

| 7.14 | Receiver Circuit                                                             | 108 |

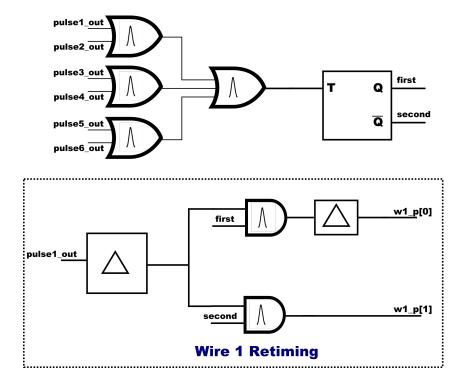

| 7.15 | Retimer Circuit                                                              | 108 |

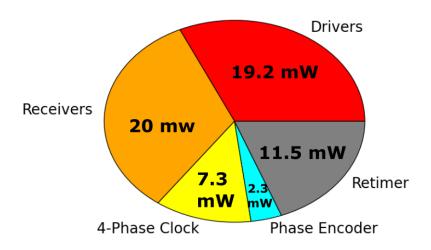

| 7.16 | Power Breakdown                                                              | 110 |

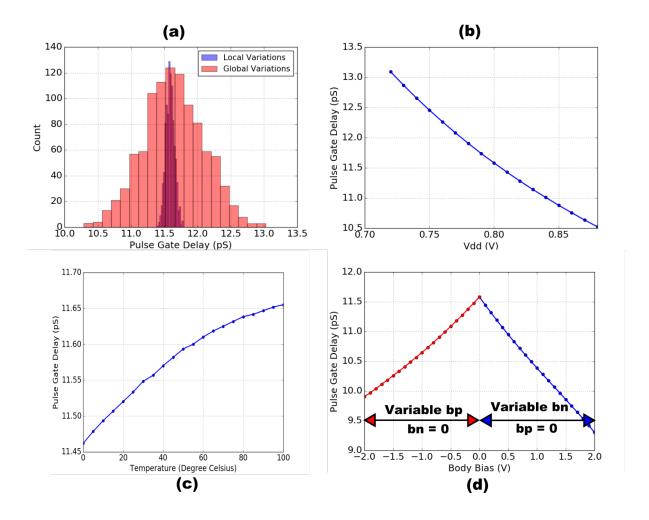

| 7.17 | Pulse Gate delay variance due to (a) Process variations, (b) Voltage vari-   |     |

|      | ations, (c) Temperature variations, (d) Body bias tuning                     | 111 |

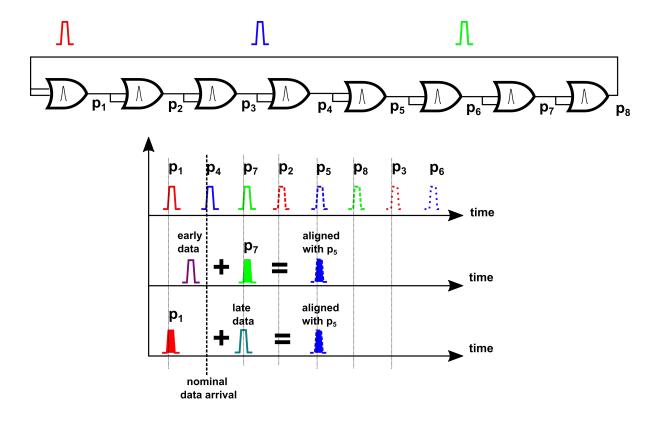

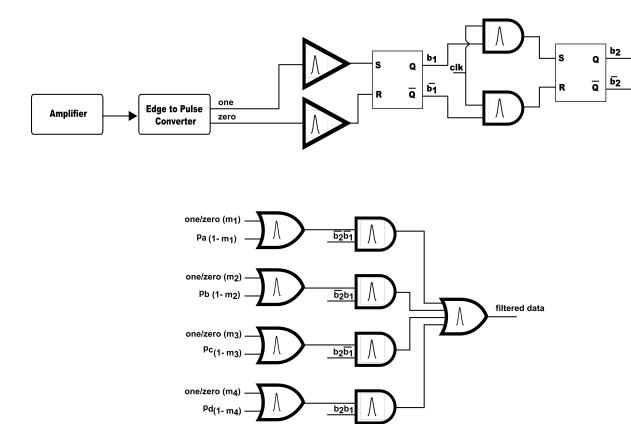

| 8.1  | g=8, p=3 CPO with 8 phases used for filtering                                | 114 |

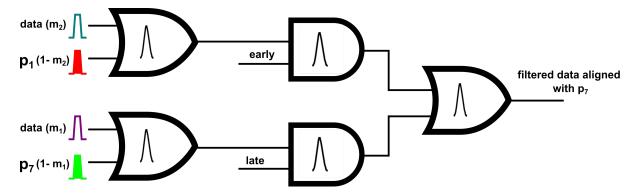

| 8.2  | Filtering circuit implemented using pulse gates                              | 115 |

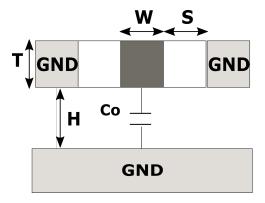

| 8.3  | Shieldied coplanar waveguide with $W = S = 3\mu m, H = 1\mu m, T = 90nm;$    |     |

|      | $C_o = 230pF/m, L_o = 160nH/m, R_o = 1.93K\Omega/m$                          | 116 |

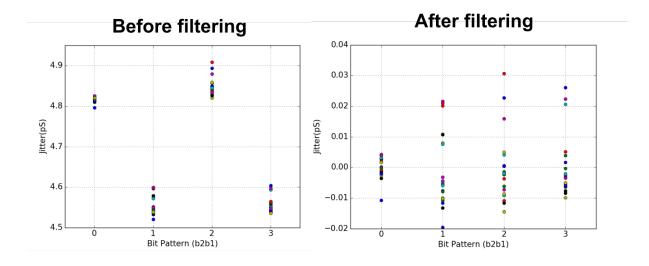

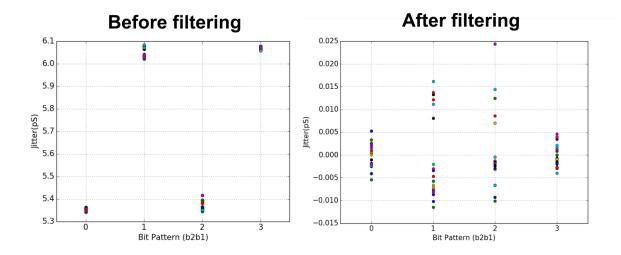

| 8.4  | Rising edge jitter reduction after 2-tap filtering                           | 116 |

| 8.5  | Falling edge jitter reduction after 2-tap filtering                          | 117 |

| 8.6 | 2-tap filtering circuit                            | 118 |

|-----|----------------------------------------------------|-----|

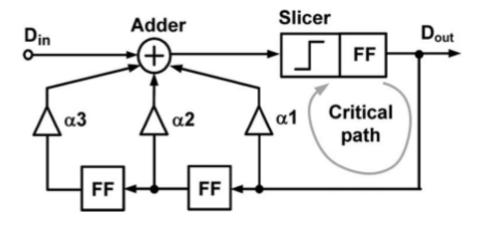

| 8.7 | Conventional multi-tap Decision Feedback Equalizer | 118 |

# List of Tables

| 4.1 | Performance Comparison of CPOs and Ring Oscillators (obtained from Hspice simulations)                                              | 49 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.1 | Performance Comparison of fabricated g=8, p=2 CPO with similar previous works                                                       | 55 |

| 6.1 | Simulation results for a fully parasitic extracted design at $V_{dd} = V_{tune} = 1.5 \text{V} \dots \dots \dots \dots \dots \dots$ | 82 |

| 6.2 | Comparison of measured pulse RTWO with other free running RTWOs $$ .                                                                | 86 |

| 7 1 | n-wire Bandwidth Comparisons                                                                                                        | 97 |

#### Abstract

Analysis and Design of Precision Timing Circuits using Pulse Mode Event Signaling

by

#### Prashansa Mukim

This thesis presents an analytical framework and circuit solutions to a host of timing problems that are applicable to systems of varying scales. These non-standard solutions provide higher performance alternatives to the issues of multi-phase clock distribution and larger-scale on-chip or on-interposer communication and coherence. The underlying circuits for all these solutions are pulse mode asynchronous and built using a logic family of gates that encode both data and the time of arrival as atomic pulses. These gates incorporate local negative feedback loops leading to useful dynamic behavior that is exploited in the design of low-noise closed loop timing circuits.

First, Collective Pulse Oscillators (or CPOs), the simplest closed loop pulse gate circuits are presented. CPOs achieve FoMs better than conventional ring oscillators, while also providing precise clock phases much finer than the delay of a typical gate in a given technology. The noise analysis of CPOs is based on a time-domain analytical model, which is expanded into a rapid behavioral simulator, and validated against measurement results for different diameter CPOs implemented in 130 nm technology. Next, complex CPO topologies that improve the high-frequency stability of loop-connected CPOs are presented and the potential of such structures in implementing timing distribution networks that utilize distributed feedback to enhance the accuracy of the timing source itself is evaluated. Architecture, design and measurement results for a 5.5 GHz low-jitter transmission-line stabilized pulsed wave oscillator implemented in 130 nm are also presented.

Second, Multi-Wire Phase Encoding (MWPE), a transition signaling strategy suitable for on-chip/on-interposer links connecting globally asynchronous modules is presented. These links are aimed at reducing the energy cost of moving data across a large scale SoC or NoC, which is known to be orders of magnitude higher than the cost of computation. MWPE, by encoding data in the time correlated switching of multiple signaling wires allows very high-bandwidth data transmission on band-limited and lossy on-chip wires, with PLL/DLL free data recovery. Theoretical and practical bandwidth limits for MWPE are derived and link performance in 22 nm FDX technology is evaluated. Finally, methods of implementing low cost time-domain linear filters that utilize precise clock phases to reduce timing noise originating from systematic noise sources are presented.

# Contents

| Cı | ırric                           | ulum Vitae                                                                                                                                                    | V                         |

|----|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| Li | st of                           | Figures                                                                                                                                                       | vi                        |

| Li | st of                           | Tables                                                                                                                                                        | xi                        |

| Αl | ostra                           | act                                                                                                                                                           | xii                       |

| 1  | Intr<br>1.1<br>1.2<br>1.3       | Background and Motivations                                                                                                                                    | 1<br>1<br>9<br>10         |

| 2  | Pul<br>2.1<br>2.2               | se Logic and Collective Pulse Oscillators Introduction to Pulse Logic                                                                                         | 11<br>11<br>14            |

| 3  | Ana 3.1 3.2                     | Alytical Noise Modeling for CPOs  Exact Solutions for Pulse Arrival Time Under Impulse Noise Perturbation Generalization of the solution to g-gates, p-pulses | 22<br>22<br>29            |

| 4  | Beh<br>CP0<br>4.1<br>4.2<br>4.3 | Time Domain Measurement of Stability Using Allan Deviation Behavioral System Simulator                                                                        | d<br>31<br>32<br>33<br>43 |

| 5  | 5.1                             | Assurement Results for Simple Loop Connected CPOs  Measurements on Chip Fabricated in 130nm                                                                   | <b>52</b><br>52           |

| 6                         | Complex CPO Topologies and Transmission Line Stabilized CPOs           |     | 61  |

|---------------------------|------------------------------------------------------------------------|-----|-----|

|                           | 6.1 Interconnected CPO Topologies                                      |     | 62  |

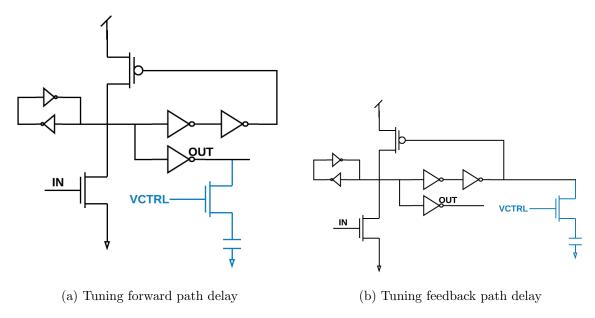

|                           | 6.2 Voltage Controlled and Injection Locked CPOs                       |     | 70  |

|                           | 6.3 Transmission Line Stabilized CPOs                                  |     | 71  |

|                           | 6.4 Conclusions                                                        |     | 87  |

| 7                         | Multi-Wire Phase Encoding (MWPE)                                       |     | 88  |

|                           | 7.1 Introduction                                                       |     | 88  |

|                           | 7.2 Multi-Wire Phase Encoding: Protocol and Theoretical Bandwidth Limi | its | 90  |

|                           | 7.3 Link Architecture and Performance on Practical Channels            |     | 98  |

|                           | 7.4 Link Implementation                                                |     | 106 |

|                           | 7.5 Conclusions                                                        |     | 112 |

| 8                         | Pulse-based Time Domain Linear Filtering                               |     | 113 |

|                           | 8.1 Introduction                                                       |     | 113 |

|                           | 8.2 Inter-symbol interference induced timing jitter reduction          |     | 115 |

| 9                         | Conclusions and Future Work                                            |     | 120 |

| $\mathbf{B}^{\mathbf{i}}$ | ibliography                                                            |     | 124 |

# Chapter 1

## Introduction

### 1.1 Background and Motivations

Timing is an integral part of most VLSI design applications such as clocking [7, 8, 9], analog-to-digital and digital-to-analog conversion [10, 11], RF communication [12, 13], clock and data recovery [14], time-based metrology [15, 16] and neuromorphic computing [17, 18]. The performance, precision and silicon footprint of timing circuits driving these systems, as well as the energy cost associated with distributing timing and maintaining a notion of global coherence play a crucial role in quantifying the success of these designs. Thus, analysis and design of timing circuits optimized for varying system-level goals has been an active area of research for the last several decades.

With the exponential trend of shrinking transistor feature sizes in the last 50 years, and the consequences of scaling on the performance and power limits of integrated circuits, the architecture of large scale ICs and processors, in particular, has undergone a paradigm shift. As shown in Fig. 1.1, even though the speed of transistors has continued to increase, the clock frequency and power density of processor chips stalled around the mid 2000s. It is believed that the exponential power growth until the mid 2000s was

mainly due to the fact that supply voltages were not scaled at the constant field rate [19], and that clock frequencies were scaled faster than the constant field scaling in the quest for performance [1]. As power is  $CV_{dd}^2f$ , and capacitance (C) scales with technology, the solution to bound the power density and associated thermal issues has been to limit the clock frequency f of uni-processors. The supply voltage  $V_{dd}$  has not been lowered below 0.8 - 1V, as a lower  $V_{dd}$  demands lower transistor thresholds, which increases the leakage currents. Instead, multi-processor chips have emerged as a solution where each individual processor operates at a lower frequency, can be selectively enabled or disabled, and the multi-processor system achieves an overall higher performance measured by its throughput.

Figure 1.1: Processor clock frequency and power density trends over the last 30 years [1]

With the advent of large scale multi-processor chips as well as Systems-on-Chip (SoCs) that allow heterogeneous integration of various functionalities, the problem of global interconnect delays has become increasingly important. The average length of the longest global interconnect in a chip of area A is approximated to be  $\sqrt{A}/2$ , and the delay of global interconnects to be  $\propto A/\lambda^2$ , where  $\lambda$  is the feature size [20]. Thus, as feature sizes

shrink and chip areas grow, there is an explosion in the delay of global interconnects. The problem of global interconnect delays not scaling, increased manufacturing variances and yield degradation of large chips led to the concept of integrating several smaller die on a common substrate. The underlying substrate and integration technology used for multidie integration has also evolved drastically over the last 30 years. What started with Multi-Chip Modules (MCMs) (Fig. 1.2a)in the 1990s, led to System-in-Package (SiP) (Fig. 1.2b) modules in the 2000s and 2.5D (Fig. 1.2c) and 3D (Fig. 1.2d) integrated circuits in the present day. These integration techniques have become increasingly efficient in terms of the connection pitch, bandwidth limits and latency. Current 2.5D integrated circuits use fine-pitched silicon interposers as the substrate, and bond each die using fine pitched microbumps with pitches ranging between  $20\mu m - 50\mu m$  [21].

Network-on-Chip (NoC) architectures have emerged as a promising interconnection fabric for such integration techniques [22], as opposed to bus based communication. While early research on NoCs goes back to the 2000s [23, 24, 25], their applicability has become even more relevant with the advent of advanced integration techniques. As shown in Fig.1.3, NoC architectures include point-to-point links between router modules, making the interconnection network scalable. Router modules communicate with their neighboring compute modules and essentially decouple the task of designing communication and computation circuits. A natural question that arises is the mechanism of timing coherence of the modules and the most efficient intra-module and inter-module communication strategies. Fully synchronous communication schemes are generally ruled-out as distribution of global low-jitter clock signals across large areas in not only expensive in terms of power, but manufacturing variances and dynamic changes in the operating environment of the circuits limit the maximum performance of such a scheme. Globally Asynchronous Locally Synchronous (GALS) schemes have shown promise [26, 27], where small digital blocks operate synchronously, but the operation of different blocks is not mutually

(a) Multi-chip module. Source: [2]

(b) Silicon-in-package. Source: [3]

(c) AMD Radeon  $^{TM}$  Fury graphics card with the "Fiji" GPU and High Bandwidth Memory. Source: [4]

(d) Xilinx Virtex-7 H580T 3D FPGA based on stacked silicon interconnect. Source: [5]

Figure 1.2: Evolution of integration techniques

Figure 1.3: Comparison of bused-based and NoC based communication. Source: [6]

synchronized [28]. Often, an asynchronous wrapper acts as an interface between the synchronous and asynchronous environments, two common solutions being using FIFO buffers and pausible clock generators [29]. Thus, small-scale local synchronous modules with controlled variances are able to a achieve a high performance at relatively low power. The global communication incurs a small overhead due to these asynchronous wrappers, but the performance of local blocks is no longer bound by the tolerances necessary to ensure correct functionality given global static and dynamic variations. In fact, all the examples of systems involving timing circuits presented so far need customized solutions based on the physical scale of the problem being solved and the target specifications of the system.

The work presented in this thesis strives to provide an analytical framework and specialized circuit solutions to timing problems that are applicable to systems of largely varying physical scales. These non-standard solutions provide higher performance alternatives to the issues of multi-phase clock distribution and larger-scale on-chip or on-interposer communication and coherence. These solutions include (i) models, tools and circuits for precision timing generation in CMOS technology, (ii) techniques for building higher-order interconnected clock structures that use distributed feedback to improve the ensemble stability of the structure, and can be utilized as a low-noise timing source for small-scale synchronous modules, (iii) transmission-line stabilized low-noise wave oscillator circuits providing non-overlapping clock phases for RF applications as well as chip-scale timing distribution, (iv) transition signaling strategies that achieve very high-bandwidth communication with instantaneous recovery at low power, between globally asynchronous on-chip or on-interposer modules and (v) methods of implementing low cost time-domain filters that utilize precision clocks to reduce timing noise originating from systematic noise sources.

The underlying circuits for all these solutions are pulse mode and built using a logic

family of pulse gates [30]. Pulse logic is self-resetting and uses atomic pulses to encode both, data and the time of arrival of data. These gates utilize local negative feedback loops that make the pulse shape largely invariant and independent of the shape of the input pulse, and also lead to interesting dynamic behavior that is exploited in the design of closed loop timing circuits. Pulse logic has been utilized for the design of several high-performance asynchronous circuits including precision pipelines [31], Intel's Pentium 4 ALU [32] and radiation-hard serial links [33]. In order to better understand the anomalous stability of completely self-timed serial links designed for the Large Hadron Collider at CERN [34], simple looping pulse gate circuits or pulse oscillators were first studied in [35], and were found to exhibit superior figures of merit than other similarly powered and sized ring oscillators. The dynamics leading to the stability were evaluated and Allan deviation [36] was proposed to be a powerful metric to analyze the temporal properties of these oscillators.

Based on the temporal dynamics of pulse gates described in [35], the first part of this thesis presents an analytical model describing the behavior of simple pulse gate loops, termed Collective Pulse Oscillators or CPOs in the presence of impulse and power-law noise. The analytical model is extended to a tool that enables rapid behavioral analysis of the noise properties of CPOs and helps establish a general mathematical relationship between CPO parameters, power usage and the phase noise of the oscillator. Comparisons drawn with inverter based ring oscillators show that CPOs are more resilient to impulse noise, uncorrelated device noise as well as power-coupled noise. Measurement results for CPOs of different diameters fabricated in IBM 130 nm technology are also presented that validate the analytical noise model as well as behavioral/Hspice simulation results. Other advantages of CPOs over ring oscillators are that they can be constructed with either even or odd number of pulse buffers, thus providing even or odd number of phases. Further, they can be operated in multiple modes by injecting different numbers of pulses

at start-up, providing precise phases with resolution smaller than the buffer delay if the number of pulses does not divide the number of phase taps. In particular, operation at high frequencies is supported independent of the number of available phase outputs. It is also possible to design CPOs that provide identically timed image clock phases at multiple physical locations. Multi-pulse CPOs provide a mechanism to improve frequency stability and phase noise without increasing the total power density.

Two closely related works based on similar closed loop dynamics are by Fairbanks et al.[37], who observed that asynchronous tokens fired into a ring led to uniform distribution of the tokens around the ring, and Self Timed Ring Oscillators (STROs) [38], constructed using Muller-C gates [39], that utilized gate dynamics to yield integrated phase noise improvements. To the best of our knowledge, this is the first work that presents detailed time-domain analysis of the behavior of oscillators that exploit local time-variant gate delays to achieve precise phase resolutions and also improve the global frequency stability. The analysis is strongly supported by simulation and measurement results.

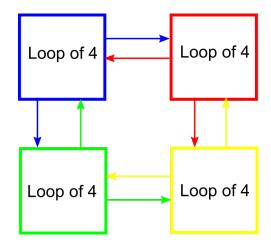

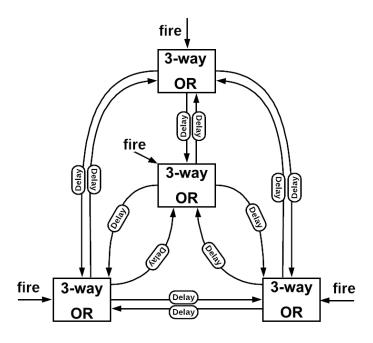

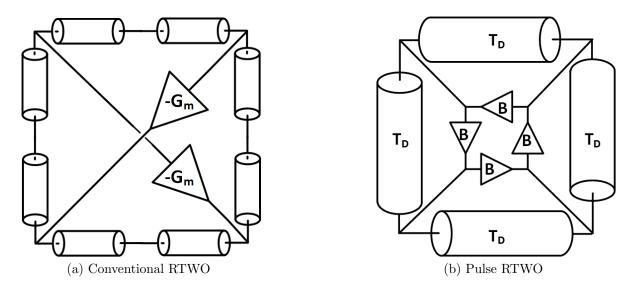

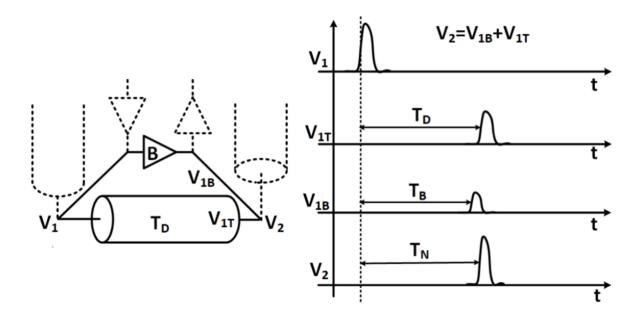

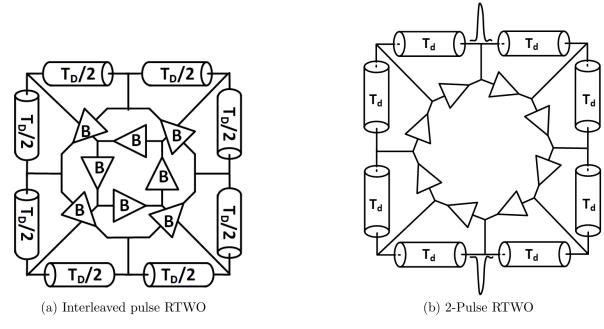

The second part of this thesis presents CPO structures that are more complex than simple loops of pulse gates. First, CPOs that make use of additional interconnections in order to improve the high-frequency noise properties of looping CPOs are studied, and interconnection strategies that scale with the size of the CPO are presented. These structures essentially make use of distributed timing feedback over short cross-links to improve the stability of strongly coupled high mass CPO rings and would serve as an excellent timing distribution solution over small-to-medium scale synchronous islands. Second, architecture, design and measurements for a transmission line stabilized pulsed rotary wave [40] CPO in IBM 130 nm are presented. This design utilizes pulse buffers as non-linear, full-swing, limiting amplifier stages to compensate for transmission line loss and maintain the wave shape of a unidirectional, low-duty cycle, fast-slope traveling pulse. It achieves further lower noise as it is coupled to a transmission line resonator and is an

ideal candidate for accurately capturing event timing at low injected jitter. Applications requiring timing distribution, or non-overlapping, low duty-cycle multi-phase clocks can effectively utilize this design.

The third part of this thesis presents Multi Wire Phase Encoding (MWPE), a signaling strategy suitable for on-chip/on-interposer links connecting globally asynchronous modules. These links are aimed at reducing the energy cost of moving data across a large scale SoC or NoC, which is known to be orders of magnitude higher than the cost of computation [41] [42] [1]. Most widely used high-performance I/O interfaces utilize PLL or DLL based data recovery at the receiver [43], [44]. These designs not only incur higher static power consumption, but also require hundreds to tens of thousands of clock cycles to achieve a lock, increasing the link overhead, especially if the communication is burst-mode or is switched from different sources.

MWPE in contrast, encodes data in the time correlated switching of multiple signaling wires as opposed to signal levels, and thus does not require a sampling clock to recover the transmitted data. This eliminates the static power consumption incurred due to a DLL or PLL at the receiver, and also makes the link 'fire-and-forget' as the data can be recovered instantaneously. Further MWPE can transmit data at effective rates (i) higher than the bandwidth limit of a single wire, (ii) higher than the rate of other known transition signaling techniques, and (iii) comparable to or higher than parallel conventional NRZ encoded links. This part of the thesis presents the MWPE protocol, deriving its theoretical bandwidth limits and evaluating its performance on practical on-chip channels. Link circuits for a 6-wire MWPE link are implemented in 22 nm FDX technology and the link is shown to operate at overall bandwidths > 100Gbps with an energy overhead of only 0.5 - 0.8pJ/bit.

The last section of this thesis introduces the potential of pulse-gate technology and the precise timing generated by CPO clocks for implementing low-cost time-domain linear

filters. These filters are designed to minimize systematic timing jitter in the arrival time of events by mixing the arrival time with the time of occurrence of a precise clock phase. Since CPOs can generate clock phases much finer than a gate delay, the mixing can be done at a very high resolution and correct for timing deviations as small as a phase fraction. A behavioral example showing the effectiveness of this technique to cancel timing jitter induced due to distortions on a wired channel is presented, showing a  $40 \times$  reduction in time deviations after filtering.

### 1.2 Thesis Organization

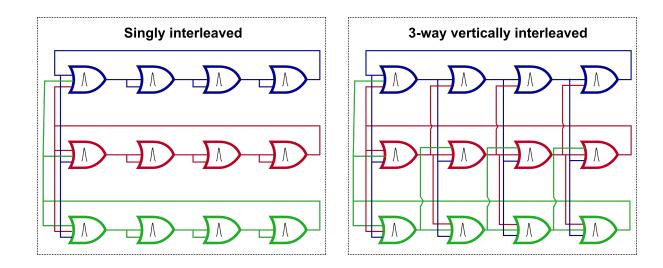

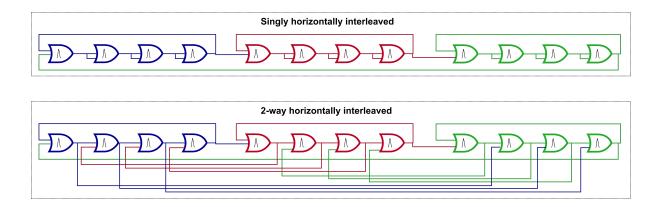

The organization of the remainder of this thesis is as following: chapter 2 introduces pulse gates and Collective Pulse Oscillators (CPOs), describes the dynamics exhibited by closed loop pulse gate circuits and construction and properties of CPOs; chapter 3 presents a time-domain analytical model based on linear difference equations that describes the temporal noise progression in CPOs when injected by an impulse of noise. Three exact solutions are presented and a second order general solution is inferred; in chapter 4, Allan deviation is reviewed as a time-domain measure of oscillator frequency stability, a behavioral simulator to analyze bigger CPO loops is presented, the general analytical solution is verified against behavioral and Hspice simulations, the performance of CPOs when subjected to power-law noise is analyzed and a comparison is drawn between the noise resilience of CPOs and inverter-based ring oscillators; chapter 5 presents measurement results for a chip fabricated in IBM 130 nm consisting of programmable 8gate and 40-gate CPOs. These CPOs are characterized using both phase noise and Allan deviation. The measurement results closely follow the theory set forth by the analytical model presented in chapter 3; chapter 6 presents complex CPO topologies that use 2-way and p-way interleaving (where p is the number of pulses) to improve the high-frequency

stability of loop-connected CPOs. Architectures that allow interleaving to be scaled to higher dimension CPOs are presented and a tetrahedron clock structure is presented that further improves the high-frequency stability. Methods for voltage tuning and injection locking of CPOs are also presented in this chapter, followed by the architecture, design and measurement results for a transmission line stabilized pulsed rotary travelling wave oscillator; chapter 7 presents Multi-Wire Phase Encoding, including derivation of theoretical bandwidth bounds, performance of the encoding on practical on-chip channels, and characterization of the link performance using circuits constructed in 22 nm FDX technology; chapter 8 introduces the realization of time-domain linear filters that utilize precise clock phases generated by CPOs to reduce the magnitute of timing noise due to systematic noise sources. An example showing reduction of timing jitter due to onchip channel distortions is presented; chapter 9 presents conclusions and future research directions.

### 1.3 Permission and Attributes

The contents of chapters 2, 3, 4 and 5 have previously appeared in the IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 28, no. 5, May 2020, doi: 10.1109/TVLSI.2019.2959532, P. Mukim et al., "Design and Analysis of Collective Pulse Oscillators". Some contents of chapter 6 have been previously presented at the IEEE Computer Society Annual Symposium on VLSI (ISVLSI), Miami, FL, USA, 2019, doi: 10.1109/ISVLSI.2019.00051, P. Mukim et al., "Distributed Pulse Rotary Traveling Wave VCO: Architecture and Design". These materials are used here under the terms of the IEEE author re-use policy allowing primary author re-use in subsequent work. Chapter 7 has been submitted to the IEEE Transactions on Very Large Scale Integration (VLSI) Systems and is currently being reviewed.

# Chapter 2

# Pulse Logic and Collective Pulse Oscillators

### 2.1 Introduction to Pulse Logic

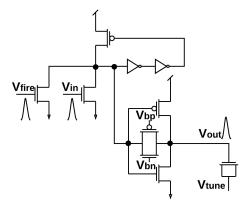

The circuits analyzed and implemented in this work are based on a logic family of pulse gates [30], and this section provides an overview of the working of pulse gates. The simplest pulse gate, i.e., a pulse buffer is shown in Fig. 2.1a. A pulse buffer is a non-linear, shape-preserving amplifier that expects a pulse input and produces a pulse output. The critical node voltage is pulled down by the input pulse signal at IN, which pulls up the output node, OUT, and triggers the PMOS transistor to pull up the critical node, resetting the gate. The keeper loop restores charge on the critical node, and prevents it from floating when it is not actively driven by an input pulse or the resetting PMOS transistor. After a suitable delay, the input to the PMOS transistor returns to its steady (high) state. As shown in Fig. 2.1b, different logic functions such as ORing pulses, implementing guarded pulse generating by ANDing a pulse with a level and other AND/OR combinations can be realized by modifying the pull-down network of pulse

gates.

Figure 2.1: Pulse gate circuits

Pulse logic makes use of SR-latches to convert pulses to levels and store state. Fig. 2.2b shows an example of a pulse gate circuit where pulse gates and an SR-latch are used to implement a toggle latch. Assuming that initially the latch is reset and  $Q=0, \bar{Q}=1$ , arrival of a pulse at IN triggers the top pulse AND gate, setting the latch and making  $Q=1, \bar{Q}=0$ . Thus, every new event toggles the state of the SR-latch.

Figure 2.2: Pulse latches

Figure 2.3: 2-bit serializer implementations

A general rule followed while designing pulse gate circuits is that every parallel stack of pull-down transistors allows a single pulse input. Operations such as ANDing two pulses are prohibited. These circuits exhibit two-sided timing constraints and automated timing verification of pulse gate circuits is currently an active area of research [45]. Although pulse logic has been primarily used to implement asynchronous circuits, small synchronous blocks to be used in a globally asynchronous setting can also be easily implemented. Fig. 2.3 shows examples of 2-bit asynchronous and clocked serializers implemented using pulse gates. In either case, one-hot pulses on 2-channels represent data values as well as mark the arrival of data, but the module in the serializer of Fig. 2.3a generates a trigger signal for the next module, whereas in the serializer of Fig. 2.3b, the module communicates to the next module via an edge that it has processed the input clock pulse, and now it is the next module's turn to be evaluated on the next clock pulse. While pulse-mode signaling allows data and timing to be self-contained in the same signal, it also leads to interesting dynamic behavior in closed loop circuits or Collective Pulse Oscillators, which are described in the next section.

## 2.2 Collective Pulse Oscillators: System Description

CPOs can be used as Voltage controlled oscillators (VCOs) that are required in a broad range of digital, mixed-signal, and RF integrated circuit (IC) designs for logic timing, sampling, and frequency synthesis. Applications such as time to digital converters (TDCs)[46, 47], analog to digital converters (ADCs) [48, 49], clock and data recovery (CDR) [50] and microprocessor clocking [9] require low integrated timing noise and often utilize multiple oscillator phases. Ring oscillators, consisting of inverters or differential limiting amplifiers, are commonly used as VCOs due to their small footprint, broad tuning range and availability of multiple clock phases.

Widely-used techniques to improve phase noise of ring oscillators include transistor sizing [51, 52], jitter minimization [53], transmission line stabilization [54] and spatial-coupling [55, 56]. Phase-noise is improved by increasing the power or by coupling to a high-Q resonator. Increasing the power yields a phase noise improvement of  $-10 \log p$ , where the oscillator power is  $\propto p$ . On the other hand, linear spatial coupling between p-identical oscillators yields a phase noise improvement of  $-10 \log p$  only near the carrier frequency [56]. At frequency-offsets far from the carrier or equivalently over small time-scales, the improvement in frequency stability is less than  $\propto 1/\sqrt{p}$ . This is due to the finite time associated with correction of noise perturbations in a weakly coupled system [57]. However, the possibility of achieving multiple clock phases with resolutions independent of the smallest gate delay for a given technology [55] and ease of low-skew low-jitter timing distribution [58] make their use viable for a variety of applications [59, 60, 61, 62].

For widely analyzed ring or LC oscillators, it is known that phase shifts due to noise persist indefinitely [63]. However, the behavior of CPOs is distinct in this regard. CPOs exhibit temporal degradation of phase error to a magnitude smaller than the initial injected phase error. This is achieved by partial retention of past state in the form of residual gate charge. Effectively, each gate of the CPO shows local negative timing feedback and corrects phase errors, leading to improvement of the global frequency stability. The self-correction of phase error occurs at time scales that are close to the oscillation frequency. As a result, the behavior of CPOs is similar to that of spatially-coupled oscillators with frequency stability improvement  $\propto 1/\sqrt{p}$  across all time scales beyond the correction settling time.

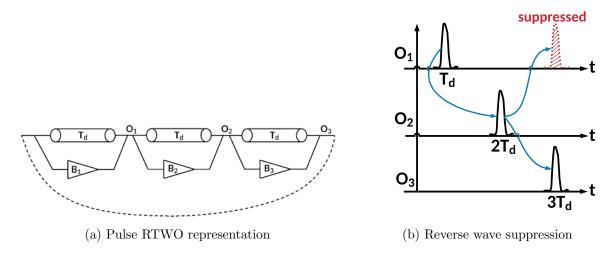

CPOs are formed by connecting pulse gates in a loop and Fig. 2.4b shows the voltages at different nodes of a pulse buffer during pulse generation. Here,  $t_{Dp}$  is the delay of the forward path from the input to the output pulse and  $t_{Dn}$  is the delay of the reset

t<sub>pp[i]</sub>  $\mathbf{t}_{\mathsf{Dp}[i+1]}$ <u>τ[</u>i+1 Vin  $p_{1[i+1]}$  $p_{1[i]}$ Vcrit Causes repulsion, p1\_o[i+1] is delayed  $p_{1_{q[i]}}$ p<sub>1\_o[i+1]</sub> Vout **Vreset -**t y[i] x[i+1]y[i+1] x[i]

(b) Voltage at pulse gate nodes during pulse generation

Figure 2.4: CPO: Construction and Timing

Figure 2.5: Delay-separation dynamics

loop. The relative values of  $t_{Dp}$  and  $t_{Dn}$  lead to interesting dynamics. These dynamics are represented through a delay-separation curve that shows how the input-output gate delay  $(t_{Dp})$  is modulated by the time separation  $(\tau)$  between consecutive input pulses at that gate. Fig. 2.5a shows delay separation curves for repulsive, constant or attractive dynamics in amplifiers. Here m is the slope of the curve and b is the y-intercept. While this slope is negative in pulse gates, typical inverters have a very slightly positive slope, i.e. the delay of the gate decreases as pulses approach in time. This leads to the well-known 'settling' of ring oscillators to the lowest possible mode. Fig. 2.5b shows the delay separation curve for a typical pulse gate. This curve comprises of three regions:

- Region-1: If the separation  $\tau[i+1]$  between consecutive pulses p[i] and p[i+1] is small such that  $V_{crit}$  is still pulled low when pulse p[i+1] occurs, the pulse  $p\_o[i+1]$  at  $V_{out}$  will coalesce with the pulse  $p\_o[i]$ . In effect, the input pulse p[i+1] is rejected.

- Region-2: If the separation  $\tau[i+1]$  between consecutive pulses p[i] and p[i+1] is

such that  $V_{crit}$  has been pulled-up substantially, but the gate is in its reset phase when pulse p[i+1] occurs, i.e.,  $V_{reset}$  is active (low), trying to pull-up  $V_{crit}$ , a distinct pulse  $p_{-}o[i+1]$  at  $V_{out}$  will be generated. However, with both the pull-down and pull-up transistors active, the time to discharge  $V_{crit}$  increases, increasing the delay of the gate, effectively causing repulsion of  $p_{-}o[i+1]$ . This behavior leads to a high-slope delay-separation region.

• Region-3: If the separation  $\tau[i+1]$  between consecutive pulses p[i] and p[i+1] is such that the reset phase has concluded when p[i+1] occurs, the stored charge in the keeper hysteresis loop slightly delays the pulse  $p_{-}o[i+1]$  at  $V_{out}$ . This leads to a low-slope delay-separation region.

By changing the relative delays of a pulse gate's forward and feedback paths  $(t_{Dp})$  and  $t_{Dn}$ , both b and m can be tuned. Methods for this are described in [64]. When pulse gates are connected in a loop as is the case with CPOs, pulses distribute uniformly in time around the loop due to the repulsive dynamics of the gates. Hence, a precise phase tap is available at each CPO gate. A CPO ring can be constructed with either even or odd number of pulse gates, making it possible to generate both even or odd number of clock phases. A g-gate CPO operating with p-pulses where g/p is an integer will exhibit g/p different phases, with each phase available at p gates. If p and p are relatively prime, each gate will produce a unique phase with period  $(g/p)*t_{Dp}$  and phase resolution  $t_{Dp}/p$ . Thus a CPO can easily produce pulses with phase resolution finer than  $t_{Dp}$ .

For a CPO that has p pulses traveling around the loop, the oscillation frequency depends on the ratio of gates per pulse (g/p) and  $t_{Dp}$ , and is equal to  $(g/p) * t_{Dp}$ . The ratio g/p also sets the region of operation on the delay-separation curve. By increasing the number of pulses p while keeping the g/p ratio a constant, the rate of pulse arrival at each gate stays unchanged and the oscillator operates at the same frequency. However,

the total power increases  $\propto p$ , and the effective frequency stability is enhanced. The duty cycle of the oscillator is determined by the ratio of the width of pulses (set by the delay of the reset loop,  $t_{Dn}$ ) and the oscillator period.

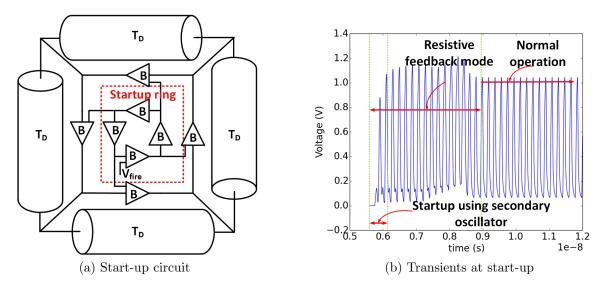

Since it is possible for a g gate CPO to run in multiple modes set by the number of pulses p, it is crucial to ensure a reliable start-up in the desired mode. The  $V_{fire}$  input of the pulse gate is used to inject a start-up pulse into the CPO. Starting a mode with p pulses can be done in two ways: (1) p pulses can be injected sequentially into the  $V_{fire}$  node of a single pulse gate with relative separations close to the expected period of the CPO, (2) the  $V_{fire}$  nodes of p uniformly-spaced gates can be injected with a pulse simultaneously.

As long as the separation of start-up pulses is large enough to avoid pulse coalescence, the CPO will start-up reliably. If the pulse injection period at start-up does not exactly match the period of a stably operating CPO or there is a skew between the fire inputs to the different gates, the repulsive dynamics in pulse gates will still lead to uniform distribution of pulses, and the CPO will rapidly settle to a stable state. Fig. 2.6 shows the start-up circuit and output waveforms for a g=8, p=2 CPO. The fire pulse is generated by converting an external edge to a pulse, and is injected into gates 1 and 5 of the CPO. Fig. 2.7 shows the period of pulse arrival obtained from Hspice simulations for a g=8, p=2 CPO in GFUS8RF technology at different gates after start-up. Since at start-up the  $V_{crit}$  nodes of the CPO do not store any residual charge, the gate delay and period of the CPO are different from the stable period. Once oscillations are sustained, the pulse arrival period settles to a stable value at all gates in a few cycles.

Widely used models for the design of oscillators like the Linear Time-Variant (LTV) model using Impulse Sensitivity Function (ISF) [63] and non-linear analysis techniques of stable oscillators in the presence of perturbations [65] assume that phase errors due to noise persist indefinitely, with their magnitude equal to the initial injected error. They

Figure 2.6: Start-up circuit and waveforms for g=8, p=2 CPO

Figure 2.7: Period of pulse arrival at different gates of g=8, p=2 CPO after start-up settles to a constant value in less than 10 cycles

do not account for non-linear phase error corrections with time, a property fundamental to the operation of CPOs, and hence cannot be directly applied to analyze CPOs. To overcome this challenge, a new sequential time delay model is formulated and presented in chapter 3. It explains the noise properties of CPOs as a function of various oscillator parameters.

### Chapter 3

## Analytical Noise Modeling for CPOs

This chapter presents time-domain analytic solutions for the pulse arrival time for CPOs perturbed by a noise impulse. Although a bilinear approximation for the delay-separation curve is more accurate (Fig. 2.5b) for CPOs, the model assumes small perturbations for which the CPO operates in either one of the linear regions (Region 2 or Region 3). Analytic solutions are obtained by modeling the arrival time of pulses at each pulse gate via a set of linear difference equations. The goal is to derive exact solutions for a few lower order loops, that can be used to construct a general perturbation solution.

# 3.1 Exact Solutions for Pulse Arrival Time Under Impulse Noise Perturbation

**3.1.1**

$$Gates(g) = 1$$

,  $Pulses(p) = 1$

Consider a single gate CPO with the output of a pulse buffer looping back to its input, that has been started by an external event. Let x[k] be the arrival time of the  $k^{th}$  pulse at the gate. Then x[k] is given by Equation 3.1, where b and m are constants.

Figure 3.1: 1-pulse travelling in a 1-pulse-gate loop

$$x[k] = x[k-1] + b + m(x[k-1] - x[k-2])$$

(3.1)

The arrival time of a pulse at the gate is the sum of the arrival time of the previous pulse and the delay of the gate. The delay here is represented as a linear function of the separation, that is set by the arrival times of the previous two pulses. In the case of ideal (noise-less) operation, the period (x[k] - x[k-1] = x[k-1] - x[k-2]) will be a constant given by b/(1-m). If an impulse of timing error of magnitude  $\epsilon$  is introduced into the system at k=1, the initial conditions are given by Equation 3.2.

$$x[0] = 0, x[1] = \epsilon + \frac{b}{1 - m}$$

(3.2)

Solving this linear difference equation, the  $k^{th}$  pulse arrival time is given by Equation 3.3.

$$x[k] = \frac{bk}{1-m} + \frac{\epsilon}{1-m} - \frac{\epsilon m^k}{1-m} \tag{3.3}$$

The solution consists of three distinct terms:

- The first term represents the ideal pulse arrival time, if no noise were introduced into the system.

- For m < 0 (the case for CPOs), the second term represents the residual phase error

after a sufficiently long interval. It can be observed that an injected impulse error of  $\epsilon$  is reduced in magnitude to a residual error of  $\epsilon/(1-m)$ .

• For m < 0 and |m| < 1 (again the case for CPOs), the third term represents a rapidly diminishing transient that reduces the magnitude of the phase error to its final residual value. However, it can be seen that if m > 0 or if |m| > 1, the phase error can grow with time, making the oscillator unstable.

Since m > 0 or |m| > 1 have been shown to make the oscillator unstable, the subsequent analysis excludes these cases and is strictly for CPOs with |m| < 1. Next, we will evaluate the case of a single pulse travelling in a loop comprising of two pulse gates.

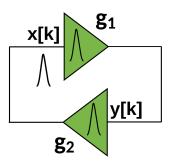

#### **3.1.2** Gates(g) = 2, Pulses(p) = 1

Let x[k] and y[k] be the arrival times of the  $k^{th}$  pulses at gates 1 and 2 respectively. Then x[k] and y[k] are given by Equation 3.4 and Equation 3.5, where b and m are constants.

Figure 3.2: 1-pulse travelling in a 2-pulse-gate loop

$$y[k] = x[k] + b + m(x[k] - x[k-1])$$

(3.4)

$$x[k] = y[k-1] + b + m(y[k-1] - y[k-2])$$

(3.5)

In the case of ideal (noise-less) operation, the pulse arrival periods at the two gates (x[k] - x[k-1] = y[k] - y[k-1] = y[k-1] - y[k-2]) will be constants given by 2b/(1-2m), with each gate contributing to half of the delay. If an impulse of timing error of magnitude  $\epsilon$  is introduced when a pulse arrives at gate 2 at k=1, the initial conditions are given by Equation 3.6.

$$x[0] = 0, y[0] = \frac{b}{1 - 2m}, x[1] = \frac{2b}{1 - 2m}, y[1] = \epsilon + \frac{3b}{1 - 2m}$$

(3.6)

Solving this system of linear difference equations, the  $k^{th}$  pulse arrival times are given by Equation 3.7.

$$x[k] = \frac{2bk}{1 - 2m} + \frac{\epsilon}{1 - 2m} - \frac{\epsilon * 2^{-k}}{2(1 - 2m)} * o[k]$$

(3.7)

where o[k] is given by Equation 3.8.

$$o[k] = \frac{1}{\sqrt{m(m+4)}} \times \left[ (m(m+2-\sqrt{m(m+4)}))^k + (m(m-2+\sqrt{m(m+4)}))^k + (m-2)((m(m+2-\sqrt{m(m+4)}))^k - (m(m+2+\sqrt{m(m+4)}))^k) \right]$$

$$(3.8)$$

For CPOs with m < 0 and |m| < 1, this loop operates at a period that is slightly smaller than twice the period of the previous case, where g = 1, p = 1. The magnitude of the residual phase error is further reduced compared to the g = 1, p = 1 case. The transient term however, is a fairly complex function of time and the delay separation slope m as is expected of a  $3^{rd}$  order system. This transient term represents the settling trajectory (and time) of the loop to a stable state, in response to the impulse injection.

#### **3.1.3** Gates(g) = 2, Pulses(p) = 2

Let x[k] and y[k] be the arrival times of the  $k^{th}$  pulses at gates 1 and 2 respectively. Then x[k] and y[k] are given by Equation 3.9 and Equation 3.10, where b and m are constants.

Figure 3.3: 2-pulses travelling in a 2-pulse-gate loop

$$y[k] = x[k-1] + b + m(x[k] - x[k-1])$$

(3.9)

$$x[k] = y[k-1] + b + m(y[k] - y[k-1])$$

(3.10)

In the case of ideal (noise-less) operation, the pulse arrival periods at the two gates (x[k] - x[k-1] = y[k] - y[k-1]) will be constants given by b/(1-m). If an impulse of timing error of magnitude  $\epsilon$  is introduced when a pulse arrives at gate 2 at k=1, the initial conditions are given by Equation 3.11.

$$x[0] = 0, y[0] = 0, x[1] = \frac{b}{1-m}, y[1] = \epsilon + \frac{b}{1-m}$$

(3.11)

Solving this system of linear difference equations, the  $k^{th}$  pulse arrival times are given

by Equation 3.12 and Equation 3.13.

$$x[k] = \frac{bk}{1 - m} + \frac{\epsilon}{2(1 - m)} - \frac{\epsilon * 2^{-k} m^k}{2(1 - m)} * o_x[k]$$

(3.12)

$$y[k] = \frac{bk}{1-m} + \frac{\epsilon}{2(1-m)} - \frac{\epsilon * 2^{-k}(-m)^k}{2(1-m)} * o_y[k]$$

(3.13)

where  $o_x[k]$  and  $o_y[k]$  are given by Equation 3.14 and Equation 3.15 respectively.

$$o_x[n] = \frac{1}{\sqrt{1 + m(m+6)}} \times ((-m-1)\sqrt{1 + m(m+6)})^n - (-m-1)\sqrt{1 + m(m+6)})^n$$

(3.14)

$$o_y[n] = -o_x[n] \tag{3.15}$$

The first term of the solution in this case exactly matches the first term of the case where g=1, p=1. This also matches the intuitive expectation, as fixing the g/p ratio and changing p should result in the same oscillation frequency. The magnitude of the residual phase error (the second term in Equation 3.12 and Equation 3.13) is exactly half, compared to the g=1, p=1 case. This illustrates that by doubling the effective mass of the ring (and its power consumption), while keeping its oscillation frequency constant, the magnitude of the residual phase error is made twice as small. Once again, the transient terms for the two gates are fairly complex, but also show a symmetry. The two gates act in conjunction such that their respective phase errors symmetrically approach the final residual phase error in the loop.

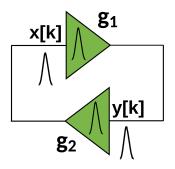

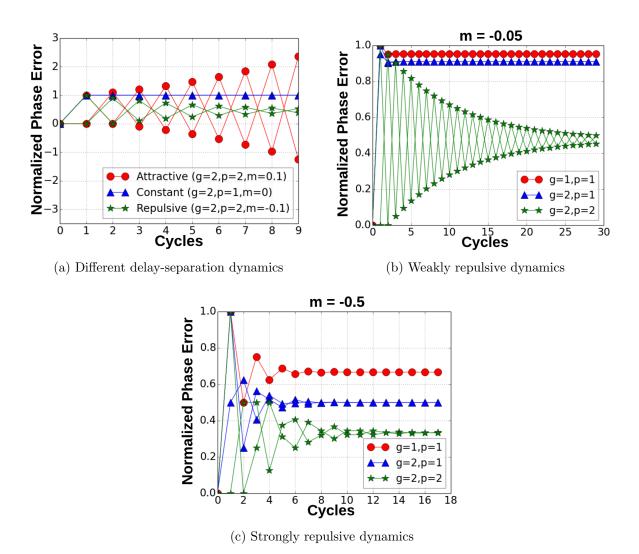

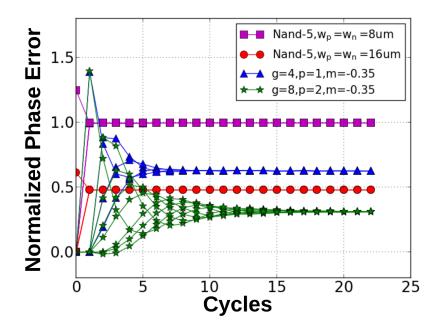

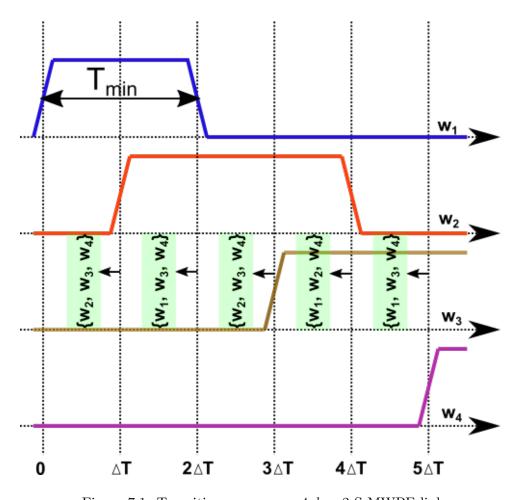

Based on the three exact solutions derived so far, the normalized phase error (obtained by subtracting the ideal noise-less arrival time from the derived solutions and normalizing it with respect to the magnitude of the injected impulse  $\epsilon$ ) is plotted in Fig 3.4. The following observations can be made from these plots:

Figure 3.4: Normalized phase error obtained from analytical solutions

- Fig. 3.4a compares the normalized phase error for oscillators exhibiting attractive (m > 0), constant (m = 0) and repulsive (m < 0) dynamics. It can be seen that constant dynamics result in a constant phase error of magnitude equal to the impulse noise injection, as is the case with conventional oscillators. To model a conventional ring oscillator, the p = 1 mode was chosen, as inverter-based ring oscillators only involve circulation of a single event around the ring. The phase error for attractive dynamics increases in magnitude, making the oscillator unstable. With repulsive dynamics, the oscillator settles to a phase error smaller in magnitude than the initial injected impulse.

- Increasing the number of gates (g), number of pulses (p) or the magnitude of the (negative) delay-separation slope (m), reduces the magnitude of the residual phase error.

- The settling time, i.e., the time taken by the transient term to diminish in magnitude, is a complex function of the loop topology and operating slope. While it can be inferred that a multi-pulse ring tends to have a longer settling time, increasing the magnitude of the operating slope can increase or decrease the settling time, as can be seen in Fig. 3.4b and Fig. 3.4c. For the g = 1, p = 1 and g = 2, p = 1 CPOs increasing the magnitude of m from -0.05 to -0.5 increases the settling time. Whereas for the g = 2, p = 2 CPO, it causes the settling time to decrease.

#### 3.2 Generalization of the solution to g-gates, p-pulses

Obtaining exact solutions for higher-order loops (order > 3) is difficult. However, based on the three exact solutions derived, the fixed (noise-less) pulse arrival time and magnitude of the residual error can be inferred to have forms shown in Equation 3.16.

$$x[k] = \frac{gbk}{p(1 - (g/p)m)} + \frac{\epsilon}{p(1 - (g/p)m)} + \epsilon * transient_x[k, g, p, m]$$

(3.16)

$$or, x[k] = T_o k + \Phi[k] \tag{3.17}$$

The general solution of Equation 3.16 is re-written in Equation 3.17 as the sum of: (i) the nominal arrival time (with  $T_o$  as the nominal period of the CPO), represented by the first term of Equation 3.16 and (ii) phase deviation  $\Phi[k]$ , represented by the sum of second and third terms of Equation 3.16. The correctness of this general solution has been verified against both behavioral and Hspice simulations presented in chapter 4. The general analytic solution shows that:

- For a fixed number of gates g and (negative) m, CPOs operating in different modes set by the number of pulses p, see a reduction in period that is less than  $\propto p$ .

- The magnitude of both the residual phase error and the transient term is directly proportional to the magnitude of the injected noise impulse. This makes the settling time independent of the magnitude of noise injection.

- Increasing the number of gates g, the number of pulses p or the magnitude of the (negative) delay-separation slope m, reduces the magnitude of the residual phase error.

- For a fixed oscillation frequency (obtained by having g/p and m constant), the residual phase error reduction for an noise impulse is proportional to the number of pulses p, and hence the total power consumption. Qualitatively, this shows that for a loop, each gate's noise injection is scaled by the number of pulses which react as an ensemble to reduce the magnitude of the injected error.

These analytic solutions are based on impulse noise injection into a single CPO gate. To analyze the frequency stability with continuous power-law noise injection, Allan deviation, a time domain stability measurement metric is used and over-viewed in chapter 4.

### Chapter 4

# Behavioral and Hspice Simulation Results for Simple Loop Connected CPOs

This chapter first provides an overview of Allan deviation [66], a time-domain frequency stability metric for oscillators. Next, the analytic model presented in chapter 3 is expanded into a generic behavioral tool, enabling the analysis of more complex loops with arbitrary imposed noise. The behavioral model is validated against Hspice simulations and the effect of power-law noise on different parameter CPOs is analyzed. A comparison between CPOs and ring oscillators in terms of their response to impulse noise, uncorrelated white device noise and power coupled noise is also drawn.

# 4.1 Time Domain Measurement of Stability Using Allan Deviation

We use Allan deviation as the analysis metric as it a very useful aid in measuring the stability of CPOs at different time scales. It characterizes the fractional frequency fluctuations (F[k]) in oscillators given by Equation 4.1 where  $\Phi[k]$  is the phase deviation (in seconds) as a discrete function of time and  $\tau$  is the measurement interval.

$$F[k] = \frac{\Phi[k+\tau] - \Phi[k]}{\tau} \tag{4.1}$$

Noise in circuits generally exhibits a power law given by  $S_F(f) \propto f^{\alpha}$ , where  $S_F(f)$  is the autospectral density of fractional frequency fluctuations F[k] and the exponent  $\alpha$  ranges from -3 to +2 typically. The well-analyzed noise sources in circuits, white FM and flicker FM, have  $\alpha$  of 0 and -1 respectively. Allan deviation is the same as the ordinary standard deviation of fractional frequency fluctuation values for white FM noise, but has the advantage, for more divergent noise types such as flicker noise, of converging to a value that is independent on the number of samples [66]. Allan deviation is given by the square root of  $\sigma^2(\tau)$  in Equation 4.2, where  $\Phi_i$  is the  $i^{th}$  phase error value spaced by the measurement interval  $\tau$  and N is the number of samples of phase error values averaged over  $\tau$ .

$$\sigma^{2}(\tau) = \frac{1}{2(N-2)\tau^{2}} \sum_{i=1}^{N-2} [\Phi_{i+2} - 2\Phi_{i+1} + \Phi_{i}]^{2}$$

(4.2)

Overlapping Allan deviation is a variant of the original Allan deviation that provides better statistical confidence [66]. Modified Allan deviation given by the square-root of Equation 4.3 is another variant that can additionally distinguish between noise behaviors having  $\alpha \geq 1$  [36]. Here, the measurement interval  $\tau = a\tau_o$ , a is the averaging factor and

$\tau_o$  is the basic measurement interval.

$$Mod \sigma^{2}(\tau) = \frac{1}{2a^{2}\tau^{2}(n - 3a + 1)} \times \sum_{j=1}^{N-3a+1} \{ \sum_{i=j}^{j+a-1} [\Phi_{i+2a} - 2\Phi_{i+a} + \Phi_{i}] \}^{2}$$

$$(4.3)$$

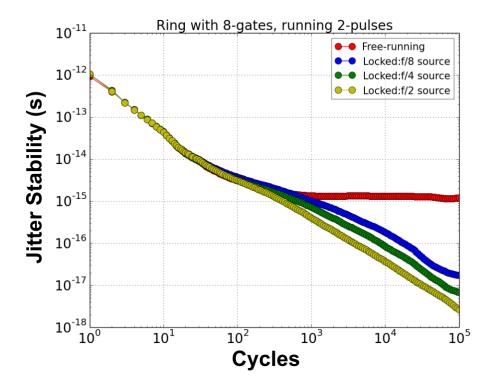

Different frequency domain noise profiles can be identified by measuring the slope of modified Allan deviation  $(Mod\sigma^2(\tau))$  on a log-log scale. White FM and Flicker FM have a slope of -1/2 and 0 respectively. Results in this chapter use modified Allan deviation to characterize the frequency stability of CPOs at different time scales. The dynamic phase error correction properties and the settling time associated with them are represented on modified Allan deviation plots by an initial high-slope (<-1/2) region. For comparing the jitter of CPOs operating at different frequencies, the Allan deviation values are scaled by the oscillation period  $(T_o)$  and plotted as a function of number of clock cycles. This metric is termed "Jitter Stability" in this work and the k-cycle Jitter Stability, J[k] is defined as follows:

$$Jitter\ Stability, J[k] = Mod\ \sigma(kT_o) * T_o$$

$$(4.4)$$

#### 4.2 Behavioral System Simulator