# **UCLA**

### **UCLA Electronic Theses and Dissertations**

#### **Title**

Learned Approximate Computing for Machine Learning

#### **Permalink**

https://escholarship.org/uc/item/1p7556nc

#### **Author**

Li, Tianmu

### **Publication Date**

2023

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA

Los Angeles

Learned Approximate Computing for Machine Learning

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical and Computer Engineering

by

Tianmu Li

#### ABSTRACT OF THE DISSERTATION

Learned Approximate Computing for Machine Learning

by

#### Tianmu Li

Doctor of Philosophy in Electrical and Computer Engineering

University of California, Los Angeles, 2023

Professor Puneet Gupta, Chair

Machine learning using deep neural networks is growing in popularity and is demanding increasing computation requirements at the same time. Approximate computing is a promising approach that trades accuracy for performance, and stochastic computing is an especially interesting approach that preserves the compute units of single-bit computation while allowing adjustable compute precision. This dissertation centers around enabling and improving stochastic computing for neural networks, while also discussing works that lead up to stochastic computing and how the techniques developed for stochastic computing are applied to other approximate computing methods and applications other than deep neural networks. We start with 3pxnet, which combines extreme quantization with model pruning. While 3pxnet achieves extremely compact models, it demonstrates limits of binarization, including the inability to scale to higher precision levels and performance bottlenecks from accumulation. This leads us to stochastic computing, which performs single-gate multiplications and additions on probabilistic bit streams. The initial SC neural network implementation in ACOUSTIC aims at maximizing SC performance benefits while achieving usable accuracy. This is achieved through design choices in stream representation, performance optimizations

using pooling layers, and training modifications to make single-gate accumulation possible. The subsequent work in GEO improves the stream generation and computation aspects of stochastic computing and reduces the accuracy gap between stochastic computing and fixed-point computing. The accumulation part of SC is further optimized in REX-SC, which allows efficient modeling of SC accumulation during training. During these iterations of the SC algorithm, we developed efficient training pipelines that target various aspects of training for approximate computing. Both forward and backward passes of training are optimized, which allows us to demonstrate model convergence results using SC and other approximate computing methods with limited hardware resources. Finally, we apply the training concept to other applications. In LAC, we show that an almost arbitrary parameterized application can be trained to perform well with approximate computing. At the same time, we can search for the optimal hardware configuration using NAS techniques.

The dissertation of Tianmu Li is approved.

Yizhou Sun

Nader Sehatbakhsh

Sudhakar Pamarti

Puneet Gupta, Committee Chair

University of California, Los Angeles 2023

To my parents for their support.

# TABLE OF CONTENTS

| 1 | Intr | oducti | $\mathbf{ion}$                       | 1  |

|---|------|--------|--------------------------------------|----|

|   | 1.1  | Comp   | utation in deep neural networks      | 1  |

|   | 1.2  | Comp   | utation with reduced accuracy        | 4  |

| 2 | Spa  | rse Bi | narized Processing                   | 9  |

|   | 2.1  | Introd | luction                              | 9  |

|   |      | 2.1.1  | A case for sparse XNOR networks      | 10 |

|   | 2.2  | Relate | ed Work                              | 12 |

|   |      | 2.2.1  | Binarized neural networks            | 12 |

|   |      | 2.2.2  | Weight pruning                       | 13 |

|   |      | 2.2.3  | Sparse binary networks               | 14 |

|   |      | 2.2.4  | Machine learning on embedded systems | 14 |

|   | 2.3  | The 3  | PXNet Approach                       | 15 |

|   |      | 2.3.1  | XNOR networks                        | 15 |

|   |      | 2.3.2  | Challenges in pruning XNOR networks  | 15 |

|   |      | 2.3.3  | Pruning a packed XNOR network        | 17 |

|   |      | 2.3.4  | Training 3PXNet                      | 19 |

|   | 2.4  | Exper  | imental Setup                        | 21 |

|   |      | 2.4.1  | Platforms                            | 21 |

|   |      | 2.4.2  | Benchmarks                           | 21 |

|   |      | 2.4.3  | Baseline                             | 22 |

|   | 2.5  | Result | s and Discussion                     | 23 |

|   |     | 2.5.1   | Accuracy & model size                      | 23         |

|---|-----|---------|--------------------------------------------|------------|

|   |     | 2.5.2   | Performance & energy                       | 26         |

|   | 2.6 | Conclu  | asion                                      | 27         |

| 3 | Mal | king St | tochastic Computing Work for Deep Learning | 29         |

|   | 3.1 | Stocha  | astic Computing Primer                     | 31         |

|   |     | 3.1.1   | Error behavior                             | 31         |

|   |     | 3.1.2   | Stream generation                          | 32         |

|   |     | 3.1.3   | Computation                                | 33         |

|   |     | 3.1.4   | Storage                                    | 38         |

|   |     | 3.1.5   | Non-linear computation                     | 38         |

|   | 3.2 | Stocha  | astic Computing Baseline Implementation    | 38         |

|   |     | 3.2.1   | Split-unipolar stream representation       | 38         |

|   |     | 3.2.2   | Computation skipping for average pooling   | 40         |

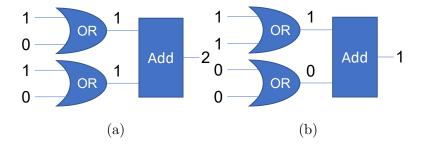

|   |     | 3.2.3   | Making OR accumulation practical           | 40         |

|   |     | 3.2.4   | Modeling the error of stochastic computing | 41         |

|   | 3.3 | Conclu  | ısion                                      | 43         |

| 4 | Imp | oroving | SC Generation and Execution                | <b>4</b> 4 |

|   | 4.1 | Co-op   | timized Shared Generation and Training     | 45         |

|   | 4.2 | Partia  | l Binary Accumulation                      | 46         |

|   | 4.3 | Result  | s                                          | 49         |

|   |     | 4.3.1   | Evaluation methodology                     | 49         |

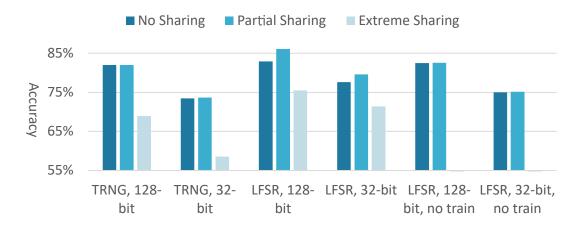

|   |     | 4.3.2   | GEO accuracy comparisons                   | 50         |

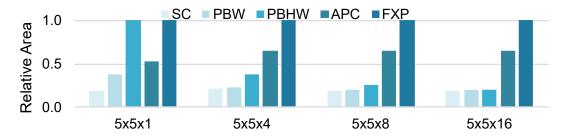

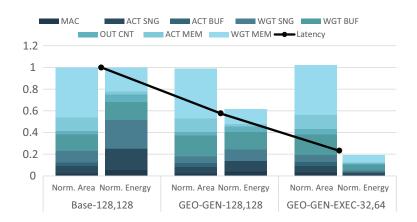

|   |      | 4.3.3  | Performance Impact of GEO Enhancements     | 51 |

|---|------|--------|--------------------------------------------|----|

|   | 4.4  | Conclu | asion                                      | 52 |

| 5 | Opt  | imizin | g SC accumulation                          | 53 |

|   | 5.1  | Motiva | ation                                      | 55 |

|   |      | 5.1.1  | SC accumulation primer                     | 56 |

|   |      | 5.1.2  | Precision                                  | 56 |

|   |      | 5.1.3  | Efficiency                                 | 58 |

|   | 5.2  | Range  | -extended OR Accumulation                  | 60 |

|   |      | 5.2.1  | Increasing the accuracy of OR accumulation | 60 |

|   |      | 5.2.2  | Efficient OR_n implementation              | 66 |

|   |      | 5.2.3  | Efficient training for OR_n accumulation   | 68 |

|   | 5.3  | Result | SS                                         | 75 |

|   |      | 5.3.1  | Evaluation                                 | 75 |

|   |      | 5.3.2  | Accuracy improvements                      | 76 |

|   |      | 5.3.3  | Training speed improvements                | 78 |

|   |      | 5.3.4  | Performance                                | 80 |

|   |      | 5.3.5  | OR_n for non-trained applications          | 82 |

|   | 5.4  | Conclu | asion                                      | 83 |

| 6 | Solv | ing th | ne Training Issue                          | 84 |

|   | 6.1  | Speed  | ing up SC simulation                       | 86 |

|   |      | 6.1.1  | Stream packing                             | 87 |

|   |      | 6.1.2  | Computation optimization                   | 92 |

|   |     | 6.1.3 Generation optimization                                  |            | 100  |

|---|-----|----------------------------------------------------------------|------------|------|

|   | 6.2 | Training Neural Networks for Execution on Approximate Computin | g Hardware | e100 |

|   |     | 6.2.1 Activation proxy function                                |            | 100  |

|   |     | 6.2.2 Error injection training                                 |            | 103  |

|   |     | 6.2.3 Fine tuning                                              |            | 107  |

|   |     | 6.2.4 Gradient checkpointing                                   |            | 108  |

|   |     | 6.2.5 Results                                                  |            | 109  |

|   | 6.3 | Conclusion                                                     |            | 111  |

| 7 | Lea | arned Approximate Computing                                    |            | 113  |

|   | 7.1 | Introduction                                                   |            | 113  |

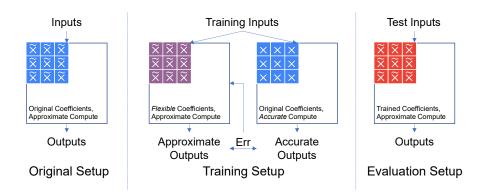

|   | 7.2 | Fixed Hardware LAC                                             |            | 115  |

|   |     | 7.2.1 Training applications for a fixed hardware               |            | 116  |

|   | 7.3 | Evaluation on Fixed Hardware                                   |            | 117  |

|   |     | 7.3.1 Approximate hardware                                     |            | 117  |

|   |     | 7.3.2 Applications                                             |            | 118  |

|   |     | 7.3.3 Dataset                                                  |            | 120  |

|   |     | 7.3.4 Optimization solvers                                     |            | 120  |

|   |     | 7.3.5 Results                                                  |            | 122  |

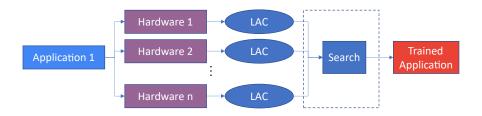

|   | 7.4 | Trained Hardware LAC                                           |            | 123  |

|   | 7.5 | Evaluation on Trained Hardware                                 |            | 126  |

|   | 7.6 | Conclusion                                                     |            | 128  |

| 2 | Cor | zelucion                                                       |            | 190  |

| 8.1    | Valida  | ation of SC-based Neural Networks on More Models and Datasets 131 |

|--------|---------|-------------------------------------------------------------------|

| 8.2    | Efficie | ent Model Transfer for Stochastic Computing                       |

| 8.3    | Enabl   | ing SC for Large Language Models                                  |

| 8.4    | SC for  | Homomorphic Encryption                                            |

| 8.5    | Specia  | alized SC Architectures for Emerging Compute Paradigms 134        |

|        | 8.5.1   | Range-adjustable OR_n accumulation                                |

|        | 8.5.2   | Delta-sigma SC                                                    |

| Refere | nces .  |                                                                   |

# LIST OF FIGURES

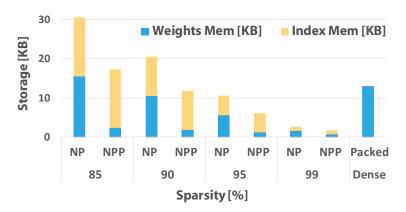

| 2.1 | Storage requirements for Dense, NP, and NPP XNOR "small" MNIST MLP for                |    |

|-----|---------------------------------------------------------------------------------------|----|

|     | varying levels of sparsity                                                            | 16 |

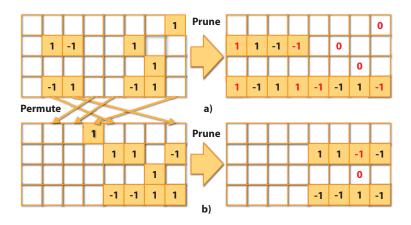

| 2.2 | Pruning with packing constraint of 4 bits a) without permutation, b) with per-        |    |

|     | mutation                                                                              | 18 |

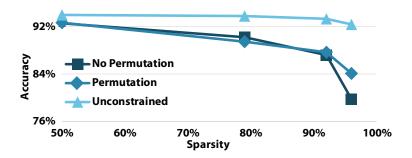

| 2.3 | Comparison of training results with and without permutation for different sparsities. | 18 |

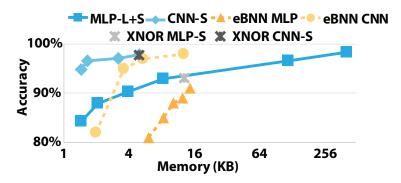

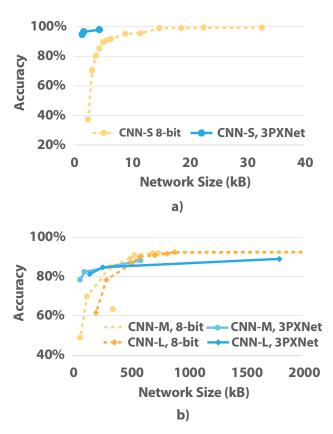

| 2.4 | Accuracy vs. Memory tradeoff compared to eBNN and dense XNOR                          | 23 |

| 2.5 | Accuracy comparison between sparse 8-bit network and 3PXNet, for MNIST (a)            |    |

|     | and CIFAR-10 (b)                                                                      | 25 |

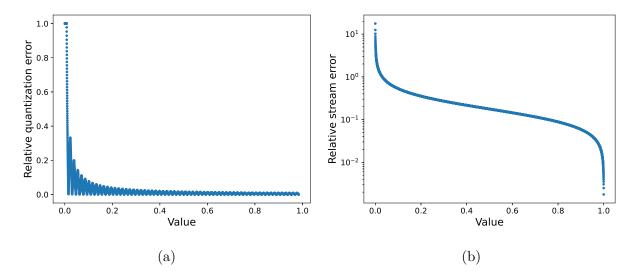

| 3.1 | Relative error resulting from (a) quantization and (b) randomness of stochastic       |    |

|     | computing                                                                             | 34 |

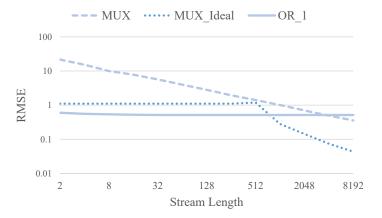

| 3.2 | Comparison of MUX- and OR-based adders' error with respect to accurate addition.      | 37 |

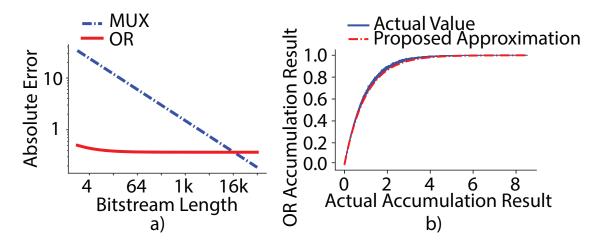

| 3.3 | Accuracy comparison between MUX and OR a) and comparison of approximation             |    |

|     | methods for OR accumulation b)                                                        | 42 |

| 4.1 | Accuracy vs. sharing for TRNG and LFSR-based random number generation                 | 47 |

| 4.2 | Area comparison for different hardware implementations of SC-based MAC units          |    |

|     | for different kernel sizes and different levels of partial binary accumulation        | 48 |

| 4.3 | Area, energy, and latency comparison between baseline and different GEO con-          |    |

|     | figurations (normalized to Base-128,128). The first bar in every group is for area    |    |

|     | while the second is for energy                                                        | 51 |

| 5.1 | (a) best and (b) worst case for partial binary accumulation                           | 54 |

| 5.2  | Area (a), critical path (b), and area-delay product (ADP) (c) for different dot   |            |

|------|-----------------------------------------------------------------------------------|------------|

|      | product implementations. For SC implementations, ADP is calculated after mul-     |            |

|      | tiplying the stream length, which is assumed to be 32 for each split-unipolar     |            |

|      | part                                                                              | 59         |

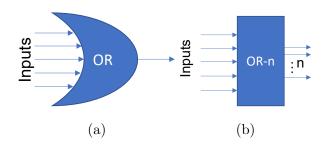

| 5.3  | Overview comparison between (a) OR and (b) OR_n                                   | 61         |

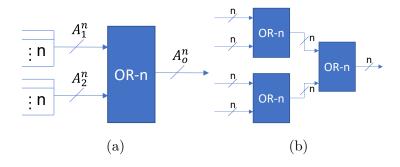

| 5.4  | (a) Single OR_n gate and (b) cascaded OR_n gates                                  | 61         |

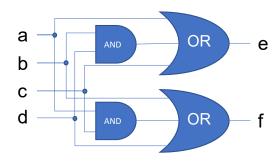

| 5.5  | OR_2 circuit implementation. Similar to Tab. 5.2, a, b, c, and d are the four     |            |

|      | input bits, and e and f are the two output bits. $\dots$                          | 67         |

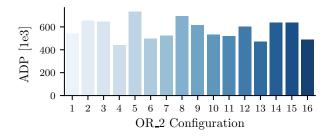

| 5.6  | ADP comparison between different OR_2 truth table implementations                 | 67         |

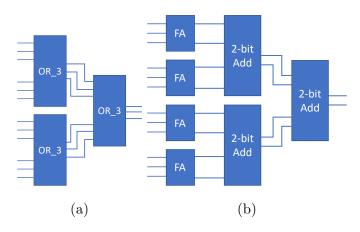

| 5.7  | (a) Parallel and (b) saturating adder implementation of OR_3                      | 68         |

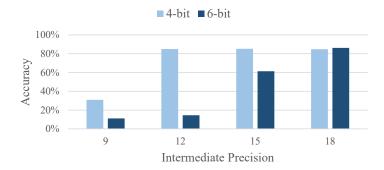

| 5.8  | TinyConv accuracy of with fixed-point computation using different intermediate    |            |

|      | precision.                                                                        | 69         |

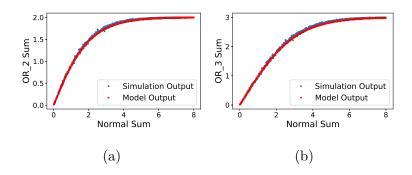

| 5.9  | Modeling performance of (a) OR_2 and (b) OR_3                                     | 70         |

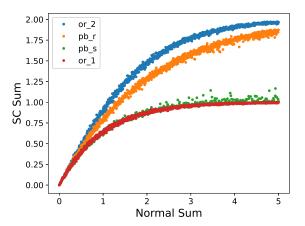

| 5.10 | Modeling performance comparison of OR_2 and 2-way partial binary accumula-        |            |

|      | tion. pb_r and pb_s use the same inputs and only the order of computation is      |            |

|      | changed, such that for pb_r partial sums are roughly equal, and for pb_s they are |            |

|      | very different                                                                    | 71         |

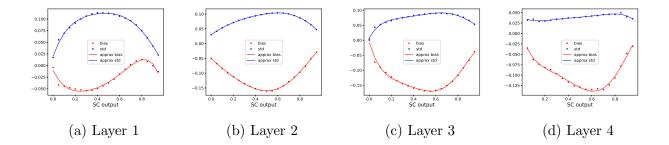

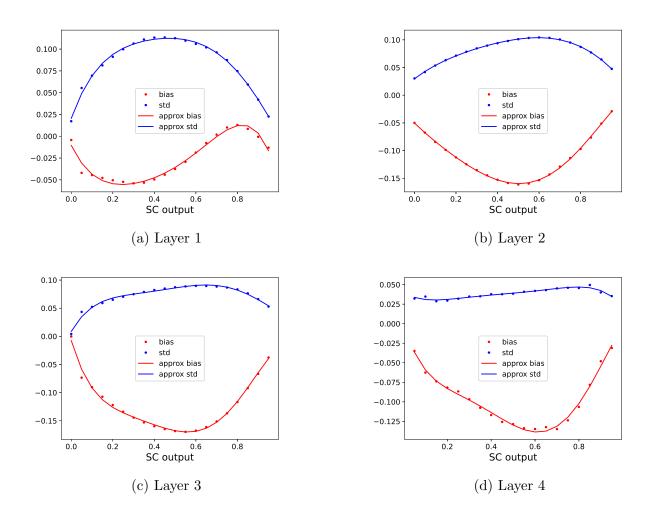

| 5.11 | Difference between outputs from stream computation and normal computation+active  | vation. 72 |

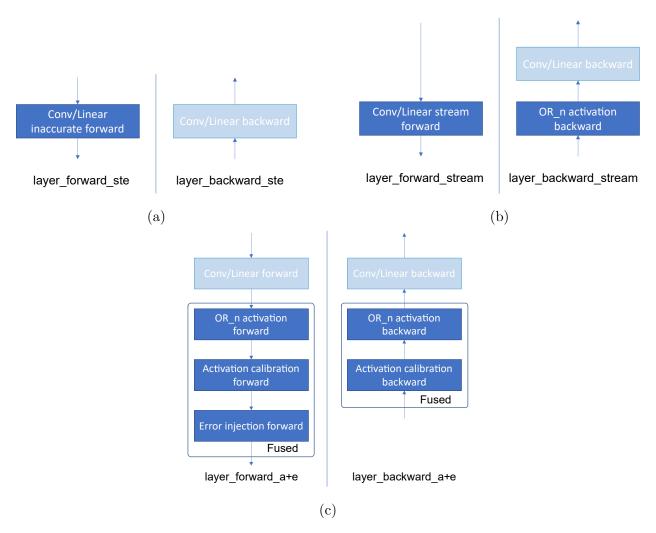

| 5.12 | Comparison between (a) vanilla STE [Ben13], (b) stream with OR_n activation       |            |

|      | and (c) a+e training step                                                         | 73         |

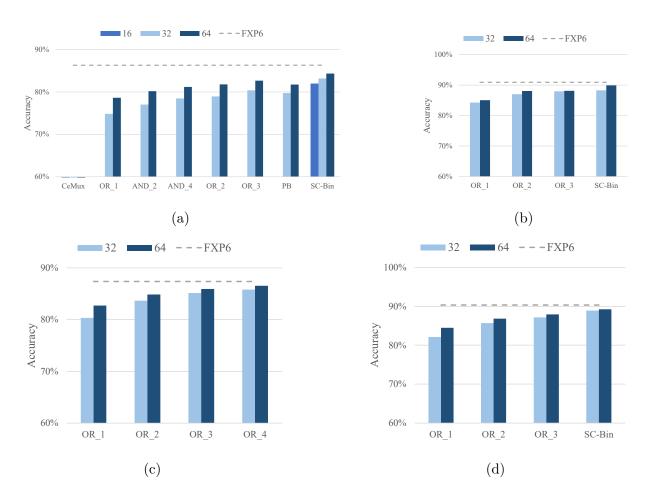

| 5.13 | Accuracy comparison for (a) TinyConv and (b) VGG-16 on CIFAR-10, (c) Resnet-      |            |

|      | 18, and (d) Resnet-34 on ImageNet. 16-bit SC-Bin only has an accuracy result      |            |

|      | for TinyConv as it does not converge for other larger models                      | 75         |

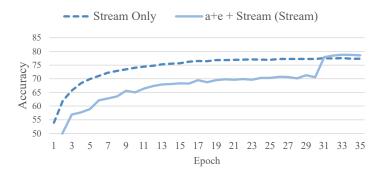

| 5.14 | Convergence behavior of stream only and a+e. The drop in accuracy at epoch        |            |

|      | 31 for a+e is when switching to using streams for the forward pass                | 79         |

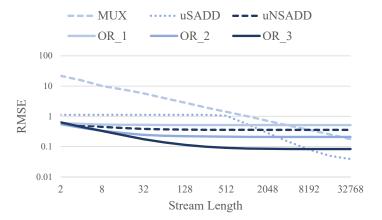

| 5.15 | Comparison of multiplexer- and OR_n-based adders' root mean squared error           |              |

|------|-------------------------------------------------------------------------------------|--------------|

|      | (RMSE) with respect to normal addition. We use sums of 1000 positive inputs         |              |

|      | with outputs having an average of 1 and a variance of 0.5                           | 82           |

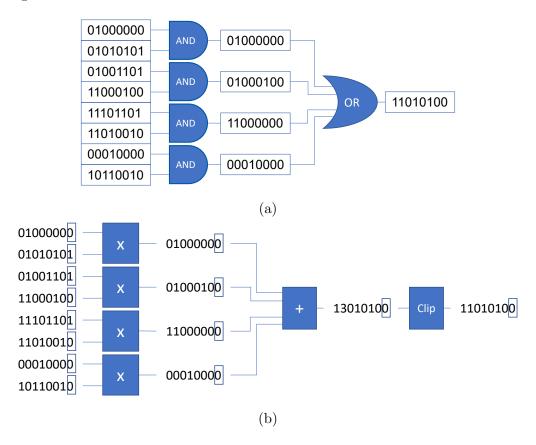

| 6.1  | Comparison between (a) SC AND-OR dot product and (b) an equivalent imple-           |              |

|      | mentation using single-bit multiply-add operations                                  | 88           |

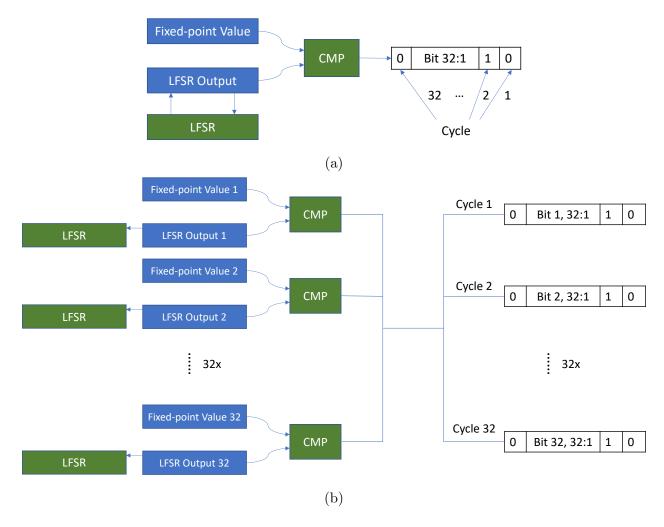

| 6.2  | Comparison between stream generation for packing in (a) bitstream and (b) input     |              |

|      | channel dimension for a single thread                                               | 90           |

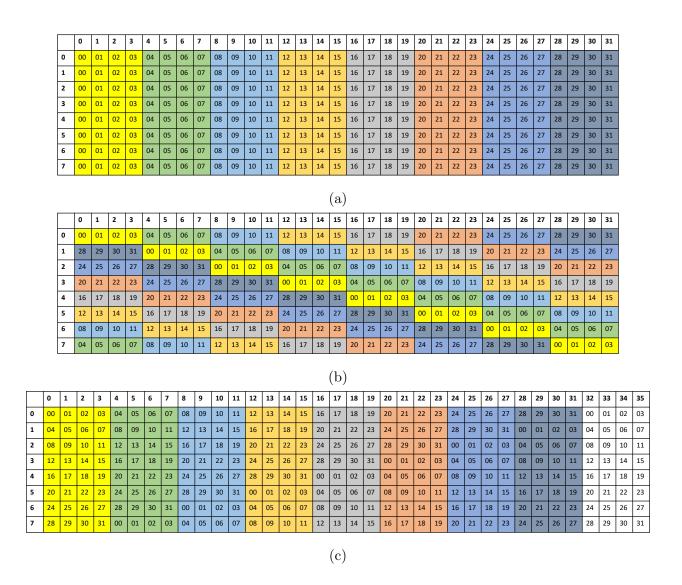

| 6.3  | (a) Naive memory layout, (b) strided memory layout used, and (c) padded mem-        |              |

|      | ory layout for an $8x32(32-bit)$ array. The colored cells are for data storage, and |              |

|      | the rest are either index (first row and column) or unfilled storage in (c). The    |              |

|      | numbers in the cell have slightly different meanings. In (a), the number repre-     |              |

|      | sents both the column index in a column-major matrix and the bank index, as         |              |

|      | the number of columns matches the number of banks. In (b), the number repre-        |              |

|      | sents the column index, and the bank index matches the column number. In (c),       |              |

|      | the number presents the bank index, and the column index matches the column         |              |

|      | number                                                                              | 94           |

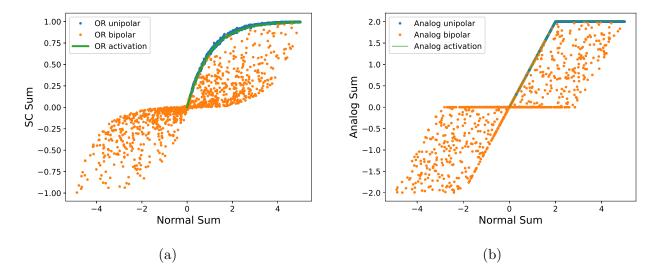

| 6.4  | Activation modeling behavior of unipolar and bipolar (a) stochastic and (b) ana-    |              |

|      | log computation. The bipolar versions performs subtraction between two unipolar     |              |

|      | (positive and negative) inputs to achieve the full range. For analog computation,   |              |

|      | the ADC saturation is modeled as a clamp at 2 in this example, and other effects    |              |

|      | (e.g. size of accumulation) are not considered                                      | 102          |

| 6.5  | Difference between outputs from stream computation and normal computation+action    | ivation. 106 |

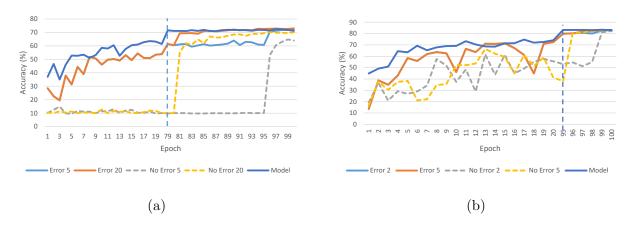

| 6.6 | Convergence behavior of TinyConv with and without error injection using (a)        |     |

|-----|------------------------------------------------------------------------------------|-----|

|     | stochastic computing and (b) approximate multiplication. Stochastic computing      |     |

|     | and approximate multiplication models are trained from scratch for 100 epochs      |     |

|     | and the first 20 epochs and the last few epochs are shown. "Error X" means         |     |

|     | training with error injection with X epochs of fine-tuning with an accurate model. |     |

|     | "No Error X" means training without error injection with X epochs of fine-tuning.  |     |

|     | "Model" means accurate modeling throughout training                                | 108 |

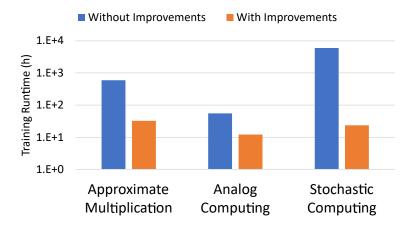

| 6.7 | End-to-end runtime improvements. Time is measured in hours required to con-        |     |

|     | verge. The "Without Improvements" results are estimated for models that are        |     |

|     | impossible to train without the improvements                                       | 112 |

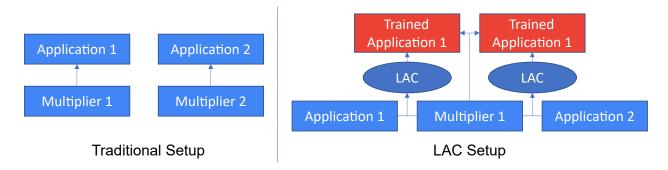

| 7.1 | Difference between traditional and LAC setups. LAC focuses on optimizing the       |     |

|     | application kernels rather than optimizing the hardware approximations             | 115 |

| 7.2 | Overview of LAC for fixed hardware                                                 | 116 |

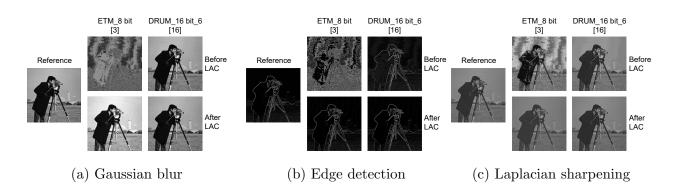

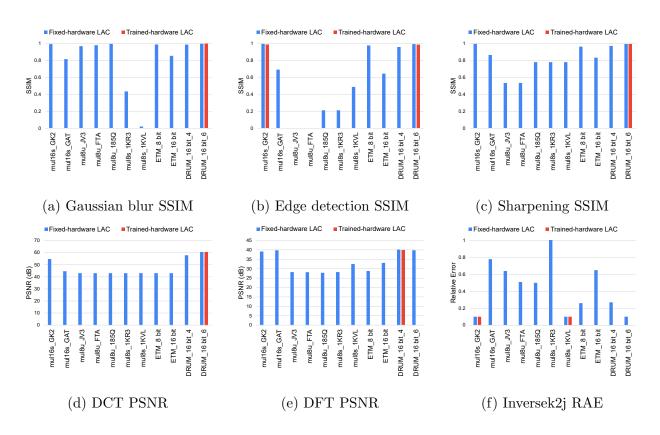

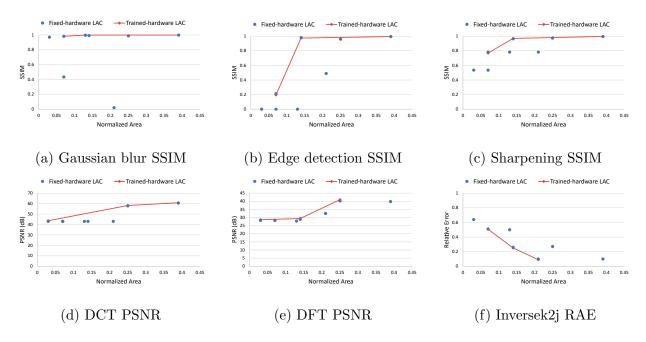

| 7.3 | Quality improvements of (a) Gaussian blur, (b) edge detection, (c) image sharp-    |     |

|     | ening, (d) JPEG compression using DCT, (e) DFT, and (f) Inversek2j                 | 121 |

| 7.4 | Quality improvements of (a) Gaussian blur, (b) edge detection, and (c)image        |     |

|     | sharpening. Figures on the right use Pareto optimal multipliers with the highest   |     |

|     | SSIM before optimization                                                           | 121 |

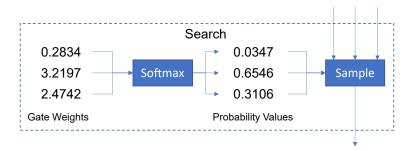

| 7.5 | Overview of LAC for trained hardware                                               | 123 |

| 7.6 | Illustration of the binarized gate used for choosing between different hardware    |     |

|     | outputs                                                                            | 123 |

| 7.7 | LAC search results of (a) Gaussian blur, (b) edge detection, (c) image sharpening, |     |

|     | (d) JPEG compression using DCT. (e) DFT, and (f) Inversek2i.                       | 126 |

| 7.8 | LAC performance-centric search results of (a) Gaussian blur, (b) edge detection, |     |

|-----|----------------------------------------------------------------------------------|-----|

|     | (c) image sharpening, (d) JPEG compression using DCT, (e) DFT, and (f) In-       |     |

|     | versek2j                                                                         | 127 |

|     |                                                                                  |     |

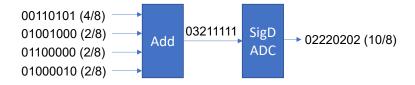

| 8.1 | Accumulation demonstration of OR-based SCIM accumulation                         | 135 |

| 8.2 | Accumulation demonstration of SD SCIM accumulation                               | 136 |

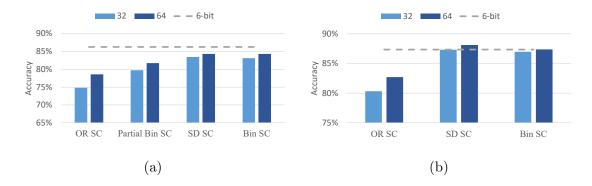

| 8.3 | Accuracy of SC with sigma-delta ADC compared to OR SC and SC with binary         |     |

|     | accumulation for (a) TinyConv on CIFAR-10 and (b) Resnet-18 on ImageNet          | 137 |

# LIST OF TABLES

| 2.1 | Weight storage requirements of different networks depending on precision            | 11 |

|-----|-------------------------------------------------------------------------------------|----|

| 2.2 | Hardware platforms used for the runtime experiments. Only the <i>Small</i> platform |    |

|     | has a DSP extension with hardware multiply-accumulate unit. All three micro-        |    |

|     | controllers are from the ST Nucleo family                                           | 21 |

| 2.3 | Benchmark models and datasets                                                       | 22 |

| 2.4 | Accuracy and network size (KB, in brackets) comparison                              | 23 |

| 2.5 | Runtime (ms) and energy (mJ, in brackets) for MNIST networks. A dash indi-          |    |

|     | cates a given model could not fit in memory                                         | 27 |

| 2.6 | Runtime (ms) and energy (mJ, in brackets) for CIFAR-10/SVHN/Speech net-             |    |

|     | works. A dash indicates a given model could not fit in memory                       | 27 |

| 3.1 | Validation accuracy of a 4-layer CNN[LSC18] for SC hardware with different          |    |

|     | training methods                                                                    | 43 |

| 4.1 | Accuracy comparison with fixed-point, other SC implementations, and so on           | 50 |

| 5.1 | Summary of various SC addition methods and works using them                         | 55 |

| 5.2 | Comparison between a full truth table and a sum transfer function. This is one      |    |

|     | possible truth table of a two-input OR_2 gate that corresponds to Candidate 6 in    |    |

|     | Tab. 5.3. This particular truth table sets the two output bits to $e = a + c + bd$  |    |

|     | and $f = b + d + ac$ respectively, assuming a, b, c, and d are the four input bits, |    |

|     | and $e$ and $f$ are the two output bits                                             | 63 |

| 5.3 | Candidate transfer functions between input and output sums for 2-input OR_2.        | 64 |

| 5.4 | Candidate transfer functions between input and output sums for 3-input OR_2.        | 65 |

| 5.5 | TinyConv Neural network accuracy of Candidate 1, 4, and 6 for OR <sub>2</sub> . Models                                                                                                                                                                        |     |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | are trained using 32-bit streams on CIFAR-10                                                                                                                                                                                                                  | 66  |

| 5.6 | LFSR seed sharing scheme demonstration                                                                                                                                                                                                                        | 76  |

| 5.7 | Array size, compute area and power, clock period, inference latency, energy, and energy improvement compared to 6-bit fixed-point, for different models and datasets with different types of SC accumulation                                                  | 77  |

| 5.8 | Iteration time comparisons between $OR_n$ and partial binary accumulation. Time is measured in s/256 images on an RTX 3090. The numbers before "PB" are the sizes of $OR$ accumulation, with smaller numbers leading to more binary accumu-                   |     |

| 5.9 | End-to-end training time comparison in hours between OR_n and partial binary accumulation. Results for OR_n and PB are estimated as they take prohibitively                                                                                                   | 78  |

|     | long to train.                                                                                                                                                                                                                                                | 80  |

| 6.1 | Operator and data format comparison between bitstream and input channel packing                                                                                                                                                                               | 89  |

| 6.2 | Accuracy benefits of using activation functions                                                                                                                                                                                                               | .01 |

| 6.3 | Activation functions for stochastic computing and analog computing. $x$ is the output of a layer before activation. $x_{pos}$ is the output of positive weights and $x_{neg}$ is the output of negative weights. Inputs are assumed to be non-negative due to |     |

|     | ReLU activation                                                                                                                                                                                                                                               | .03 |

| 6.4 | Relative multiplication and addition cost. FP32 multiplication and addition are used as the baseline. The number of operations in C++ is used as the cost value. 1                                                                                            | .04 |

| 6.5 | Accuracy impact of modeling approximate computation. "With Model" models                                                                                                                                                                                      | .04 |

| 66  |                                                                                                                                                                                                                                                               |     |

| 0.0 | Accuracy impact of error injection training                                                                                                                                                                                                                   | .07 |

| 6.7  | Training runtime and memory requirement of stochastic computing without and      |     |

|------|----------------------------------------------------------------------------------|-----|

|      | without gradient checkpointing. We use the maximum batch size achievable which   |     |

|      | is a power of 2                                                                  | 109 |

| 6.8  | Runtime impact of error injection training. Shown is the time (seconds) required |     |

|      | per epoch. Runtimes are measured on an RTX 3090 using TF32 precision and         |     |

|      | batch size=256. SC and approximate multiplication are slower due to the need     |     |

|      | to split positive and negative computations discussed in Sec. 6.2.1. Fine-tuning |     |

|      | runtime is the same as the runtime with accurate model (the "With Model"         |     |

|      | $\operatorname{column}).\ \ldots\ \ldots\ \ldots\ \ldots\ \ldots\ \ldots$        | 110 |

| 6.9  | Epochs used for training. Methods with higher accuracy require fewer epochs of   |     |

|      | fine-tuning.                                                                     | 110 |

| 6.10 | Top-1 accuracy of Resnet-18 on ImageNet                                          | 111 |

|      |                                                                                  |     |

| 7.1  | Multiplier summary. Performance numbers are normalized to 16-bit multipliers.    | 118 |

| 7.2  | Application summary                                                              | 118 |

#### ACKNOWLEDGMENTS

This dissertation is the culmination of years of work, and would not have been possible without the inspiration and guidance from a lot of people. I would like to use this as an opportunity to express my gratitude.

First, I would like to thank my advisor Prof. Puneet Gupta. None of the work in this dissertation would have been possible without his help. I am very grateful for him giving me this opportunity to study and perform research in this lab and also for his constant support and guidance throughout the many years I spent in this lab.

I would like to especially thank my lab mate, Wojciech Romaszkan. He is a collaborator for most of the works listed in this dissertation. His contributions to the performance and architectural analysis have been crucial to these works. He has also been extremely helpful throughout my life in the lab and in the various other projects that we collaborated on.

I would like to thank my undergrad mentor, Shaodi Wang. He was an alumnus of this lab and was my mentor when I worked as an undergrad. It was under his guidance that I learned the concepts of stochastic computing. The exploratory research I performed as an undergrad eventually formed the basis of this dissertation, and our work on stochastic computing using magnetic tunnel junctions formed the basis of a proposal. That proposal eventually lead to the project that funded my Ph.D. career.

I would like to thank my mentors and colleagues at ARM and Intel, where I joined as an intern. While the projects I worked on during my internships had little in common with the overall scheme of this dissertation, they both involved software optimizations to improve deep learning performance. It's through these internship experiences that I learned the value of low-level optimizations. These optimizations never became the centerpiece of my research, but they are an enabler of a lot of the experiments.

I would like to thank all my other labmates that accompanied me throughout this process. They include Weiche Wang, Saptadeep Pal, Irina Alam, Shurui Li, Alexander Graening, and Rhesa M. Ramadhan (ordered by their (prospective) graduation date). NanoCAD lab really emphasizes in-person communications, and I enjoyed working with all my labmates throughout this process. We worked in the same room, collaborated on various projects, and ate out now and then. The conversations we had throughout the years have been extremely inspirational to my research, and the various activities we participated in added variations to my otherwise straightforward Ph.D. career.

Finally, I would like to thank my parents for their continued support. It's always reassuring to know that I always have a place to return to, and they backed me up through all the difficulties I had.

#### VITA

2013–2017 B.S. (Electrical Engineering), UCLA.

2017-present Graduate Student Researcher, UCLA.

#### **PUBLICATIONS**

Wojciech Romaszkan, **Tianmu Li**, and Puneet Gupta. "3PXNet: Pruned-Permuted-Packed XNOR Networks for Edge Machine Learning." *ACM Transactions on Embedded Computing Systems (TECS)*, November 2019.

Wojciech Romaszkan, **Tianmu Li**, Tristan Melton, Sudhakar Pamarti, and Puneet Gupta. "ACOUSTIC: Accelerating Convolutional Neural Networks through Or-Unipolar Skipped Stochastic Computing." In 2020 Design, Automation & Test in Europe Conference & Exhibition (DATE), pp. 768–773, 2020.

**Tianmu Li**, Wojciech Romaszkan, Sudhakar Pamarti, and Puneet Gupta. "GEO: Generation and Execution Optimized Stochastic Computing Accelerator for Neural Networks." In 2021 Design, Automation & Test in Europe Conference & Exhibition (DATE), pp. 1–6, 2021.

Vaibhav Gupta, **Tianmu Li**, and Puneet Gupta, "LAC: Learned Approximate Computing." In *IEEE/ACM Design*, *Automation and Test in Europe*, p. 4, March 2022.

**Tianmu Li**, Shurui Li, and Puneet Gupta. "Training Neural Networks for Execution on Approximate Hardware." In *International Research Symposium on Tiny Machine Learning* (tinyML), p. 6, March 2023.

**Tianmu Li**, Wojciech Romaszkan, Sudhakar Pamarti, and Puneet Gupta. "REX-SC: Range-Extended Stochastic Computing Accumulation for Neural Network Acceleration." *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD)*, June 2023

# CHAPTER 1

### Introduction

Machine learning has seen massive developments in recent years, and state-of-the-art models have been pushing the boundary of what can be modeled using neural networks. However, model capacity has greatly outpaced the development of hardware. Popular large language models (LLMs) require a large cluster with thousands to tens of thousands of GPUs to train in a reasonable time [HBM22]. Even performing inference of the trained model can be prohibitively expensive [PA]. As a result, a lot of machine learning inference tasks run in the cloud. However, running everything in the cloud creates multiple issues. Network connectivity is a concern, and the strict power budget of resource-constrained devices can prevent the usage of relatively expensive network connections. Transmitting training and inference data over the network also creates privacy and security concerns. As a result, there is always interest in performing local inference on resource-constrained devices.

# 1.1 Computation in deep neural networks

At the core of today's high-performance machine learning models are deep neural networks. Neural networks consist of multiple layers connected in different fashions, and the way connections happen within and between layers defines the type of neural network. Multi-layer perceptrons connect layers sequentially, with an all-to-all connection within each layer. Reduced connections within layers generate convolutional neural networks (CNN) [LBB98]. Cyclic connections between layers generate recurrent neural networks (RNNs) [RM87]. Connections with themselves in a layer generate attention layers that form the backbone of

transformers [VSP17]. While neural networks come in numerous variants with the number of variants still rapidly increasing, the core computation is defined by the connections within a layer, which are made up of multiply-accumulate operations, or dot products. To improve computation efficiency, most of the computations in neural networks contain dot products of the same size, which can be mapped to matrix multiplications. Apart from linear matrix computations, neural networks also have non-linear computations between layers, also known as activation functions. This non-linear computation forms the basis of the universal approximation property of neural networks [HSW89]. Despite their importance, they are typically made up of element-wise operations where the same operation is applied to all elements (usually) equally. Compared to the dot product and matrix multiplication computations, activation functions are typically cheaper to implement, and can often be fused with dot product kernels in libraries like cuDNN and oneDNN to further reduce their impact on performance. As a result, dot products and matrix multiplications remain the dominant computation in today's neural networks.

Computations in neural networks come in two variants, training, and inference. Training refers to modifying the parameters of the neural network so that the output of the model is close to the desired output. If the desired output is manually labeled, this process is called supervised learning. An example is the ImageNet challenge [RDS15], where the model needs to create a label for a given image. During training, the label is provided as the desired output. If the desired output is not labeled, this process is called unsupervised learning. An example of unsupervised learning is the pre-training phase of language models. The popular Bidirectional Encoder Representations for Transformers (BERT) [DCL18] is pre-trained on English Wikipedia for instance. During pre-training, the model needs to predict the content of a randomly masked word in a sentence or predict whether a sentence is the correct next sentence. Unsupervised learning is sometimes not sufficient to generate a model suitable for a given task, in which case the model needs to be fine-tuned on the specific task afterward. Regardless of whether supervised or not, the training of neural networks

can be further broken down into two passes, the forward pass and the backward pass. The forward pass computes the final output and intermediate outputs of the model for a given (minibatch of) input. The final output is compared with the desired output and generates a loss value using a loss function. During the backward pass, the loss value is used to calculate the gradient of different weight values through backpropagation [RHW86]. The backpropagation step can be seen as the inverse of the computation in the forward pass. For the dot product/matrix multiplication part of the computation, the backpropagation step is separated into backward\_input and backward\_weight steps. <sup>1</sup> In the backward\_input step, the gradient with respect to the input values is computed using the output gradient value and weight values. The input gradient will then become the output gradient of the previous layer. In the backward\_weight step, the gradient with respect to the weight values is computed using the output gradient value and output value. As a result, the intermediate output values of layers need to be stored for the backward pass (there are methods to trade this memory requirement for more computation, which will be discussed in Chap. 6). After backpropagation through all layers, the weight gradients are used to update the weight values using an optimizer. Optimizer options range from simple ones like stochastic gradient descent (SGD), or adaptive ones that modify the per-weight update rate like Adam [KB14].

After training a neural network, it can then be used for inference, which refers to running the forward pass for a given prediction task.<sup>2</sup> During inference, the weights are typically fixed and don't need to be updated. As a result, the intermediate output of layers can be discarded during inference. Whereas training performs three matrix multiplications, one in the forward pass and two in the backward pass, inference only performs one. This makes neural network inference generally cheaper than training. Despite the reduced cost for a

<sup>&</sup>lt;sup>1</sup>Backpropagation through activation layers only have backward\_input step as there are no weights. Backpropagation through matrix multiplication of two input matrices (self-attention) has two backward\_input steps, as both operands of the matrix multiplication are inputs.

<sup>&</sup>lt;sup>2</sup>Generation (as is now popular with likes of Stable Diffusion [RBL21] for image generation and ChatGPT [Ope23] for text generation) can be viewed as the prediction of the next pixel or the prediction of the next word.

single input, the cost of inference can become dominant in the long run. Once trained, a single model may be used for inference for a lot more inputs than being used during training. This factor makes neural network inference acceleration important despite the apparent low cost compared to training for the same number of inputs.

Between the two variants of neural network computation, training generally requires higher-precision computation. As the range of weight and input values of a layer can change dramatically during training, floating-point number formats are generally preferred over fixed-point numbers. Inference, on the other hand, has lower precision requirements in general. Since the weight and (to some extent) input distributions are fixed during inference, fixed-point quantization generally performs well enough during inference once the range of inputs and weights is correctly adjusted.

## 1.2 Computation with reduced accuracy

As neural network inference can be the dominant computation and requires less precision than training, multiple computation methods have been proposed to improve the efficiency of neural network inference at the cost of reduced accuracy for single computation.

One line of work continues from the previously-mentioned fixed-point quantization. Compared to computation using 32-bit floating-point numbers, 8-bit quantized weights and computation reduce both computation and memory costs during inference. In terms of accuracy, 8-bit fixed-point numbers have been shown to lose only a little accuracy when quantizing from a floating-point model without training. Quantization without training is known as post-training quantization (PTQ) and allows easy deployment of floating-point models with fixed-point computation [Mig17]. For cases where training is allowed, quantization-aware training (QAT) can further improve accuracy [JKC18, ZWN16]. In the most common form, QAT performs fake quantization during part of or entire training. In a fake quantization setup, a copy of weight values is kept at high precision, which is also known as master weights.

In the forward pass, the master weights are quantized to compute layer outputs. In the backward pass, these outputs are used to compute the weight gradients using high-precision computation. The gradients are then used to update the high-precision master weight values. This setup is known as a straight-through estimator (STE) [Ben13]. Training-aware quantization further reduces the accuracy loss induced by quantization, and a lot of models lose very little to no accuracy with 8-bit quantization-aware training. With the success of 8-bit quantization, there has been continued work to push the precision further down. 4-bit quantization on weights has been shown to be sufficient for various models [BNS19]. In the extreme case, 1-bit quantization was proposed to limit both storage and computation to single bits [CHS16] at the cost of some accuracy loss.

Another line of work focuses on dropping unimportant computations in neural networks altogether, also known as pruning. As neural network training uses a first-order optimization algorithm, training convergence is typically slower and noisier compared to more traditional optimization algorithms like Newton's method which require higher-order information. As a result, there are observations that a lot of the weights in the trained neural networks are redundant, and can be effectively dropped without significantly impacting the final accuracy [HPT15]. Dropping weights in a neural network can theoretically save both the weight storage cost and the associated computation cost.

The last line of work tries to use approximate computing methods to further reduce the cost of computation. Compared to quantization which tries to perform the same operations but at lower precision or pruning which tries to remove unimportant computation, approximate computing deliberately introduces errors or uncertainties into the computation. Some examples of approximate computing include approximate arithmetic, analog computation, and stochastic computation. Approximate arithmetic tries to simplify the digital arithmetic circuits, typically multipliers, even if such simplification generates errors for certain input computations. With careful selection of the places to simplify, approximate computing can further reduce the area and power of arithmetic operations with only a small loss to model

accuracy [GSG22]. Analog computing tries to perform computations using circuits not originally designed for computation, typically memory [YJH21]. Performing computation in memory arrays offers multiple benefits. On the one hand, this saves memory movement costs, as weights are stored in the memory array and don't need to be read out. On the other hand, novel memory technologies like magnetic memory (MRAM) [POZ18] and resistive memory (RRAM) [CLX16] improve computation efficiency compared to fixed-point and floating-point computation.

Stochastic computing (SC) is another one of the approximate computing methods. SC performs computation using randomized bitstreams and is shown to be promising for neural network acceleration [SNL17]. With the stream representation, stochastic computing enables multiplications and additions using single gates. This setup significantly improves the computation density. The improved density in turn increases input value reuse during computation, which reduces memory movement requirements [RLM20]. However, these benefits don't come for free. As is obvious from the name, stochastic computing is random. Both the generation and computation of bit streams create errors, which hampers the accuracy of stochastic computing.

This thesis mainly focuses on improving the efficiency of neural network inference using stochastic computing. Apart from the implementation of SC for neural networks, this thesis will also discuss the motivations for using SC in the first place, and also discuss the application of the training techniques for SC-based neural networks on other approximate computation methods and other applications.

The thesis will be organized as follows:

• Chapter 2 will discuss 3pxnet: packed, pruned, and permuted xnor-net, which aims to achieve maximal compression of a model by combining 1-bit quantization and pruning. By performing multiple optimizations including bit packing and input channel permutation, we demonstrate further memory reduction and performance gains over model

binarization and pruning alone.

- Chapter 3 will discuss my contributions in ACOUSTIC: Accelerating Convolutional Neural Networks through Or-Unipolar Skipped Stochastic Computing. It will start with how we arrived at stochastic computing from the initial work on model binarization and pruning. Following a brief introduction to SC will be the initial implementation of an SC-based neural network, which serves as a basis for further optimizations.

- Chapter 4 will discuss my work on GEO: Generation and Execution Optimized Stochastic Computing Accelerator for Neural Networks. It includes optimizations to the generation and execution components of stochastic computing. These optimizations improve the accuracy-performance tradeoff of stochastic computing.

- Chapter 5 will discuss my work on REX-SC: range-extended stochastic computing for neural network execution. While the generation optimizations of GEO are mostly sufficient, the execution optimizations introduce multiple complications. REX-SC introduces OR-n as an alternative to execution optimization in GEO. OR-n enables more efficient modeling during training, which allows us to demonstrate the benefits of SC on larger models and more complicated datasets.

- Chapter 6 will discuss my efforts to improve the training performance for neural networks using stochastic computing and other approximate computing methods in general. This chapter discusses the difficulties faced during training along with solutions to each one of them. The introduced optimizations act as enablers for the models used in Chapter 4.

- Chapter 7 will discuss the application of the training idea to other applications and other approximate computing methods. In LAC; learned approximate computing search, we allow optimization of an almost arbitrary parameterizable application for a particular approximate hardware configuration. For a fixed approximate hardware

configuration, LAC improves application performance and allows hardware reuse. For cases where the hardware can also be changed, we enable an automatic search of the hardware configuration that finds the hardware with the best accuracy-performance tradeoff after training.

• Chapter 8 will provide a conclusion of the thesis along with some promising directions for future research.

# CHAPTER 2

# Sparse Binarized Processing <sup>1</sup>

#### 2.1 Introduction

With the increasing need for intelligence in Internet-of-things devices, there is a growing interest in deploying neural networks on mobile and edge devices. However, state-of-the-art deep learning models have sizes in tens or hundreds of megabytes and require millions of multiply-accumulate operations, making them impossible to use on heavily resource-constrained platforms.

To cope with this, various model compression schemes have been developed in recent years, chief among them, quantization and pruning [CWZ17]. Multiple works have shown that decreasing the precision of underlying computation through quantization does not affect accuracy, while significantly improving storage and runtime [VSM11, CCR13, GAG15, ZWN16, JAM17, JBB17]. In the most extreme case of precision reduction, binarization can be used without a significant drop in accuracy [CSM15, CHS16, KS16, ROR16, CHS16].

Exploiting redundancy through sparsity has been studied since the advent of neural networks [LBB98, HSW93], and recent work [HPT15] has shown over 10x compression on popular network models with the same accuracy. Although model compression through pruning significantly reduces the required computational complexity, it is hard to efficiently

<sup>&</sup>lt;sup>1</sup>This work is performed in collaboration with Wojciech Romaszkan and Puneet Gupta. This chapter contains material previously used in [RLG19]. My contributions to this work include training the models, including the fixed-point baseline and dense and sparse binarized networks, and developing the methodologies around the training and pruning components.

exploit, especially on highly-parallel hardware [YLP17]. Combining binarization and pruning is the next logical step when pushing the limit of model compression [YSN18]. Unfortunately, naively induced sparsity makes exploiting binarization-enabled parallelism prohibitively costly. To achieve actual performance gains over dense binarized implementation, a form of structured pruning needs to be employed [LZP17]. However, this enforced structure might in turn constrain pruning flexibility and negatively affect the accuracy of the network, which in itself is undesirable.

#### 2.1.1 A case for sparse XNOR networks

Table 2.2 shows available memory in some of the common embedded microcontroller platforms. This is usually limited to a few hundred kilobytes at most. Such severe resource constraints make the implementation of reasonable deep learning networks on these platforms very challenging. For example consider a few network models shown in Table 2.1. Most floating point and even 8-bit fixed point implementations are 10-1000X off from where they need to be for these platforms.

By constraining weights and activations to binary values, Binarized Neural Networks can perform 32 multiply-accumulate operations using XNOR and population count (popcount) instructions in a 32-bit processor (with appropriate "packing" of weights and activations), which gives it a potential 32x storage and computation saving compared to a 32-bit implementation (see Table 2.1). While this in itself is impressive, it might not be enough to use common models on typical embedded development platforms. Further compression is, therefore, necessary to use large models on those devices, or in the case of the most memory-constrained ones, make it feasible to deploy them at all.

In this paper, we propose a Pruned-Permuted-Packed XNOR Neural Network (3PXNet) model aiming to combine binarization and pruning in a way that is computationally efficient and does not significantly degrade accuracy. We specifically target resource-constrained edge devices and provide implementation results on a range of embedded platforms. Our pruning

Table 2.1: Weight storage requirements of different networks depending on precision.

| Network                     | Weight Memory [MB] |       |      |

|-----------------------------|--------------------|-------|------|

|                             | F32                | FP8   | XNOR |

| ILSVRC VGG-D [SZ14]         | 553.4              | 138.3 | 17.3 |

| ILSVRC AlexNet [KSH12]      | 227.5              | 56.9  | 7.1  |

| MNIST MLP [CHS16]           | 147.2              | 36.8  | 4.6  |

| MNIST MLP Small (This work) | 0.40               | 0.10  | 0.01 |

| CIFAR-10 CNN [CHS16]        | 56.1               | 14    | 1.7  |

| CIFAR-10 CNN Small [LSC18]  | 0.36               | 0.09  | 0.01 |

method allows further model size reduction and speedup compared to a binarized network. Contributions of this work are as follows.

- We develop methods to prune binarized XNOR networks aware of the need for packing them into words for computational efficiency.

- We develop training methods for such 3PXNets and open-source the training routines using PyTorch framework [PGC17].

- We show that 3PXNets offer some of the most compact networks with good accuracy: 3x-38x (22x-307x) size reduction versus dense binary (8-bit), with 0-5.2% (0.3-10.4%) accuracy drop on MNIST and 2.3-3.8% (3.5-5%) on Google Speech dataset, depending on the level of sparsity.

- We develop the *first* software implementation of sparse binarized networks and open source implementation of 3PXNets.

- We make multiple design optimizations, like loop ordering, fused kernels, and implicit padding, which result in a very low memory footprint and runtime. 3PXNet imple-

mentation can be as much as 3X (25X) faster and more energy efficient than dense binarized (8-bit fixed point) networks enabling real-time inference on IoT platforms.

#### 2.2 Related Work

#### 2.2.1 Binarized neural networks

Reducing the computational complexity of Neural Network training and inference has become a major research topic in recent years [CWZ17]. Multiple works have shown that decreasing the precision of underlying computation through quantization does not affect accuracy, while significantly improving storage and runtime [VSM11, CCR13, GAG15, ZWN16, JAM17, JBB17]. To reduce the computational complexity to its limit, researchers have proposed a variety of implementations that binarized both weights and activations [CSM15, CHS16, KS16, ROR16, CHS16]. Those Networks are commonly referred to as XNOR-Nets because multiplication can be implemented using a bitwise XNOR operation.

The promise of significant performance and storage improvements given by XNOR-Nets has resulted in multiple software and hardware implementations. Umuroglu et. al. [UFG17] have created FINN, a framework for binarized FPGA accelerators, which was further expanded to larger models by Fraser et. al. [FUG17]. Other binarized accelerators have been proposed, both targeting FPGAs [LLX17, ZSZ17, LXY17, YHF18], ASIC [ACR18, BKA18, CSB18, SNT18], and in-memory compute [JKW17, BYM18]. Yang et. al. [YFB17] have developed BMXNet, an extension of MXNet [CLL15] based on a binarized GEMM kernel. Depth-first binarized convolution implementations have also been shown for both CPU and GPU [HZL18, PTT18, MTK17]. Our implementation leverages the same depth-first approach to convolutional layers, while also incorporating coarse intra-kernel pruning.

#### 2.2.2 Weight pruning

Weight pruning in Neural Networks was first proposed over 20 years ago as a way of improving generalization and reducing computational complexity for both training and inference [CDS90, HSW93]. Recently, Han et. al. [HPT15] have shown over 10x compression on popular network models with no increase in error rates. By further coupling pruning with quantization and efficient coding, in a scheme called Deep Compression, they achieved up to 49x size reduction [HMD15]. However, deploying pruned models on highly-parallel architectures has proven problematic due to storage overhead and irregular memory access patterns of sparse matrix multiplication [YLP17, SCS17].

To make pruning more regular, multiple forms of "structured" pruning have been proposed. Lebedev and Lempitsky [LL15] proposed group-wise sparsification. Forosch et. al. [FTP15] hard-coded the sparsity patterns into the source code, achieving up to 6.88x speedup on CPUs. Anwar et. al. [AS16, AHS17] explored different granularities of pruning: feature map, kernel, and intra-kernel and introduce kernel strided sparsity. Sredojevic et. al. [SCS17] have proposed an algorithmic way of inducing regularity in sparse networks. Yu et. al. [YLP17] have developed a hardware-aware pruning method called Scalpel, which matches the coarseness of pruning to the parallelism of the underlying hardware. Our approach to packing is based on Scalpel but applied to binarized models and uses CPU bitwidth as packing granularity, while also permuting layer inputs to improve packing opportunities. Wang et. al. [WZW18] have used structured sparsity in unrolled kernels after im2col conversion. Pruning has been successfully exploited in custom accelerators by using compressed storage, skipping memory accesses, gating computation, and exploiting novel dataflows [CKE16, ZDZ16, PRM17, JDS17]. Crossbar-aware pruning has also been proposed given the recent emergence of analog crossbar-based accelerators [LDZ18].

#### 2.2.3 Sparse binary networks

While traditional implementations of ternary networks can be considered binary-sparse, they store numbers in 2-bit format and don't skip computation, which makes it impossible to capitalize on the benefits of either binarization (XNOR multiplication) or sparsity (storage and computation reduction) [ZHM16, LZL16, ALP17, MKM17, KBM17, YSN18, HGF18]. Thus we would like to make a distinction between explicitly Ternary Networks, using 2-bit representation, and Binary-Sparse Networks, leveraging XNOR multiplication and size compression, like ours. As an example of the latter, Lin et. al. [LXZ17], exploited Singular Value Decomposition to reduce kernel sizes in BNNs. Certain software and hardware implementations rely on operand-gating XNOR multiplication [HBO18, DJP18], however, they still require 2 bits of information per weight: value and mask. Li and Ren [LR18] decomposed first-layer activations into "bit-slices" and explore pruning opportunities in those, but their scheme does not extend over the whole network. Faraone et. al. [FFG17] have discussed the implications of exploiting sparsity in binarized FPGA accelerators, but not software ones.

## 2.2.4 Machine learning on embedded systems

Edge Machine Learning inference on embedded platforms has been explored in recent years as a way to remove the communication energy and latency involved in offloading it to the servers. Due to the severe memory and energy constraints of such devices, various model compression techniques have been used to make such applications feasible. Compressed Neural Network models like SqueezeNet [IHM16] and MobileNets [HZC17] have been developed, specifically targeting low memory footprints. Lai et. al. [LSC18], have developed CMSIS-NN, a software library for ARM Cortex-M microcontrollers with 8- and 16-bit fixed-point support. Microsoft is developing EdgeML, a Machine Learning library containing algorithms optimized for low storage, energy, and latency [KGV17, GSG17].

## 2.3 The 3PXNet Approach

In the following sections, we describe the principal components of the Pruned-Permuted-Packed XNOR Networks.

#### 2.3.1 XNOR networks

Binarized neural networks reduce network size by having only one bit for each weight, allowing multiple weights to be packed in a binary vector, e.g. a processor 32-bit word. By constraining the activations to binary values, they can also be packed, and 32 multiply-accumulate operations (MAC) can be performed in parallel using a bitwise XNOR and popcount instructions on the activation and weight packs in a 32-bit processor (or 64 MACs in a 64-bit processor). In theory, this can reduce weight storage and computation requirement by a factor of 32 compared to a 32-bit floating point implementation.

#### 2.3.2 Challenges in pruning XNOR networks

Dense binarized XNOR networks are relatively straightforward to pack for both weights and activations thereby getting close to the "32x" leverage [CHS16]. However, introducing sparsity on top of binarization will not necessarily improve the results further. We first illustrate how naively pruning binarized networks worsens storage and runtime. Consider a "small" binarized MLP used for MNIST (see Table 2.1) classification with the input layer of size 784, one hidden layer with 128 neurons, and an output layer of size 10, both followed by batch normalization. If we prune it without any constraints and store the sparse weight matrix using compressed-sparse-row (CSR) format, binary weight packing and "SIMD" XNOR multiplication cannot be leveraged easily. We refer to this scheme as Naively-Pruned (NP) network. If the number of non-zero weights for each kernel is constrained to be the same multiple of 32, binary weights can now be packed to save storage, but activations need to be fetched individually and packed separately for each kernel during computation. We refer

to this scheme as Naively-Pruned, Packed Network (NPP). NPP scheme has two advantages over NP in terms of storage overhead. First is packing weights into binary vectors instead of storing values individually. Second is getting rid of row extent values in the CSR format - having the same number of packs per kernel means that only one row extent value per layer needs to be stored. This will have a more profound impact on high levels of sparsity, because while the number of column indices goes down with sparsity, the number of rows, and therefore row extents stays the same. Figure 2.1 shows the total storage required for NP and NPP implementations, compared to a dense implementation. NPP offers significant storage reduction over NP, mainly through a reduction in weight storage itself. However, to break even with Dense XNOR, sparsity levels of over 90% and 95% are required for NPP and NP respectively.

Figure 2.1: Storage requirements for Dense, NP, and NPP XNOR "small" MNIST MLP for varying levels of sparsity.

While NPP allows for packing non-zero weights, there is no easy way to leverage input packing. As runtime is usually a concern for convolutional layers, we implemented both Dense and NPP kernels for the Large CNN model (Table 2.3) for CIFAR-10. Even with sparsity set to 87.5% for each convolutional layer, except for the first one, which is kept as dense Binary-Weight (BWN - using full-precision activations and binarized weights), the NPP version is 15X-29X slower compared to the unpruned dense XNOR Net on the different convolutional layers, running on a Raspberry Pi 3. This clearly shows that naively pruning

binarized networks, even with packing, is not beneficial at best, and possibly detrimental to both their size and runtime.

#### 2.3.3 Pruning a packed XNOR network

To make the inference of pruned binarized neural networks more efficient, inputs (activations) need to be fetched in packs, and those packs need to work for all kernels in a layer. This leads us to constrain the non-zero, or "active", weights of each kernel to packs of 32 consecutive positions. These 32-bit packs are aligned across all kernels of a layer so that the activations only need to be packed once. This packing constraint reduces the number of indices to store by a factor of 32 compared to NPP implementation.

Forcing the packing constraint reduces the flexibility of the network, and can result in excessive pruning in some packs and insufficient pruning in others. To alleviate this effect, we propose to permute the weight matrix so that weights inside the 32-bit packs are more likely to be all zeros in the ternary network. Figure 2.2 illustrates the effect of permutation on packing for a pack size of 4. A similar approach is also used in [LDZ18] albeit in the context of crossbar neuromorphic systems. Weight permutations are performed on input channels (NI) of a fully-connected or convolutional layer. For a convolutional layer with weight shape (KN, KZ, KY, KX), the weight is first flattened in all dimensions except KZ to (KN-flat, KZ), and then treated as a fully-connected layer.

Permutation tries to group similar input channels into packs of 32 in a method resembling Prim's algorithm. Before grouping, weights are first ternarized to  $\{-1,0,+1\}$ . For each pack, a random input channel is chosen as starting point. A similarity score is calculated by counting the overlap of 0 positions between the existing input channels in the pack and all other channels that have not been grouped, and the channel with the most overlap is added to the pack. If a group has both 0s and  $\{-1, +1\}$  values in a position, it is considered as a non-zero position, as it's unclear if weights in the pack will be pruned or not, and either choice will result in some weights being forced to change. On the other hand, positions filled

Figure 2.2: Pruning with packing constraint of 4 bits a) without permutation, b) with permutation

with 0s in a pack will be pruned, and the pruning action will not force any weight change. Once a pack is filled, another random input channel is chosen as the starting position for the next pack. This process continues until all input channels are grouped into packs. Input channel permutations can be directly translated to output channel reordering of the previous layer, so it is completely free in terms of inference except for the first layer. Figure 2.3 shows the effect of using permutation in a small MLP, where maximal benefit (¿4%) is observed with very high sparsity.

Figure 2.3: Comparison of training results with and without permutation for different sparsities.

#### 2.3.4 Training 3PXNet

Network pruning is usually performed by training a dense network and then deleting some edges or kernels. Since 0 cannot be represented in a binarized network, and the binary values contain no information about the importance of each weight, we start the training with ternary weights to introduce zero values. The training algorithm is adapted from the one in [CHS16] where full-precision weights are kept during training and binarized during inference, except that the weights are ternarized using a threshold function instead of binarized.

Listing 2.1: Pseudocode for calculating threshold for NPP.

```

weight_sorted = sort(weight, descending=True)

index = ceil((1-sparsity)*size/word_width) * word_width

thres = weight_sorted[index-1]

```

The threshold used is calculated using Algorithm 2.1. The weight tensor is first flattened and sorted based on the floating point values. The threshold value is then chosen to make sure that the sparsity roughly aligns with the sparsity constraint of that layer, and that the number of active weights aligns with the word width of the processor (typically set to 32). The result of this phase of training follows the NPP scheme, which allows efficient storage of weights but requires high indexing overhead. We then permute the weight matrices using the method mentioned above and enforce the packing constraint.

Listing 2.2: Pseudocode for calculating threshold for packed pruning.

```

weight_split = split(weight, split_size=word_width)

// For every split weight pack

for sp = 0 to size/word_width

weight_sum[sp] = sum(abs(weight_split[sp]))

weight_sorted = sort(weight_sum, descending=True)

index = ceil((1-sparsity) * size / word_width)

thres = weight_sorted[index-1]

```

Similar to the NPP phase, a threshold is calculated using Algorithm 2.2 to determine the packs to prune. For each kernel in the weight matrix, we split the weight values into packs aligned to the word width of the processor, and sum the absolute value of weights inside each pack. We then calculate the threshold so that the sparsity roughly matches the sparsity requirement of the layer, and prunes away the packs with sums below the threshold. For packs that are not pruned, the weights inside are forced into  $\{-1, +1\}$ , even if they were originally 0. Before pruning is fixed, the pruned packs can still be unpruned if the sum of another pack drops lower than the pruned pack. The network is trained for a few more epochs to determine which packs to prune. Finally, the packs to be pruned are fixed, and the model is fine-tuned to further improve accuracy. The final pruned, permuted and packed binarized network is referred to as 3PXNet.

As shown in Figure 2.3, forcing the packing constraint reduces network accuracy compared to unconstrained pruning, and permutation cannot fully recover accuracy loss. Permutation of inputs changes the allowed topology of the final network, which is the case for MLPs. For CNN we are not pruning the input layer, so permutation doesn't change the achievable topology. Because we are permuting entire kernel planes, permutation is also more restrictive for convolutional layers. Immediately after permuting, packing, and pruning a trained network, permutation has a significant advantage in accuracy (as much as 20% from 23.0 to 43.2%) but we fine-tune the network after permutation and it largely recovers irrespective of permutation indicating that the networks have significant redundancy unless the sparsity is very high (¿90%). Because of the negligible effect of permutation on training and inference runtime, all networks are trained with and without permutation, and the better-performing one is chosen as the result.

## 2.4 Experimental Setup

Hardware and software platforms, benchmark datasets, and neural network architectures we use for our experiments are outlined below.

#### 2.4.1 Platforms

We test our implementation on three different embedded development platforms from the STM Nucleo family [STM18], and a Raspberry Pi, with the configurations shown in Table 2.2.

Table 2.2: Hardware platforms used for the runtime experiments. Only the *Small* platform has a DSP extension with hardware multiply-accumulate unit. All three microcontrollers are from the ST Nucleo family.

| Name          | Model    | SRAM<br>(KB) | Flash (KB) | Core<br>Type | Clock<br>(MHz) |

|---------------|----------|--------------|------------|--------------|----------------|

| NUC Large     | F746ZG   | 320          | 1024       | ARM CM7      | 216            |

| $NUC\ Medium$ | F103RB   | 20           | 128        | ARM CM3      | 72             |

| $NUC\ Small$  | F031K6   | 4            | 32         | ARM CM0      | 48             |

| Name          | Model    | L2           | DRAM       | Core         | Clock          |

|               |          | (MB)         | (GB)       | Type         | (GHz)          |

| RPi           | Model B+ | 2            | 1          | ARM CA53     | 1.2            |

#### 2.4.2 Benchmarks

We evaluate our approach using two fully-connected networks (MLP) and a small convolutional neural network (CNN) on the MNIST dataset, and two convolutional neural networks on CIFAR-10 and SVHN dataset as shown in Table 2.3. All datasets are image classification datasets with 10 classes. MLP-Large (MLP-L) and CNN-Large (CNN-L) are used in [CHS16]. CNN-Medium (CNN-M) uses the same convolutional layers as CNN-L but only has

one fully-connected layer. CNN-Small (CNN-S) is a modified version of LeNet in [LBB98], and MLP-Small (MLP-S) is a minimally sized MLP with one hidden layer. We also tested the same CNN-M for Google Speech Command dataset [War18]. Networks are trained with PyTorch 0.4.1. All models are trained on the training set provided, and accuracies are measured on the testing sets. We used Adam optimizer [KB14] for training, with a batch size of 256 and an initial learning rate of 0.001.

Table 2.3: Benchmark models and datasets

| Dataset       |        | Model          | Architecture               |

|---------------|--------|----------------|----------------------------|

|               | MLP    | Large [CHS16]  | 784-4096-4096-4096-10      |

|               | MILIF  | Small          | 784-128-10                 |

| MNIST         |        |                | 32CONV5-MP2                |

|               | CNN    | Small          | 32CONV5-MP2                |

|               |        |                | 10FC                       |

| CIEAD 10      |        | I aman [CHC16] | $128CONV3 \times 2 - MP2$  |

| CIFAR-10      | CONTAC | Large [CHS16]  | $256CONV3 \times 2 - MP2$  |

| SVHN          | CNN    | Medium         | $512CONV3 \times 2 - MP2$  |

| Speech[War18] |        | Medium         | $(1024FC \times 2) - 10FC$ |

#### 2.4.3 Baseline

On Nucleo boards, we use the ARM CMSIS-NN [ARM19], version 5.3.0 optimized for Cortex-M processors. On Raspberry Pi we use Arm Compute Library [ARM18], version 18.03, with NEON extension enabled for a fair comparison with 3PXNet. For both CMSIS-NN and Compute Library we use 8-bit precision:  $q7_{-}t$  and QS8 datatypes respectively. The first layer in CNNs is implemented using CMSIS-NN/CL routines with binarization overhead since they are not packed and sparsified. All results are generated for a batch size of B=1. Larger batch sizes increase storage requirements and can make the models even more prohibitive to deploy on resource-constrained devices.

#### 2.5 Results and Discussion

We discuss results for 3PXNet accuracy separately from performance as only the latter depends on the hardware platform.

#### 2.5.1 Accuracy & model size

Table 2.4: Accuracy and network size (KB, in brackets) comparison.

| Dataset                | MNIST          |               |                    | CIFA           | R-10           | SV             | Speech             |                |

|------------------------|----------------|---------------|--------------------|----------------|----------------|----------------|--------------------|----------------|

| Model                  | MLP-L          | MLP-S         | CNN-S              | CNN-L          | CNN-M          | CNN-L          | CNN-M              | CNN-M          |

| 8-bit                  | 98.67% (36.9k) | 98.28% (102)  | 99.42% (32.7)      | 92.52% (14.1k) | 92.51% (4.69k) | 95.65% (14.1k) | 95.15% (4.69k)     | 97.87% (4.70k) |

| XNOR                   | 98.40% (4.64k) | 93.15% (13.1) | 97.83% (4.46)      | 89.07% (1.80k) | 88.29% (592)   | 95.03% (1.80k) | 95.00% (592)       | 96.64% (591)   |

| $3PXNet_{low}$         | 98.37% (421)   | 90.35% (3.96) | $96.60\% \ (1.66)$ | 84.74% (257)   | 82.49% (98.8)  | 93.51% (257)   | $92.57\% \ (98.8)$ | 94.32% (97.6)  |

| 3PXNet <sub>high</sub> | 96.58% (120)   | 87.93% (2.08) | $96.27\% \ (1.46)$ | 81.40% (143)   | 78.28% (61.7)  | 92.25% (143)   | 90.61% (61.7)      | 92.81% (60.5)  |

Figure 2.4 compares accuracy vs. model size of 3PXNet to a dense binarized network eBNN [MTK17]. 3PXNet achieves up to 4X (2.5X) reduction in MLP (CNN) model size with the same or better accuracy than eBNN. While both implementations use quantization, for eBNN, additional size compression comes from tweaking the network structure itself, whereas for us it comes from pruning.

Figure 2.4: Accuracy vs. Memory tradeoff compared to eBNN and dense XNOR.

Training results are shown in Table 2.4. Each network is trained with two sparsities, and the size of the network is shown in parenthesis next to accuracy. For most models, the