# Scalable High Performance Memory Subsystem with Optical Interconnects

By

#### Pouya Fotouhi Dissertation

Submitted in partial satisfaction of the requirements for the degree of

DOCTOR OF PHILOSOPHY

in

Electrical and Computer Engineering

in the

Office of Graduate Studies

of the

University of California

**Davis**

Approved:

S.J. Ben Yoo, Chair

Venkatesh Akella

Jason Lowe-Power

Committee in Charge

2021

Copyright © 2021 by

Pouya Fotouhi

All rights reserved.

# Contents

|   | List | of Figur | res                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | V    |

|---|------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|   | List | of Table | es                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | vii  |

|   | Abst | tract    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | viii |

|   | Ack  | nowledg  | gments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ix   |

| 1 | Intr | oductio  | n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1    |

| 2 | Bacl | kground  | il and the state of the state o | 4    |

|   | 2.1  | Micro    | ring Resonators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4    |

|   |      | 2.1.1    | Optical Buses with MRs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6    |

|   |      | 2.1.2    | Broadband Ring Resonators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6    |

|   | 2.2  | Arraye   | ed Waveguide Grating Router                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7    |

|   |      | 2.2.1    | Achieving High Node-to-node Bandwidth in AWGRs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 9    |

|   |      | 2.2.2    | AWGRs vs. State-of-the-art SiPhs Interconnects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 11   |

| 3 | Pho  | tonic In | terconnects for Large-scale 2.5D Integrated Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 13   |

|   | 3.1  | 2.5D I   | ntegrated Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16   |

|   |      | 3.1.1    | 2.5D Integration: Opportunities and Challenges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 16   |

|   |      | 3.1.2    | Using Silicon Photonics To Overcome Design Challenges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 17   |

|   | 3.2  | AWGF     | R-enabled Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 18   |

|   |      | 3.2.1    | Bipartite Graphs with AWGRs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 19   |

|   |      | 3.2.2    | All-to-all Connectivity with AWGR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20   |

|   |      | 3.2.3    | AWGRs vs. State-of-the-art SiPh Fabrics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 21   |

|   | 3.3  | Metho    | dology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 23   |

|   |      | 3.3.1    | Experimental Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 24   |

|   |      | 3.3.2    | NoCs Under Investigation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 25   |

|   | 3.4  | Evalua   | ation Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 26   |

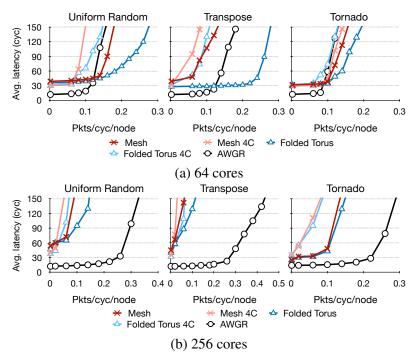

|   |      | 3.4.1    | Synthetic Traffic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 26   |

|   |      | 342      | Application Traffic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 28   |

|   |      | 3.4.3     | Discussion                                                       | 29 |

|---|------|-----------|------------------------------------------------------------------|----|

|   | 3.5  | Conclu    | asion                                                            | 31 |

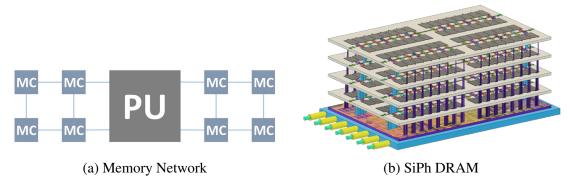

| 4 | Opti | ically-Ir | nterconnected Memory Networks                                    | 32 |

|   | 4.1  | Hybrid    | Memory Cubes                                                     | 34 |

|   |      | 4.1.1     | Design Challenges                                                | 35 |

|   | 4.2  | Silicon   | Photonics for Processor-to-MC Communication                      | 36 |

|   | 4.3  | Relate    | d Work                                                           | 36 |

|   | 4.4  | Propos    | sed Solution                                                     | 37 |

|   | 4.5  | Evalua    | tion                                                             | 40 |

|   |      | 4.5.1     | Methodology                                                      | 40 |

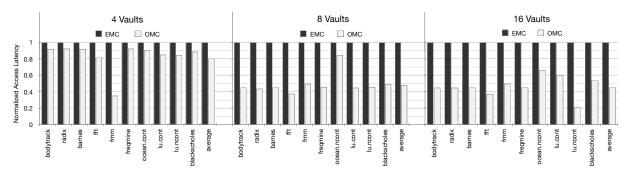

|   |      | 4.5.2     | Benchmarking Results                                             | 41 |

|   |      | 4.5.3     | AWGR vs. Alternative SiPh Interconnects                          | 43 |

|   | 4.6  | Conclu    | asion and Future Work                                            | 46 |

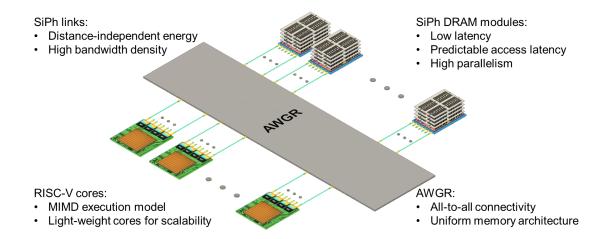

| 5 | Scal | able Ch   | hiplet-based Uniform Memory Architectures with Silicon Photonics | 48 |

|   | 5.1  | Chiple    | t-based Systems: Challenges and Opportunities                    | 51 |

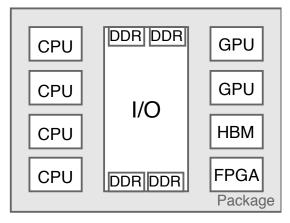

|   |      | 5.1.1     | Packaging and Interconnect Technologies                          | 52 |

|   |      | 5.1.2     | Packaging: Implications on System Design                         | 55 |

|   |      | 5.1.3     | Opportunities with Silicon Photonics                             | 57 |

|   | 5.2  | Scalab    | le Chiplet-based Uniform Memory Architecture                     | 58 |

|   |      | 5.2.1     | Addressing the Interconnect Challenge                            | 59 |

|   |      | 5.2.2     | Addressing the NUMA Challenge                                    | 60 |

|   |      | 5.2.3     | Addressing Disintegration Limits                                 | 61 |

|   |      | 5.2.4     | Addressing the Packaging Challenge                               | 62 |

|   | 5.3  | Metho     | dology                                                           | 64 |

|   | 5.4  | Simula    | ation Results                                                    | 67 |

|   |      | 5.4.1     | Synthetic Workloads                                              | 67 |

|   |      | 5.4.2     | Application Workloads                                            | 68 |

|   |      | 5 4 2     | Discussions                                                      | 70 |

|   | 3.3 | Concil   | ISION                                                          | 12 |

|---|-----|----------|----------------------------------------------------------------|----|

| 6 | HTA | A: A Sca | nlable High-Throughput Accelerator for Irregular HPC Workloads | 73 |

|   | 6.1 | HTA -    | Background, Rationale, and Design                              | 75 |

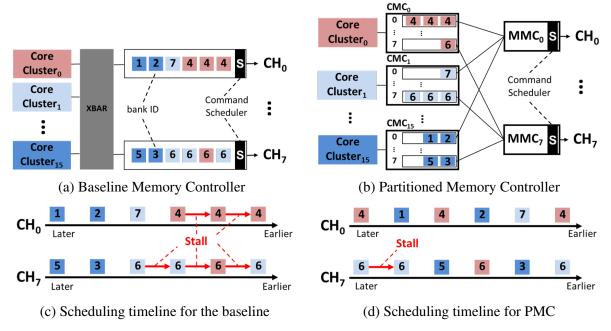

|   |     | 6.1.1    | Partitioned Memory Controller                                  | 77 |

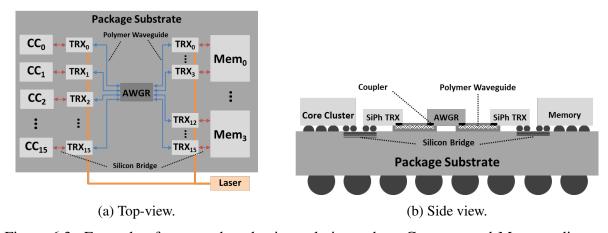

|   |     | 6.1.2    | Interconnect                                                   | 80 |

|   |     | 6.1.3    | Packaging                                                      | 81 |

|   |     | 6.1.4    | HTA Architecture                                               | 82 |

|   | 6.2 | Metho    | dology                                                         | 84 |

|   |     | 6.2.1    | System Comparisons                                             | 84 |

|   |     | 6.2.2    | Simulations                                                    | 85 |

|   | 6.3 | Evalua   | tion                                                           | 86 |

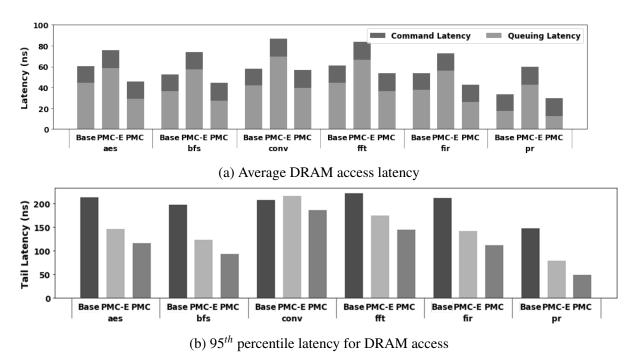

|   |     | 6.3.1    | Evaluation of Partitioned Memory Controller                    | 86 |

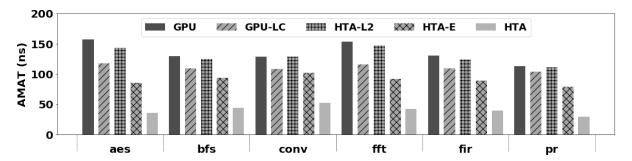

|   |     | 6.3.2    | Evaluation of HTA                                              | 88 |

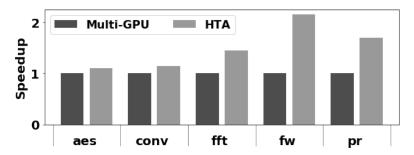

|   |     | 6.3.3    | Comparison with Multi-GPU systems                              | 89 |

|   | 6.4 | Conclu   | asion                                                          | 91 |

| 7 | Con | clusions | s and Future Work                                              | 92 |

|   | 7.1 | Conclu   | isions                                                         | 97 |

# List of Figures

| 2.1 | Reference SiPhs Optical Link                            | 5  |

|-----|---------------------------------------------------------|----|

| 2.2 | Optical Buses with Microrings                           | 6  |

| 2.3 | AWGR Structure and Switching Functionality              | 7  |

| 2.4 | Bidirectional AWGR                                      | ç  |

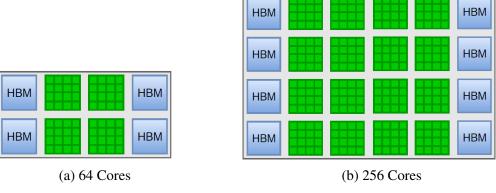

| 3.1 | Example Interposer-based systems                        | 16 |

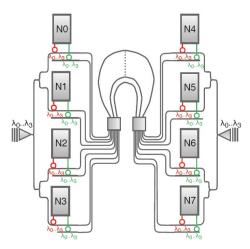

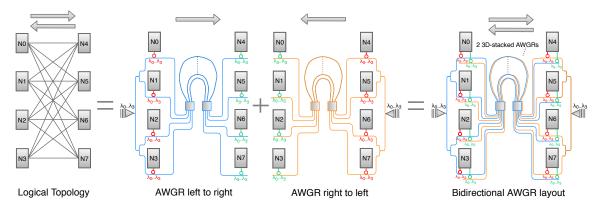

| 3.2 | Bipartite Graph with two Unidirectional AWGRs           | 19 |

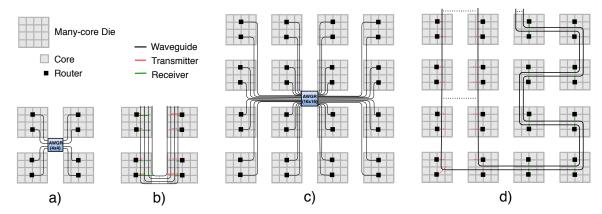

| 3.3 | NoC Layout with Optical Buses and AWGR                  | 21 |

| 3.4 | Average Packet Latency                                  | 26 |

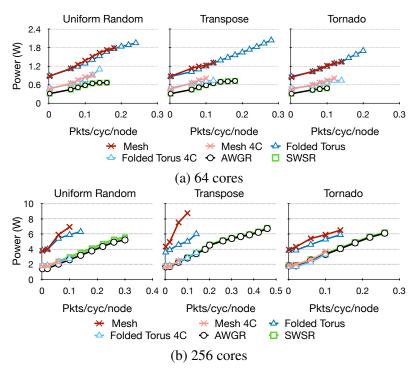

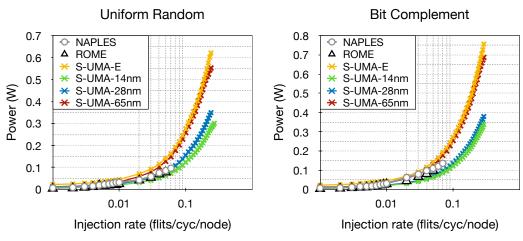

| 3.5 | Power Consumption                                       | 27 |

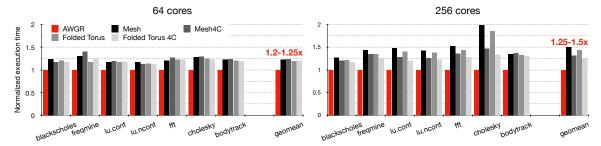

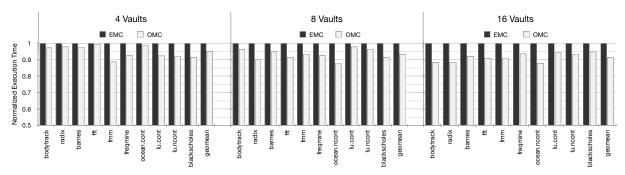

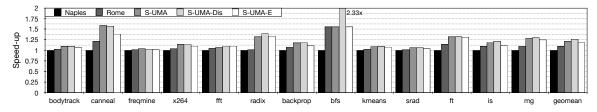

| 3.6 | Application Execution Time                              | 28 |

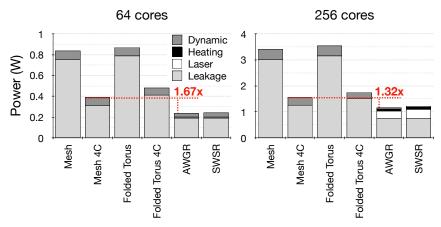

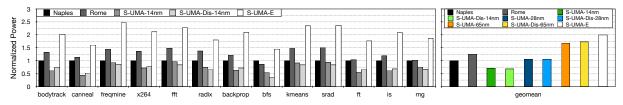

| 3.7 | Power Breakdown                                         | 29 |

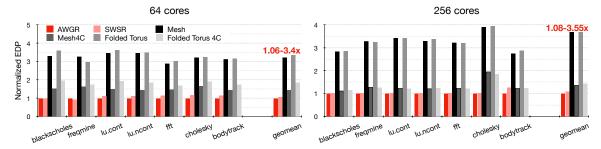

| 3.8 | Energy-Delay-Product                                    | 30 |

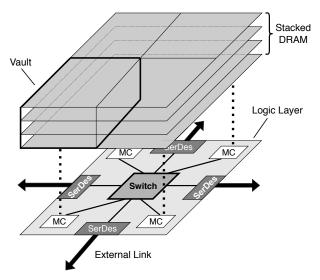

| 4.1 | Structure of a Memory Cube                              | 34 |

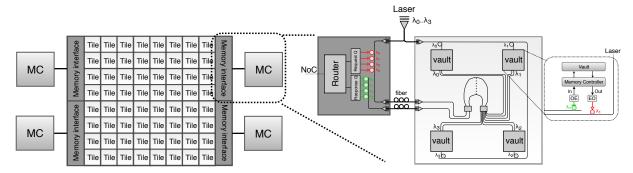

| 4.2 | Target System                                           | 38 |

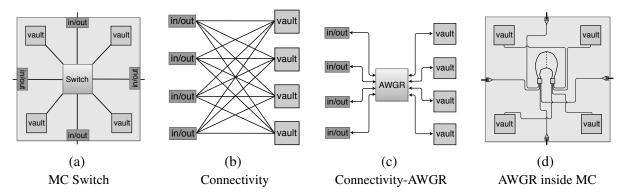

| 4.3 | Memory Cube with an AWGR                                | 39 |

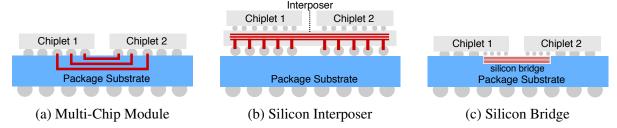

| 4.4 | DRAM Access Latency                                     | 42 |

| 4.5 | Application Execution Time                              | 42 |

| 4.6 | DRAM Access Energy                                      | 43 |

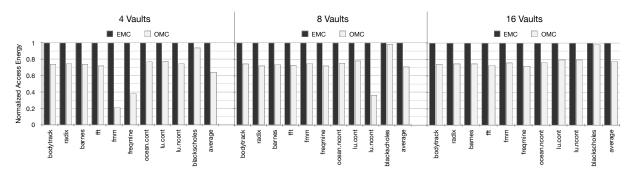

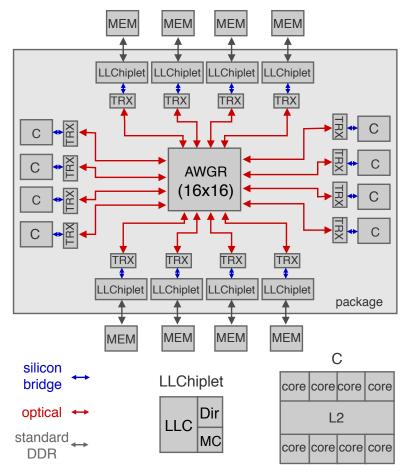

| 5.1 | Example of a Heterogeneous Chiplet-based System         | 52 |

| 5.2 | State-of-the-art for Chiplet-to-chiplet Interconnection | 53 |

| 5.3 | Target System                                           | 59 |

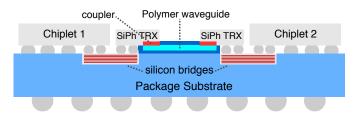

| 5.4 | Optically-interconnected Chiplets                       | 62 |

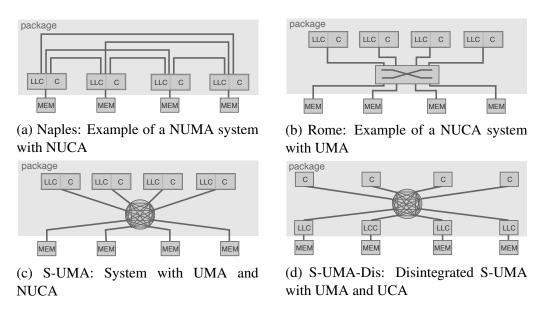

| 5.5 | Logical Topologies of Chiplet-based Systems             | 64 |

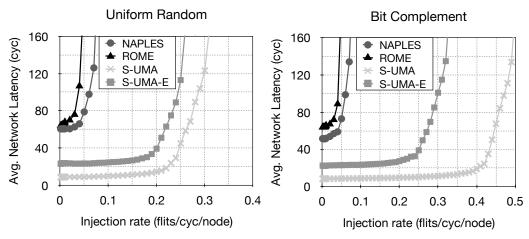

| 5.6 | Average Network Latency vs. Injection Rate              | 67 |

| 5.7 | Power Consumption vs. Injection Rate                    | 68 |

| 5.8 | Speed-up                                                | 69 |

| 5.9 | Power Consumption                      | 70 |

|-----|----------------------------------------|----|

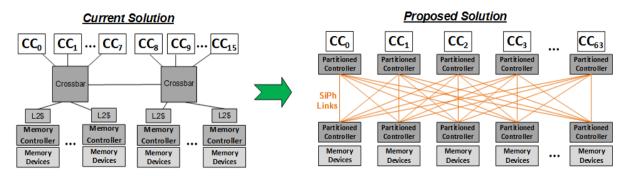

| 6.1 | Proposed Memory System                 | 75 |

| 6.2 | Working Example of PMC                 | 78 |

| 6.3 | Example of Proposed Packaging Solution | 81 |

| 6.4 | DRAM Performance                       | 87 |

| 6.5 | Average Memory Access Time             | 88 |

| 6.6 | HTA vs. Multi-GPU systems              | 90 |

| 7.1 | Optically Interconnected Memory System | 93 |

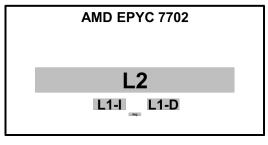

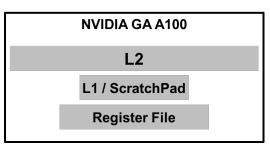

| 7.2 | Memory Organization in CPUs vs. GPUs   | 94 |

| 7.3 | Data-Driven Graph Processor            | 96 |

# LIST OF TABLES

| 3.1 | System Configuration                                  | 24 |

|-----|-------------------------------------------------------|----|

| 4.1 | SiPh Interconnect Fabric Comparisons                  | 44 |

| 5.1 | Properties of State-of-the-art Integration Techniques | 55 |

| 5.2 | System Configurations                                 | 65 |

| 5.3 | SiPh Device Parameters                                | 66 |

| 6.1 | Simulation Parameters                                 | 84 |

#### ABSTRACT

#### Scalable High Performance Memory Subsystem with Optical Interconnects

Data movement has become a limiting factor in terms of performance, power consumption, and scalability of high-performance compute nodes with increasing numbers of processor and memory systems. Optical interconnects enabled by Silicon Photonics could not only overcome this limitation but also change the way we think about system architectures and memory hierarchies. This dissertation aims to introduce and evaluate scalable high performance computing architectures based on optical interconnects. This dissertation presents the motivation and background, architecture design, and evaluation results for the following case studies:

Investigating the design challenges in large-scale many-core processors, the impact of interconnection fabric on the overall system performance and power consumption, and how Silicon Photonics can alleviate system constraints.

Studying off-chip memory networks capable of providing HPC compute nodes with terabytes of memory capacity by interconnecting several 3D stacked DRAM modules through a packet-switched network interface. Replacing legacy interconnects with sophisticated optical networks could significantly reduce memory access time and energy - a largely unexplored research area.

Addressing the scaling limitations in chiplet-based systems, in particular, large inter-chiplet non-uniform latencies, distance-related energy overheads, and limited Input-Output (IO) bandwidth, and exploiting the properties of optical interconnects to propose a scalable uniform memory architecture.

Rethinking the architecture of state-of-the-art high-throughput accelerators, the impact of memory access latency variations on the overall performance and system design, and the key challenges in scaling memory and compute capacity in these systems. A new architecture is proposed to reduce the contention within the memory system with the help of a partitioned memory controller and an all-to-all passive optical interconnect that is amenable for a 2.5D based implementation using off-the-shelf memory modules.

#### ACKNOWLEDGMENTS

I would like to thank Professor Yoo for giving me the opportunity to be part of his dynamic research team at UC Davis. This multi-dimensional learning experience would benefit my career without any doubts.

I owe my gratitude to my committee members Professor Akella and Professor Lowe-Power. Professor Akella was exactly the advisor I needed to close the gap between the architectural ideas and discussions at the technology level. Looking back at my interactions with Jason, I cannot imagine a better mentor for this chapter of my life. I am truly grateful for having the opportunity to work with Jason as any aspect of my technical character is influenced and improved by him.

I would like to thank my colleagues in UC Davis, Dr. Roberto Proietti, Dr. Sebastian Werner, Xian Xiao, and Marjan Fariborz for fruitful discussions and collaborations over the years.

Finally, I would like to thank my family for their support along the way. To my parents, Farideh and Fereidoun, thank you for your ever-present support in every step. To my wife, Elnaz, thank you for being there in all the ups and downs. Without your consistent encouragement I could not achieve my academic goals.

# **Chapter 1**

# Introduction

Modern High-Performance Computing (HPC) systems exploit increasing numbers of interconnected heterogeneous processor and memory systems to achieve peta-FLOP performance goals [1, 2]. For example, exascale computing initiatives such as Frontier and El Capitan announced by the US government recently are expected to have thousands of CPU and GPU nodes to meet their performance targets. Meanwhile, we are on the threshold of an exponentiallygrowing data-driven transformation of the entire economy. Running data-intensive HPC applications on heterogeneous systems in a distributed fashion ties the overall performance of the system to the cost and efficiency of data movements.

Moreover, growing data sets in modern workloads are driving the need for higher processing power and memory bandwidth/capacity in HPC systems. Unfortunately, the slowing down of Moore's law reduces the ability to attain higher processing power and memory capacity within a single compute node ("scale-up") for each generation of silicon technology, forcing system designers to add compute nodes ("scale-out") to satisfy performance demands. Scaling-out, however, leads to distributed memory architectures with compute nodes operating in different address spaces, and requires explicit synchronization through software (e.g. message passing). Again, this approach results in significant performance and energy overheads for data movement between compute nodes - a key challenge in current HPC systems. Scaling-up shared memory architectures within a single address space, on the other hand, allows hardware-managed coherence which is significantly faster and allows programmers to focus on what matters for parallel speed-ups rather than synchronization. Moreover, the cost of providing hardware coherence

(i.e., traffic, storage cost for tracking sharers, latency, and energy) is generally considered to scale gracefully with the core count for hierarchies in modern systems [3]. Given the technological limitations of electrical interconnects in terms of link bandwidth, link charge time, attainable radix, and energy consumption, the interconnect fabric has become a bottleneck in HPC systems [4].

Silicon Photonics (SiPh) offers high-bandwidth distance-independent links within a lower power envelope and potentially enabling flatter topologies for higher performance. Moreover, SiPh devices can exploit Wavelength-Division Multiplexing (WDM) to perform wavelength-selective routing which allows one node to be connected to multiple other nodes through a single optical IO pin (addressing them on different wavelengths), enabling high-radix low-diameter networks with high bandwidth density.

While SiPh manufacturing process is not as mature and largely adopted as standard CMOS, SiPh manufacturing and photonic integrated circuit design kits (PDKs) have seen significant growth and investment in the past ten years, now allowing low-cost SiPh integration [5]. Among several SiPh fabrics, the Arrayed Waveguide Grating Router (AWGR) is a passive SiPhs fabric with compact layout which offers scalable all-to-all connectivity through use of wavelength routing. Recent advances in the fabrication process of AWGRs now enable their integration with significantly reduced footprint (1mm²), crosstalk (<-38dB), and loss (<2dB), making AWGRs a favorable candidate for energy-efficient all-to-all connectivity within HPC systems.

This dissertation explores the design space of AWGR-based interconnects for both processor and memory systems, and comparing them to the state-of-the-art SiPhs fabrics and aggressive electrical baselines under contemporary workloads.

The organization of this dissertation is as follows. Chapter 2 presents a brief background discussion on SiPhs as the major enabling technology used throughout this dissertation. Chapter 3 evaluates the use of AWGR-based SiPhs Network-on-Chip to achieve energy-efficient all-to-all connectivity in large-scale interposer-based HPC systems. Chapter 4 studies off-chip memory networks capable of providing tera-bytes of memory capacity by optically interconnecting several 3D stacked DRAM modules through a packet-switched network interface. Chapter 5 investigates the scaling limitations in chiplet-based systems, in particular, large inter-chiplet

non-uniform memory architecture (NUMA) latencies, distance-related energy overheads, and limited IO bandwidth, and exploiting the properties of optical interconnects to propose a scalable uniform memory architecture (S-UMA) that overcomes all NUMA-related performance challenges. Chapter 6 discusses the architecture of state-of-the-art high-throughput accelerators, the impact of memory access latency variations on overall performance and system design, and key challenges in scaling memory and compute capacity in these systems. This chapter proposes a novel high-throughput accelerator architecture which aims to reduce the contention within the memory system with the help of a partitioned memory controller and an all-to-all passive optical interconnect. At last, Chapter 7 presents a summary of the work presented in this dissertation and illustrates future perspectives.

# Chapter 2

# **Background**

This dissertation investigates different components in HPC systems in search for performance and power improvements. This chapter presents a brief discussion on SiPhs as the major enabling technology used throughout this dissertation.

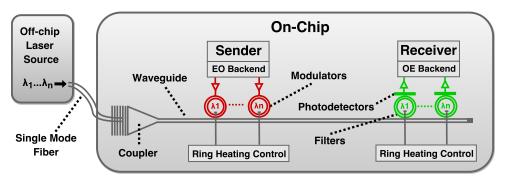

Figure 2.1 depicts a reference optical SiPhs link. A laser functions as a light source to provide the optical medium, confined within a waveguide, for data transmission, on which data is transmitted through modulators and received through filters and photodetectors. Both modulators and filters are based on microring resonators (MRs), each of which tuned to one particular wavelength.

# 2.1 Microring Resonators

Microring resonators are designed and fabricated to resonate only with specific individual wavelengths. The resonance optical frequencies are repeated at intervals known as the Free Spectral Range (FSR). That is, a microring with f as original resonance frequency will also resonate at  $f \pm k \times FSR$  where  $k \in \mathbb{Z}$ . This frequency specific response enables implementation of MRs as filters. This filtering functionality can be obtained using passive MRs with a fixed resonance frequency assigned during the design process, or through use of active MRs designed to *tune* their resonance frequency as the amount of current in their base layer changes. The latter class of MRs, with tunable resonance frequencies, are ideal candidates for modulation.

In order to understand the significance of MRs to SiPhs interconnects, it is useful to discuss how data transmission is performed in an optical link. Figure 2.1 depicts an example optical

Figure 2.1: Reference SiPhs Optical Link

link with all components needed to transmit data between a source-destination pair. Light generated from a laser is confined inside an optical fiber which is then coupled into an on-chip waveguide. Modulators encode bits onto the optical medium (electrical-to-optical (EO) conversion), and filter-photodetector pairs extract the optical signal, performing optical-to-electrical (OE) conversion.

Optical signals can consist of multiple frequencies  $(f_0 - f_n)$  on which data can be transmitted in parallel - a technique commonly referred to as Wavelength-Division Multiplexing (WDM). In order to exploit WDM, one modulator and MR filter per wavelength is needed at the sender and receiver, respectively. Given that MRs are resonant devices, their resonance wavelength depends on device geometry, dimensions, the ambient temperature, and variation thereof can cause the resonance frequency to deviate from their design values, effectively causing malfunctioning. While fabrication yield can be mitigated by MR trimming, protecting MRs from on-chip temperature variations requires integrated heaters ensuring thermo-optical control of each individual MR.

Aside from ensuring a correct behavior, integrated heaters can also be used deliberately to dynamically turn on/off MR filters and implementing wavelength-selective switching devices by "dropping" wavelengths from one waveguide to another. Changing the ambient temperature of a MR with heaters so that its resonance wavelength shifts beyond the free spectral range of all wavelengths on a link effectively allows to dynamically turn off (and on) a MR. Several previous studies leverage this approach to implement path setup and tear down functionality of circuit-switched optical networks based on wavelength-selective routing [6–8].

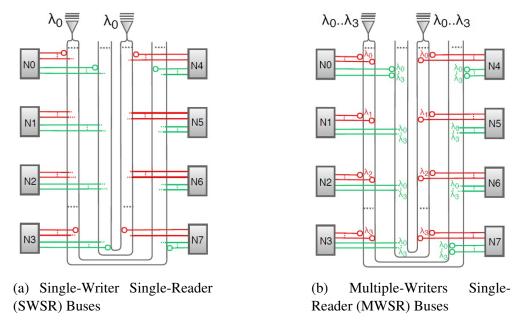

Figure 2.2: Single Reader Optical Buses Implemented using Microrings with (a) Single Writer and (b) Multiple Writers [9].

#### 2.1.1 Optical Buses with MRs

Microrings, in combination with WDM, can be used to implement optical buses. The reference example in Figure 2.1 connects one source-destination pair, and it is referred to as Single-Writer-Single-Reader (SWSR) optical bus. An implementation of a 4×4 SWSR bus is shown in Figure 2.2a. Alternatively, WDM can also be leveraged to connect multiple source-destination pairs with just one waveguide. By equipping each destination with MR filters tuned to different wavelengths a Single-Writer-Multiple-Reader (SWMR) bus can be implemented. Similarly, as shown in Figure 2.2b, a Multiple-Writer-Single-Reader (MWSR) can be implemented using MR modulators tuned to different wavelengths at sender side.

# 2.1.2 Broadband Ring Resonators

MRs are promising SiPh devices for implementing filtering and modulation functionalities. However, since MRs are designed to resonate at a narrow range of wavelengths, MR based solutions often require enormous amount of MRs to be fabricated. In contrast, Broadband Ring Resonators (BRRs) [6][10] can be tuned at a wide range of wavelengths and have been proposed with a circuit switched approach in which path setup/teardown phases are necessary prior to data

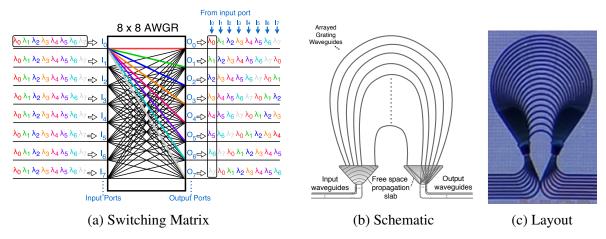

Figure 2.3: The Arrayed Waveguide Grating Router (AWGR). (a) AWGR Structure. (b) Switching Functionality. (c) Realized Physical Layout of a SiN AWGR

transmission. That is, BRRs must be dynamically tuned to a certain wavelength range to route data to the correct destination. Although promising, with the current technology in hand, BRRs have been found to be less practical due to the latency overheads caused by the setup/teardown and tuning phases and large area footprint [10].

# 2.2 Arrayed Waveguide Grating Router

An AWGR functions as a wavelength-multiplexer and demultiplexer, with the wavelength routing pattern as shown in Figure 2.3a. All wavelengths ( $\lambda_0...\lambda_7$ ) inside a waveguide entering the AWGR on a given input port are evenly distributed over all the output ports of the AWGR (one wavelength to one unique output port), effectively implementing a wavelength demultiplexer function (as shown for input 0 in Figure 2.3a). At the same time, different inputs can communicate to the same output on different wavelengths, effectively implementing a multiplexer function at each AWGR output port. One intriguing property of AWGRs is that multiple signals on the same wavelengths can traverse the AWGR without interfering with each other out as long as they enter the device on different input ports. This means that multiple input waveguides can be connected to an AWGR (like in Figure 2.3a), whose wavelengths are evenly distributed to the output ports (depending on the input port), effectively forming an all-to-all, non-blocking switching fabric—with just one device and without the need for MR filters or a large number of waveguides.

Figure 2.3b shows the schematic of an AWGR device. Wavelengths inside the input waveguides enter the free-space propagation region and subsequently traverse the grating waveguides, which have a constant length increment ( $\delta L$ ). Each wavelength undergoes a constant change of phase attributed to the constant length increment in the grating waveguides. Light diffracted from each waveguide of the grating interferes constructively and refocuses at the output waveguides, with the output channels being wavelength dependent on the array phase shift. Figure 2.3c is a screen-shot of the physical implementation of a fabricated Silicon Nitride (SiN)  $8 \times 8$  AWGR, which is just  $1mm \times 0.8mm$  in size.

AWGRs have already found application in the telecom industry allowing for years of fabrication know-how with high-yield manufacturing [11]. Several previous studies for on-chip implementations dismissed the use of AWGRs due to their large area footprint (in the range of multiple  $mm^2$ ); however, those footprints mostly refer to AWGRs fabricated with Silica. Recently demonstrated Silicon Nitride (SiN) based AWGRs have an area footprint of less than  $1mm^2$  [12], a completely reasonable footprint for the architectures investigated in this proposal.