# Hardware Architectures for Scalable Graph Processing

By

# Marjan Fariborz DISSERTATION

Submitted in partial satisfaction of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

in

Electrical and Computer Engineering

in the

OFFICE OF GRADUATE STUDIES

of the

UNIVERSITY OF CALIFORNIA

DAVIS

Approved:

S.J. Ben Yoo, Chair

Venkatesh Akella

Jason Lowe-Power

Committee in Charge

2023

To My Parents

# Contents

| Abstract                                                                    | V   |

|-----------------------------------------------------------------------------|-----|

| Acknowledgments                                                             | vii |

| Chapter 1. Introduction                                                     | 1   |

| Chapter 2. Background and Related Work on Graph Workloads                   | 6   |

| 2.1. Background on Graph Workloads                                          | 6   |

| 2.2. Related Work                                                           | 7   |

| 2.3. Limitations of Previous Work                                           | 10  |

| Chapter 3. Scalable Engine for Graph Acceleration                           | 14  |

| 3.1. Background on Message-driven Graph Applications                        | 16  |

| 3.2. A Model for Scalable Accelerator                                       | 17  |

| 3.3. SEGA Architecture                                                      | 21  |

| 3.4. Methodology                                                            | 31  |

| 3.5. Evaluation                                                             | 32  |

| 3.6. Applications of Model                                                  | 39  |

| 3.7. Conclusion                                                             | 42  |

| Chapter 4. Enabling Large Scale Graph Accelerations Using Silicon Photonics | 44  |

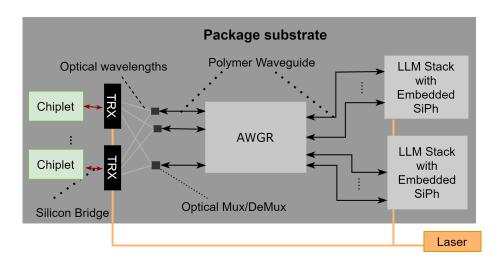

| 4.1. Background on Chiplet-base Systems                                     | 46  |

| 4.2. SEGA a Chiplet-Based System for Large Graph Acceleration               | 49  |

| 4.3. Packaging                                                              | 59  |

| 4.4. Methodology and Evaluation                                             | 61  |

| 4.5. Conclusion                                                             | 63  |

| Chapter 5. Low Latency Memory                                               | 65  |

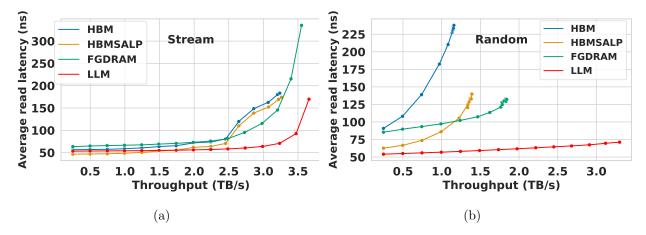

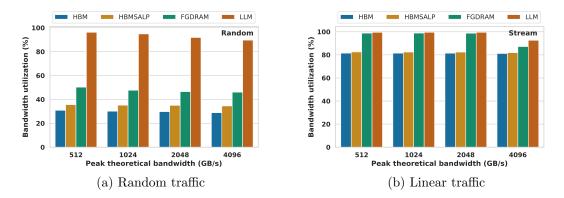

| 5.1. Introduction                                                           | 65  |

| 5.2.    | Motivation                                          | 66 |

|---------|-----------------------------------------------------|----|

| 5.3.    | Silicon photonic enabling technologies              | 68 |

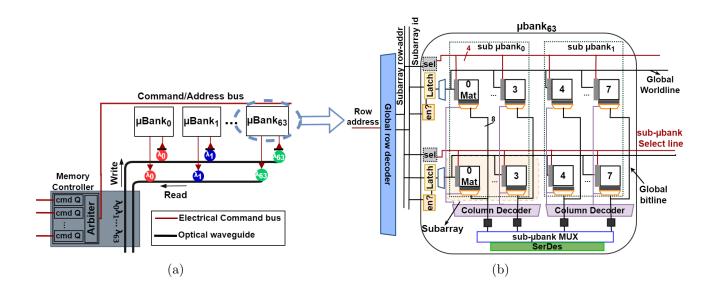

| 5.4.    | Architecture                                        | 69 |

| 5.5.    | Methodology                                         | 75 |

| 5.6.    | Evaluation                                          | 78 |

| 5.7.    | Related Work                                        | 84 |

| 5.8.    | Conclusion                                          | 85 |

| Chapte  | r 6. Conclusion and Future Works                    | 87 |

| 6.1.    | Opportunities for Disaggregated Memories            | 88 |

| 6.2.    | Support for Streaming Graphs                        | 90 |

| 6.3.    | State of the art Memory Systems for Graph Workloads | 91 |

| 6.4.    | Conclusion                                          | 92 |

| Bibliog | ${f raphy}$                                         | 95 |

#### Abstract

Graph analytics has become a popular method for understanding the relationships between data collected from various sources, such as social media, sensor feeds, and scientific data. This allows analysts to identify patterns in the data and answer difficult questions that were previously unanswerable. A more complete picture of the problem can be understood by understanding the complex relationships between different data feeds. However, due to the sparse nature of real-world graphs, these applications tend to show random memory access patterns and low locality. Current computing and memory systems are optimized for applications that exhibit high locality by utilizing deep cache hierarchy and large memory access support. Throughout this work, we show the limitations of running graph workloads on general-purpose systems in terms of both performance and scalability. This work presents scalable solutions for processing graph applications. This dissertation presents the following case studies:

First, designing a graph processing system that can scale to graph sizes that are orders of magnitude larger than what is possible on a single accelerator requires a careful codesign of accelerator memory bandwidth and capacity, the interconnect bandwidth between accelerators, and the overall system architecture. We present a high-level bottleneck-analysis model for the design and evaluation of scalable and balanced accelerators for graph processing. We further studied the scalability limitations of previous graph accelerators and designed an accelerator that overcame those limitations. We used the analytical model to capture the system-level requirements, such as the memory systems.

Second, we analyzed the network requirements of graphs as we scaled up the system to larger nodes and more memory. We demonstrate that the traffic pattern between graph processing nodes has a uniform random distribution, and while the bandwidth requirements are not significant, having a low-diameter interconnect can improve the performance.

The third part of this work proposes a new memory system that is optimized for applications with random memory patterns. Our goal was to create a new memory that reduces the amount of contention on the data path since contention on the shared resources was the main source of performance bottleneck. By utilizing 2.5D/3D integration and multi-wavelength (WDM) silicon photonic (SiPh) technologies, we create a new memory system with low memory access latency and

latency variation in addition to  $4\times$  higher bandwidth compared to high bandwidth memories such as HBM2 given the same amount of capacity.

### Acknowledgments

I would like to express my heartfelt gratitude to Professor S.J. Ben Yoo for giving me the opportunity to be part of his diverse research team at UC Davis.

I would like to extend my deepest appreciation to my esteemed committee members, Professor Venkatesh Akella and Jason Lowe-Power. Their invaluable guidance, expertise, patience, and time have profoundly influenced my growth as a researcher. The insightful discussions I shared with them have been instrumental in shaping my academic journey.

I am also indebted to my colleagues at UC Davis, Mahyar Samani, Dr. Pouya Fotouhi, and Dr. Roberto Proietti for their invaluable contributions. Collaborating with such exceptional scientists and wonderful individuals has been a pleasure.

Finally, I wish to extend my deepest appreciation to my parents and my brother, Mehri, Shahriar, and Jamshid. Your unwavering belief in me, your support, and your encouragement have been pivotal in every success I have achieved. I consider myself incredibly fortunate to have in my life.

### CHAPTER 1

## Introduction

Large-scale data analytics is fueling breakthroughs in a broad range of applications such as logistics and transportation, advertising, security, understanding social behavior, tax policy, drug discovery, cosmology, etc. The problem sizes in these applications are increasing exponentially in volume, variety, and complexity. Data for these applications is often sparse and stored in structures with poor data locality. These applications are represented in terms of sparse matrix dense vector operations and can be modeled by graph operations. Processing and storing these large-scale data can no longer be ignored as in many scenarios they account for a significant fraction of the overall execution time and consume a significant portion of machine resources. Thus, we need to understand the characteristics of these workloads.

The memory access patterns are very irregular (especially in large-scale graph data analytics) which results in poor data locality and makes the deep hierarchy of caches used in the current computing systems ineffective. In addition, moving the data through a multilevel cache hierarchy consumes a significant amount of energy. Graph analytics applications are often memory-bound with little data reuse and low spatial and temporal locality with fine-grain random accesses to memory. Due to these characteristics, the current general-purpose computing systems are not efficient. These inefficiencies include:

- Graph traversals often require many memory accesses relative to only small amounts of computation. Ham et al. [40] shows that only 6% of instructions are dedicated to computation and the rest 94% of instructions are used for traversing the graph and loading the graph-specific arguments.

- In graph applications data is accessed at a fine granularity which is smaller than the memory access granularity. This discrepancy between the data access demand and memory access granularity causes a significant amount of off-chip memory bandwidth waste.

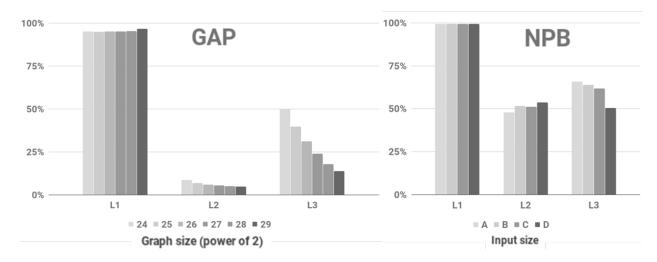

- Ineffective on-chip memory usage caused by lack of temporal and spatial locality in graph workloads. Figure 1.1 illustrates workloads from both benchmark suits benefit similarly

from L1 data caches with average hit rates of 99% for NPB and 95% for GAP. However, the lower levels of the cache hierarchy are much less useful for these large workloads. The irregular graph workloads (GAP) show even more ineffective use of cache than the HPC workloads (NPB) with below a 5% hit ratio at the L2 cache. As the size of the workloads grows in the future large caches will continue to be wasteful in terms of area and power.

FIGURE 1.1. Cache hit rates (average values of all workloads) for NPB and GAP benchmark suites. We used input sets A to D for workloads in NPB, and graphs with 224 to 229 vertices for GAP kernels.

With advances in 2.5D/3D integration and multi-wavelength (WDM) silicon photonic (SiPh) technologies over the past decade, it is time to rethink and redesign computing systems and memory subsystems to make them more amenable to applications with random memory access. Additionally, we aim to design new computing systems that can scale to meet the demands of ever-growing data.

One approach to reducing the data movement energy for these sparse applications is to flatten both the memory hierarchy and the network interconnect. By flattening the memory hierarchy as far as possible by eliminating the cache hierarchy to realize a memory system that exhibits low and predictable latency. Photonic networks with devices such as high port count chip-scale AWGRs can be used to flatten the network topology (basically reduce the hop count) by increasing the radix of the intermediate switches and/or adding auxiliary direct links (express links) to create a custom topology that matches the unique dataflow of the application during different phases of execution. This can unleash new computing architectures that are not only more energy efficient but also easier to program.

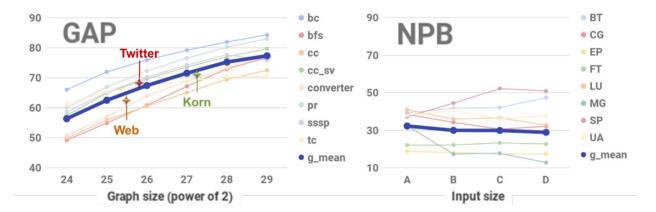

FIGURE 1.2. Target DRAM latency (in nano-seconds) to achieve the same AMAT in a system with no L2/L3 caches for GAP and NPB workloads. Using workloads from GAP benchmark suite [17] The results of this analysis for Web [30] with 50.6 M nodes, Twitter [49] with 61.6 M nodes, and Korn [3] with 134.2 M nodes are presented as single data points (geometric means across different kernels).

To improve the performance of these sparse applications, we need to rethink the architecture of the memory subsystem. By reducing contention for the memory data access for sparse workloads, we can reduce the memory access latency. Also, by taking advantage of WDM silicon photonic interconnects, we can increase the memory access bandwidth and reduce the data movement energy consumption. The hypothesis is that this low latency and high bandwidth memory sub-system allows us to ultimately flatten the memory system. Therefore, we codesigned the processor, the DRAM microarchitecture, and the memory controller by taking advantage of 2.5D/3D integration with WDM silicon photonic interconnects.

Figure 1.2 presents an initial study of the required memory latency required to remove these ineffective L2 and L3 caches. As our initial analysis, we determine the desired latency of DRAM for achieving the exact same performance (average memory access time, AMAT) with no L2 and L3 caches. We conservatively assume 90ns memory latency (unloaded local DRAM access time), 12 cycles L2 hit, and 34 cycle L3 hit latencies. As Figure 1.2 shows, workloads in NPB require a DRAM access latency of 30ns (66% improvement goal) for a system with no L2/L3. For GAP kernels using synthetic graphs, the ineffectiveness of caches translates into a modest required DRAM latency of 77ns (15% goal) for a system with no L2/L3.

To support the fast processing of the growing data structures, we create a large-scale graph accelerator. Designing a graph processing system that can scale to graph sizes that are orders of

magnitude larger than what is possible on a single accelerator. However, this system requires a careful codesign of accelerator memory bandwidth and capacity, the interconnect bandwidth between accelerators, and the overall system architecture. We present a high-level bottleneck-analysis model for the design and evaluation of scalable and balanced accelerators for graph processing. This model chooses the right mix of different memory types, network topology, network bisection bandwidth, and system-level architecture to match the access patterns and capacity requirements of different data structures for a given graph and a performance target. Designers can use this model to help them understand the bandwidth, capacity, and microarchitectural needs of their system to achieve desirable performance. This analytical model can also be used to evaluate the performance of emerging memory and interconnect technologies in graph accelerators.

While the proposed analytical model helps with understanding the system requirements of designing scalable graph accelerators, we need the accelerators' processing elements to be able to process large graphs with high performance. Previous accelerators improved performance and reduced memory access costs by designating the data structure with random access patterns (vertex information) and storing this data structure on-chip. However, given that the amount of on-chip memory by definition is limited, most of the designs reported in recent literature rely on partitioning the graph into smaller slices and time-share the on-chip memory between different graph partitions (temporal partitioning). Although effective for relatively small graphs with a few million vertices, their performance tends to degrade for larger graphs, making them unscalable and inefficient for processing large graphs. Due to the limitations of temporal partitioning and the dependence of previous graph accelerators on temporal partitioning to exploit locality and achieve high performance, we propose a new graph accelerator node that doesn't rely on locality to achieve high performance. Instead, this new accelerator relies on the on-chip memory to hide the off-chip random memory access latency.

This proposed graph accelerator is composed of multiple processing elements (PEs). Each processing element processes a subset of vertices and edges that are stored in the off-chip memory designated for each processing element. Each processing element can process any graph size without temporal partitioning as long as it fits on its off-chip memory. To scale to significantly large graphs, we propose scaling out the number of PEs, partitioning the graph, and assigning each partition to

a designated PE. With the new graph accelerator's processing element design, we can utilize the analytical model to help us understand the system needs of designing a large-scale graph accelerator.

The organization of this dissertation is as follows. Chapter 2 presents background on the graph application, background on previous studies on accelerating graph workloads, and their limitations. of graph with previous graph accelerators and their scalability challenges. Chapter 3 presents the overview of our proposed graph accelerator and an analytical model that can be used to understand the system-level requirement to scale to a specific graph size. Chapter 4 presents the network requirements of scaling to large graphs and explores the traffic pattern on the system. Chapter 5 discusses the architecture of a state-of-the-art memory system with low latency and high throughput customized for applications with random memory access patterns. At last, Chapter 6 presents a summary of the work presented in this dissertation and illustrates future perspectives.

### CHAPTER 2

# Background and Related Work on Graph Workloads

### 2.1. Background on Graph Workloads

Graph processing frameworks follow the **vertex-centric** or **edge-centric** paradigm for sequencing their computation. In the edge centric model, edges are streamed into the processor through vertex indices. The processor needs to read both source and destination addresses. This programming model suffers from poor spatial locality when reading vertices since there is a little chance of both source and destination vertices being stored in consecutive memory locations.

The vertex-centric paradigm is more popular than edge-centric due to its implementation simplicity and lower number of redundant vertex reads. The vertex-centric paradigm is designed from a vertex's perspective, i.e., a vertex property value is updated by a computation based on the property of its neighbors [61].

Vertex-centric computation model follows one of two approaches: **pull** or **push**. In the pull approach, each vertex reads the properties of all its incoming neighbors and updates their values. Thus, it involves random and redundant reads of the neighboring vertices, resulting in poor memory bandwidth utilization and wasted parallelism due to memory latency. On the other hand, the push approach each vertex performs a read-modify-write operation for each of its outgoing neighbors.

Vertices can be scheduled using **bulk-synchronous** or **asynchronous** model. In the bulk-synchronous parallel model (BSP) [90] the workload is abstracted into iterations. During each iteration vertex values get updated and new vertices get activated for the next iteration. The asynchronous programming model [91] there are no definition of iteration which allows asynchronous processing of vertices and thus substantially increasing available parallelism.

Graph workloads use two main data structures to represent a graph: 1) an array-like data structure containing vertex specific information, and 2) an array-like data structure containing edge specific information. We refer to vertex and edge data structures as worklist and edgelist

respectively. While the worklist represents the property of each vertex in the graph, the edgelist represents the structure and connectivity or the relationship of the vertices in the graph.

In addition, graph workloads use a tertiary data structure that contains vertices that need to be processed. We refer to these vertices as active and this data structure as active set or frontier.

Traditionally, graphs are processed on CPUs and GPUs. Libraries such as Galois [73], Ligra [81], GAPBS [17], Gunrock [93] are designed to optimize graph applications on CPUs and GPUs. The goal of these libraries is to improve load-balancing and improving work efficiency by exploiting locality. Galois [73] provides flexibility in the programming model by using different operator abstraction which allows them to support topology aware priority scheduling. Similar to Galois, Ligra [81] uses a load-balancing strategy that is based on CilkPlus [50] to support multicore servers. Ligra uses hybrid data representation for sparse and dense active sets. Both Galois and Ligra are the highest performing lightweighted and generalized software framework for shared-memory machines. Gunrock is a GPU-based library for graph processing. It allows programmers to develop graph primitives to GPU systems. Gurock improve the performance of graph analytic by improving the load-balancing and improving memory efficiency. Almost all these platform support the hybrid push-pull based traversal based on the sparsity of their active sets.

#### 2.2. Related Work

In this chapter, we present previous works that focused on improving the performance of graph workloads. In the past decade, there has been a plethora of work on graph accelerators [10, 14, 40, 59, 63, 64, 66, 68, 75, 76]. Studies focusing on enhancing the performance of graph applications either through software improvements on general-purpose systems or hardware accelerators. The primary goal of these studies has been to reduce data movement either by moving to compute near data or optimizing locality.

State-of-the-art graph accelerators such as PolyGraph and GraphPulse [29,75] utilize on-chip memory to enhance locality. These accelerators use temporal partitioning to scale graphs larger than their on-chip memory capacity and spatial partitioning for graphs larger than their off-chip memory capacity.

In temporal partitioning, on-chip memory can be shared by different partitions sequentially over time, while in spatial partitioning, multiple accelerator chips can house all slices while an interconnection network streams inter-slice events in real-time.

Other graph accelerators use a traditional memory hierarchy with multi-levels of private and shared caches. However, these architectures suffer from an overwhelming amount of data movement due to poor data-reuse in graph workloads. As a result, cache thrashing leads to more than 50% of all memory accesses missing in the last level cache [59].

Accelerators such as PolyGraph [29], GraphPulse [75], and ScalaGraph [99] utilize high-bandwidth off-chip memory for processing edges while storing partitions of vertices on-chip. This approach enables these accelerators to achieve high performance by leveraging the benefits of high-bandwidth memory. However, we demonstrate that larger graphs with more partitions can adversely impact the performance.

In this chapter, we review the literature related to accelerators, specifically PIM-based accelerators and hardware-based graph accelerators. Then, we focus on the limitations of these previous works for processing large graphs.

**2.2.1.** Hardware Accelerators. Previous hardware graph accelerators improve performance by creating customized pipelining mechanisms [10,14,40,63,64,68,75,76] or by decoupling data access and computation [59,66,100]. All of these studies focus on improving off-chip memory efficiency for graph processing.

Mukkara et al. [62] reduces random off-chip memory accesses using a hardware-accelerated traversal scheduler that allows the system to improve locality. GraphDyns [98] represents a new programming model to extract data dependencies in graph processing dynamically. It uses a load-balanced scheduling mechanism, and a specialized prefetcher for off-chip edge data access. ScalaGraph [99] proposes the use of high bandwidth memory and a distributed memory assignment to improve the edge throughput while eliminating the atomic memory accesses. Chronos [10] avoids temporal partitioning and uses an on-chip cache and speculative execution model to avoid coherency overheads. Ozdal [68] defines a custom cache corresponding to each different data type (edge indices, edge data, vertex info, vertex data) of each graph object type to reduce the data access energy. Graphlily [43], ScalaGraph [99], and PolyGraph [29] utilized HBM memory for higher bandwidth access to the edge memory. However, in all these designs, HBM was used only to

improve the edge bandwidth throughput. Dalorex [67] stores the entire data in the on-chip memory, and they scale their performance significantly as they scale their processing tiles. However, for them to maintain their performance, they require to have a significant amount of on-chip memory.

PolyGraph [29] proposes a flexible accelerator that supports multiple variants, including non-slice, sliced, synchronous, and asynchronous modes. In their experiments, the non-slice variant is observed to be effective only for small graphs or phases of the workload with a low number of active vertices. For instance, they propose switching to the non-sliced variant at the beginning/ending iterations of the Breath-First Search algorithm (BFS).

Dalorex [67] eliminated the off-chip memory access by storing the entire graph in on-chip memory. The on-chip bandwidth dictates their performance, allowing them to achieve much higher performance compared to PolyGraph. To scale to larger graphs (beyond what is supported by their on-chip memory), they spatially partition the graph and increase the number of accelerator cores to support large graphs. They require gigabytes of on-chip memory to store large-scale graphs without temporal partitioning. Similar to Cerebras WSE-2 Delorax consists of multiple graph processing nodes and gigabytes of on-chip memory that are uniformly distributed between these cores. Leaving only kilobytes of capacity for each graph processing nod. Therefore, each node only processes a small fraction of the graph. In addition to scaling to terabyte or petabyte graphs, Dalorex is required to perform temporal partitioning on the disk or scale the number of graph processing boards. The size of these accelerators is quite large (in a 16×16 Dalorex with 67.2MiB on-chip memory capacity, the area is (305mm2)), which results in an interconnection with long latency making this off-chip accesses expensive.

It should be mentioned that in all these studies, the goal has been to improve performance by reducing off-chip memory.

2.2.2. PIM-based Accelerators. A promising solution to remove the memory wall challenges in the graph workloads is to use processing in the memory (PIM). PIM-based acceleration is possible due to the recent advancement of the 3D integration technology that facilitates stacking logic and memory dies in a single package. PIM-based architectures provide high levels of parallelism, low memory access latency, and large aggregate memory bandwidth.

Some studies rely on emerging memory technologies such as ReRAMs [12] to perform computing in memory in addition to storing data [23, 82, 106]. Other PIM-based architectures use 3D

stacked memory technologies, such as Hybrid Memory Cube (HMC) [72] to eliminate the irregular data movement [11,102,110]. Tesseract [11] is a PIM-based graph processing architecture that supports vertex programming model with architectural primitives to enable inter-memory cube communication. Graphq [82] proposed the first multi-node PIM-based graph processing architecture built on the recent work Tesseract [11]. Graphq uses a two-phase programming model enabling efficient partitioning of graphs between different memory cubes.

These accelerators propose using Hybrid Memory Cube and non-volatile memories such as ReRAM to store their randomly accessed data structures. Whereas in our proposed scalable graph accelerator, depending on the capacity, performance, and available resources, the architect can decide on the vertex or edge memories.

#### 2.3. Limitations of Previous Work

Prior accelerator designs rely on improving spatial and temporal locality. In previous accelerators, the graph is divided into temporal slices that fit into on-chip memory and they time share the limited on-chip memory for all the temporal slices. Temporal partitioning of the graph ensures all the vertices that need processing reside in the on-chip memory during the processing of a partition. Thus, these designs remove random accesses to the off-chip memory and reduce the access time to vertices. However, temporal partitions come with additional costs in terms of preprocessing, portability, and overhead of switching between slices, and underutilization of hardware resources. Next, we will describe these costs in more detail.

2.3.1. Preprocessing Cost and Portability. Ideally, the graph should be partitioned into slices that are individually highly connected and mostly independent. However, optimal algorithms for such preprocessing can exceed the computation complexity of basic graph processing algorithms such as BFS. For example, polynomial time solutions for min-cut have not been found yet, while BFS has a complexity of O(||V|| + ||E||) [13,15,46]. In recent studies, Balaji et al. show that RABBIT++ requires 1047 iterations of SpMV (Sparse Matrix times Dense Vector) kernels to amortize for preprocessing costs [15]. Therefore, works such as PolyGraph rely on simpler partitioning heuristics such as chunking the vertex set based on the id of the vertices [29,109]. Chunking has a complexity of O(V), but it comes at the cost of reducing the independence of the partitions that are generated. Moreover, for every vertex that has an edge that crosses partitions, that vertex has to be replicated

in the destination partition. The replicated vertices are used to communicate information from one partition to another. Furthermore, temporal partitioning of graphs is not a portable approach because the amount of available on-chip memory determines the size of each slice. This means a graph partitioned for an accelerator with 8 MiB of on-chip memory has to be repartitioned for an accelerator with a different amount of on-chip memory.

2.3.2. Switching Cost and Resource Utilization. In addition to the preprocessing cost, there is also the cost of increased processing time due to switching and underutilization of hardware resources. There are three processing steps when switching between temporal slices: (1) The current partition's vertices must be written back to the off-chip memory and the new partition's vertices must be read from off-chip memory. (2) Each slice has a set of replicated vertices to facilitate temporal partitioning, and any vertex updated by the current temporal slice which resides in other slices must be read and updated in off-chip memory. (3) All replicated vertices of the new partition must be read to create the inter-slice messages. Finally, each slice must be processed multiple times because of the inter-slice edges, which adds to work inefficiency.

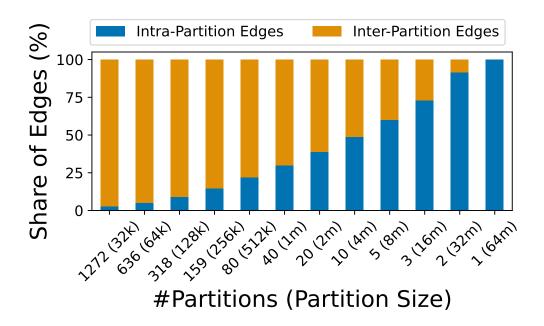

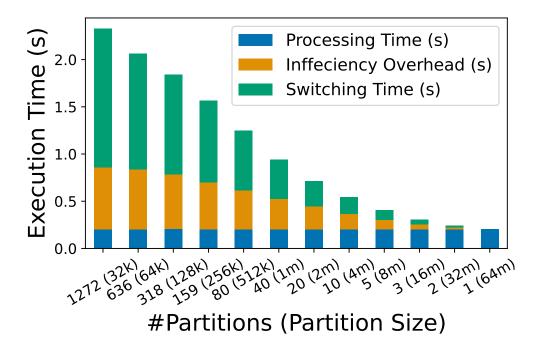

FIGURE 2.1. Distribution of edges within and between partitions as the size of a partition grows for Twitter graph.

FIGURE 2.2. Overhead of temporal partitioning as the number of partitions increases using BFS and Twitter graph.

To quantify the overhead of partition switching, we implemented the partitioning technique used in PolyGraph [29, 109]. For every switch operation, we chose the partition that has the most updated vertices to process as the next partition. We used the Twitter graph as an input to the BFS workload and broke the execution time down into two components. (1) Processing time accounts for time spent processing partitions. (2) Switching time accounts for time spent switching partitions including writing the current partition, reading the new partition, and reading/writing inter-partition replicated vertices. (3) Inefficiency overhead accounts for the time spent processing partitions more than once (i.e., the extra time from the decreased work efficiency<sup>1</sup>).

Figure 2.1 shows the distribution of edges within and between partitions for various graph sizes. This figure shows that as the number of partitions grows, the number of intr-partition edges outgrows the number of edges inside of partitions. With ten partitions, almost 50% of edges are inter-partition edges. This increase in the number of inter-partition edges results in higher switching time since more replicated vertices need to be updated.

<sup>&</sup>lt;sup>1</sup>Work required by the optimized sequential execution (in terms of edges processed) over the work performed in parallel execution

Figure 2.2 shows the breakdown of execution time between processing time, inefficiency overhead, and switching time as the number of partitions grows (larger graphs). Inefficiency overhead and switching time constitute approximately 20% of the execution time when there are less than three partitions. As the number of partitions grows, the inefficiency overhead increases quickly. For instance, in the case of 318 partitions, inefficiency overhead makes up more than 75% of the execution time. Figure 2.2 shows that temporal partitioning of larger graphs with more partitions can reduce the performance, making the accelerators that use this method unscalable.

When using temporal slicing, there is no way to eliminate inter-tile events, even with an optimal tiling strategy (e.g., min-cut). Furthermore, as the number of tiles increases either due to using larger graphs or smaller on-chip memory, the overhead of inter-tile events will increase, and the work efficiency will decrease.

### CHAPTER 3

# Scalable Engine for Graph Acceleration

Modern data-driven scientific discovery is based on understanding relationships between data entities that are modeled as graphs—i.e., graph processing. Traditionally, graphs are processed on CPUs and GPUs using optimized libraries such as Galois [73], Ligra [81], GAPBS [17], Gunrock [93], etc., but the performance of software implementations on these large graphs is unacceptably poor in many applications. As a result, there has been strong interest in new hardware accelerators for graph processing. Starting with early work in FPGA-based graph exploration [54,107,108], numerous architectures for graph processing hardware have been reported in the literature over the past few years, including accelerators which leverage processing in/near memory and run at the wafer-scale. At the same time, the size of these graphs is growing quickly as it is becoming increasingly easier to collect large amounts of data. For instance, WDC12 [3] has 3.6 billion vertices and 128.7 billion edges, requiring over a terabyte of working memory.

There is currently a mismatch between graph accelerator designs and the growing graph data scale, which this paper aims to address. Most graph accelerators leverage vertex-centric programmers where processing vertices exhibit low spatial and temporal locality, leading to frequent random memory accesses.

To address this, many prior studies [29, 40, 75] have sought to exploit locality and reduce data movement overheads. These prior works use large on-chip memories, in/near memory processing [11, 83], and the addition of hardware to improve locality for graph processing [10]. Some prior work [29, 40, 67, 75] optimizes performance by storing vertices in the on-chip memory while storing the graph structure (i.e., edges) higher capacity off-chip memory like HBM or DDR4. In these accelerator designs, the data is explicitly moved from off-chip memory to on-chip memory, and their efficiency hinges on finding locality within the vertex updates. However, as the size of the graphs processed increases, the vertex set will exceed the on-chip memory capacity. To address this problem, prior work relies on partitioning the graph into slices that fit in the available on-chip memory and temporally sharing the on-chip resources. This temporal portioning is akin to memory

swapping and time-shared multiplexing of the processor in operating systems. Like these related techniques, temporal partitioning in graph accelerators imposes significance when switching between partitions. Furthermore, the generated partitions often exhibit inter-dependencies, requiring multiple processing of each generated partition. Our analysis (described in Chapter 2) shows that as the number of partitions grows, the overheads constitute an increased share of the execution time, up to 90% of the execution time. The overheads from temporal partitioning, which is required for larger graphs, cause current graph accelerator designs to exhibit poor throughput scaling as the graph size grows.

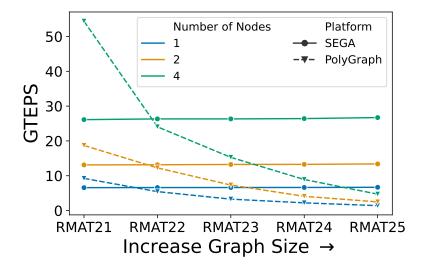

Figure 3.1 shows how PolyGraph's performance varies as the graph size grows, given a fixed-size on-chip memory. As the graph size increases, the throughput drops, indicating that the locality improvement depends heavily on the on-chip resources. As discussed in Section 2, temporal partitioning is the main limitation preventing PolyGraph and similar systems from scaling to large graphs efficiently.

This work presents a new graph processing architecture that enables a consistent graph processing throughput independent of graph input size. Instead of focusing on capturing locality, SEGA uses on-chip resources to enable enough parallelism—abundantly available in large graphs—to hide the latency of accessing the off-chip memory. The intuition behind our design is that for each reduction operation (i.e., message to update a vertex property), multiple propagations take place (i.e., many neighbors need to be updated). As a result, the throughput of the propagation procedure is more resilient to the latency of accesses to the memory. In our design, we introduce a runtime procedure to efficiently orchestrate vertex information between reduction and propagation. Our design enables leveraging the capacity of both on-chip and off-chip memory to store the active working set. In turn, we increase our coalescing space to the whole vertex set, resulting in increased work efficiency. Furthermore, our design is scalable because we leverage the idea of [message-driven processing to push updates to the local processing element responsible for each vertex. CF Graph is a microarchitectural and system-level design for scalable graph processing based on the idea of active messages. Instead of storing active vertices on the on-chip memory for faster access and better coalescing, we move the entire active vertices to the off-chip memory. Moving data to the off-chip memory removes the use of temporal partitioning in our design. Additionally, by enabling all vertices to be active simultaneously, we can coalesce more updates and increase work efficiency compared to prior work with temporal partitioning.

This chapter focuses on the following:

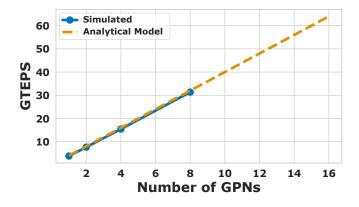

- An analytical model that helps designers understand the system-level requirements of large graph analysis. This proposed model can also predict performance based on the network, memory, reuse distance, and tiling schemes.

- We identify the scalability limitations of prior work because of their reliance on temporal partitioning to achieve high performance.

- We introduce a new graph processing microarchitecture: SEGA, and we describe multiple architectural tradeoffs in its design.

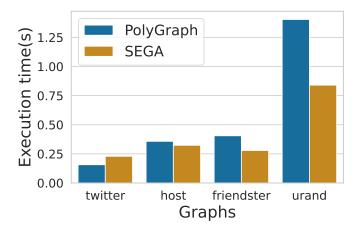

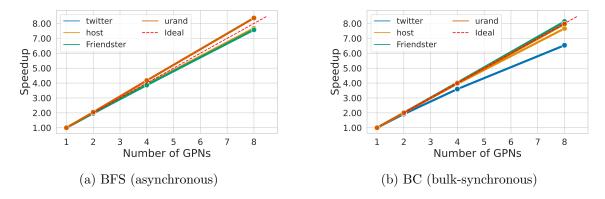

- We evaluate our new microarchitecture, at multiple scales, and show 1.3× to 1.84× performance improvement compared to PolyGraph. We observe that for smaller graphs, PolyGraph outperforms SEGA. However, as the size of the graph increases, PolyGraph's performance drops.

FIGURE 3.1. Both systems have 1.5 MiB on-chip memory and 332.8 GB/s for BFS workload. GTEPS (giga traversed edge per second) represents the system throughput. Higher GTEPS shows higher throughput.

### 3.1. Background on Message-driven Graph Applications

Vertex-centric programming is a common paradigm for implementing graph algorithms [10,11, 17,29,40,73,75,76,81,85]. In this computation paradigm, programmers describe graph algorithms

as a series of operations from the perspective of a vertex [61]. Some graph processing workloads can be implemented using the *message-driven* paradigm, which can be thought of as each vertex sending *messages* to its neighbors. Each *message*, such as  $\langle u, \delta \rangle$ , has two main attributes: a destination vertex (u) and an update  $(\delta)$ . In this *message-driven* model, an active vertex (such as u) calculates an update for each of its neighbors and sends the update through the message.

In the message-driven model, every workload is described using two main functions: **Reduce**, which determines the new property for a vertex using its current property and a message for that vertex, and **Propagate**, which determines the update of a message using the property of the vertex and the weight of an edge. Algorithm 1 shows an example of a message-driven vertex-centric algorithm used in SEGA.

### 3.2. A Model for Scalable Accelerator

The proposed performance model calculates the system-level requirements assuming an asynchronous implementation of the widely used vertex-centric programming paradigm for graph processing. We assume a system is constructed by combining a set of accelerator tiles (the basic building blocks) with an appropriate interconnection network. The requirements are in terms of memory capacity and memory bandwidth for different types of memory, the network bandwidth, and number of tiles. These requirements depend on the structure of the graph, representation of different data structures, and physical constraints such as the maximum I/O on each tile. With the assumption that graph algorithms are throughput limited, these requirements capture the behavior of many graph accelerators. Additional constraints could be added to the model if this assumption does not hold (e.g., the compute capability is a limiting factor).

To calculate the bandwidth for each component, we consider the maximum performance required from each component individually. Equation 3.1 shows Graph Algorithm Iron Law (GAIL) [18] which calculates the execution time for graph workloads. GAIL separates algorithm and hardware performance. Traversed Edge Per Second (TEPS) shows the hardware performance. For the same algorithm implementation, larger TEPS will result in a smaller execution time. Our model focuses on maximizing this TEPS performance metric.

(3.1)

$$\frac{\text{time}}{\text{kernel}} = \frac{\text{number of edges}}{\text{kernel}} \times \frac{1}{\text{TEPS}}$$

- **3.2.1. Memory System.** Next we describe what data structures to store in the memory and the capacity and bandwidth requirement of these data structures. Both edges and vertices have different characteristics. The proposed model calculates the capacity and bandwidth requirements of edges and vertices separately. For simplicity we only consider vertex and edge data structures in the description below, but the model can extend with other data structures easily.

- 3.2.1.1. Edge. In general, edges require a larger memory capacity compared to vertices (graphs such as WDC12, Twitter, and LiveJournal have  $36\times$ ,  $34\times$ , and  $15\times$  more edges than vertices). In most graph programming models [41, 56, 73] access to edges are sequential and read-only. The model should determine the number of memory devices that provides enough capacity for a targeted graph. Table 3.1 Row 1 shows the required capacity for the edge memory which depends on the number of bits representing edge information. The size of the edge is different between accelerators. At a minimum it should include the vertex ID (destination or source) and the weight of the edge. The other constraint for the edge memory is the required bandwidth to achieve a certain performance in TEPS (shown in Table 3.1 Row 2).

- 3.2.1.2. Vertex. In contrast to edges, vertices have low spatial and temporal locality in most graph algorithms. This lack of locality causes inefficient off-chip memory access and low memory access throughput. Prior work exploits locality through graph pre-processing [40] or by online traversal scheduling [?] to improve the on-chip cache usage. Other hardware accelerators use on-chip SRAMs to store vertices and/or events to reduce off-chip memory access [75].

The required vertex bandwidth depends on the performance of the edge memory. For every edge read there is at most one vertex read and one vertex update. Therefore, vertex access rate is  $2\times$  higher than edge access rate. The maximum supported bandwidth also depends on the access granularity to the vertex memory system (a.k.a.  $atom\ size$ ). On-chip caches reduce the off-chip vertex memory access rate. Therefore in our model we use a parameter  $\alpha$  to model accelerators with on-chip memory assigned to vertices.  $\alpha$  indicates the fraction of the off-chip memory bandwidth that is needed by the accelerator.  $\alpha$  is a value between zero and one. An accelerator that exploits locality/reuse will have a smaller  $\alpha$  which means it will have lower off-chip memory bandwidth requirement. Table 3.1 Row 3, shows the maximum required bandwidth for vertex memory given a TEPS (usually from the peak edge bandwidth (Table 3.1 Row 2). In addition to the bandwidth,

we must also meet the capacity requirement of the vertex memory. Our model needs to consider the capacity of vertices (Table 3.1 Row 4).

**3.2.2. Network Requirements.** After finding the best memory technology for vertex and edge data structures, we must ensure that data movement among accelerators will not cause a performance bottleneck. We consider the *network* as the third constraint in our model. What we consider as network in our scaled-out system is the interconnection fabric between accelerators. Accelerators use this network to communicate inter-slice updates. A well-partitioned graph with a low inter-slice event rate does not require a high bandwidth network. The proposed model takes into account the bisection bandwidth, port bandwidth, and topology of interconnection network.

3.2.2.1. Bisection Bandwidth. The required bisection bandwidth is dependent on the performance of each accelerator and the size of the message communicated through the network. With every edge read a new message is created to another vertex. Hence, TEPS indicate the maximum rate of messages generated from the aggregate edge memory across all accelerators. We use  $\gamma$  to indicate the fraction of the messages targeting vertices in remote accelerators and have to be communicated over the network interconnect. Table 3.1 Row 5 shows the required network bisection bandwidth.

Data representation dictates the size of the message communicated in the system. It depends on the implementation of the accelerator and is a parameter in our model.

3.2.2.2. Port Bandwidth. The required network bandwidth for each accelerator can also be a limiting factor. Port bandwidth depends on the required bisection bandwidth and the number of accelerators in the system. See Table 3.1 Row 6.

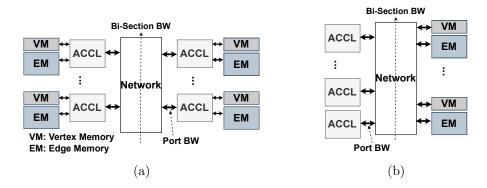

FIGURE 3.2. System architecture for the scaled-out accelerator. a) Near memory processing. b) disaggregated memory-based.

3.2.2.3. System Architecture. The system architecture dictates the interconnection traffic patterns and depends on the port bandwidth and the interconnection network topology. We model two systems: near memory processing architectures and disaggregated memory-based architectures as shown in Figure 3.2. In the near-memory processing system, each accelerator tile is connected to a local memory system, and the interconnection network is between the accelerators. Here, each accelerator is operating on its local vertex and edge information, and only events are communicated through the interconnect (Table 3.1 Row 5). Whereas in the disaggregated memory-based system the accelerators do not communicate directly with each other—the communication is through the memory. In this topology, accelerators use interconnects for communicating events and for reading/writing vertex and edge information. Hence, it required a larger bisection bandwidth in the network (Table 3.1 Row 7).

| 1 | $\frac{\text{Edge}}{\text{Capacity}} = \text{Number of edges} \times \text{Sizeof(Edge)}$                    |

|---|--------------------------------------------------------------------------------------------------------------|

| 2 | $\frac{\mathrm{Edge}}{\mathrm{Bandwidth}} = \mathrm{Maximum} \ \mathrm{TEPS} \times \mathrm{Sizeof(Edge)}$   |

| 3 | $\frac{\text{Vertex}}{\text{Bandwidth}} = 2 \times \text{ atom size} \times \text{TEPS} \times \alpha$       |

| 4 | $\frac{\text{Vertex}}{\text{Capacity}} = \text{Number of vertices} \times \text{Sizeof(Vertex)}$             |

| 5 | $\frac{\text{Bisection BW}}{\text{(Near-memory)}} = \text{TEPS} \times \text{Sizeof(message)} \times \gamma$ |

| 6 | $rac{	ext{Port}}{	ext{Bandwidth}} = rac{	ext{Bisection Bandwidth}}{	ext{Number of accelerators}}$          |

| 7 | $\frac{\text{Bisection BW}}{(\text{disagg.})} = \text{Vertex BW} + \text{Edge BW}$                           |

Table 3.1. System constraints used in the proposed model.  $\alpha$  is the miss ratio of vertex on-chip memory.  $\gamma$  is the percentage of inter-accelerator to intra-accelerator communication.

3.2.3. Accelerator Node. The internal architectural parameters of accelerators are another constraint in our model. These parameters are: 1) Number of bits for representing data structures. This parameter impacts the network's bisection and port bandwidth and the edge memory bandwidth requirement. 2) On-chip resources such as caches and SRAMs. These on-chip memory systems will impact the required bandwidth from the main memory  $(\alpha)$ . 3) The number of I/O pins connected to each accelerator and their data rate limits the number of memory nodes connected to the accelerators (total capacity supported by a single accelerator) and the port bandwidth of the

interconnect. Given the high memory access and communication-to-computation ratios of graph workloads, we do not consider the computation within the accelerator as a bottleneck in our model. Ham et al. show that only 6% of instructions executed in a graph workload are responsible for custom graph computations, and the rest of the instructions are used for loading and traversing the graph [40].

#### 3.3. SEGA Architecture

In the previous section, we demonstrated that depending on temporal partitioning for enhancing locality is a limiting factor for processing large graphs. Therefore, we design SEGA, a scalable graph accelerator that can achieve high performance without exploiting locality and temporal partitioning. In this section, we will explore the microarchitectural and system-level considerations that enable the scalability of graph processing to handle large-scale graphs. Our main objectives are twofold: first, to decouple performance from the on-chip memory size and eliminate the need for temporal partitioning for large graphs, and second, we will investigate a system-level approach to creating a balanced graph accelerator that maximizes performance while minimizing cost (i.e., with the least over-provisioning of bandwidth and capacity) as we scale to large graphs.

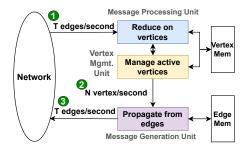

Prior work achieves high (though not full) utilization of their edge memory bandwidth by placing vertices in on-chip memory. However, since on-chip memory is limited, it must be temporally shared between different partitions of the graph. We eliminate the need for temporal partitioning by storing and processing vertices in off-chip storage, mitigating the performance degradation caused by temporal partitioning. Furthermore, we architect a balanced design such that messages are processed at the rate they are generated, and active vertices are available to generate messages at the rate they are processed. Figure 3.3 shows a logical diagram of SEGA where we decouple the reduction operations from the message propagation. The rest of this section describes how we decouple vertex processing from edge-based message propagation so they can run at different rates through the message processing unit (Section 3.3.2), the message generation unit (Section 3.3.3), and the vertex management unit (Section 3.3.4).

FIGURE 3.3. Logical demonstration of a balanced system.

Algorithm 1 Decoupled message-driven implementation for single source shortest path.

```

\operatorname{dist}[:||V||] = \infty;

messages.append(\{u,0\});

while not messages.empty() do

for u, \delta in messages do

old_dist = dist[u];

dist[u] = min(old\_dist, \delta);

if old_dist != dist[u] then

active_list.append(u);

while not active_list.empty() do

for v in active_list do

start, end = row_ptr[v], row_ptr[v+1];

active_vertex_info.append({dist[v],start,end});

while not active_vertex_info.empty() do

for \alpha, start, end in active_vertex_info do

for i in range(start, end) do

dest = edge_dests[i];

\epsilon = \mathbf{add}(\alpha, \text{edge\_wgt[i]});

messages.append(\{\text{dest}, \epsilon\});

```

3.3.1. System-level design of SEGA. SEGA consists of one or many graph processing nodes (GPNs). The building block of a GPN is a processing elements (PE). A single PE is a message-driven processor capable of executing algorithms expressed using the model described in Algorithm 1. Algorithm 1 shows the decoupled message-driven implementation of the SSSP workload. For SSSP, the reduce function is the minimum function, and the propagate function is the addition function. Decoupling the reduction from message propagation enables SEGA to support both asynchronous [104] and bulk synchronous parallel [90] execution models. In the bulk synchronous parallel execution, the red block (message propagation) is executed serially after there

are no more messages to process in the blue block (message processing). This serial execution is enforced by the decoupled active list (shown in yellow). When executing in bulk-synchronous mode, these three blocks continue to execute until no messages are generated, i.e. the program has converged. In asynchronous [104] execution, all blocks are executed simultaneously until there are no more messages.

A PE consists of three main units which correspond to the three parts of Algorithm 1. The colors of the units in Figure 3.3 and Figure 3.4 correspond the colors in Algorithm 1 as well.

- Message processing unit processes messages and updates vertices. It determines the new property of a vertex using the reduce function.

- Vertex management unit keeps track of active vertices from the message processing unit and sends active vertices to the message generation unit.

- Message generation unit uses active vertices and their edges to generate new messages. It produces the update in a message using the propagate function.

For every vertex processed by the message processing unit, there can be many messages generated by the message generation unit since each vertex can have many outgoing edges. This one-to-many relationship where one message creates many messages can cause the buffers on the message processing units to become full which introduces backpressure and queuing at the message generation unit. However, to empty the incoming message queue we must have available buffers in the message generation unit. Thus, we need a way to deal with the back pressure in the system without causing deadlock when the system is overwhelmed with messages. To break this deadlock, we decouple message processing from message generation with the active vertex management unit. The combination of active vertex management unit and the decoupling allows us to support bulk synchronous execution.

The message processing unit *pushes* new active vertices into the active\_list in the vertex management unit, and when the message generation unit is ready to accept more work, it *pulls* from the vertex management unit. The vertex management unit allows the active vertices to *spill* into the vertex memory if the work generation and work consumption are not balanced. By decoupling the push and the pull from the message processing and generation units, the vertex management unit allows SEGA to balance the work generation and fully utilize the off-chip bandwidth resources.

**3.3.2.** Message Processing Unit. The primary function of the message processing unit is to process vertices based on incoming network messages. To process a message  $(\langle u, \delta \rangle)$ , the destination vertex (u) has to be read. After the vertex has been read, its property (e.g., distance in case of SSSP) and the message's update  $(\delta)$  are used by the reduce function (e.g., minimum in case of SSSP) to determine the new property of the vertex. In addition, the read, modify, and write steps on each vertex should be done atomically to ensure correctness.

Due to a lack of locality in accesses, reading vertices from DRAM can result in long access latency. The message processing unit utilizes a hardware managed buffer to track multiple atomic operations and hide the access latency. Nevertheless, due to the massive size of some graphs, it is unlikely that the buffer can capture much locality. In our implementation, we have configured this buffer with a size of 64 KiB for each PE (512 KiB per GPN). We have evaluated the effect of the size of this buffer in Section 3.5.

When the read data arrives from the memory, the whole memory block is placed in this buffer and the destination vertex (u) is sent to the reduction engine. After the reduction, the memory block data in the buffer is updated with the new copy of the vertex.

SEGA manages this buffer as a direct-mapped cache, and the following steps are taken upon insertion and eviction.

**Insertion:** blocks of memory are placed in this buffer every time a vertex has to be read. The location of a block of memory in this buffer is determined using a direct-mapped function based on vertex's address. Therefore, it is possible that two read requests collide with each other, in which case the two requests have to be serialized.

Eviction: blocks of memory are evicted from the buffer in two circumstances. (1) The whole buffer is flushed back to the memory upon the completion of execution. (2) Blocks of memory are written back to memory upon a read conflict. Before a block is evicted, if it contains active vertices, the message processing unit notifies the vertex management unit of this eviction. The vertex management unit will track this memory block as an active block for use by the message generation unit.

The choice of a direct-mapped function for the placement is an appropriate decision because conflicts are not frequent enough for an associative design to exhibit significant benefits. We found that  $\sim 4\%$  of the accesses result in conflict. Therefore, the choice of direct-mapped placement results in lower latency and simpler design.

3.3.3. Message Generation Unit. The main purpose of the message generation unit is to propagate messages to the destination vertex. The messages are generated using the edges<sup>1</sup> of active vertices from the vertex management unit (an active vertex is an updated vertex that needs to communicate its value to its neighbors). The unit initiates its process by reading an entry from the active vertex buffer (as described in the next subsection). Each entry in the active vertex buffer has three members  $< \alpha, start, end >$ .  $\alpha$  denotes the property of the active vertex, and < start, end > identifies the location of its edges in the edge memory.

For each edge,  $\langle v, w \rangle$ , in  $\langle start, end \rangle$ , a message is generated. The destination of the message is determined by the destination vertex of the edge (v), and the message update is calculated using the propagate function on the property of the vertex  $(\alpha)$  and the weight of the edge (w). Subsequently, the message is sent to the network, where it is received by its designated message processing unit. The addressing function is assigned at initialization time since vertices are statically assigned to PEs.

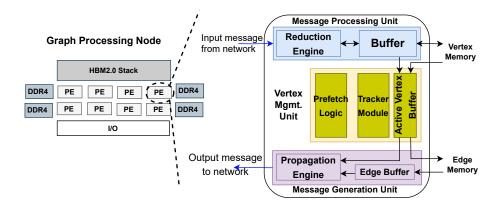

Figure 3.4. Hardware implementation of processing elements.

**3.3.4.** Vertex Management Unit. The main role of the vertex management unit is to: 1) keep track of active vertices assigned to a PE and 2) send active vertices to the message generation unit.

<sup>&</sup>lt;sup>1</sup>We store the destination vertex and edge weight in the edge memory and the vertex property values and other CSR metadata such as index array pointers in the vertex memory.

The vertex management unit has three main components. (1) An on-chip memory to keep track of active vertices in the vertex memory (tracker module in Figure 3.4). (2) A first-in-first out buffer to send active vertices to the message generation unit (active vertex buffer in Figure 3.4). (3) Control logic for searching and recovering active vertices from the vertex memory (prefetch logic in Figure 3.4). In the following section, we discuss the details of the implementation of each component and how the vertex management unit accomplishes its tasks.

During the execution of our graph accelerator, new active vertices can be generated faster than messages created from prior active vertices because each active vertex generates multiple messages (i.e., one vertex can connect to multiple edges). Therefore, the active vertices will quickly outgrow the on-chip memory size in the message processing unit. Due to the one-to-many relationship between vertices and edges and the presence of fixed-size queues in the system, storing all active vertices on limited on-chip storage causes a deadlock. In this scenario, active vertices are spilled to the backing vertex memory to prevent stalls or potential deadlocks. The active vertices spilled from the buffer can overwrite their previous values in the vertex memory. However, to accurately execute the application, these spilled active vertices will have to be accessed and sent to the message generation unit.

When the message generation unit has the bandwidth for creating and sending new messages, spilled active vertices are accessed and sent to the message generation unit. To access the spilled active vertices, we can perform an associative search in the vertex memory or track the spilled active vertices. Performing associative searches in DRAM is significantly more expensive compared to SRAM. Hence, we developed a tracking mechanism to allow the vertex management unit to track the location of these off-chip active vertices.

Naively, keeping a single bit for every vertex in the graph would enable us to track the active vertices, but it would result in significant on-chip capacity. For example, in WDC12, a structure that keeps 1 bit per vertex would require approximately 440 MiB of on-chip storage. In addition, the size of the vertex data structure can vary greatly depending on the program or programmer, making it difficult to predict the number of vertices that need to be tracked with a constant capacity for tracking information.

We take three approaches to track active vertices efficiently: (1) We track locations in memory with active vertices, not the vertices themselves, (2) we group these locations in memory (memory

blocks) into superblocks to reduce the tracking metadata, and (3) prefetch active vertices before they are requested from the message generation unit.

While graph workloads operate at the granularity of vertices, any transaction with the vertex memory happens at a fixed size referred to as the block size. We will refer to a block of the memory that stores at least one active vertex as an active block. Tracking active blocks instead of active vertices has two main benefits. (1) Unlike vertices, which are program-specific data structures, a memory block has a fixed size; separating the size of the vertex management unit from the size of the vertex data structure. (2) It is safe to assume that a block of the vertex memory is bigger than the size of a vertex. Tracking active blocks instead of active vertices allows us to reduce the size of the tracking information.

In SEGA, we track active vertices based on a superblock of N blocks and count the number of active blocks in the superblock. Therefore, the capacity to implement the tracker module could be significantly reduced by grouping more blocks into a superblock. The total capacity required by such an implementation could be calculated using Equation 3.2 and Equation 3.3 where  $super\_block\_dim$  denotes the number of memory blocks grouped into a superblock, and  $block\_size$  denotes the block size for the vertex memory. In our implementation, we use  $super\_block\_dim = 128$  and HBM2 ( $block\_size = 32~B$ ) as our vertex memory. Given these parameters, only 1 MiB of on-chip storage is required to track a 4 Hi stack of HBM2 with a capacity of 4 GiB (128 KiB per PE). Storing WDC12 vertices with 4 B for each vertex requires 4 HBM2 stacks and only 4 MiB of on-chip storage across four GPNs.

It should be noted that grouping memory blocks is a middle ground between tracking one bit per vertex and no tracking at all. Therefore, instead of **eliminating** the need for performing an associative search in the vertex memory, this implementation **reduces** the amount of associative search. We analyze the sensitivity of performance to the size of the tracker module in Section 3.5.4.2.

$$(3.2) cap_{bits} = (\log_2 super\_block\_dim + 1) * num\_super\_blocks$$

$$num\_super\_blocks = \frac{vertex\_memory\_capacity}{super\_block\_dim * block\_size}$$

Finally, the message generation unit depends on the vertex management unit for its execution. Therefore, the vertex management unit needs to fetch and deliver activate vertices to the message generation unit in a timely manner. To hide the latency of searching for active vertices in the vertex memory, the vertex management unit takes advantage of a buffer (active vertex buffer) to prefetch active vertices.

The active vertex buffer is an 80-entry buffer that can be populated with active blocks of vertices. The prefetch logic is configured to read 16 blocks of memory from a superblock whenever there are 16 or more entries available in the buffer. When the data arrives from the memory, only the active blocks are placed in the buffer. The remaining blocks are dropped. In turn, this associative search in DRAM results in some wasted bandwidth. We have investigated the effect of vertex recovery on the utilization of vertex memory bandwidth in Section 3.5.4.2.

**3.3.5.** Choice of off-chip Memory. In graph workloads, vertices and edges have different requirements for capacity and bandwidth. In general, edges require a larger memory capacity compared to vertices. In most graph programming models [56, 73], access to edges is sequential and read-only. In contrast to edges, vertices have low spatial and temporal locality in most graph algorithms. This lack of locality results in a long memory access latency. Due to these differences, we have chosen a heterogeneous system for the off-chip memory in a GPN.

We have chosen HBM2 as the off-chip memory to store vertex information. HBM2 is an appropriate choice for storing vertex because it offers substantially more bandwidth under **random** access patterns [94]. Moreover, HBM allows for finer granularity accesses (32 bytes), resulting in less bandwidth waste.

To store the edges, we have chosen DDR4 as the off-chip memory. This is because the edge information is accessed with a **mostly sequential** and **read-only** pattern. Lastly, for most graphs, edges require a much bigger storage than vertices. Therefore, DDR4 is an appropriate choice for storing the edges because of its high capacity density compared to HBM2 and its high bandwidth under sequential access. Fariborz et al. showed heterogeneous memory system is the most cost-effective solution for creating a system that meets the capacity and bandwidth requirements of the two data structures [34].

We have assigned eight PEs to one stack of HBM2 memory (eight channels). Each PE is dedicated to one channel of the HBM2 stack and operates only on the vertices stored in that channel. Fariborz et al. show that vertex memory needs to offer  $4\times$  the bandwidth of the edge

memory [34]. Therefore, we have allocated four DDR4 channels for the edge memory for each GPN ( $\frac{1}{2}$  of a channel per PE) to create this balance.

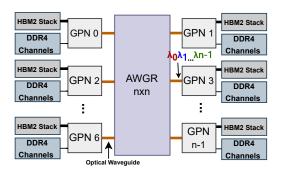

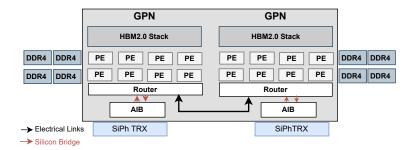

FIGURE 3.5. System-level architecture of SEGA with n GPNs. To scale to the Size of WDC12 (3.6 Billion vertices and 128.7 Billion edges) SEGA requires eight GPNs (n=8) using 8×8 AWGR with eight wavelengths per port is used. [79]

3.3.6. Graph Processing System Using GPNs. Figure 3.4 shows the layout of one SEGA node or GPN. A GPN consists of multiple PEs connected through an interconnected network and off-chip memory as storage for storing the vertices and edges. We connect PEs within one GPN through a point-to-point on-chip electrical network. Scaling to larger graphs is possible by connecting multiple GPNs together. The choice of the inter-GPN interconnect is an important design decision as it affects both the bandwidth and energy/bit. Electrical interconnects can support the bisection bandwidth for small number of GPNS. However, when scaling to more than 8 GPNs (to support WDC12) we propose using optical interconnectss.

Optical links provide low latency, high bandwidth density through wavelength division multiplexing (WDM) [65], and distance-independent energy consumption and latency. By exploiting WDM one GPN can connect to multiple GPNs through a single optical IO pin (addressing them on different wavelengths), enabling high-radix and low-diameter networks. Array Waveguide Grating Router (AWGR) [79] is a passive silicon photonic fabric with a compact layout that offers scalable all-to-all connectivity through wavelength routing. Recent advances in the fabrication process of AWGRs now enable their integration with a significantly reduced footprint (1 mm<sup>2</sup>), crosstalk (< -38dB), and loss (< 2dB) [79]. Initial studies have shown AWGR to be a promising choice for processor-to-memory network [36, 37]. The number of ports in an AWGR can easily scale up to 64 ports [26]. We propose to use an Array Waveguide Grating Router (AWGR) based optical

network [37,79] as the inter-GPN interconnection network as shown in Figure 3.5 that can easily scale to WDC12.

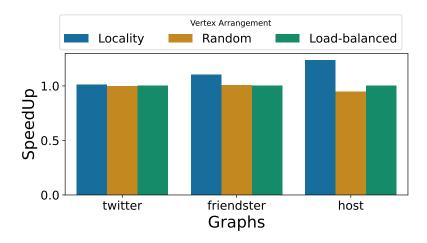

3.3.7. Spatial Vertex Mapping. In our proposed architecture, each vertex and its edges are assigned to a single PE. Choosing the vertex assignment is a tradeoff between preprocessing cost, load balancing, and locality. In a load balanced system, a similar number of edges are assigned to each PE for processing. The approach to optimizing load balance is to sort the vertices by their out-degree and distribute the vertices with the highest out degrees uniformly across PEs. Interleaving vertices between PEs with a fine granularity ensures load balance. In the locality-based approach, we used community detection techniques such as RABBIT [13] to detect highly connected vertices and assign sequential ids to vertices in each community. By taking advantage of locality, we can reduce network traffic at the cost of a lower load balance. We can also use the original ordering made by the graph publisher and eliminate any pre-processing. In this case, we interleave the vertices based on their vertex IDs between PEs, assigning a similar number of vertices to each PE.

3.3.8. Summary of Design. As described in this section, we create a balanced architecture by (1) decoupling vertex and edge processing to process edges and vertices at different rates; (2) spilling active vertices to HBM and tracking the active vertices to avoid expensive off-chip memory search; (3) using a heterogeneous memory system that optimizes the different memory access patterns in the graph workloads with higher vertex bandwidth to edge bandwidth; (4) proposed using a passive optical all-to-all interconnect to scale out the accelerator to multiple nodes enabling support for larger graphs.

To extract maximum throughput, active vertices need to be sent to the message generation unit at a high rate (path 1 in Figure 3.3). On the other hand, messages generated by the message generation unit should also be processed at the same rate (path 2 in Figure 3.3). Both these criteria require vertices to be processed with low latency.

In a graph workload, for every modified vertex, multiple messages will be created depending on the degree of the active vertex. Therefore, the message processing unit needs to process the incoming messages at a faster rate than the message generation unit creates them (path 3 in Figure 3.3). Separating vertex and edge processing allows the accelerator to process vertices at a higher rate. By decoupling, the message generation unit requests new work when it has enough bandwidth at

| Specifications per GPN | SEGA                                                                |

|------------------------|---------------------------------------------------------------------|

| # PE                   | 8 @ 2GHz                                                            |

| Spad                   | 512  KB (buffer) + 1  MiB (VMU)                                     |

| Vertex memory          | ${\rm HBM2~stack}$ - ${\rm 8GB~cap.}$ - ${\rm 256GB/s}$             |

| Edge memory            | 4 DDR4 channels - 128GB cap 76.8GB/s                                |

| Inter-GPN Net.         | $8\times 8$ SiN AWGR, 8 Wavelengths per port, 4GiB/s per wavelength |

Table 3.2. System specifications.

the edge memory. Since the vertex processing is faster, SEGA ensures that the message generation engine can pull active vertices upon request.

Now the size of on-chip memory is no longer dictated by the size of the graph. In our design, the on-chip hardware buffer simply hides the long off-chip memory access latency instead of storing all active vertices. We sized the on-chip buffer using Little's law based on the message generation rate of the edge memory and the average vertex latency when running with random traffic.

Finally, the active vertex management acts as an intermediary between message generation and processing, allowing the processing unit to store active vertices in off-chip memory without performing costly associative searches by tracking the locations of spilled vertices. Simultaneously, this unit enhances the message generation engine's ability to read active vertices at a faster rate by prefetching them from the buffer or DRAM.

#### 3.4. Methodology

We implemented our model in gem5 v22.0 [57]. We implement cycle-level models for all the modules in a GPN (Figure 3.4) proposed message generation unit, message processing unit, vertex management unit, and a model for the point-to-point interconnect network and AWGR at 2GHz in gem5. We used gem5's models for HBM2 and DDR4 memories. The implementations of SEGA is shown in Table 3.2.

We also implemented a model of PolyGraph [29] in gem5 including the partitioning of a large graph into slices. We compared our performance to PolyGraph since it already showed better performance compared to notable graph accelerators such as GraphPulse, Chronos, Ozdal, and Grapicionado [10, 40, 68, 75], and software platforms such as Ligra, and Galois. [73, 81].

**3.4.1.** Workloads. We implemented five graph analytics workloads specified in GAPBS [17]. We used breadth first search (BFS), connected components (CC), single source shortest path

| Graph                 | Footprint            | Vertices          | Edges | Description     |

|-----------------------|----------------------|-------------------|-------|-----------------|

| RoadUSA [1]           | $805.7~\mathrm{MiB}$ | 23.9M             | 58.3M | Road graph      |

| Twitter [ <b>49</b> ] | $14.4~\mathrm{GiB}$  | $41.65\mathrm{M}$ | 1.46B | Social network  |

| Friendster [49]       | $15.4~\mathrm{GiB}$  | 65.6M             | 1.8B  | Social network  |

| Host [8]              | $16.6~\mathrm{GiB}$  | 101M              | 2B    | Hyperlink graph |

| Urand [ <b>33</b> ]   | $34.0~\mathrm{GiB}$  | $134.2\mathrm{M}$ | 4.2B  | Synthetic graph |

Table 3.3. Graph Workloads used in evaluations.

(SSSP), page rank (PR) and betweenness centerality (BC). We have implemented BFS, CC, and SSSP in the asynchronous mode, while PR and BC are implemented in the bulk-synchronous mode. BC in its proposed asynchronous implementations requires forward and backward passes, which doubles the number of edges required to be stored. Our implementation of PR-delta as specified by [75] proved to be very sensitive to the order of the traversal of the graph. To find the optimal order of traversal requires an overall view of the graph at the timing of scheduling updates. Therefore, ordering is not a feasible solution for problem sizes that are significantly bigger than the size of on chip resources. Hence, we have chosen to implement PR in BSP mode.

**3.4.2.** Input Graphs. Our objective is to evaluate how SEGA performs for large graphs. Table 3.3 demonstrates the details of each of our input graphs. We have used a combination of synthetic graphs (Urand and RMAT [51]) along with real-world graphs such as Twitter. Previous accelerators used Twitter and RMAT  $2^{26}$  as their largest graph input [29,67]. We evaluate SEGA using Urand which has  $2\times$  more vertices and  $1.5\times$  edges compared to Twitter, as the input to our workloads.

#### 3.5. Evaluation

To evaluate the performance of SEGA, we conducted a thorough evaluation across multiple dimensions. This includes (1) performance comparison with PolyGraph, (2) strong and weak scaling, (3) estimation of resources needed for PolyGraph, Dalorex, and SEGA to scale to WDC12 size graphs, and (4) the sensitivity analysis of GPNs to various design parameters, such as buffer size, and the size of memory used by vertex management unit to track active vertices in the main memory, and different vertex placements between PEs.

**3.5.1. Scaling to Terascale Graphs.** WDC12 [8] is a hyperlink graph representing 3.5 billion web pages and 128 billion hyperlinks. This is representative of future terascale graph analytics.

| Accelerator | HBM             | DDR       | SRAM/  | Cores  | # of       |

|-------------|-----------------|-----------|--------|--------|------------|

|             | Stacks          | Channels  | eDRAM  |        | Partitions |

| SEGA        | 14 (56 GiB)     | 56 (1TiB) | 21 MiB | 112    | 1          |

| PolyGraph   | 272 (1.088 TiB) | -         | 4 GiB  | 2176   | 15         |

| PolyGraph   | 256 (1 TiB)     | -         | 56 GiB | 6400   | 1          |

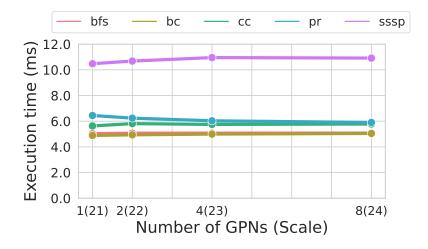

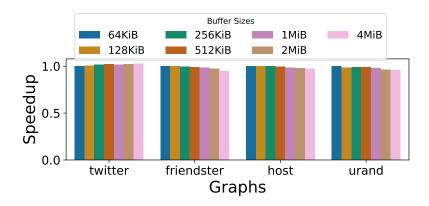

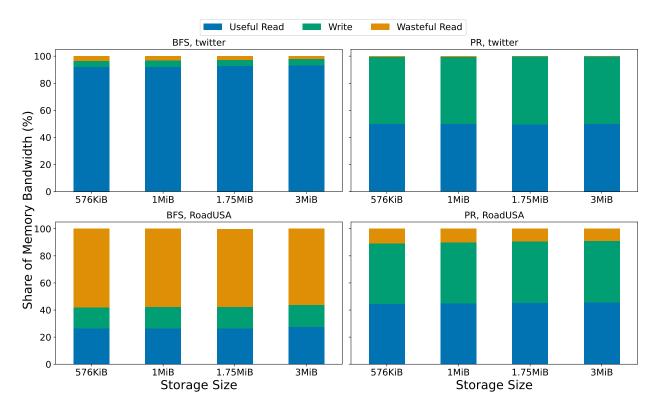

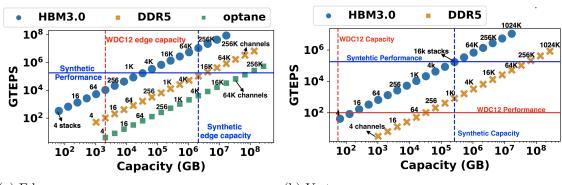

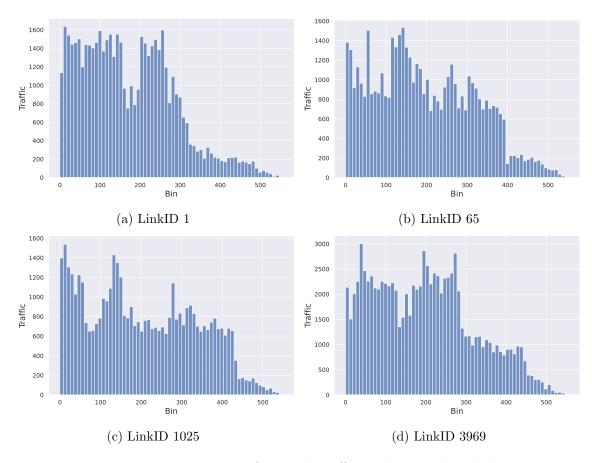

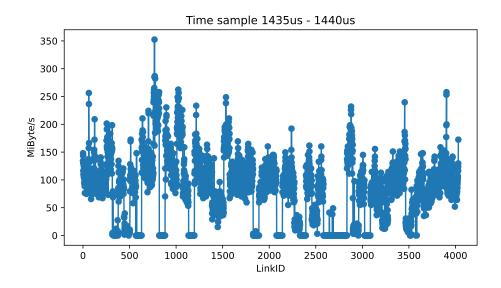

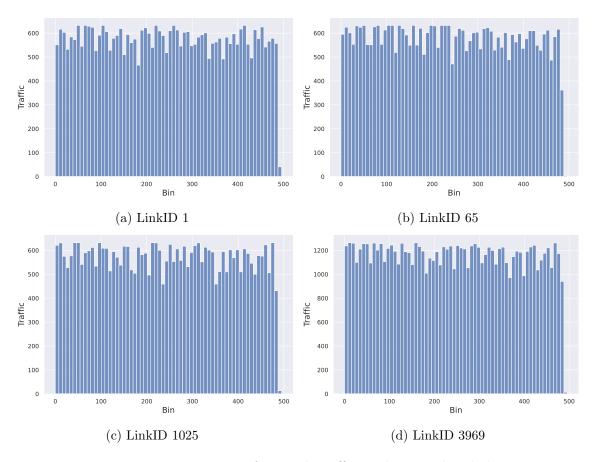

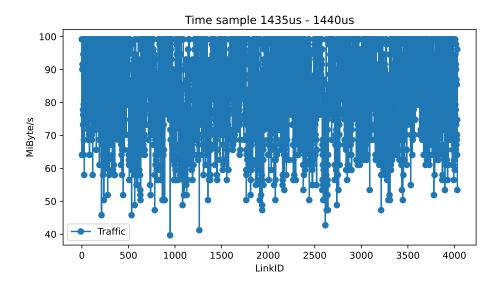

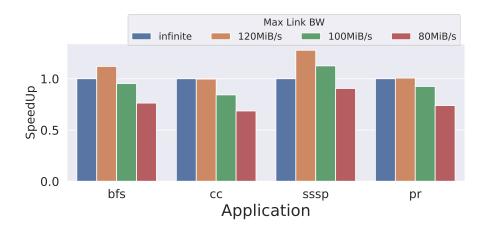

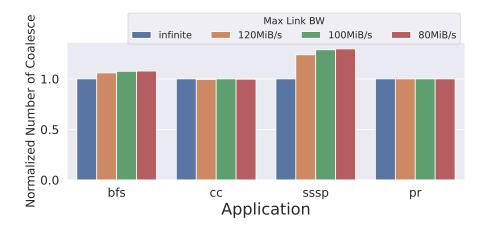

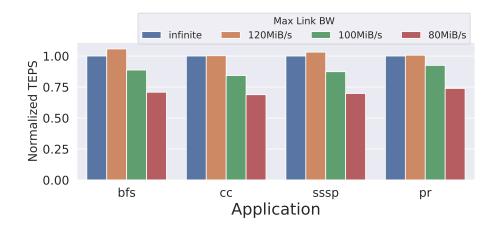

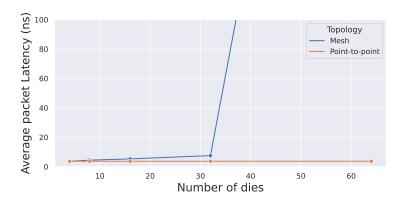

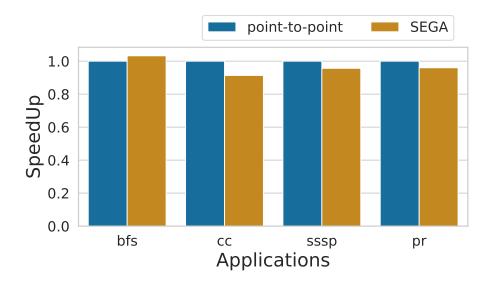

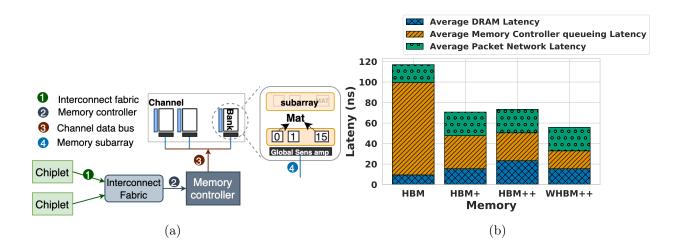

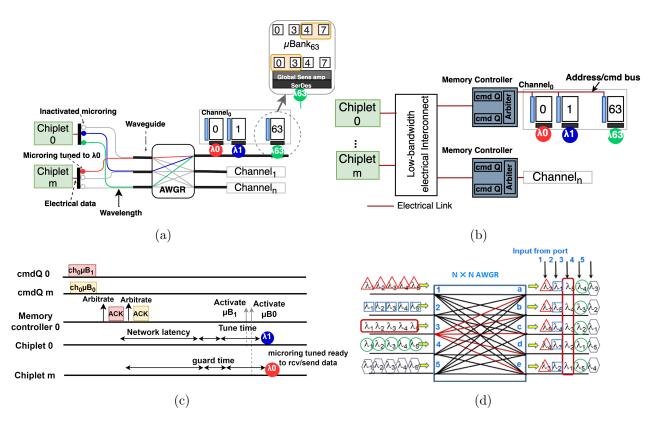

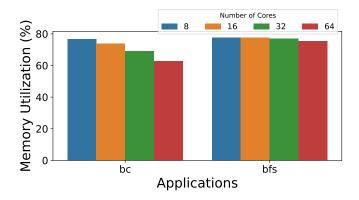

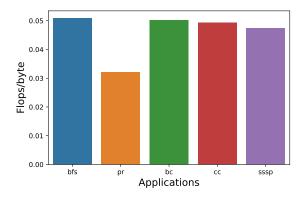

| non-sliced  |                 |           |        |        |            |