## UC Riverside UC Riverside Electronic Theses and Dissertations

#### Title

Parallel CAD Algorithms and Hardware Security for VLSI Systems

#### Permalink

https://escholarship.org/uc/item/1tj3k5mm

## Author

He, Kai

# Publication Date 2016

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA RIVERSIDE

Parallel CAD Algorithms and Hardware Security for VLSI Systems

A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

**Electrical Engineering**

by

Kai He

August 2016

Dissertation Committee:

Dr. Sheldon Tan, Chairperson Dr. Qi Zhu Dr. Daniel Wong

Copyright by Kai He 2016 The Dissertation of Kai He is approved:

Committee Chairperson

University of California, Riverside

#### Acknowledgments

This thesis could not have been completed without the great support that I have received from so many people over the years. I wish to offer my most heartful thanks to the following people.

I would like to thank my advisor, Prof. Sheldon Tan for guiding and supporting me over years. He has set an example of excellence as researcher, mentor, instructor and role model. His kindness, insight and suggestions always lead me to the right way.

I would like to thank my thesis committee members, Prof. Qi Zhu and Prof. Daniel Wong for their direction, dedication and invaluable advice.

I would like to thank all the members in our VSCLAB. I thank especially Xuexin, Zao, Xin, Tan, Taeyoung, Haibao, Yan, David, Yue, Hengyang, Zhongdong, Chase and Zeyu for the collaborative research works, discussion and help, which lead to the presented works in this thesis. I appreciate the friendship of my fellow students in UCR.

Last but not least, I would like to thank my wife and my parents for the love, support, and constant encouragement during the years of my study. I undoubtedly could not have done this without them. To my wife and my parents for all the support.

#### ABSTRACT OF THE DISSERTATION

Parallel CAD Algorithms and Hardware Security for VLSI Systems

by

Kai He

#### Doctor of Philosophy, Graduate Program in Electrical Engineering University of California, Riverside, August 2016 Dr. Sheldon Tan, Chairperson

As integration scales to the 20nm regime and below, the integrated circuit (IC) design has seen the billion transistor counts. For instance, the latest Pascal GPU using 16nm FinFET technology from Nvidia has 150 billion transistors. As a result, it becomes very challenging to verify those billion-transistor chips and there is an urgent need to develop advanced and parallel simulation technique. On the other hand, the counterfeit ICs have become a major security threat for commercial and mission-critical systems. In addition to the huge economic impacts, they post significant security and safety threats on those systems. The objective of this thesis is to develop new techniques to address above two tough issues encountered in VLSI research: new fast parallel circuit simulation and potential solutions to mitigate the counterfeit IC problem.

To accelerate the circuit simulation, we study several important linear algebra operations in simulation steps, such as sparse matrix-vector multiplication (SpMV), direct linear LU factorization and iterative general minimum residual linear solver. Parallel computing such as general purpose GPU programs are good solutions for improving performance of these operations. We apply GPU for these tasks and attain impressive speedup over traditional or CPU methods. All algorithms and implementations are demonstrated with representative numerical experiments and thorough comparisons among different methods and platforms.

For various types of counterfeit ICs - recycled, remarked, cloned, out-of-spec, and over-produced, we propose a multi-functional on-chip sensor and post-authentication policy for detecting and preventing them. Especially for recycled ICs, we propose two kinds of aging sensors, which are based on electromigration (EM)-induced aging effects and ringoscillator (RO)-based frequency aging effects. These two aging sensors can effectively detect chip usage time for both short and long periods. Simulated results show the advantage of the proposed multi-purpose sensor against the existing on-chip sensors in terms of functionality, detection coverage and usage time estimation range and accuracy.

# Contents

| List | of | Figures |

|------|----|---------|

|------|----|---------|

$\mathbf{xiv}$

## List of Tables

| 1        | Intr | oducti  | lon                                                              | 1         |

|----------|------|---------|------------------------------------------------------------------|-----------|

|          | 1.1  | Introd  | uction                                                           | 1         |

|          |      | 1.1.1   | Parallel Sparse Linear Algebra for Circuit Simulation            | 1         |

|          |      | 1.1.2   | Recycled Integrated Circuits – Detection and Avoidance           | 4         |

|          |      | 1.1.3   | Goal and Dissertation Contributions                              | 7         |

|          |      | 1.1.4   | Organization of the thesis                                       | 9         |

| <b>2</b> | GP   | U-Acc   | elerated Parallel Sparse LU Factorization                        | 10        |

|          | 2.1  | Introd  | uction                                                           | 10        |

|          | 2.2  | Review  | w of LU factorization algorithms and CUDA                        | 14        |

|          |      | 2.2.1   | Right-looking factorization method                               | 14        |

|          |      | 2.2.2   | Left-looking factorization method                                | 15        |

|          |      | 2.2.3   | Related works                                                    | 17        |

|          |      | 2.2.4   | Review of GPU Architecture and CUDA programming                  | 19        |

|          |      | Propo   | sed GLU solver based on the hybrid column-based right-looking LU |           |

|          |      | metho   | d on GPU platforms                                               | 22        |

|          |      | 2.3.1   | The column-based right-looking algorithm                         | 22        |

|          |      | 2.3.2   | Preprocessing and symbolic analysis                              | 25        |

|          |      | 2.3.3   | Numerical computing phase                                        | 30        |

|          |      | 2.3.4   | Parallel implementation on GPU                                   | 32        |

|          | 2.4  | Nume    | rical results and discussions                                    | 34        |

|          |      | 2.4.1   | Performance comparisons                                          | 36        |

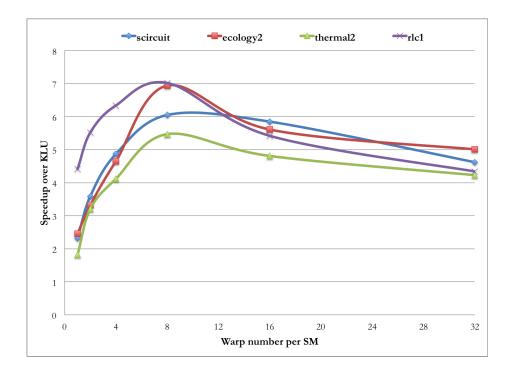

|          |      | 2.4.2   | Impacts of warp number on performance                            | 42        |

|          | 2.5  | Summ    | ary                                                              | 43        |

| 3        | Par  | allel G | MRES Solver on GPU Platforms                                     | <b>45</b> |

|          | 3.1  | Introd  | uction                                                           | 45        |

|          | 3.2  | Review  | w of power gird simulation and GPU architecture                  | 49        |

|          | 3.3                    | Parallel GMRES solver on the GPU-CPU platform                     | 49<br>51   |

|----------|------------------------|-------------------------------------------------------------------|------------|

|          |                        |                                                                   | $51 \\ 54$ |

|          |                        | -                                                                 | 54<br>58   |

|          | 3.4                    |                                                                   | 60         |

|          | <b>J</b> .1            |                                                                   | 61         |

|          |                        |                                                                   | 65         |

|          | 3.5                    |                                                                   | 70         |

|          | 0.0                    |                                                                   | 71         |

|          |                        |                                                                   | 74         |

|          |                        |                                                                   | 76         |

|          |                        | U A                                                               | . •<br>79  |

|          |                        |                                                                   | 82         |

|          | 3.6                    | · ·                                                               | 85         |

| 4        | $\mathbf{E}\mathbf{M}$ | -Based on-Chip Aging Sensor for Detection and Prevention of Recy- |            |

| -        |                        |                                                                   | 86         |

|          | 4.1                    | Introduction                                                      | 86         |

|          | 4.2                    | Review of EM effects and EM models                                | 90         |

|          |                        | 4.2.1 Review of EM-induced failure effects                        | 90         |

|          |                        | 4.2.2 Physics-based EM model                                      | 95         |

|          | 4.3                    | Proposed EM-based aging sensor circuit                            | 97         |

|          |                        | 4.3.1 Wire structure for accurate EM-Induced aging detection      | 97         |

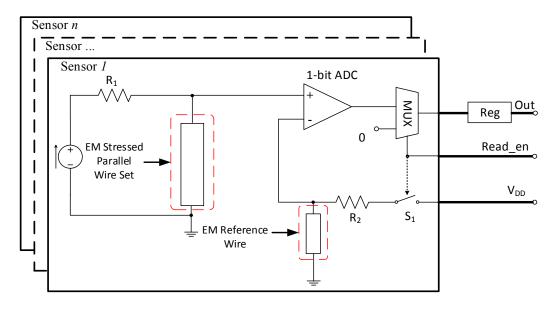

|          |                        | 4.3.2 Resistance detection sensor circuit                         | 99         |

|          | 4.4                    | Performance analysis and experimental results                     | 01         |

|          |                        | 4.4.1 Effect of number of wires 1                                 | 01         |

|          |                        | 4.4.2 Effect of length of wires                                   | 02         |

|          |                        | 4.4.3 Experimental results                                        | 05         |

|          | 4.5                    | Summary 1                                                         | 08         |

| <b>5</b> | $\mathbf{Mu}$          | ti-Functional On-Chip Sensor for Comprehensive Detection of Coun- |            |

|          |                        |                                                                   | 09         |

|          | 5.1                    |                                                                   | 09         |

|          |                        |                                                                   | 11         |

|          |                        |                                                                   | 13         |

|          | 5.2                    |                                                                   | 15         |

|          |                        | 0                                                                 | 15         |

|          |                        |                                                                   | 18         |

|          |                        |                                                                   | 21         |

|          | 5.3                    |                                                                   | 23         |

|          | 5.4                    |                                                                   | 26         |

|          |                        | 0 0                                                               | 28         |

|          |                        | 8 8                                                               | 30         |

|          |                        | 5.4.3 Performance analysis and comparison                         | 33         |

|    | 5.5              | Summ   | nary                                                       | 135 |

|----|------------------|--------|------------------------------------------------------------|-----|

| 6  | Con              | clusio | n                                                          | 136 |

|    | 6.1              | Summ   | ary of Research Contributions                              | 137 |

|    |                  | 6.1.1  | GPU-accelerated sparse linear algebra for VLSI systems     | 137 |

|    |                  | 6.1.2  | Potential solutions to mitigate the counterfeit IC problem | 138 |

| Bi | Bibliography 141 |        |                                                            |     |

# List of Figures

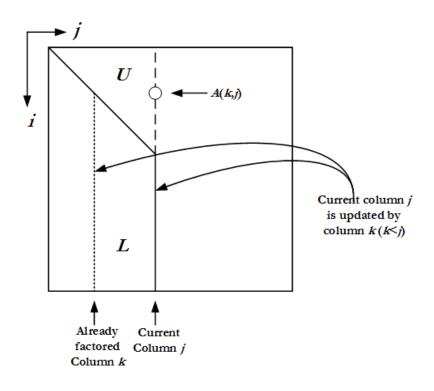

| 2.1  | Left-looking update for column $j$                                                     | 18 |

|------|----------------------------------------------------------------------------------------|----|

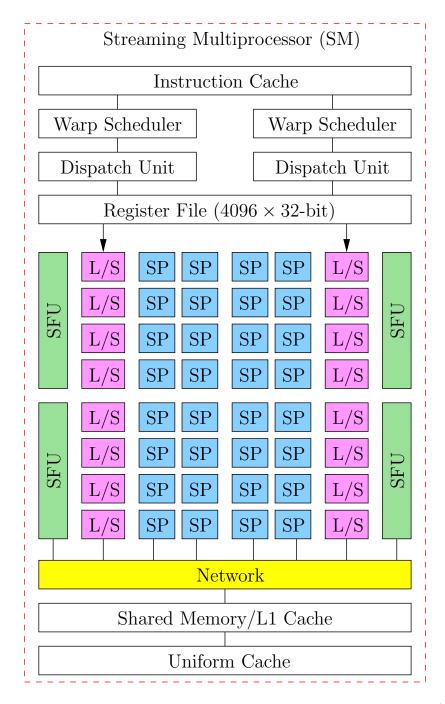

| 2.2  | Diagram of a streaming multiprocessor in NVIDIA Tesla C2070. (SP is                    |    |

|      | short for streaming processor, L/S for load/store unit, and SFU for Special            |    |

|      | Function Unit.)                                                                        | 20 |

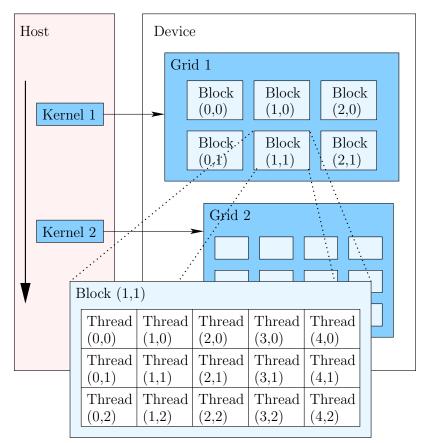

| 2.3  | The programming model of CUDA                                                          | 21 |

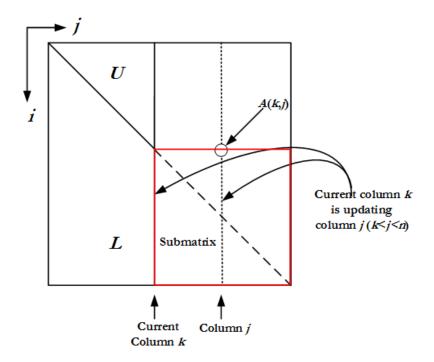

| 2.4  | The illustration of the hybrid column-based right-looking algorithm and the            |    |

|      | submatrix update at each iteration                                                     | 24 |

| 2.5  | Nonzero pattern for a sparse triangular solver.                                        | 27 |

| 2.6  | The original matrix $A$ (left) and the matrix $A$ (right) after symbolic analysis      |    |

|      | with predicted nonzero pattern of LU factors of $A$                                    | 28 |

| 2.7  | The illustration of the resource-aware levelization scheme.                            | 29 |

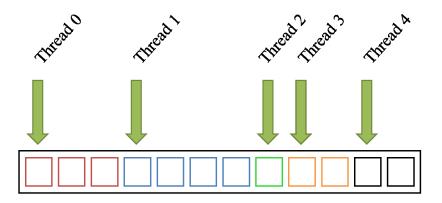

| 2.8  | The comparison of the concurrency exploitation on GPU in terms of warp                 |    |

|      | scheduling.                                                                            | 34 |

| 2.9  | Speedup over KLU vs. number of warps per SM on K40c                                    | 42 |

| 0.1  |                                                                                        | -  |

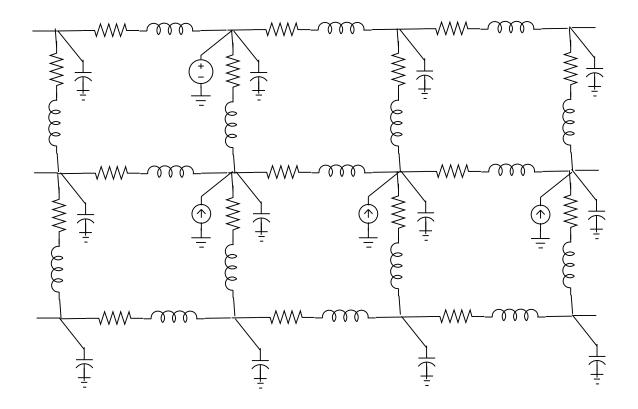

| 3.1  | An RLC model of power grid network.                                                    | 50 |

| 3.2  | The proposed GPU-accelerated parallel preconditioned GMRES solver. We                  |    |

|      | also show the partitioning of the major computing tasks between CPU and                |    |

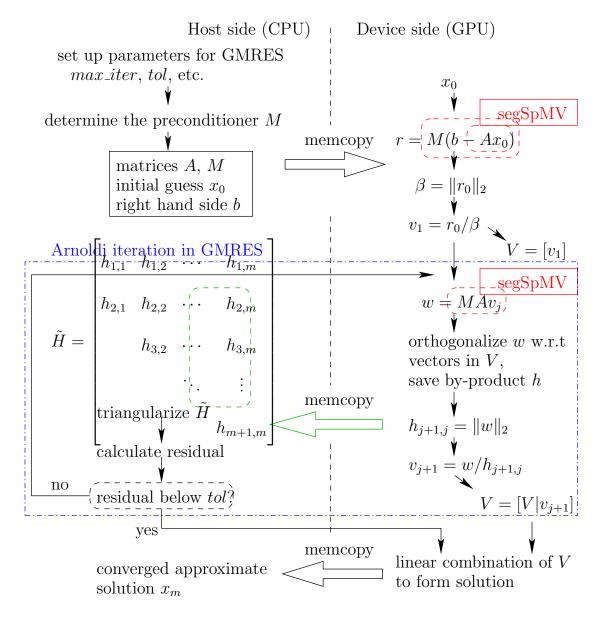

| 0.0  | GPU here                                                                               | 57 |

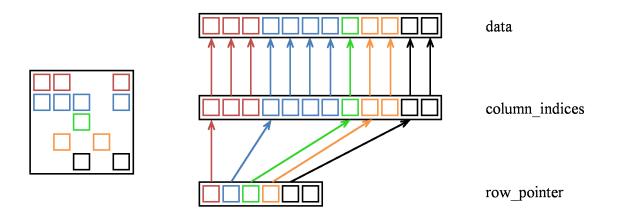

| 3.3  | The CSR format of a sparse matrix                                                      | 61 |

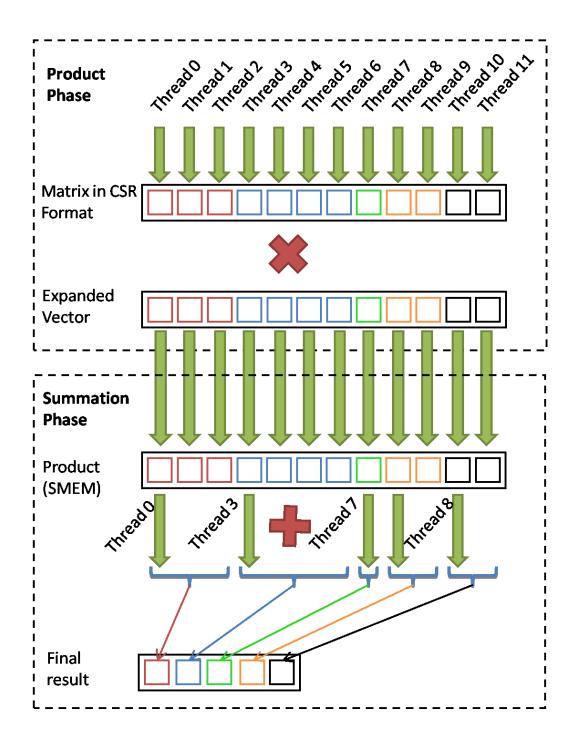

| 3.4  | The illustration of the row-based $B\&G$ algorithm                                     | 62 |

| 3.5  | The illustration of the warp-based $B\&G$ algorithm                                    | 63 |

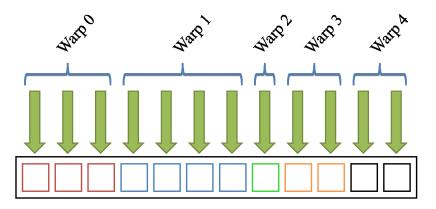

| 3.6  | The vector expansion concept in the $P\&S$ method $\ldots \ldots \ldots \ldots \ldots$ | 64 |

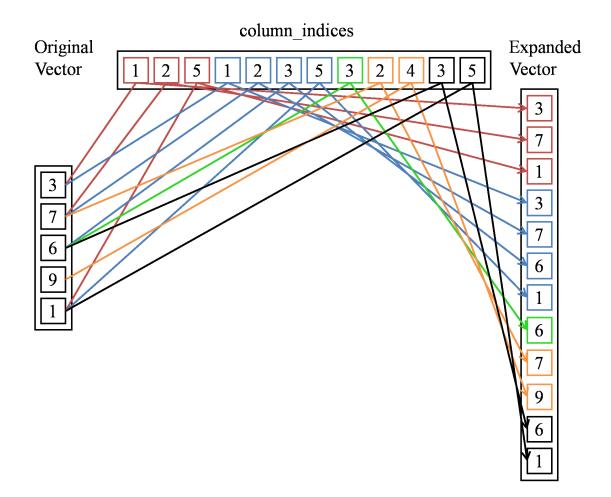

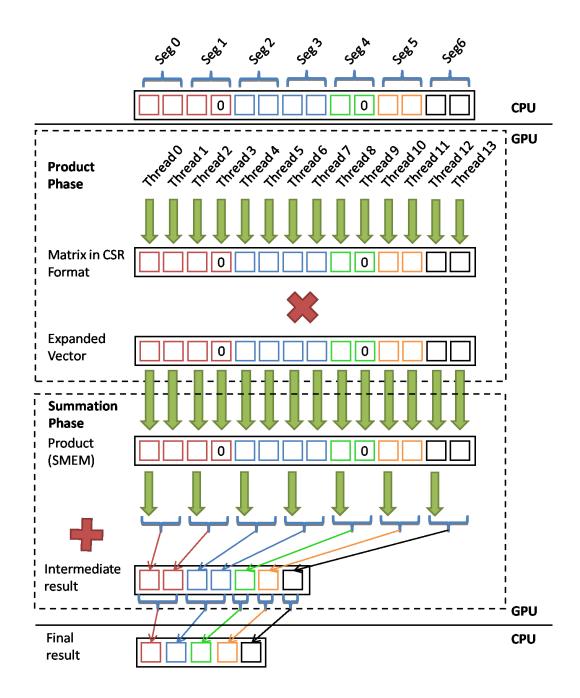

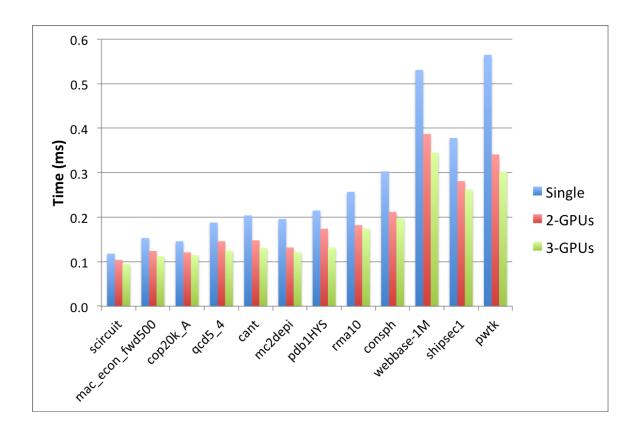

| 3.7  | The illustration of the $P\&S$ algorithm                                               | 66 |

| 3.8  | The proposed segment-SpMV method or segSpMV method                                     | 69 |

| 3.9  | The performance comparison of multi-GPU segSpMV method                                 | 75 |

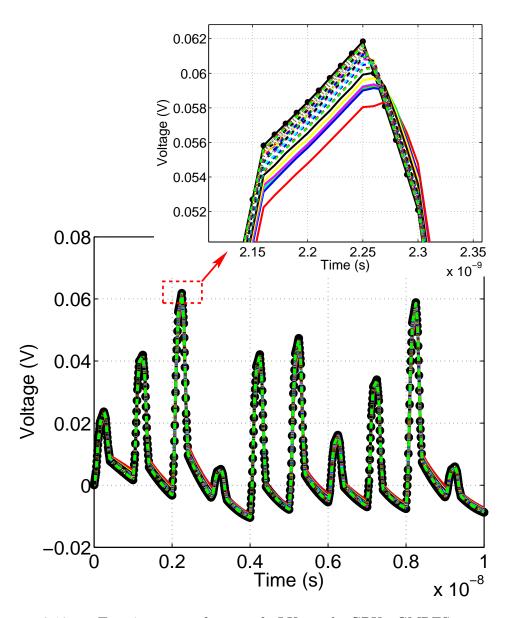

| 3.10 | Transient waveforms of LU and GPU GMRES at port node n0_5480720_1102640                |    |

|      | in ibmpg6t. The black curve with dots is from LU direct method. All other              |    |

|      | colored curves are results of GMRES with preconditioners set to different              |    |

|      | ILU threshold, i.e., from 0.1 to 3.0                                                   | 77 |

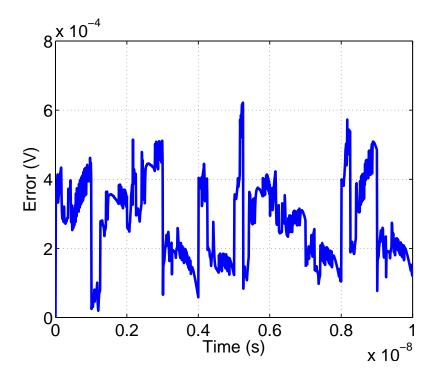

|      | The error of GPU GMRES result compared to LU golden result. This curve is calculated at node n0_5480720_1102640 of ibmpg6t, whose waveform is shown in Fig. 3.10.                                                                                                                                                                                                                              | 78   |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

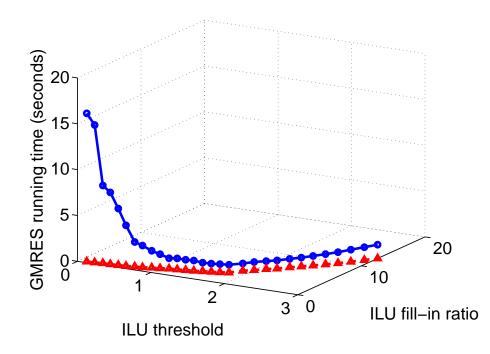

| 3.12 | The impact of ILU threshold on fill-in ratio and GMRES solving time. The<br>blue curve in 3D space is GMRES solving time with respect to threshold and<br>fill-in ratio, and the red curve on the bottom plane reflects the changes of<br>fill-in ratio caused by different threshold values. All the measurements are                                                                         |      |

|      | from ibmpg4t                                                                                                                                                                                                                                                                                                                                                                                   | 82   |

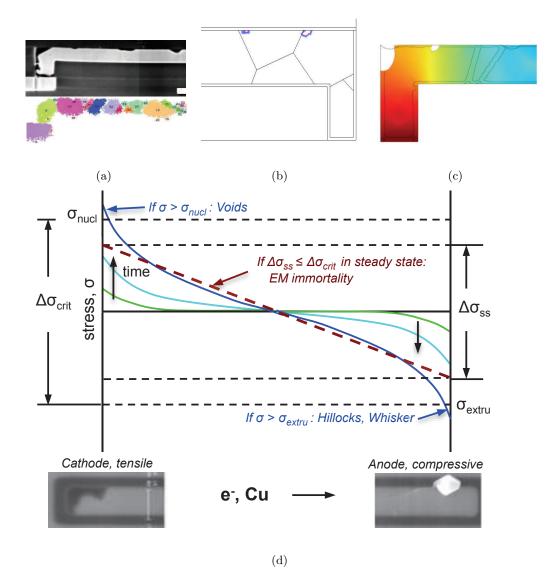

| 4.1  | (a): TEM picture of voids nucleated at the top interface, [1], (b) and (c): simulated kinetics of the void nucleation at the triple points and growth (electron flow from right to left), [2], (c): simulated growth of the line corner void by scavenging the vacancy flux and agglomerating with the small voids drifting along the top interface [3]. (d) The EM-induced stress development |      |

|      | and distribution of an interconnect wire                                                                                                                                                                                                                                                                                                                                                       | 93   |

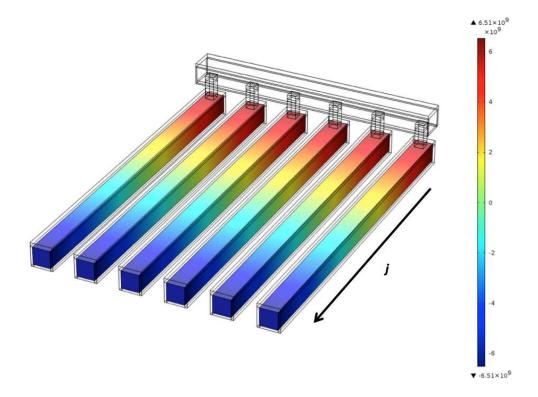

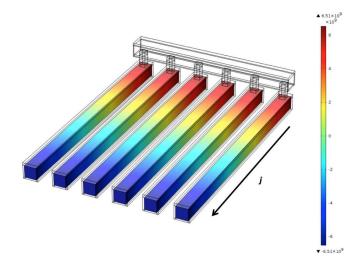

| 4.2  | The proposed parallel multi-wire structure for the aging sensor and its stressed                                                                                                                                                                                                                                                                                                               |      |

|      | condition                                                                                                                                                                                                                                                                                                                                                                                      | 98   |

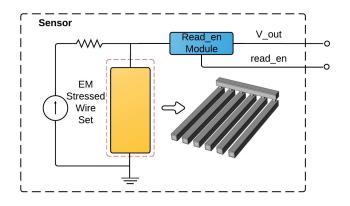

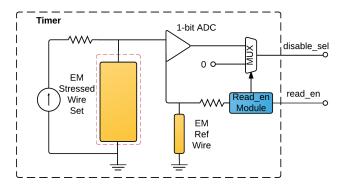

| 4.3  | The structure of the EM-based aging sensor.                                                                                                                                                                                                                                                                                                                                                    | 100  |

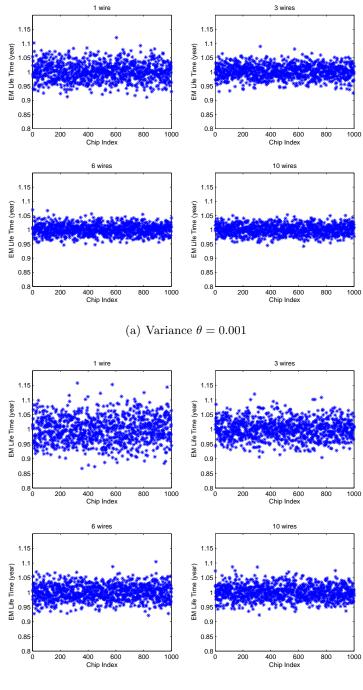

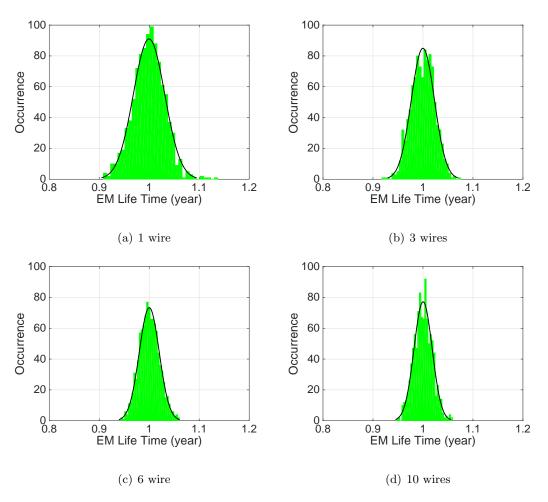

| 4.4  | (a) and (b) the statistical study of stressed wires connected in parallel with                                                                                                                                                                                                                                                                                                                 |      |

|      | different wire numbers and variations.                                                                                                                                                                                                                                                                                                                                                         | 103  |

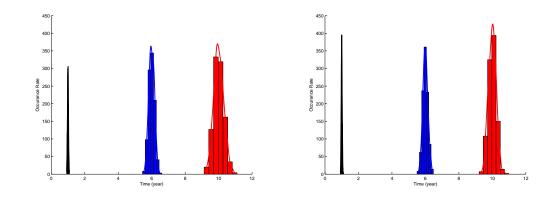

| 4.5  | The statistical lifetime detections from the stressed wires: (a) using the con-<br>stant 6 wires; (b) using the varying number wires (6 wires for 1 year, 10 wires                                                                                                                                                                                                                             |      |

|      | for 6 years, and 14 wires for 10 years)                                                                                                                                                                                                                                                                                                                                                        | 104  |

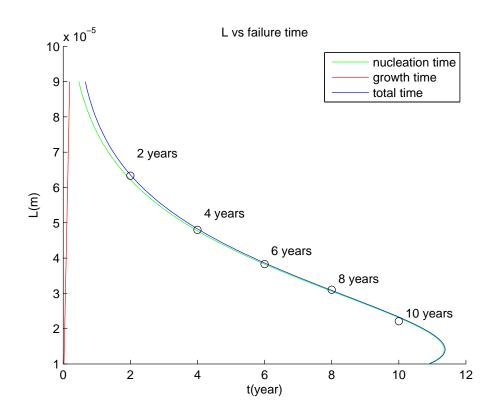

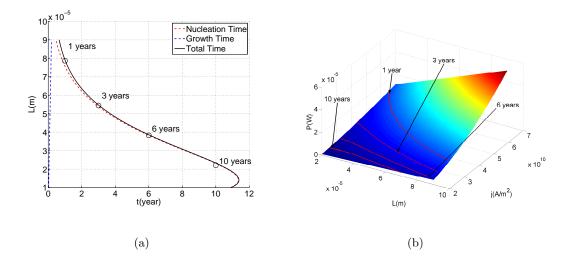

| 4.6  | Length versus EM lifetime of a wire.                                                                                                                                                                                                                                                                                                                                                           | 105  |

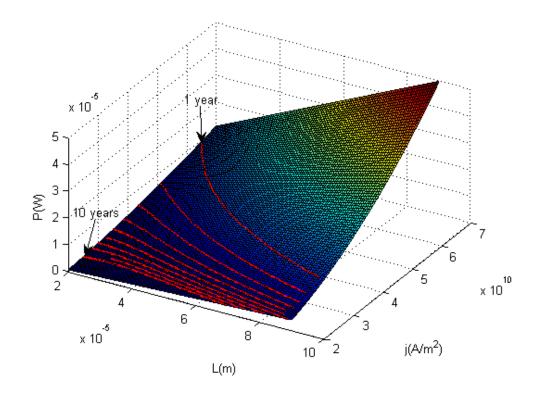

| 4.7  | The power consumption of stress wires versus wire length and current density                                                                                                                                                                                                                                                                                                                   | .106 |

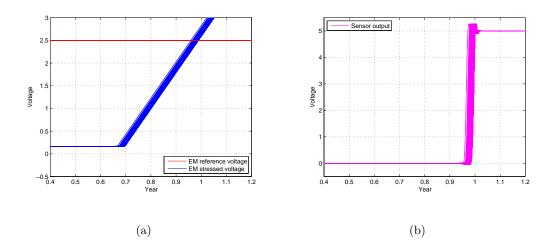

| 4.8  | (a) The statistical voltage inputs for the ADC; (b) The statistical ADC out-                                                                                                                                                                                                                                                                                                                   |      |

|      | put.                                                                                                                                                                                                                                                                                                                                                                                           | 107  |

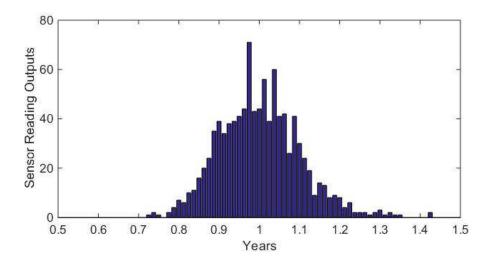

| 4.9  | The statistical distribution of the lifetime of the sensor wires detected                                                                                                                                                                                                                                                                                                                      | 107  |

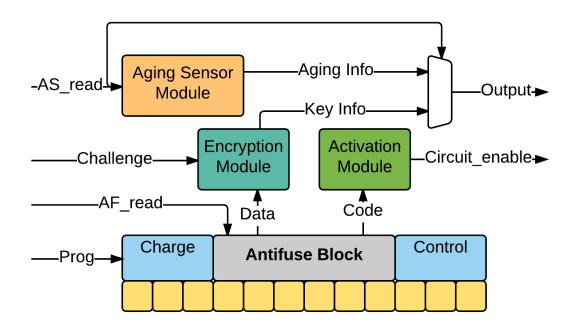

| 5.1  | The architecture of proposed on-chip sensor                                                                                                                                                                                                                                                                                                                                                    | 116  |

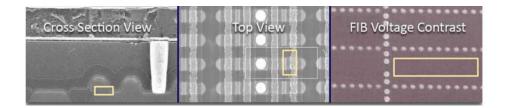

| 5.2  | CMOS logic antifuse physical layer security                                                                                                                                                                                                                                                                                                                                                    | 118  |

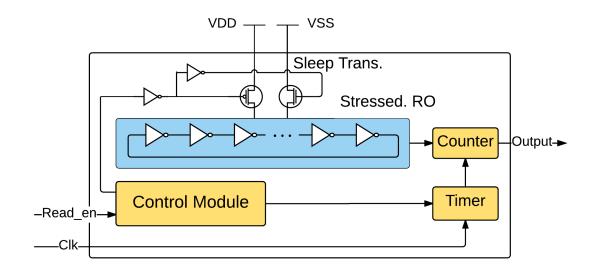

| 5.3  | Structure of RO aging sensor                                                                                                                                                                                                                                                                                                                                                                   | 119  |

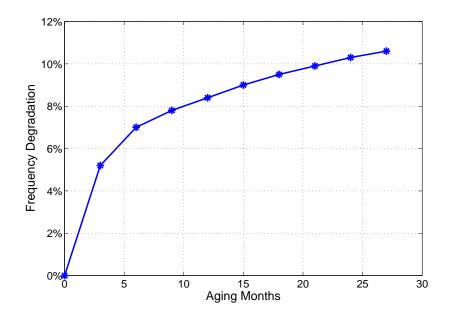

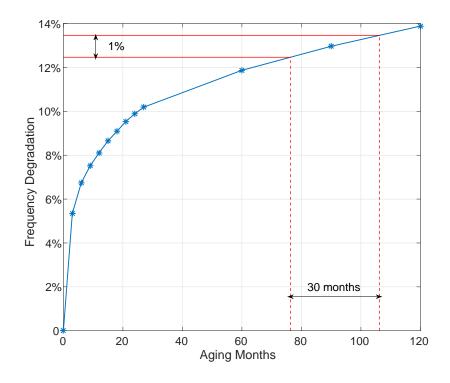

| 5.4  | Frequency degradation of a 5-stages RO                                                                                                                                                                                                                                                                                                                                                         | 120  |

| 5.5  | The multi-wire structure                                                                                                                                                                                                                                                                                                                                                                       | 121  |

| 5.6  | The EM sensor-only circuit                                                                                                                                                                                                                                                                                                                                                                     | 122  |

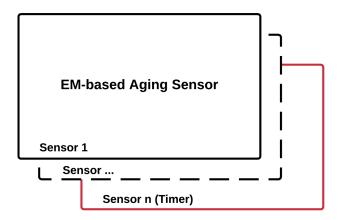

| 5.7  | The whole aging sensor with multiple EM sensors and timers                                                                                                                                                                                                                                                                                                                                     | 122  |

| 5.8  | The structure of EM aging sensor                                                                                                                                                                                                                                                                                                                                                               | 123  |

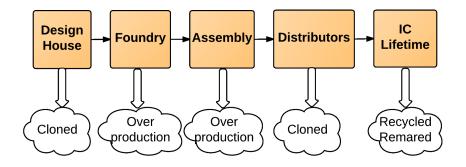

| 5.9  | The electronic component supply chain and vulnerabilities                                                                                                                                                                                                                                                                                                                                      | 124  |

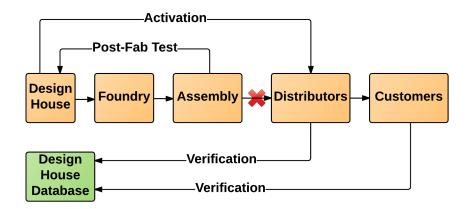

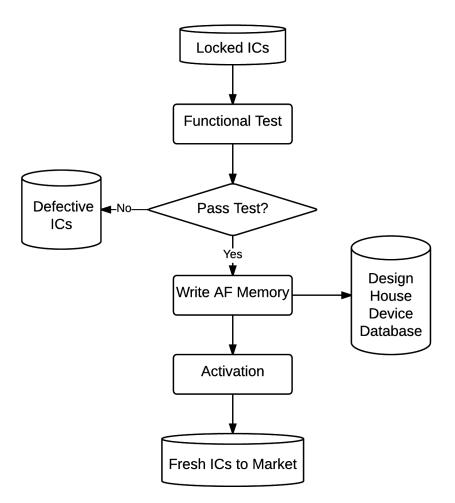

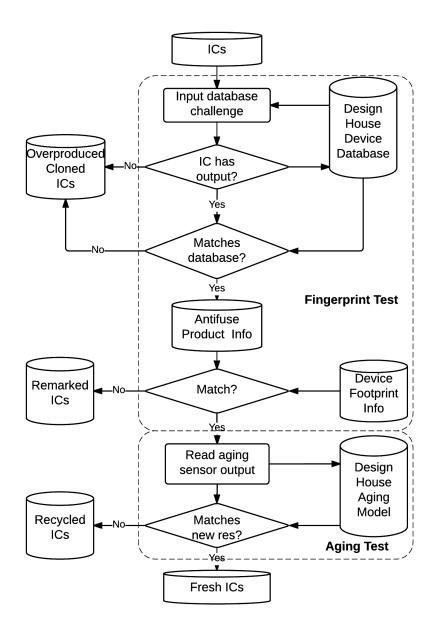

| 5.10 | The proposed supply chain with post-fabrication authentication                                                                                                                                                                                                                                                                                                                                 | 125  |

| 5.11 | The proposed post-fabrication authentication                                                                                                                                                                                                                                                                                                                                                   | 126  |

|      | The proposed comprehensive detection methodology for counterfeit ICs                                                                                                                                                                                                                                                                                                                           | 127  |

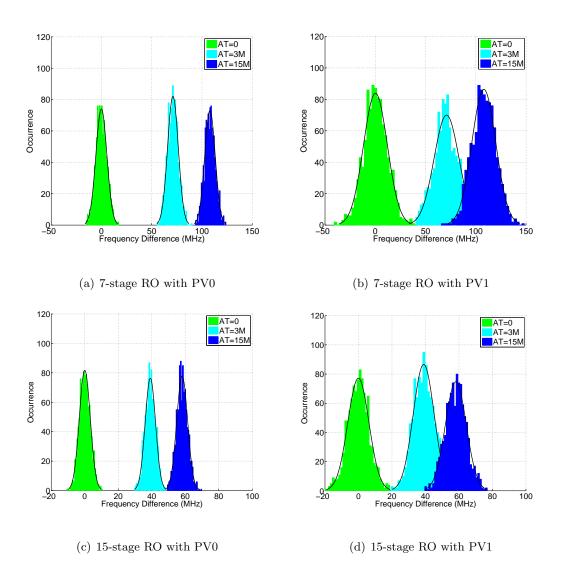

| 5.13 | Process variation impacts on frequency spreading and recycled IC detection                                                                                                                                                                                                                                                                                                                     |      |

|      | probability.                                                                                                                                                                                                                                                                                                                                                                                   | 131  |

| 5.14 | The statistical study of stressed wire set with different wire numbers                                                                                                                                                                                                                                                                                                                         | 132  |

| 5.15 | (a) Length versus EM lifetime of a wire. (b) The power consumption of stress |     |

|------|------------------------------------------------------------------------------|-----|

|      | wires versus wire length and current density.                                | 133 |

| 5.16 | The RO-based aging sensor error rate for long period time                    | 134 |

# List of Tables

| 2.1 | The General Benchmark Matrices                                                                                                                                                                                                                         | 35  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2 | The Performance Comparison Over General Benchmark Matrices                                                                                                                                                                                             | 37  |

| 2.3 | The Circuit Benchmark Matrices                                                                                                                                                                                                                         | 38  |

| 2.4 | The Performance Comparison Over Circuit Benchmark Matrices                                                                                                                                                                                             | 40  |

| 3.1 | The matrices and their properties from UFL Sparse Matrix Collection                                                                                                                                                                                    | 72  |

| 3.2 | The performance comparison over UFL matrices on K40c GPU                                                                                                                                                                                               | 73  |

| 3.3 | Statistics of IBM power gird benchmarks and solver performance. Column 14                                                                                                                                                                              |     |

| 3.4 | lists the speed up of GPU GMRES over LU method on all the 1,000 time<br>step points in a transient simulation calculated as $\frac{C3+1000\cdot C4}{C6+C9+1000\cdot C12}$ The performance comparison of ILU preconditioners with different fill-in ra- | 79  |

|     | tios. The same circuit matrix from IBM power gird benchmark ibmpg4t is used in all the cases. GMRES convergence tolerance is set to $10^{-7}$                                                                                                          | 83  |

| 5.1 | Aging Sensor Comparison                                                                                                                                                                                                                                | 128 |

| 5.2 | Process variations used                                                                                                                                                                                                                                | 129 |

## Chapter 1

## Introduction

#### 1.1 Introduction

#### 1.1.1 Parallel Sparse Linear Algebra for Circuit Simulation

The verification of today's large linear global networks such as on-chip large power grid networks is very challenging for chip designers. Fast verification of voltage drops and other noises on power delivery networks is critical for final design closure. As the VLSI technology proceeds into sub-65 nm scale [4], one challenging job of power grid network is to predict and ensure a reliable on-chip power delivery.

Since the power grid network usually comes with a huge size, its simulation and verification take a lot of time, and sometimes even make the analysis completely failed. Intensive researches have been carried out to seek for efficient analysis of large power grid networks in the past decade. Various algorithms have been proposed to improve scalability in computing time and to reduce memory footprints [5, 6, 7, 8, 9]. But most of those tech-

niques are based on the homogeneous single-core architectures, which means their resource usage is still limited.

The course of computing has been permanently altered by the recent leap from single-core to multi-core or many-core technologies. Among them, the graphics processing unit (GPU), is one of the most powerful many-core computing systems arousing interests and input from both research and industry community [10]. Today, more and more high performance computing servers are equipped with GPUs as co-processors. These GPUs work in tandem with CPUs (on same computing node) connected by high-speed link like PCIe buses. GPU's massively parallel architecture allows high data throughput in terms of floating point operations (flops). For instance, the state-of-the-art NVIDIA Kepler K40c chip has a peak performance of over 4 Tflops performance in comparison with about 80– 100 Gflops of Intel i7 series quad-core CPUs [11]. Currently, GPUs or GPU-clusters can easily deliver tera-scale computing, which was only available on super-computers in the past, for solving many large scientific and engineering problems.

Until now, dense linear algebra support on GPU is well developed, with its own BLAS library [12], but sparse linear algebra support is still limited. Modern NVIDIA GPUs are throughput-oriented many-core processors that can offer very high peak computational throughput. They favor computations exhibiting sufficient regularity of execution paths and memory access patterns. For sparse-matrix-based analysis, there are two kinds of solvers in general: the direct LU solver and the iterative solver. Although there are some recent efforts in this direction [13, 14], the sparse direct LU solvers on GPU is considered to be difficult due to the irregular structure of matrices and the complicated data dependency during the numerical LU factorization. As a result, there remain a challenge for GPU-based fine-grained parallel LU solver. On the other hand, iterative solvers, which mainly depend on simple operations such as matrix-vector multiplication and inner product of vectors, are more amicable for parallelization, especially on GPU platforms. There are some newly published papers, such as [15, 16, 17, 18, 19], which confirm the practicality and effectiveness of iterative solvers in solving large linear dynamic networks like power grid networks.

Several research efforts have been proposed for parallelizing sparse LU factorization on shared memory multi-core CPU and GPUs. SuperLU [20, 21] implemented supernodebased Gilbert-Peierls (G/P) left-looking algorithm [22], and SuperLU\_MT [21] is its multithreaded parallel version developed for shared memory multi-core architectures. However, it is not easy to form super-node in some sparse matrix such as circuit matrix. KLU [23], which is specially optimized for circuit simulation, adopts Block Triangular Form based on G/P left-looking algorithm.

Recently, the KLU algorithm has been parallelized on multi-core architecture by exploiting the column-level parallelism [24, 25]. However, for parallel LU factorization solvers on GPU, existing works mainly focus on dense matrices including [26, 27, 28], very few works on the sparse matrix have been proposed. Ren *et al.* recently proposed a GPU-based sparse LU solver based on the G/P left-looking algorithm [14]. It exploits the column-level parallelism due to sparse nature of the matrix. The left-looking based method, which transforms the factorization computing into a number of triangular matrix solving, seems more efficient on GPU computing. But it possesses higher data dependency coming from solving the triangular matrices. The traditional right-looking LU factorization, which involves only less data dependent vector operations, has not been well studied in GPU implementation.

There are also some research works for GPU-based iterative solver for sparse systems [29, 30, 31, 32, 33, 34, 35, 36]. In [30], GMRES solver has been accelerated on GPU by simply parallelizing the computing of polynomial preconditioners. In [31], Jacobipreconditioned conjugate gradient algorithm is parallelized based block compressed row storage format. But this solver only works on single GPU and symmetric matrices. Work in [36] proposed a parallel GMRES based on existing GPU-enabled BLAS library [12]. Also a few existing works have been proposed to explore the hybrid accelerators such as GPUs and Xeon Phi.

#### 1.1.2 Recycled Integrated Circuits – Detection and Avoidance

The counterfeiting and recycling of integrated circuits (ICs) have become major problems in recent years. These ICs potentially impact the security of electronic systems especially for military, aerospace, medical and other critical applications. In addition to diminishing system dependability and usability, counterfeiting reduces total revenue of companies from their research and development efforts, discourages innovation through the theft of intellectual properties (IPs), and produces low-quality products under established brand names [37]. According to couterfeit IC categorization and definition in [38], an electronic part is considered as as a counterfeit component which is not genuine if it is an unauthorized copy; or it does not conform to the original component manufacturer's (OCM) design, model, and/or performance; or it is not produced by the original component manufacturer or is produced by unauthorized contractors; or it is an off-specification, defective, or used OCM product sold as "new" or working; or it has incorrect or false markings and/or documentation.

Today the most widely reported type of counterfeit parts is the recycled type. It is reported that in today's supply chain, more than 80% of the counterfeit components are recycled [39]. These used or defective ICs enter the market when electronic "recyclers" divert scrapped circuit boards away from their designated place of disposal for the purposes of removing and reselling the ICs on those boards. The recycling process involves removing ICs from the board or even dies in the ICs. There are several security issues associated with these ICs. Firstly, a used IC can act as a ticking time bomb [40] since it does not meet the specification of the OCM of the ICs; secondly additional die on top of the recovered die can carry a back-door attack, sabotage circuit functionality under certain conditions, or cause a denial of service [41].

The detection methods for recycled chips can be classified into physical methods and electrical methods [37]. Physical methods consist of incoming inspection methods such as visual inspection, X-ray imaging, package analysis method such as laser scanning microscopy, delid method, and the material analysis method such as using Fourier transform infrared, and X-ray fluorescence. Electrical methods contain the parameter tests, function tests, built-in tests and structural tests. In general, physical methods can be applied to all part types, but some of the methods are destructive and take hours to test. As a result, sampling is required to certify a batch of parts by observing a small number of parts. On the other hand, conventional electrical test methods are non-destructive and time efficient, yet they can be very expensive because such techniques are not necessarily designed for counterfeit detection. Electrical test techniques are advantageous because the sampling is not required, and all parts can be tested. However, there are some issues associated with electrical tests that must be addressed.

In order to fast detect and effectively prevent the recycled chip, one viable approach is to insert a lightweight aging detecting sensor, which can directly tell the usage of the chips and some early efforts have been explored [42, 43, 44]. Method in [43] designed the ring-oscillator-based (OR-based) aging sensor that relies on the aging effects of MOSFETs to change a ring oscillator frequency in comparison with the reference one embedded in the chip. As the chip ages owing to the wear-out mechanisms such as negative biased temperature instability (NBTI) and hot carrier injection (HCI), the shift threshold voltage of MOSFET devices, thus the frequency of ring oscillator indicates the level of aging, and provides a simple readout of the value. However, this method can only give very rough estimation of the usage age of the chip as the shift of the frequency depends on many factors. In order to mitigate this problem, the antifuse-based (AF-based) sensor was developed in [37]. The AF-based sensor essentially is a counter, which counts the clocks or derivatives of the clock events to log the usage of the chip. The antifuse memory is used to make sure the data in the count will not be erased or altered by attackers. However, the AF-based sensors suffer large area overhead especially when more accurate usage is required [37]. Another problem with this method is that it may not reflect the true aging-dependent usage of a chip. For instance, it will log the same usage time for a chip for different on-chip temperatures, however, which can have dramatically impacts on the aging effects from electromigration, NBTI and HCI [45].

#### 1.1.3 Goal and Dissertation Contributions

Implementation of efficient and scalable numerical methods on highly-parallel processors is an interdisciplinary task. Our aim is to provide new highly parallel schemes and algorithms for building different direct and iterative solvers for circuit simulation and more general scientific computing on CPU-GPU platforms. Special focus goes to a hybrid rightlooking LU factorization algorithm and a general GPU-accelerated dynamic iterative solver with fast sparse matrix-vector multiplication.

On the other hand, for hardware security aspect, our goal is to design a lightweight on-chip sensor, which is based on electromigration-induced aging effects for fast detection and prevention of recycled ICs.

The contributions of this dissertation are summarized as follows:

• GPU-accelerated sparse LU solver We propose a new column-based right-looking LU factorization method, which is shown to be more amenable for exploiting the concurrency of LU factorization. The new method preserves the benefit of column-level concurrency and symbolic analysis in the left-looking method meanwhile, it allows more parallelism to be exploited. We show that the new *GLU* LU solver allows the parallelization of all three loops in the LU factorization on GPUs. In contrast, the existing GPU-based left-looking LU factorization approach can only allow two-level parallelization. We conduct comprehensive studies on the new GPU LU solver on a number of published general matrices, circuit matrices and self-made large RLC circuit matrices against some existing LU solvers to demonstrate the advantage of the proposed GLU solver.

- Preconditioned GMRES iterative solver on CPU-GPU platform We propose a new method called *GPU-GMRES*, which is based on the preconditioned Generalized Minimum RESidual (GMRES) iterative solver. We implemented it on heterogeneous CPU-GPU platforms with multiple GPUs. The proposed GPU-GMRES solver adopts a very general and robust incomplete LU based preconditioner with tunable fill-ins. We show that by properly selecting the right amount of fill-ins in the incomplete LU factors, a good trade-off between GPU efficiency and convergence rate can be made to achieve the best overall performance of the solver. Such tunable feature can make this algorithm very adaptive and flexible for different problems.

- EM-based on-chip sensor for recycled IC detection Instead of using traditional aging effects from devices (such as MOSFETs), the new EM-based aging sensor exploits the natural aging/failure mechanism of interconnect wires to time the aging of the chip. The new sensor is based on a newly proposed hydrostatic stress evolution model of EM effects for accurate prediction of the EM failure [46]. As a result, we can design the interconnect wire structures based on the copper interconnect technology so that the resulting wires can have detectable EM failure at a specific time with sufficient accuracy.

- Multi-Functional on-chip sensor for comprehensive detection of couterfeit ICs The proposed on-chip sensor can detect both recycled/remarked/out-of-spec chips, as well as cloned and over-produced ICs. The new on-chip sensor, which combines aging sensors with antifuse memory, can serve as a central on-chip security hardware IP for counterfeit IC detection, on-chip timer and post-fabrication authen-

tication and even activation module for ICs. On top of the new sensor hardware, we propose a post-fabrication authentication process to detect and prevent the nondetective counterfeit ICs.

#### 1.1.4 Organization of the thesis

The rest of this thesis is organized as follows.

To carry out parallel linear sparse algebra for circuit simulation, Chapter 2 starts from CPU-GPU based programming architecture, which is used to accelerate our proposed solvers. Then, Chapter 2 describes a novel column-based right-looking LU factorization method, and hence results in an efficient direct solver for circuit simulation and general scientific computing. In Chapter 3 we present an efficient parallel dynamic linear solver, called *GPU-GMRES*, for transient analysis of large linear dynamic systems such as large power grid networks.

For the recycled ICs detection and avoidance, we present a new lightweight on-chip aging sensor in Chapter 4. The EM effect and physics-based EM model is reviewed. Then the aging sensor as well as the interconnect wire structures are presented. We investigate the parameters of the sensor and show the trade-off between accuracy and area cost. In Chapter 5, a multi-functional on-chip sensor for comprehensive detection of counterfeit ICs is discussed. We also propose a post-authentication policy for detecting and preventing all kinds of counterfeit ICs, including the recycled/ remarked/out-of-spec ICs, as well as cloned and over-produced ICs.

Finally, Chapter 6 concludes the thesis with brief summaries of the works.

## Chapter 2

# GPU-Accelerated Parallel Sparse LU Factorization

#### 2.1 Introduction

Transforming a sparse matrix into its LU form is of crucial importance in linear algebra as it plays an important role in many numerical and scientific computing applications such as finite difference and finite element based methods. LU factorization operation represents the dominant computing cost in those problems and it is very important to improve the efficiency of the LU factorization algorithms. LU factorization for sparse matrices is the most important computing step for general circuit simulation problems for circuit designs. But parallelizing LU factorization on the popular many-core platforms such as Graphic Processing Units (GPU) turns out to be a difficult problem due to intrinsic data dependency and irregular memory access, which diminish GPU computing power. Modern computer architecture has shifted towards the multi-core processor [47, 48] and many-core architectures [49]. The family of GPU is among the most powerful manycore computing systems in mass-market use [10]. For instance, the state-of-the-art NVIDIA Kepler K40 GPU with 2880 cores has a peak performance of over 4 TFLOPS versus about 80–100 GFLOPS of Intel i7 series Quad-core CPUs [50, 11]. In addition to the primary use of GPUs in accelerating graphics rendering operations, there has been considerable interest in exploiting GPUs for general purpose computation (GPGPU) [51].

Until now, dense linear algebra support on GPU is well developed, with its own BLAS library [12], but sparse linear algebra support is still limited. Modern NVIDIA GPUs are throughput-oriented many-core processors that can offer very high peak computational throughput. They favor computations exhibiting sufficient regularity of execution paths and memory access patterns. For sparse-matrix-based analysis, GPU acceleration has been applied to parallelize the shooting-Newton method for transient radio-frequency circuit analysis [52] and to speedup the generalized minimum residual analysis (GRMES) based iterative method for large-scale thermal analysis [36] in the past. However, parallelizing the sparse LU factorization operation is very difficult because of the irregular structure of matrices and the high data-dependency during the numeric LU factorization. As a result, they remain a challenge for GPU-based fine-grained parallel computing [50].

Several research efforts have been proposed for parallelizing sparse LU factorization on shared memory multi-core CPU and GPUs. SuperLU [20, 21] implemented supernodebased Gilbert-Peierls (G/P) left-looking algorithm [22], and SuperLU\_MT [21] is its multithreaded parallel version developed for shared memory multi-core architectures. However, it is not easy to form super-node in some sparse matrix such as circuit matrix. KLU [23], which is specially optimized for circuit simulation, adopts Block Triangular Form based on G/P left-looking algorithm.

Recently, the KLU algorithm has been parallelized on multi-core architecture by exploiting the column-level parallelism [24, 25]. For parallel LU factorization solvers on GPU, existing works mainly focus on dense matrices including [26, 27, 28], very few works on the sparse matrix have been proposed. Ren *et al.* recently proposed a GPU-based sparse LU solver based on the G/P left-looking algorithm [14]. It exploits the column-level parallelism due to sparse nature of the matrix. The left-looking based method, which transforms the factorization computing into a number of triangular matrix solving, seems more efficient on GPU computing. But it possesses higher data dependency coming from solving the triangular matrices. The traditional right-looking LU factorization, which involves only less data dependent vector operations, has not been well studied in GPU implementation.

In this chapter, we propose a new sparse LU solver on GPUs for circuit simulation and more general scientific computing. The new method, called *GLU* method, is based on a hybrid right-looking LU factorization algorithm. We show that more concurrency can be exploited in the right-looking method than the left-looking method, especially on GPU platforms. We have the following contributions:

• We propose a new column-based right-looking LU factorization method, which is shown to be more amenable for exploiting the concurrency of LU factorization. The new method preserves the benefit of column-level concurrency and symbolic analysis in the left-looking method meanwhile, it allows more parallelism to be exploited. • We show that the new *GLU* LU solver allows the parallelization of all three loops in the LU factorization on GPUs. In contrast, the existing GPU-based left-looking LU factorization approach can only allow two-level parallelization. We conduct comprehensive studies on the new GPU LU solver on a number of published general matrices, circuit matrices and self-made large RLC circuit matrices against some existing LU solvers to demonstrate the advantage of the proposed GLU solver.

Numerical results show that the proposed GLU solver can deliver  $5.71 \times$  and  $1.46 \times$  speedup over the single-threaded and the 16-threaded PARDISO solvers [53] respectively, 19.56 × speedup over the KLU solver [23], 47.13 × over the UMFPACK solver [54] and 1.47 × speedup over a recently proposed GPU-based left-looking LU solver [14] on the set of typical circuit matrices from University of Florida Sparse Matrix Collection (UFL) [55]. Furthermore, we also compare the proposed GLU solver on a set of general matrices from UFL, GLU achieves  $6.38 \times$  and  $1.12 \times$  speedup over the single-threaded and the 16-threaded PARDISO solvers respectively,  $39.39 \times$  speedup over the KLU solver,  $24.04 \times$  over the UMF-PACK solver and  $2.35 \times$  speedup over the same GPU-based left-looking LU solver. Also comparison on self-generated RLC mesh networks shows a similar trend, which further validates the advantage of the proposed method over the existing sparse LU solvers.

This chapter is organized as follows. Section 2.2 reviews previous work that has been done to factorize sparse matrices into LU form on GPU, in particular the left-looking algorithm, GPU architecture and CUDA programming. In Section 2.3, we present the new column-based right-looking algorithm and its parallel implementation on GPU. Several numerical examples and discussions are presented in Section 2.4. Last, Section 2.5 concludes.

#### 2.2 Review of LU factorization algorithms and CUDA

Before we present our new approach, we first review the two main-stream LU factorization methods: the left-looking G/P factorization algorithm [22] and a variant of the right-looking algorithms such as the Gaussian elimination method. We then review some recent works on LU factorizations on GPU and the NVIDIA CUDA programming system.

The LU factorization of a  $n \times n$  matrix, A, has the form A = LU, where L is a lower triangular matrix and U is an upper triangular matrix. For a full matrix, LU factorization has  $O(n^3)$  complexity as it has three embedded loops.

#### 2.2.1 Right-looking factorization method

The right-looking LU factorization is the traditional factorization including the Gaussian elimination method. The algorithm can be explained by the following equation:

$$\begin{bmatrix} l_{11} \\ l_{21} & L_{22} \end{bmatrix} \begin{bmatrix} u_{11} & u_{12} \\ & U_{22} \end{bmatrix} = \begin{bmatrix} a_{11} & a_{12} \\ a_{21} & A_{22} \end{bmatrix},$$

(2.1)

where  $l_{11} = 1$  is the a scalar, and  $l_{21}$  and  $u_{12}$  are the column and row vectors respectively, and  $L_{22}$  and  $U_{22}$  are the  $(n-1) \times (n-1)$  submatrices. They can be computed by  $u_{11} = a_{11}$ ,  $u_{12} = a_{12}, l_{21} = a_{21}/u_{11}$ . After this, we end up with a  $(n-1) \times (n-1)$  equation to solve:  $L_{22}U_{22} = A_{22}-l_{21}u_{12}$ . The process repeats until we reach a  $1 \times 1$  equation to solve. As we can see, the traditional right-looking method solves one row for U matrix and then one column for L matrix at each iteration. Then it updates the  $(n-1) \times (n-1)$  submatrix  $A_{22}$  on the right part of the whole matrix and solves the reduced matrix recursively (so it is called the rightlooking method). Note that the right-looking method requires that  $A_{ii}$  is first factored before we can factor  $A_{i-1,i-1}$ , which indicates the sequential data dependency of this algorithm and its limits for potential parallel implementations (although the multifrontal based hierarchical schemes can be exploited for parallelization [56]). Note that we ignore all the reordering steps for fill-in reduction and numerical pivoting as well as symbolic analysis steps as we will visit them later.

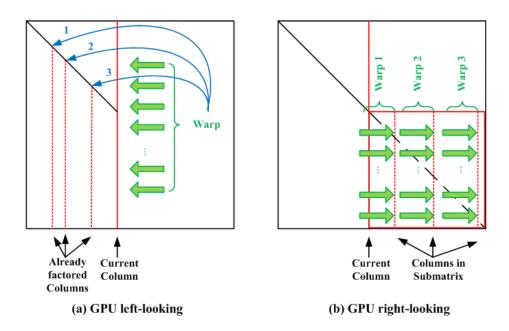

#### 2.2.2 Left-looking factorization method

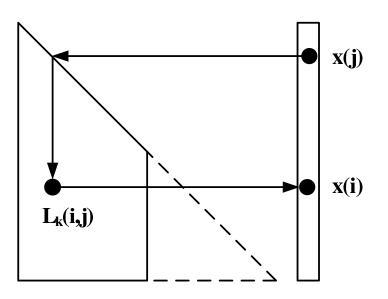

The G/P left-looking method shows better performances for sparse matrices and easier implementation than the traditional Gaussian elimination based methods. It also allows the symbolic fill-in analysis of L and U matrices before the actual numerical computing. Instead of computing one row of U and one column of L, the left-looking method computes one column for both L and U instead. This is achieved by solving a lower triangular matrix. This lower triangular solution is repeated n times during the entire factorization (where n is the size of the matrix) and each solution step computes a column of the L and Ufactors. In this method, the matrix is traversed by columns from left to right. To compute current column, the algorithm has to look at all the previous computed columns on the left part of the L and U. So it is called left-looking method. Algorithm 1 shows one detailed implementation of the left-looking LU factorization. In this pseudo code, the current column is indexed by j, and the columns to the left of the current column are indexed by k. To compute the current column j, the algorithm looks left and finds all already factored column k (k < j), where  $A_s(k, j) \neq 0$ , and then uses these columns to update current column j.  $A_s(x, y)$  indicates the LU symbolically factorized A matrix, where all the fill-ins and non-zero elements are assigned with non-zero initial values and their memories are allocated. Fig. 2.1 illustrates the basic idea of the left-looking algorithm. The key operation of the left-looking algorithm is the triangular matrix solving, which is actually performed by the so-called vector multiple-and-add (MAD) operations sequentially.

One important observation for the left-looking algorithm is that since all the fill-in patterns of factored matrices are exploited, we know some columns can be solved independently and in parallel, which is called column-level parallelism in the existing approaches. Such concurrency does not exist in the existing traditional right-looking algorithms due to the recursive nature of the algorithm as we mentioned before. 1: for j = 1 to n do

- 2: /\*Triangular matrix solving\*/

- 3: for k = 1 to j 1 where  $A_s(k, j) \neq 0$  do

- 4: /\*Vector multiple-and-add\*/

- 5: for i = k + 1 to *n* where  $A_s(i, k) \neq 0$  do

6:

$$A_s(i,j) = A_s(i,j) - A_s(i,k) * A_s(k,j)$$

- 7: end for

- 8: end for

- 9: /\*Compute column j for L matrix\*/

- 10: for i = j + 1 to *n* where  $A_s(i, j) \neq 0$  do

- 11:  $A_s(i,j) = A_s(i,j)/A_s(j,j)$

- 12: end for

- 13: end for

#### 2.2.3 Related works

The G/P left-looking method shown in Fig. 2.1 has been parallelized on GPU recently [14]. This method exploits the two-level concurrency in the left-looking algorithm due to the sparsity patterns of the matrices. First, it exploits the column-level parallelism in the left-looking algorithm as mentioned earlier. Based on the matrix sparsity pattern, the independent columns can be grouped into levels. So the outer j loop of Algorithm 1 can be parallelized by processing columns level by level. The so-called *cluster mode* in this

Figure 2.1: Left-looking update for column  $\boldsymbol{j}$

algorithm is for levels with many independent columns, while the *pipeline mode* is for levels with only a few columns. It also explores the parallelism within the vector MAD operation, which is reflected in the i loop of Algorithm 1. However, the middle k loop of column-bycolumn update, which is the key operation, is still in serial. The reason is that there is only one column j of the U matrix and updating this column must be done sequentially.

#### 2.2.4 Review of GPU Architecture and CUDA programming

In this subsection, we review the GPU architecture and CUDA programming. CUDA, short for Compute Unified Device Architecture, is the parallel programming model for NVIDIA's general-purpose GPUs. The architecture of a typical CUDA-capable GPU is consisted of an array of highly threaded streaming multiprocessors (SM) and comes with up to a huge amount of DRAM, referred to as global memory. Take the Tesla C2070 GPU for example. It contains 14 SMs, each of which has 32 streaming processors (SPs, or CUDA cores called by NVIDIA), 4 special function units (SFU), and its own shared memory/L1 cache. The structure of a streaming multiprocessor is shown in Fig. 2.2.

As the programming model of GPU, CUDA extends C into CUDA C and supports such tasks as threads calling and memory allocation, which makes programmers able to explore most of the capabilities of GPU parallelism. In CUDA programming model, illustrated in Fig. 2.3, threads are organized into blocks; blocks of threads are organized as grids. CUDA also assumes that both the host (CPU) and the device (GPU) maintain their own separate memory spaces, which are referred to as host memory and device memory respectively. For every block of threads, a shared memory is accessible to all threads in

Figure 2.2: Diagram of a streaming multiprocessor in NVIDIA Tesla C2070. (SP is short for streaming processor, L/S for load/store unit, and SFU for Special Function Unit.)

that same block. The global memory is accessible to all threads in all blocks. Developers can write programs running millions of threads with thousands of blocks in parallel. This massive parallelism forms the reason that programs with GPU acceleration can be much faster than their CPU counterparts. CUDA C provides its extended keywords and built-in variables, such as  $blockIdx.\{x,y,z\}$  and  $threadIdx.\{x,y,z\}$ , to assign unique ID to all blocks and threads in the whole grid partition. Therefore, programmers can easily map the data partition to the parallel threads, and instruct the specific thread to compute its own responsible data elements. Fig. 2.3 shows an example of 2-dim blocks and 2-dim threads in a grid, the block ID and thread ID are indicated by their row and column positions.

Figure 2.3: The programming model of CUDA.

# 2.3 Proposed GLU solver based on the hybrid column-based right-looking LU method on GPU platforms

In this section, we explain our new hybrid column-based right-looking sparse LU factorization method on the GPUs – GLU solver. GLU solver was originally inspired by the observation that the existing left-looking LU factorization has inherent limitations for concurrency exploitations due to the required solving of triangular matrices. To mitigate this problem, we look at the traditional right-looking LU factorization method, which seems more amenable for parallelization especially on GPU platforms. But we also want the benefits of symbolic analysis for storage management of factorized matrices and columnlevel concurrency in the left-looking based method. The resulting method is the hybrid column-based right-looking LU method, which will be discussed in the following.

### 2.3.1 The column-based right-looking algorithm

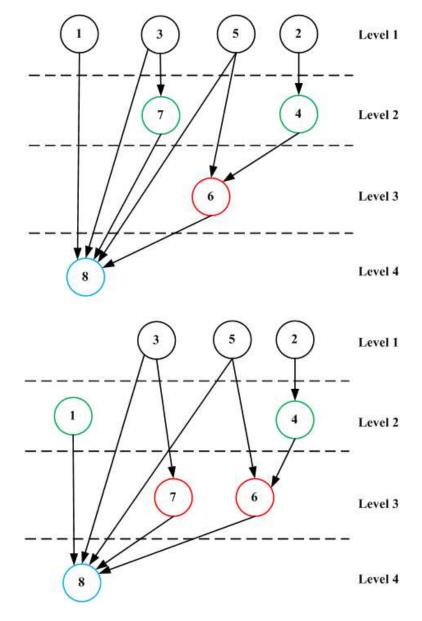

Our starting point is still the left-looking algorithm as we want to keep the columnconcurrency and symbolic analysis and we still compute one column for both L and Umatrices. But unlike the left-looking algorithm, once a column of L is computed, its impacts on the yet-to-be-solved columns will be updated right away (so we now start to look right in this sense). Algorithm 2 shows the hybrid column-based right-looking LU factorization algorithm, which turns out to be more amenable for GPU parallelization. In this pseudo code, the current column are indexed by k, and the columns to the right of the current column, which are updated immediately after the current column has been computed, are indexed by j. After current column k is computed, the algorithm looks right and finds all column j (j > k) in the submatrix, where  $A_s(k, j) \neq 0$ , and then uses column k to update these columns.  $A_s(x, y)$  indicates the LU symbolically factorized A matrix, where all the fill-ins and non-zero elements are assigned with non-zero initial values and their memories are allocated. Fig. 2.4 illustrates the basic idea of the hybrid column-based right-looking algorithm. The key operation of the right-looking algorithm becomes submatrix update now. But such change makes a major difference in terms of concurrency exploitation as we will show soon.

## Algorithm 2 The hybrid column-based right-looking algorithm 1: for k = 1 to n do

- 2: /\*Compute column k of L matrix\*/

- 3: for i = k + 1 to n where  $A_s(i, k) \neq 0$  do

- 4:  $A_s(i,k) = A_s(i,k)/A_s(k,k)$

- 5: end for

- 6: /\*Update the submatrix for next iteration\*/

- 7: for j = k + 1 to n where  $A_s(k, j) \neq 0$  do

- 8: for i = k + 1 to n where  $A_s(i, k) \neq 0$  do

9:

$$A_s(i,j) = A_s(i,j) - A_s(i,k) * A_s(k,j)$$

- 10: **end for**

- 11: **end for**

- 12: **end for**

In this column-based right-looking algorithm, we still have three loops. The outer k-loop chooses the current column k that will be factorized; the middle j-loop chooses the

Figure 2.4: The illustration of the hybrid column-based right-looking algorithm and the submatrix update at each iteration

column j in the submatrix right to column k that depends on column k; and the inner i-loop is used to perform MAD operations between column k and column j. But now, we will show that these three loops can be parallelized because the submatrix is updated by the i and j loops, which is more amenable for parallelization than the solving triangular matrices in the left-looking method (see details in Subsection 2.3.3).

We remark the hybrid LU factorization method is similar to the multifrontal based right-looking LU factorization method, in the sense that each independent column and its connected columns can form a frontal matrix [56]. But in our approach, no elimination tree is used to build the frontal matrices and the hierarchical matrix analysis structure. The column-level parallelization is mainly based on the dependency graph (to be discussed later).

## 2.3.2 Preprocessing and symbolic analysis

As we mentioned earlier that the proposed method combines the benefits of both left-looking method and the right-looking methods. As a result, it still follows the preprocessing and symbolic analysis steps to improve the factorization efficiency. Hence the new factorization algorithm can still be split into three phases. In the sequel, we give a brief description of the first two steps for the self-contained purpose. Then we analyze the related data dependency from the symbolic analysis step for GPU computing.

First, the preprocessing phase preorders the matrix A to minimize fill-in and to ensure a zero-free diagonal. Second, the symbolic phase performs symbolic factorization and determines the structure of lower triangular matrix L and upper triangular matrix U. Then it groups independent columns into levels. Third, the numerical phase obtains the resulting lower and upper sparse triangular factors by solving the columns level by level. The preprocessing phase and symbolic phase are performed only once on CPU (which will be discussed in this section). The numerical phase can be performed multiple times on GPU. For the completion of the algorithm, we also present the first two phases.

In the preprocessing phase, we use HSL MC64 [57] to decrease the likelihood of encountering tiny pivots and AMD (Approximate Minimum Degree) algorithm [58] to reduce the fill-ins. The nonzero structure of the sparse matrix may dramatically change in course of LU factorization. In this step, we perform a left-looking algorithm based symbolic analysis [22] to determine the nonzero patterns of L and U. The core operation of leftlooking algorithm is to solve the lower triangular system  $L_k x = b$  in order to compute the kth column, where  $L_k$  is lower matrix representing the already computed (k - 1) columns and the vector b is the kth column of matrix A. This pseudo core operation is shown in Algorithm 3.

Algorithm 3 Forward substitution for solving sparse triangular matrices 1: x = b

- 2: for j = 0 to k 1 where  $b(j) \neq 0$  do

- 3: for i = j + 1 to n where  $L(i, j) \neq 0$  do

- 4: x(i) = x(i) L(i, j)x(j)

- 5: end for

- 6: **end for**

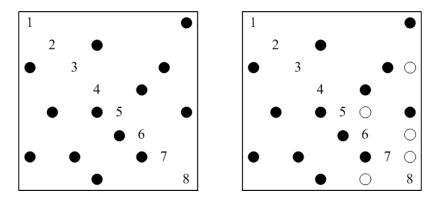

From the pseudo code, we can see that entries in x can become nonzero in only two places, the first and fourth lines. We can represent these two relationships as a directed graph G = (V, E), where the nodes V = 1...n represent the rows and the edges E = (j, i)where  $L(i, j) \neq 0$ . Thus, line 1 is equivalent to marking all nodes that are nonzeros in the vector b, whereas line 4 implies that if a node j is marked and it has an edge to a node i, then the latter must be also marked. Fig. 2.5 graphically highlights these two relationships. Therefore, the nonzero pattern can be computed by determining the nodes that are reachable from the nodes of vector b, which is also the computed column vector of U from the previous iteration of the left-looking method. This reachability problem can be solved using a classical depth-first search in G. Then we can determine the nonzero pattern of the new matrices L and U.

Fig. 2.6 shows a sparse matrix A and the predicted nonzero pattern of the LU factors of A after symbolic analysis (L and U share the same space of A), in which the

black circle and white circle represent original entries of A and fill-in entries respectively. As a result, the matrix A now contains the fill-ins and elements in the original matrix. When we copy A to GPU's memory, we actually copy the L and U matrices (with their values yet to be determined). After the factorization, the A becomes the resulting L and Umatrices physically and it doesn't contain the original matrix any more.

Column k

Figure 2.5: Nonzero pattern for a sparse triangular solver.

Another important problem is the column dependencies. It is clear that any column dependencies in the overall left-looking algorithm only arise from the sparse triangular solve step, the line 2 of Algorithm 3. However, when we compute column k, not all the columns to its left are needed, as it was illustrated in Algorithm 3. In fact, the factorization of column k only depends on the columns that satisfy  $a_{ij} \neq 0$  for i < j. In other words, the dependencies between rows are defined by the sparsity pattern of the upper triangular

Figure 2.6: The original matrix A (left) and the matrix A (right) after symbolic analysis with predicted nonzero pattern of LU factors of A

matrix U and are independent of the lower triangular matrix L.

We use a directed acyclic graph (also called dependency graph) to represent the data dependencies in the LU factorization of the matrix in Fig. 2.6. In which, if column k depends on column i, then a directed edge exists from node i to node k, where i < k. Fig. 2.7 (top figure) illustrates the column dependencies of example matrix A. The graph was computed using predicted nonzero structure of matrix U only. All the columns in the same level are independent and can be computed in parallel. For instance, column 1, 2, 3, 5 can be evaluated in parallel; however, column 6 cannot be processed until columns 4 and 5 are computed.

Note that the concurrent computation resources (warps per streaming multiprocessor (SM), shared memory per block, threads per block) on GPU are limited. As a result, the number of columns, which can be solved in parallel, in each level should be limited. Hence, we propose a resource-aware levelization scheme, in which the number of columns of each level will be limited by a fixed number. For instance, Fig. 2.7 (bottom figure) shows the levelization result from the top figure in which the maximum number of allowed columns is 3. This resource-aware levelization scheme will be applied to parallelize the outer k-loop of the proposed right-looking algorithm.

Figure 2.7: The illustration of the resource-aware levelization scheme.

## 2.3.3 Numerical computing phase

The algorithm based symbolic analysis can be altered to expose the column-level parallelism. Despite this exposed column-evaluation concurrency, in the numerical factorization phase, it is possible to explore more parallelism available in each level using multiple threads.

On GPU, the global memory access from the same CUDA warp (one warp consists of 32 threads and it is scheduling unit on one SM on GPU) can be coalesced if they are visiting the consecutive memory address. However, for sparse LU factorization, irregular nonzero pattern leads to many uncoalesced global memory accesses, which greatly degrades the performance. To maximize the coalescence, we use compressed sparse column (CSC) format to store the A matrices (L and U share the same storage of A) and record all nonzeros in L and U. In addition, to maximize parallelization during the factorization, we also use compressed sparse row (CSR) format to record the nonzero positions of symbolic U (but not its values), and its usage will become clear soon.

Now let us look at how the three loops in the proposed right-looking method can be parallelized in GPU platforms. Algorithm 4 is the pseudo code for the proposed parallel column-based right-looking algorithm. The first loop is to choose a number of columns of Lmatrix in one level, which can be factorized in parallel. Both the proposed method and the left-looking method enjoy this *column-level parallelism* as the proposed method is also based on the symbolic left-looking level analysis. The difference is in the other two loops of the two algorithms. Next, let us look at the computing steps inside the first loop (between line 2 and line 14). There are two stages. In the first stage, we compute the current column *col*  of the L matrix by vector-scalar division and it can be performed in parallel easily. Due to the first column-level parallelism, we may have several current column col's to be updated.

In the second step, we perform the submatrix update (MAD operations) for the current column *col*. We are concerned *col*'s that are needed by other columns of the submatrix (means that  $A(k, j) \neq 0$  in line 7 of Algorithm 2). We call the columns in submatrix which depends on current column *col*, the *subcol*. To facilitate locating those *subcol*'s, we need to access the dependency graph, which is represented by the symbolic upper triangular matrix U. For instance, the *subcol*'s of a current column, say k, can be found by using the nonzero position information of row k of L. This also explains why we need to have symbolic U in the CSR format. Note that the current column *col* needs to be stored into a un-compressed array and the *subcol*'s can access the un-compressed array to get the *col* information to update themselves. Since the *subcol*'s only read information from the un-compressed column, there's no conflict.

Notice that each *subcol* only needs to be updated once by the current column. As a result, all *subcol*'s in one submatrix can be updated in parallel. This parallelism in the loop is called *submatrix update parallelism*. In the third loop, the core operation is vector MAD operation, which is used to update a *subcol*. In contrast, the current column *col* needs to be updated by all solved and relevant columns to its left in the left-looking algorithm in the left-looking algorithm and the updates to column k must be performed sequentially. Hence it cannot enjoy the *submatrix update parallelism*. As a result, we parallelize essentially all the loops in LU factorization in the proposed new method.

- 2: /\*column-level parallelism\*/

- 3: for all *col*'s in *current level* in parallel do

- 4: compute current col of L matrix

- 5: end for

- 6: synchronize threads

- 7: for all *col*'s in *current level* in parallel do

- 8: /\*submatrix update parallelism\*/

- 9: for all *subcol*'s in *current submatrix* which depends on *col* in parallel do

- 10: /\*vector MAD operation parallelism\*/

- 11: update elements in one *subcol*

- 12: **end for**

- 13: **end for**

- 14: synchronize threads

- 15: end for

## 2.3.4 Parallel implementation on GPU

In the parallel implementation of sparse LU factorization, the CPU is responsible for initializing the matrix and doing the symbolic analysis. The GPU only concentrates on the numerical factorization. The CPU is also responsible for allocating the device memory, copy the host inputs to the device memory, and copy the computed device results back to the host.