# **UC Berkeley**

# **UC Berkeley Electronic Theses and Dissertations**

#### **Title**

Photonics Links -- From Theory to Automated Design

#### **Permalink**

https://escholarship.org/uc/item/1v53d8x7

#### **Author**

Settaluri, Krishna Tej

#### **Publication Date**

2018

Peer reviewed|Thesis/dissertation

#### Photonic Links - From Theory to Automated Design

by

Krishna Tej Settaluri

A dissertation submitted in partial satisfaction of the requirements for the degree of  ${\bf Doctor\ of\ Philosophy}$

in

Engineering - Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Vladimir Stojanović, Chair Professor Eli Yablonovitch Professor Costas Grigoropoulos

Fall 2018

Photonic Links – From Theory to Automated Design

Copyright © 2018 by

Krishna Tej Settaluri

#### Abstract

Photonic Links – From Theory to Automated Design

by

Krishna Tej Settaluri Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

> University of California, Berkeley Professor Vladimir Stojanović, Chair

Recent advancements in silicon photonics show great promise in meeting the high bandwidth and low energy demands of emerging applications. However, a key gating factor in ensuring this necessity is met is the utilization of a link design methodology which transcends the various levels in the hierarchy, ranging from the device and platform level up to the systems level. In this dissertation, a comprehensive methodology for link design will be introduced which takes a two-prong approach to tackling the issue of silicon photonic link efficiency. Namely, a fundamentals-based first principles approach to link optimization will be introduced and validated. In addition, physical design trade-offs connecting levels in the architectural hierarchy will also be studied and explored. This culminates in an intermediate goal of this dissertation, which is the first-ever design and verification of a full silicon photonic interconnect on a 3D integrated electronic-photonic platform. To proceed and further enable the rapid exploration of the link design architectural space, the analog macros for a majority of this dissertation were auto-generated using the Berkeley Analog Generator (BAG). With these key design tools and framework, performance bottlenecks and improvements for silicon photonic links will be analyzed and, from this analysis, the motivation for a new, single comparator-based PAM4 receiver architecture shall emerge. This architecture not only showcases the tight bond in dependency between high-level link specifications and low level device parameters, but also shows the importance of physical design constraints alongside fundamental theory in influencing end-to-end link performance.

To Mom and Dad.

# Contents

| $\mathbf{C}$ | ontei                                        | nts     |                                            | ii  |  |

|--------------|----------------------------------------------|---------|--------------------------------------------|-----|--|

| Li           | st of                                        | Figur   | es                                         | iii |  |

| Li           | st of                                        | Table   | S                                          | iv  |  |

| 1            | Inti                                         | roducti | ion                                        | 1   |  |

| 2            | Background                                   |         |                                            |     |  |

|              | 2.1                                          | Silicor | Photonic Links                             | 3   |  |

|              |                                              | 2.1.1   | Photonic Building Blocks                   | 4   |  |

|              |                                              | 2.1.2   | Optical Communication Links                | 6   |  |

|              |                                              | 2.1.3   | Circuit Design Challenges and Methodology  | 7   |  |

|              | 2.2                                          | Silicor | Photonic Integration Platforms             | 7   |  |

|              |                                              | 2.2.1   | 3D Integration Using Thru-Oxide Vias       | 8   |  |

|              |                                              | 2.2.2   | 3D Integration Using Flip Chip $\mu$ Bumps | 8   |  |

|              | 2.3                                          | Analo   | g Circuit Design Challenges and Automation | 9   |  |

|              |                                              | 2.3.1   | BAG Architecture and Flow                  | 9   |  |

|              | 2.4                                          | Concl   | usion                                      | 13  |  |

| 3            | End-to-End Optical Link Design Methodology 1 |         |                                            |     |  |

|              | 3.1                                          | Introd  | luction                                    | 15  |  |

|              | 3.2                                          | Optica  | al Link Modeling                           | 17  |  |

|              |                                              | 3.2.1   | High-Level Receiver Abstraction            | 17  |  |

|              |                                              | 3.2.2   | Gain-Bandwidth product                     | 18  |  |

|              |                                              | 3.2.3   | Voltage Amplifiers                         | 18  |  |

|              |                                              | 3.2.4   | Transimpedance Amplifier                   | 19  |  |

|              |                                              | 3.2.5   | Sampler Model in Receiver                  | 20  |  |

|              | 3.3                                          | Macro   | -Parameter Derivations                     | 25  |  |

|              |                                              | 3.3.1   | Sensitivity calculation                    | 25  |  |

|              |                                              | 3.3.2   | Energy per bit                             | 26  |  |

|              |                                              | 3 3 3   | Model inputs and optimization variables    | 29  |  |

|   |     | 3.3.4 Model purpose and limitations                                 | 29         |

|---|-----|---------------------------------------------------------------------|------------|

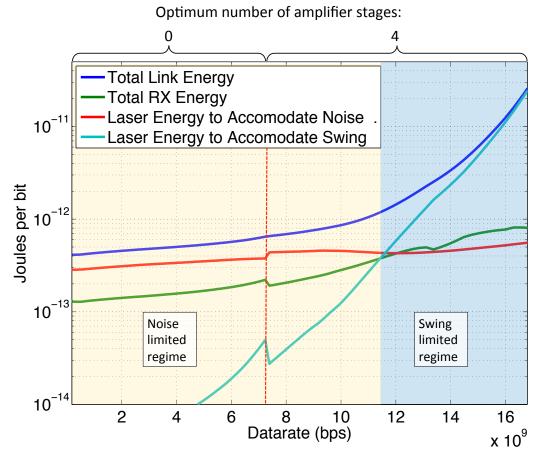

|   | 3.4 | Sensitivity and energy limits                                       | 29         |

|   |     | 3.4.1 Front end noise limit                                         | 29         |

|   |     | 3.4.2 Limits at high data rates                                     | 31         |

|   |     | 3.4.3 Limits at low datarates                                       | 31         |

|   |     | 3.4.4 E/b power laws                                                | 32         |

|   | 3.5 | Observations in Scaling and Technology                              | 32         |

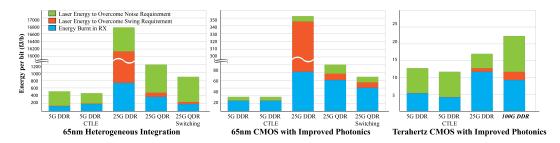

|   |     | 3.5.1 Improvements in Photonics and Interconnects                   | 33         |

|   |     | 3.5.2 Improvements in Photonics+CMOS                                | 33         |

|   | 3.6 | Link Framework and First-Principles Summary                         | 36         |

|   | 3.7 | Conclusion                                                          | 36         |

| 4 | Lin | k Framework Application for NRZ Front-End Design                    | 38         |

|   | 4.1 | Introduction                                                        | 38         |

|   | 4.2 | Model Application for 65nm Heterogenously Integrated Photonic Plat- |            |

|   |     | form                                                                | 39         |

|   |     | 4.2.1 Technology overview                                           | 39         |

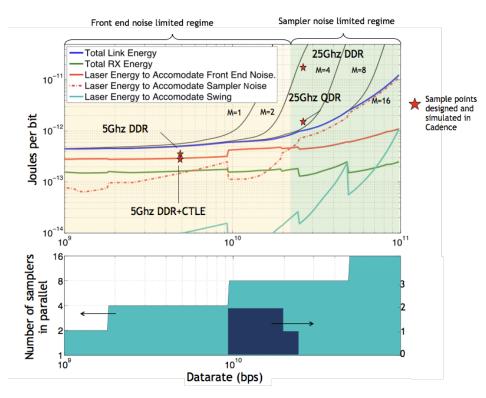

|   |     | 4.2.2 Single slicer case $(M=1)$                                    | 39         |

|   |     | 4.2.3 Multiple slicer case $(M \ge 1)$                              | 40         |

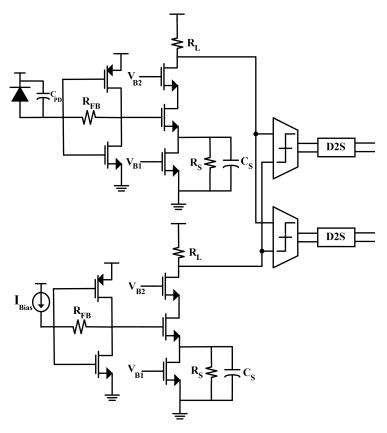

|   | 4.3 | Schematic designs of model results                                  | 42         |

|   |     | 4.3.1 5Gbps optical receiver                                        | 42         |

|   |     | 4.3.2 Active-CTLE enhanced 5Gbps optical receiver                   | 43         |

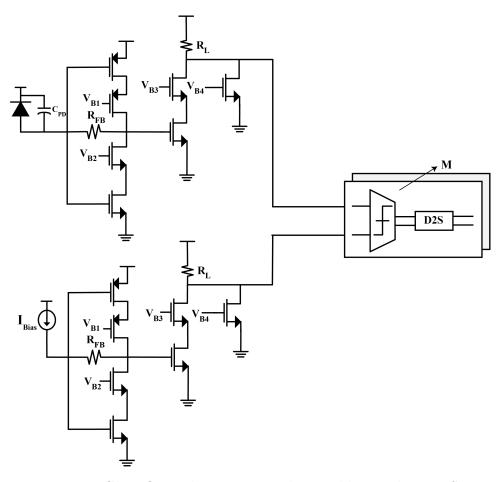

|   |     | 4.3.3 DDR 25Gbps optical receiver                                   | 44         |

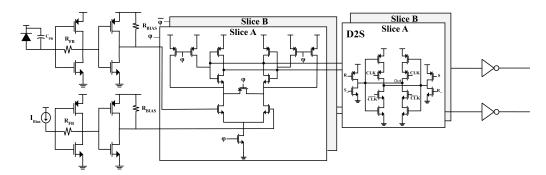

|   |     | 4.3.4 QDR 25Gbps optical receiver                                   | 46         |

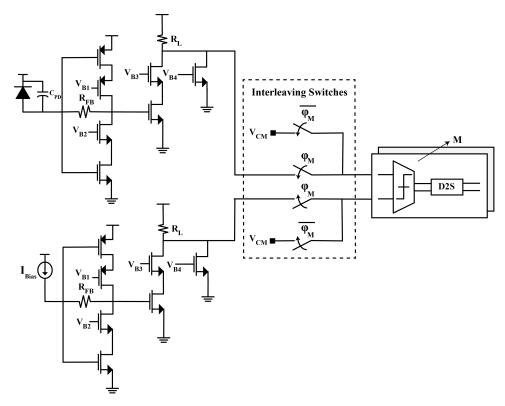

|   |     | 4.3.5 Switched QDR 25Gbps optical receiver                          | 47         |

|   | 4.4 | Conclusion                                                          | 48         |

| 5 | 3D  | Integrated Silicon Photonic Interconnects                           | <b>4</b> 9 |

|   | 5.1 | Introduction                                                        | 49         |

|   | 5.2 | Overview                                                            | 50         |

|   | 5.3 | 3D Integration of CMOS and Photonics                                | 51         |

|   | 5.4 | Chip Architecture and Optical Link System                           | 52         |

|   |     | 5.4.1 Transmitter Design                                            | 53         |

|   |     | 5.4.2 Receiver Design                                               | 55         |

|   |     | 5.4.3 Thermal Tuner Design                                          | 57         |

|   |     | 5.4.4 Link Implementation and Test setup                            | 57         |

|   | 5.5 | Conclusion                                                          | 59         |

| 6 | •   | •                                                                   | 63         |

|   | 6.1 | Introduction                                                        | 63         |

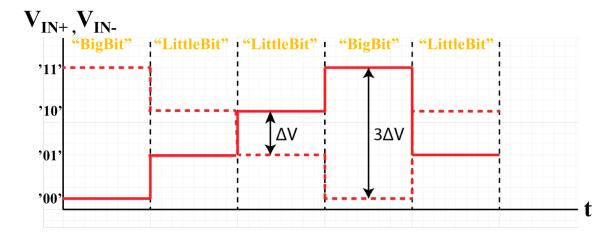

|   | 6.2 | PAM4 Introduction and Link Trade-Offs                               | 63         |

|   | 6.3 | Single Comparator PAM4 Receiver                                     | 67         |

|    |                        | 6.3.1   | Motivation                                             | 68  |  |  |  |

|----|------------------------|---------|--------------------------------------------------------|-----|--|--|--|

|    |                        | 6.3.2   | Proposed Architecture and Formulation                  | 69  |  |  |  |

|    |                        | 6.3.3   | Design Methodology and Theoretical Performance         | 74  |  |  |  |

|    |                        | 6.3.4   | End-to-End Photonic Co-Simulation Results              | 79  |  |  |  |

|    | 6.4                    | 0.0     | usion                                                  | 81  |  |  |  |

|    | 0.1                    | Conci   | usion                                                  | 01  |  |  |  |

| 7  | Acacia System Design 8 |         |                                                        |     |  |  |  |

|    | 7.1                    | Introd  | luction                                                | 83  |  |  |  |

|    | 7.2                    |         | a System Design                                        | 83  |  |  |  |

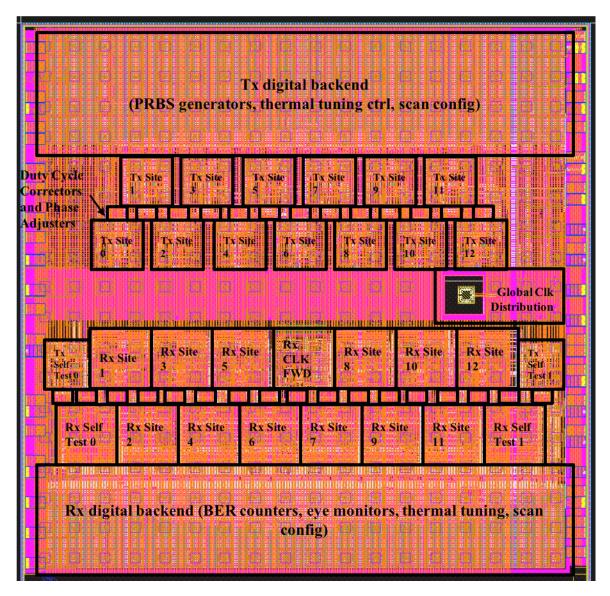

|    |                        | 7.2.1   | Front-End Floorplanning and PDK Generation Constraints | 83  |  |  |  |

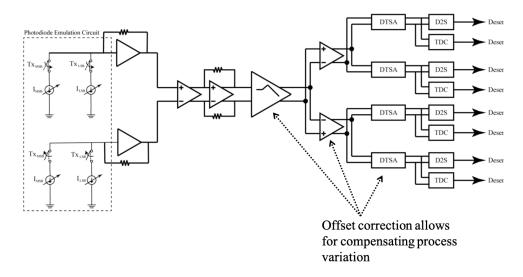

|    |                        | 7.2.2   | Receiver AFE Design and Insights                       | 91  |  |  |  |

|    |                        | 7.2.3   | Transmitter Design and Automation                      | 92  |  |  |  |

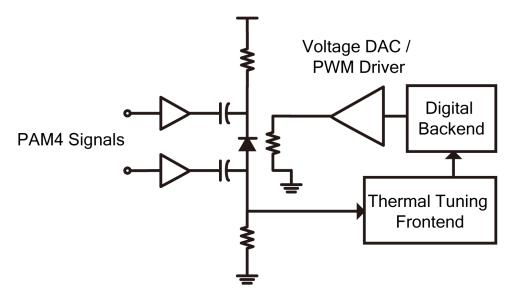

|    |                        | 7.2.4   | New Transmit-Side Thermal Tuning                       | 93  |  |  |  |

|    |                        | 7.2.5   | Tx-Rx Self Test Setup                                  | 94  |  |  |  |

|    |                        | 7.2.6   | Putting together the Acacia System                     | 95  |  |  |  |

|    | 7.3                    | Result  | ts                                                     | 96  |  |  |  |

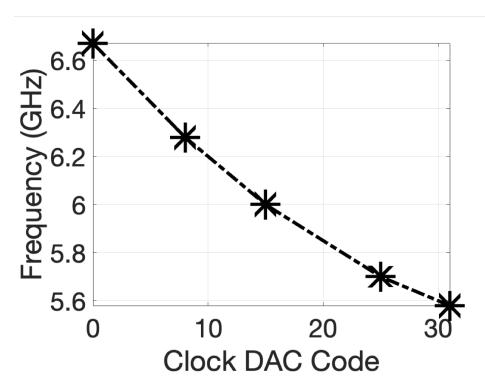

|    |                        | 7.3.1   | On-Chip Clock Network                                  | 96  |  |  |  |

|    |                        | 7.3.2   | Rx AFE and Self Test Characterization                  | 98  |  |  |  |

|    |                        | 7.3.3   | 25.6Gbps Self Test Link                                | 99  |  |  |  |

|    | 7.4                    | Concl   | usion                                                  | 99  |  |  |  |

| 8  | Conclusion 103         |         |                                                        |     |  |  |  |

| Ū  | 8.1                    |         | S Contributions                                        | 101 |  |  |  |

|    | 8.2                    |         | e Work and Final Thoughts                              |     |  |  |  |

| B  | iblica                 | graphy  |                                                        | 103 |  |  |  |

| וע | DITOF                  | 51 apny |                                                        | 100 |  |  |  |

# List of Figures

| 2.1  | The microring modulator enables OOK encoding while also enabling wavelength selectivity                                                |

|------|----------------------------------------------------------------------------------------------------------------------------------------|

| 2.2  | The photodetector is responsible for generating an output current de-                                                                  |

| 2.2  | pendent on the input optical power                                                                                                     |

| 2.3  | A WDM link composed of many transmit and receive side rings is an attractive solution which allows high bandwidth density.             |

| 2.4  | A cross section and top view of the TOV are shown                                                                                      |

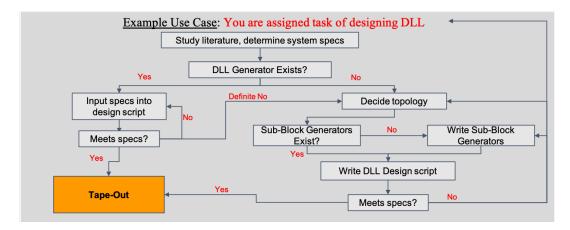

| 2.5  | The design flow of a new block within the BAG framework is shown.                                                                      |

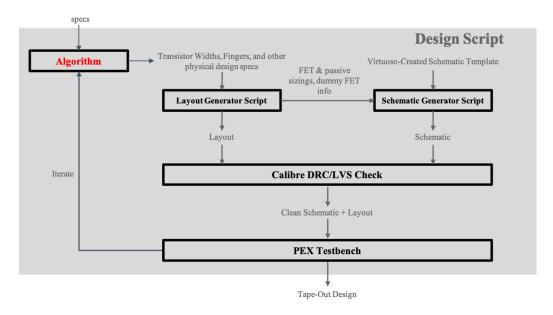

| 2.6  | The design flow with feedback from the output of simulations enables                                                                   |

|      | rapid iteration. [4]                                                                                                                   |

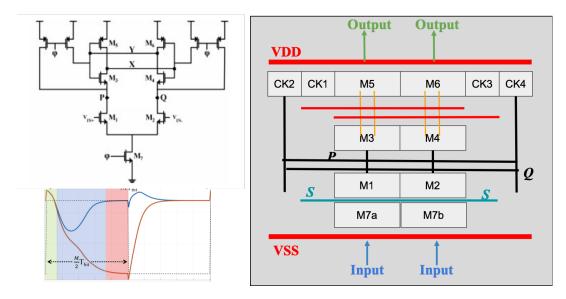

| 2.7  | The schematic, transient, and example floorplan of the StrongArm is                                                                    |

|      | shown                                                                                                                                  |

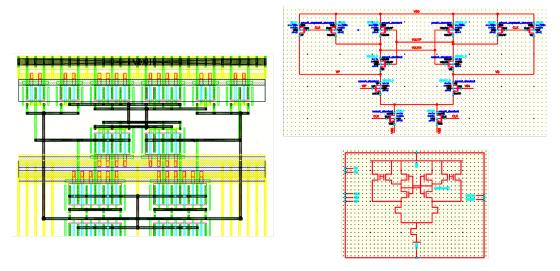

| 2.8  | The output of the schematic and layout generators produce DRC and                                                                      |

|      | LVS clean instances of the StrongArm                                                                                                   |

| 2.9  | The framework allows for push-button instantiation and verification to                                                                 |

| 2.10 | generate quick, correct instances                                                                                                      |

| 3.1  | Demonstrated Optical Link Efficiencies [6-15], Against Objectives From [6]. Further information at linksurvey.eecs.berkeley.edu        |

| 3.2  | Optical Link System Overview                                                                                                           |

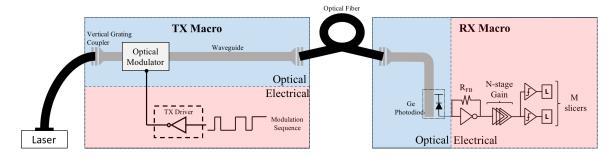

| 3.3  | StrongArm Sampler Schematic                                                                                                            |

| 3.4  | Sampler Timing Evaluation Breakdown                                                                                                    |

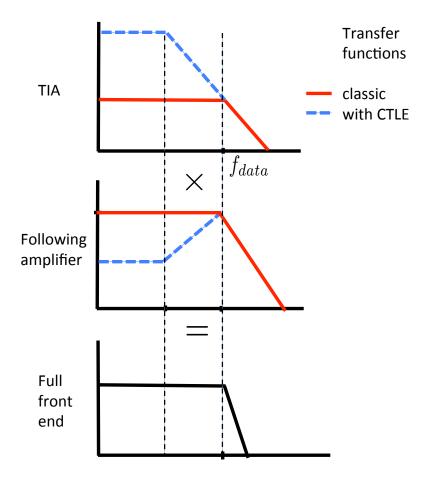

| 3.5  | Ideal Transfer Function of A System with Equalization                                                                                  |

| 3.6  | Technology Dependent Performance Prediction                                                                                            |

| 4.1  | Optimal Energy Per Bit Versus Data rate For Optimal Topologies With Parameters From Table ??. Only One Slicer is Allowed in This Case. |

| 4.2  | Optimal Energy Per Bit Versus Data rate For Optimal Topologies With                                                                    |

| 4.0  | Parameters from Table ?? with the Possibility of Multiple Slicers                                                                      |

| 4.3  | 5Gbps Receiver Topology                                                                                                                |

LIST OF FIGURES vi

| 4.4<br>4.5<br>4.6 | 5Gbps Model-Predicted Receiver Topology with Active-CTLE 25Gbps Optical Receiver With Variable Interleaving Stages Switching Time-Interleaved 25Gbps QDR Receiver                                | 44<br>45<br>47 |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

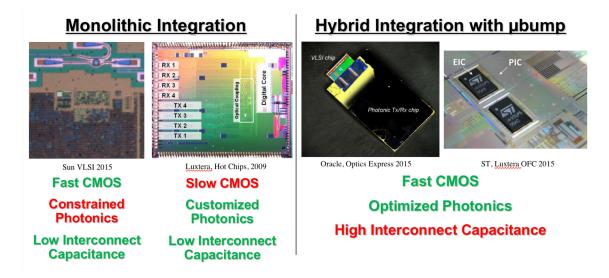

| 5.1               | A comparison of the integration technology categories shows pros and cons for both                                                                                                               | 50             |

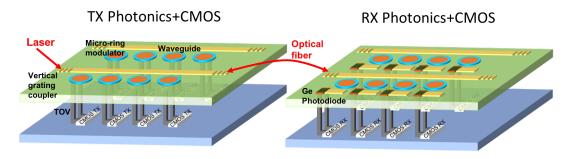

| 5.2               | An example diagram of the full WDM link using a heterogeneous platform shows independent photonic and CMOS wafers on both the Tx                                                                 |                |

| 5.3               | and Rx side                                                                                                                                                                                      | 51<br>52       |

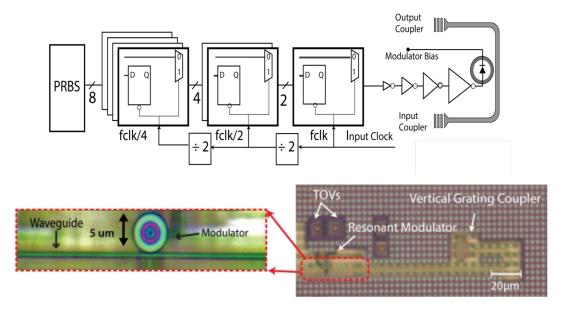

| 5.4<br>5.5        | A full system of the heterogeneously integrated EPHI system The Tx Macro consists of high speed serializers and drivers shift the                                                                | 53             |

| 5.6               | ring resonance                                                                                                                                                                                   | 54<br>55       |

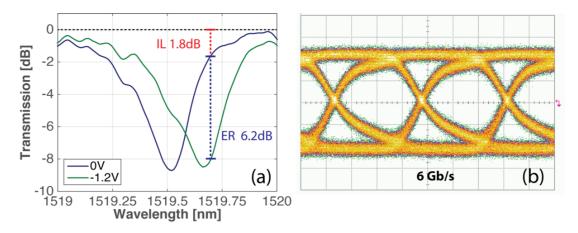

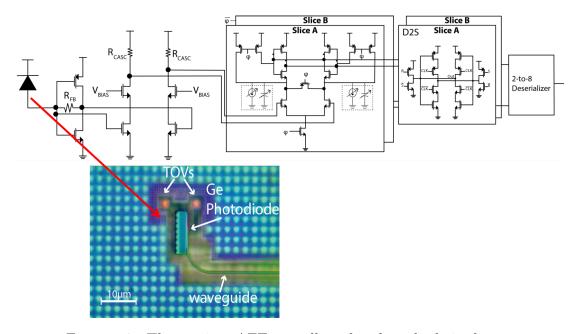

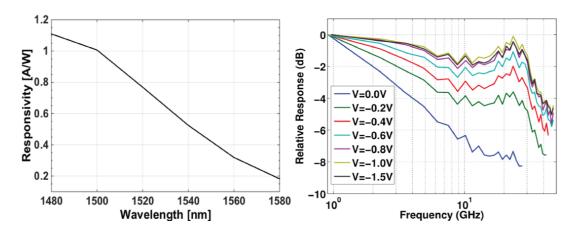

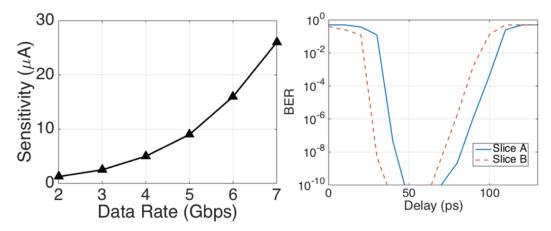

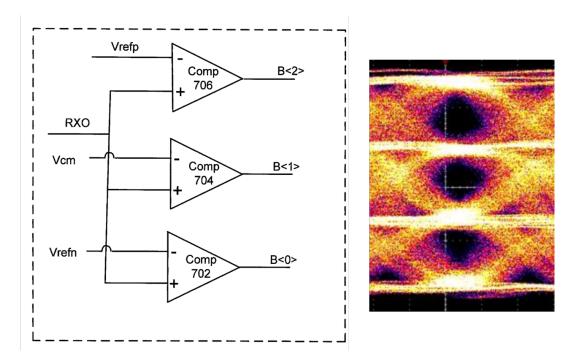

| 5.7<br>5.8<br>5.9 | The receiver AFE as well as the photodiode is shown  The Rx photonic ring responsivitity and response versus frequency.  Measured receiver average photo-current sensitivity over different data | 55<br>56       |

|                   | rates and BER bathtub curves for both receiver slices                                                                                                                                            | 57             |

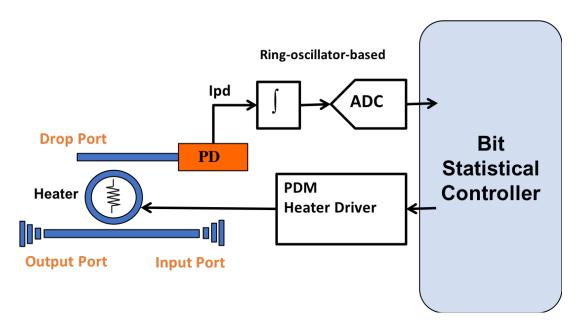

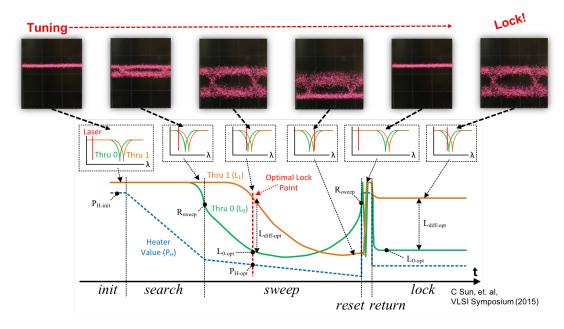

| 5.11              | nance is shown                                                                                                                                                                                   | 58             |

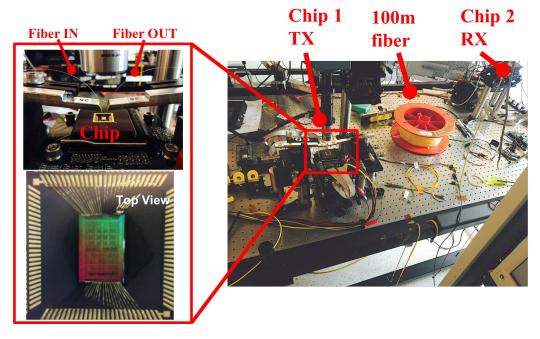

| 5.12              | for the thermal tuner                                                                                                                                                                            | 59<br>60       |

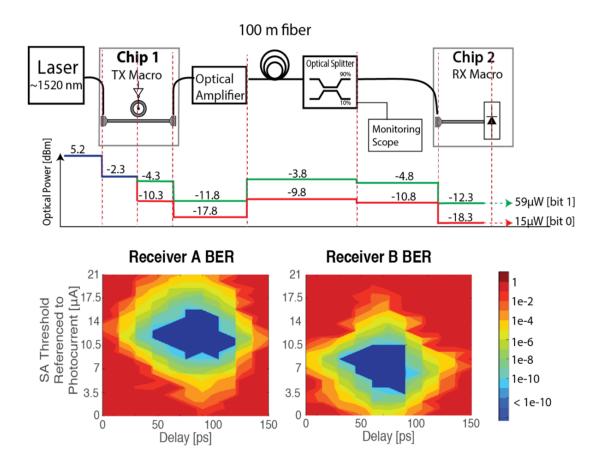

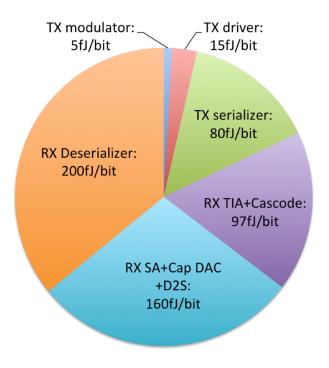

| 5.14              | Full optical link with optical power budget and performance Electrical energy breakdown for the Tx and Rx macros in a 5Gb/s link. Comparison with previous work                                  | 61<br>62<br>62 |

| 6.1               | The traditional PAM4 architecture comprises of three comparators after the AFE to slice the 4-level eye                                                                                          | 64             |

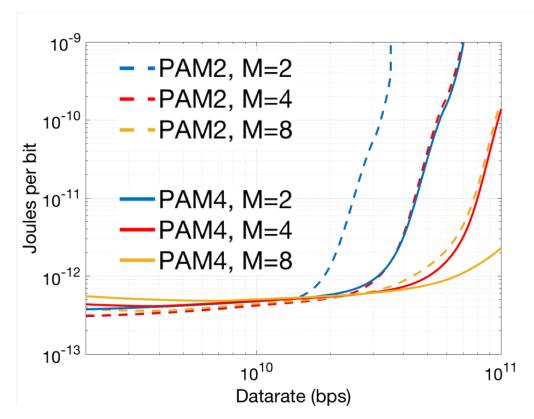

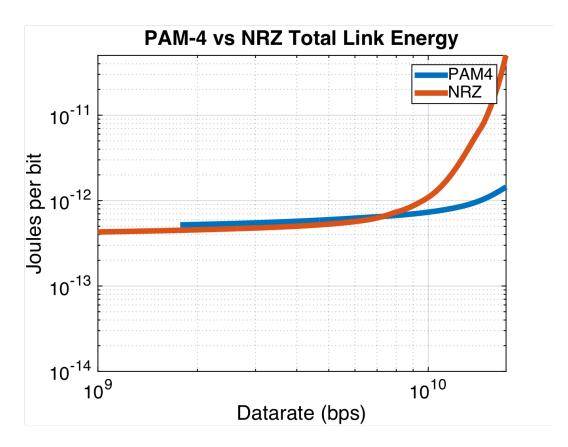

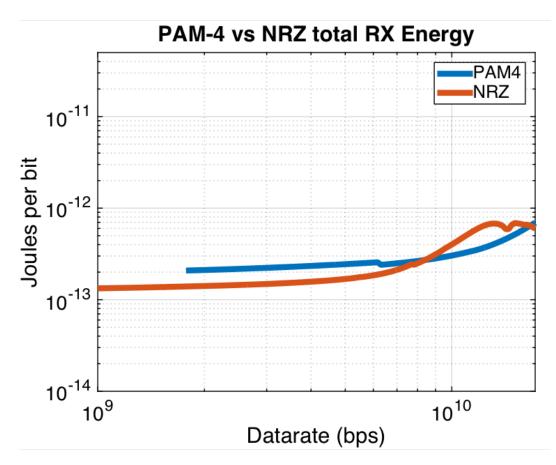

| 6.2               | Removing all constraints on the receiver architecture shows that the PAM4 architecture is superior to NRZ under particular system con-                                                           | C.F.           |

| 6.3               | straints                                                                                                                                                                                         | 65             |

| 6.4               | over NRZ                                                                                                                                                                                         | 66             |

| 6.5               | NRZ                                                                                                                                                                                              | 67<br>68       |

LIST OF FIGURES vii

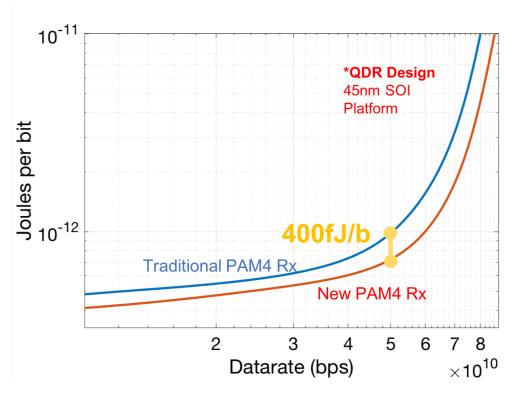

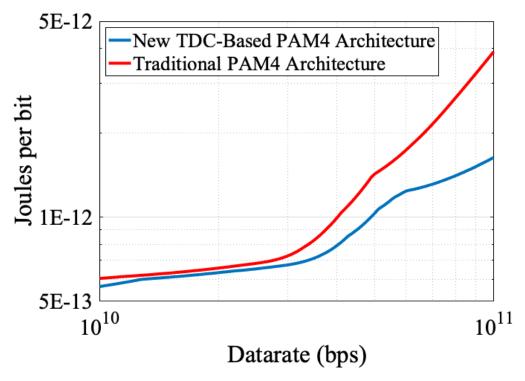

| 6.6  | Preliminary link performance results show the benefit of scaling down                                                                |

|------|--------------------------------------------------------------------------------------------------------------------------------------|

|      | the sampler capacitance by $3\times$                                                                                                 |

| 6.7  | Behavior of a PAM4 receiver with a single comparator yield "NRZ-                                                                     |

|      | equivalent" behavior                                                                                                                 |

| 6.8  | The StrongArm Sense Amplifier schematic along with two sets of wave-                                                                 |

|      | forms (red and green) showing the output due to a large and small input                                                              |

|      | signal, respectively.                                                                                                                |

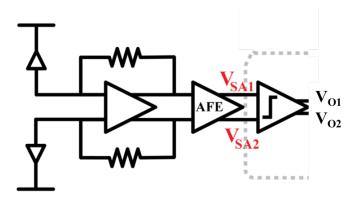

| 6.9  | A fully differential PAM4 front-end will have two complementary out-                                                                 |

|      | puts centered about the common-mode                                                                                                  |

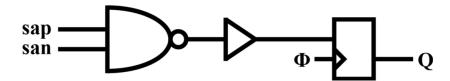

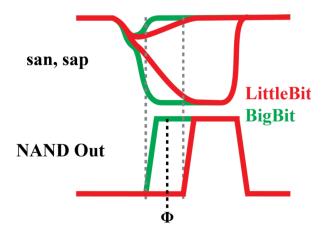

| 6.10 | A time-to-digital circuit takes an input the differential outputs of the                                                             |

|      | StrongArm sense amplifier                                                                                                            |

| 6.11 | The sample waveforms of the TDC block show pulse width's depen-                                                                      |

|      | dency on the output StrongArm waveforms                                                                                              |

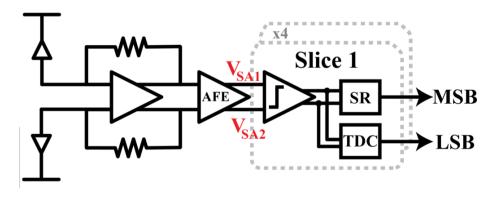

| 6.12 | The TDC receiver architecture composed of the AFE and a single in-                                                                   |

|      | terleaving way composed of the StrongArm, D2S, and new TDC (from                                                                     |

|      | Figure ??)                                                                                                                           |

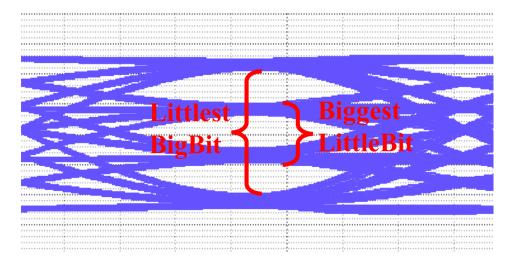

| 6.13 | Non-idealities in the AFE result in a voltage ratio between the BigBit                                                               |

|      | and LittleBit that is smaller than theoretical $3 \times \dots \dots \dots$                                                          |

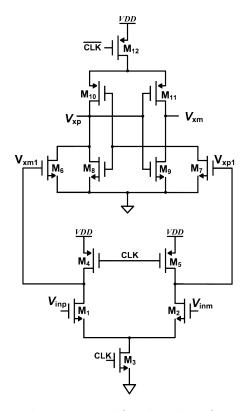

| 6.14 | The double tail sense amplifier has benefits in the new PAM4 context                                                                 |

|      | that outweigh the traditional StrongArm sense amplifier                                                                              |

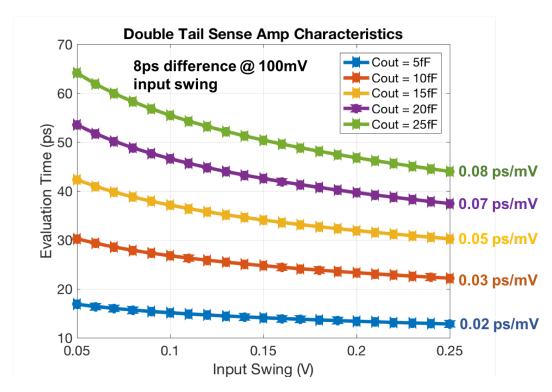

| 6.15 | The double tail sense amplifier evaluation-time "gain" may be characterized using Equations ?? and ??. The MATLAB simulation results |

|      | are plotted here                                                                                                                     |

| 6 16 | A comparison of the new, TDC-based PAM4 receiver and the tradi-                                                                      |

| 0.10 | tional, three-comparator architecture show the potential benefits when                                                               |

|      | viewing the link energy consumption. These results reflect not only                                                                  |

|      | the three-comparator difference, but also any secondary limitations on                                                               |

|      | $g_m$ due to the presence of the TDC                                                                                                 |

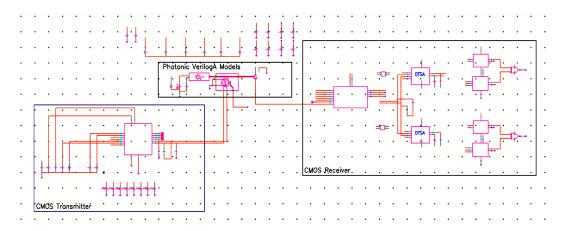

| 6.17 | The end-to-end photonic co-simulation schematic shows the Tx driver,                                                                 |

| 0.1. | photonic components, and the CMOS receiver                                                                                           |

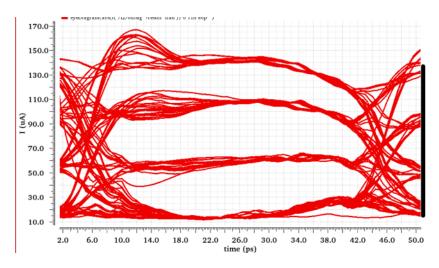

| 6.18 | The receiver input current eye is shown. This signal was produced by a                                                               |

|      | CMOS transmitter driving a photonic microring. The modulated light                                                                   |

|      | goes into a VerilogA photodiode to produce this eye                                                                                  |

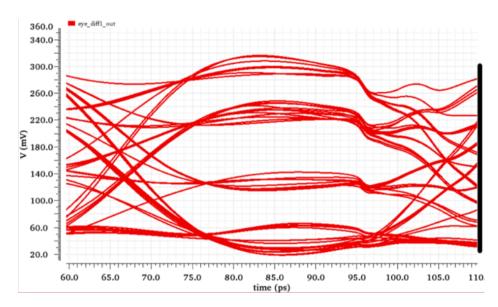

| 6.19 | The output of the Rx AFE is shown. This signal subsequently traverses                                                                |

|      | into a single slicer prior to digitizing.                                                                                            |

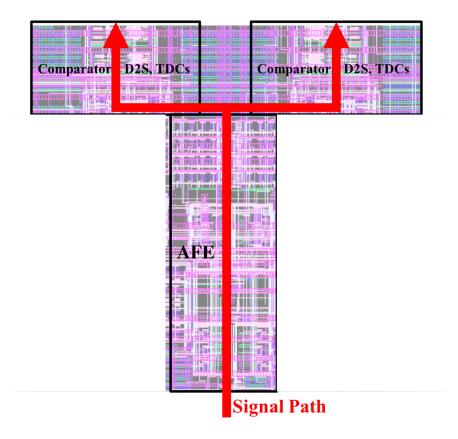

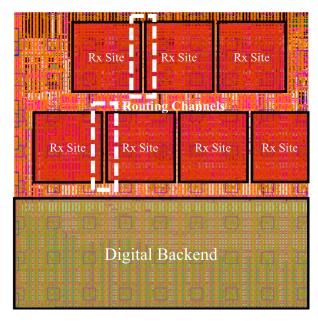

| 7.1  | The AFE's signal-critical blocks are placed first to ensure optimized                                                                |

|      | performance and minimize path lengths and parasitics                                                                                 |

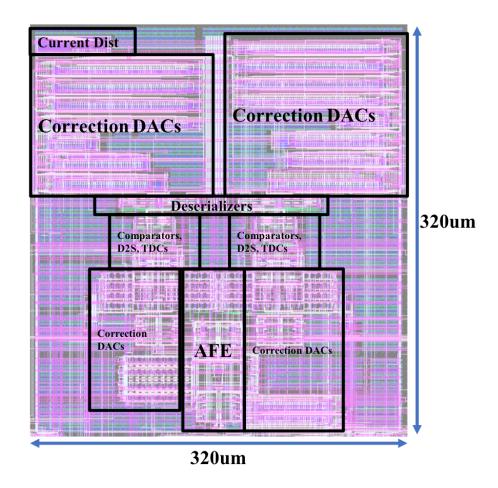

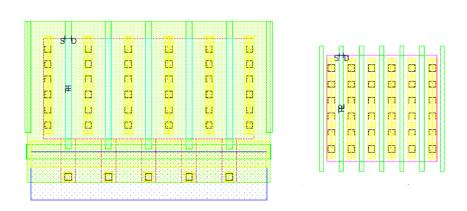

| 7.2  | The full Rx front-end layout is composed of the signal-critical blocks,                                                              |

|      | deserializers, and DACs                                                                                                              |

LIST OF FIGURES viii

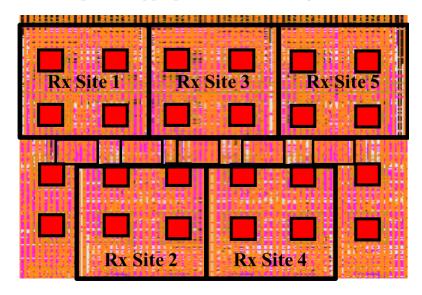

| 7.3  | The bumps (shown using the artistically rendered red squares) are spaced evenly, with the purpose of interposing with the components             |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------|

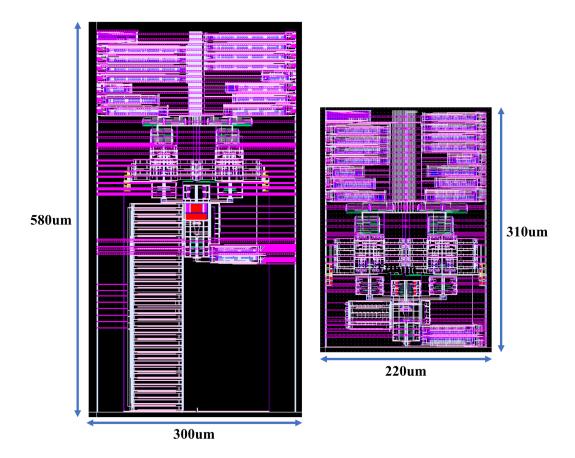

| 7 1  | on the photonic reticle                                                                                                                          |

| 7.4  | Bump pitch variations result in very simple changes to the macro script in order to produce the two flavors of Rx above (drawn to scale relative |

|      | ·                                                                                                                                                |

| 7.5  | to one another)                                                                                                                                  |

| 1.5  | front-end, provide much needed space to allow proper routing between                                                                             |

|      | the front-end digital bits and the digital backend                                                                                               |

| 7.6  | The body-connected and non-body connected transistor flavors are                                                                                 |

|      | vastly different from the standpoint of the generator. This image shows                                                                          |

|      | the two flavors, with similar widths and 5 fingers                                                                                               |

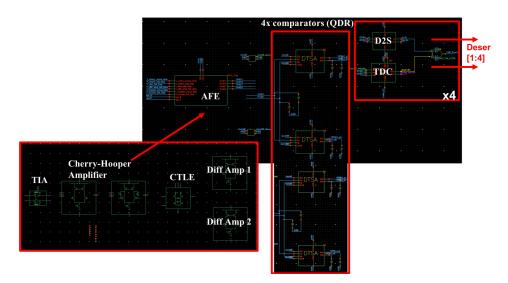

| 7.7  | The Rx AFE (simplified) schematic shows the main blocks along the                                                                                |

|      | critical signal path                                                                                                                             |

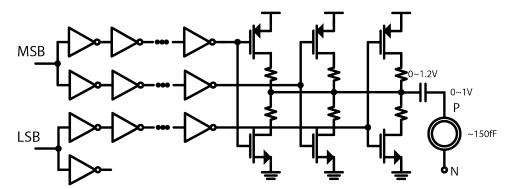

| 7.8  | The Tx-side AC driver uses a push/pull architecture to maximize the                                                                              |

|      | voltage swing across the microring modulator                                                                                                     |

| 7.9  | The closed loop thermal tuner serves to ensure that the microring                                                                                |

|      | resonance remains in lock. This scheme has the added benefit of not                                                                              |

|      | requiring an additional drop-port                                                                                                                |

| 7.10 | The self test schematic shows the full data path to characterize the                                                                             |

|      | AFEs                                                                                                                                             |

| 7.11 | The full Acacia system realizes a high speed, high performance end-                                                                              |

|      | to-end optical link with all necessary critical peripherals within the                                                                           |

|      | system                                                                                                                                           |

| 7.12 | By modifying the capacitive DAC code, the output frequency of the                                                                                |

|      | global clock distribution can be modified according to the plot above.                                                                           |

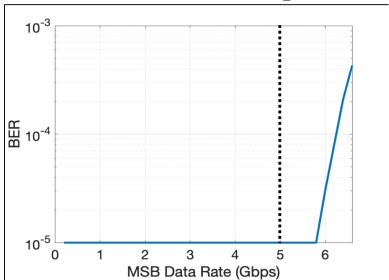

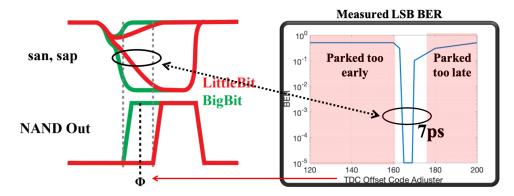

| 7.13 | The link's performance is shown for low frequency and operating in                                                                               |

|      | MSB-mode.                                                                                                                                        |

| 7.14 | The link's performance is shown for low frequency and operating in                                                                               |

| 715  | MSB-mode.                                                                                                                                        |

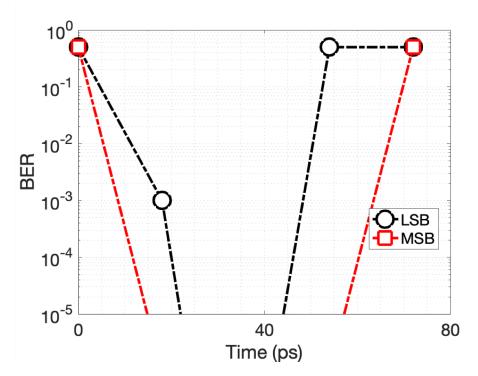

| (.15 | The bathtub curve of the Acacia link operating at 25.6Gbps is shown.                                                                             |

# List of Tables

| 3.1 | Model inputs and optimization variables                              | 28 |

|-----|----------------------------------------------------------------------|----|

| 3.2 | Minimum power laws for E/b limits dependence                         | 33 |

| 3.3 | Performance Comparison of Model-Predicted and Schematic-Simulated    |    |

|     | Optical Receivers                                                    | 35 |

| 6.1 | This table summarizes the alternate interpretation of the PAM encod- |    |

|     | ing scheme, using a single comparator's "timing information"         | 72 |

LIST OF TABLES x

#### Acknowledgments

This PhD came at a very opportune time in my life. On the one hand, I began this journey with a more refined sense of judgment, thought, and knowledge than, say, when I entered undergrad. On the other, I still consider myself young enough to mold, adapt, and grow to the people and environment around me. Putting that together, the people I bonded with during the last five years are special in not only being unique, exceptionally talented, loving, and hilarious but also having the ability to teach and change me for the better.

To begin, none of this would be possible without my advisor, Professor Stojanović. He gave me a chance and an opportunity to succeed at a time when I needed it the most. His knowledge was inspiring and his optimism has been the bane of my existence for the last half decade. And, most recently, his incredible dance moves have shown me that I have much to learn. Oh, and thanks for not caring about the many coffee-related issues in Cory.

During my PhD, I had the wonderful opportunity to engage with colleagues and faculty members both inside and outside of the circuits space. Thanks to Professor Eli Yablonovitch, whose brain-scratching questions left me dazed for days and to Professor Ming Wu for valuable insight into the photonic-device space. To Chris Keraly and Nicolas Andrade, thank you for your help refining and innovating the link framework. To Professor Elad Alon, looking forward to our next adventure together. To Professor Ali Niknejad, I wish we could have played more soccer, but the times we did play were boundlessly fun. And, to Erman Timurdogan, Zhan Su, and Prof Michael Watts at MIT for support with EPHI and Acacia.

This thesis would not be possible without the kind, caring direction of my fellow BWRC lab mates. To begin, teamvlada has been an endless source of literally everything. Sen Lin and Sajjad Moazeni have been my battle buddies throughout the years. Nandish Mehta has been a loving, caring force of nature for many a tape-outs. Pavan Bhargava, you are my fiercest ally and friend. To the Acacia team composed of Sidney, Kourosh, Ruocheng, Zhaokai, Eric KJ, and Nick, I really hope you learned a great deal during the process and had as much "fun" as I did. To Taehwan, Panos, and Christos thanks for your help and support over the years.

I would like to thank others at BWRC. Thank you to Greg and Luke who have never changed and I sincerely hope never will. Your support and intimidatingly strong background in circuits has been beyond helpful. To Antonio and John, thank you for your continued friendship and beards. To Bonjern, thanks for being the most excited Warriors fan I know. Nathan, thanks also for the beard and coming to my wedding. Looking forward to what's next. And thank you to Sameet, who was the best wedding officiant a guy could ask for. You are hilarious, logical, sharp, and caring. I hope there are no more pasta aglio e olios in our future.

Thank you to Chen, Mark, and Ranko for being fantastic mentors during my PhD. You have taught me many a lesson and I'm sure that that will continue.

Thank you Candy for basically running the center, for providing granola, and for plants/life/food advice. To Ajith, Brian, Fred, Melissa, Olivia, Yessica, Erin, and Leslie thanks for being the backbone of this center.

To those outside of BWRC, thank you to Vinay (and James, I guess) for still putting up with my incessant altitude humor. Thank you, Korok, for many fascinating conversations and chin (not a typo). Thank you, Jasdeep and Pingy for TiddleWinkle Pingydinkle and so much more. Thanks to the Bandits for letting me never sub out of ball games. This might be a good time to also thank Twalve for his support and ability to hold many many cars in his garage (and many hearts in his fish bowl). Thank you Kevin, Katrina, Jorge, and Dani for continued support. To Pallovy, Abhiram, Jiwon, Susan, Ankush, Riley, Anusha (blabla), Josh Hsaio, and Lakshmi, thank you all for being there for me.

I would not be an iota of the person I am now today without my family. To my dad, Dr. Raghu Kumar Settaluri, and mom, Sandhya Rani Settaluri. You two are jaw-droppingly inspiring and loving. Seriously, well done! To my dearest sister, Keertana. I'm so grateful to have you in my life and in BWRC. You will always have a special place in my heart, booboo.

Last, but certainly not least, thank you to my dearest wife, Pallavi. You have been a part of my life during all its ups and downs, yet you remain grounded, logical, and hilarious. I cannot think of a reality without you and I am endlessly in your debt. I am sure we have a lot more adventures to go on and I know we are ready for anything. And I'll be sure to take care of you anywhere we go – after all, I'm a doctor now.

-Krishna

# Chapter 1

# Introduction

With the recent increase in demand of high performance computing and with the emergence of the 5G mobile market, global IP traffic has steadily increased over the past 5 years and is projected to continue doing so for the foreseeable future. To meet these consumer communication bandwidth demands, modern data-centers and computers require optimization at every level in the system hierarchy. Silicon photonics integration within large-scale systems-on-chip (SoCs) has emerged as a primary contender in not only enhancing the capabilites of CMOS technologies, but also meeting the high bandwidth and low energy demands of these next-generation computing interconnects. Recent years have seen great strides in the development and commercialization of silicon photonic technologies.

However, as complexity and performance of these systems ever increases, many problems still remain and numerous new ones emerge. Specifically, to continue optimizing system efficiencies given new and ever changing process, technologies, and devices, a unified framework needs to be in place to quickly characterize and explore the design landscape. Moreover, to truly realize rapid design exploration, automation at every level in the hierarchy becomes mandatory – from high-level place and route optimization to low-level analog automation.

This thesis delves into optimizing the silicon photonic link performance by means of two parallel thrusts. First, the optimization of performance shall be approached by taking a fundamentals, theory-oriented approach. A link design framework which is versatile in process, technology, and device will be introduced in Chapter 3. This framework allows for quick optimization contingent on the CMOS as well as photonic parameters. From here, the validity of the framework will be further enforced in Chapter 4, wherein particular design points for the 65nm heterogeneously integrated photonic platform will be selected and explored. This work was published in "First Principles Optimization of Opto-Electronic Communication Links" in the IEEE Transactions on Circuits and Systems I: Regular Papers [1]. The authors of this work were Krishna T. Settaluri, Christopher Lalau-Keraly, Eli Yablonovitch, Vladimir Stojanovic. The author of this dissertation contributed in developing the

theory and methodology for the link design framework.

In addition, transmit-side exploration will also take place with the utilization of a new, nanoLED-based transmitter model. The nanoLED-based transmit work was published in "Optical Antenna nanoLED Based Interconnect Design" in the IEEE IPC 2018 [2]. The authors of this work were Nicolas M. Andrade, Krishna T. Settaluri, Seth A. Fortuna, Sean Hooten, Kevin Han, Eli Yablonovitch, Vladimir Stojanovic, and Ming C. Wu. The author's contribution to this work were in the form of the end-to-end link model incorporation with the nanoLED transmitter model.

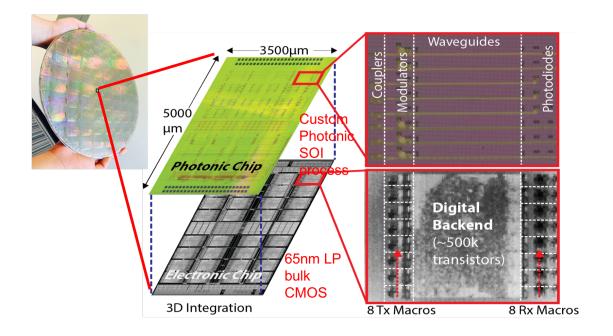

Next, in Chapter 5, a detailed analysis and design of an end-to-end 5Gbps NRZ link will be introduced. Here, we get a taste of the full design flow or "package" which comes about from aiming to design a full fledged optical link. This work was taped out and tested. The results were published in "Demonstration of an Optical End-to-End Link in a 3D Integrated Electronic-Photonic Platform" in ESSCIRC 2015, and authored by Krishna Settaluri, Sajjad Moazeni, Chen Sun, Erman Timurdogan, Michele Moresco, Zhan Su, Yu-Hsin Chen, Gerald Leake, Douglas LaTulipe, Colin McDonough, Jeremiah Hebding and Douglas Coolbaugh [3].

In the last portion of this dissertation, the performance bottleneck of optical links will be studied and it will be proven why the newly introduced single-comparator based PAM4 receiver architectures proves superior. Moreover, the rapid design flow and physical design challenges attributed to the various layers in the hierarchy will be looked into in detail.

# Chapter 2

# Background

In the parlance of circuit design, silicon photonics has stepped up as a clear contender in enhancing the capabilities of CMOS technologies. Indeed, photonics alongside CMOS systems can potentially improve energy efficiency and realize applications requiring higher bandwidths. Additionally, photonic links have the added benefit of having the channel loss (i.e. loss through an optical fiber) be weakly dependent on distance, allowing for better performance in long-range networks such as within the data center. Lastly, by incorporating multiple wavelengths of light within the same fiber through a techique called Wavelength Division Multiplexing (WDM), bandwidth density is greatly increased as compared with traditional, CMOS-only techniques.

In this chapter, we will introduce the foundational building blocks of silicon photonic links, namely components like photodiodes and microring resonators. Additionally, this chapter will showcase how these components fit together to enable true, end-to-end link operation. Lastly, with increasing complexity in analog design, tools that simplify the tasks of designing and laying out analog IP blocks are a treat to any mixed signal and systems engineer. This chapter will introduce the Berkeley Analog Generator (BAG), which aims to re-think the design process and redirect effort towards research and optimization of circuits rather than drawing polygons and laying out. Indeed, BAG is the foundation for a majority of this thesis and, as such, the mechanics and methodology for the tool will be "layed out" in this chapter.

## 2.1 Silicon Photonic Links

Silicon photonics-based links provide benefits over counterparts that use conventional, discrete optics or components. By utilizing a manufacturing platform that enables mass production and low cost, silicon photonic links and their associated designs follow an approach analogous with traditional CMOS-only systems, but with

added functionality and while retaining all the benefits. Silicon photonics also have the luxury of minimal overhead when incorporating with CMOS processes, thereby enabling very large-scale co-designs, where photonic components sit alongside CMOS circuits and transistors.

#### 2.1.1 Photonic Building Blocks

#### 2.1.1.1 Modulators and Microring Resonators

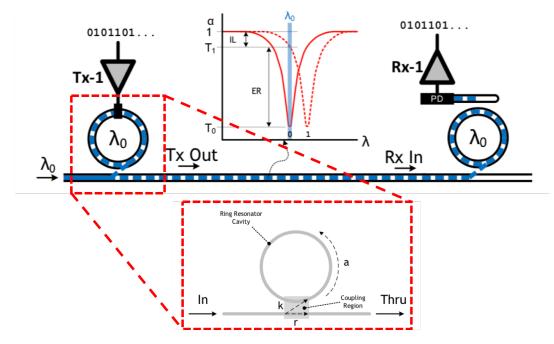

An optical modulator is responsible for "modulating" light on the transit side of an optical link. The mechanism for modulating the light as well as the means for encoding it are both free variables, dependent on the system architecture and purpose. However, in general, the modulator contains an electrical driver, which takes as input a digital rail-to-rail signal, which drives an optical component in a way that encodes the incoming digital sequence into variations in light intensity. The microring-based optical modulator, shown in Figure 2.1 is an attractive device in part because it enables on-off keyed (OOK) encoding easily, while also allowing for wavelength selectivity.

Figure 2.1: The microring modulator enables OOK encoding while also enabling wavelength selectivity.

A microring modulator, when coupled with a bus waveguide (shown as a zoomin in Figure 2.1), acts as a notch filter that either passes or circulates light from the "In-port" to the "Thru-port". The location of the notch in the wavelength-space is dependent on not only the length of the ring, but also the index of refraction. The location of the notch is also very dependent on the incoming electrical stimulus. This stimulus modifies the depletion width of the p-n junctions with the microring, thereby causing a change in the effective index of refraction and thus a shift in the notch location. Additionally, the ring introduces periodic notches in the wavelength space, which is contingent on the round trip distance that light traverses before either constructively or destructively interfering with the incoming light. This is summarized with the equation below:

$$\lambda_0 = \frac{n_{eff}L}{m} \quad m = 1, 2, 3, \dots$$

(2.1)

Aside from the location of the resonance itself, from the context of an end-to-end optical link, a few other parameters of the modulator are also important in dictating performance and behavior. Firstly, the insertion loss (IL) of the modulator, shown in Figure 2.1, dictates the loss caused by the ring when *inserted* into the system. Secondly, the extinction ratio (ER), also shown in Figure 2.1, is the power ratio between the ring driven by a "0"-signal and "1"-signal. Together, these two factors greatly infuence the performance and design of an end-to-end optical link. In general, to have the best behavior and ease the receiver-side design, smaller IL and larger ER are desirable. This manifests itself as a large optical modulator amplitude (OMA), while reducing the incoming laser power.

These specifications on the modulator become critical when optimizing endto-end link performance. As will be evident in later chapters, the design and cooptimization of these parameters, along with the design attributes of the CMOS technology itself, drastically influence the best-case energy per bit (E/b) of the link.

#### 2.1.1.2 Photodetectors

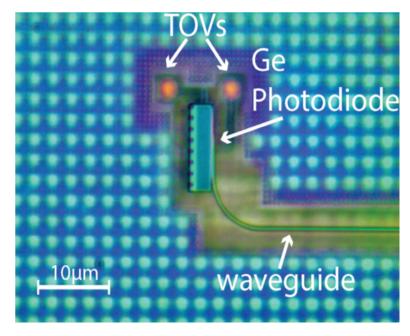

A photodetector (or photodiode) is a device which converts the incoming light into electrical current which may be decoded via the receiver circuitry. An example photodetector layout is shown in Figure 2.2.

The incoming waveguide provides the optical input to the photdetector. Based on the absorption properties of the detector, which are heavily dependent on the characteristics of the material composition, the detector generates a current proportional to the magnitude of the input optical signal. Indeed, because of the broad-band nature of the photodetector, a microring is generally appended before the photodiode itself to allow for wavelength selectivity.

Once again, from the context of an optical link system, particular specifications at the photodetector device level become critical in influencing the overall energy per bit. Namely, the three biggest contributors in performance are the optical bandwidth, responsivity, and added capacitance. The optical bandwidth of the photodetector,

Figure 2.2: The photodetector is responsible for generating an output current dependent on the input optical power.

or equivalently the Full Width Half Max (FWHM) of the pulse response for a linear photodiode, is a byproduct of transit time limitations of the material itself. Any degradations in generating carriers slows down rise/fall times of the incoming bit stream. The responsivity of the photodiode dictates how efficiently the device is able to generate electron/hole pairs. Lastly, the capacitance of the photodiode influences the electrical bandwidth. Contingent on the resistance seen by the photodiode, the resulting R-C time constant needs to be sufficiently high to not cause signal power roll-off. All of these specs, again combined with the CMOS properties of the receiver, influence the best-case performance of the link. Moreover, co-designing the various sub-components of the link (both CMOS and photonic) are critical in attaining the global optima.

## 2.1.2 Optical Communication Links

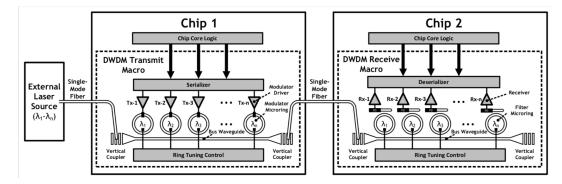

Putting together the sub-components detailed above along with an electronic backbone to encode, decode, and control the optics, a full optical link, shown in Figure 2.3 can be designed.

Figure 2.3 shows a bank of microring modulators on the transmit side and a similar bank on the receive side which drops the light onto the respective photodiodes. Notice also the presence of serializers and deserializers which aim to provide a low speed communication means to the rest of the digital backend. Additionally, the presence of thermal tuners on both sides allow the ring to maintain resonance lock

Figure 2.3: A WDM link composed of many transmit and receive side rings is an attractive solution which allows high bandwidth density.

despite thermal aggressors surrounding the system. In general, a separate drop port alongside the microring picks up fractions of the incoming light to allow for passive, background monitoring and tuning. Later in this work, during the design process for the Acacia system, a new type of thermal tuner will be introduced which does not rely on this added drop port. Rather, careful monitoring of the data sequence itself enables one to extract the approriate resonance information to ensure locking.

### 2.1.3 Circuit Design Challenges and Methodology

The best case energy per bit performance of an optical link is dependent on a multitude of factors. Parameters like data rate, technology, circuit topology, parasitics, etc. all influence the behavior and design of the system. Indeed, trade-offs between the devices, the technology, and system architecture all motivate the utilization of an all-encompassing photonic plus CMOS co-design. As will be the objective of later chapters, this precise co-design approach will be enforced in producing designs with optimal performance.

However, as is painfully evident to all high speed circuit designers, layout parasitics, matching, and other layout-specific design attributes greatly influence performance and functionality. As such, a design and layout engine or framework with the objective of simplifying the design and execution of these blocks is paramount. As will be detailed in Section 2.3, this framework combined with the co-design mantra detailed above, high speed, high performance optical link systems may be realized with ease.

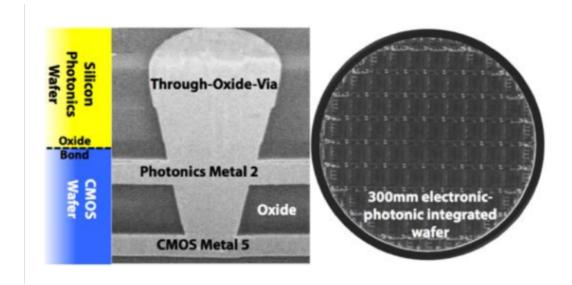

# 2.2 Silicon Photonic Integration Platforms

The integration platform with which the photonic and CMOS components intertwine is a key parameter which influencing the overall performance. Namely, the parasitic characteristics associated with the interconnect may easily become a bottleneck in performance. This section will detail the two main platforms used in this dissertation. Both of these platforms are heterogenously integrated platforms, meaning that the CMOS and photonics are designed independently on separate wafers. Shortly thereafter, they are attached to one another either using through-oxide vias (TOVs) and C4 ( $\mu$ Bumps).

#### 2.2.1 3D Integration Using Thru-Oxide Vias

The first wafer-scale 3D integration using TOVs was developed by the SUNY College of Nanoscale Sciences (CNSE).

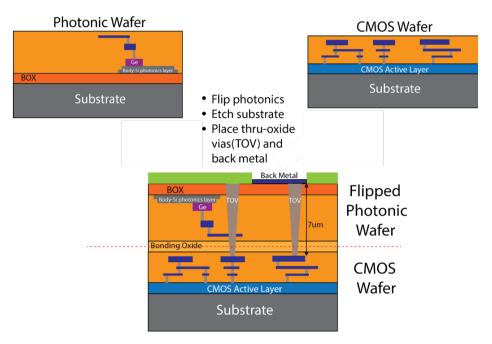

Figure 2.4: A cross section and top view of the TOV are shown.

The TOV, shown in Figure 2.4, connects the top metal layer of the CMOS wafer with that of the photonics. The process relies on firstly flipping the CMOS wafer, etching away the substrate to further reduce capacitance, and then punching TOVs to allow connectivity. With this approach, approximately 3fF of capacitance per TOV was observed. Indeed, this technique was utilized for demonstrating a full end-to-end link and will be detailed in a later chapter.

## 2.2.2 3D Integration Using Flip Chip $\mu$ Bumps

Using  $\mu$ Bumps is another popular technique to allow integration of the CMOS and photonics. In this technique, small, conductive balls are first placed on the top passivation opening of the wafer. The other wafer is then flipped and aligned onto the first. Once the alignment is correct, the balls are melted and collapsed to effectively

solder the connection between the two wafers. Using this technique, past work has demonstrated 20-50fF of capacitance per bump. However, their high yield and process dependence proves this techique promising.

# 2.3 Analog Circuit Design Challenges and Automation

As was detailed beforehand, analog and mixed signal design motivates the necessity of an alternative means of design. The Berkeley Analog Generator (BAG) is a framework that captures the methodology of the designer within the confines of a new framework that provides many useful features. More specifically, this framework allows not only for layout parameterization (which produces push-button design rule check clean and layout-versus-schematic clean designs), but rapid iteration on designs. Function calls enable generation of new designs, calls to simulators, parsing the simulator output results, and iterating quickly based on the feedback. BAG was utilized in the Acacia system for all analog and mixed signal sub-blocks.

#### 2.3.1 BAG Architecture and Flow

#### 2.3.1.1 Overview

An example BAG-based design flow which an engineer may undertake is shown in Figure 2.5.

Figure 2.5: The design flow of a new block within the BAG framework is shown.

Here, the objective is to design a DLL within the BAG framework. Due to the rapid iteration abilities of the framework, along with the reusability of past designs, the designer begins by checking the existing work for a similar script to run. Additionally, due to the parameterizable attributes of BAG-generated layouts, a multitude

of DLLs may be generated with a single design script, all at the push of a button. This allows for rapid reusability, contingent on the generator writer's scope for usage. Should the original generator not meet the needs of this specific architecture, the designer may choose to write his or her own generator, specific to the methodology employed by said designer. Lastly, iteration is highly possible based on the output of characterization scripts and simulations. Verification of specifications can also be done within the framework. This feedback-based design flow information is summarized in Figure 2.6.

Figure 2.6: The design flow with feedback from the output of simulations enables rapid iteration. [4]

#### 2.3.1.2 Design Example: StrongArm Sense Amplifier Generator

To further understand the design usage of the BAG framework, an example generator for a simple sub-block is outlined below. In this case, a StrongArm sense amplifier is chosen as the block of interest.

The StrongArm sense amp, shown in Figure 2.7, functions as a rudimentary analog-to-digital converter. The block takes as input two small analog voltages and generates rail-to-rail swing outputs. It does this by relying on the current discharge path of the input pair, followed by the cross-coupled action of the inverters.

Figure 2.7 not only shows the schematic, but also the example transient waveform of the outputs during the evaluation phase. Notice that the evaluation phase is composed of the initial linear (or integration) phase of the StrongArm followed by

Figure 2.7: The schematic, transient, and example floorplan of the StrongArm is shown.

the evaluation phase wherein the outputs cross-couple to opposite railed values. This is then proceeded by the reset phase, wherein both outputs take a  $V_{DD}$  value.

An important first step when undertaking designing a block within the BAG framework is to draw a sample floorplan of the block (this presumes that the topology is "fixed" or needs little maneuverability). This floorplan not only shows the positions of the various transistors and important signal wires, but also shows the direction of growth for the various transistors. The drawing of the important signal wires aid in identifying critical layout-dependent characteristics, such as presuming differential matching or minimizing trace lengths. The floorplan drawing aids the designer in properly coding up routings without the mental hassle of remembering all growth conditions and layout design constraints. The floorplan is then coded within the Python-based framework as a layout generator. The code itself follows a "boiler-plate" template, beginning with importing the parameter values, specifying the total width per row (within the framework, each horizontal row of transistors assumes a fixed FET width but can have variable number of fingers), drawing the basic template layout, instantiating the transistors themselves, creating the wire connections, and finally adding pins and fillers.

The schematic generator is also written by the designer, but is substantially easier to implement than the layout generator script. A simple template schematic followed by appropriately updating the parameters is sufficient to create a generator which outputs parameter-specific schematics. The layout generator script, combined with the schematic generator, produce unique schematic and layout instances dependent on an input list of parameters, such as FET widths, and number of fingers. A

sample output of the generators is shown in Figure 2.8.

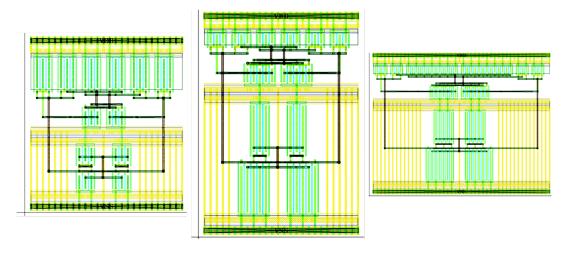

Figure 2.8: The output of the schematic and layout generators produce DRC and LVS clean instances of the StrongArm.

Indeed, with this layout and schematic generator, various instances of the StrongArm sense amplifier can be designed with the push and execution of the code. By simply modifying the dimensions of the transistors, instances such as those in Figure 2.9 can very easily be generated and verified. Notice that because the generator was written with sizing parameters incorporated within the layout, any permutation of transistor widths would easily yield DRC and LVS clean layout designs.

Figure 2.9: The framework allows for push-button instantiation and verification to generate quick, correct instances.

To further ensure that a layout and schematic are behaving properly when sim-

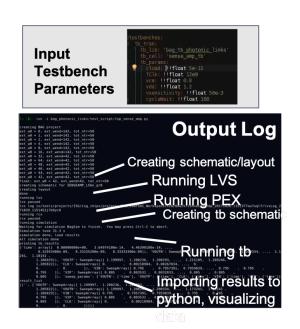

ulated, any particular instance can be pushed through the "entirety" of the flow, enabling rapid layout and schematic generation, verification, and post-PEX simulation to ensure the design specifications are met. This is highlighted in Figure 2.10. Input parameters, both within the layout and also within the simulation environment, can be modified and the design can proceed through the flow. The log shows the generation of the layout and schematic, run LVS, run PEX simulations, and analyze the resulting outputs. The waveforms are processed and shown in the right side of Figure 2.10.

Figure 2.10: Pushing an instance through a full design flow is simple within this codified environment.

## 2.4 Conclusion

In this chapter, we introduced the foundational blocks of both silicon photonics and analog automation. In providing this introduction, the reader should take careful note on the power of growing vast systems which rely on the marriage of these underlying foundations. Notably, understanding the device and block level parameters that influence macro-specifications at the system level is a powerful step in designing high performance optical links. Moreover, realizing that operating at these high speed-high performance corners rely heavily on layout parameters is the key to motivating the need for analog automation. With these two in mind, the rest of this

thesis aims to operate at the intersection of these foundations – one that focuses on multi-hierarchical fundamental theory and the other which focuses on executing and optimizing beginning with the "optimized" circuits and ending with physical design.

# Chapter 3

# End-to-End Optical Link Design Methodology

### 3.1 Introduction

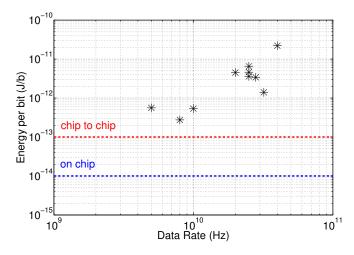

Optical interconnects, after having completely replaced electrical interconnects for long haul communication, are forecast to continue their expansion to shorter and shorter links, eventually bringing data directly to the processing chips, and even potentially replacing some of the longer interconnects on the chip itself [5]. This is due to several key aspects of optical interconnects: their potential for extremely high bandwidth, distance insensitivity of optical channel loss when compared with electrical, and better optical components and technology. Nevertheless, as illustrated in Fig. 3.1, in a world where energy dissipation from computing units is becoming increasingly important, optical links must still prove that they can offer a more energy efficient communication means than electrical links for shorter distances.

Commonly cited objectives for chip to chip links range in the  $\sim 100 \mathrm{fJ}$  per bit, and drop to  $\sim 10 \mathrm{fJ}$  per bit when considering on-chip interconnects [6]. These energy requirements, when combined with the extremely high bandwidths needed, still pose a number of challenges for optical links. The emergence of Silicon Photonics is offering new possibilities and prospects in this regard by enabling seamless integration of photonics and electronics on a single platform, thereby increasing energy efficiency. The purpose of this work is to model these links and optimize them in order to explore what limits can be reached in terms of energy efficiency and how these limits depend on the specific technology available.

Prior literature in this space has made strides in accurately modeling particular aspects of the link data path, namely the front-ends and the systems-level energy breakdowns ([7–9]). However, a proper marriage between "analog"-dominated and "digital"-dominated constraints has yet to be demonstrated. More specifically, in the context of optical receiver design, specifications on the sensitivity and power

Figure 3.1: Demonstrated Optical Link Efficiencies [6-15], Against Objectives From [6]. Further information at linksurvey.eecs.berkeley.edu.

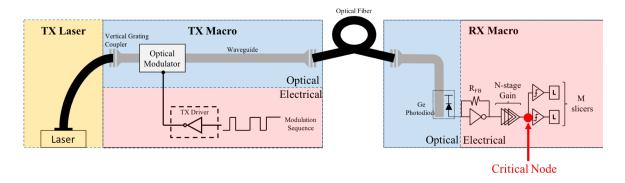

Figure 3.2: Optical Link System Overview

of the signal are contingent on the interaction of the front-end and the follow-on samplers that ultimately convert the analog signal into a digital bit, to set the overall energy, bandwidth, gain and noise properties. Linking all of these relevant interactions together, this work shows the behavior of the full optical link under different regimes of operation from the context of energy-efficiency and noise.

In this chapter, we will introduce and analyze the optical modeling framework, beginning with a high-level link picture and slowly delving down into the various subcomponents. The theory and "interface" between these blocks will also be studied. Once this foundation has be layed out, the focus will shift to the link-level, where macro-parameters will be derived and initial trade-offs will be studied. Lastly, using the framework, performance projections will be made which, in turn, gives insight into the direction of possible fabrication improvements in the future.

## 3.2 Optical Link Modeling

We consider a very general model for the optical link, which enables us to perform optimizations on its topology and estimate the optimal energy per bit which can be achieved at particular data rates given the technology constraints. The parameterized model topology is depicted in Fig. 3.2 and is detailed as such: the receiver element is constructed with a transimpedance front end followed by N amplifications stages and terminated with a sampling unit composed of M individual samplers. The number of amplification stages N, the size of each stage, the number of sampling units M and the sizing of its transistors constitute optimization variables. There is of course a variety of other receiver topologies or variations on the one suggested. The framework we describe next will be readily extendable to these topologies.

The energy consumed in the receiver can be computed from the bias currents and circuit capacitances, and its sensitivity is determined by two constraints: a noise constraint, and a system output voltage constraint. Finally, the energy consumed by the transmitter can be calculated starting from the receiver sensitivity requirement, and back-propagating that through the data path losses to the transmitter. The total energy is the sum of the receiver and transmitter energy, which is minimized with respect to the optimization variables at hand.

#### 3.2.1 High-Level Receiver Abstraction

The receiver is modeled as illustrated in Fig. 3.2. The front end consists of a transimpedance amplifier (TIA) that converts the input photocurrent to an output voltage signal, and is followed by N chained gain stages forming a voltage amplifier (VA) to further amplify the signal. All these amplifiers are considered to be first order stages (except for the TIA which has two poles: one from the photodiode capacitance and feedback resistor, and one from the input capacitance of the VA). The chaining of such stages causes the overall bandwidth to degrade. The bandwidth  $B_{chain}$  resultant from N first order stages of bandwidth  $f_S$  is [19]:

$$B_{chain} \sim f_S \frac{0.9}{\sqrt{N+1}} \tag{3.1}$$

We set the target end-to-end bandwidth to  $0.7 \times f_{data}$ , where  $f_{data}$  is the Nyquist rate of the input data stream. This implies that the bandwidth  $f_S$  of each stage must be

$$f_S > 0.7 f_{data} \frac{\sqrt{(N+2)+1}}{0.9}$$

(3.2)

in order to satisfy this constraint. The factor of 2 comes as a result of the two poles imposed by the TIA.

#### 3.2.2 Gain-Bandwidth product

While the unity current gain-bandwidth of a technology is  $f_T$ , the actual gain bandwidth that is achieved in an individual gain stage that is loaded by its replica will be lower due to various parasitics and non idealities. Additionally, different gain stage topologies will yield different GBWs. For example, inductive peaking is a popular way of enhancing the bandwidth and will yield a higher GBW than simple resistively-loaded stages. Therefore we use a parameter  $\alpha$  which describes what fraction of  $f_T$  is achieved by each individual gain stage. The GBW of a replica-loaded stage is therefore  $f_a = \alpha f_T$ .

#### 3.2.3 Voltage Amplifiers

Here, we introduce the analysis of the follow-on voltage amplifiers, which helps lay the foundation for the analysis of the transimpedance amplifier stage. Every stage in the voltage amplifier is defined by input transistor gate width  $W_{gate,i}$  (where "i" denotes its position in the amplifier chain), which then also defines its transconductance  $g_{m,i}$ , gate capacitance  $C_{ox,i}$  and bias current  $I_{d,i}$ . To simplify the problem, we assume that  $g_m$ ,  $C_{ox}$ , and  $I_d$  are simply proportional to  $W_{gate}$ , which implies that the biasing for each transistor is relatively similar—a reasonable assumption to first order. The GBW of each stage depends on the capacitance seen at the output, and in the case of simple resistively loaded stages, we have  $GBW_i = g_{m,i}/(C_{out,i} + C_{in,i+1})$ . We define  $\beta = C_{out}/C_{in}$  as the ratio of output to input capacitance of a gain stage. Similar to  $\alpha$ ,  $\beta$  is dependent on the stage topology.

In the model, two factors are used to characterize the individual gain stages:  $\alpha = \frac{f_a}{f_T}$ , the ratio of the gain bandwidth to  $f_T$  of a replica loaded stage, and  $\beta = \frac{C_{out}}{C_{in}}$ , the ratio of input to output capacitance. Here we calculate  $\alpha$  and  $\beta$  for simple  $g_m R_L$  topology and cascode stages for the 65nm platform used.

#### 3.2.3.1 $\alpha$ -factor Derivation

For a simple  $g_m R_L$  topology we have

$$C_{in} = C_{ox} + AC_{gd} (3.3)$$

where the second term accounts for the Miller Effect, and  $C_{out} = C_{gd} + C_{ds}$ . For a cascode stage, we have

$$C_{in} = C_{ox} + C_{qd} (3.4)$$

Notice that the  $C_{GD}$  seen by the input does not see the Miller effect due to the intermediary FET between the input FET and the output node.

Given that  $C_{ox} = 0.5 fF/\mu m$ ,  $C_{gd} = 0.2 fF/\mu m$ ,  $C_{gs} = 0.27 fF/\mu m$ , we have  $\alpha = 0.36$  for a standard  $g_m R_L$  stage and  $\alpha = 0.4$  for a cascode stage.

#### 3.2.3.2 $\beta$ -factor Derivation

With the expressions given above, it is easy to show that  $\beta = 0.29$  for  $g_m R_l$  stages and  $\beta = 0.4$  for cascode stages.

To summarize,

$$f_a = \frac{g_m}{(1+\beta)C_{in}} \tag{3.5}$$

and we can derive the GBW of every stage as:

$$GBW_{i} = \frac{g_{m,i}}{C_{out,i} + C_{in,i+1}} = f_{a} \frac{1 + \beta}{\beta + \frac{W_{gate,i+1}}{W_{gate,i}}}$$

(3.6)

As mentioned earlier, each gain stage must also have a 3-dB bandwidth of  $f_S$ , so that the DC gain of stage i in the linear amplifier is:

$$G_{DC,i} = \frac{f_a}{f_S} \frac{1+\beta}{\beta + \frac{W_{gate,i+1}}{W_{gate,i}}}$$

(3.7)

The maximum gain is capped by the intrinsic gain of the devices  $g_m r_0$ . For the last stage, the capacitance driven is the sampler's input capacitance  $C_{SA}$ . Finally the power consumed by each stage is  $V_{DD}I_{bias,i}$ , where  $I_{bias,i} = g_{m,i}V_{ov}$ , where  $V_{ov}$  is the stage overdrive voltage, which is considered to be the same for every stage. The motivation for the constant overdrive voltage stems from insight gained while executing the optimization framework. Namely, adding  $V_{ov}$  as an optimization parameter yielded little performance improvement over holding it constant, while adding a significant time overhead in terms of optimization convergence.

## 3.2.4 Transimpedance Amplifier

The transimpedance amplifier (TIA) is composed of a gain stage similar to those in the VA, with a feedback resistor chosen to meet the bandwidth requirement per stage  $(f_S)$ . The open loop gain is calculated similar to the VA stage gain. The feedback resistor is therefore set to:

$$R_{FB} = \frac{G_{DC,TIA}}{2\pi f_S(C_{PD} + C_{in,TIA})}$$

(3.8)

where  $C_{PD}$  is the photo-detector parasitic capacitance including the interconnect between the photo-detector and the TIA, and  $C_{in,TIA}$  is the TIA input capacitance. The two poles resulting from the TIA designed in this fashion are not real, and the damping factor is  $\zeta = \frac{1}{2} \frac{2 + G_{DC,TIA}}{1 + G_{DC,TIA}}$  bounded as  $0.5 < \zeta < 1$ , implying the bandwidth is marginally greater than if the poles were real. This means that (3.2) slightly overestimates the required bandwidth per stage. To first order this is an acceptable approximation.

The total transimpedance gain of the front end is therefore

$$R_{tot} = \frac{R_{FB} G_{DC,TIA}}{1 + G_{DC,TIA}} \prod_{i=1}^{N} G_{DC,i}$$

(3.9)

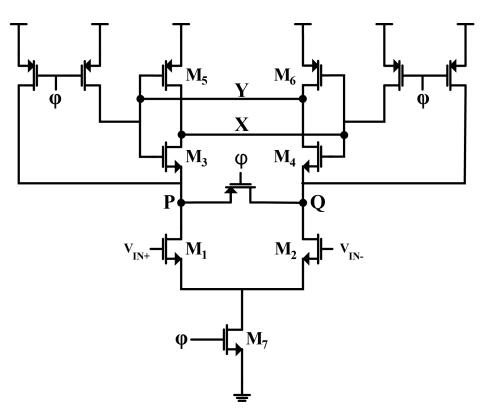

Figure 3.3: StrongArm Sampler Schematic

## 3.2.5 Sampler Model in Receiver

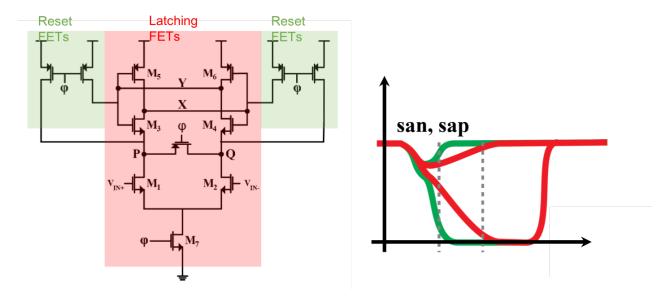

The role of the sampler is to bring the signal coming out of the amplifier to logic levels so that the digital circuit can effectively process it at the output. The modeling described here enables the efficient optimization of transistor sizes in order to yield optimal sampler performance in terms of sensitivity and power consumption. Most samplers rely on a positive feedback latching mechanism, such as a cross coupled inverter pair in order to achieve exponential gain and recover digital levels from

extremely low signal voltages. The sampler analyzed here, and depicted in Fig. 3.3 is known as the StrongArm, but the presented analysis and trends can be generalized to a large family of sampler topologies, such as CML-based samplers or more exotic techniques such as double-tail sampling.

#### 3.2.5.1 StrongArm Operating Principle

Before the sampler starts evaluating, the clock is down, and the nodes P,Q,X and Y are brought up to VDD by the reset transistors driven by clock,  $\phi$ . The evaluation starts when the clock goes up, and is composed of two periods,: the sampling period, where in the nodes P,Q, X and Y discharge through M1, M2, M3, M4 and M7, building a differential voltage on nodes X and Y. The sampling period ends when  $V_{X,Y}$  reach  $V_{DD} - V_{th,P}$  and the cross coupled inverters composed of M3, M4, M5 and M6 turn on. The regeneration then starts and the differential voltage on nodes X and Y is amplified to logic level by the latch.

#### 3.2.5.2 Sampling Period

The sampling phase can itself be divided into two separate phases. The first, during which only M1 and M2 are on, discharges nodes P and Q until they reach  $V_{DD} - V_{th,N}$ . The common mode voltage  $V_{PQ}$  behaves as  $V_{DD} - \frac{I_1 t}{C_{PQ}}$  where  $I_1 = g_{m1,2}V_{CM}$  is the current drawn by the common mode and lasts  $t_1 = \frac{V_{th,N}C_{PQ}}{I_1}$

The second phase starts when M3 and M5 are also on, therefore discharging nodes X and Y. It ends when  $V_{XY} = V_{DD} - V_{th,P}$ . The common mode behaves according to

$$V_{XY} = V_{DD} - \frac{I_1}{C_{PQ} + C_{XY}}$$

$$[(t - t_1) + \tau (exp(-\frac{t - t_1}{\tau}) - 1)]$$

where  $\tau = \frac{C_{XY}C_{PQ}}{g_{m,3}(C_{XY} + C_{PQ})}$  (3.10)

There is no closed form solution to determine when nodes XY reach  $V_{DD} - V_{th,P}$ , but if  $\tau$  is small compared to  $V_{th,P}(C_{PQ} + C_{XY})/I_1$ , which is usually the case, the end time of the second sampling phase may be approximated as

$$t_2 \sim \frac{V_{th,P}(C_{PQ} + C_{XY})}{I_1} + \tau + t1$$

(3.12)

The differential mode, during the second phase, can be shown [20] to follow the equation:

$$\frac{d\Delta V_{XY}}{dt} = \frac{g_{m3,4}}{C_{XY}} (1 - \frac{C_{XY}}{C_{PO}}) \Delta V_{XY} - g_{m3,4} \frac{\Delta It}{C_{PO}C_{XY}}$$

(3.13)

$$\Delta V_{XY}(t) = \int \left[ \frac{g_{m3,4}}{C_{XY}} (1 - \frac{C_{XY}}{C_{PQ}}) \Delta V_{XY} - g_{m3,4} \frac{\Delta It}{C_{PQ}C_{XY}} \right] dt$$

(3.14)

$$\Delta V_{XY}(t) = \frac{g_{m,1}}{C_{XY} - C_{PO}} \left( t - t_1 + \tau_{\Delta} \left( 1 - exp\left(\frac{t - t_1}{\tau_{\Delta}}\right) \right) \right)$$

(3.15)

$$\tau_{\Delta} = \frac{g_{m,3}}{C_{XY}} \left( 1 - \frac{C_{XY}}{C_{PO}} \right) \tag{3.16}$$

Since  $C_{XY}$  is usually greater than  $C_{PQ}$ ,  $\tau_{\Delta}$  is usually negative, and there is no regeneration gain during the sampling period. The sampling gain can be approximated as

$$G \sim \frac{V_{thresh}}{V_{CM} - V_{thresh}} \frac{C_{PQ} + C_{XY}}{C_{XY} - C_{PQ}}$$

(3.17)

## 3.2.5.3 Regeneration Period

Once the top PMOS transistors turn on, the regeneration period starts. The approximation is made that only the cross-coupled inverter pairs are on, providing positive feedback gain, with a time constant

$$\tau_{reg} = \frac{g_{m,3} + g_{m,5}}{C_{in,D2S} + C_{out,SA}} \tag{3.18}$$

#### 3.2.5.4 StrongArm Model within Framework

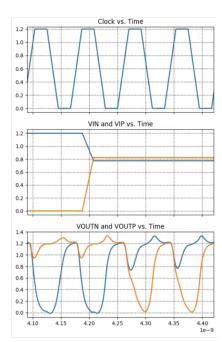

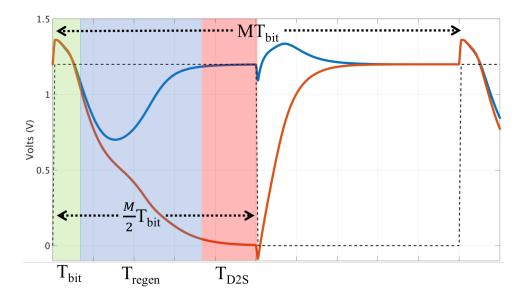

The modeled sampling stage is made of M interleaved StrongArm samplers (also referred to as Sense Amplifiers (SA)), that evaluate the bits sequentially. This means each individual StrongArm has a cycle  $M \times T_{bit}$  long. Half of this period is dedicated to the resetting of the sampler, while the other half is dedicated to the integration and regeneration of the bit (minus the setup time of the follow-on flip-flop  $T_{D2S}$ ) so that the actual time the sampler is evaluating is  $T_{SA}$ , given in (3.21). The schematic of an individual sampler is depicted in Fig. 3.3 and sample transient waveforms are shown in Fig. 3.4. The blue and red lines show the complementary outputs of the StrongArm sampler (nodes X and Y in Fig. 3.3). The integration period lasts while the input pair discharges nodes P,Q,X and Y until nodes X and Y reach  $V_{DD} - V_{th,P}$  which dictate when the cross coupled pair turns on and the regeneration period starts [20]

$(V_{th,P})$  is the threshold voltage of the PMOS). Fig. 3.4 shows a StrongArm's transient characteristics with the three main regimes of operation highlighted. The regeneration gain is generated by a cross coupled pair forming a latch, is exponential with time, and brings the output signal to logic levels.

Figure 3.4: Sampler Timing Evaluation Breakdown

The optimization variables available are the common mode voltages at the input, the gate widths of the input transistors, and the gate widths for the cross coupled pair transistors. These define the length of the integration period (which must stay under  $T_{bit}$  in order to avoid intersymbol interference), the integration gain, and the regeneration gain. The size of the tail transistor,  $M_7$ , is not considered to be an optimization parameter and is sized to be at least 2x larger than the input pair,  $M_1$  and  $M_2$ , and therefore not current-limiting the signal path.

The sampler then drives a dynamic to static (D2S) converter stage which we simply characterize as a load capacitance to the sampler,  $C_{in,D2S}$  [21]. The D2S requires a fixed amount of time  $T_{D2S} \sim \frac{2}{f_T}$  to latch, which is taken out of the total evaluation time. Approximations are nevertheless given here:

$$T_{int} \sim \frac{V_{TH}(2C_{PQ} + C_{XY})}{g_{m.1}(V_{CM} - V_{TH})}$$

(3.19)

$$G_{int} \sim \frac{V_{TH}}{V_{CM} - V_{TH}} \frac{C_{PQ} + C_{XY}}{C_{XY} - C_{PQ}}$$

(3.20)

$$T_{SA} = M/2 \times T_{bit} - T_{D2S} \tag{3.21}$$

$$G_{SA} \sim G_{int} \exp\left(\frac{T_{SA} - T_{int}}{\tau_{reg}}\right)$$

(3.22)

$$\tau_{reg} = \frac{g_{m,3} + g_{m,5}}{C_{in,D2S} + C_{out,SA}};$$

(3.23)

where  $V_{TH}$  is the absolute value of the threshold voltages and  $G_{SA}$  is the final sampler gain. Finally the input capacitance of the SA seen by the front end is given by  $M \times C_{ox,SA}$ . The fanout M is detrimental to the gain of the front end, and, as will be shown, can be amortized by using switches that connect only one sampler at a time to the output of the VA. In this case, the input capacitance seen by the front end is approximately  $C_{ox,SA}$  neglecting wire capacitance and junction capacitance effects of the sampling switches and the RC time associated with them. This assumption holds true for reasonable number of samplers:

$$M < \frac{f_T}{f_{data}} \frac{C_{ox}}{C_{ad}} \tag{3.24}$$