# UCLA UCLA Electronic Theses and Dissertations

### Title

Digital Calibration of Wide Bandwidth Open-Loop Phase Modulator

# Permalink

https://escholarship.org/uc/item/1x7892fb

### **Author** Nidhi, Nitin

# Publication Date 2015

Peer reviewed|Thesis/dissertation

# UNIVERSITY OF CALIFORNIA

Los Angeles

Digital Calibration of Wide Bandwidth Open-Loop Phase Modulator

A dissertation submitted in partial satisfaction of the

requirements for the degree Doctor of Philosophy

in Electrical Engineering

by

Nitin Nidhi

2015

© Copyright by

Nitin Nidhi

2015

## **ABSTRACT OF THE DISSERTATION**

### Digital Calibration of Wide Bandwidth Open-Loop Phase Modulator

by

Nitin Nidhi

Doctor of Philosophy in Electrical Engineering University of California, Los Angeles, 2015 Professor Sudhakar Pamarti, Chair

The rapid rise in demand for high data rates has led to communication standards like LTE that use signals with wide signal bandwidth and high peak-to-average power ratio. Since, total power consumption is largely determined by the efficiency of the power amplifier used, high efficiency architectures like polar and out-phasing, are preferable for future transmitter designs. Such architectures require a phase modulator (PM) as one of their key building blocks. The recent developments in phase modulator design have demonstrated superior wide-bandwidth performance of open loop modulation techniques. However, currently the resolution is limited by systematic errors inherent in the phase modulator circuit and random errors due to inevitable component mismatches.

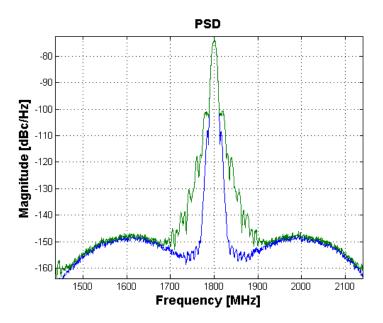

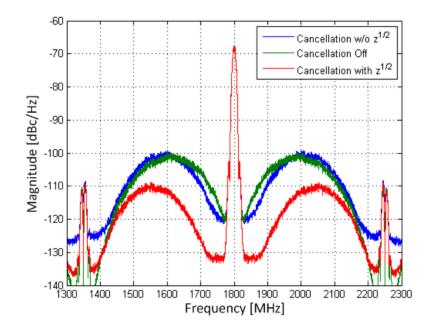

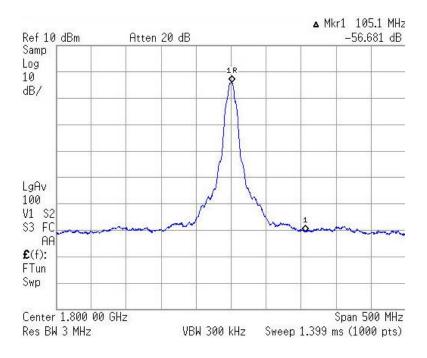

In this dissertation, a phase-interpolator based open-loop phase modulator is proposed, which leverages a digital calibration technique to mitigate the sources of phase errors and achieves excellent phase resolution. At the heart of this technique, a time-todigital converter performs high resolution measurement of phase errors of the phase modulator. These measurements are used to continuously pre-distort the modulation data, so that the linearity of the overall transfer function is enhanced, thereby resulting in low out-of-band emission and low in-band noise. A prototype IC was implemented in 0.13 µm CMOS process. Measurements on the prototype show that out-of-band quantization noise is 56-dB lower than the signal when transmitting 20-Mb/s GFSK signal and the r.m.s. error is only 3.2%. The power consumption of the phase modulator is 18 mW. Since the IC was implemented in 0.13 µm CMOS process, the power is expected to reduce a lot, if it is implemented in finer process nodes. The dissertation also presents theory and measurement results on frequency synthesis using the open-loop phase modulator. New frequency can be synthesized with very fine frequency step size, by applying a digital phase ramp to the phase modulator. However, the non-linearity of the phase modulator results in strong spurious tones. Digital compensation is proposed to mitigate these spurs, and generate multiple lowjitter clocks.

The dissertation of Nitin Nidhi is approved.

Babak Daneshrad

Milos D. Ercegovac

Dejan Markovic

Sudhakar Pamarti, Committee Chair

University of California, Los Angeles

2015

Dedicated to my parents and wife

### ACKNOWLEDGMENTS

First and foremost, I wish to express my sincere thanks to my advisor Professor Sudhakar Pamarti for his continuous technical support and guidance, and for providing me with all the necessary facilities for the research. His insightful guidance has made this a very thoughtful and rewarding journey. I appreciate his ability to provide discerning feedback and spur original thinking.

Next, I would also like to express my honest appreciation towards my doctoral committee members: Professor Babak Daneshrad, Professor Dejan Markovic and Professor Milos D. Ercegovac, for their generous time and support, as I progressed along with my research.

I am extremely thankful to Pin-En Su for generously sharing his research work. I am thankful to Chun-Ming Hsu, Michael Straayer and Professor Michael Perrott for allowing me to use their PLL design.

I have learned a lot through my interactions with my groupmates and friends, Nitesh Singhal and Abhishek Ghosh. I am extremely grateful towards my other groupmates who also extended their generous support at various points of time: Neha, Mukesh, Vikrant, Pritika, Sunbo, Manas, Jeffrey, Sameed and Haoxing. Neha and Abhishek were extremely helpful in getting things done at UCLA, while I was in San Diego.

My stay at UCLA was made extremely enjoyable by the company of several other friends: Vaibhav, Hari, Joseph, Pratyush, Richa, Vijay, Gaelen, Shaunak, Bibhu and many others.

Above all, I am thankful to my parents, and my sister Shalini for their encouragement and blessing, for all these years. Finally, I would like to thank my wife Sonam for her constant love and invaluable support.

### VITA

| 2005      | Bachelors in Engineering Physics<br>Indian Institute of Technology<br>Bombay, India               |

|-----------|---------------------------------------------------------------------------------------------------|

| 2005-2007 | Masters in Electrical Engineering<br>University of California, Los Angeles                        |

| 2007-2008 | RFIC Design Engineer<br>Conexant, Los Angeles                                                     |

| 2008-2012 | Design Engineer<br>NXP Semiconductors, San Diego                                                  |

| 2012-     | Principal Engineer<br>IQ-Analog, San Diego                                                        |

| 2008-2015 | Graduate Student<br>Department of Electrical Engineering<br>University of California, Los Angeles |

#### PUBLICATIONS

Singhal, N.; Nidhi, N.; Pamarti, S.; "A power amplifier with minimal efficiency degradation under back-off," Circuits and Systems (ISCAS), Proceedings of 2010 IEEE International Symposium on, vol. no. pp. 1851-1854, May 30 2010-June 2 2010.

Singhal, N.; Nidhi, N.; Ghosh, A.; Pamarti, S.; , "A 19 dBm 0.13um CMOS parallel class-E switching PA with minimal efficiency degradation under 6 dB back-off," Radio Frequency Integrated Circuits Symposium (RFIC), 2011 IEEE, vol. no., pp.1-4, 5-7 June 2011.

Singhal, N.; Nidhi, N.; Patel, R.; Pamarti, S.; , "A Zero-Voltage-Switching contour-based power amplifier with minimal efficiency degradation under back-off," Microwave Theory and Technique, IEEE Transactions on, vol. 59, no. 6, pp. 1589-1598, June 2011.

Nidhi, N., Su, P.-E., and Pamarti, S., "Open-Loop Wide-Bandwidth Phase Modulation Techniques," Journal of Electrical and Computer Engineering, vol. 2011, Article ID 507381, 12 pages, 2011.

Nidhi, N.; Pin-en Su; Pamarti, S., "Open loop modulation techniques for wide bandwidth digital frequency synthesis," Circuits and Systems (MWSCAS), 2011 IEEE 54th International Midwest Symposium on , vol., no., pp.1,4, 7-10 Aug. 2011

Weinan Gao; Huff, B.; Hess, K.; Coulibaly, D.; Pala, C.; Jiang Cao; Bhatia, J.; Waltari, M.; Levin, L.; Cathelin, C.; Nouvet, T.; Nidhi, N.; Kodkani, R.; Maeda, R.; Costa, D.; McFee, J.; Moazzam, R.; Vincent, H.; Durieux, P., "A digital single-wire multiswitch (DSWM) channel-stacking IC in 45nm CMOS for satellite outdoor units," Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2013 IEEE International , vol., no., pp.244,245, 17-21 Feb. 2013

Nidhi, N.; Pamarti, S., "A 1.8GHz wideband open loop phase modulator with TDC based nonlinearity calibration in 0.13 um CMOS," Radio Frequency Integrated Circuits Symposium (RFIC), 2015 IEEE, 17-19 May, 2015

| ABSTRAC     | CT OF THE D    | SSERTATION ii                                          |

|-------------|----------------|--------------------------------------------------------|

| ACKNOW      | LEDGMENT       | S vi                                                   |

| VITA        |                | viii                                                   |

| List of Tab | oles           | xiii                                                   |

| List of Fig | ures           | xiv                                                    |

| Chapter 1:  | Introduction   | 1                                                      |

| 1.1         | Motivation     | 1                                                      |

| 1.1         | Organization.  | 4                                                      |

| Chapter 2:  | Wideband Dig   | tial Phase Modulation – Prior Art6                     |

| 2.1         | Closed Loop    | Phase Modulators                                       |

| 2.2         | Open Loop Pl   | ase Modulators                                         |

|             | 2.2.1 Multiple | Output Clock Generation17                              |

| Chapter 3:  | Open Loop Pl   | ase Modulation                                         |

| 3.1         | Introduction   |                                                        |

| 3.2         | Design Consid  | derations In Digital Phase Modulation24                |

|             | 3.2.1 Generati | on of Discrete Phases                                  |

|             | 3.2.2 Phase Q  | uantization Noise                                      |

|             | 3.2.2.1        | Power Spectral Density of Phase Quantization Noise .32 |

|             | 3.2.2.2        | Phase Quantization Noise Shaping32                     |

|             | 3.2.2.3        | Phase Quantization Noise Cancellation                  |

|             | 3.2.3 Spectral | Images                                                 |

|             | 3.2.4 Synchro  | nization of Phase Switching                            |

|             | 3.2.5 Phase En | rors in the Phase Generator40                          |

|             | 3.2.5.1        | Systematic Errors                                      |

|             | 3.2.5.2        | Random Errors40                                        |

|             | 3.2.5.2        | Dynamic Errors                                         |

| 3.3         | Quantization   | Noise Cancellation: Optimization Techniques43          |

|           | 3.3.1 Advancement of Cancellation Signal                                       | 43     |

|-----------|--------------------------------------------------------------------------------|--------|

|           | 3.3.2 Reduction in Integration Time                                            | 47     |

|           | 3.3.3 Combination of Cancellation Signal Advancement and F<br>Integration Time |        |

|           | 3.3.4 Optimized Modulator for PQN Shaping                                      | 50     |

|           | 3.3.4 Quantization of Cancellation Signal                                      | 50     |

| 3.4       | Receive Band Noise                                                             | 53     |

| 3.5       | Chapter Appendix                                                               | 55     |

|           | 3.5.1 Noise Transfer Function in Phase Quantization Noise                      | 55     |

|           | 3.5.2 Spectral Images of Phase Ramp                                            | 57     |

|           | 3.5.3 Harmonic Mixing of RF Carrier Harmonics and Phase R                      | .amp59 |

| Chapter 4 | 4: Digital Calibration of Phase Modulator                                      | 62     |

| 4.1       | Prior Art on Phase Modulator Linearity Improvement                             | 62     |

|           | 4.1.1 Phase Interpolation with Low Offset Reference Phases                     | 62     |

|           | 4.1.2 LC Filtering of LO Input                                                 | 63     |

|           | 4.1.3 Digital Pre-distortion                                                   | 63     |

| 4.2       | Proposed Non-Linearity Calibration Technique                                   | 64     |

|           | 4.2.1 Proposed Technique: Concept                                              | 64     |

|           | 4.2.2 Proposed Technique: Design Considerations                                | 68     |

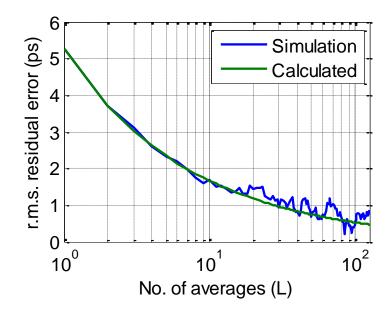

|           | 4.2.2.1 Averaging and Residual Noise                                           | 68     |

|           | 4.2.2.2 Calibration Speed                                                      | 72     |

|           | 4.2.2.3 Temperature Sensitivity                                                | 73     |

|           | 4.2.2.4 Dynamic Errors                                                         | 74     |

| Chapter : | 5: Phase Modulator Circuit Design and Measurement Results                      | 77     |

| 5.1       | Circuit Design                                                                 | 77     |

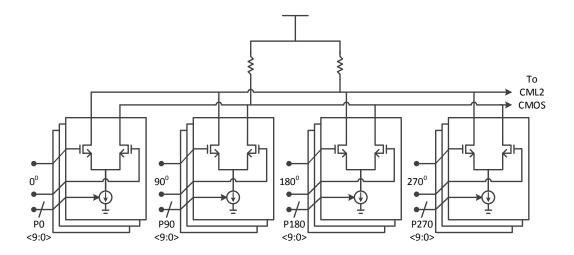

|           | 5.1.1 Phase Generator Design                                                   | 77     |

|           | 5.1.1.1 Digital Data Interface                                                 | 78     |

|           | 5.1.2 Digital PLL                                                              | 79     |

|           | 5.1.3 Reference Phase Buffer Design                                            | 80     |

|           | 5.1.4 CML-to-CMOS Design                                                       | 82     |

|           | 5.1.5 System Design         | 84 |

|-----------|-----------------------------|----|

| 5.2       | Measurement Results         | 85 |

|           | 5.2.1 Measurement Setup     | 85 |

|           | 5.2.2 GFSK Modulated Data   | 87 |

|           | 5.2.3 16-QAM Modulated Data | 93 |

|           | 5.2.4 Frequency Generation  | 94 |

| Chapter 6 | : Conclusion                | 96 |

| Reference | es                          | 98 |

# List of Tables

| Table 5.1: Breakdown Of Power Consumption By Each Block  | 88 |

|----------------------------------------------------------|----|

| Table 5.2: Comparison with Prior Art on Phase Modulators | 92 |

| Table 5.3: Comparison with Prior Art on Clock Generators | 95 |

# **List of Figures**

| Fig. 1.1: Eve | olution of data rates in wireless communication standards  | 2  |

|---------------|------------------------------------------------------------|----|

| Fig. 1.2: (a) | a polar transmitter, and (b) an outphasing transmitter.    | 3  |

| Figure 2.1:   | Direct VCO modulation requires period frequency re-locking | 7  |

| Figure 2.2:   | Offset PLL                                                 | 7  |

| Figure 2.3:   | Frequency Modulation by Multi-Modulus Divider (MMD) of a   |    |

|               | Fractional-N PLL                                           | 8  |

| Figure 2.4:   | Fractional-N PLL with digital pre-emphasis                 | 8  |

| Figure 2.5:   | Fractional-N PLL with quantization-noise cancellation      | 9  |

| Figure 2.6:   | Two-point modulation                                       | 10 |

| Figure 2.7:   | Block diagram of DCO gain calibration as used in [47]      | 11 |

| Figure 2.8:   | Two-point FM in an all-digital PLL [25]                    | 12 |

| Figure 2.9:   | Conceptual open-loop phase modulator                       | 13 |

| Figure 2.10:  | Frequency divider based open loop phase modulator [1]      | 14 |

| Figure 2.11:  | Phase quantization noise cancellation [2]                  | 15 |

| Figure 2.12:  | Open loop phase modulator with segmented topology using a  |    |

|               | combination of DLL and DCDL [3]                            | 15 |

| Figure 2.13:  | Flying adder architecture for clock generation [48]        | 18 |

| Figure 2.14:  | Multiple digital fractional-N PLL                          | 20 |

| Figure 2.15:  | Open loop clock generation using fractional dividers       | 20 |

| Figure 3.1:   | Digital open loop phase modulation (DPM)                   | 23 |

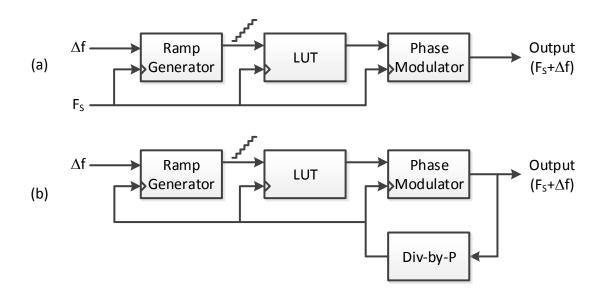

| Figure 3.2:   | Application of DPM in frequency synthesis                  | 24 |

| Figure 3.3:   | Phase generation by a divide-by-2 circuit                  | 25 |

| Figure 3.4:   | Ring oscillator based phase generator                      | 26 |

| Figure 3.5:   | Inverter-delay line based phase generator                  | 27 |

| Figure 3.6:  | DLL based phase generator                                                                            | 28       |

|--------------|------------------------------------------------------------------------------------------------------|----------|

| Figure 3.7:  | Digitally controlled delay line                                                                      | 29       |

| Figure 3.8:  | Phase Interpolation                                                                                  | 30       |

| Figure 3.9:  | Power spectral density of phase quantization noise vs. number of                                     | bits     |

|              | (for 16 QAM modulation, at a data rate of 18 Mbps and switching                                      |          |

|              | frequency of 450 Mbps)                                                                               | 31       |

| Figure 3.10: | Power spectral density of phase quantization noise for digital trur                                  | ncation, |

|              | $1^{st}$ order $\Sigma - \Delta$ , and $2^{nd}$ order $\Sigma - \Delta$ modulated output (for 64 QA) | М        |

|              | modulation, at a data rate of 18 Mbps and switching frequency of                                     | 450      |

|              | Mbps).                                                                                               | 32       |

| Figure 3.11: | ACPR of digital truncation, $1^{st}$ order $\Sigma - \Delta$ , and $2^{nd}$ order $\Sigma - \Delta$  |          |

|              | modulated output                                                                                     | 34       |

| Figure 3.12: | EVM of digital truncation, $1^{st}$ order $\Sigma - \Delta$ , and $2^{nd}$ order $\Sigma - \Delta$   |          |

|              | modulated output                                                                                     | 34       |

| Figure 3.13: | Block diagram of phase quantization noise cancellation [8]                                           | 35       |

| Figure 3.14: | Typical sample and held waveform of PM data                                                          | 36       |

| Figure 3.15: | Minimum rejection due to sinc filtering                                                              | 37       |

| Figure 3.16: | Typical output spectrum after sinc filtering due to zero-order hold                                  | 137      |

| Figure 3.17: | Phase synchronization clock, F <sub>S</sub> for frequency generation derived                         | from:    |

|              | (a) Clean, unmodulated PLL output; or (b) Phase modulated output                                     | ut of    |

|              | phase modulator                                                                                      | 38       |

| Figure 3.18: | Output phase vs input digital code for phase interpolator with inp                                   | ut 90°   |

|              | phase offset between reference phases                                                                | 41       |

| Figure 3.19: | Output distortion due to systematic non-linearity of a phase interp                                  | oolator  |

|              | (simulated output of 18 Mbps GFSK data, switching at 450 Mbps)                                       | ) 41     |

| Figure 3.20: | The simulated PSD of a GFSK modulated signal showing PQN                                                                                                                                                                                                                                                                                                                       |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | cancellation obtained with and without Ts/2 advancement                                                                                                                                                                                                                                                                                                                        |

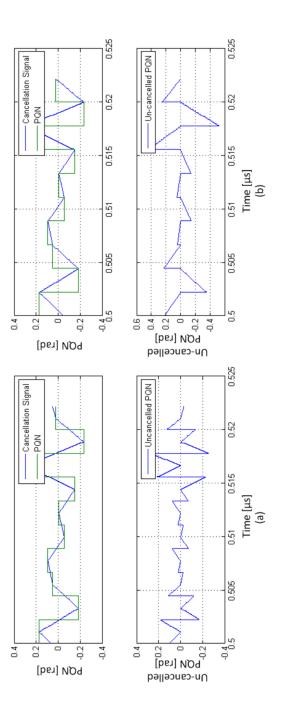

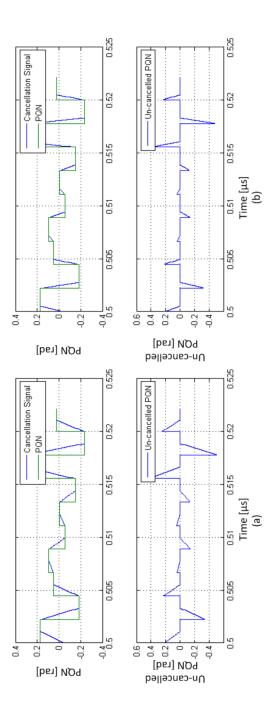

| Figure 3.21: | Timing diagram for PQN cancellation technique for (a) Ts/2                                                                                                                                                                                                                                                                                                                     |

|              | advancement in cancellation signal, and (b) no advancement in                                                                                                                                                                                                                                                                                                                  |

|              | cancellation signal45                                                                                                                                                                                                                                                                                                                                                          |

| Figure 3.22: | Timing diagram for PQN cancellation technique for (a) integration time                                                                                                                                                                                                                                                                                                         |

|              | of Ts/2 and (b) integration time of Ts/4, within each time period46                                                                                                                                                                                                                                                                                                            |

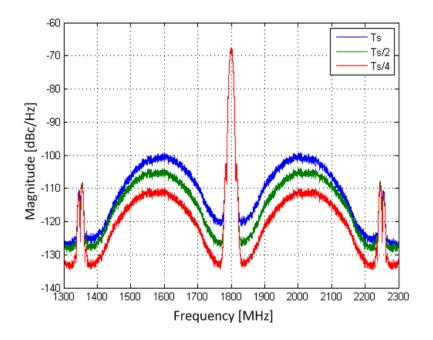

| Figure 3.23: | The simulated PSD of a GFSK modulated signal showing PQN                                                                                                                                                                                                                                                                                                                       |

|              | reduction with decrease in integration time                                                                                                                                                                                                                                                                                                                                    |

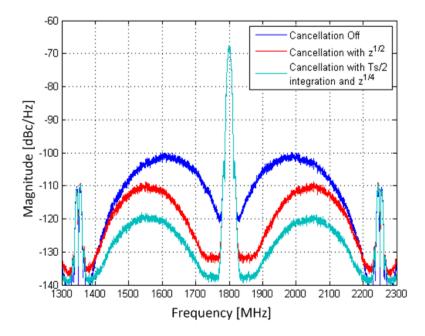

| Figure 3.24: | The simulated PSD of a GFSK modulated signal showing PQN                                                                                                                                                                                                                                                                                                                       |

|              | reduction with optimized cancellation signal advancement and                                                                                                                                                                                                                                                                                                                   |

|              |                                                                                                                                                                                                                                                                                                                                                                                |

|              | integration time                                                                                                                                                                                                                                                                                                                                                               |

| Figure 3.25: | integration time                                                                                                                                                                                                                                                                                                                                                               |

| Figure 3.25: | -                                                                                                                                                                                                                                                                                                                                                                              |

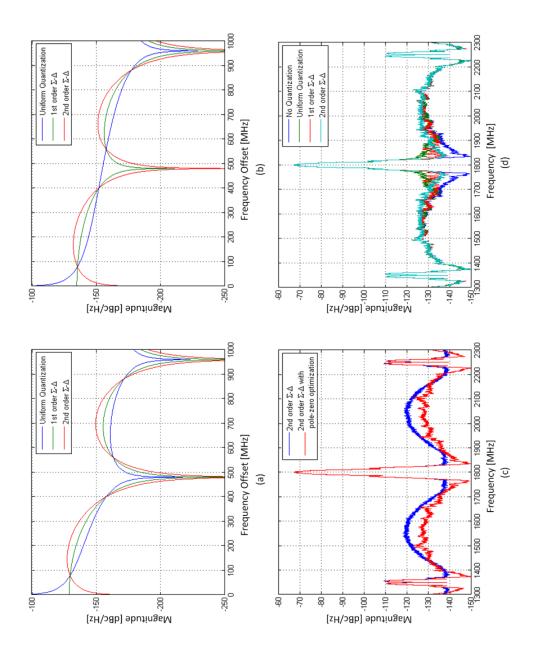

| Figure 3.25: | Plot of analytical expression for output quantization noise due to                                                                                                                                                                                                                                                                                                             |

| Figure 3.25: | Plot of analytical expression for output quantization noise due to quantization in the cancellation path for (a) integration time of Ts, and                                                                                                                                                                                                                                   |

| Figure 3.25: | Plot of analytical expression for output quantization noise due to quantization in the cancellation path for (a) integration time of Ts, and (b) integration time of Ts/2. The simulated PSD of a GFSK modulated                                                                                                                                                               |

| Figure 3.25: | Plot of analytical expression for output quantization noise due to quantization in the cancellation path for (a) integration time of Ts, and (b) integration time of Ts/2. The simulated PSD of a GFSK modulated signal showing (c) PQN reduction with poles in the NTF of phase path,                                                                                         |

|              | Plot of analytical expression for output quantization noise due to<br>quantization in the cancellation path for (a) integration time of Ts, and<br>(b) integration time of Ts/2. The simulated PSD of a GFSK modulated<br>signal showing (c) PQN reduction with poles in the NTF of phase path,<br>and (d) impact of quantization in the cancellation path using three types   |

| Figure 3.26: | Plot of analytical expression for output quantization noise due to quantization in the cancellation path for (a) integration time of Ts, and (b) integration time of Ts/2. The simulated PSD of a GFSK modulated signal showing (c) PQN reduction with poles in the NTF of phase path, and (d) impact of quantization in the cancellation path using three types of quantizers |

| Figure 3.26: | Plot of analytical expression for output quantization noise due to quantization in the cancellation path for (a) integration time of Ts, and (b) integration time of Ts/2. The simulated PSD of a GFSK modulated signal showing (c) PQN reduction with poles in the NTF of phase path, and (d) impact of quantization in the cancellation path using three types of quantizers |

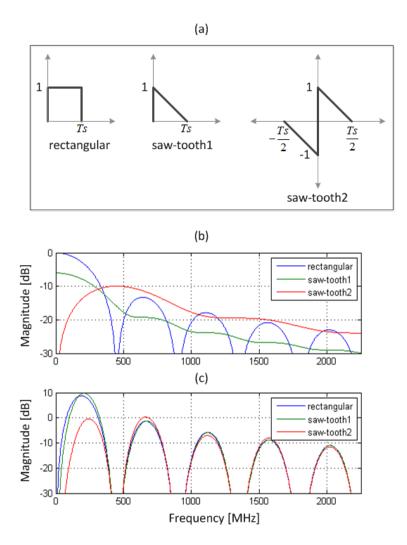

| Figure 3.28: | (a) Pulse shapes for rectangular, saw-tooth1 and saw-tooth2. (b)  | Pulse   |

|--------------|-------------------------------------------------------------------|---------|

|              | shaping function $P1(f)$ for rectangular, saw-tooth and modified  | saw-    |

|              | tooth functions. (c) Calculated transfer function of un-cancelled | PQN for |

|              | the three cases. (Ts = $1/450$ MHz)                               | 56      |

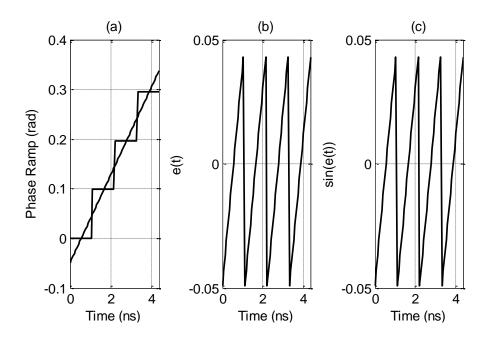

| Figure 3.29: | Timing diagram of error signal in frequency generation: (a) Pha   | se ramp |

|              | and continuous time ideal ramp; (b) Error waveform, e(t); and (c  | )       |

|              | sin(e(t))                                                         | 58      |

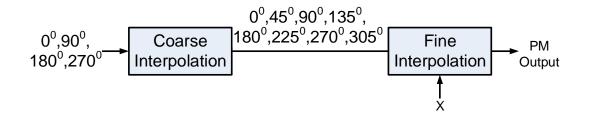

| Figure 4.1:  | Two stage phase interpolation [2]                                 | 62      |

| Figure 4.2:  | LC filtering of LO input [5]                                      | 63      |

| Figure 4.3:  | Estimation of phase errors in [4]                                 | 64      |

| Figure 4.4:  | Conceptual diagram of the proposed technique                      | 65      |

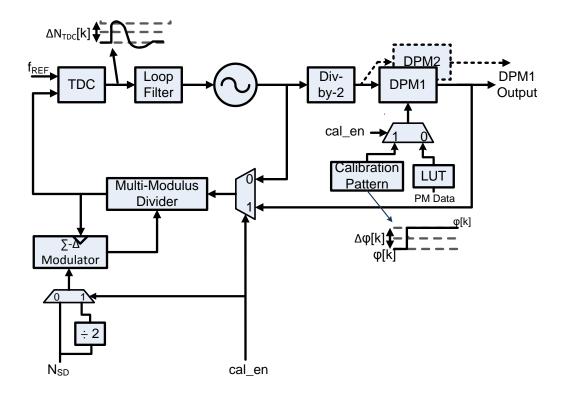

| Figure 4.5:  | Block diagram of DPM calibration                                  | 66      |

| Figure 4.6:  | Timing diagram of DPM calibration                                 | 67      |

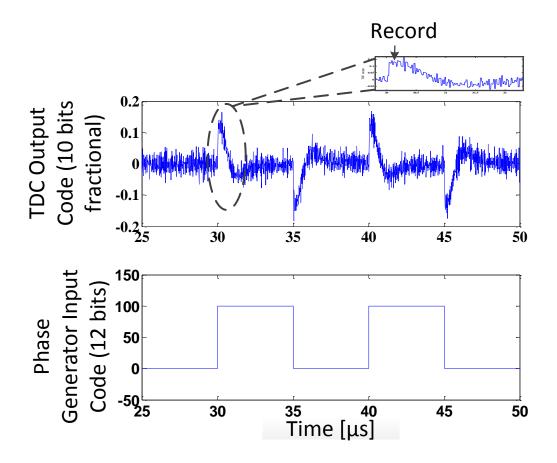

| Figure 4.7:  | Residual noise of phase measurement, terr vs. number of average   | s, L70  |

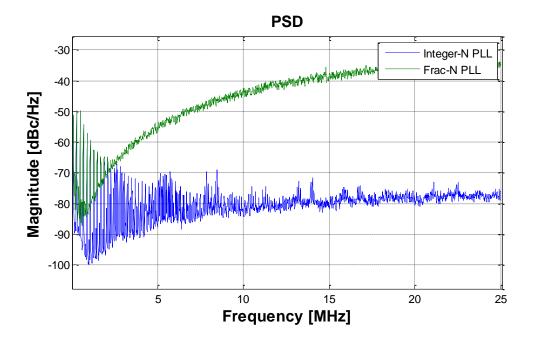

| Figure 4.8:  | Power spectral density of TDC output during calibration in integ  | ger-N   |

|              | mode and fractional-N mode                                        | 71      |

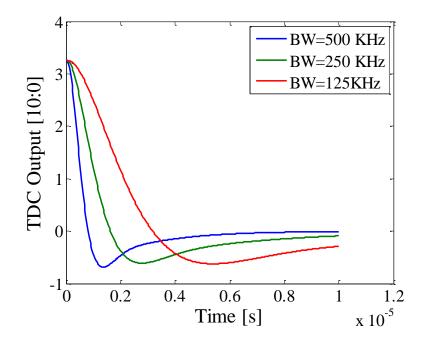

| Figure 4.9:  | Step response from DPM input to TDC output as a function of P     | LL loop |

|              | bandwidth                                                         | 72      |

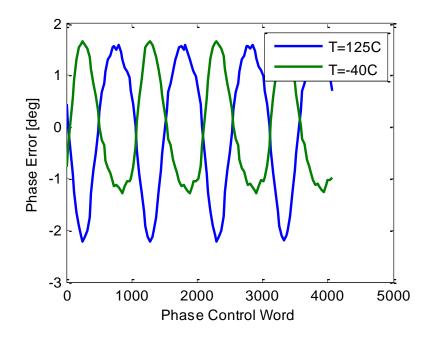

| Figure 4.10: | Simulated phase error at 125C and -40C                            | 73      |

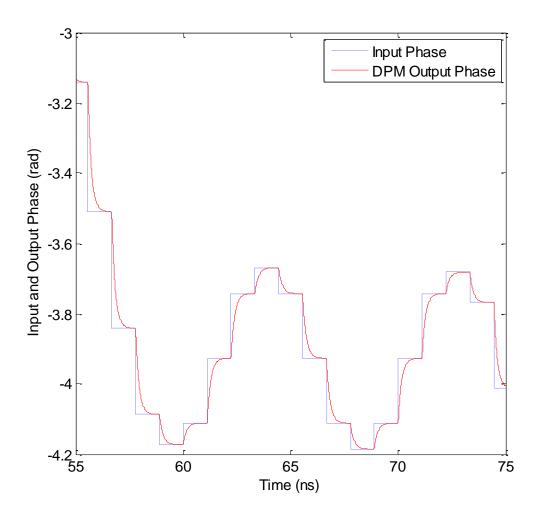

| Figure 4.11: | Behavioral simulation depicting transient phase response of DPM   | 1 outpu |

|              | due to non-ideal phase switching pulse response                   | 76      |

| Figure 5.1:  | Phase generator architecture                                      | 78      |

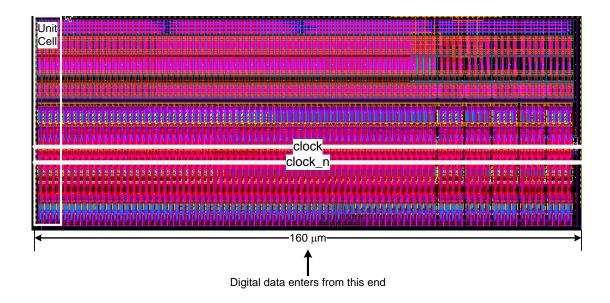

| Figure 5.2:  | Phase generator layout showing arrangement of layout cells and    | digital |

|              | data interface                                                    | 79      |

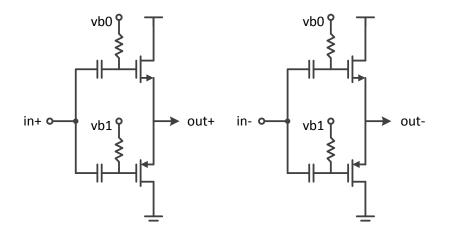

| Figure 5.3:  | Analog complementary MOS voltage buffer                           | 81      |

|              |                                                                   |         |

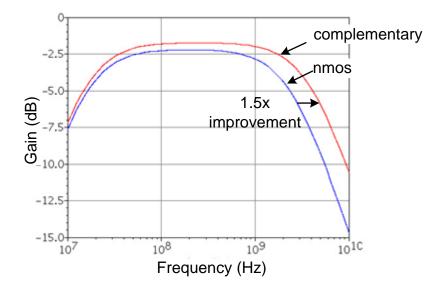

| Figure 5.4:  | Bandwidth comparison of complementary buffer with nmos source    |     |

|--------------|------------------------------------------------------------------|-----|

|              | follower                                                         | 81  |

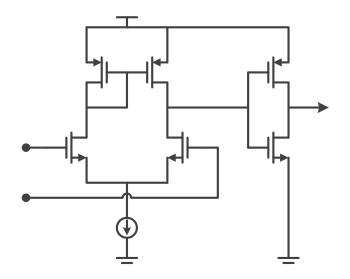

| Figure 5.5:  | CML-to-CMOS circuit                                              | 83  |

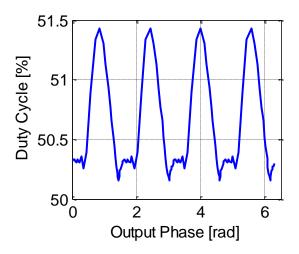

| Figure 5.6:  | Simulated output duty cycle vs output phase                      | 83  |

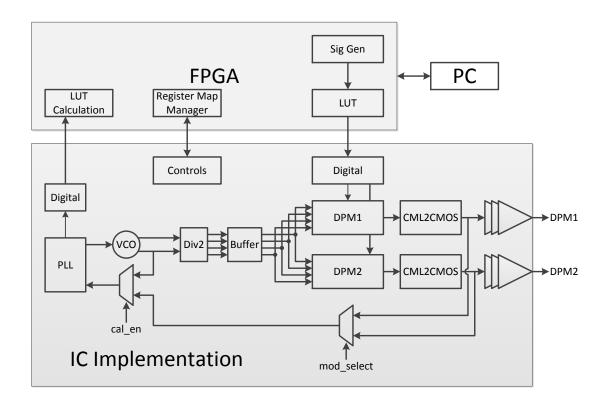

| Figure 5.7:  | System architecture of phase modulator                           | 84  |

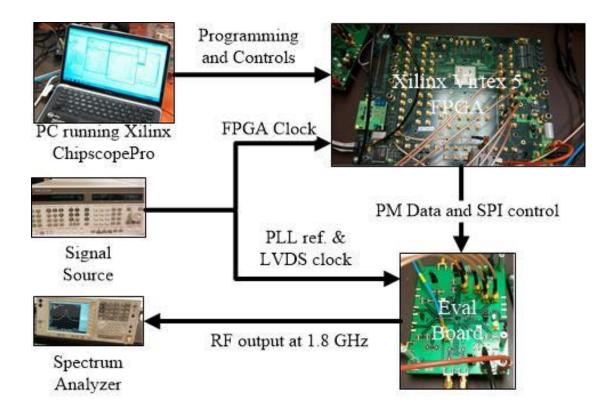

| Figure 5.8:  | Measurement setup                                                | 86  |

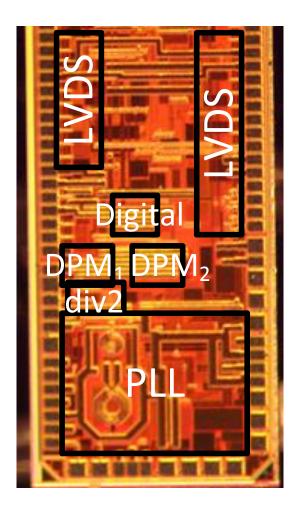

| Figure 5.9:  | Die photo                                                        | 87  |

| Figure 5.10: | Phase LUT                                                        | 89  |

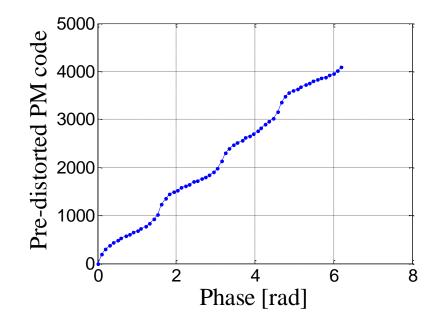

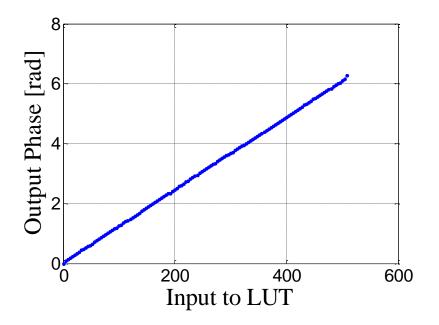

| Figure 5.11: | Output phase vs pre-distorted input                              | 89  |

| Figure 5.12: | Measured output spectrum of 20 Mb/s GFSK data                    | 90  |

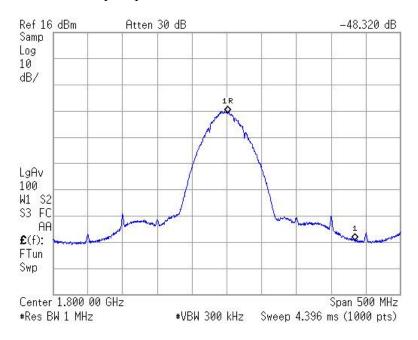

| Figure 5.13: | Measured output spectrum of 100 Mb/s GFSK data                   | 90  |

| Figure 5.14: | Measured transmitted eye-diagram of 20 Mb/s GFSK data            | 91  |

| Figure 5.15: | Measured transmitted eye-diagram of 100 Mb/s GFSK data           | 91  |

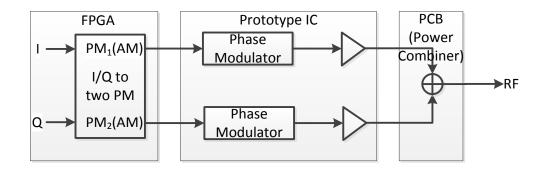

| Figure 5.16: | Measurement setup for output-phasing transmitter                 | 92  |

| Figure 5.17: | Measured output spectrum of 20 Mb/s 16-QAM data                  | 92  |

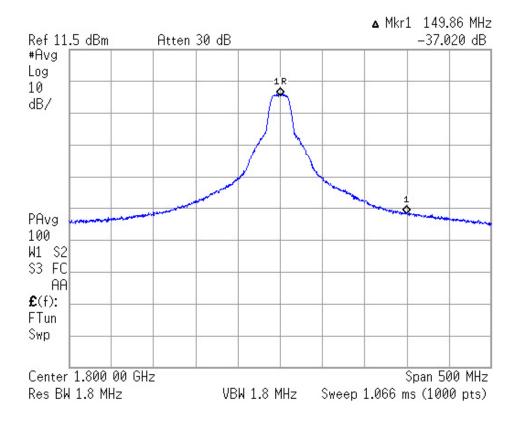

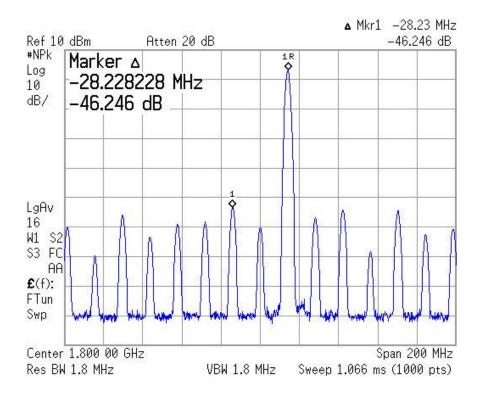

| Figure 5.18: | Measured output spectrum to show frequency synthesis at 1.8141 G | GHz |

|              |                                                                  | 94  |

### **Chapter 1**

### Introduction

### 1.1 MOTIVATION

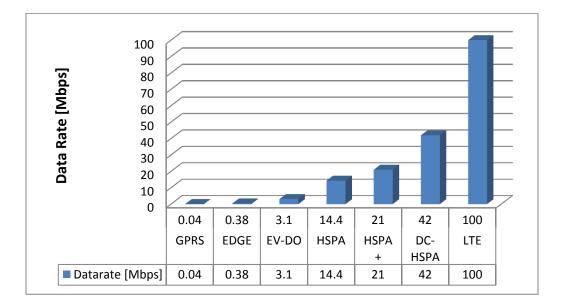

The widespread growth in the communications industry is primarily characterized by rapid increase in data rates and improvements in power efficiency. Fig. 1.1 depicts the evolution of data rates from 40 kbps in the GPRS system to the current maximum rate of 100 Mbps in LTE systems. However, this positive trend demands circuits which process signals which are wider in bandwidth, have a high signal-to-noise ratio and a high peakto-average power ratio. In addition to the growth in data rates, the power efficiency of the modern radio chip, which is immensely versatile in integrating several transceivers on a single die, must also improve. Unfortunately, the design of RF transmitters meeting these specifications in the traditional manner of I—Q up conversion can significantly increase the total power consumption of the RF frontend and therefore, current research is actively looking into high efficiency architectures like polar [16-20] and out-phasing [21,22] for future designs.

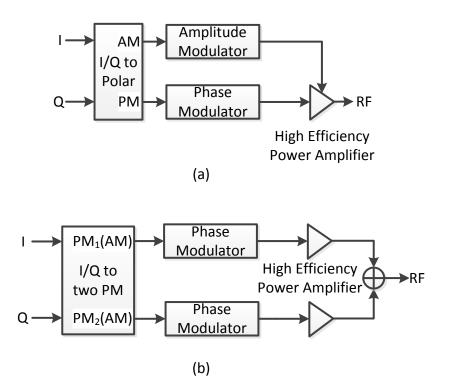

In the polar architecture (Fig. 1.2 (a)), the in-phase and quadrature components are transformed into amplitude and phase components; the out-phasing architecture (Fig. 1.2 (b)) transforms the signal into two phase components. By making these transformations, high efficiency switching power-amplifiers can now be used in the transmitter design, which have a theoretical maximum efficiency of 100%. Furthermore, recent works have demonstrated techniques to maintain this efficiency over large power back-off conditions as well [50]. However, in order to realize these wide-bandwidth and

Fig. 1.1: Evolution of data rates in wireless communication standards

power-efficient transmitter circuitry, a corresponding wide-bandwidth and power efficient phase modulator is required, for both, the polar and the out-phasing topology. Besides this, the bandwidth of the phase modulated signal increases by 6-8 times the bandwidth of the RF signal, further accentuating the wide bandwidth requirement in phase modulator design. In addition to being wideband, the phase modulator must meet the stringent in-band noise and the out-of-band emission requirements.

Traditionally, for narrow bandwidth signals, PLL based architectures like  $\Sigma - \Delta$  modulation of feedback divider [26], digital pre-emphasis [23], quantization noise cancellation [24], and two-point modulation have been used in the past [25,29]. More recently, for wider bandwidth signals, digital open loop modulation has reported the best performance [1—5]. A detailed overview of all the prior-art on phase modulators and their advantages and shortcomings is presented in Chapter 2. It will be shown that that phase errors due to inevitable random mismatches in the device components and

Fig. 1.2: (a) a polar transmitter, and (b) an outphasing transmitter.

systematic errors due to circuit topology, poses a challenging problem for achieving very high resolution phase modulation.

Closely related to phase modulation for digital communication is the challenge of designing low jitter, multiple output clock generation units. Such multiple output clock management unit is required in modern SOCs, which integrate several sub-systems like CPU cores, graphics, power management, high-speed I/O interface, ADC/DACs, modem, etc. The phase modulator which meets the high performance modulation requirements of RF phase modulation applications, is also suitable for low jitter clock synthesis. Furthermore, digital open-loop frequency generation techniques can generate multipleoutputs and have a fast response enabling dynamic frequency scaling. In an attempt to solve the problem of low power, wide-bandwidth and high resolution phase modulation, a digital calibration technique is developed in this dissertation, to tackle performance degradation due to modulator topology and random component mismatches. To demonstrate its usefulness, the designed open loop phase modulator was tested for: (a) phase modulation in a GFSK and an out-phasing transmitter; and (b) low jitter, multiple output clock generation.

#### **1.1 ORGANIZATION**

Chapter 2 of this dissertation is a comprehensive review of all the architectures for achieving wide bandwidth phase modulation.

Chapter 3 of this dissertation is an extensive analysis of the design of an open loop phase modulator. Several key design challenges are identified in this chapter. A noise cancellation scheme for phase quantization noise of phase modulators was introduced in [2]. In this chapter, techniques for optimization of this scheme is discussed, which are supported with extensive simulation results. Additionally, a digital modulator is proposed to reduce the quantization noise in the receive band of the transmitter.

Chapter 4 of this dissertation introduces the proposed digital calibration technique for the estimation and correction of phase errors in a phase modulator. The signal processing details and the performance bounds of the technique are subsequently discussed.

Chapter 5 of this dissertation describes the IC implementation details of the prototype fabricated as a proof-of-concept of the proposed technique. Several circuit techniques for improvements in the wide-bandwidth capability of the circuit are

explained. Afterwards, the measurement results of the prototype IC are discussed and a comparison with the current state-of-the-art is presented in this chapter.

Finally, Chapter 6 concludes this dissertation with a summary of all the improvements achieved in this work.

### Chapter 2

### Wideband Digital Phase Modulation – Prior Art

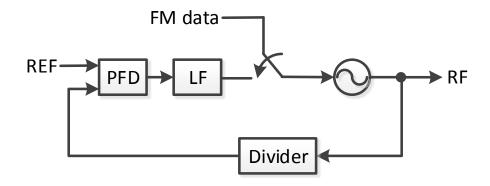

In one of the simplest implementation of phase or frequency modulation, the modulation data is applied to the control voltage of a Voltage Controlled Oscillator (VCO) (Fig. 2.1). Although, this technique is open-loop and wideband, it suffers from frequency drift, VCO transfer function non-linearity and variations over PVT, high closein phase noise and loss of transmission during periods of frequency lock. In order to find a solution for these problems, broadly two categories of phase modulators have emerged

1. Closed loop phase modulators, and

2. Open loop phase modulators

#### 2.1 CLOSED LOOP PHASE MODULATORS

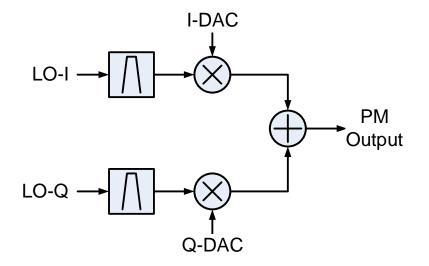

If continuous feedback control is applied to a VCO, to arrive at a conventional PLL, close-in phase noise is improved and carrier frequency is tightly controlled. The phase modulation can, now, be injected from several ports of the PLL loop. In the popular offset-PLL (Fig. 2.2) [39, 40], the phase modulated data was obtained by an I-Q modulator running at a lower frequency and applied to the reference input port of the PLL. This topology can achieve excellent noise performance however modulation bandwidth is severely limited by the loop bandwidth of the PLL.

In other cases, digital modulation data has been successfully applied using a Multi-Modulus feedback Divider (MMD) in a fractional-N PLL (Fig. 2.3) [26, 41] to achieve phase modulation with low phase noise and very good control over the output

Figure 2.1: Direct VCO modulation requires periodic frequency re-locking.

Figure 2.2: Offset PLL

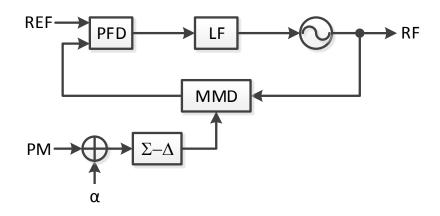

carrier frequency. In this technique, however, the high frequency content of the modulation data is again filtered out by the loop filter of the PLL making it unsuitable for wide-bandwidth phase modulation. Additionally, the digital  $\Delta - \Sigma$  modulator output, which controls the MMD, has high quantization noise and fractional spurs. Both of these sources of noise must be suppressed by the loop filter and therefore, the system bandwidth is further reduced.

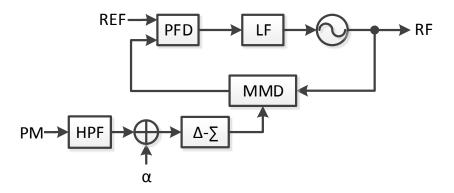

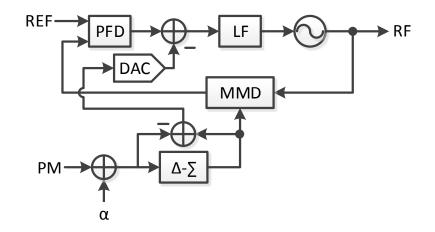

Several bandwidth extension techniques have been proposed for closed loop phase modulators. The digital pre-emphasis as shown in Fig. 2.4 provided some extension beyond the PLL's loop bandwidth, but, it requires precise knowledge of PLL loop dynamics. In the quantization noise cancellation technique [24, 30–32, 42], the  $\Sigma - \Delta$  quantization noise is estimated and cancelled by adding a second port at the input of the loop filter (Fig. 2.5). In [34], quantization noise reduction was achieved by

Figure 2.3: Frequency Modulation by Multi-Modulus Divider (MMD) of a Fractional-N PLL

Figure 2.4: Fractional-N PLL with digital pre-emphasis

Figure 2.5: Fractional-N PLL with quantization-noise cancellation

employing a multi-phase generator for fractional frequency division in the feedback path. LMS based quantization noise cancellation [32], and type-I fractional-N PLL with sharp loop filter to suppress quantization noise [35] are other proposed techniques to extend the bandwidth of phase modulated signals. But, even the best in state-of-the-art designs have not exceeded 3 MHz. Additionally, these techniques can create low-frequency fractional spurs at PLL output which can lower output SNR or violate transmit spectrum mask.

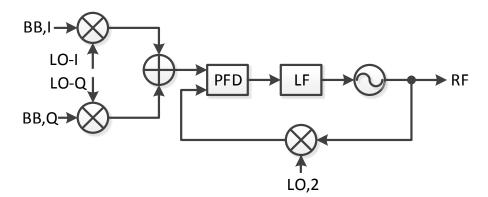

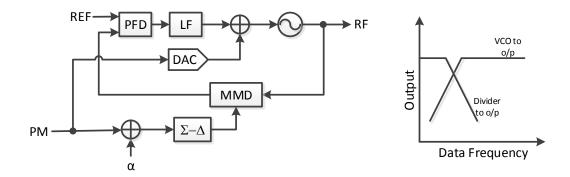

In order to obtain further increase in bandwidth, the so-called two-point modulation has been often used [25, 29, 43-46]. Since the injection of modulation data at any node of the PLL loop is either high pass filtered or low pass filtered, it is injected at two nodes simultaneously such that the sum of the two transfer functions becomes wideband (Fig. 2.6). The most commonly used injection nodes are the MMD and the VCO control voltage to achieve wide bandwidth FM. A common problem encountered in this approach is the loss in SNR due to gain and phase mismatch between the two paths.

Figure 2.6: Two-point modulation

Before injecting the data signal at the VCO control voltage input, it must be attenuated by VCO gain,  $K_{VCO}$  and hence  $K_{VCO}$  must be known a priori in this technique. Since,  $K_{VCO}$  can vary over PVT, an on-chip  $K_{VCO}$  estimation method becomes important. Nonetheless, this technique has been successfully used to generate transmit signals meeting GSM/EDGE and WCDMA requirements.

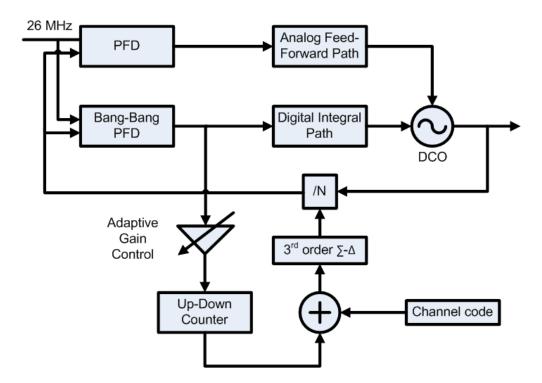

In [36], gain matching was obtained by applying a square wave input to the two modulation input nodes, and the voltage across the resistor, which implements the zero of the loop filter, was monitored. The calibration loop then minimizes the error voltage developed across the resistor. The approach to measure Digitally Controlled Oscillator (DCO) gain and PLL loop gain, in [47], was to measure the phase error in response to a DCO control change. The PLL loop, reduced to type I operation by holding the digital integral path, compensates for the frequency error by adjusting the phase error at phase detector input. The calibration loop then senses the phase error using a bang-bang PFD and modulates the fractional part of the feedback divider until the phase error is reduced to a very small value. Using the new frequency divider value so obtained, the DCO gain

Figure 2.7: Block diagram of DCO gain calibration as used in [47]

can be calculated. For measuring loop gain, a current pulse was injected at the charge pump output and the resultant frequency change was measured using the same method.

The design presented in [43] introduced VCO transfer function linearization technique for two-point modulation for WCDMA. It utilizes a local negative feedback loop around the VCO to obtain a fairly constant  $K_{VCO}$ . This local loop employs an analog technique to measure the VCO frequency, which forms the feedback signal.

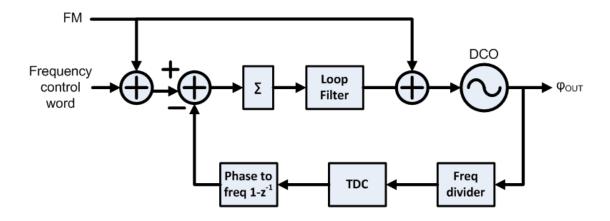

The development of an all-digital PLL (ADPLL) [6, 25, 37-38], has opened up new possibilities for accomplishing phase modulation, as the signals within the PLL loop have become more predictable. Besides this, injection of digital data can be readily achieved in the digital domain, at most of the internal nodes of the PLL. The design presented in [25] took advantage of this feature of a digital PLL and injected the frequency modulation data to the control word of DCO and the carrier frequency control word of the PLL (Fig. 2.8). The second input was described as a compensating signal for the first one, but it can also be viewed as the low frequency path of a two-point modulation.

Figure 2.8: Two-point FM in an all-digital PLL [25]

In [22], a hybrid of many of the techniques mentioned earlier was designed for GSM and WCDMA. The outphasing angle was generated using an 8-bit phase interpolator, while phase modulation was generated by two-point modulation. However, it also used phase-to-digital converters in a negative feedback loop to correct for the non-linearity of phase interpolators, thereby reducing the available bandwidth. Phase modulation techniques at 60 GHz are also being researched. [52] implemented a novel method to obtain phase modulation at 60 GHz by digitally controlling the effective dielectric constant of a differential transmission line. This was achieved by digitally switching in and out a 4-bit bank of floating M6 and M7 strips placed underneath the

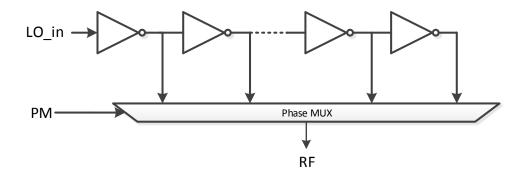

Figure 2.9: Conceptual open-loop phase modulator

transmission line, which leads to a digitally variable phase of S21. However, its dynamic performance under data transmission was not presented.

Although gain and phase calibration techniques have helped to increase the robustness and bandwidth of phase modulators, to the best of the author's knowledge, their application have not been demonstrated on even wider modulation standards such as WLAN, WiMAX and LTE.

### 2.2 **OPEN LOOP PHASE MODULATORS**

The bandwidth limitation and gain and phase mismatch issue associated with twopoint modulation techniques can be avoided by using open-loop modulation techniques, where modulation is performed outside the frequency synthesizer loop. Essentially, it isolates the carrier frequency generation block from the data modulation block, yielding a modulator which does not involve a low-pass filter (the loop filter) in its path. Hence, these modulators can achieve very wide bandwidth.

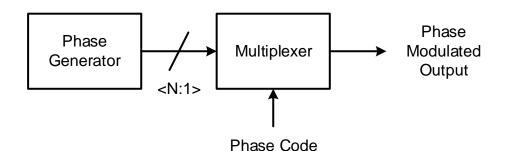

In a typical open-loop phase modulator, a phase generator block produces multiple phases at the carrier frequency. It is followed by a phase multiplexer whose

Figure 2.10: Frequency divider based open loop phase modulator [1]

output is controlled by the phase modulation data (Fig. 2.9). The operation is similar to a digital-to-analog converter, but the analog quantity of interest is the phase of the carrier signal. Due to a digital implementation of the modulator, this technique easily lends itself for quantization noise shaping, digital pre-distortion to compensate for errors due to PVT variation, dynamic element matching and other similar digital techniques.

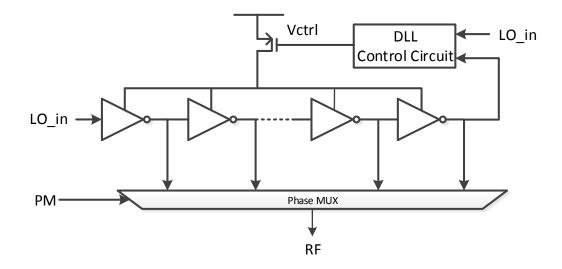

In these modulators, the bank of reference phases are commonly generated by: frequency division [1], delay-locked loops (DLL), digitally controlled delay-line (DCDL) [3,4], and on demand, using phase interpolation [2,5].

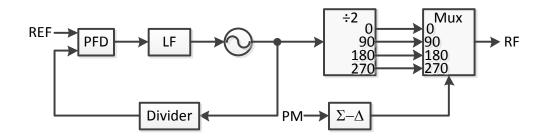

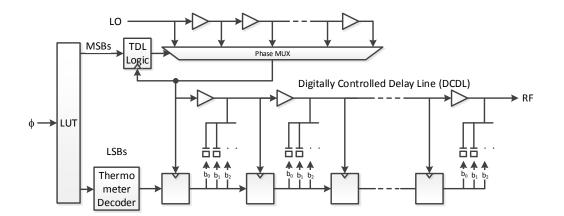

Frequency division [1] results in very few phases at GHz carriers, resulting in high quantization noise (Fig. 2.10). With  $\Sigma - \Delta$  quantization noise shaping, the in-band noise was lowered at the expense of large out-of-band noise (-25 dBr observed from the measured spectrum). The number of discrete phases can be increased by using a large division modulus, but output frequency is reduced by doing so. A segmented topology with CMOS inverter based delay locked loop (DLL), followed by digitally controlled delay lines (DCDL) was used in [3] to realize 9-bit phase modulators (Fig. 2.12). The DCDL suffered from phase errors and the required calibration was performed using

Figure 2.11: Phase quantization noise cancellation [2]

Figure 2.12: Open loop phase modulator with segmented topology using a combination of DLL and DCDL [3]

external equipment. However, the reported power consumption in inverter based phase modulators has remained high, even in an advanced process node. Furthermore, the inverter based phase modulators can be sensitive to supply noise. Phase interpolation offers a low power alternative that eschews the phase multiplexer and generates the desired phase on demand [2,5]. It generates a weighted sum of two reference phases of the carrier. It is fully differential, consumes low power and offers wide bandwidth. The quantization noise of a 6-bit phase interpolator was increased by a quantization noise cancellation technique in [2], where, the quantization noise, which is known *apriori*, is digitally computed and subtracted from the output by adjusting the VCO phase. Even if quantization noise cancellation is not used, excellent phase resolution can be achieved with phase interpolators, if not for systematic and random errors.

Phase interpolators have a non-linear transfer function from the phase control code to output phase. In [2], the non-linearity was reduced by using two stages of interpolation and applying systematic pre-distortion. However, the accuracy of this type of systematic correction worsens in the presence of higher order harmonics of the RF carrier, when the functional form of interpolated phase is not known precisely. In [5], the linearity and the effective resolution were improved by band-pass filtering the phase interpolator inputs. The band-pass filters employ inductors that make it unattractive to applications that need multiple open loop modulators. Furthermore, this approach requires a tunable filter to accommodate changes in carrier frequency and/or redesign of the filter for a change in process node.

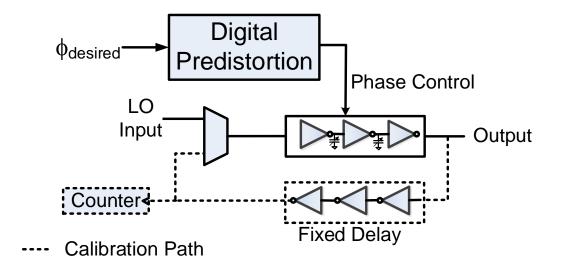

Irrespective of the kind of phase modulator circuit employed (phase interpolator or delay line based), digital calibration is generally essential to achieve high resolution, particularly in the face of random circuit mismatches. For digitally controlled delay lines, [4] had devised a calibration method based on measuring the frequency of a ringoscillator formed with the delay line PM. However, this method is not suitable for phase interpolator based modulators.

In this work, a phase interpolator based open loop phase modulator with a TDC based digital calibration is presented. Systematic non-linearity and random errors caused by mismatches are both estimated and corrected using a look-up table using the proposed calibration technique.

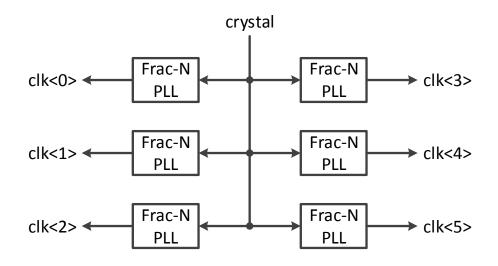

# 2.2.1 Multiple Output Clock Generation

The phase modulator which meets the high performance modulation requirements of RF phase modulation applications, is also suitable for low jitter clock synthesis. Although, several of the phase modulation techniques described earlier can synthesize clocks with low-jitter, they are not capable of generating multiple clock outputs. In particular, all the closed loop PLL techniques and their offshoots for bandwidth extension, including two-point modulation, can only generate a single phase modulated, or clock output. For example, a second clock output from a fractional-N PLL requires a "second" PLL, doubling the total area and power consumption. Besides this, if the design requires an LC oscillator then the magnetic coupling of the two LC tanks further aggravates the design challenges. On the other hand, digital open-loop frequency generation techniques can generate multiple-outputs by only requiring a second digital phase modulator, resulting in power and area savings of several shared circuit blocks, like VCO, PLL, and frequency divider. In addition to this, owing to their open-loop operation,

Figure 2.13: Flying adder architecture for clock generation [48]

they have a fast settling response to changes in output frequency, thereby, enabling dynamic frequency scaling, for power reduction in a digital processor.

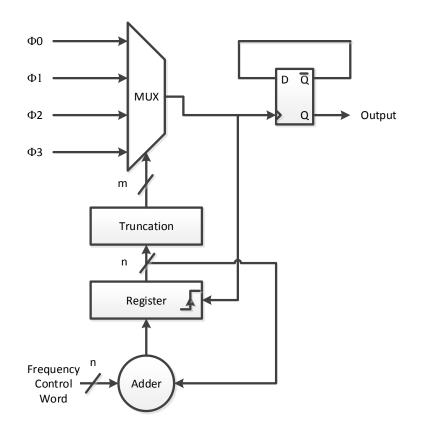

Traditionally, direct-digital synthesizer (DDS) is popular for low frequency clock synthesis; however, they require high resolution DACs for phase-to-amplitude conversion, and high roll-off analog filters, which becomes challenging at RF frequencies. Flying-adder architecture [48] for direct-digital clock synthesis (Fig. 2.13), simplifies the analog design by selecting the desired output phase of a phase generator, but they suffer from strong spurious tones in their output. Recently, several other techniques utilizing advances in PLL techniques and open loop modulation were proposed for application in multiple output clock generators. However, their jitter performance is unacceptable for performance critical applications like high speed I/O, data converters and RF transceiver.

In [10], multiple fractional-N PLLs sharing a common crystal clock input was proposed for multiple clock requirements. Multiple LC-oscillators in each PLL becomes exorbitantly area intensive, therefore, ring oscillators are the only feasible alternative in this approach (Fig. 2.14). However, the clock jitter of such a topology using ring VCOs, and the area requirement for multiple PLLs tends to be high. The VCO noise can be filtered by the PLL loop of a wide-bandwidth PLL, but this comes at the cost of increased TDC quantization noise and increased  $\Sigma - \Delta$  quantization noise of a digital fractional-N PLL.

The phase noise of the digital ring oscillator based PLL was improved by injection locking. In the integer-N mode of injection locking, the output is an integer multiple of the reference clock and the clean edge of the reference is injected to the ring oscillator at an integer multiple. This injection locking technique was extended to fractional ratios in [9], to improve the resolution of achievable frequency steps in a digital PLL. Although, the technique addresses the issues due to high noise of the digital ring oscillator and improves the frequency resolution, the frequency resolution is still limited by the number of stages in the ring oscillator. Increasing the number of phases in the ring

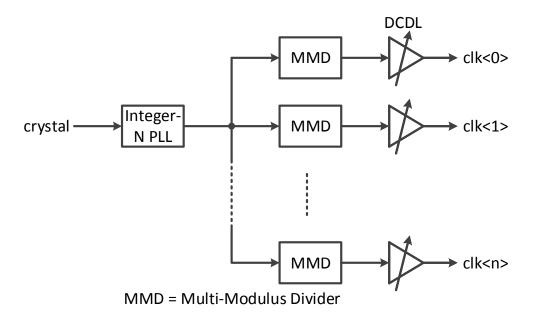

Figure 2.14: Multiple digital fractional-N PLL

Figure 2.15: Open loop clock generation using fractional dividers oscillator to improve the frequency resolution has the drawback of reducing the oscillator frequency. The supply sensitivity of the ring oscillator is also drastically degraded. The order of the frequency control loop was reduced in a delay-locked loop (DLL) simultaneously reducing, both the complexity of the control loop and the response time of the clock generator. Additionally, the drawbacks of the closed-loop topology were removed by using open-loop generation in [11]. The circuit used digitally controlled delay lines (DCDL) driven by a digital modulator to synthesize the output waveform. However, it suffers from the phase errors in the delay line, and the reported power consumption was quite high.

The range of available frequencies was extended by preceding the digitally controlled delay line by a fractional frequency divider in [13] (Fig. 2.15). It, however, did not address the issue of phase errors in the delay line. Furthermore, the inverter based topology is very sensitive to power supply noise.

In conclusion, all the prior-art on clock generation are either not suitable for multiple output generation, or have degraded jitter and/or power performance due to phase errors in the phase modulator. The digital inverter based techniques suffer from high power supply noise sensitivity, as well. In this work, the errors in the phase modulator are compensated, to demonstrate the generation of clean output signal from an RF phase modulator. The open loop topology enables the generation of multiple clock outputs. In addition, the differential topology benefits from improved power supply noise sensitivity.

# Chapter 3

# **Open Loop Phase Modulation**

This chapter presents a formal introduction to open loop phase modulation, followed with a detailed discussion on the design considerations for achieving high resolution. Subsequently, a few optimization techniques for the phase noise cancellation technique [2] are discussed. Finally, an optimization for the digital quantizer is discussed for improving the noise performance in the receive band of the system.

# 3.1 INTRODUCTION

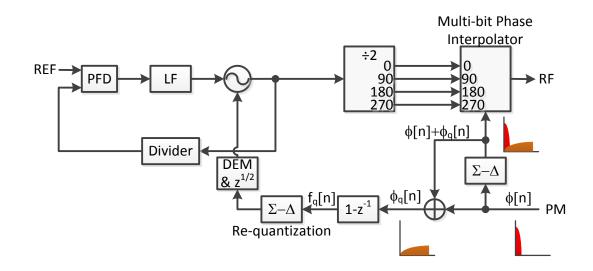

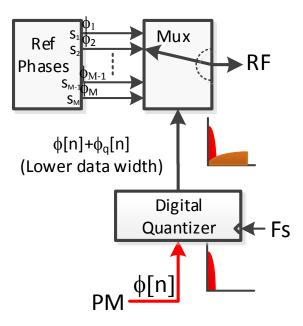

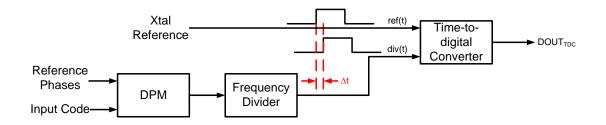

In a typical open loop phase modulator, a phase generator block produces multiple phases at the carrier frequency. It is followed by a phase multiplexer whose output is controlled by the phase modulation data (Fig. 3.1). For a given sequence of desired digital phase values  $\varphi[n]$ , a  $\Sigma - \Delta$  modulator quantizes each phase sample  $\varphi[n]$  to one of the M available phases,  $2\pi \times \frac{k}{M}$ , k = 0, 1, ..., M - 1. The output of the  $\Sigma - \Delta$ modulator controls a digital-to-phase converter, whose inputs are M phase signals,  $s_k = \cos\left(\omega_c + 2\pi \times \frac{k}{M}\right)$ . Note that  $\omega_c$  is the carrier frequency in rad/s. The digital-tophase converter can be a phase multiplexer with M phase inputs or a digital phase interpolator. The resultant synthesized signal can be written as:

$$s_s(t) = \cos\left(\omega_c t + \sum_{n=1}^{\infty} (\phi[n] + \phi_q[n]) \cdot p(t - nT_s)\right)$$

(3.1)

where pulse-shaping function, p(t) is nominally a rectangular pulse of unit amplitude with duration Ts, and  $\phi_q[n]$  is the error in quantizing  $\phi[n]$ . By employing a large number of

Figure 3.1: Digital open loop phase modulation (DPM)

phases, M, and a high switching frequency,  $F_S = 1/T_S$ , desired angle modulation, e.g., PSK, GMSK etc. can be realized with good EVM and ACPR.

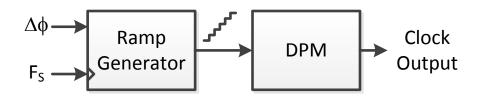

Alternatively, if  $\phi[n]$  were a ramp, i.e.  $\phi[n] = \Delta \phi . n$ , as shown in Fig. 3.2, a periodic signal with frequency:

$$F_{OUT} = F_C - \frac{F_S \cdot \Delta \phi}{2\pi} \tag{3.2}$$

is synthesized; i.e., frequency synthesis is possible by choosing an appropriate  $\Delta\phi$ . The frequency resolution may seem to be limited by the smallest phase step,  $\Delta\phi$ , that can be achieved. However, arbitrarily fine frequency synthesis can be achieved by employing a  $\Sigma-\Delta$  modulator ("Digital Quantizer" in Fig. 3.1) to quantize the phase ramp. Note also

Figure 3.2: Application of DPM in frequency synthesis

that the range of frequency which can be synthesized by this method is bounded by  $\pm F_s/2$  around  $F_c$  [28] but can be extended further by employing frequency dividers after the multiplexer.

Note that the clock source for phase switching,  $F_S$  can be derived synchronously either from the reference phase input to PM,  $F_C$  or from the DPM's RF output,  $F_{OUT}$ , with significant implications on output frequency, quantization noise, spectral purity and ease of implementation. These are discussed in section 3.2.4 in more detail.

# 3.2 DESIGN CONSIDERATIONS IN DIGITAL PHASE MODULATION

The design of an open loop phase modulator must address the following challenges for achieving high resolution:

- 1. Generation of discrete phases

- 2. Phase quantization noise

- 3. Spectral images due to digital switching

- 4. Synchronization of phase switching

- 5. Phase errors in the phase generator

A detailed discussion of each of the above challenges is presented in the following subsections.

# 3.2.1 Generation of Discrete Phases

The bank of discrete phases are commonly generated by:

- 1. Frequency division [1],

- 2. Ring oscillators,

- 3. Delay-locked loops [3]

- 4. Digitally controlled delay-line (DCDL) [3,4]

- 5. Phase interpolation [2,5]

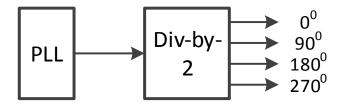

The simplest method for generating discrete phases is by using a frequency divide-by-2 circuit [1]. A divide-by-2 circuit readily generates the quadrature phases at a lower frequency. This commonly used circuit block can achieve very high frequencies. However, it only generates four discrete phases. For many applications, the quantization noise of the four phases overwhelms the circuit performance. Quantization noise shaping was used in [1]. With  $\Sigma - \Delta$  quantization noise shaping, the in-band noise was lowered at the expense of large out-of-band noise (-25 dBr observed from the measured spectrum). In [1], while transmitting at 403.2 MHz, the measured FSK errors at 6 Mb/s data rate was

Figure 3.3: Phase generation by a divide-by-2 circuit

Figure 3.4: Ring oscillator based phase generator

4.1 % and 11.6 % for 2-FSK and GFSK modulations, respectively.

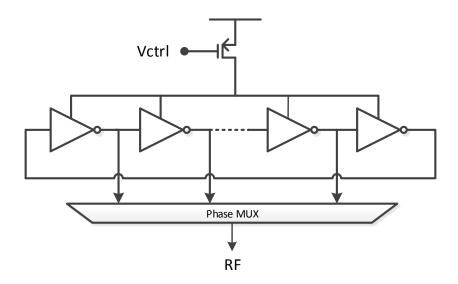

The number of discrete phases can be moderately increased by using a ring oscillator. The available number of phases increases as the number of inverter stages are increased, although, at the expense of reducing the oscillator speed. The trade-off between oscillator speed,  $f_{osc}$ , number of available phases, N and process-dependent inverter delay,  $t_{inv}$  is expressed by:

$$f_{osc} = \frac{1}{2 \times N \times t_{inv}} \tag{3.3}$$

Ring oscillators also suffer from high phase noise of the oscillator. The approach is, still, useful for low frequency, low resolution applications, like generation of clocks for digital circuits. Ring oscillators with LC stages are also possible for an improvement in phase noise, although their design will be highly constrained by the area requirement of an inductor. Phase noise in the reference phases can be moderately improved by using a low phase noise oscillator for generating a reference phase and using it to drive a chain of inverters for generating the discrete phases as shown in Fig. 3.5. The discrete phases are inverter delay apart and varies with process, voltage and temperature. In this implementation, if a phase range of  $360^{\circ}$  is required, this variation results in large errors at the  $360^{\circ}$  to  $0^{\circ}$  phase transition.

The static delay variation is improved by controlling the inverter delay chain inside a delay-locked loop (Fig. 3.6). The delay-locked loop forces the total variation across the inverter chain to equal once clock cycle of the reference phases. The issues due to inverter delay variation are fixed by this approach, although at the expense of additional control circuitry for adjusting inverter delays. The phase resolution is, however, still limited by an inverter gate delay.

Figure 3.5: Inverter-delay line based phase generator

Figure 3.6: DLL based phase generator

In [3], the number of available discrete phases was further increased by adding a bank of digitally controlled capacitors for generating fine steps in the phase generator (Fig. 3.7). The capacitor bank enables very fine inverter gate delay control, which is, usually, about 10x better than one inverter delay. The phase modulator in [3] had 9 bit resolution for phase control. The digital logic was simplified by splitting the inverter delays between a coarse delay stage and a fine delay stage. It should be noted that such splitting of phase control results in added complexity due to the gain and timing mismatch between the two stages.

Irrespective of improvements in resolution, all of the inverter based phase generator have high sensitivity to supply noise, necessitating the use of a supply regulator in high resolution applications. The supply noise added by the inverter stages can be reduced by using differential stages at all levels. Although, not as good as a differential analog circuit, differential inverting stages contribute lower power supply noise than a corresponding single ended stage. Additionally, the impact of power supply noise on the output phase of an inverter delay depends on the slew rate of the signal:

$$\Delta t_n = \frac{v_n(t)}{SR} \tag{3.4}$$

where  $v_n(t)$  is power supply noise, SR is slew rate of inverter output, and  $\Delta t_n$  is the timing noise added to inverter output. Clearly, a high slew rate is desirable to combat the impact of power supply noise in inverter based phase generators.

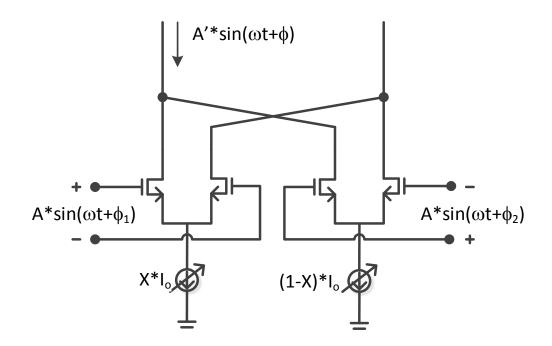

Phase interpolation offers a low power alternative that eschews the phase multiplexer and generates the desired phase on demand [2,5]. Fig. 3.8 shows a conceptual interpolation circuit. It generates a weighted sum of two reference phases of the carrier. It is fully differential, consumes low power and offers wide bandwidth. Excellent phase resolution can be achieved if not for systematic and random errors.

Figure 3.7: Digitally controlled delay line

Figure 3.8: Phase Interpolation

For example, for sinusoidal inputs, phase interpolation of two reference phases at  $\phi_1$ and  $\phi_2$  results in an output signal with phase,  $\phi$  given by:

$$\phi = \sin^{-1} \left( \frac{X \cdot \sin(\phi_1) + (1 - X) \cdot \sin(\phi_2)}{X \cdot \cos(\phi_1) + (1 - X) \cdot \cos(\phi_2)} \right)$$

(3.5)

where X and (1-X) are the weights applied to the interpolating phases. For  $\phi_1 = 90^0$  and  $\phi_2 = 0^0$ , Eq. 3.5, reduces to:

$$\phi = \tan^{-1}\left(\frac{X}{1-X}\right) \tag{3.6}$$

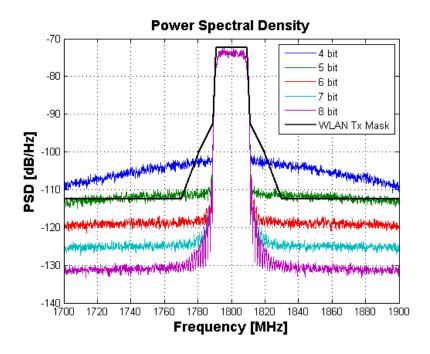

Figure 3.9: Power spectral density of phase quantization noise vs. number of bits (for 16 QAM modulation, at a data rate of 18 Mbps and switching frequency of 450 Mbps).

#### **3.2.2** Phase Quantization Noise

Phase quantization noise (PQN) can be contrasted with the quantization noise added by baseband DACs in an I—Q architecture. In the latter, out-of-band quantization noise and spectral images of baseband DACs can be removed by baseband low pass filters, although the total power consumption also gets increased. Furthermore, the noise generated by the low pass filters adds on top of the contributions from the mixer and amplifiers in the transmit chain. Such a filter in a digital phase modulator will have to be RF band pass, requiring high Q passive components or a SAW filter. Such a filter is both area and power hungry, therefore, other circuit and system techniques are desired to reduce phase quantization noise.

Figure 3.10: Power spectral density of phase quantization noise for digital truncation,  $1^{st}$  order  $\Sigma - \Delta$ , and  $2^{nd}$  order  $\Sigma - \Delta$  modulated output (for 64 QAM modulation, at a data rate of 18 Mbps and switching frequency of 450 Mbps).

## 3.2.2.1 Power Spectral Density of Phase Quantization Noise

Similar to a voltage DAC, the output spectrum of phase quantization noise improves by 6 dB per bit increase in phase resolution. The simulated phase quantization noise when transmitting 18 Mbps, 64 QAM modulation and switching at 450 MHz, is plotted in Fig. 3.9.

# 3.2.2.2 Phase Quantization Noise Shaping

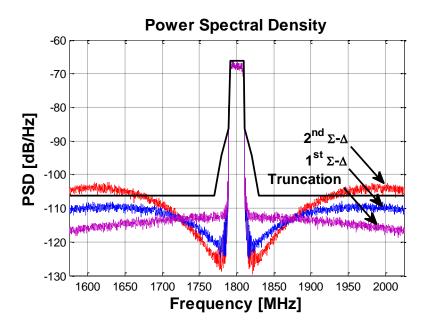

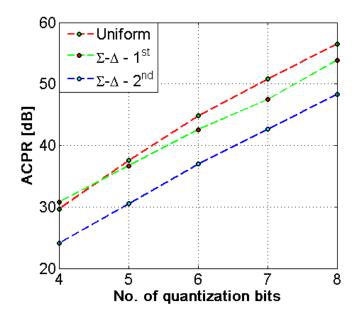

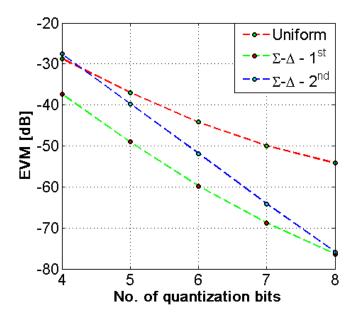

The shape of phase quantization can be shaped to meet the requirements on spectral mask, while requiring minimal level of quantization. For example, a 1<sup>st</sup> order  $\Sigma - \Delta$  modulated quantization has low in-band noise, while the noise at high-offset

frequencies are elevated. As the order of noise shaping is increased, the noise at highoffset frequencies increases rapidly (Fig. 3.10). The trade-offs become evident as we look at the ACPR and EVM plots for the simple truncation,  $1^{st}$  order  $\Sigma - \Delta$  and  $2^{nd}$  order  $\Sigma - \Delta$ modulated outputs. For low quantization level,  $1^{st}$  order  $\Sigma - \Delta$  results in better EVM than digital truncation without much impact on ACPR. Also, in the  $2^{nd}$  order  $\Sigma - \Delta$  modulator, the quantization noise can fold in-band, when the level of noise is relatively high, as seen in a 4-bit phase modulator.

#### 3.2.2.3 Phase Quantization Noise Cancellation

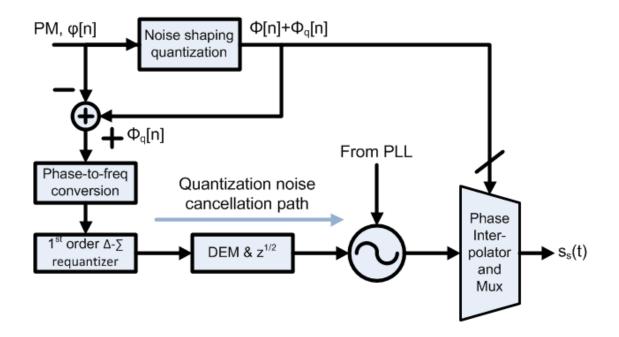

A quantization noise cancellation path can be added to the modulator output, through a second VCO control port as shown in Fig. 3.13 [2]. The required cancellation signal is obtained by first subtracting the input signal,  $\phi[n]$  from the quantized signal,  $\phi[n] + \phi_q[n]$ . Thus, the quantized phase data  $\phi[n] + \phi_q[n]$  is applied through the digital-to-phase converter, while the PQN cancellation signal of  $-\phi_q[n]$  is applied through a cancellation path through the VCO.

Frequency of the VCO output can be controlled in a straightforward manner through an analog control signal, or through a digital word in the case of a Digitally Controlled Oscillator. Its phase, on the other hand, is the outcome of an integration of the resultant frequency. Since the cancellation signal is a phase quantity, while the VCO input port controls its frequency, the required cancellation phase is differentiated,  $(1 - z^{-1})$  to obtain an equivalent VCO frequency deviation. It must also be attenuated by VCO's control voltage-to-frequency gain, K<sub>VCO</sub>.

Figure 3.11: ACPR of digital truncation,  $1^{st}$  order  $\Sigma - \Delta$ , and  $2^{nd}$  order  $\Sigma - \Delta$  modulated output

Figure 3.12: EVM of digital truncation,  $1^{st}$  order  $\Sigma - \Delta$ , and  $2^{nd}$  order  $\Sigma - \Delta$  modulated output

Figure 3.13: Block diagram of phase quantization noise cancellation [8]

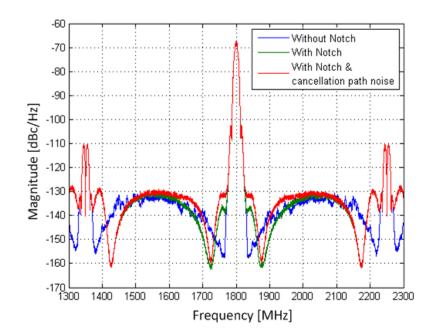

In [2], a state-of-the-art implementation of PQN cancellation was presented on a 2.4 GHz wide-bandwidth open-loop GFSK transmitter IC. The phase cancellation path was implemented by adding a second VCO port to control a 4-bit capacitor bank, with DEM logic incorporated in the selection process. In [2], 9 dB improvement was the measured while transmitting 20 Mb/s GFSK modulation output spectrum, after enabling the phase noise cancellation technique.

# 3.2.3 Spectral Images

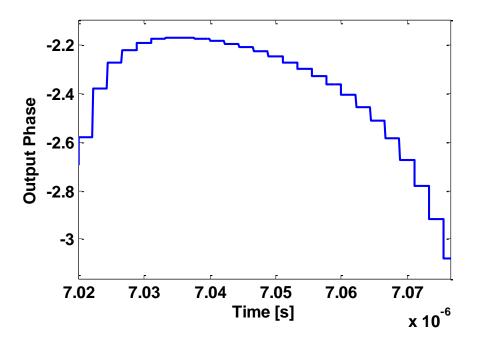

Due to the digital implementation of the phase modulator, the digital data is held constant for one clock cycle of the switching clock (Fig. 3.14). This zero-order hold imparts a square pulse shape, as the phase modulation data transitions from the digital to

Figure 3.14: Typical sample and held waveform of PM data

the analog domain. In the frequency domain, this operation is equivalent to convolution of the spectrum of the digital data with that of the square pulse.

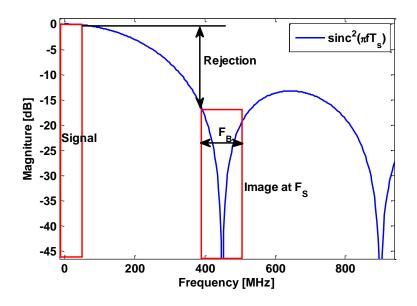

In the analog domain, spectral images are created at multiples of the switching frequency. Additionally due to the zero order hold, the input signal, quantization noise and spectral images are filtered by a sinc-shaped filter resulting from the convolution with the square pulse shape. The level of spectral images after the sinc filtering can be expressed as:

$$Min. Rejection = 10 \times \log_{10} \left( sinc^2 \left( \pi \times \left( 1 - \frac{F_B}{2F_S} \right) \right) \right)$$

(3.7)

where F<sub>B</sub> is the bandwidth of the input signal, Fs is the switching frequency, and rejection is the minimum difference in levels between the input signal and spectral images as

Figure 3.15: Minimum rejection due to sinc filtering

Figure 3.16: Typical output spectrum after sinc filtering due to zero-order hold

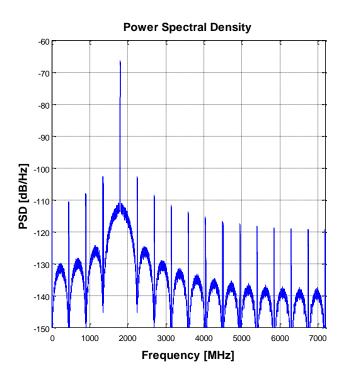

shown in Fig. 3.15. As the ratio  $(F_B/F_S)$  is reduced by increasing  $F_S$ , the rejection also improves. As  $F_S$  is increased, the spectral images are also pushed farther away from the RF output, making image filtering by a passive filter easier. The spectral images after sinc filtering in a typical output of the phase modulator is depicted in Fig. 3.16.

#### 3.2.4 Synchronization of Phase Switching

As mentioned before, the phase switching clock,  $F_S$  (see Fig. 3.1) can be derived from: (a) the clean, unmodulated PLL output, or (b) the phase modulated RF output. In this work, the former approach was employed. This simplifies the digital interface between the DSP generating the phase modulation data and the phase modulator itself, as both can run from a single clock domain. In contrast, the latter approach could have degraded EVM and ACPR performance because the phases would have been switched

Figure 3.17: Phase synchronization clock, F<sub>S</sub> for frequency generation derived from:(a) Clean, unmodulated PLL output; or (b) Phase modulated output of phase modulator

non-uniformly owing to the use of a phase modulated clock.

It is important to note that our choice comes with certain disadvantages particularly when performing frequency synthesis (Fig. 3.17). In this case,  $F_{out}$  may not be harmonically related to F<sub>s</sub>, the rate of phase jumps. So, strong fractional spurs will result. For example, for a desired output at  $F_{out} = F_C + \Delta f$ , there would be a very strong spur at  $F_C - \Delta f$ . The magnitude of this spur is computed in Appendix 3.5.2 and its magnitude for  $\Delta \phi \ll 2\pi$ , is approximated by:

$$P_{fund} - P_{imag} = 20 \times \log_{10}(\frac{\Delta\phi}{2k\pi})$$

(3.8)

where  $k = 2F_C/F_S$ ,  $F_C$ ,  $P_{fund}$  and  $P_{imag}$  are strengths of the RF carrier, fundamental output and image tone, respectively. Additionally, the harmonics of the fundamental carrier also cause spurs at close-in frequencies. For example, the third harmonic of the RF carrier causes a spur at  $F_C \pm 3\Delta f$ . The magnitude of this spur is computed in Appendix 3.5.3 and its magnitude is given by:

$$P_{fund} - P_{3x} = 20 \times \log_{10} \left( \alpha_3 sinc \left( k \pm \frac{3\Delta\omega}{2\pi F_S} \right) \right)$$

(3.9)

where  $P_{3x}$  is the strength of the tone at  $F_C \pm 3\Delta f$  and  $\alpha_3$  is the magnitude of third harmonic of RF carrier relative to fundamental.

In contrast, if  $F_S$  were derived from  $F_{out}$  (e.g., is a subharmonic of  $F_{out}$ ) these fractional spurs would be theoretically absent. The reader is referred to an excellent analysis of so-called "flying adders" that employ such a synchronization strategy [14-15].

#### 3.2.5 Phase Errors in the Phase Generator

The primary sources of static phase errors in the phase generator can be classified

into:

- 1. Systematic errors

- 2. Random errors

- 3. Dynamic errors

We discuss each of these errors in detail in the following sub-sections.

#### 3.2.5.1 Systematic Errors

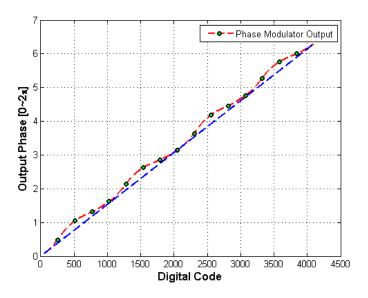

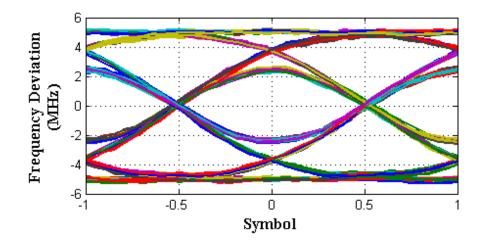

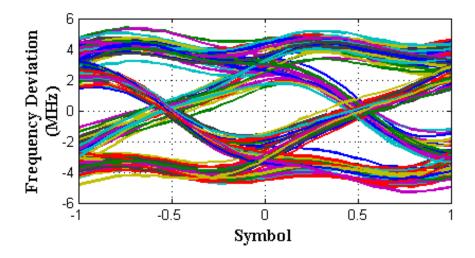

Systematic sources of phase errors include circuit non-linearity and phase errors due to higher harmonics in the reference phase input. In a phase interpolator based phase generator (see section 3.2.1), the expression for output phase (Eq. 3.5) is sinusoidal and therefore output will have strong spurs, if this sinusoidal non-linearity is not compensated. For a phase interpolator with two reference phases that are  $90^{0}$  apart, the output phase vs input control code is plotted in Fig. 3.18. The distortion caused due to systematic errors is evident from elevated levels of out-of-band noise in Fig. 3.19. This error is one of the most dominant source of performance limitation for achieving high resolution and techniques to improve systematic linearity will be discussed in greater detail in Chapter 3.

# 3.2.5.2 Random Errors

Aside from the systematic errors, the inevitable component mismatches due to component fabrication is another source of phase errors in a phase modulator. They are un-avoidable in any architecture. The device mismatch (both threshold and beta) is

Figure 3.18: Output phase vs input digital code for phase interpolator with input 90° phase offset between reference phases

Figure 3.19: Output distortion due to systematic non-linearity of a phase interpolator (simulated output of 18 Mbps GFSK data, switching at 450 Mbps)

proportional to device area and the standard deviation of the mismatch coefficient can be expressed as:

$$\sigma = \frac{A}{\sqrt{W \times L}} \tag{3.10}$$

where A is a constant, W and L are the width and length of the transistor, respectively. Additionally, the current mismatch is also dependent on the overdrive voltage, and it becomes worse as the overdrive voltage is lowered. Therefore, at constant bandwidth, both the area and the power consumption of the transistor must be increased. This leads to a proportional increase in power consumption of the driving stages as well.

# 3.2.5.2 Dynamic Errors

Dynamic errors include errors due to incomplete settling, code dependent settling time of the phase modulator, and supply noise due to digital activity. Supply noise can be reduced by ensuring differential signals for most of the circuits connected to the same supply as that of the phase modulator. For a well-designed, high bandwidth phase modulator, issues due to incomplete settling can be minimized. However, these sources become the dominant source of error once the random and systematic sources are compensated. In this work, dynamic errors were avoided by careful circuit and layout design and it is surmised, that system solutions for tackling dynamic errors can further improve the performance of the phase modulator.

# 3.3 QUANTIZATION NOISE CANCELLATION: OPTIMIZATION TECHNIQUES