# UC Berkeley UC Berkeley Electronic Theses and Dissertations

### Title

Human-Centered Circuit Board Design With Flexible Levels of Abstraction and Ambiguity

**Permalink** https://escholarship.org/uc/item/1xr238zt

#### Author Lin, Richard

Publication Date 2021

Peer reviewed|Thesis/dissertation

Human-Centered Circuit Board Design With Flexible Levels of Abstraction and Ambiguity

by

Richard Cheng Lin

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

$\mathrm{in}$

Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Björn Hartmann, Co-chair Professor Elad Alon, Co-chair Professor Kimiko Ryokai

Fall 2021

Human-Centered Circuit Board Design With Flexible Levels of Abstraction and Ambiguity

Copyright 2021 by Richard Cheng Lin

#### Abstract

Human-Centered Circuit Board Design With Flexible Levels of Abstraction and Ambiguity

by

Richard Cheng Lin

Doctor of Philosophy in Computer Science

University of California, Berkeley

Professor Björn Hartmann, Co-chair

Professor Elad Alon, Co-chair

Printed Circuit Board (PCB) design tools are critical in enabling users to build non-trivial electronics devices. However, mainstream tools work at the lowest level of design — schematics and individual components — which can make design difficult for beginners and tedious for experts.

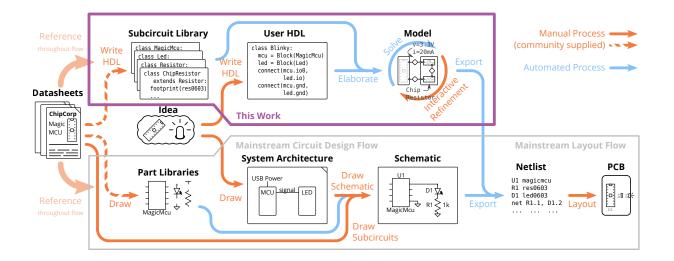

In this work, we start by examining current board design practices to learn how a variety of users approach the process, what tools they use, what works well, and where things are lacking. From those results, we focus on building tools to support the system architecture level of design — a representation that we believe captures the most important design decisions without getting mired in the details.

Taking inspiration from software engineering and chip design languages, we implement a hardware construction language (HCL) that supports users at multiple levels of abstraction (from system to subcircuits), enables mixed-ambiguity design through abstract components (such as a generic resistor instead of a particular part number), and encodes the methodology for subcircuit design instead of static instances (for example, automatically sizing a resistor in a LED circuit). To support users working with this very different interface to board design, we also build an integrated development environment (IDE) plugin that adds a linked graphical view and editor to the standard textual code editor.

Small but in-depth user studies on these tools indicate that this approach can provide benefits over mainstream flows, but also suggests avenues for continued work.

i

# Contents

| Co  | onten                                          | nts                                                                                                                                                                        | ii                                            |

|-----|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Lis | st of                                          | Figures                                                                                                                                                                    | iv                                            |

| Lis | st of                                          | Tables                                                                                                                                                                     | vi                                            |

| 1   | <b>Intr</b><br>1.1<br>1.2<br>1.3<br>1.4        | oduction         Overview and Thesis         Contributions         Roadmap         Statement of Prior Publication                                                          | <b>1</b><br>1<br>2<br>3<br>3                  |

| 2   | Bac<br>2.1<br>2.2<br>2.3<br>2.4                | kgroundSchematic CaptureLayout and AssemblyHistorical ContextCreativity Support Tools                                                                                      | <b>5</b><br>5<br>7<br>7<br>10                 |

| 3   | <b>Rela</b><br>3.1<br>3.2<br>3.3<br>3.4<br>3.5 | ated Work         Empirical Studies         Electronics Design         Electronics Prototyping and Beyond         Hardware Description Languages         Programming Tools | <b>11</b><br>11<br>14<br>15<br>16             |

| 4   | Form<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6 | mative Studies         Introduction                                                                                                                                        | <b>18</b><br>18<br>19<br>20<br>20<br>25<br>28 |

|          | $4.7 \\ 4.8 \\ 4.9$ | Mockup Study: Findings         | 30<br>33<br>34 |

|----------|---------------------|--------------------------------|----------------|

| <b>5</b> | Har                 | dware Description Language     | 36             |

|          | 5.1                 | Introduction                   | 36             |

|          | 5.2                 | System Design                  | 38             |

|          | 5.3                 | System Implementation          | 46             |

|          | 5.4                 | Example Applications           | 47             |

|          | 5.5                 | User Study: Methodology        | 48             |

|          | 5.6                 | User Study: Results            | 50             |

|          | 5.7                 | Limitations and Future Work    | 54             |

| 6        | Inte                | grated Development Environment | 57             |

|          | 6.1                 | Introduction                   | 57             |

|          | 6.2                 | System Description             | 59             |

|          | 6.3                 | System Implementation          | 65             |

|          | 6.4                 | User Study: Methodology        | 67             |

|          | 6.5                 | User Study: Results            | 69             |

|          | 6.6                 | Discussion                     | 71             |

| 7        | Con                 | clusion                        | 74             |

|          | 7.1                 | Summary of Contributions       | . – 74         |

|          | 7.2                 | Future Work                    | 75             |

|          | 7.3                 | Conclusion                     | 78             |

| 8        | Glos                | ssary                          | 79             |

| Bi       | bliog               | raphy                          | 81             |

# List of Figures

| $2.1 \\ 2.2 \\ 2.3$                                     | Example schematic in KiCad.Example layout in KiCadExample netlist snippet generated from a KiCad schematic                                                              | 6<br>8<br>9                             |

|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| $\begin{array}{c} 4.1 \\ 4.2 \\ 4.3 \\ 4.4 \end{array}$ | The electronics design flow, as described by our participants                                                                                                           | 18<br>25<br>28<br>29                    |

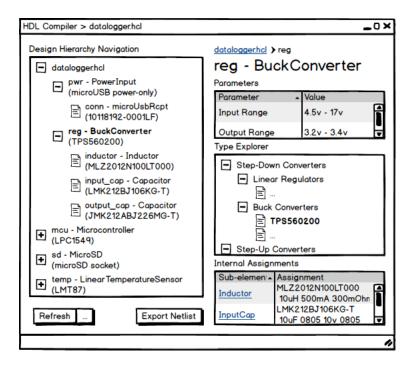

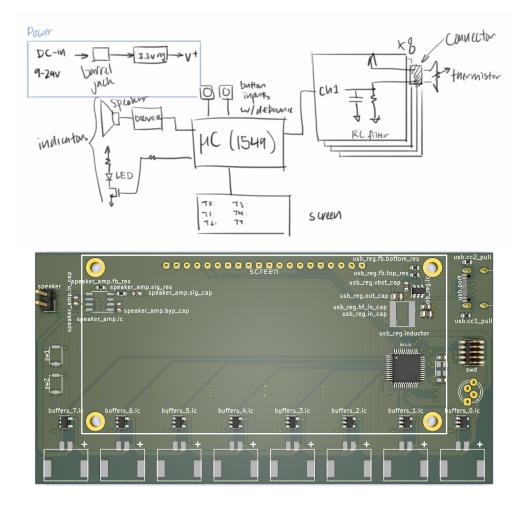

| $5.1 \\ 5.2$                                            | The Polymorphic Circuit Blocks HCL design flow                                                                                                                          | 37<br>38                                |

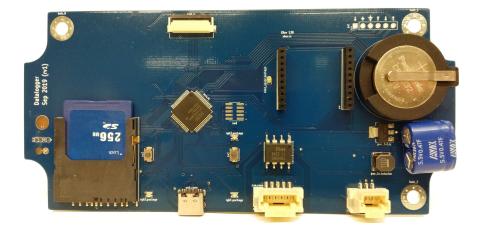

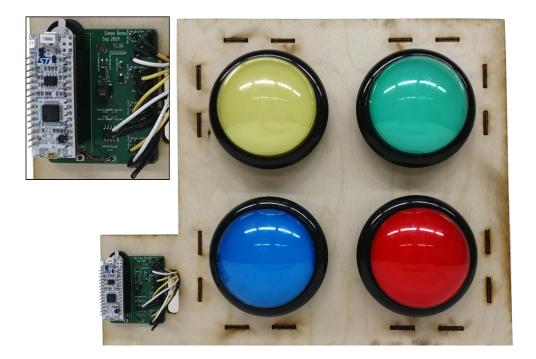

| 5.3                                                     | A more complex example: the datalogger PCB designed in Polymorphic Circuit<br>Blocks                                                                                    | 39                                      |

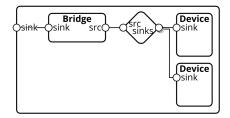

| 5.4                                                     | Example of a bridge pseudo-block, which adapts an externally facing port to an internally facing link                                                                   | 40                                      |

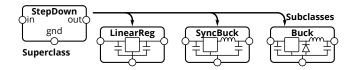

| $5.5 \\ 5.6$                                            | Class hierarchy example with step-down voltage converters                                                                                                               | 41                                      |

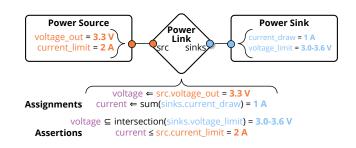

| 5.7                                                     | Blocks model                                                                                                                                                            | 42                                      |

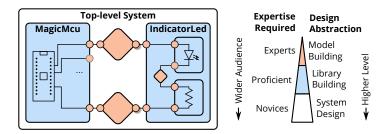

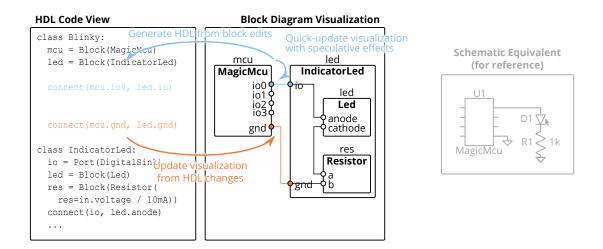

| $5.8 \\ 5.9$                                            | skill levels can fit in          Example code defining the Blinky circuit Block          Example of an alternative structure for instantiating the Blinky circuit using | 43<br>43                                |

| 5.10                                                    | implicit connect and chain       Simplified code for the indicator LED subcircuit                                                                                       | $\begin{array}{c} 44 \\ 45 \end{array}$ |

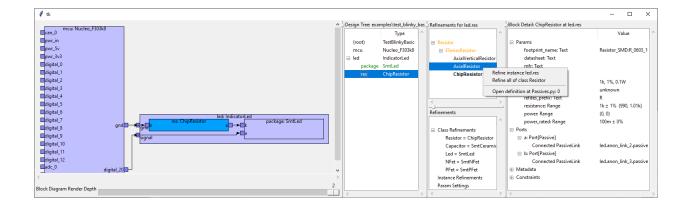

|                                                         | Visualization and refinement GUI with the Blinky example                                                                                                                | $45\\48$                                |

| 5.13                                                    | PH02's initial system diagram for the thermistor reader                                                                                                                 | 51<br>56                                |

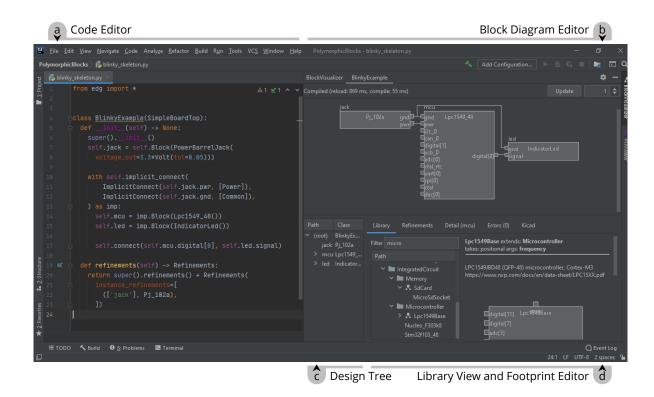

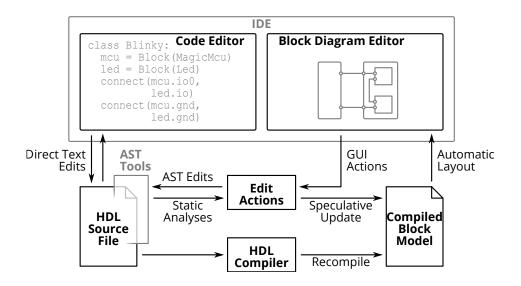

| 6.1                                                     | An overview of our integrated development environment approach to support<br>working with circuit board-level hardware description languages                            | 58                                      |

| 6.2                                                     | Overview of the IDE components                                                                                                                                          | 59                                      |

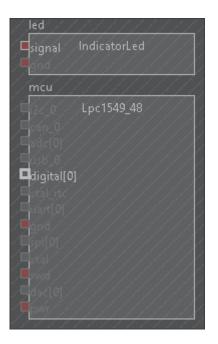

| 6.3  | Example system-level design HCL                                                 | 61 |

|------|---------------------------------------------------------------------------------|----|

| 6.4  | Example part definition of a Lf21215TMR digital magnetic field sensor           | 62 |

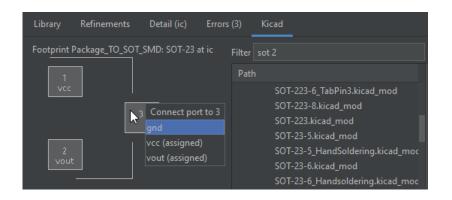

| 6.5  | The connection interface, showing legal connections from the microcontroller's  |    |

|      | digital IO                                                                      | 63 |

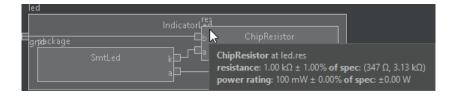

| 6.6  | Inspection of the resistor in the IndicatorLed block                            | 64 |

| 6.7  | The IDE's footprint assignment and pinning interface                            | 65 |

| 6.8  | Overall architecture of the IDE                                                 | 66 |

| 6.9  | Potential flow-preserving IDE interface concept with insertion options and live |    |

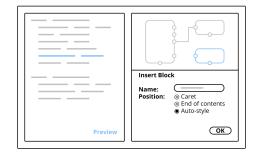

|      | preview                                                                         | 72 |

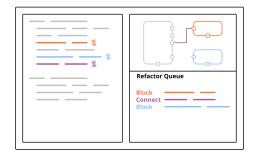

| 6.10 | Potential flow-preserving IDE interface concept that tracks inserted blocks for |    |

|      | later refactoring                                                               | 73 |

# List of Tables

| 4.1 | Summary of study participants. |  |  |  |  |  |  |  |  | • |  |  |  | • |  |  |  |  |  | • |  | • |  |  | • | 19 | ) |

|-----|--------------------------------|--|--|--|--|--|--|--|--|---|--|--|--|---|--|--|--|--|--|---|--|---|--|--|---|----|---|

|-----|--------------------------------|--|--|--|--|--|--|--|--|---|--|--|--|---|--|--|--|--|--|---|--|---|--|--|---|----|---|

#### Acknowledgments

First and foremost, my deepest thanks to my advisors Björn Hartmann and Elad Alon for supporting my journey through grad school. Your input – whether in designing and implementing systems, writing clear and concise papers and presentations, or in general being a researcher – has been invaluable in helping me get where I am today.

Thanks additionally to committee members Kimiko Ryokai and Prabal Dutta for providing additional perspectives and feedback that have helped strengthen this work. Furthermore, I'm deeply grateful to both Björn and Prabal for taking me on, adopting this board HDL project in the early years, and giving me the opportunity to build all this out.

I'd also like to thank James Demmel for both taking me on as an undergraduate researcher and for serving as my first year advisor – and critically, giving me the freedom to explore in that first year, which led me to hardware design, hardware description languages, and ultimately this project.

This project has been interdisciplinary and collaborative, and I've been fortunate to work with fellow grad student Rohit Ramesh, who shares a similar interest in electronics design and has a complementary formal methods and theory focus. His work on the core models provided the foundation that ultimately enables the design tools and interactions in this work. Continuing discussions will hopefully improve the power and expressiveness of these core models while keeping everything consistent, usable, and amenable to synthesis.

Throughout the years, many undergraduate researchers have also contributed to various parts of this project according to their interests. Their contributions have been helpful in getting systems built and evaluated, and many are still in the modern codebase. In particular, thanks to Sharan Satish Kumar for investigating Python GUI frameworks, Yulie Park for building the KiCad netlister, Connie Chi for investigating datasheet parsing (which turned out to be fundamentally hard), Nikhil Jain and Ryan Nuqui for exploring the underlying model and implementing IDE features, Josephine Koe and Tengis Dashmunkh for building parts libraries and generators, and Leena Elzeiny for making core compiler improvements. And a huge thanks to all who pre-tested the systems and user study protocols, and found bugs so that our participants didn't.

None of this would have been possible without all the user study and interview participants who have provided their time and feedback. And additional thanks to the anonymous peer reviewers of the conference papers that made up this dissertation for their suggestions that have helped make this work better.

Beyond this project, I'd like to thank b-crew labmates Andrew Head, Forrest Huang, Bala Kumaravel, Eldon Schoop, James Smith, Jeremy Warner, and J.D. Zamfirescu, who have provided feedback, insight, support, and fun times. Further thanks to Paulos lab members Molly Nicholas, Sarah Sterman, Kevin Tian, and Cesar Torres, especially for organizing reading parties where we could find (and fix) deficiencies in our papers so that the conference peer reviewers didn't. And an additional shout-out to administrative staff Aleta Martinez

for making all kinds of logistics painless, including the dreaded scheduling of the qualifying exam.

And while my dissertation focuses on a board HDL rather than a chip HDL, I would like to thank all those who I've worked with as part of the ASPIRE and ADEPT labs. Chisel has been a major source of inspiration for this project, in the high level generator HDL concept, the lower-level implementation choices, and how to engineer large systems that don't topple. Shout-outs to fellow grad students Adam Izraelevitz, Jack Koenig, Vignesh Iyer, and Kevin Laeufer who I've worked the closest with as part of the Chisel and ChiselTest projects, but also many others on what was a huge effort. Additional shout-outs to the lab's amazing administrative staff Roxana Infante, Tami Chouteau, and Ria Briggs who have kept the lab running and planned events; our systems administrator Kostadin Ilov who kept our infrastructure running; and staff engineers Jim Lawson and Chick Markley for dealing with the less-glamorous-yet-absolutely-critical day-to-day operations of the Chisel codebase.

No less important are the departmental staff Shirley Salanio and Jean Nguyen, who have been invaluable in helping navigate the administrative side of grad school as well as supporting me through more difficult times.

Beyond grad school, the solar car project team (CalSol) has been a major part of both my undergraduate and graduate years. Over my twelve years on the team, I've been able to engage in hands-on and interdisciplinary work, race solar cars across both the United States and Australia, and have the fortune of working with many amazing people. While there's too many to list comprehensively, I'd like to acknowledge fellow grad students members Derek Chou and Jean-Étienne Tremblay, and our milestone project of building an FPGA-based active battery balancing system within a month in 2018. Additional shout-outs to longtime members Tristan Lall, Byron Hopps, and Devan Lai, who have stayed involved past their undergraduate years and have been an invaluable source of expertise.

The COVID years were particularly challenging to our team, and I'd like to give special recognition to co-program directors Andrew Wang and Anthony Zhou for pulling us through while providing the most humanistic leadership in recent memory, and engineering director Erik Francis for his tireless dedication which was crucial to getting cars done and onto the racetrack. Additional special thanks to my COVID-era housemates and teammates Geoffrey Ding and Alexander Zerkle for being awesome people, making lockdown not all that bad, and putting up with (and contributing to) all the inanimate ducks, plush or otherwise.

CalSol's electrical sub-team (and by extension, some example boards in the dissertation like the datalogger in Figure 5.3) has heavily relied on the Supernode makerspace in Cory Hall, and I'd like to thank our departmental staff contacts David Au and Jeremy Kramer for keeping the place available as an open and student-run makerspace. I'd also like acknowledge my fellow student admins over the years Derek Chou, Calvin Li, Nick Firmani, Roy Tu, Allan Zhao, Lam Nguyen, Alicia Auduong, Avinash Jois, Harrison Zheng, Olivia Hsu, Dinesh Parimi, Kevin Zheng, Eric Deck, and Sylvia Jin, all of whom have helped keep the place running by contributing to new user training, staffing, equipment deployment and maintenance, and all the mundane-but-necessary upkeep like cleaning. It's been an amazing eight years in grad school and twelve years in Berkeley, and I'm sure I've probably forgotten someone above - but thanks to you as well for being part of my time here.

This work was supported in part by NSF awards CNS 1505728, IIS 1149799, CNS 1505773, and CNS 1822332; DARPA contract FA8750-20-C-0156 (SDCPS); Synergy: Collaborative: CPS-Security: End-to-End Security for the Internet of Things; the CONIX Research Center, one of six centers in JUMP, a Semiconductor Research Corporation (SRC) program sponsored by DARPA; the Paul and Judy Gray Alumni Presidential Chair in Engineering Excellence; ADEPT Lab industrial sponsor Intel; ADEPT Lab affiliates Google, Siemens, and SK Hynix; Advanced Research Projects Agency-Energy (ARPA-E), U.S. Department of Energy, under Award Number DE-AR0000849; and the Camozzi Group via the iCyPhy consortium. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

# Chapter 1 Introduction

Electronics devices are all around us and play an increasingly large part in our lives - from the things that we directly interact with like smartphones and game pads, to those that quietly operate in the background like thermostats and internet-connected sensors. Almost universally, electronics are built on printed circuit boards (PCBs), which in turn are designed with electronics design automation (EDA) tools. Yet, the circuit design aspect supported by these tools still revolve around drawing schematics – largely unchanged over the past several decades, despite significant gains in computational power and the shifting context of design as do-it-yourself and making have become more popular and accessible.

Although schematics provide a very direct mapping to the components on the board and allows a fine degree of control, this low level of design is not without tradeoffs. For novices and hobbyists, these tools require an understanding of electrical engineering details in order to build a working circuit and board. For experts and professionals, the low-level representation can be tedious and inefficient, requiring every degree of freedom to be resolved even when there is a large acceptable design space.

## 1.1 Overview and Thesis

Overall, this dissertation aims to examine how to re-think circuit design tools to support modern expectations of automation, while minimizing tradeoffs in flexibility and control that higher level design tools often make. This work takes an interdisciplinary approach: not only looking at the electrical engineering aspect of the problem, but also taking inspiration from modern programming languages that enable a wide variety of users to build custom automations, and with a human-computer interaction framing to understand underlying user needs and ensure solutions remain usable.

As such, the thesis at the core of this work is:

a hardware description language approach to board design can better support user design goals by providing a higher level of design and abstracting away lower-level tasks, while remaining usable and minimizing trade-offs in flexibility.

# **1.2** Contributions

Supporting that thesis, this dissertation makes the following contributions:

- A formative interview study with 15 participants to assess current practices and problems in board-level design, taking a holistic end-to-end ideas-to-device perspective without being limited to current EDA flows (Chapter 4). We found that a significant amount of design work happens before EDA tools come into play - and often without the help of software at all. By the time users get to schematic capture, much of the interesting and creative work has already been done, and schematic capture itself involves a lot of rote transcription.

- A concept for a hardware construction language (HCL) based system that address major issues with current flows revealed in the above formative study, and preliminary user feedback on mockups of this language and supporting tooling (Chapter 4). Though users indicated enthusiasm around the system architecture level of abstraction, they also expressed caution around issues such as dependence on and trust in libraries. We further discuss relevant design principles for future board tools based on our results.

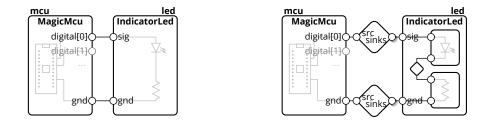

- An implementation of the above system as a Python-embedded HCL, based around a hierarchy block model to scale across multiple levels of abstraction and supporting design re-use through user-definable libraries of blocks (Chapter 5). Blocks can be generators, containing executable code that constructs the block's sub-circuit from higher-level parameters (for example, calculating resistance given a voltage and current specification), while a type system and electronics model supports substitution and refinement (for example, whether a particular step-down converter subcircuit can be used in place of a generic voltage converter).

We evaluate this system by designing several example boards in this system and with a small user study where participants built devices of their choice. Users were able to complete designs in our system and provided a wide range of feedback including suggestions for better tooling and areas of concern such as the higher learning curve.

• Supporting tooling for the above HCL in the form of an integrated development environment (IDE) to bridge the novel code approach with familiar schematic views, by augmenting the standard text editor with a block diagram visualization supporting schematic editor like actions (Chapter 6). As both views are linked – the visualization can be updated from code edits, and code can be generated from schematic like actions – users can easily move between interfaces based on their own preferences and the task at hand.

We evaluate this interface with a small user study in which participants complete a pre-defined project, and make generalized recommendations for similar tools based on the results. Although users differed in whether they preferred to produce HCL by writing text or through graphical actions, the visualization still provides something for everyone, such as by acting as an intuitive reference for writing HCL.

## 1.3 Roadmap

These chapters form the rest of this dissertation:

**Chapter 2: Background** provides an overview of the workflow for modern board-level EDA tools, along with the historical context and the overarching class of creativity support tools.

**Chapter 3: Related Work** looks at related work, both in novel board-level design tools and empirical studies, as well as in adjacent fields such as general electronics debugging, chiplevel digital logic design, and programming tools. While recent work on board-level design tools also aim to raise the level of design with libraries of blocks, they often neither support user-defined libraries nor address how libraries are created, which we believe is a crucial step for generalizability and practical usage. To address this, we take inspiration from novel chiplevel hardware description languages, which successfully span multiple levels of abstraction from library-level modules to entire chips while offering a high degree of automation.

Chapters 4, 5, and 6 describe the novel work in this dissertation, and are summarized in more detail above in Section 1.2.

**Chapter 7: Conclusion** concludes the dissertation with a summary of contributions and findings and ideas for future work.

Chapter 8: Glossary provides a definition of selected terms and acronyms.

# **1.4** Statement of Prior Publication

This thesis is based on, and incorporates material from, these prior published works:

- Beyond Schematic Capture: Meaningful Abstractions for Better Electronics Design Tools [42] (CHI '19), co-authored with Rohit Ramesh, Antonio Iannopollo, Alberto Sangiovanni Vincentelli, Prabal Dutta, Elad Alon, and Björn Hartmann

- Polymorphic Blocks: Unifying High-level Specification and Low-level Control for Circuit Board Design [43] (UIST '20), co-authored with Rohit Ramesh, Connie Chi, Nikhil Jain, Ryan Nuqui, Prabal Dutta, and Björn Hartmann

- Opportunities and Challenges for Circuit Board Level Hardware Description Languages [41] (HATRA '20), co-authored with Björn Hartmann

- Weaving Schematics and Code: Interactive Visual Editing for Hardware Description Languages [44] (UIST '21), co-authored with Rohit Ramesh, Nikhil Jain, Josephine Koe, Ryan Nuqui, Prabal Dutta, and Björn Hartmann

I am the first author on all these papers, but none of this would have been possible without the effort of all the co-authors, including my advisors Björn Hartmann and Elad Alon, graduate student colleagues Rohit Ramesh and Antonio Iannopollo, and all the undergraduates who have worked with us over the years.

# Chapter 2 Background

Today, a wide range of users design circuit boards for a variety of reasons - spanning hobbyists and makers working on personal projects, to commercial teams working on complex products. The falling cost of production (especially for one-off prototypes), an active maker community, and beginner-friendly platforms like Arduino [4] have helped make electronics and board design more accessible. In mainstream practice, EDA tools for board design generally have two parts: *schematic capture*, where users draw the circuit, and *board layout*, where users place and route components from the schematic on a virtual board. This rest of this chapter provides a brief overview of mainstream board design tools, as well as principles for the larger class of creativity support tools.

A variety of board-level EDA tools exist for different user groups: for example KiCad [35] is open source; EAGLE [6] is largely geared towards hobbyists; while Altium [1], Cadence Allegro [12], and Mentor Xpedition [55] are geared towards professionals working on complex projects. This chapter only covers high-level concepts and notable features of these tools, but more in-depth tutorials and user guides are readily available online.

# 2.1 Schematic Capture

In graphical schematic capture tools such as the one shown in Figure 2.1, users create the schematic by placing schematic symbols (representing components - for example, the squiggly lines for a resistor) onto the schematic sheet, then drawing wires to connect their pins. Symbols for common parts are often available in libraries [40], such as bundled with the tool, provided by the component manufacturer, or created by the community. The circuits themselves can be designed by referencing well-known circuits (such as RC low-pass filters and various opamp circuits) and application schematics in manufacturer-provided datasheets.

While computerized schematics can theoretically be infinitely large, schematics are often drawn to fit on printable sheets. More complex designs often require multiple sheets, and there are two common organizational techniques:

• A flat schematic simply treats the contents of multiple sheets as if they were the

Figure 2.1: Example schematic in KiCad.

contents of one big schematic. Connections between sheets are handled with tunnels, where tunnels with the same name are connected together.

• A hierarchical schematic abstracts sheets of sub-circuits into a symbol that is treated like a component. This provides for abstraction and re-use in design, for example the same sub-circuit can be instantiated several times simply by duplicating the block.

While sub-sheets in hierarchical schematics can theoretically be shared, practical barriers to large scale direct re-use of design files include different file formats and tailoring subcircuits (for example, tuning component values) for each design. However, organizations may re-use internal schematic files [54].

Tools often support automated schematic checks with Electrical Rule Checks (ERC). Typically, pins are assigned some type (like Power Input and Power Output), and rules check for illegal connections between pins (for example, multiple Power Outputs driving a single wire, or pin that is not connected). This tends to be a pretty coarse system: for example the Power Output pin type does not further define voltages. Otherwise, schematic verification tends to be done by human peer review [53].

Tools also provide varying degrees of automation features, to ease repetitive tasks. The simplest example are various wizards, such as for creating a chip symbol with rows of pins on both sides. Slightly more complex is Altium's Smart Paste [2], which allows a copied selection to be pasted as different objects - for example, converting a group of selected pins to tunnels.

More complete tools may also offer some kind of programming interface for end-users, such as in the form of a scripting language or plugin API. While coding expertise is required to write custom scripts, pre-made scripts are often shared on the internet and can be used directly. More advanced plugin can integrate directly into the tool's GUI and only require installation.

Overall, however, these are still first and foremost schematic drawing tools and very limited in what they do to actually support system and circuit design.

# 2.2 Layout and Assembly

As schematics are an abstract representation of a circuit, they cannot be directly made into circuit boards. The core connectivity data from the schematic, such as in the form of a *netlist* consisting of a list of components and connections between their pins, can be imported into a board layout tool. An example netlist is shown in Figure 2.3. As in Figure 2.2, components are dumped on the virtual board and must then be placed and routed by the user. The layout can typically be incrementally updated from a changed schematic, without needing to restart layout.

Placement and routing can be fully manual, tool-assisted (such as with *online DRC*, which stops dragging a wire when it gets too close to another one), or fully automated (such as with *autorouters*). Some tools may support features for replicating layouts of similar subcircuits, such as Altium's rooms feature [63] or KiCad's Action Plugins [59]. There has also been much work on autorouting algorithms [21], but quality of results varies widely with factors such as choice of tool and design complexity.

Tools commonly perform two kinds of basic correctness checks. Design rules check (DRC) checks for physical manufacturability, such as minimum wire width, minimum spacing between wires, and minimum hole sizes. Layout vs. schematic (LVS) checks that the connectivity on the layout is the same as the schematic, catching unintentionally crossed wires or unconnected pins. Some tools also support more advanced layout-sensitive analyses, such as for signal integrity (mainly for high-speed signals) and power analysis (for voltage drop and power loss over the copper lines).

# 2.3 Historical Context

While modern tools are undoubtedly easier to use, the fundamental paradigms have been around for almost half a century. Computerized graphical schematic appeared in the liter-

Figure 2.2: **Example layout in KiCad**. The components on the top have been freshly imported from a netlist generated from a schematic, while the components on the bottom have already been placed and routed.

ature as early as the 1970s, as a response to the awkwardness of punch card or text based schematic entry. Matthews [48] criticized tools of the time as "operator-aided computers", and describes a system similar to today's mainstream schematic tools. Despite the requirement for more user time on then-expensive computing resources, this system both reduced the overall design time and eliminated an error-prone punch card step.

Shiraishi regarded interactive schematic drawing as time-consuming, and his ICAD/PCB system [69] instead digitizes hand-drawn schematics using pattern recognition techniques. However, it focused on logic circuits and required a standard schematic style.

Another common theme of EDA systems from this era was integration between the different steps that we take for granted in modern EDA tools, such schematic entry, layout, and simulation. Reasons included the time, cost, and potential for errors from manual translation [48, 8, 39].

Systems also explored methods for component placement and board routing. Varying degrees of automatic placement were part of many tools, while other systems provided interactive feedback on manual placements [48, 69]. Autorouting was also a research theme

| 1        | (components                                                         |

|----------|---------------------------------------------------------------------|

| <b>2</b> | (comp (ref U2)                                                      |

| 3        | (value STM32F103C8Tx)                                               |

| 4        | (footprint Package_QFP:LQFP-48_7x7mm_P0.5mm)                        |

| 5        | )                                                                   |

| 6        | (comp (ref J2)                                                      |

| 7        | <pre>(value USB_C_Receptacle_USB2.0)</pre>                          |

| 8        | <pre>(footprint Connector_USB:USB_C_Receptacle_BSC_A40-00119)</pre> |

| 9        | )                                                                   |

| 10       | (comp (ref U1)                                                      |

| 11       | (value TPS562200)                                                   |

| 12       | <pre>(footprint Package_T0_SOT_SMD:SOT-23-6)</pre>                  |

| 13       | )                                                                   |

| 14       | )                                                                   |

| 15       | (nets                                                               |

| 16       | (net (code 6) (name +3V3)                                           |

| 17       | (node (ref U2) (pin 24))                                            |

| 18       | (node (ref U2) (pin 48))                                            |

| 19       | (node (ref U2) (pin 9))                                             |

| 20       | (node (ref U2) (pin 36))                                            |

| 21       | (node (ref U2) (pin 1))                                             |

| 22       | )                                                                   |

| 23       | (net (code 10) (name DM)                                            |

| 24       | (node (ref J2) (pin B7))                                            |

| 25       | (node (ref J2) (pin A7))                                            |

| 26       | (node (ref U2) (pin 32)))                                           |

| 27       | (net (code 11) (name DP)                                            |

| 28       | (node (ref J2) (pin B6))                                            |

| 29       | (node (ref J2) (pin A6))                                            |

| 30       | (node (ref U2) (pin 33))                                            |

| 31       | )                                                                   |

| 32       | )                                                                   |

Figure 2.3: Example netlist snippet generated from a KiCad schematic, showing the components, their properties (value or part number and footprint), and the nets (connections) their pins are a part of.

[39, 8, 48, 47], typically in conjunction with interactive manual routing.

Rager and Weiner [64] did an in-depth study on dense board layouts, recommending an interactive system where a human guides automated processes, but is provided with powerful assistive tools when lower-level manual intervention is needed.

# 2.4 Creativity Support Tools

EDA tools are part of the larger class of creativity support tools, which have received attention in the HCI literature with topics ranging from theoretical foundation, observations, and suggestions. In particular, Shneiderman et al. [70, 72, 71] and Resnick et al.[67] identifies several design principles, including supporting exploratory search, collaboration, and "low thresholds, high ceilings, and wide walls" (easy for novices while powerful for experts). Furthermore, meaningful evaluation strategies for creativity support tools are less clear than for traditional productivity tools with their controlled studies and standardized measures. This dissertation combines these high-level principles with domain knowledge and user feedback to build tools that aim to better support users in building electronics.

# Chapter 3 Related Work

In recent years, there has been a significant body of work on electronics, especially for nonprofessionals such as students and makers, and spanning from empirical studies to tools with a variety of underlying technical approaches. Although this dissertation mainly focuses on board-level electronics, this chapter also briefly reviews relevant work in chip design and programming tools that inspires some of the approaches taken.

# 3.1 Empirical Studies

The rise of the maker movement has spurred some recent work on examining how people actually work with electronics and the practical issues that arise. For example, Crossed Wires [11] examines mistakes by novices in prototyping a physical computing system onto a breadboard, observing mistakes in both the hardware construction, software development, and the interface between the two. Mellis [52] observed novices over the course of a six week workshop as they were taught embedded design and ultimately built printed circuit boards. While it is possibly the most comprehensive examination involving modern EDA tools and practices so far, the focus on novices sets a low complexity ceiling.

However, there does not seem to be much work on the more professional and advanced users side. While tool vendors likely conduct usability studies, the results generally are not available to the academic community. This poses challenges for reimagining design tools that can be useful throughout the design complexity spectrum, instead of narrowly tailored for novices. As such, we start by conducting a study of current design practices for a range of users.

# 3.2 Electronics Design

While mainstream design practice has largely settled on schematics, novel work provides more automation such as by synthesizing the circuit from a specification, or by raising the level of design with pre-made modules.

#### Synthesis Approaches

Synthesis approaches take a variety of inputs. For example, Trigger-Action-Circuits [3], takes input specified at a behavioral and dataflow level – what the circuit is supposed to do – and produces a breadboarding diagram. On the other hand, circuito.io [16] and EDASolver [19] allows users to specify the design as a list of peripherals connected to a microcontroller. However, technical details are scarce: only Trigger-Action-Circuits had a corresponding publication, which focused more on interactions and an user study. None emphasize user-defined parts, which limits users to the parts library supplied by the tool vendor.

Embedded Design Generation (EDG) [65] and Echidna [57, 58] are similar, allowing users to specify a partial design such as sensors and motors, then automatically completes the design through interface-driven synthesis, for example by adding power systems and compute elements. While functionally similar, these systems have different underlying technical approaches: EDG translates the circuit design problem and passes it to a SAT solver, while Echidna is based on heuristic-assisted tree search.

Synthesis approaches have also been applied to other domains, such as for aircraft power systems [62]. However, it structures the problem as a collection of equations specified by the user, rather than the more user-friendly domain-specific abstractions provided by EDG and Echidna. While this dissertation does not address synthesis, it does continue work on domain-specific formal models for electronics that may support synthesis tools in the future.

Model-driven synthesis aside, AutoFritz [45] extends a schematic-like design system with data-driven circuit autocomplete suggestions. Such an approach makes different trade-offs: while model-driven tools require the (potentially tedious) creation of libraries of parts, data-driven tools can mine existing schematics. However, without an understanding of electronics, they may be more liable to make mistakes and may not be able to generalize past their dataset. While suitable for a recommendation system where the human still ultimately controls low-level details, this may be a significant limitation for higher-level design.

Although highly automated schematic tools do not appear to be in common use today, there are many existing tools that can synthesize sub-circuits from specifications. For example, TI's WEBENCH [32] automatically selects power conversion chips from their product line given high-level parameters (such as input and output voltage) and provides a full subcircuit around it. Online calculators are also available for well-known circuits, such as resistor pickers for resistive dividers [31]. While very useful, these are not integrated into schematic tools and still require the user to stitch generated outputs into the final designs and ensure consistency in the face of changes. This dissertation looks at an integrated design system which can automatically invoke arbitrary sub-circuit generators.

#### Module-based Design

In contrast to synthesis tools which automate decision-making, module-based design keeps users in control and instead speed up design by working at the level of modules instead of components. A module contains some subcircuit, much like hierarchy blocks in modern schematic tools, but is otherwise a black box and do not allow the user to modify its implementation.

Recent commercial tools combine module-based circuit design with a layout view: instead of placing abstract component on a schematic sheet, users place module bounding boxes on a board view. Connections between components are still abstract (they do not physically correlate to circuit board trace layouts), so board layout and routing still happen separately. Examples include Sparkfun À La Carte [75] and Geppetto [25], but details have not been published, so their internal models, library creation process, and algorithms are not known.

MorphSensor [88] also makes use of module-based design with mixed schematic and physical views, but focuses more on the novel 3D design view for flexible PCBs. Circuit design is out of scope of that tool, and it instead imports connectivity data from files produced by mainstream schematic editors.

#### **Electronics Models**

Synthesis tools generally need some kind of electronics model to check parts for functionality and compatibility to produce correct designs. For example, this may include encoding voltage limits of parts, then checking it against the actual voltage on the power line it is connected to.

EDG [65] defines a mixed electronics model (modeling voltages and their limits, currents and their limits, and digital logic threshold voltages) and software model (modeling programming interfaces like buttons and LEDs) on ports and their connections. This dissertation builds upon the electronics model. Additionally, both Sparkfun À La Carte [75] and Geppetto [25] appear to have some model that limits incorrect connections, but again comprehensive technical details have not been published.

Design tools aside, Valydate [56] provides automated schematic checking. As it is also commercial work, technical details have not been published, but it appears to have some kind of electronics model and parts library that includes voltage and current limits.

#### Summary

Overall, one common characteristic of recent work, both commercial and academic, synthesis or otherwise, is the use of libraries of higher-level components. At the very least, this helps speed up design through design re-use, instead of needing the user to re-draw schematics from scratch. Many also incorporate some kind of electronics model more detailed than the coarse pin types in mainstream ERC, to automate checks or guard against user error. However, none of these projects focus on library creation by end users, a step necessary to achieve scalability and generality beyond what a team of tool developers could feasibly do. This dissertation attempts to combine a module-based design flow with an electronics model, in a tool that allows users to create both libraries and top-level boards within an unified interface.

# **3.3** Electronics Prototyping and Beyond

While boards are a relatively permanent and stable form for building electronics, prototyping may be preferred on more reconfigurable platforms like breadboards.

#### **Breadboards and Prototyping**

One thread of research has been to augment breadboards, especially as breadboards are commonly a starting point for students. These include measuring and visualizing voltages [18] and current flows [86], and detection of inserted components through active probing [85]. Bifröst [51] further combines code instrumentation and logic analyzer circuit tracing for examining the hardware-software boundary. CircuitStack [81], on the other hand, adds a printed connectivity layer to breadboards to avoid the time-consuming and error-prone process of wiring up breadboards.

A wide range of other work exists to support prototyping. One example is the use of software programmable components, such as for designing analog circuits [76] or through an augmented reality interface [36]. Augmented reality has also been used to overlay simulation data onto a physical device built with parts from a specialized kit [14]. Other projects support constructing circuits through step-by-step tutorials [83].

#### PCBs for Novices and Debugging

PCBs may still be useful for novices who have a design they want in a more stable form. Fritzing [37] helps by providing a breadboard view of a circuit as a conceptual bridge to the schematic view, but is still fundamentally a schematic drawing tool. The previously mentioned AutoFritz [45] builds on top of that with data-driven circuit autocomplete suggestions.

As PCBs don't always work the first time around, some work exists to help in the debugging process. For example, Pinpoint [77] automatically inserts test points onto a board and generates a corresponding bed-of-nails testharness. This can be used to probe signals and dynamically isolate subcircuits. BoardLab [23] takes a different approach, instead using a magnetic positioning system to link a probed point on a physical board to the schematic.

#### Scaling

While many tools focus on enabling novices, some work also examines challenges of scaling from one-of prototypes to production [34]. While the work in this dissertation does not specifically address production, aspects of the system that specify a design space such as substitutable parts may make it easier to optimize a design for production.

# **3.4** Hardware Description Languages

Although graphical schematics are mainstream for board design, hardware description languages (HDLs) dominate digital logic design for chips and can provide useful inspiration.

### Chip HDLs

HDLs like Verilog and VHDL are common in the chip design space for defining digital logic. Generally, digital logic HDLs combine a *structural component*, which specifies hardware in terms of modules and connections, and a *behavioral component*, which specifies arithmetic and logic flows. Both languages are organized in terms of modules with ports, and like hierarchical schematics for boards, digital logic modules may be composed of other modules.

Verilog-AMS [29] and VHDL-AMS [15] provide analog and mixed-signal extensions on top of their base digital languages. Though they allow for modeling and simulation of circuit behavior, they are neither design nor synthesis languages.

Hardware construction languages (HCLs) that support generators are an evolution on the basic HDL. Instead of merely providing a textual format for describing a module, these encode the rules for constructing a family of modules from high-level parameters. Chiplevel HCLs include Chisel [33] for digital hardware, and OASYS [27] and BAG [17] for analog hardware. One implementation strategy, as taken by Chisel, is providing hardware construction primitives (for example, instantiate module and connect ports) embedded in a general purpose programming language.

There is also a thread of work addressing the lengthy, often hours-long latency for chip tools to recompile from a design change – a bottleneck on productivity. Strategies include improving synthesis performance [82] and simulation performance [74, 68] through partitioning and incremental compilation. While board-level designs are orders of magnitude less complex than chip designs, similar techniques can also speed up board-level compilation.

#### **Board HDLs**

HDLs also exist for boards, with an early one being PHDL [61] which effectively is a schematic in textual format, but with modules and limited parameterization to promote design reuse. Unlike chip HDLs, PCB HDLs are purely structural, as it is unclear what behavioral abstractions can suit the wide space of PCB electronics. However, an HDL interface to the same schematic abstractions provides little more design automation than a graphical editor.

More recently, JITPCB [7] and SKiDL [73] brings generators to the PCB space by embedding circuit construction primitives in a general purpose programming language. This dissertation builds on top of that core idea, but augments it with more detailed electronics modeling to enable design support features like parts selection and correctness checks.

# 3.5 Programming Tools

Hardware description languages, and especially ones that enable generator constructs, are essentially programming languages — for which there is a large body of work including supporting tooling. For HDLs, and especially for PCB design where there is currently less familiarity with textual design methods, tools can help bridge the gap between current practice and powerful-but-novel techniques. This section reviews some of the most relevant work, which while not directly related to building PCBs, still serves as inspiration.

#### Live Programming

Live programming tools continuously run code as it is written by the user, and display the results to provide immediate feedback. These tools can help connect the more abstract representation of code to concrete examples [20], which users might find easier to work with or to help navigate execution contexts [50]. Prior empirical research [38] further indicates that simpler liveness tools were frequently used, and even small amounts of liveness can have disproportionate impact.

One critical aspect of live programming systems is the latency between code change and visible effects [66]. Prior work has discussed possible techniques to reduce latency [50, 79], such as predictively starting to compute results or returning speculative results. Compilation of HDLs can require non-negligible amounts of time, and tricks like speculative results can preserve a smooth interaction flow.

### **Graphical Tools**

Beyond one-way visualization, work has also examined *output direct manipulation* – how these visual representations could be manipulated to write code in specific domains. One recent example is Sketch-n-Sketch [28], which provides a graphical editor for a custom language for 2D graphics. Other examples include such editors for string manipulation and diagramming [49].

However, perhaps the most often used similar class of tools are graphical user interface (GUI) builders, where users can define their GUI graphically through direct manipulation interactions such as drag-and-drop. These tools similarly aim to provide an interface that is closer to the domain than the equivalent GUI construction code they generate. Yet, the code generated often is not stylistically clean or even meant to be directly edited [87] – perhaps fine for a GUI with defined integration points and static structure, but less so for an HDL where programming the structure is the point.

Separately from graphical interfaces for writing textual code, there are also visual programming languages where the language itself is graphical. Examples include educational languages such as Scratch [46] which provides a blocks interface to an imperative programming language, and studies of its usage have shown some benefits [5]. Beyond education, visual languages have also seen practical use, most notably with LabVIEW [30] which features a different, dataflow abstraction. While ideas from visual language approach could provide the capabilities of a generator HDL without any code, textual interfaces are currently the dominant and familiar way to program.

# Chapter 4

# **Formative Studies**

## 4.1 Introduction

Given the lack of recent research into how people actually design boards, diving straight into designing and building tools runs the risk of not actually understanding user needs and missing pain points. Therefore, we start by learning about current design flows, with the focus of discovering what approaches to better design tools are fruitful, and why.

We take a broadly-scoped and holistic approach of understanding the design flows from idea to physical device. This end-to-end investigation avoids being limited to assumptions baked into current tools, and tries to get at the fundamental goal of building devices. Crucially, this can also reveal steps that are under-served and where novel tools be impactful.

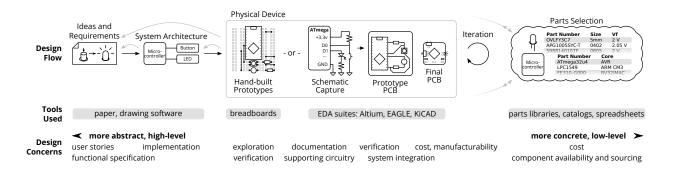

Figure 4.1: The electronics design flow, as described by our participants. Users start with an idea, refine that into a system architecture, and then iterate physical prototypes. Parts selection happens throughout the process. While certain steps require linear progression, iteration and revision of earlier stages also happen. Overall, EDA tools only support a small part of this process, and moving between steps was a major source of friction.

|     | Age        | Motivations                            | EDA tool | Design discussed                  | Mockup<br>study |

|-----|------------|----------------------------------------|----------|-----------------------------------|-----------------|

| P01 | late 20s   | school, hobby                          | EAGLE    | LED board                         | Yes             |

| P02 | early 20s  | school, hobby                          | EAGLE    | analog feedback-controlled heater | Yes             |

| P03 | early 20s  | school, job (startup)                  | EAGLE    | Arduino motor controller          | No              |

| P04 | early 20s  | school, research, hobby                | EAGLE    | music recording system            | Yes             |

| P05 | late $20s$ | research, side jobs, hobby             | EAGLE    | robotics                          | Yes             |

| P06 | early 30s  | research, hobby                        | EAGLE    | electrical muscle stimulation     | No              |

| P07 | early 20s  | school, hobby, job (industry engineer) | KiCad    | IO controller                     | Yes             |

| P08 | early 30s  | job (industry engineer), hobby         | KiCad    | educational kits                  | Yes             |

| P09 | mid $30s$  | research, school                       | EAGLE    | educational blocks kit            | Yes             |

| P10 | mid 30s    | job (industry engineer), hobby         | EAGLE    | breakout board                    | Yes             |

| P11 | late 20s   | job (research engineer), hobby         | Altium   | motherboards for chip tapeouts    | Yes             |

| P12 | early 20s  | job (industry engineer), hobby         | Altium   | power converter                   | Yes             |

| P13 | late 20s   | research                               | EAGLE    | embedded development board        | No              |

| P14 | late 20s   | job (industry engineer), hobby         | DipTrace | debug adapter                     | No              |

| P15 | late $30s$ | job (industry engineer), hobby         | Altium   | general consumer electronics      | No              |

|     |            |                                        |          |                                   |                 |

Table 4.1: Summary of study participants.

For each step in the flow, we also delve into which tools (if any) are used, whether they work well, and where the pain points are. This deeper look reveals details of designers' thought processes, intermediate goals within their workflows, and their interactions and frustrations with existing tools.

We use what we learn to envision and mock up plausible, alternate tools that can better support these design flows. Then, by examining participant feedback of these prospective designs, we look more closely at what designers find valuable, and where future tool builders should focus.

The overall contributions consist of a formative interview study with 15 participants to assess current practices and problems (in Sections 4 and 5), followed by the design of a tool concept that addresses major issues (in Section 6), and ending with user feedback on a mockup of the tool concept (in Sections 7 and 8). This overall methodology follows the example of prior papers that combine formative studies with concept designs for better tools in other domains [60, 26].

## 4.2 Participants

We conducted an interview study with 15 participants (14 male), of which 10 returned for the follow-up mockup study. While small, this group covers a wide variety of skill levels, design types, and EDA tools used. Critically, both professional and hobby users are included. A summary of participants' backgrounds is shown in Table 4.1.

All participants are familiar with the design process from idea to PCB, and all but one have completed at least one full project consisting of all those steps.

We recruited participants using two methods: personal referrals (7 participants), and relevant email lists (8 participants) such as those of a local makerspace, university design courses, and student groups. While the only criteria was some experience building PCBs in EDA tools, we did not recruit those working on highly complex designs to avoid a long tail of specialized issues. Participants were compensated with a \$20 gift card for each of the interview study and mockup study.

## 4.3 Interview Study: Methodology

Interviews were semi-structured and start with background information, including motivations, designs, and views of flow from idea to final device. Based on those responses, we then go into depth on each step in the flow, examining tools used, pain points, references used, and general suggestions or comments. Interviews averaged 90 minutes with a standard deviation of 29 minutes, and were conducted either in-person at the participant's workplace or through videoconference.

Utilizing the principles of contextual inquiry [9], we asked for an example design to ground discussions when possible. A majority of participants were able to do so, but some could not because of confidentiality and lost files. Instead, we asked them to either visualize their designs or bring up stock schematic and board layout images.

Interviews were conducted by one interviewer and audiotaped with the participant's consent. One researcher, experienced with board design and familiar with most of the tools discussed, then conducted an open coding phase over the transcriptions, and further grouped codes into related topics [84]. From these, we looked for themes that both had design implications for EDA tools and either had support among multiple participants or were notable outliers.

# 4.4 Interview Study: Findings

Participants provided rich data on their design flows, and how tools both did and did not support steps in those flows.

#### **Design** Flows

As shown in Figure 4.1, we broadly divide the design flow into these steps, in order: specification finding, system architecture development, and physical device iterations on a variety of media (including breadboards, milled PCBs, and commercially produced PCBs). Overall, each step incrementally refines the design to be more concrete, until finally a PCB can be produced. While there is a strict chain of dependencies between steps, designers regularly iterated and backtracked, especially in response to new information from testing and design.

#### CHAPTER 4. FORMATIVE STUDIES

#### **Specification Finding**

Determining the requirements and specifications for a device is a varied process that differed from user to user and from project to project. Specifications could capture a whole host of design goals including technical and functional requirements, user interactions, and aesthetic goals. These could be captured as drawings on a whiteboard, lists on documents and slide decks, or even a chip design that the system is built around. In many cases, these were living documents, with requirements and project scoping being a back-and-forth process where each edit forces many other changes down the line.

#### System Architecture Development

Specifications were then refined into a system architecture, represented as a block diagram. This serves as an intermediate step, translating from requirements into an implementation strategy.

The key distinguishing feature of this step is support for varying and mixed levels of abstraction.

Each engineer will have what feels right for them. (P15)

Blocks in participants' architecture diagrams ranged from the generic ("accelerometer", "trigger circuit", or even just "sensors") to the specific (part numbers and subcircuit schematics). Three participants had examples that mixed abstractions on the same document, with some blocks being generic and others having part numbers. Some diagrams also indicated types of information flow between design elements such as communication buses or protocol information.

Drawings were overwhelmingly the most common representation: ten participants used either paper, whiteboards, or graphics software like PowerPoint and Visio. Schematic capture tools could also be used to produce nonfunctional diagrams, and two mentioned occasionally using EDA tools for this step. While digital tools gave designers powerful advantages including hyperlinking, cloud sharing, and backup, the unconstrained nature of drawings was most important:

I feel very free to sketch in whatever language I want and whatever higher level I want. (P06)

Overall, participants generally enjoyed this step:

I kind of like it. [...] It's a very creative area where somebody gives you requirements and you have the freedom to meet them however you see fit. [...] There's the creative freedom that you don't have once you get to the schematic and the layout. (P14)

#### Prototyping

Ten participants talked about a prototyping phase, which could be done with solderless breadboards, soldered protoboards, milled PCBs, or development boards and kits. Agility was a goal, which rapid prototyping machines could help with:

I'm fortunate enough to have an LPKF [PCB mill] to mill the boards with. And that's been great. Usually the board goes through three or four revisions after soldering, so it's not just that, oh, I made one board and then it's done. (P03)

More generally, others also iterated on PCBs for their projects, with earlier boards acting as prototypes of the final design.

Prototypes were generally intended to validate some aspect of the design, though one participant also noted their value for exploring concepts and implementations. Validation was not limited to electrical functionality: mechanical characteristics, user feedback, and firmware development were also goals.

#### Schematic Capture

Schematic entry is where PCB design suites typically enter the design process.

Concerns here tended to be much lower-level, to the point where issues of schematic layout and readability were as common as those of circuit design and functionality. Participants noted the value of the schematic as a reference for later debugging or a document that should be shared with others. Aesthetics aside, messy designs could also conceal schematic errors or lead to bugs.

Mentions of manual transcription as part of the process were common – from either physical prototypes, or combining block diagrams with vendor-supplied reference schematics. While circuit designs in the abstract saw re-use, the inability to import data resulted in a time-consuming, tedious process. Yet, this was not completely devoid of designer input: reference designs may need to be adapted for the specific application through parts selection and component sizing. Quality and trust were also barriers to direct re-use: for example, worries about the quality of random Internet parts libraries or quirks in unofficial organization-wide reference designs.

Overall, attitudes about schematic entry were less positive:

It's more of a necessarily evil. I wouldn't say it's a bad thing or a good thing, it's just like, I need to do this because otherwise I can't get my board. (P03)

#### **Board Layout**

Participant concerns during this phase were also low level and often related to the physical design and the final product: mechanical integration, signal integrity, manufacturability, and cost.

Despite both schematic capture and layout being part of the same EDA suite and schematic import being a common feature in layout tools, moving between schematic and layout was a notable source of friction. Five participants complained about the initial placement of components in layout:

Altium kind of just barfs it out in a, not stacked on top of each other, but there's really not a lot of rhyme or reason. [...] It all seems pretty random. (P11)

Updating a layout after a schematic modification was also noted as problematic.

Participants also frequently consulted datasheets, placement rules, and routing guidelines during this step. While parts libraries and design guidelines could be shared between projects, layout re-use was rare. This was a result of limited tool support and projects needing customized layouts.

#### Parts Selection

Parts selection happened throughout the other stages of the design process. For example, critical parts may be specified on the block diagram, while common parts like resistors may not be picked until just before ordering.

Concerns varied widely. Eight participants mentioned optimizing for cost, while anther worked in a price-insensitive industry. Three also preferred parts that were immediately available in their makerspace or research lab. Otherwise, there was a long tail of other concerns, including hand-solderability, stocking, RoHS compliance, or avoiding vendors in organization-wide blacklists.

Overall, this phase could require significant manual work and was deceptively difficult:

It's something that I find to be challenging and I think that people underestimate,

[...] everyone's like, "eh, whatever, you're just buying stuff" and then they realize

like "oh, actually, just buying stuff is not super easy". (P05)

#### Iteration

As alluded to throughout, many concerns do not fit purely within one design phase. For example, participants mentioned going back and forth between layout and schematic to optimize pin assignments for routing, or redesigning the schematic to work around unavailable parts.

In general, while later steps are dependent on the results of earlier steps, those results are not always locked down. As an extreme example, one participant recalls being told:

Hey, you made this great device to guarantee these specs, but we really need this new part and it kind of breaks the spec that we gave you before. Deal with it. (P12)

One strategy participants used to deal with this was defensive design. This included defending against mistakes and errors, such as by inserting optional jumpers between subcircuits to allow modification or removal of connections, and defending against specification changes, such as by picking a microcontroller with a wide peripheral set for flexibility.

#### Use of Automation

Participants talked about their experiences using automation features provided by their tools. These features aim to minimize errors and ease tedious tasks, and fell into the broad categories of design verification and routing assistance.

#### **Design Verification**

EDA suites generally include electrical rules check (ERC), which checks schematics for common issues, and design rules check (DRC), which checks layouts for manufacturability.

ERC is commonly implemented by assigning pin classes (for example: input, output, or bidirectional) and defining a matrix of legal connections. Opinions were varied: six mentioned using this feature (all with caveats), while five specifically mentioned not using it. While electrical rules checking has utility in catching some simple mistakes like unconnected wires, the limitations were significant:

A lot of false negatives. And false positives. Very few true positives. (P07)

On the other hand, no one mentioned skipping layout-versus-schematic or DRC, both of which are generally very accurate. Complaints were limited to bugs, like not catching split ground planes.

#### **Routing Assistance**

Only two participants reported using autorouting, all limited to simple designs. The general view was that the benefits were not worth the time costs of setting up the job properly or fixing poor results.

However, mixed-initiative, assistive routing features were well-received. These include online or interactive DRC, which does manufacturability checks on traces as they are placed, and smart routing tools like push-and-shove, which allow the trace being placed to intelligently displace existing traces.

The auto routers are [terrible], the auto placements are [terrible]. It's a highly manual process. I like push and shove routing, those are great. (P12)

#### **Tool Selection**

We also asked participants about why they chose their particular EDA suite. Community effects dominated: their choices were influenced by the tools used by their friends or teams,

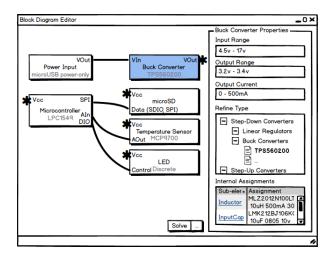

Figure 4.2: Mockup of the block diagram interface, showing the system architecture of the datalogger example design. The details pane on the right shows information on the selected buck converter: modeled operating parameters, selected and alternate implementations, and parts selections internal to the block. Showing operating parameters demonstrates how the system ensures design correctness.

the tools taught in class, and the existence of an ecosystem of tutorials and libraries. For those in industry, widespread usage was also important for compatibility with contractors and ease of hiring.

Those using or switching to KiCad noted the benefits of open-source software, such as lack of vendor lock-in, ease of sharing, and perpetual access to designs.

#### Summary

Overall, our main takeaway is that much of the interesting and creative work happens through a combination of system architecture and parts selection. Past that, schematic capture tends towards elaborating the system architecture by mashing in reference circuits, but the lack of design re-use results in a tedious and time-consuming process.

Links across steps are also major sources of friction. While converting a paper system architecture into a digital schematic is burdensome but unavoidable, moving between schematic, layout, and parts selection was just frustrating.

# 4.5 Concept Design

The core insight from the interviews, then, is for designers to work at the system architecture level. This higher level of abstraction captures the essential design intent without being mired in implementation details. This section presents the high-level design and motivation, and the actual implementation is described in Chapters 5 and 6.

Note that this strategy has support in the creativity support tools literature [67], satisfying the principles of *supporting exploration* by reducing the design effort and *designing for designers* by being grounded in actual workflows.

#### Ambiguity in Block Diagrams

As schematics are fundamentally also block diagrams, the interactions and interfaces from today's schematic capture tools provide a solid and familiar starting point. In our use case, these block diagrams would also need to scale between multiple levels of abstraction. At the lowest level, blocks would still represent individual components, but at higher levels, blocks would be sub-circuits. While many tools already support this with the notion of *hierarchy blocks*, additional features are necessary to support the system architecture level of design.

Primarily, we need support for ambiguity. While current schematics must be fully defined down to the last part, system architecture diagrams in our interviews tended to encode minimalist design intent, leaving many decisions open. An example would be labeling a block generically as "accelerometer" instead of with a specific part number.

This ambiguity further provides opportunities for tools to automate the currently-manual and sometimes-tedious parts selection process. Recent work in synthesizing schematic from high-level specifications, including EDG [65] and Trigger-Action-Circuits [3] demonstrate the technological feasibility of this approach. As participants generally optimized for some criteria (commonly, but not always, cost) during their parts selection process, tools should also optimize for an user-defined objective function. Alternatively, the system could generate and display a shortlist of alternatives as in Trigger-Action-Circuits, though they reported mixed results with their novice participants.

An underlying constraint-based data model, as described in EDG, works well here. Types of components, like "accelerometer", would be just one aspect that could be constrained. More powerfully, such a system allows users to directly enter functional specifications, such as the minimum required bandwidth of said accelerometer. This also gracefully handles nonuniform ambiguity, which we observed from diagrams containing a mix of generic blocks as well as specific part numbers.

#### Supporting Libraries