### UNIVERSITY OF CALIFORNIA SAN DIEGO

End-to-End Inference Optimization for Deep Learning-based Image Upsampling Networks

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

Electrical Engineering (Machine Learning and Data Science)

by

Ian Colbert

### Committee in charge:

Professor Kenneth Kreutz-Delgado, Chair Professor Alexander Cloninger Professor Srinjoy Das Professor Truong Nguyen Professor Nuno Vasconcelos

Copyright

Ian Colbert, 2023

All rights reserved.

| The Dissertation of Ian Colbert is approved, and it is acceptable in quality and |

|----------------------------------------------------------------------------------|

| form for publication on microfilm and electronically.                            |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

University of California San Diego

2023

## **DEDICATION**

To my family.

## **EPIGRAPH**

| If you don't have time to do it right, when will you have time to do it over?                  |

|------------------------------------------------------------------------------------------------|

| John Wooden                                                                                    |

|                                                                                                |

|                                                                                                |

|                                                                                                |

| Achievement is just a moment in pencil unless you can share it with the people you care about. |

| Scott Galloway                                                                                 |

|                                                                                                |

|                                                                                                |

## TABLE OF CONTENTS

| Disserta  | tion Ap    | proval Page                                    | iii  |

|-----------|------------|------------------------------------------------|------|

| Dedicati  | ion        |                                                | iv   |

| Epigrap   | h          |                                                | v    |

| Table of  | Conten     | ts                                             | vi   |

| List of F | Figures    |                                                | ix   |

| List of T | Tables     |                                                | xi   |

| List of A | Algorith   | ms                                             | xii  |

| Acknow    | ledgem     | ents                                           | xiii |

| Vita      |            |                                                | XV   |

| Abstract  | t of the l | Dissertation                                   | xvii |

| Chapter   | 1 In       | ntroduction                                    | 1    |

| Chapter   |            | nteger-Quantized Neural Networks               | 6    |

| 2.1       |            | action                                         | 7    |

| 2.2       |            | d Works                                        | 9    |

| 2.3       | Backg      | round                                          | 10   |

|           | 2.3.1      | Quantization-Aware Training (QAT)              | 11   |

|           | 2.3.2      | Weight Normalization                           | 12   |

| 2.4       |            | ation                                          | 13   |

|           | 2.4.1      | Generating Streaming Architectures with FINN   | 13   |

|           | 2.4.2      | Accumulator Impact on Resource Utilization     | 14   |

| 2.5       |            | nulator Bit Width Bounds                       | 16   |

|           | 2.5.1      | Deriving Lower Bounds Using Data Types         | 17   |

|           | 2.5.2      | Deriving Lower Bounds Using Learned Weights    | 18   |

| 2.6       | Trainir    | ng Quantized Neural Networks to Avoid Overflow | 19   |

|           | 2.6.1      | Constructing Our Quantization Operator         | 19   |

|           | 2.6.2      | Regularization with Lagrangian Penalties       | 21   |

| 2.7       | Experi     | ments                                          | 22   |

|           | 2.7.1      | Image Classification Benchmarks                | 23   |

|           | 2.7.2      | Single-Image Super Resolution Benchmarks       | 24   |

|           | 2.7.3      | Experiment Setup and Research Questions        | 24   |

|           | 2.7.4      | Accumulator Impact on Model Performance        | 27   |

|           | 2.7.5      | Trade-Offs Between Resources and Accuracy      | 28   |

|           | 2.7.6      | Evaluating Resource Savings                    | 29   |

|         | 2.7.7 A Deeper Look at the Impact of Our Constraints            | 30 |

|---------|-----------------------------------------------------------------|----|

| 2.8     | Conclusions and Future Work                                     | 31 |

| Chapter | 3 Low-Precision Structured Subnetworks                          | 34 |

| 3.1     | Introduction                                                    | 35 |

| 3.2     | Background                                                      | 38 |

|         | 3.2.1 Pruning                                                   | 38 |

|         | 3.2.2 Quantization                                              | 39 |

| 3.3     | Motivation                                                      | 42 |

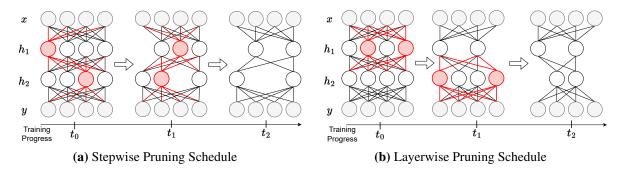

| 3.4     | Algorithms                                                      | 47 |

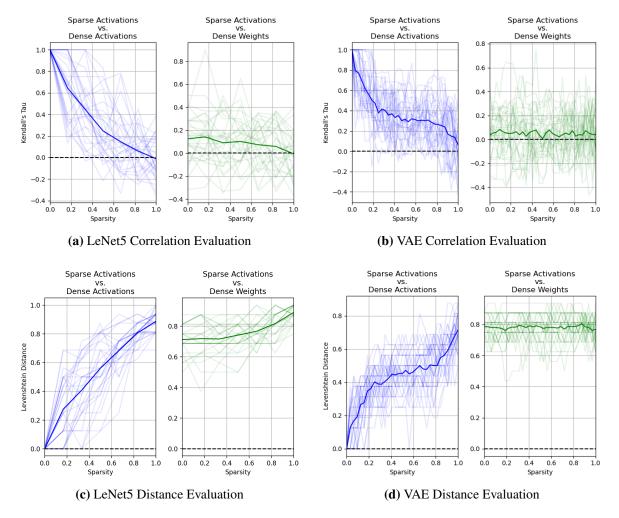

|         | 3.4.1 Layerwise Channel Pruning using Non-parametric Statistics | 47 |

|         | 3.4.2 Uniform Quantization-Aware Training                       | 49 |

| 3.5     | Experiments                                                     | 51 |

|         | 3.5.1 Evaluating Pruning Schedules and Importance Measures      | 52 |

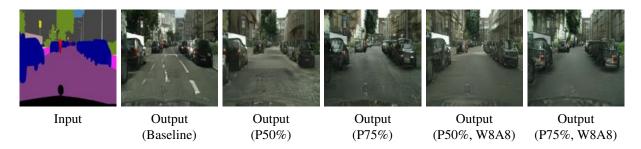

|         | 3.5.2 Evaluation of Joint Pruning and Quantization              | 54 |

| 3.6     | Conclusions and Future Work                                     | 57 |

| Chapter | 4 Unified Quantization and Pruning                              | 60 |

| 4.1     | Introduction                                                    | 61 |

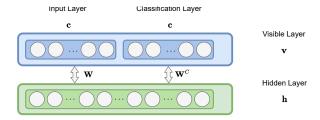

| 4.2     | Discriminative Deep Belief Networks (DDBNs)                     | 64 |

|         | 4.2.1 Discriminative Restricted Boltzmann Machines              | 64 |

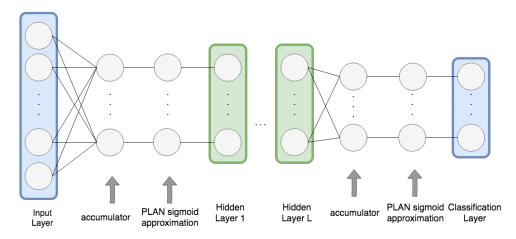

|         | 4.2.2 Discriminative Deep Belief Networks                       | 67 |

|         | 4.2.3 Network Architecture                                      | 68 |

| 4.3     | Limited Precision and Function Approximation                    | 69 |

|         | 4.3.1 Limited Precision Approximation                           | 69 |

|         | 4.3.2 Sigmoid Function Approximation                            | 69 |

| 4.4     | Neuron Ordering using Criticality Analysis                      | 71 |

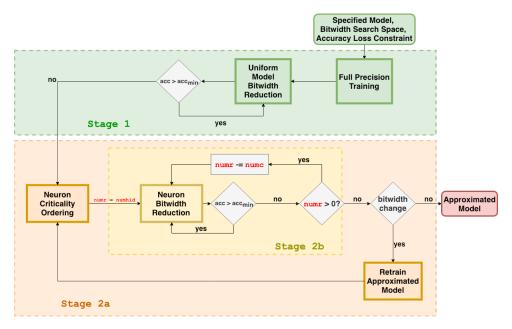

| 4.5     | AX-DBN Design Metholodogy                                       | 73 |

|         | 4.5.1 Cloud-based Model Training and Approximation              | 73 |

|         | 4.5.2 Inference on Embedded Hardware                            | 74 |

| 4.6     | Power Model for Compute and Memory Requirements                 | 75 |

| 4.7     | Experimental Results                                            | 76 |

| 4.8     | Conclusions                                                     | 77 |

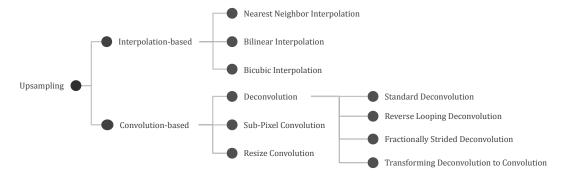

| Chapter |                                                                 | 84 |

| 5.1     | Introduction                                                    | 84 |

| 5.2     | Sub-Pixel Convolution                                           | 86 |

| 5.3     | Resize Convolution                                              | 86 |

| 5.4     | Deconvolution                                                   | 88 |

|         | 5.4.1 Reverse Looping Deconvolution                             | 89 |

|         | 5.4.2 Fractionally Strided Deconvolution                        | 90 |

|         | 5.4.3 Transforming Deconvolution to Convolution                 | 91 |

|         | 5.4.4 Comparison of Compute and Memory Requirements             | 92 |

| 5.5     | Improving Reverse Looping Deconvolution                         | 93 |

| 5.6      | Conclusions                                                  | 95  |

|----------|--------------------------------------------------------------|-----|

| Chapter  | 6 Kernel Transforms, Layer Fusions, and Time-Energy Analysis | 97  |

| 6.1      | Introduction                                                 | 98  |

| 6.2      | Related Works                                                | 100 |

| 6.3      | Deep Learning-based Image Upsampling at the Edge             | 102 |

| 6.4      | Kernel Transformations                                       | 104 |

|          | 6.4.1 Sub-Pixel Convolution to Deconvolution                 | 105 |

|          | 6.4.2 Resize Convolution to Deconvolution                    | 107 |

| 6.5      | Time and Energy Analysis at Inference                        | 109 |

|          |                                                              | 110 |

|          | 6.5.2 Estimating Energy Efficiency by Data Reuse             | 114 |

|          | 6.5.3 Roofline Models of Time and Energy                     | 115 |

| 6.6      | Results of Quantitative Analysis                             | 116 |

| 6.7      | Conclusions and Future Work                                  | 120 |

| Chapter  | 7 Hardware Acceleration for Deconvolution Inference          | 126 |

| 7.1      | Introduction                                                 | 127 |

| 7.2      | Related Works                                                | 128 |

| 7.3      | Deconvolution Algorithm                                      | 129 |

| 7.4      | FPGA Hardware Architecture                                   | 132 |

| 7.5      | Experimental Results                                         | 133 |

|          |                                                              | 134 |

|          | 7.5.2 Performance-per-Watt Comparison with Edge GPU          | 135 |

|          |                                                              | 136 |

| 7.6      | Conclusions and Future Work                                  | 137 |

| Chapter  | 8 Conclusion                                                 | 139 |

| Ribliogr | anhv                                                         | 141 |

## LIST OF FIGURES

| Figure 1.1. | End-to-end inference optimization pipeline                            | 4  |

|-------------|-----------------------------------------------------------------------|----|

| Figure 2.1. | Illustration of fixed-point arithmetic in QNN inference               | 9  |

| Figure 2.2. | Overview of the FINN framework                                        | 12 |

| Figure 2.3. | Accumulator bit width impact on LUT utilization                       | 13 |

| Figure 2.4. | Visualizing our derived accumulator bit width bounds                  | 19 |

| Figure 2.5. | Trade-offs between accumulator bit width and model quality            | 22 |

| Figure 2.6. | Trade-offs between accumulator bit width and LUT utilization          | 25 |

| Figure 2.7. | LUT utilization break down across Pareto fronts                       | 27 |

| Figure 2.8. | Visualizing impact of $\ell_1$ -norm constraints on sparsity          | 31 |

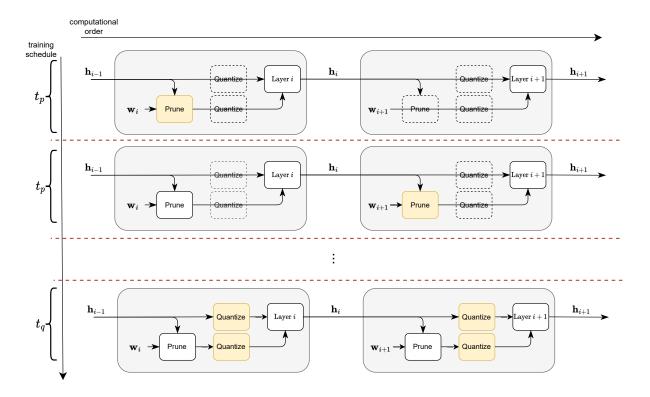

| Figure 3.1. | Joint layerwise channel pruning and uniform quantization              | 37 |

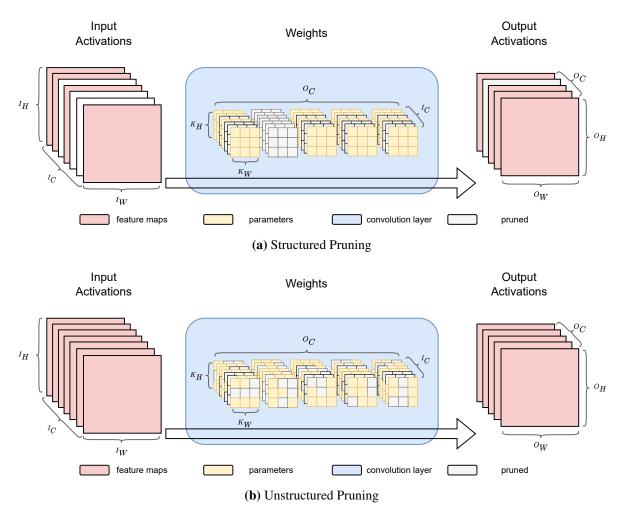

| Figure 3.2. | Structured and unstructured pruning                                   | 40 |

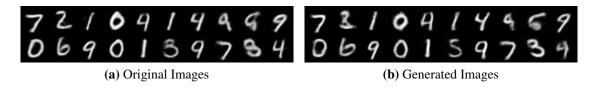

| Figure 3.3. | Visualizing images generated from VAE                                 | 44 |

| Figure 3.4. | Visualizing impact of input activation sparsity on importance metrics | 46 |

| Figure 3.5. | Stepwise and layerwise pruning schedules                              | 50 |

| Figure 3.6. | Visualizing images generated from quantized and pruned CycleGAN       | 52 |

| Figure 4.1. | Illustration of edge computing paradigm for deep learning             | 62 |

| Figure 4.2. | Discriminative restricted Boltzmann machine                           | 64 |

| Figure 4.3. | Discriminative deep belief network                                    | 68 |

| Figure 4.4. | Approximating deep belief networks                                    | 70 |

| Figure 4.5. | Illustration of our proposed approximate computing framework          | 73 |

| Figure 4.6. | Proposed hardware inference path for deep belief networks             | 76 |

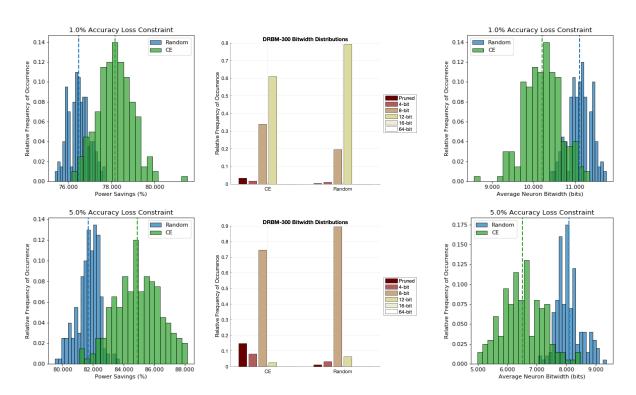

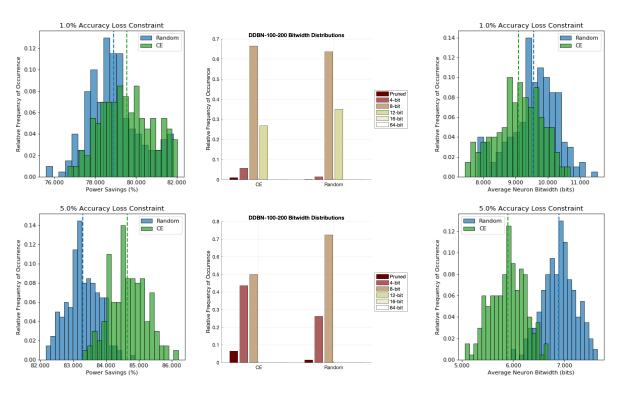

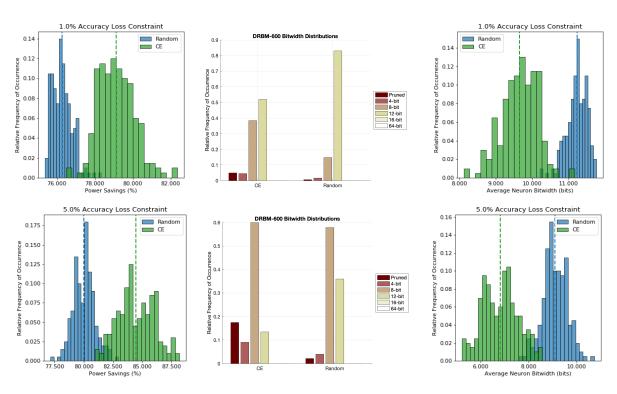

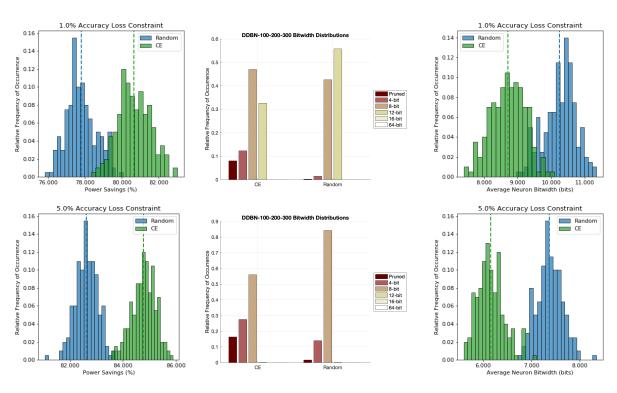

| Figure 4.7. | Visualizing results for DRBM-300                                      | 80 |

| Figure 4.8. | Visualizing results for DDBN-100-200                                  | 81 |

| Figure 4.9.  | Visualizing results for DRBM-600                                | 82  |

|--------------|-----------------------------------------------------------------|-----|

| Figure 4.10. | Visualizing results for DDBN-100-200-300                        | 83  |

| Figure 5.1.  | The image upsampling taxonomy                                   | 86  |

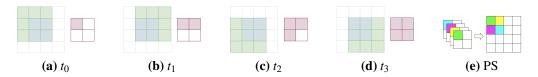

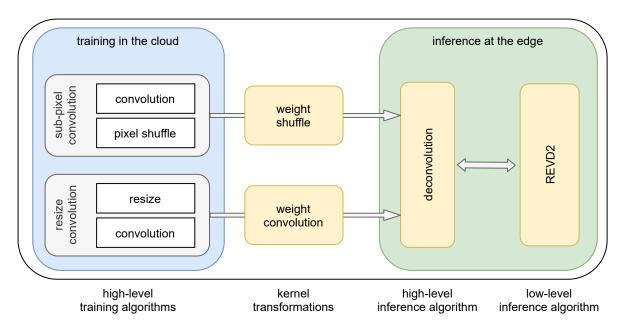

| Figure 5.2.  | Visualizing the sub-pixel convolution                           | 87  |

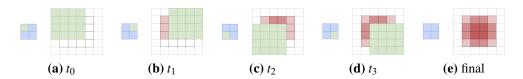

| Figure 5.3.  | Visualizing the nearest neighbor resize convolution             | 88  |

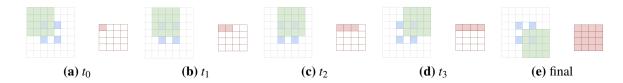

| Figure 5.4.  | Visualizing the standard deconvolution                          | 89  |

| Figure 5.5.  | Visualizing the fractionally strided deconvolution              | 91  |

| Figure 5.6.  | Visualizing overheads for variant deconvolution algorithms      | 93  |

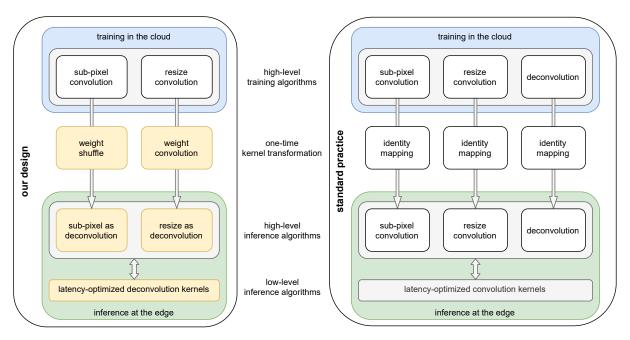

| Figure 6.1.  | Deploying image upsampling networks for inference at the edge   | 99  |

| Figure 6.2.  | Edge computing paradigm for image upsampling                    | 102 |

| Figure 6.3.  | An example use case for kernel transformations                  | 104 |

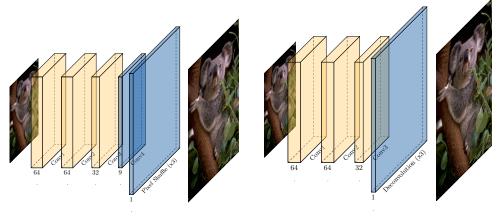

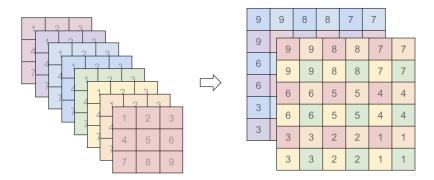

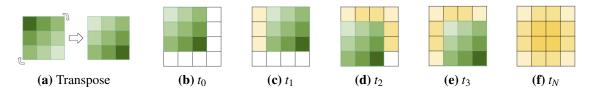

| Figure 6.4.  | Visualizing our weight shuffle algorithm                        | 107 |

| Figure 6.5.  | Visualizing our weight convolution algorithm                    | 110 |

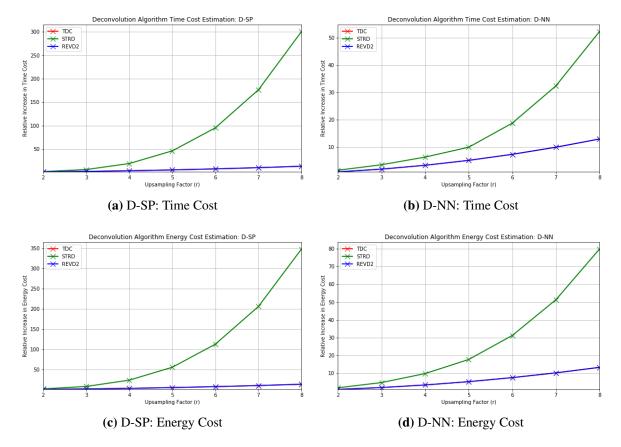

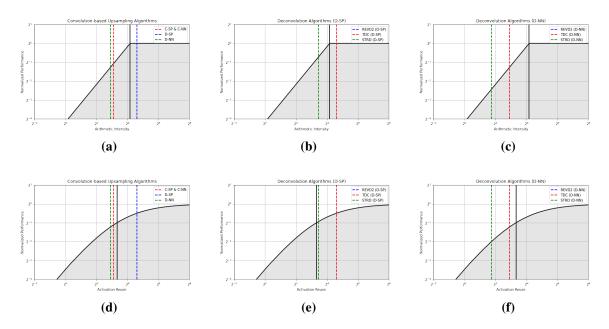

| Figure 6.6.  | Time and energy costs of deconvolution variants                 | 122 |

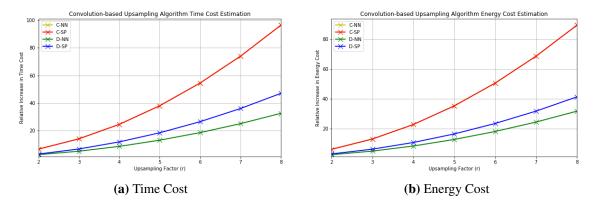

| Figure 6.7.  | Time and energy costs of transformed upsampling algorithms      | 123 |

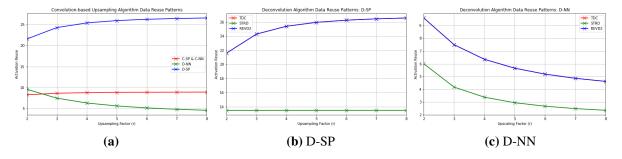

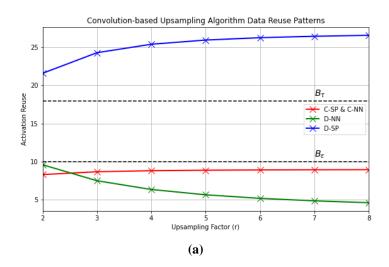

| Figure 6.8.  | Activation reuse of transformed upsampling algorithms           | 123 |

| Figure 6.9.  | Roofline models of time and energy                              | 124 |

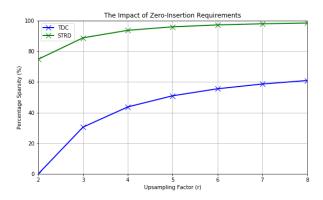

| Figure 6.10. | Visualizing algorithm scalability                               | 125 |

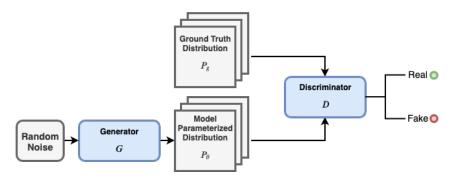

| Figure 7.1.  | Generative adversarial network architecture                     | 128 |

| Figure 7.2.  | Reverse looping deconvolution algorithm                         | 129 |

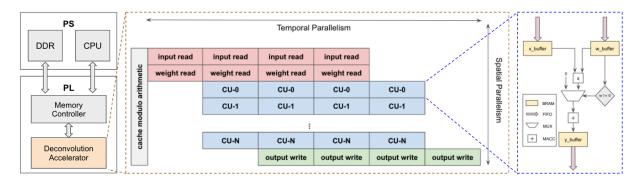

| Figure 7.3.  | Exploiting deconvolution dataflow with fine-grained parallelism | 132 |

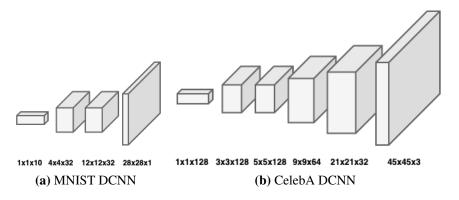

| Figure 7.4.  | Example network architectures for inference acceleration        | 133 |

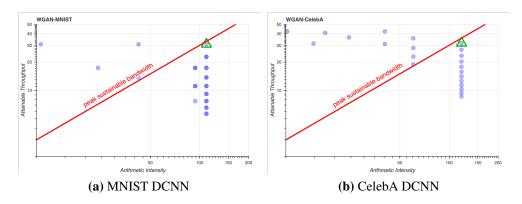

| Figure 7.5.  | Design space exploration                                        | 134 |

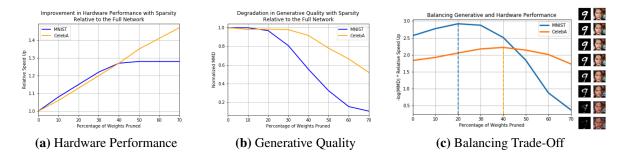

| Figure 7.6.  | Trade-offs between generative quality and hardware performance  | 136 |

## LIST OF TABLES

| Table 3.1. | Comparing pruning schedules                                          | 55  |

|------------|----------------------------------------------------------------------|-----|

| Table 3.2. | Comparing neuron importance metrics                                  | 55  |

| Table 3.3. | Results from joint pruning and quantization                          | 56  |

| Table 3.4. | Evaluating performance-per-memory footprint                          | 58  |

| Table 4.1. | Results for activation function approximation                        | 70  |

| Table 4.2. | Uniform bit width reduction results                                  | 79  |

| Table 4.3. | Mixed-precision results with 1% accuracy loss constraint             | 79  |

| Table 4.4. | Mixed-precision results with 5% accuracy loss constraint             | 80  |

| Table 5.1. | Compute and memory requirements of variant deconvolution algorithms  | 92  |

| Table 6.1. | Capabilities of assumed hardware target                              | 112 |

| Table 6.2. | Compute and memory requirements of transformed upsampling algorithms | 114 |

| Table 7.1. | Resource utilization                                                 | 135 |

| Table 7.2. | Evaluating throughput-to-power ratio                                 | 135 |

## LIST OF ALGORITHMS

| Algorithm 1.  | Layerwise channel pruning                                    | 48  |

|---------------|--------------------------------------------------------------|-----|

| Algorithm 2.  | Adaptive asymmetric activation quantization                  | 50  |

| Algorithm 3.  | Adaptive symmetric weight quantization                       | 51  |

| Algorithm 4.  | AX-DBN approximation algorithm                               | 75  |

| Algorithm 5.  | Standard convolution                                         | 87  |

| Algorithm 6.  | Pixel shuffle                                                | 88  |

| Algorithm 7.  | Standard deconvolution                                       | 89  |

| Algorithm 8.  | Reverse looping deconvolution (REVD)                         | 90  |

| Algorithm 9.  | Transforming deconvolution to convolution (weight transform) | 92  |

| Algorithm 10. | Improved reverse looping deconvolution (REVD2)               | 95  |

| Algorithm 11. | Weight shuffle                                               | 106 |

| Algorithm 12. | Weight convolution                                           | 109 |

| Algorithm 13. | Reverse looping deconvolution dataflow                       | 130 |

#### **ACKNOWLEDGEMENTS**

I would like to first acknowledge Professor Srinjoy Das, who has been a mentor, colleague, and friend throughout the entirety of my academic journey. I would like to acknowledge Professor Kenneth Kreutz-Delgado whose support, guidance, and wisdom have helped shape many of the key ideas in this work as well as my overall approach to research. I am honored to also have Professor Alex Cloninger, Professor Truong Nguyen, and Professor Nuno Vasconcelos serve on my doctoral committee. Their feedback and advice have been valuable assets.

I am grateful to the many colleagues I have worked beside at the University of California San Diego, and Advanced Micro Devices, Inc. This endeavor would not have been possible without their constructive discourse, late-night feedback sessions, and moral support. Lastly, I would be remiss in not mentioning my family and loved ones. Their constant support and unyielding belief have helped me in an immeasurable way.

Although this dissertation lists only one author, in reality, the ideas are a collection of contributions synthesized and refined through collaboration with many insightful colleagues.

Chapter 2 is based on unpublished material (Ian Colbert, Alessandro Pappalardo, and Jakoba Petri-Koenig, "Quantized Neural Networks for Low-Precision Accumulation with Guaranteed Overflow Avoidance"). The dissertation author was the primary investigator and author of this paper.

Chapter 3 is based on material as it appears in the 2022 MDPI Applied Sciences Special Issue on Hardware-Aware Deep Learning (Xinyu Zhang, Ian Colbert, and Srinjoy Das, "Learning Low-Precision Structured Subnetworks Using Joint Layerwise Channel Pruning and Uniform Quantization"). The dissertation author was a co-primary investigator and author of this paper.

Chapter 4 is based on material as it appears in the 2019 International Joint Conference on Neural Networks (Ian Colbert, Kenneth Kreutz-Delgado, and Srinjoy Das, "AX-DBN: An Approximate Computing Framework for the Design of Low-Power Discriminative Deep Belief Networks"). The dissertation author was the primary investigator and author of this paper.

Chapters 5 and 6 are based on material as it appears in the 2021 IEEE Access Journal

(Ian Colbert, Kenneth Kreutz-Delgado, and Srinjoy Das, "An Energy-Efficient Edge Computing Paradigm for Convolution-Based Image Upsampling"). The dissertation author was the primary investigator and author of this paper.

Chapter 7 is based on unpublished material (Ian Colbert, Jake Daly, Kenneth Kreutz-Delgado, and Srinjoy Das, "A Competitive Edge: Can FPGAs Beat GPUs at DCNN Inference Acceleration in Resource-Limited Edge Computing Applications?"). The dissertation author is the primary investigator and author of this paper.

#### VITA

| 2017         | Bachelor of Science, University of California San Diego  |

|--------------|----------------------------------------------------------|

| 2018-Present | Software Engineer, Advanced Micro Devices, Inc.          |

| 2019         | Master of Science, University of California San Diego    |

| 2023         | Doctor of Philosophy, University of California San Diego |

#### **PUBLICATIONS**

**Ian Colbert**, Kenneth Kreutz-Delgado, and Srinjoy Das. "AX-DBN: An Approximate Computing Framework for the Design of Low-Power Discriminative Deep Belief Networks," 2019 International Joint Conference on Neural Networks, pp. 1-9.

Alexander Potapov, **Ian Colbert**, Kenneth Kreutz-Delgado, Alexander Cloninger, and Srinjoy Das. "PT-MMD: A Novel Statistical Framework for the Evaluation of Generative Systems," 2019 53rd Asilomar Conference on Signals, Systems, and Computers, pp. 2219-2223.

**Ian Colbert**, Jake Daly, Kenneth Kreutz-Delgado, and Srinjoy Das. "A Competitive Edge: Can FPGAs Beat GPUs at DCNN Inference Acceleration in Resource-Constrained Edge Computing Applications?" arXiv preprint:2102.00294, 2021.

Siqiao Ruan, **Ian Colbert**, Ken Kreutz-Delgado, Srinjoy Das. "Generative and Discriminative Deep Belief Network Classifiers: Comparisons Under an Approximate Computing Framework," arXiv preprint:2102.00534, 2021.

**Ian Colbert**, Kenneth Kreutz-Delgado, and Srinjoy Das. "An Energy-Efficient Edge Computing Paradigm for Convolution-Based Image Upsampling," in IEEE Access, vol. 9, pp. 147967-147984, 2021.

**Ian Colbert**, Jake Daly, Norm Rubin. "Generating GPU Compiler Heuristics Using Reinforcement Learning," arXiv preprint:2111.12055, 2021.

Xinyu Zhang, **Ian Colbert**, Kenneth Kreutz-Delgado. "Learning Low-Precision Structured Subnetworks Using Joint Layerwise Channel Pruning and Uniform Quantization," Applied Sciences. 2022; 12(15):7829.

**Ian Colbert** and Mehdi Saeedi. "Evaluating Navigation Behavior of Agents in Games using Non-Parametric Statistics," 2022 IEEE Conference on Games, pp. 544-547.

Alexander Cann, **Ian Colbert**, Ihab Amer. "Robust Transferable Feature Extractors: Learning to Defend Pre-Trained Networks Against White Box Adversaries," arXiv preprint:2209.06931, 2022.

**Ian Colbert**, Alessandro Pappalardo, Jakoba Petri-Koenig. "Quantized Neural Networks for Low-Precision Accumulation with Guaranteed Overflow Avoidance," arXiv preprint:2301.13376, 2023.

### ABSTRACT OF THE DISSERTATION

End-to-End Inference Optimization for Deep Learning-based Image Upsampling Networks

by

### Ian Colbert

Doctor of Philosophy in Electrical Engineering (Machine Learning and Data Science)

University of California San Diego, 2023

Professor Kenneth Kreutz-Delgado, Chair

Many computer vision problems require image upsampling, where the number of pixels per unit area is increased by inferring values in high-dimensional image space from low-dimensional representations. Recent research has shown that deep learning-based solutions achieve state-of-the-art performance on such tasks by training deep neural networks (DNNs) on large annotated datasets. Yet, their adoption in real-time applications is predicated on the deployment costs of the resulting models since end-user devices impose significant compute and memory constraints on inference pipelines. To address this, many researchers and practitioners

have proposed methods to reduce inference costs without sacrificing model quality. However, many of these works focus on DNNs designed for image downsampling. In this thesis, we study inference optimization techniques designed for deep learning-based image upsampling networks. While some inference optimizations are applicable to both upsampling and downsampling networks, we show that specifically tailoring optimizations for image upsampling workloads can lead to more efficient and effective deployment.

We maintain a holistic view of inference optimization, from training through deployment to execution, by integrating hardware-aware deep learning techniques, compute graph transformations, and computer architecture optimizations into an end-to-end pipeline. We begin by characterizing this pipeline and the different requirements for image upsampling and downsampling workloads. We then introduce novel statistical approaches to hardware-aware deep learning techniques based on quantization and pruning. Once trained, we then introduce novel compute kernels and graph transformations that reduce the compute costs of common upsampling workloads by up to a factor of 3.3. Finally, we adapt our novel inference algorithms to a specialized hardware architecture that reduces resource utilization and improves dataflow on FPGA-based accelerators.

We evaluate a wide range of computer vision benchmarks covering both stochastic and deterministic models to show that our approaches improve power efficiency, throughput, and resource utilization without damaging model quality. Our research highlights the importance of end-to-end inference optimization for deep learning-based image upsampling networks and provides an effective solution for reducing the deployment costs of DNNs designed for real-time computer vision applications on resource-constrained platforms.

# Chapter 1

## Introduction

Since the success of deep convolutional neural networks in the 2012 ILSVRC Computer Vision Challenge [94,99,138], deep learning has become the primary approach to developing state-of-the-art solutions for many prominent computer vision problems (*e.g.*, image classification [66,77], scene segmentation [52,106], and object detection [65,133]). Over the past decade, numerous architectural variations have been proposed, each with unique benefits and capabilities [66,77,89,134,136,144]. As the availability of both data and computation has increased, both the size and quality of these models have scaled [69], resulting in widespread adoption across real-world applications including smart cities [12], medical imaging [49], and industrial robotics [172].

Many emerging computer vision applications, however, require real-time inference (*e.g.*, autonomous driver assistance systems [50,146] and high-fidelity rendering [88,149]). Thus, deep learning models are increasingly being moved closer to their data sources to run inference directly on end-user devices at the edge [44]. This migration reduces strain on network bandwidth and decreases system latency by removing any reliance on internet connectivity. However, it also imposes significant constraints on the inference pipeline since edge devices have form-factor and cost considerations that limit power budgets, compute capabilities, and memory storage [33,44]. These constraints make it challenging to deploy state-of-the-art models for real-time inference on edge devices as the compute and memory requirements of large models often exceed the

capabilities of such platforms [53, 63].

To address the rising inference costs, researchers and practitioners have introduced hardware, software, and algorithmic optimizations in the pursuit of minimizing the trade-offs between hardware performance and model quality [2, 35, 54, 63, 75, 81, 176, 179, 183, 191]. The resulting body of work surrounding inference optimization research has rapidly expanded to cover many modalities ranging from images [33, 81, 149] to natural language [55, 165, 179], all with a shared goal of minimizing hardware costs while maintaining model quality. We have focused our attention on computer vision applications, where we have observed inference optimization research to be heavily skewed towards image downsampling workloads [2, 35, 61, 62, 75, 86, 97, 111, 117], leaving the optimization of image upsampling workloads an open challenge approached by few [23, 33, 161, 177].

Many recent state-of-the-art neural architectures have increasingly employed image upsampling [74, 89, 134, 136, 144], where the number of pixels per unit area (*i.e.*, resolution) is increased by inferring values in high-dimensional image space from low-dimensional representations. This class of architectures, which we refer to as *deep learning-based image upsampling networks*, is now commonly used to train models for tasks such as super resolution [144, 149], image generation [57,74,89], and style transfer [134,190]. In contrast to downsampling, which is a many-to-one mapping used to extract or encode high-level features from an image by reducing dimensionality, upsampling is a one-to-many mapping used to infer or recover information in an image by increasing dimensionality. The differences in these workloads present unique and interesting inference optimization problems. While some inference optimization techniques are applicable to both upsampling and downsampling workloads, we show that specifically tailoring optimizations for image upsampling workloads can lead to more efficient and effective deployment of deep learning-based image upsampling networks.

To demonstrate one aspect of these differences, let us compare the weight and activation requirements of common downsampling and upsampling networks assuming 32-bit floating-point implementations. When trained on CIFAR10 [93], LeNet5 [100] requires roughly 248 KB for

weights and 38 KB for activations. Conversely, when trained for Set5 [14], ESPCN [144] requires roughly 239 KB for weights and 7 MB for activations, nearly 180x more activations than LeNet5 with 4% fewer weights. Let us additionally consider large-scale models. When trained for ImageNet [42], ResNet50 [66] requires roughly 102 MB for weights and 31 MB for activations. Conversely, when trained on DIV2K [5], U-Net [136] requires roughly 45 MB for weights and 1.4 GB for activations, nearly 46x more activations than ResNet50 with 56% fewer weights. This is in large part because image upsampling applications often have higher dimensional inputs when compared to their downsampling counterparts, which is only exacerbated by the expanding output fields [33]. Such differences often render image upsampling workloads memory-bound, where optimizations that improve dataflow and reduce memory requirements can yield substantial gains [33].

We study inference optimization techniques designed for deep learning-based image upsampling networks. Since their benefits often depend on the characteristics of the deep learning workload and the capabilities of the target hardware, maximally exploiting inference optimizations often requires aggressive hardware-software (HW-SW) co-design. For example, unstructured weight pruning can offer high compression rates with minimal accuracy degradation due to its inherent topological flexibility [51,63]; however, such flexibility results in irregular sparsity patterns that lead to poor data locality and can result in low hardware efficiency if not exploited by sparse inference kernels [54] or specialized hardware accelerators [23,31,122]. In an effort to fully exploit our contributions, we maintain a holistic view of inference optimization, integrating hardware-aware deep learning techniques, compute graph transformations, and specialized hardware accelerators into an end-to-end pipeline.

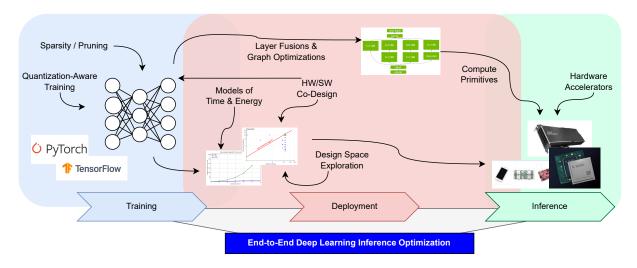

We visualize our inference optimization pipeline in Fig. 1.1, where we split the process into three stages: training, deployment, and inference. We first use hardware-aware deep learning techniques based on quantization and pruning to train our models to take advantage of the hardware characteristics of a specific platform (described in Chapters 2, 3, and 4). While we consider both general-purpose platforms and programmable hardware, we primarily study

**Figure 1.1.** A high-level flow diagram of our end-to-end inference optimization pipeline.

deployment on FPGA-based accelerators as they can take advantage of fine-grained parallelism and custom data types to a greater extent [34]. Given the trained model, we introduce novel graph transformations and compute kernels (described in Chapters 5 and 6, respectively) that reduce the compute costs of common image upsampling workloads by up to a factor of 3.3. We then adapt our novel image upsampling algorithm to an FPGA-based accelerator (described in Chapter 7). Finally, we conclude with additional deployment considerations as well as implications for broader impact. The contributions of our work are summarized as follows:

- 1. In Chapter 2, we introduce a novel quantization-aware training algorithm that constrains an integer-quantized neural network to use a low-precision accumulator without numerical overflow while inherently increasing the sparsity of the resulting weights.

- 2. In Chapter 3, we introduce a data-driven structured weight pruning algorithm that uses non-parametric measures of importance to greedily remove redundant channels in quantized neural networks trained for computer vision applications.

- 3. In Chapter 4, we introduce a systematic approximation framework that optimizes the power consumption of stochastic neural networks using a unified pruning and quantization formulation guided by surrogate measures of neuron criticality.

- 4. In Chapter 5, we introduce a novel deconvolution inference algorithm that exposes more opportunities for concurrent execution to improve adaptability to resource-constrained settings.

- 5. In Chapter 6, we introduce novel graph transformations that can significantly reduce the data movement costs of common image upsampling workloads.

- 6. In Chapter 7, we adapt our novel compute kernels to a specialized hardware architecture that reduces resource utilization and improves dataflow on an FPGA-based accelerator.

# Chapter 2

# **Integer-Quantized Neural Networks**

Quantizing the weights and activations of neural networks significantly reduces their inference costs, often in exchange for minor reductions in model accuracy. This is in large part due to compute and memory cost savings in operations like convolutions and matrix multiplications, whose resulting products are typically accumulated into high-precision registers, referred to as accumulators. While many researchers and practitioners have taken to leveraging low-precision representations for the weights and activations of a model, few have focused attention on reducing the size of accumulators. Part of the issue is that accumulating into low-precision registers introduces a high risk of numerical overflow which, due to wraparound arithmetic, can significantly degrade model accuracy. In this chapter, we introduce a quantization-aware training algorithm that guarantees avoiding numerical overflow when reducing the precision of accumulators during inference. We leverage weight normalization as a means of constraining parameters during training using accumulator bit width bounds that we derive. We evaluate our algorithm across multiple quantized models that we train for different tasks, showing that our approach can reduce the precision of accumulators while maintaining model accuracy with respect to a floating-point baseline. We then show that this reduction translates to increased design efficiency for custom FPGA-based accelerators. Finally, we show that our algorithm not only constrains weights to fit into an accumulator of user-defined bit width but also increases the sparsity and compressibility of the resulting weights. Across all of our benchmark models trained

with 8-bit weights and activations, we observe that constraining the hidden layers of quantized neural networks to fit into 16-bit accumulators yields an average 98.2% sparsity with an estimated compression rate of 46.5x all while maintaining 99.2% of the floating-point performance.

## 2.1 Introduction

Quantization is the process of reducing the range and precision of the numerical representation of data. Among the many techniques used to reduce the inference costs of neural networks (NNs), integer quantization is one of the most widely applied in practice [56]. The reduction in compute and memory requirements resulting from low-precision quantization provides increased throughput, power savings, and resource efficiency, usually in exchange for minor reductions in model accuracy [80]. During inference, information is propagated through the layers of an NN, where most of the compute workload is concentrated in the multiply-and-accumulates (MACs) of operators such as convolutions and matrix multiplications. It has been shown that reducing the bit width of the accumulator can increase throughput and bandwidth efficiency for general-purpose processors by creating more opportunities to increase parallelism [40, 121, 170]. However, exploiting such an optimization is non-trivial, as doing so incurs a high risk of overflow which can introduce numerical errors that significantly degrade model accuracy due to wraparound twos-complement arithmetic [121].

Previous work has sought to either reduce the risk of numerical overflow [139, 170] or mitigate its impact on model accuracy [121]. In this work, we train quantized NNs (QNNs) to avoid numerical overflow altogether when using low-precision accumulators during inference. To fully exploit the wider design space exposed by considering low-precision weights, activations, and accumulators, we target model deployment on FPGA accelerators with custom spatial streaming dataflow rather than general-purposes platforms like CPUs or GPUs. The flexibility of FPGAs makes them ideal devices for low-precision inference engines as they allow for bit-level control over every part of a network; the precision of weights, activations, and accumulators can

be individually tuned to custom data types for each layer without being restricted to power-of-2 bit widths like a CPU or a GPU would be. The contributions of our work are summarized as follows:

- We show that reducing the bit width of the accumulator can reduce the resource utilization of custom low-precision QNN inference accelerators.

- We derive comprehensive bounds on accumulator bit widths with finer granularity than existing literature.

- We introduce a novel quantization-aware training (QAT) algorithm that constrains learned parameters to avoid numerical overflow when reducing the precision of accumulators during inference.

- We show that our algorithm not only constrains weights to fit into an accumulator of user-defined bit width, but also significantly increases the sparsity and compressibility of the resulting weights.

- We integrate our algorithm into the Brevitas quantization library [126] and the FINN compiler [7] to demonstrate an end-to-end flow for training and deploying QNNs using low-precision accumulators with custom streaming architectures on AMD-Xilinx FPGAs.

To the best of our knowledge, we are the first to explore the use of low-precision accumulators to improve the design efficiency of programmable QNN inference accelerators. However, our results have implications outside of the accelerators generated by FINN. Constraining the accumulator bit width to a user-defined upper bound has been shown to increase throughput and bandwidth efficiency on general-purpose processors [40, 121, 170] and reduce the compute overhead of homomorphic encryption arithmetic [107]. Furthermore, our experiments show that our algorithm can offer a better trade-off between resource utilization and model accuracy than existing approaches, confirming the benefit of including the accumulator bit width in the overall hardware-software (HW) co-design space.

### 2.2 Related Works

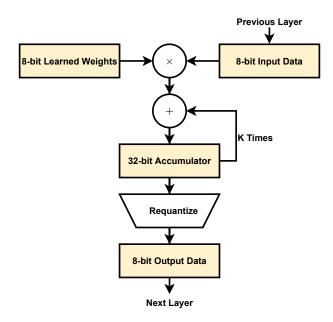

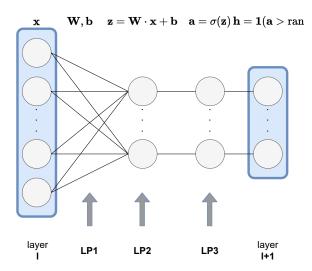

As activations propagate through the layers of a QNN, the intermediate partial sums resulting from convolutions and matrix multiplications are typically accumulated in a high-precision register before being requantized and passed to the next layer, which we depict in Figure 2.1. While many researchers and practitioners have taken to leveraging reduced precision representations for weights and activations [56, 81, 119, 183], few works have focused attention on reduced precision accumulators [40, 121, 139, 170].

**Figure 2.1.** A simplified illustration of fixed-point arithmetic in neural network inference. Quantized weights are frozen during inference. Input/output data is dynamic and thus, scaled then clipped as the hidden representations (*i.e.*, activations) are passed through the network. The accumulator needs to be big enough to fit the dot product of the learned weights with input data vectors, which are assumed to both be *K*-dimensional.

One approach to training QNNs to use low-precision accumulators is to mitigate the impact of overflow on model accuracy. Xie *et al.* [170] sought to reduce the risk of overflow using an adaptive scaling factor tuned during training; however, their approach relies on distributional assumptions that cannot guarantee overflow avoidance during inference. Alternatively, Ni *et al.* [121] proposed training QNNs to be robust to overflow using a cyclic activation function based

on expensive modulo arithmetic. They also use a regularization penalty to control the number of overflows. In both approaches, overflow is accounted for at the outer-most level, which fails to consider possible overflow when accumulating intermediate partial sums. Moreover, modeling overflow at the inner-most accumulation level during QAT is not easily supported by off-the-shelf deep learning frameworks as it is not directly compatible with fake-quantization over pre-existing floating-point backends. As such, the current practice is to either use high-precision registers or simply saturate values as they are accumulated; however, such clipping can still: (1) introduce errors that cascade when propagated through a QNN; and (2) require saturation logic, which can break associativity and add to latency and area requirements [8]. Thus, in our work, we train QNNs to completely avoid overflow rather than simply reducing its impact on model accuracy.

Most similar to our work is that of [40], which proposed an iterative layer-wise optimization strategy to select mixed-precision bit widths to avoid overflow using computationally expensive heuristics that assume signed bit widths for all input data types. Our proposed method constrains weights to avoid numerical overflow through the construction of our weight normalization-based quantization formulation, which accounts for both signed and unsigned input data types while adding negligible training overhead.

Tangential to our work, Wang *et al.* [160] and Sakr *et al.* [139] study the impact of reduced precision floating-point accumulators for the purpose of accelerating training. Such methods do not directly translate to fixed-point arithmetic, which is the focus of this work.

## 2.3 Background

Our work explores the use of weight normalization as a means of constraining weights during quantization-aware training (QAT) for the purpose of avoiding overflow when using low-precision accumulators. Here, we provide background related to this objective.

## **2.3.1** Quantization-Aware Training (QAT)

The standard operators used to emulate quantization during training rely on uniform affine mappings from a high-precision real number to a low-precision quantized number, allowing for the core computations to use integer-only arithmetic [81]. The quantizer (Eq. 2.1) and dequantizer (Eq. 2.2) are parameterized by zero-point z and scaling factor s. Here, z is an integer value that maps to the real zero such that the real zero is exactly represented in the quantized domain, and s is a strictly positive real scalar that corresponds to the resolution of the quantization function. Scaled values are rounded to the nearest integers using half-way rounding, denoted by  $\lfloor \cdot \rfloor$ , and elements that exceed the largest supported values in the quantized domain are clipped:  $\text{clip}(x;n,p) = \min(\max(x;n);p)$ , where n and p are dependent on the data type of x. For signed integers of bit width b, we assume  $n = -2^{b-1}$  and  $p = 2^{b-1} - 1$  and assume n = 0 and  $p = 2^b - 1$  when unsigned.

quantize

$$(x; s, z) := \text{clip}(\left\lfloor \frac{x}{s} \right\rfloor + z; n, p)$$

(2.1)

$$dequantize(x; s, z) := s \cdot (x - z) \tag{2.2}$$

It has become increasingly common to use unique scaling factors for each of the output channels of the learned weights to adjust for varied dynamic ranges [118]. However, extending this strategy to the activations incurs additional overhead as it requires either storing partial sums or introducing additional control logic. As such, it is standard practice to use per-tensor scaling factors for activations and per-channel scaling factors on only the weights. It is also common to constrain the weight quantization scheme such that z = 0, which is referred to as symmetric quantization. Eliminating these zero points reduces the computational overhead of cross-terms when executing inference using integer-only arithmetic [83]. During training, the straight-through estimator (STE) [13] is used to allow local gradients to permeate the rounding

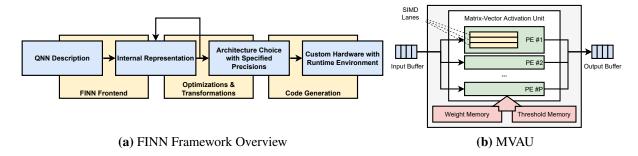

**Figure 2.2.** We adapt images from [18, 153] to provide: (a) an overview of the FINN framework; and (b) an abstraction of the matrix-vector-activation unit (MVAU), which is one of the primary building blocks used by the FINN compiler to generate custom streaming architectures.

function such that  $\nabla_x[x] = 1$  everywhere, where  $\nabla_x$  denotes the local gradient with respect to x.

### 2.3.2 Weight Normalization

Weight normalization reparameterizes each weight vector w in terms of a parameter vector v and a scalar parameter g as given in Eq. 2.3, where  $||v||_2$  is the Euclidean norm of the K-dimensional vector v [141]. This simple reparameterization fixes the Euclidean norm of weight vector w such that  $||w||_2 = g$ , which enables the magnitude and direction to be independently learned.

$$\boldsymbol{w} = g \cdot \frac{\boldsymbol{v}}{\|\boldsymbol{v}\|_2} \tag{2.3}$$

Tangential to our work, prior research has sought to leverage weight normalization as a means of regularizing long-tail weight distributions during QAT [20]. They replace the standard  $\ell_2$ -norm with an  $\ell_\infty$ -norm and derive a projection operator to map real values into the quantized domain. As further detailed in Section 2.6, we replace the  $\ell_2$ -norm with an  $\ell_1$ -norm to use the weight normalization parameterization as a means of constraining learned weights during training to use a pre-defined accumulator bit width during inference.

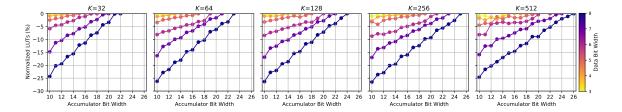

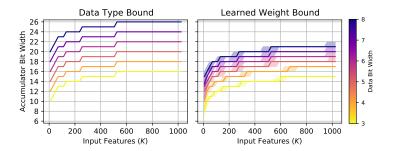

**Figure 2.3.** Reducing the size of the accumulator in turn reduces LUT utilization as we vary the size of the dot product (K) and the input and weights bit widths, N and M respectively. For simplicity, we use the same bit width for the weights and activations such that N = M for all data points and jointly refer to them as "data bit width." For a given dot product size and data bit width, we normalize the LUT utilization to the largest lower bound on the accumulator bit width as determined by the data types of the inputs and weights.

## 2.4 Motivation

To motivate our research objective, we evaluate the impact of accumulator bit width on the resource utilization of custom FPGA accelerators with spatial dataflow architectures. To do so, we adopt FINN [18, 153], an open-source framework designed to generate specialized streaming architectures for QNN inference acceleration on AMD-Xilinx FPGAs.

## 2.4.1 Generating Streaming Architectures with FINN

The FINN framework, depicted in Figure 2.2a, generates specialized QNN accelerators for AMD-Xilinx FPGAs using spatial streaming dataflow architectures that are individually customized for the network topology and the data types used. At the core of FINN is its compiler, which empowers flexible hardware-software (HW-SW) co-design by allowing a user to have perlayer control over the generated accelerator. Weight and activation precisions can be individually specified for each layer in a QNN, and each layer is instantiated as its own dedicated compute unit (CU) that can be independently optimized with fine-grained parallelism.

As an example of how a layer is instantiated as its own CU, we provide a simplified abstraction of the matrix-vector-activation unit (MVAU) in Figure 2.2b. The MVAU is one of the primary building blocks used by the FINN compiler for linear and convolutional layers [18]. Each CU consists of processing elements (PEs), which parallelize work along the data-independent

output dimension, and single-instruction multiple-data (SIMD) lanes, which parallelize work along the data-dependent input dimension. Execution over SIMDs and PEs within a layer is concurrent (*i.e.*, spatial parallelism), while execution over layers within a network is pipelined (*i.e.*, temporal parallelism). All quantized monotonic activation functions in the network are implemented as threshold comparisons that map high-precision accumulated results from the preceding layer into low-precision output values. During compilation, batch normalization, biases, and even scaling factors are absorbed into this threshold logic via mathematical manipulation [154]. The input and output data for the generated accelerators are streamed into and out of the chip using AXI-Stream protocols while on-chip data streams are used to interconnect these CUs to propagate intermediate activations through the layers of the network. During inference, all network parameters are stored on-chip to avoid external memory bottlenecks. For more information on the FINN framework, we refer the interested reader to [7, 18, 153].

### 2.4.2 Accumulator Impact on Resource Utilization

FINN typically relies on look-up tables (LUTs) to perform MACs at low precision; in such scenarios, LUTs are often the resource bottleneck for the low-precision streaming accelerators it generates. Furthermore, because activation functions are implemented as threshold comparisons, their resource utilization exponentially grows with the precision of the accumulator and output activations [18]. Thus, reducing the size of the accumulator has a direct influence on both the compute and memory requirements.

To evaluate the impact of accumulator bit width on LUT utilization, we consider a fully connected QNN with one hidden layer that is parameterized by a matrix of signed integers. The QNN takes as input a *K*-dimensional vector of unsigned integers and gives as output a 10-dimensional vector of signed integers. We use the FINN compiler to generate a streaming architecture with a single MVAU targeting an AMD-Xilinx PYNQ-Z2 board with a frequency of 100 MHz. We report the resource utilization of the resulting RTL post-synthesis. To simplify our analysis, we assume that LUTs are the only type of resources available and configure the FINN

compiler to target LUTs for both compute and memory so that we can evaluate the impact of accumulator bit width on resource utilization using just one resource.

As further discussed in Section 2.5, the minimum accumulator bit width that can be used to avoid overflow is a function of the size of the dot product (K) as well as the bit widths of the input and weight vectors x and w, respectively denoted as N and M. In Figure 2.3, we visualize how further reducing the accumulator bit width in turn decreases resource utilization as we vary K, N, and M. For a given dot product size and data bit width, we normalize the LUT utilization to the largest lower bound on the accumulator bit width as determined by the data types of the inputs and weights. To control for the resource utilization of dataflow logic, we use a single PE without applying optimizations such as loop unrolling, which increase the amount of SIMD lanes.

We observe that the impact of accumulator bit width on resource utilization grows exponentially with the precision of the data (i.e., M and N). As we reduce the size of the accumulator, we observe up to a 25% reduction in the LUT utilization of a layer when N=M=8, but only up to a 1% reduction in LUT utilization when N=M=3. This is expected as compute and memory requirements exponentially grow with precision and thus have larger proportional savings opportunities. We also observe that K has a dampening effect on the impact of accumulator bit width reductions that is also proportional to the precision of the data. When N = M = 8 and K = 32, we observe on average a 2.1% LUT reduction for every bit that we reduce the accumulator, but only a 1.5% LUT reduction when K = 512. Conversely, we observe on average a 0.2% LUT reduction for every bit that we reduce the accumulator when N = M = 3regardless of K. We hypothesize that this dampening effect is in part due to the increased storage costs of larger weight matrices because, unlike threshold storage, the memory requirements of weights are not directly impacted by the accumulator bit width. Therefore, the relative savings from accumulator bit width reductions are diluted by the constant memory requirements of the weights. We explore this further in Section 3.5, where we break down the resource utilization of FPGA accelerators generated for our benchmark models.

## 2.5 Accumulator Bit Width Bounds

Figure 2.1 illustrates a simplified abstraction of accumulation in QNN inference. As activations are propagated through the layers, the intermediate partial sums resulting from operations such as convolutions or matrix multiplications are accumulated into a register before being requantized and passed to the next layer. To avoid numerical overflow, the register storing these accumulated values needs to be wide enough to not only store the result of the dot product, but also all intermediate partial sums.

Consider the dot product of input data x and learned weights w, which are each K-dimensional vectors of integers. Let y be the scalar result of their dot product given by Eq. 2.4, where  $x_i$  and  $w_i$  denote element i of vectors x and w, respectively. Since the representation range of y is bounded by that of x and w, we use their ranges to derive lower bounds on the bit width P of the accumulation register, or accumulator.

$$y = \sum_{i=1}^{K} x_i w_i \tag{2.4}$$

It is common for input data to be represented with unsigned integers either when following activation functions with non-negative dynamic ranges (*e.g.*, rectified linear units, or ReLUs), or when an appropriate zero point is adopted (*i.e.*, asymmetric quantization). Otherwise, signed integers are used. Since weights are most often represented with signed integers, we assume the accumulator is always signed in our work. Therefore, given that the scalar result of the dot product between x and w is a p-bit integer defined by Eq. 2.4, it follows that  $\sum_{i=1}^{K} x_i w_i$  is bounded such that:

$$-2^{P-1} \le \sum_{i=1}^{K} x_i w_i \le 2^{P-1} - 1 \tag{2.5}$$

To satisfy the right-hand side of this double inequality, it follows that  $|\sum_{i=1}^{K} x_i w_i| \le 2^{P-1} - 1$ . However, the accumulator needs to be wide enough to not only store the result of the dot product, but also all intermediate partial sums.

Since input data is not known *a priori*, our bounds must consider the worst-case values for every MAC. Thus, because the magnitude of the sum of products is upper-bounded by the sum of the product of magnitudes, it follows that if  $\sum_{i=1}^{K} |x_i| |w_i| \le 2^{P-1} - 1$ , then the dot product between  $\boldsymbol{x}$  and  $\boldsymbol{w}$  fits into a P-bit accumulator without numerical overflow, as shown below.

$$|\sum_{i} x_i w_i| \le \sum_{i} |x_i w_i| \le \sum_{i} |x_i| |w_i| \le 2^{P-1} - 1$$

(2.6)

### 2.5.1 Deriving Lower Bounds Using Data Types

The worst-case values for each MAC can naïvely be inferred from the representation range of the data types used. When  $x_i$  and  $w_i$  are signed integers, their magnitudes are bounded such that  $|x_i| \leq 2^{N-1}$  and  $|w_i| \leq 2^{M-1}$ , respectively. In scenarios where  $x_i$  is an unsigned integer, the magnitude of each input value is upper-bounded such that  $|x_i| \leq 2^N - 1$ ; however, we simplify this upper bound to be  $|x_i| \leq 2^N$  for convenience of notation<sup>1</sup>. Combining the signed and unsigned upper bounds, it follows that  $|x_i| \leq 2^{N-1}_{\text{signed}}(x)$ , where  $1_{\text{signed}}(x)$  is an indicator function that returns 1 if and only if x is a vector of signed integers.

Building from Eq. 2.6, it follows that the sum of the product of the magnitudes is bounded such that:

$$\sum_{i=1}^{K} |x_i| |w_i| \le K \cdot 2^{N+M-1-\mathbb{1}_{\text{signed}}(\boldsymbol{x})} \le 2^{P-1} - 1$$

(2.7)

Taking the log of both sides, we can derive a lower bound on the accumulator bit width P:

$$\log_2\left(2^{\log_2(K) + N + M - 1 - \mathbb{1}_{\text{signed}}(\boldsymbol{x})} + 1\right) + 1 \le P \tag{2.8}$$

<sup>&</sup>lt;sup>1</sup>Note that our simplification of the upper bound for unsigned input data does not compromise overflow avoidance.

This simplifies to the following lower bound on *P*:

$$P \ge \alpha + \phi(\alpha) + 1 \tag{2.9}$$

$$\alpha = \log_2(K) + N + M - 1 - \mathbb{1}_{\text{signed}}(\boldsymbol{x})$$

(2.10)

$$\phi(\alpha) = \log_2(1 + 2^{-\alpha}) \tag{2.11}$$

In Figure 2.4, we visualize this bound assuming that x is a vector of unsigned integers such that  $\mathbb{1}_{\text{signed}}(x) = 0$ . There, we show how the lower bound on the accumulator bit width increases as we vary both the size of the dot product (K) and the bit width of the weights and activations.

### 2.5.2 Deriving Lower Bounds Using Learned Weights

Since learned weights are frozen during inference time, we can use knowledge of their magnitudes to derive a tighter lower bound on the accumulator bit width.

Building again from Eq. 2.6, the sum of the product of magnitudes is bounded by Eq. 2.12, where  $\|w\|_1$  denotes the standard  $\ell_1$ -norm over vector w.

$$\sum_{i=1}^{K} |x_i| |w_i| \le 2^{N-1_{\text{signed}}(\boldsymbol{x})} \cdot ||\boldsymbol{w}||_1 \le 2^{P-1} - 1$$

(2.12)

Here, we define a tighter lower bound on *P*:

$$P \ge \beta + \phi(\beta) + 1 \tag{2.13}$$

$$\beta = \log_2(\|\boldsymbol{w}\|_1) + N - \mathbb{1}_{\text{signed}}(\boldsymbol{x})$$

(2.14)

$$\phi(\beta) = \log_2(1 + 2^{-\beta}) \tag{2.15}$$

In Figure 2.4, we visualize this bound again assuming that x is a vector of unsigned integers. Because Eq. 2.14 is dependent on the values of the learned weights, we randomly

**Figure 2.4.** We visualize the differences between our accumulator bit width bounds as we vary the size of the dot product (K) as well as the bit width of the weights (M) and input activations (N), which we jointly refer to as "data bit width" such that M = N.

sample each K-dimensional vector from a discrete Gaussian distribution and show the median accumulator bit width along with the minimum and maximum observed over 300 random samples. We show that using learned weights (right) provides a tighter lower bound on the bit width of the accumulator than using data types (left) as we vary both the size of the dot product (K) and the bit width of the weights and input activations.

### 2.6 Training Quantized Neural Networks to Avoid Overflow

To train QNNs to use low-precision accumulators without overflow, we use weight normalization as a means of constraining learned weights w to satisfy the bound derived in Section 2.5.2. Building from Eq. 2.12, we transform our lower bound on accumulator bit width P to be the upper bound on the  $\ell_1$ -norm of w given by Eq. 2.16. Note that because each output neuron requires its own accumulator, this upper bound needs to be enforced channelwise.

$$\|\boldsymbol{w}\|_{1} \leq \left(2^{P-1} - 1\right) \cdot 2^{\mathbb{I}_{\text{signed}}(\boldsymbol{x}) - N} \tag{2.16}$$

### 2.6.1 Constructing Our Quantization Operator

To enforce this constraint during QAT, we reparameterize our quantizer such that each weight vector w is represented in terms of parameter vectors g and v. Similar to the standard weight normalization formulation discussed in Section 2.3.2, this reparameterization decouples

the norm from the weight vector; however, unlike the standard formulation, the norm is learned for each output channel. For a given layer with C output channels, we replace the per-tensor  $\ell_2$ -norm of the standard formulation (Eq. 2.3) with a per-channel  $\ell_1$ -norm. This reparameterization, given by Eq. 2.17, allows for the  $\ell_1$ -norm of weight vector  $\boldsymbol{w}$  to be independently learned per-channel such that  $g_i = \|\boldsymbol{w}_i\|_1$  for all  $i \in \{1, \dots, C\}$ , where  $\boldsymbol{w}_i$  denotes the weights of channel i and  $g_i$  denotes element i in parameter vector  $\boldsymbol{g}$ .

$$\boldsymbol{w}_i = g_i \cdot \frac{\boldsymbol{v}_i}{\|\boldsymbol{v}_i\|_1} \quad \forall i \in \{1, \dots, C\}$$

(2.17)

Similar to the standard quantization operator, our weight normalization-based quantization relies on a uniform affine mapping from the high-precision real domain to the low-precision quantized domain using learned per-channel scaling factors  $s = \{s_i\}_{i=1}^C$ . Thus, by constraining  $g_i$  to satisfy Eq. 2.18, we can learn quantized weights that satisfy our accumulator bit width bound and avoid overflow.

$$g_i \le s_i \cdot (2^{P-1} - 1) \cdot 2^{\mathbb{1}_{\text{signed}}(x) - N}$$

(2.18)

Below, we articulate our weight normalization-based quantization operator. For clarity and convenience of notation, we consider a layer with one output channel (i.e., C=1) such that parameter vectors  $\mathbf{g} = \{g_i\}_{i=1}^C$  and  $\mathbf{s} = \{s_i\}_{i=1}^C$  can be represented as scalars g and s, respectively.

quantize

$$(\boldsymbol{w}; s, z) := \operatorname{clip}\left(\left\lfloor \frac{g}{s} \frac{\boldsymbol{v}}{\|\boldsymbol{v}\|_1} \right\rfloor + z; n, p\right)$$

(2.19)

During training, our weight quantization operator applies fours elementwise operations the following in order: scale, round, clip, then dequantize. As with the standard operator, we eliminate the zero points in our mapping such that z = 0. We use an exponential parameterization of both the scaling factor  $s = 2^d$  and the norm parameter  $g = 2^t$ , where d and t are both log-scale parameters to be learned through stochastic gradient descent. This is similar to the work

of [83] with the caveat that we remove integer power-of-2 constraints, which provide no added benefit to the streaming architectures generated by FINN as floating-point scaling factors can be absorbed into the threshold logic via mathematical manipulation [18]. The scaled tensors are then rounded to zero, which we denote by  $\lfloor \cdot \rfloor$ . This prevents any upward rounding that may cause the norm to increase past our constraint. Note that this is another difference from the conventional quantization operators, which use half-way rounding. Finally, once scaled and rounded, the elements in the tensor are then clipped and dequantized using Eq. 2.2. Our resulting quantization operator used during training is given by Eq. 2.20, where n and p depend on the representation range of weight bit width M.

$$q(\boldsymbol{w};s) := \operatorname{clip}\left(\left|\frac{g}{s} \frac{\boldsymbol{v}}{\|\boldsymbol{v}\|_{1}}\right|; n, p\right) \cdot s \tag{2.20}$$

where

$$s = 2^d$$

(2.21)

and

$$g = 2^{\min(T,t)}$$

(2.22)

and

$$T = \mathbb{1}_{\text{signed}}(x) + \log_2(2^{P-1} - 1) + d - N$$

(2.23)

When quantizing our activations, we use the standard quantization operators discussed in Section 2.3.1. All activations that follow non-negative functions (*i.e.*, ReLU) are represented using unsigned integers, otherwise they are signed.

To update our learnable parameters during training, we use the straight-through estimator (STE) [13] to allow local gradients to permeate our rounding function such that  $\nabla_x \lfloor x \rfloor = 1$  everywhere, as is common practice.

### 2.6.2 Regularization with Lagrangian Penalties

To avoid t getting stuck when t > T in Eq. 2.22, we introduce the Lagrangian penalty  $\mathcal{L}_{penalty}$  given by Eq. 2.24. For a neural network with L layers, each with  $C_l$  output channels,  $t_{i,l}$  denotes the log-scale parameter of the norm for channel i in layer l and  $T_{i,l}$  denotes its upper bound as given by Eq. 2.23. Note that, even when  $\mathcal{L}_{penalty} > 0$ , we still satisfy our accumulator

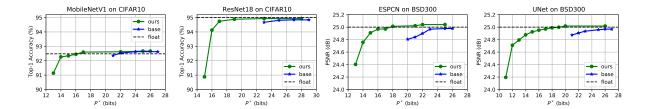

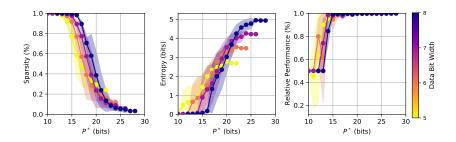

**Figure 2.5.** Using image classification and single-image super resolution benchmarks, we show that we are able to maintain model performance with respect to the floating-point baseline even with significant reductions to the accumulator bit width. We visualize this trade-off using Pareto frontiers estimated using a grid search over various weight, activation, and accumulator bit widths. Here, we use  $P^*$  to denote the largest accumulator bit width allowed across all layers in the network. We compare our algorithm (**green dots**) against the standard quantization baseline algorithm (**blue stars**) and repeat each experiment 3 times, totaling over 500 runs per model to form each set of Pareto frontiers. We observe that our algorithm dominates the baseline in all benchmarks, showing that we can reduce the accumulator bit width without sacrificing significant model performance even with respect to a floating-point baseline.

constraints by clipping the norm in Eq. 2.22. However, our Lagrangian penalty encourages norm  $g_i$  and scale  $s_i$  of each channel i in each layer to jointly satisfy the bound without clipping, which allows their log-scale parameters to be updated with respect to only the task error.

$$\mathcal{L}_{\text{penalty}} = \sum_{l=1}^{L} \sum_{i=1}^{C_l} (t_{i,l} - T_{i,l})_{+}$$

(2.24)

It is important to note that our formulation is task agnostic. Assuming base task loss  $\mathcal{L}_{task}$ , our total loss  $\mathcal{L}_{total}$  is given by Eq. 2.25, where  $\lambda$  is a Lagrange multiplier. In our experiments, we fix  $\lambda$  to be a constant scalar, although adaptive approaches such as [137] could be explored.

$$\mathcal{L}_{\text{total}} = \mathcal{L}_{\text{task}} + \lambda \mathcal{L}_{\text{penalty}}$$

(2.25)

# 2.7 Experiments

We evaluate our algorithm using image classification and single-image super resolution benchmarks. Because our algorithm is the first of its kind, we compare our approach to the standard QAT formulation discussed in Section 2.3.1. We implement all algorithms in PyTorch

using Brevitas v0.7.2 [126], where single-GPU quantization-aware training times range from 5 minutes (*e.g.*, ESPCN) to 2 hours (*e.g.*, MobileNetV1) on an AMD MI100 accelerator. To generate custom FPGA architectures for the resulting QNNs, we work from FINN v0.8.1 [7] and add extensions to support our work.

#### 2.7.1 Image Classification Benchmarks

We train MobileNetV1 [77] and ResNet18 [66] to classify images using the CIFAR10 dataset [93]. We closely follow the network architectures originally proposed by the respective authors, but introduce minor variations that yield more amenable intermediate representations given the image size as we discuss below. As is common practice, we fix the input and output layers to 8-bit weights and activations for all configurations, and initialize all models from floating-point counterparts pre-trained to convergence on CIFAR10. We evaluate all models by the observed top-1 test accuracy.

For MobileNetV1, we use a stride of 2 for both the first convolution layer and the final average pooling layer. This reduces the degree of downscaling to be more amenable to training over smaller images. All other layer configurations remain the same as proposed in [77]. We use the stochastic gradient descent (SGD) optimizer to fine-tune all models for 100 epochs in batches of 64 images using a weight decay of 1e-5. We use an initial learning rate of 1e-3 that is reduced by a factor of 0.9 every epoch.

For ResNet18, we alter the first convolution layer to use a stride and padding of 1 with a kernel size of 3. Similar to MobileNetV1, we remove the preceding max pool layer to reduce the amount of downscaling throughout the network. We also use a convolution shortcut [67] rather than the standard identity as it empirically proved to yield superior results in our experiments. All other layer configurations remain the same as proposed in [66]. We use the SGD optimizer to fine-tune all models for 100 epochs in batches of 256 using a weight decay of 1e-5. We use an initial learning rate of 1e-3 that is reduced by a factor of 0.1 every 30 epochs.

#### 2.7.2 Single-Image Super Resolution Benchmarks

We train ESPCN [144] and UNet [136] to upscale single images by a factor of 3x using the BSD300 dataset [113]. Again, we closely follow the network architectures originally proposed by the respective authors, but introduce minor variations that yield more hardware-friendly network architectures. As is common practice, we fix the input and output layers to 8-bit weights and activations for all configurations; however, we train all super resolution models from scratch. We empirically evaluate all models by the peak signal-to-noise ratio (PSNR) observed over the test dataset.

For ESPCN, we replace the sub-pixel convolution with a nearest neighbor resize convolution (NNRC), which has been shown to reduce checkerboard artifacts during training [124] and can be efficiently executed during inference [33]. All other layer configurations remain the same as proposed in [144]. We use the Adam optimizer [90] to fine-tune all models for 100 epochs in batches of 16 images using a weight decay of 1e-4. We use an initial learning rate of 1e-4 that is reduced by a factor of 0.98 every epoch.

For UNet, we use only 3 encoders and decoders to create a smaller architecture than originally proposed by [136]. We replace transposed convolutions with NNRCs, which have been shown to be functionally equivalent during inference [33], but have more favorable behavior during training [124]. We replace all concatenations with additions and reduce the input channels accordingly. We use the Adam optimizer to fine-tune all models for 200 epochs in batches of 16 images using a weight decay of 1e-4. We use an initial learning rate of 1e-3 that is reduced by a factor of 0.3 every 50 epochs.

# 2.7.3 Experiment Setup and Research Questions

We design our experiments around the following questions:

- How does reducing the accumulator bit width impact model performance?

- What are the trade-offs between resource utilization and model performance?

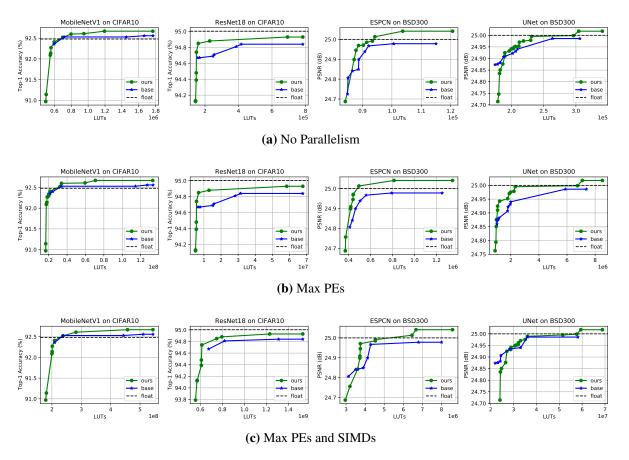

**Figure 2.6.** To evaluate the trade-off between resource utilization and accuracy, we visualize the Pareto frontier observed over our image classification and single-image super resolution benchmarks. We evaluate these Pareto frontiers in the following scenarios: (a) no spatial parallelism; (b) maximizing the PEs for each layer; and (c) maximizing the PEs and SIMDs for each layer. In each scenario, we observe that our algorithm (**green dots**) provides a dominant Pareto frontier across each model when compared to the standard quantization algorithm (**blue stars**), showing that our algorithm can reduce LUT utilization without sacrificing significant model performance.

• Where do our resource savings come from as we reduce accumulator bit width?

Similar to the experiments described in Section 3.3, we simplify our analysis and assume that LUTs are the only type of resources available. We configure the FINN compiler to target LUTs for both compute and memory wherever possible so that we can evaluate the impact of accumulator bit width on resource utilization using just one type of resource.

Throughout our experiments, we focus our attention on data bit widths between 5 and 8 bits for two reasons: (1) reducing precision below 5 bits often requires uniquely tailored

hyperparameters, which would not make for an even comparison across bit widths; and (2) reducing the size of the accumulator has a negligible impact on LUT utilization at lower data bit widths, as shown in Section 3.3. Still, even with a reduced set of possible data bit widths, it is computationally intractable to test every combination of weight, activation, and accumulator bit widths within the design space exposed by the QNNs that we use as benchmarks. Thus, for weight and activation bit widths, we uniformly enforce precision for each hidden layer in the network such that M and N are constant scalars, aside from the first and last layers that remain at 8 bits such that M = N = 8. The accumulator bit width, however, is dependent on not only the weight and activation bit widths, but also the size of the dot product (K), as discussed in Section 2.5. To simplify our design space, we constrain all layers in a given network to use the same accumulator bit width that we denote as  $P^*$  such that the maximum accumulator bit width for any layer is  $P^*$  bits. Recall that the value for  $P^*$  is used by Eq. 2.16 to upper bound the  $\ell_1$ -norm of each weight per-channel and used by Eq. 2.23 to enforce this constraint during training.

To collect enough data to investigate our research questions, we perform a grid search over weight and activation bit widths from 5 to 8 bits. For each of these 16 combinations, we calculate the largest lower bound on the accumulator bit width as determined by the data type bound (Eq. 2.9) of the largest layer in the network. Using this to initialize  $P^*$ , we evaluate up to a 10-bit reduction in the accumulator bit width to create a total of 160 configurations. Finally, we benchmark our results against the standard quantization algorithm discussed in Section 2.3.1; however, because it does not expose control over accumulator bit width, this grid search is restricted to the 16 combinations of weight and activation bit widths. We run each configuration 3 times to form a total of 528 runs per model. In the following sections, we summarize our findings.

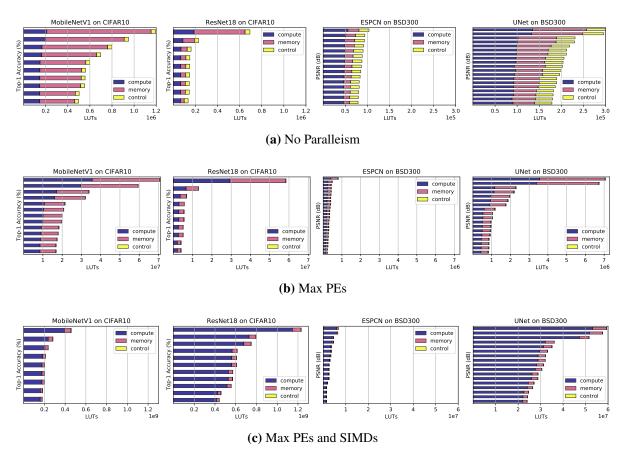

**Figure 2.7.** We break down LUT utilization into compute, memory, and control flow for each of our Pareto optimal models from Figure 2.6.

# 2.7.4 Accumulator Impact on Model Performance

Our algorithm introduces a novel means of constraining the weights of a QNN to use a pre-defined accumulator bit width without overflow. As an alternative to our algorithm, a designer can choose to heuristically manipulate data bit widths based on our data type bound given by Eq. 2.9. Such an approach would still guarantee overflow avoidance when using a pre-defined accumulator bit width P, but is an indirect means of enforcing such a constraint. Given a pre-defined accumulator bit width upper bound  $P^*$ , we compare the performance of models trained with our algorithm against this heuristic approach. We visualize this comparison as a Pareto frontier in Figure 2.5. It is important to note that, while this is not a direct comparison against the algorithm proposed by [40], the experiment is similar in principle. Unlike [40],

we use the more advanced quantization techniques detailed in Section 2.3.1, and replace the computationally expensive loss-guided search technique with an even more expensive, but more comprehensive grid search.

The Pareto frontier shows the maximum observed model performance for a given  $P^*$ . We observe that our algorithm can push the accumulator bit width lower than what is attainable using current methods while also maintaining model performance. Furthermore, most models show less than a 1% performance drop from even the floating-point baseline with a 16-bit accumulator, which is most often the target bit width for low-precision accumulation in general-purpose processors [40, 170].

#### 2.7.5 Trade-Offs Between Resources and Accuracy

To understand the impact that accumulator bit width can have on the design space of the accelerators generated by FINN, we evaluate the trade-offs between resource utilization and model performance. For each of the models trained in the grid search detailed in Section 2.7.3, we use the FINN compiler to generate resource utilization estimates and use Pareto frontiers to visualize the data. In Figure 2.6, we provide the maximum observed model performance for the total LUTs used by the accelerator. We evaluate these Pareto frontiers with three optimization configurations. First, we instantiate each layer in each model as a CU without any spatial parallelism optimization and visualize the Pareto frontiers in Figure 2.6a. Second, we maximize the number of PEs used in each layer in each model and visualize the Pareto frontiers in Figure 2.6b. Finally, we maximize both the number of PEs and the SIMD lanes used and visualize the Pareto frontiers in Figure 2.6c.