# UC San Diego Technical Reports

**Title** Reproducible User-Level Simulation of Multi-Threaded Workloads

Permalink https://escholarship.org/uc/item/22t3w1wm

**Author** Pereira, Cristiano

Publication Date 2007-09-30

Peer reviewed

## UNIVERSITY OF CALIFORNIA, SAN DIEGO

## Reproducible User-Level Simulation of Multi-Threaded Workloads

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

$\mathrm{in}$

Computer Science

by

### Cristiano Pereira

Committee in charge:

Brad Calder, Chair Bill Lin Harish Patil Tajana Rosing Curt Schurgers Dean Tullsen

© Cristiano Pereira, 2007 All rights reserved. The dissertation of Cristiano Pereira is approved, and it is acceptable in quality and form for publication on microfilm:

Chair

University of California, San Diego

2007

# DEDICATION

This dissertation is dedicated to my family, who have defined the person I have become. To my dad Glebson, my mom Magdalena and my brother Marcelo.

# EPIGRAPH

"for Distinction Sake, a Deceiving by Words, is commonly called a Lye, and a Deceiving by Actions, Gestures, or Behavior, is called Simulation."

Robert South (1643-1716)

# TABLE OF CONTENTS

|    | Signature Page                                                                                                                                                                                                                                                                                                                                                                         |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | Dedication Page                                                                                                                                                                                                                                                                                                                                                                        |

|    | Epigraph                                                                                                                                                                                                                                                                                                                                                                               |

|    | Table of Contents                                                                                                                                                                                                                                                                                                                                                                      |

|    | List of Figures                                                                                                                                                                                                                                                                                                                                                                        |

|    | List of Tables xii                                                                                                                                                                                                                                                                                                                                                                     |

|    | Acknowledgments                                                                                                                                                                                                                                                                                                                                                                        |

|    | Vita and Publications                                                                                                                                                                                                                                                                                                                                                                  |

|    | Abstract                                                                                                                                                                                                                                                                                                                                                                               |

| Ι  | Introduction1A. How computer architects use simulation2B. Motivation5C. Contributions8D. Organization9                                                                                                                                                                                                                                                                                 |

| II | Simulation Background11A. Level of simulation detail121. Functional simulation132. Cycle-accurate (detailed) simulation143. Detailed simulation methodologies16B. Full-system and user-level simulation21C. Reducing the amount of simulation through sampling221. Reaching the simulation samples242. Choosing the simulation samples371. Using parallel hosts372. Direct-execution39 |

|    | 3. FPGA-based simulation40E. Binary instrumentation41F. Summary43                                                                                                                                                                                                                                                                                                                      |

| III | Efficient Checkpointing for Uni-Processor User-Level Simulation 44                                                                                               |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | A. Application-Level Simulation                                                                                                                                  |

|     | 1. pinLIT $\ldots \ldots 47$                                          |

|     | 2. SimpleScalar $\ldots \ldots \ldots$           |

|     | B. Existing Logging Approach                                                                                                                                     |

|     | 1. Emulating System Calls                                                                                                                                        |

|     | 2. Benefit of Automated Logging                                                                                                                                  |

|     | C. Automatic Logging $\ldots \ldots \ldots$      |

|     | 1. Overview $\ldots \ldots 57$                                        |

|     | 2. Introducing pinSEL                                                                                                                                            |

|     | 3. Dynamic Instrumentation                                                                                                                                       |

|     | 4. Timestamps $\ldots \ldots \ldots$             |

|     | 5. System Effects Log Files                                                                                                                                      |

|     | 6. Simulating Multi-threaded Programs on                                                                                                                         |

|     | Uniprocessor Systems                                                                                                                                             |

|     | 7. Atomic Analysis $\ldots \ldots 72$                                 |

|     | 8. Architecture Simulation                                                                                                                                       |

|     | D. Logging Results                                                                                                                                               |

|     | 1. Benchmarks                                                                                                                                                    |

|     | 2. Avoiding Software Complexity of System Effects Emulation 77                                                                                                   |

|     | 3. Log Sizes and Logging Overhead                                                                                                                                |

|     | 4. Log Sizes Per Simulation Point                                                                                                                                |

|     | 5. Log Sizes for Non SPEC Programs                                                                                                                               |

|     | E. Other Uses of pinSEL Checkpoints                                                                                                                              |

|     | F. Related Work                                                                                                                                                  |

|     | 1. Handling system effects for User-Level Simulation                                                                                                             |

|     | 2. Full system simulation $\ldots \ldots \ldots$ |

|     | 3. Checkpoint Mechanisms                                                                                                                                         |

|     | G. Summary                                                                                                                                                       |

| IV  | Deterministic Simulation for Multi-Threaded Workloads                                                                                                            |

|     | on Multi-Processors                                                                                                                                              |

|     | A. Checkpoints for Reproducible Multi-Threaded Execution 99                                                                                                      |

|     | 1. Logging Shared Memory Dependencies for Multi-Processors 99                                                                                                    |

|     | 2. Memory Model and Deterministic Simulation                                                                                                                     |

|     | 3. Picking Samples for Simulation                                                                                                                                |

|     | B. Deterministic Simulation                                                                                                                                      |

|     | 1. Deterministic Simulation Implementation                                                                                                                       |

|     | C. Comparing Samples across Architecture Configurations 114                                                                                                      |

|     | 1. Differences Between Checkpointed Behavior and Baseline Con-                                                                                                   |

|     | figuration $\ldots \ldots \ldots$                |

|   | 2. Classifying the Synchronization Stalls                    |

|---|--------------------------------------------------------------|

|   | 3. Matching Synchronization Stalls Across Configurations 118 |

|   | 4. Calculating Sample Speed-ups                              |

|   | D. Methodology                                               |

|   | E. Evaluation                                                |

|   | 1. Estimating the speed-ups across simulation runs           |

|   | 2. Understanding the synchronization stalls                  |

|   | 3. Limitations of Deterministic Simulation                   |

|   | F. Related Work                                              |

|   | 1. Dealing with Non-Determinism                              |

|   | G. Summary                                                   |

| V | Summary and Future Challenges                                |

|   | A. Capturing operating system side effects automatically 142 |

|   | B. Deterministic simulation of multi-threaded programs       |

|   | C. Future Challenges                                         |

|   | Bibliography                                                 |

# LIST OF FIGURES

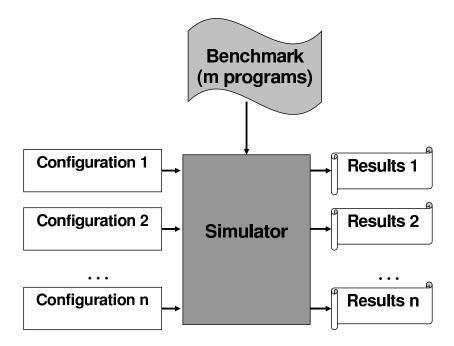

| Figure I.1    | Typical scenario when comparing architecture config-<br>urations. A benchmark, consisting of $m$ programs, is<br>simulated through $n$ different configurations | 4  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

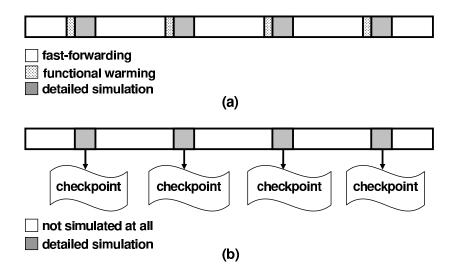

| Figure II.1   | (a) On-line sampling; (b) off-line sampling, using check-<br>points                                                                                             | 25 |

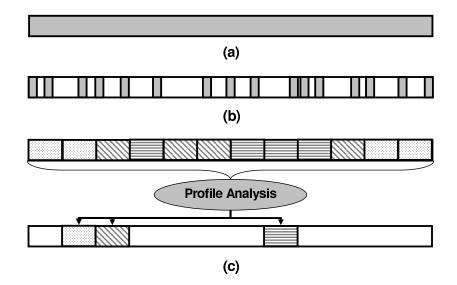

| Figure II.2   | (a) Full program detailed-simulation; (b) Statistical sam-<br>pling; (c) Representative sampling.                                                               | 31 |

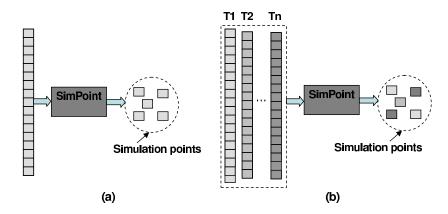

| Figure II.3   | (a) SimPoint for single-threaded program; (b) SimPoint for shared-memory multi-threaded programs                                                                | 37 |

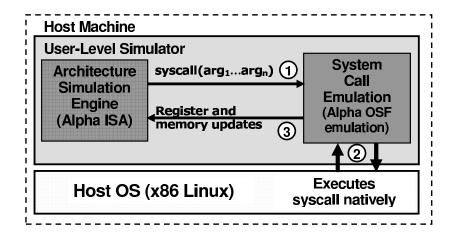

| Figure III.1  | Traditional emulation of system calls in user-level sim-<br>ulators                                                                                             | 52 |

| Figure III.2  | Code snippet taken from the SimpleScalar source file (syscall.c) used to emulate system calls                                                                   | 54 |

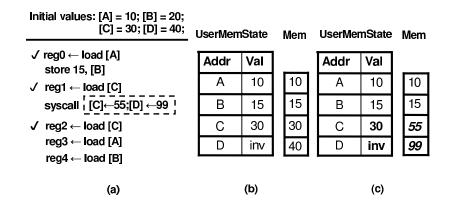

| Figure III.3  | Instructions executed by the thread. Check marks mean<br>the load value was logged.                                                                             | 58 |

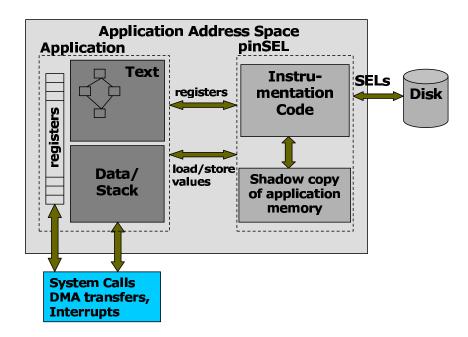

| Figure III.4  | pinSEL instrumentation tool representation.                                                                                                                     | 60 |

| Figure III.5  | Example of pinSEL's mechanism to log system effects.                                                                                                            | 66 |

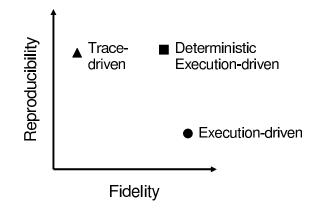

| Figure III.6  | Atomic analysis problem                                                                                                                                         | 73 |

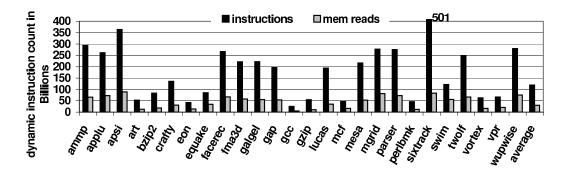

| Figure III.7  | Number of dynamic instructions and dynamic read mem-<br>ory instructions for the SPEC2000 programs examined.                                                    | 79 |

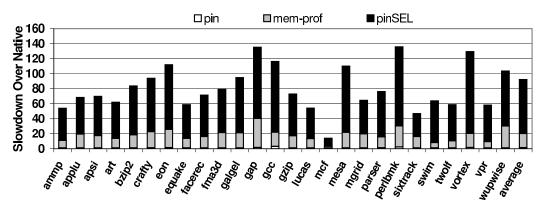

| Figure III.8  | pinSEL logger runtime slowdown (number of times, not<br>percentage) over native execution for the SPEC2000                                                      | 01 |

| Figure III.9  | programs                                                                                                                                                        | 81 |

|               | ing bzip2                                                                                                                                                       | 81 |

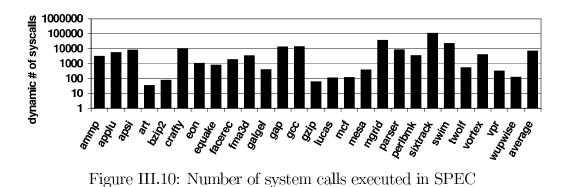

| Figure III.10 | Number of system calls executed in SPEC                                                                                                                         | 83 |

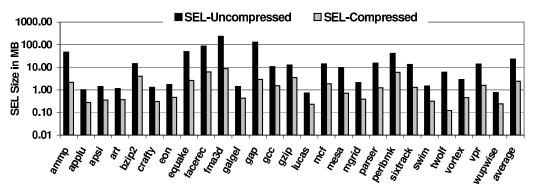

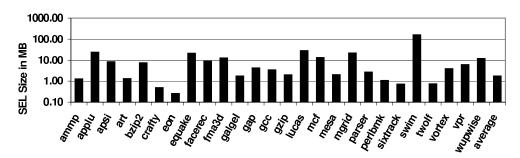

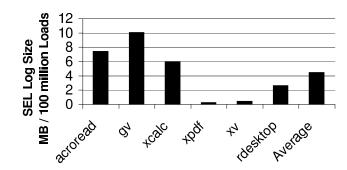

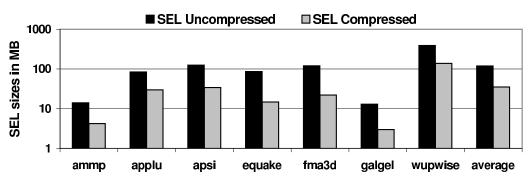

| Figure III.11 | SEL size required to capture a simulation point of 100M instructions for each SPEC program on average, with-                                                    |    |

| Figure III.12 | out compression                                                                                                                                                 | 83 |

| Figure III.13 | sion                                                                                                                                                            | 85 |

|               | rupts)                                                                                                                                                          | 85 |

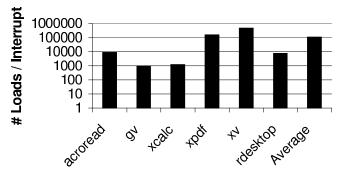

| Figure IV.1     | Comparison of deterministic execution-driven simula-<br>tion with trace-driven and pure execution-driven simu- |              |

|-----------------|----------------------------------------------------------------------------------------------------------------|--------------|

|                 | lation for multi-threaded workloads on multi-processors.                                                       | 97           |

| Figure IV.2     | Netzer transitive optimization                                                                                 | 100          |

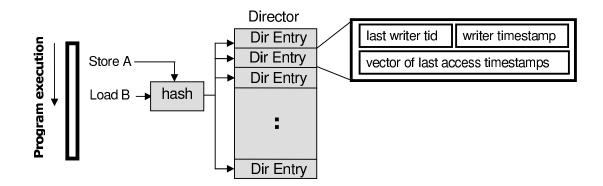

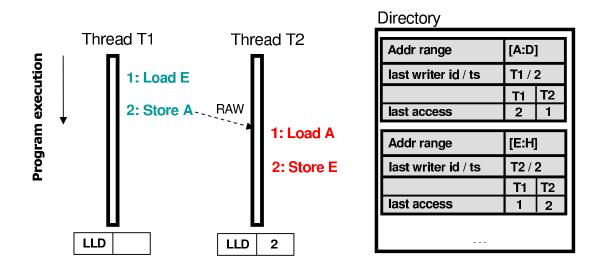

| Figure IV.3     | Directory table used to detect shared memory depen-                                                            |              |

| 0               | dencies                                                                                                        | 101          |

| Figure IV.4     | Example for the directory table state after hypothetical                                                       |              |

|                 | memory operations executed by threads 1 and 2                                                                  | 103          |

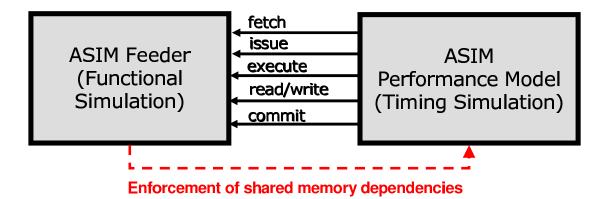

| Figure IV.5     | Deterministic simulation using Asim [28]. The feeder in-                                                       |              |

|                 | forms the performance model that certain instructions                                                          |              |

|                 | need to be synchronized. The feeder wakes up the in-                                                           |              |

|                 | structions when the dependencies are satisfied                                                                 | 109          |

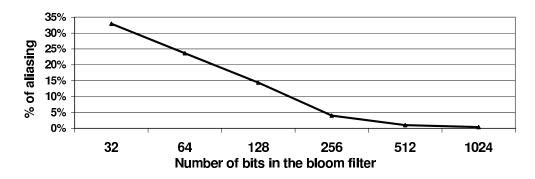

| Figure IV.6     | Percentage of instructions predicted as shared memory                                                          |              |

|                 | dependencies by the bloom filter due to aliasing as the                                                        | 110          |

|                 | number of bits used to implement it varies                                                                     | 112          |

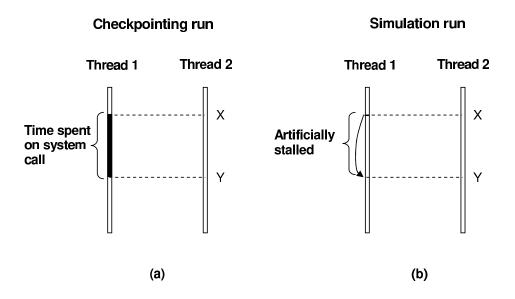

| Figure IV.7     | Problem with skipping system calls; (a) Checkpointing                                                          | 114          |

| Element IV 9    | run; (b) Simulation run                                                                                        | 114          |

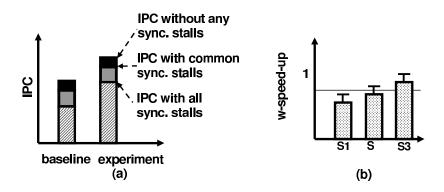

| Figure IV.8     | (a) - IPCs with all synchronization stalls, with only                                                          |              |

|                 | common stalls and without any stall; (b) - Weighted<br>Speed-up Calculation                                    | 122          |

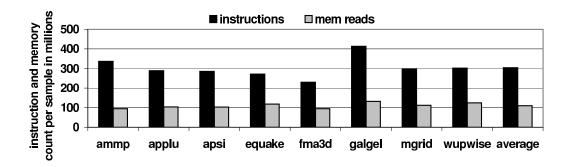

| Figure IV.9     | Average number of instructions and memory operations                                                           | 122          |

| Figure 17.9     | per sample for each benchmark                                                                                  | 126          |

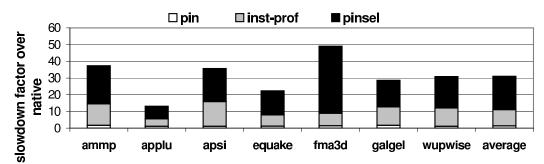

| Figure IV.10    | Slowdown to collect the 10 samples for each program .                                                          | $120 \\ 126$ |

| Figure IV.11    | Log sizes of the SEL checkpoints per sample                                                                    | $120 \\ 126$ |

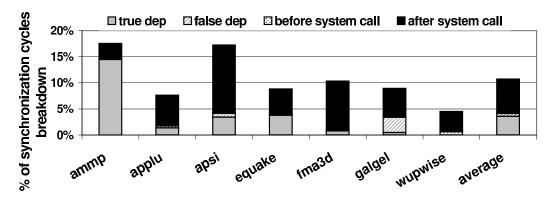

| Figure IV.12    | Percentage of synchronization stall for baseline configu-                                                      | 120          |

| 0               | ration, broken down in categories: (a) true-dependencies                                                       |              |

|                 | (RAW); (b) false-dependencies (WAR/WAW); (c) Before-                                                           |              |

|                 |                                                                                                                | 128          |

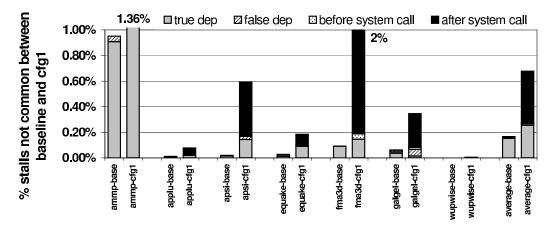

| Figure IV.13    | Percentage of synchronization stalls not common across                                                         |              |

|                 | the <i>baseline</i> and <i>cfg1</i> , w.r.t. the total number of cycles                                        |              |

|                 | simulated                                                                                                      | 128          |

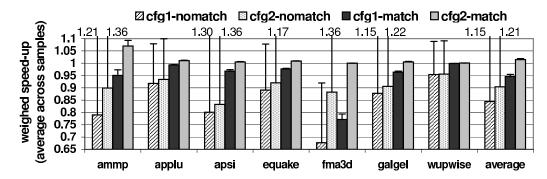

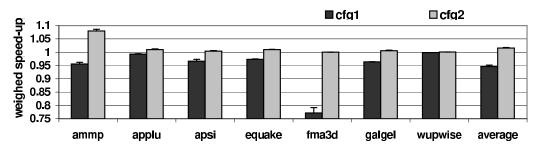

| Figure IV.14    | Weighted speed-ups computation for baseline against                                                            |              |

|                 | cfg1 and cfg2, when using only the non-common syn-                                                             |              |

|                 | chronization stalls across the runs, and when using all                                                        | 100          |

|                 | the synchronization stalls.                                                                                    | 130          |

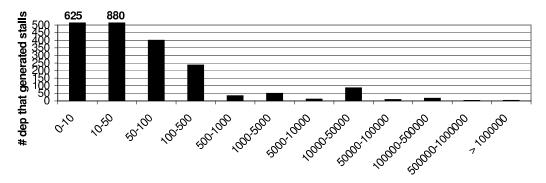

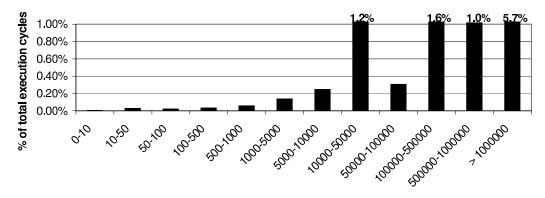

| Figure IV.15    | Histogram of number of dependencies that generate syn-                                                         |              |

|                 | chronization stalls, classified by stall length, across all                                                    | 191          |

| Figure IV.16    | programs                                                                                                       | 131          |

| 1 igure 1 v .10 | to total number of cycles, classified by stall length                                                          | 131          |

|                 | to total number of cycles, classified by stall tength                                                          | 101          |

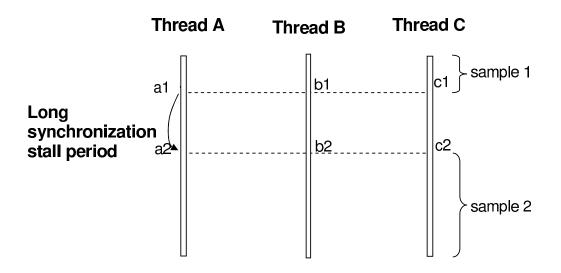

| Figure IV.17 | Sample breakdown representation. Long synchroniza-                                                                                                         |    |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|              | tion period starts at instruction counts $a1$ , $b1$ and $c1$                                                                                              |    |

|              | and ends at instructions $a^2, b^2, c^2 \dots \dots$ | 34 |

| Figure IV.18 | Weighted speed-up computation after breaking down                                                                                                          |    |

|              | the samples for eliminating the stalls longer than $100,000$                                                                                               |    |

|              | cycles from the baseline runs                                                                                                                              | 35 |

# LIST OF TABLES

| Table II.1 | Levels of detail for architecture simulation 1 | 3 |

|------------|------------------------------------------------|---|

| Table IV.1 | Baseline simulator configuration               | 3 |

| Table IV.2 | SpecOMP programs used                          | 4 |

| Table IV.3 | Experimental and baseline configurations 12    | 7 |

### ACKNOWLEDGMENTS

None of the work presented in this dissertation would have been possible without the assertive guidance of Prof. Brad Calder, who always kept me focused and motivated about the research conducted throughout the years we worked together. Thank you for bringing me to the architecture lab, for opening the doors at Intel and for doing a great job as an advisor, whether in person or remotely.

I also would like to thank my colleagues from the architecture lab and the embedded systems lab, where I started the long PhD journey. From the embedded systems lab, I would like to thank Frederic Doucet, for the countless hours of discussions and for the camaraderie; Ravindra Jejurikar, for his stressfree way of handling things and the many discussions on various research topics; Yuvraj Aggarwal, for always trying to keep it fun. I must also thank Jeffrey Namkung and Zhen Ma for many hours spent on discussions and coffee breaks. I cannot forget my friends from UC Irvine, where everything started so many years ago. In particular, Marcio Buss, for his friendship, for the surfing together and for all the beers we drank together. From the architecture lab, at UC San Diego, I would like to thank Satish Narayanasamy, for the research discussions, for making things look simple and for the games of table tennis. I also would like to thank Erez Perelman, Jeremy Lau, Jeffrey Brown, Jack Sampson, Michael Van Biesbrouck and Ganesh Venkatesh for their help on many technical and non-technical issues.

I must not forget to thank all of the folks from VSSAD, Intel, Massachusetts, whose help and support were also indispensable for completing this dissertation. In particular, I am very thankful to Harish Patil for his mentorship, enthusiasm, perseverance and for the great advice given during my long and rewarding internship at Intel. I am also grateful to other VSSAD members: Robert Cohn, Greg Lueck, Chi-Keung (CK) Luk, Geoff Lowney, Aamer Jaleel, Michael Adler, Mark Charney, Joel Emer and many others.

I am also grateful to Kaylene Grove, who has always supported me and given me a good reason to leave the office and go home. I am also thankful to her family, who have adopted me and made me feel at home here in the US.

Finally, I would like to thank my family back in Brazil. They are the reason I was able to make it this far. They have always supported my decisions, even when I decided to leave them to embark on a journey 6,000 miles away from them.

Chapter III contains material that appears in "Automatic Logging of Operating System Effects to Guide Application-Level Architecture Simulation", Satish Narayanasamy, Cristiano Pereira, Harish Patil, Robert Cohn and Brad Calder, in *International Conference on Measurement and Modeling of Computer Systems (SIGMETRICS)*. The dissertation author was the primary investigator and author of this paper. Portions of Chapter III are Copyright ©2006 by the Association for Computing Machinery, Inc. Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from Publications Dept., ACM, Inc., fax +1 (212) 869-0481, or permissions@acm.org.

Chapter IV contains material that appears in "Reproducible Simulation of Multi-Threaded Workloads for Architecture Design Exploration", Cristiano Pereira, Harish Patil and Brad Calder, submitted to the 14th International Symposium on High-Performance Computer Architecture, Salt Lake City, UT February 16-20, 2008. The dissertation author was the primary investigator and author of this paper.

VITA

| 1998 | Bachelor of Science in Computer Science<br>Pontifical Catholic University of Minas Gerais, Brazil |

|------|---------------------------------------------------------------------------------------------------|

| 2000 | Master of Science in Computer Science<br>Federal University of Minas Gerais, Brazil               |

| 2007 | Doctor of Philosophy in Computer Science<br>University of California, San Diego, USA              |

### PUBLICATIONS

"Reproducible Simulation of Multi-Threaded Workloads for Architecture Design Exploration" Cristiano Pereira, Harish Patil, Brad Calder. Submitted to the 14th International Symposium on High-Performance Computer Architecture. February, 2008.

"Recording Shared Memory Dependencies for Application-Level Replay Debugging" Satish Narayanasamy, Cristiano Pereira, Brad Calder. The 12th International Conference on Architectural Support for Programming Languages and Operating Systems. October, 2006.

"Software Profiling for Deterministic Replay Debugging of User Code" Satish Narayanasamy, Cristiano Pereira and Brad Calder. *The 5th International Conference on Software Methodologies Tools and Techniques.* October, 2006.

"Automatic Logging of Operating System Effects to Guide Application-Level Architecture Simulation" Satish Narayanasamy, Cristiano Pereira, Harish Patil, Robert Cohn and Brad Calder. *International Conference on Measurement and Modeling of Computer Systems.* June, 2006.

"Dynamic Phase Analysis for Cycle-Close Trace Generation" Cristiano Pereira, Jeremy Lau, Brad Calder, Rajesh Gupta. *Proceedings of the International Con*ference on Hardware/Software Codesign and System Synthesis. September, 2005.

"Leakage Aware Dynamic Voltage Scaling for Real-Time Embedded Systems" Ravindra Jejurikar, Cristiano Pereira, Rajesh Gupta. *Proceedings of 41st Design Automation Conference (DAC'04) San Diego.* June, 2004.

"PASA: A Software architecture for building power aware embedded systems" Cristiano Pereira, Rajesh Gupta, Mani Srivastava. In the proceedings of the IEEE CAS Workshop on Wireless Communications and Networking - Power efficient wireless ad hoc networks. September, 2002.

"JADE: An Embedded Systems Specification, Code Generation and Optimization Tool" Cristiano Pereira, et. al. *Proceedings of the XIII Symposium on Integrated Circuits and System Design*. September, 2000.

"Code Generation and Optimization for Embedded Systems Specified in SDL" Cristiano Pereira, *MSc. Dissertation - UFMG (Federal University of Minas Gerais) - Computer Science Department, Belo Horizonte, Minas Gerais, Brazil.* July, 2000.

### ABSTRACT OF THE DISSERTATION

Reproducible User-Level Simulation of Multi-Threaded Workloads

by

Cristiano Pereira Doctor of Philosophy in Computer Science University of California, San Diego, 2007 Professor Brad Calder, Chair

As the complexity of processors increases, it becomes harder for designers to understand the non-trivial and many times non-intuitive interactions among the micro-architecture internal structures. Understanding these interactions is important because it helps pinpoint bottlenecks, enabling designers to reason about sources of performance loss and improve their next generation of processors. To help designers understand these interactions in current and, more importantly, in future generation designs, designers make heavy use of computer architecture detailed simulation. These simulators model the behavior of the processor on a per-cycle basis, allowing designers to look at very detailed trade-offs. Building and maintaining these simulators is a large and complicated task. In addition, recent trends in designing micro-architectures with multiple cores in the same chip brings new challenges that affect the way simulation results should be compared. This dissertation focuses on techniques to help build and maintain simulators, as well as techniques to improve the way architects evaluate design choices using simulation.

Existing user-level simulators require manual hand coding for the emulation of each and every possible system effect (e.g., system call, interrupt, DMA transfer) that can impact the application's execution. Developing such an emulator for a given operating system is a tedious exercise, and it can also be costly to maintain it to support newer versions of that operating system. Furthermore, porting the emulator to a completely different operating system might involve building it all together from scratch. The first contribution of this dissertation is a technique to automatically capture the system effects to an application. The system effects are captured in logs and then used to guide achitecture simulation. By using the proposed technique, the complexity of implementing and maintaining user-level simulators is greatly reduced. In addition, the technique guarantees deterministic simulation on uni-processor systems.

As multi-core processors become main stream, techniques to address efficient simulation of multi-threaded workloads are needed. Simulation of multithreaded workloads on multi-core systems suffer from non-determinism across runs in different architecture configurations. If the execution paths between two simulation runs of the same benchmark, with the same input, are too different, the simulation results cannot be used to compare the configurations. The other contributions of this dissertation focus on techniques to efficiently collect simulation checkpoints for multi-threaded workloads. It extends the previous technique to efficiently collect logs for uni-processor simulation. Using these checkpoints, multi-threaded simulation in multi-core systems becomes deterministic. The deterministic simulation results in stalls that would not naturally occur in execution. This dissertation proposes techniques that allow one to accurately compare performance across architecture configurations in the presence of these stalls.

# Ι

# Introduction

Advances in system integration technology have enabled a steady increase in transistor density, with more transistors used by every new generation of processors. Recent processor designs, such as the Intel Dual-Core Itanium 2 Processors, released in 2006, have more than 1 billion transistors in a single chip. This abundance of transistors allows the design of complex architectures, enabling the implementation of aggressive techniques to dynamically execute instructions out-of-order, exploiting as much instruction level parallelism as possible [32]. More recently, even as the rate of performance increase achieved by exploiting instruction level parallelism bottoms out, computer architecture still continues to advance by transitioning to designs where many processing units are included in a single chip [29], known as multi-core processors.

As the complexity of processors increases, it becomes harder for designers to understand the non-trivial and many times non-intuitive interactions among the micro-architecture internal structures. Understanding these interactions is important because they determine the speed at which programs execute in that architecture. To help designers understand these interactions in current and, more importantly, in future generation designs, designers make heavy use of computer architecture simulation. In a recent study, Yi *et al* [79] shows the trend in performance evaluation methodologies for papers accepted to the *International Symposium on Computer Architecture* (ISCA), the most important conference on computer architecture. In summary, in 1985, 7% of the papers accepted evaluated their architectural enhancements using simulators. In 2004, the number jumped to 87%. The reason for that is the complexity of recent designs. The micro-processor manufacturing industry is not different. Mainstream microprocessor design and manufacturing companies such as *Intel Corporation* and *Advanced Micro Devices* (AMD) also rely heavily on simulation to help evaluate design choices and understand the behavior of workloads running on their chips. This is also due to complexity of new designs and the prohibitive cost to build prototypes, as the fabrication processes become more expensive. Therefore, it is clear that simulators are indispensable tools for the current and future success of computer architecture research, both in academia and industry.

This dissertation focuses on techniques to help build and maintain simulators, as well as techniques to improve the way architects evaluate design choices using simulation of multi-threaded workloads in multi-core processors.

### I.A How computer architects use simulation

Researchers use simulators to model the behavior of a micro-processor architecture in details. Simulators can be used for many purposes: 1) to understand the bottlenecks of the current designs; 2) to assess the viability of implementing architectural enhancements, which in many cases are proposed as a result of understanding the bottlenecks; 3) to project performance of workloads and benchmarks in new architectures; 4) to create inputs to analytical models. The *de facto* standard for computer architecture simulation models is based on execution-driven, cycle-accurate simulators. These are simulators that execute each instruction of the workload being examined, modeling the path through which the instruction proceeds as it advances through the various stages of a processor pipeline. This behavior is modeled on a per-cycle basis, to help understand what happens during each cycle of execution, in the various processing units. They are widely used because of their accuracy in predicting performance and because of their ability to model speculative execution. They enable the evaluation of detailed trade-offs, which is not possible using other higher-level simulation models, such as analytical simulation.

To help evaluate the performance of a given micro-architecture, designers typically execute standard workloads that represent a diversity of behaviors, also known as benchmarks [3, 4, 9, 24]. When understanding the effects of a new architectural feature or enhancement, the benchmarks are run in the simulators, modeling different architecture configurations – where each configuration implements a possible variation of the enhancement (perhaps with different parameters) – in order to collect quantitative results. These results are then analyzed and a conclusion is drawn as to whether the enhancement is beneficial. Figure I.1 illustrates the scenario. A benchmark, composed of m programs, is simulated with ndifferent configurations. Each configuration represents a design point in the space of possible choices. For example, the first configuration can be a processor with half the size of L1 data and instruction caches as configuration 2. Or configuration 1 can use a different implementation of a cache coherence protocol, compared to configuration 2. Typically one of the configurations is the baseline, which is used as a common denominator to rank the results of the other configurations<sup>1</sup>. The simulations for each configuration are run and the results are output. These statistics, collected during the simulation runs, are used to evaluate them. For example, if the goal of the enhancement is to maximize performance, a common

$<sup>^1</sup>$ Alternatively, designers may look at radically different design options. In those cases, however, higher level models are also adequate.

Figure I.1: Typical scenario when comparing architecture configurations. A benchmark, consisting of m programs, is simulated through n different configurations.

way to evaluate the design choices is to use a performance-related metric, such as the number of instructions completed per cycle (IPC), for a workload. Once the IPCs for the configurations are available, the next step is to compute the speedup across the runs. If the goal is minimize energy consumption, other metrics are better suited, such as the energy-delay-product, which seeks to minimize energy without a significant impact on performance. One basic requirement for these comparisons to work is that the amount and type of work executed across the various simulation runs is the same. As will be shown later, this is not always the case, and techniques to ensure this property are beneficial.

### I.B Motivation

As previously noted, a cycle-accurate and execution-driven simulator is a powerful tool to understand the behavior of a program running on a microarchitecture, and the complex interactions among internal micro-architectural structures. However, the accuracy and visibility comes at the cost of very high run-times required to complete the simulations. For instance, Simplescalar, a widely used simulator employed by academics, can execute less than 1 million instructions per second (on a modern Pentium 4 2.4GHz processor) when modeling a moderately complex out-of-order single core processor, with a very simple memory hierarchy. Industry simulators, on the other hand, which tend to model real architectures with very detailed and complex models, are even slower. The performance model used in Chapter IV simulates a multi-core processor, with a complex memory hierarchy and interconnection network. These models execute on the order of 1K to 10K instructions per second. This is because of the complexity of the models, the richer level of detail, and because the modular nature of the simulator's implementations, which are meant to be used for generations of processor designs. This leads the implementation of industry simulators to emphasize on re-usability and well defined interfaces across the various components modeled.

Simulators are also be classified in terms of what they model. Two broad categories are commonly found: user-level and full-system simulators. Fullsystem simulators simulate in detail both the user-level code, the operating system and device drivers code. They model the processor and all other peripherals needed for the correct execution of the program. These simulators can generally boot unmodified operating system codes. However, implementing and maintaining a full-system simulator is a very complex task. Even configuring benchmarks to run in those simulators can be a hard task. If the applications do not spend a significant amount of execution in the operating system, the complexity of implementing these simulators is not warranted. Examples of full-system simulators are Simics [43], SimOS [59] and SoftSDV [70]. User-level simulators only perform detailed simulation of the user-code and the system shared libraries. Even so, the interactions with the operating system need to be emulated for the program to execute correctly during simulation. For example, if the program executes a system call to read data from a file, that system call's side effects have to be reflected in the simulation for correct execution, otherwise the program does not read the data it needs to continue its execution. Examples are such simulators *Simplescalar* [17] and SMTSim [68].

Existing application-level simulators require manual hand coding for the emulation of each and every possible system effect (e.g., system call, interrupt, DMA transfer) that can impact the application's execution. Developing such an emulator for a given operating system is a tedious exercise, and it can also be costly to maintain it to support newer versions of that operating system. Furthermore, porting the emulator to a completely different operating system might involve building it altogether from scratch. This is the first problem area where this dissertation makes contributions. A technique to automatically capture the system effects to an application in logs is proposed. A collection of logs, referred to as a *checkpoint*, is then used to guide architecture simulation. By using the proposed technique, the complexity of implementing and maintaining user-level simulators is greatly reduced. In addition, the technique guarantees deterministic simulation on uni-processor systems, which is desired for accurate comparison of configurations. Chapter III presents and discusses the proposed technique in detail.

The cost of running simulations is worsened as the length of benchmarks to be simulated increases. The latest version of SPEC benchmarks, released in 2006, executes close to one trillion instructions on average, up from an average of 114 billion instructions for SPEC2000. With the recent focus on multi-core architectures increasing attention has shifted to the simulation of multi-threaded benchmarks. These programs are good candidates to exploit the full benefit of multi-core architectures, by the use of thread-level parallelism. Examples of these programs are found in multi-threaded benchmarks such as SPECOMP2001 [9] and RMS (Recognition-Mining-Synthesis) [24]. These programs consist of multiple threads of execution, which execute cooperatively in order to accomplish a program's task. These programs also have a large dynamic instruction count, in the order of trillions of instructions.

Furthermore, multi-threaded benchmarks, when executed in multi-core architectures, present vet another challenge: non-determinism across simulation runs with different architecture configurations, as pointed out by Alameldeen et al [7] and Lepak et al [41]. This breaks the requirement noted earlier in section I.A, that the execution paths are executed across the simulations runs, guaranteeing that the workload is performing the same amount of work across the runs. However, this is not true for shared-memory multi-threaded programs. The non-determinism comes from the fact that threads do access shared memory locations in a different order during simulation of different architecture configurations. This is because threads' rate of progress with respect to one another changes. For example, the order in which locks are acquired by threads in one architecture configuration can be different across two runs. Also, the number of cycles and instructions spent spinning for a lock can be different. As a result, the execution paths across two executions are not guaranteed to be the same. If the variation in the execution paths is significant, two simulation runs cannot be compared directly, because the amount and type of work performed differs across executions. The problem is worsened when the operating system behavior is also modeled, since changes in the architecture configuration can result in interrupts arriving at different points in the execution, causing the OS to schedule threads differently across two runs. One possible solution to overcome this problem is to increase the number of simulation runs needed to evaluate a given configuration, as proposed by Alameldeen *et al* [7] (and explained in chapter IV). This, however, increases the run-time cost of evaluating new designs significantly. This is the second problem area where this dissertation makes contributions. In particular, an extension to the checkpointing mechanism for uni-processor simulation is presented in Chapter III. This extension allows efficient capturing of enough information to guarantee deterministic execution also in multi-core architecture simulation. To guide simulation from these checkpoints, modifications in a simulator are required. These modifications make the simulation deterministic. Deterministic simulation requires the introduction of *stalls* in the simulation that would not naturally occur in the execution of the program. This dissertation proposes techniques to account for these *stalls* in order to allow designers to compare simulation runs and make decisions about them.

# I.C Contributions

The complexity of building and maintaining computer architecture simulators, the need for determinism across simulations, the need for techniques for efficient creation of user-level simulation checkpoints, and the new challenges arising as a result of the multi-core era, motivated the development of the techniques presented in this dissertation. The contributions of this work are summarized as follows:

• Automatic logging of operating system effects. A technique and a tool to capture and log operating system effects for simulation is presented. The technique enables capturing checkpoints for user-level simulators in a very

easy and portable manner. It trivializes the need to implement emulation support in these simulators. It also enables deterministic simulation on uni-processor systems because it removes the sources of non-determinism from the simulation. This is especially important if one wants to analyze interactive applications and applications whose interactions with the outside world (e.g. network I/O) dictate its behavior.

- Efficient capture of multi-threaded program behavior. An extension of the tool to capture system effects enables capturing of multi-threaded program executions on multi-core<sup>2</sup> systems. These checkpoints can be used to guide multi-threaded workload simulation on multi-cores deterministically.

- A technique for comparing design alternatives using deterministic simulation in the presence of artificial stalls, introduced to remove non-determinism. The implementation of a deterministic simulator and a technique to compare simulation runs when using a deterministic simulator is presented. Deterministic simulation introduces artificial stalls to ensure same execution paths across simulation runs with different configurations. The proposed techniques show how to account and deal with these stalls.

### I.D Organization

This dissertation is organized as follows. Chapter II presents a brief description of simulation in computer architecture. It describes different simulation styles and techniques to reduce and speed-up simulation. In particular, it discusses statistical and representative sampling. These are techniques used to select samples for simulation. Chapter III also explains mechanisms used to reach a sample for simulation, once it is selected. The techniques presented in

$<sup>^{2}</sup>$ The focus is on multi-core systems, but nothing prevents a user from applying the technique on multi-processor systems.

other chapters can be directly applied with both types of simulation sampling. This chapter concludes with an introduction to binary instrumentation, which is used in the implementation of the tools described in chapters III and IV. Chapter III discusses a tool, called pinSEL, and the algorithm applied to automatically capture system effects in checkpoints, which are then used to guide architecture simulation. It provides a detailed description and an evaluation of log sizes and run-time overhead to collect the logs. Chapter IV describes the extensions made to the pinSEL checkpoints to support deterministic simulation of multi-core workloads. This technique is a step towards addressing variability in multi-threaded workloads, when running in multi-processor systems. It also describes the simulation changes needed to guide simulation from these checkpoints. Chapter IV concludes with a description of the techniques to deal with the artificial stalls introduced during simulation, in order to allow design exploration in multi-core architectures. These stalls can be used to provide a speed-up estimate when comparing two designs. Finally, chapter V summarizes the dissertation and identifies future research directions.

# $\mathbf{II}$

# Simulation Background

Simulators model the performance of a system. They are used to predict the behavior of future generation machines and to understand the performance of current machines, in order to find bottlenecks and fix performance bugs. For future generation processors, a simulator, usually implemented in software, is an inexpensive and flexible way to understand the performance, simply because the processor does not exist. An alternative would be to prototype the processor, but that is expensive, especially with today's designs, whose implementations contain more than one billion transistors in a single chip. Understanding the performance of existing processors can be done with direct measurements, but simulation models provide a much higher level of visibility, and enable the flexibility to change the sizes of internal structures very easily (e.g. cache associativity). Although inexpensive compared to building a prototype, and flexible, simulators are complex to implement and maintain, particularly as the number of cores per chip increases.

Simulators are, in general, software tools. The platform in which the simulator executes is defined as the *host*, and the architecture simulated is called the *target*. The host platform can be any architecture and does not need to be tied with the target. For instance, the host platform can be a x86 machine, and

the target a PowerPC architecture.

### II.A Level of simulation detail

Simulation can be performed at various levels of detail, depending on the type of study to be done and also the amount of accuracy required. At the lowest level, a micro-architecture can be modeled at the circuit level, to verify and understand the behavior of the transistors implementing the system. Executing simulations at this level of detail is extremely slow, and not practical for a typical computer architecture study, where many millions of instructions are executed. A common practice is to use circuit-level simulators to derive analytical models, which are then used along with simulators that model the architecture at higher levels of abstraction 40. At a higher level of abstraction there are also gate-level simulators. These simulators do not model circuits, but structures such as AND or XOR gates and their wire interconnections. Above gate-level, one can find RTL (register transfer level) simulators. These model structures such as adders and multipliers, and registers. The registers store intermediate results between computations. A common way to specify an RTL model is to use hardware description languages (e.g. VHDL). Instead of connecting gates with wires, higher level statements, such as reg0 = reg1 + reg2, describe the implementation of the architecture. Above the RTL level, there are detailed cycle-accurate simulators. These simulators model the behavior of micro-architectural structures and their inter-connection, on a per-cycle basis. These models are usually implemented by high-level languages such as C/C++. Typical micro-architectural structures present in these models are caches, instruction queues, re-order buffers, branch predictor tables, etc. At this level, the internal implementation of these structures is irrelevant, and only the time to perform operations and the functionality are modeled. For instance, users of cycle-accurate simulators do not care how

| Level of detail | What is modeled                                   |

|-----------------|---------------------------------------------------|

| Circuit         | transistor behavior                               |

| Gate            | gates (AND, OR, etc) and wires                    |

| RTL             | registers and arithmetic structures (ADDERs,      |

|                 | MUXes, etc)                                       |

| cycle-accurate  | micro-architecture structures (branch predictors, |

|                 | instruction queues, caches, re-order buffers)     |

| functional      | programmer visible structures (registers          |

|                 | and memory)                                       |

| analytical      | abstract structures (queues, servers, etc)        |

Table II.1: Levels of detail for architecture simulation

many gates are used for implementing a cache. Instead they care whether a given address is a hit or miss, as well as the latency and power to access it. Functional simulators implement yet another level of abstraction, where no internal microarchitectural structures are modeled. Rather, only programmer-visible structures exist. Finally, there are analytical models, which use theories such as queuing models or petri-nets, for instance, to model the behavior of the architecture. Table II.1 presents a summary of the descriptions above. The focus of this dissertation is on cycle-accurate simulation models, which are very popular in both academia and in industry, due to their accuracy in predicting performance. The next section expands on cycle-accurate and functional simulators, due to their importance in computer architecture research.

### **II.A.1** Functional simulation

Functional simulation models the functional behavior of the architecture. This involves executing or interpreting the instructions defined by the instruction set architecture (ISA) correctly. Functional simulators model the visible architectural registers and the memory states. The only goal is to correctly execute instructions from a program by updating the simulated registers and memory. Hence, no modeling of time or internal micro-architectural structures is performed.

Functional simulation is useful for many tasks. One example is characterization of the micro-architectural independent program behavior throughout the execution. By looking at basic block profiles, instructions mixes (e.g. number of integer, floating point, memory access, control instructions, etc), one can understand the nature of the program. This is useful, for example, to create input for statistical simulators [52, 26]. Functional simulators can also emulate other peripherals, in addition to the processor. This allows software developers to write code for a future hardware platform before the platform is built.

### II.A.2 Cycle-accurate (detailed) simulation

Cycle-accurate simulation not only models the functional behavior of the micro-architecture ISA, but also the timing behavior of each instruction. When executing cycle-accurate simulations, the path taken by an instruction while executing through the processor's pipeline is modeled in detail. As a result, the time to execute an instruction depends on its type (integer or floating point arithmetic, control flow, etc), and also on the state of the internal micro-architecture structures. For example, a load instruction that misses the cache will take longer to execute than one that does not. Due to the level of detail simulated, computer architecture cycle-accurate simulators are also called detailed simulators. In this dissertation these terms will be used interchangeably.

Detailed simulators are much more complex to implement, because they model the interactions between internal structures in the micro-architecture. Typically every pipeline stage is modeled. At each cycle of execution, the state of each structure is updated, and instructions advance in the pipeline according to the latencies specified by the performance model. In addition, the simulators keep track of the simulated time and statistics related to each step (e.g. cache misses, branch mispredictions). Detailed simulators usually separate the functional model from the performance model. The latter is what models the timing (e.g. latencies) and functional (e.g. branch prediction outcomes) behavior of the various structures of the micro-architecture. Since hardware structures have finite sizes, resource contention also needs to be modeled accurately. For instance, if at some point all floating point functional units are busy executing instructions, a new floating point instruction ready to dispatch has to wait for a unit to be freed before it starts executing. Also, support to flush instructions in the wrong-path of execution is required, if speculation is supported. All of this detailed modeling adds to the run-time cost of executing these simulators, which is not as high as lower level simulators, but is still significant. Cycle-accurate simulators in academia execute less than one million instructions per second.

Multi-processor cycle-accurate simulation. When simulating multiple cores of execution, the overheads are higher because work in p different processing units is modeled at every clock cycle. In addition, interactions across processors take place. For instance, a shared memory location that is written by one processor has to be invalidated in other processors' caches. This invalidation takes a given number of cycles, depending on the interconnection network. At every clock cycle the interconnection network also models the packets traveling through it. When the cycle at which the invalidation message is supposed to arrive is reached, the remote processor receives the data, causing its cache line to be invalidated. If a multi-processor simulator is implemented sequentially, there is p times as much work to do, where p is the number of processing units in the target, in addition to the work to model the inter-connection network.

### **II.A.3** Detailed simulation methodologies

There are traditionally two styles of detailed simulation: *trace-driven* and *execution-driven*.

### Trace-driven

In trace-driven simulation, as the name implies, a trace of events is fed to the simulator. For a cache simulator, an event can be a memory access event, represented by an effective address and the type of access (read or write). For a branch simulator, a trace can be a sequence of program counter values and a flag, indicating if the branch is taken or not. Traditionally, trace-driven simulation consists of three stages: trace collection, trace reduction and trace processing. The events can be collected in different ways. A common way is to use hardware support for collecting them by probing the system buses. Another way is using binary instrumentation [65, 42]. Binary instrumentation allows the registration of call-backs, which are executed during run-time. The call-backs can specify arguments through which the architectural state is passed, which is then output as traces. Trace compression can be implemented by using a standard compression algorithm (e.g. Lempel-Ziv), trace filtering (storing partial addresses, for cache lines only) or trace sampling. Uhlig and Mudge [71] present a comprehensive survey on trace-driven memory simulation, covering techniques for collection, compression and processing.

Trace-driven simulation feeds a fixed trace of events, regardless of the feedback from the timing model. This fixed trace is the sequence of events observed when the trace was collected. Typically, only the committed path of execution is captured. As a result, speculative execution cannot be modeled. One could obviously augment the trace with alternative paths for speculation, but that adds complexity and increases the sizes of the traces. Another issue with trace-driven simulation is that it is hard to accurately model the behavior of modern processors, which execute instructions out-of-order dynamically and very aggressively. For example, for a trace of memory accesses, it is hard to model the correct latencies between memory operations accessing the cache, and in what order. This is because this information depends on aspects other than the address and the memory operation type. These other aspects are the latencies for executing other instructions, on which the memory access instruction depends, the type of the instructions, and internal structures of the pipeline. To model these correctly, more information needs to be added to the trace, which also adds complexity and increases the trace size.

In spite of the drawbacks previously described, trace-driven simulation does have its advantages. Trace-driven simulators are easy to implement, because they do not need to model the functional behavior of the architecture, but only interpret the events in the trace. The simulations are also completely reproducible, a consequence of the inflexibility inherent to the traces.

Multi-processor trace-driven simulation. Trace-driven simulation has also been used to study performance of multi-processors. On multi-processors, the interleaving of the events depend on the latencies associated with the target micro-architecture. A trace represents one possible interleaving, which occurred when it was collected. When simulating different configurations though, the interleaving can change. The changes in interleaving can result in different execution paths across the different runs. Un-protected access to data (data races) and synchronization operations are examples of such occurrences. When using traces, however, even if the interleavings change, the change does not affect the traces. This can result in inaccuracies because the traces from the various processing units deviate from the original parallel behavior, and the new parallel behavior traced is not coherent with the interleaving, because the trace is fixed. The phenomena has been defined by Dubois et al [25] as trace-shifting. It can result in incorrect logical behavior and timing predictions. Koldinger et al [35] showed that different runs in multi-processors generate different traces, and these traces result in a different number of cache misses for different cache block sizes. This is because of the variability across different runs for collecting the traces. This variability has been recently defined by Alameldeen et al [7] as space-variability. Space-variability comes from the fact that different interleavings for shared memory updates are resultant in each run. The different interleavings happen because the relative progress of threads differs from run to run when running on real hardware. This is due to differences in the environment across the runs, different OS scheduling, levels of bus congestion, arrival time for interrupts or differences in the system load when running a program on a real machine. Koldinger *et al* [35] showed that, for comparing simulation results across two cache block sizes, one has to either average out the results from the different traces, for each configuration, or compare the simulations of the same trace. They observed that when the same trace is used across configurations, the trend in cache misses is the same for all the traces. However, it must be pointed out that errors due to trace-shifting are not accounted for, and those errors can affect the results of the traced run. A technique is presented in chapter IV to account for these variations by stalling threads when the behaviors deviate, providing an error metric for the performance estimates. In addition, the technique uses execution-driven simulation, with some restrictions to guarantee determinism.

#### Execution-driven

Execution-driven simulation <sup>1</sup>, on the other hand, does not rely on a fixed trace of events. Instead, it fetches the actual instructions from the program

$<sup>^{1}</sup>$ Instruction-driven was the common term used in the 80s and early 90s; execution-driven at those times referred to what is now called direct-execution.

binary, decodes and executes them just like the real hardware would. On a branch prediction, the predicted program counter determines the next instructions to simulate. Since the actual instructions have all the information necessary to simulate its path as it advances in the pipeline, a very accurate simulation model can be built and executed. On a detailed simulator, instructions are only executed when their operands are available, and there are free hardware structures to accommodate them. Execution-driven simulation also allows accurate modeling of speculation. When a branch is mispredicted, the simulator executes the wrongpath instructions until it finds out that the path is incorrectly predicted. At that point it kills all the instructions in the wrong-path and flushes them out of the pipeline, rolling back any effect they may have enacted. The dynamic behavior of the micro-architecture is therefore modeled with much more accuracy than a trace-driven simulator. This accuracy, on the other hand, is also a disadvantage of execution-driven simulation, because of the complexity necessary to implement it.

Multi-processor execution-driven simulation. These simulators model multiple processors or cores of execution. At every clock cycle, each processor advances its own instructions in the pipeline. On top of the additional slowdowns, multi-processor simulation also suffers from non-determinism when executing multi-threaded cooperative workloads. Alameldeen *et al* [7] point out that multi-threaded workload runs on multi-processor simulators are nondeterministic across different architectural configurations. This is referred to as *space-variability*. As a result, two simulation runs cannot be compared directly because they are not guaranteed to execute the same paths, as in most singlethreaded workloads. Consequently, one does not know if the differences in performance are because of the architectural change or because different paths were executed. In single-threaded workloads, the sequence of committed instructions is usually deterministic.<sup>2</sup> As a result, comparing multi-threaded workload simulation runs in multi-processors requires a different methodology. Alameldeen et al[7] showed that for a fair comparison, each workload needs to be run for n times for the same configuration to obtain average behavior in each one of them. However, for the same configuration, simulators are deterministic, differently from real machine runs as shown by Koldinger et al [35]. To obtain variability during simulation for the same configuration, they proposed the insertion of random perturbations in the latencies to access memory. This results in variable behavior even when running the same configuration during simulation. Once a program is run for n times in each configuration, the average results can be used to make decisions. Using statistical techniques, they can choose n to give a certain confidence on the results. For very small architectural configuration changes, n can be quite large, as shown by Lepak *et al* [41]. The cost of running n times is increased run-time for performing simulations, which is now n times more expensive when using multi-threaded workloads. Given simulators' speed and length of benchmarks, the run-time cost increases quite significantly, especially when many configurations are to be explored. Barr [11] also demonstrated the variability across runs of multi-threaded benchmarks. Lepak et al [41] proposed a technique for deterministic-simulation, where a single run of a benchmark in each configuration is used to compare the runs. Their technique uses logs to guide the simulator and ensure determinism by introducing artificial stalls. A determinismstall error metric is used to estimate the error in simulation results. The simulator then ensures the same path of execution for each thread. The technique proposed in Chapter IV builds upon the same idea. However, the method to collect the logs is more efficient and can be used with large applications. The mechanism to account for the artificial stalls and compute the performance estimates is also

$<sup>^{2}</sup>$ There can be examples where this is not true. Some system calls are inherently non-deterministic. Even some libraries can change their behavior depending on the architecture configuration.

improved significantly.

# **II.B** Full-system and user-level simulation

Some benchmarks spend significant time executing operating system code. Example are I/O bound applications like TPC-C [22] and other server applications like DSS (Darwin Streaming Server) or web servers. For accurate performance modeling of these applications, it is important to execute not only the application code, but also the operating system code (e.g. system calls, interrupt handlers, etc). Full-system simulators perform detailed simulation of the user-code, shared libraries, operating system code and device-drivers as well. Hardware structures such as I/O devices, DMAs, interconnection buses, network devices, and timers need to be modeled in these simulators, so the operating system code and device-drivers execute correctly. Although very detailed, maintaining full-system simulators is a complex task. These simulators need to be capable of booting and executing un-modified operating system and device drivers code. Supporting different versions of operating systems requires constant updating of the simulators. Another obstacle for full-system simulation is the difficulty to reproduce the complex environments needed for by real applications. These applications may require special run-time license-checking mechanisms, special device drivers, they may have specific kernel dependencies, large storage requirements and elaborate installation procedures, all of which are non-trivial tasks to accomplish. Therefore, getting latest versions of some applications to run in those simulators is a time-consuming task. Hence, the complexity of such simulators is warranted only if the applications spend a significant amount of time in the OS code.

User-level simulation performs detailed simulation of the user-level (application) code and the system shared libraries only. For correctly executing programs, these simulators need to emulate the behavior of the operating system, and reflect the side effects of the system interactions in the application's execution. These side effects result from system calls, asynchronous interrupts and DMA transfers. The emulation is a complex task, but it is significantly simpler than simulating the behavior of the full machine. Typical user-level simulators, however, only emulate a limited set of system interactions, in particular system-call interactions. This is due to the tedious and time-consuming nature of the emulation. The traditional techniques for emulation are also hard to port across different operating systems because they rely on the host platform for the emulation, tying the simulator to it. Chapter III explains in detail how the traditional emulation techniques work. Furthermore, asynchronous interrupts and DMA transfers are not emulated, limiting the scope of possible applications that can be simulated. If the benchmarks to be studied do not spend significant time in the OS code, using user-level simulators is a better option because they are simpler to build, modify and maintain.

Chapter III proposes a scheme to collect logs for user-level simulation trivializing the need for emulation support. This scheme relies on a binary instrumentation tool we created. The log collection mechanism is simple, automatic and independent of the OS. Furthermore, the problems with reproducing the execution environment to run an application are minimized. If the application can run on the native environment, it can be analyzed by our tool, which creates logs to guide simulation.

# II.C Reducing the amount of simulation through sampling

Given today's simulator speeds and the dynamic instruction counts of benchmarks, it is impossible for designers to simulate full program runs in order to evaluate a new architectural enhancement. Full runs of SPEC2000 benchmarks would take, on average, more than a month to complete. On more detailed models, such as the ones used in industry, full runs of SPEC2000 benchmarks would take years. With multi-processor architecture and multi-threaded workloads, non-determinism makes the problem even worse. As a result, a lot of research has focused on techniques to reduce the amount of simulation. In particular, many have focused on techniques to simulate only selected samples of execution for a given benchmark, because of their dramatic impact on the run-time cost of running the simulations. A sample, in this context, is an interval of execution.<sup>3</sup> An interval of execution is a contiguous sequence of dynamic instructions

for a given benchmark, because of their dramatic impact on the run-time cost of running the simulations. A sample, in this context, is an interval of execution.<sup>3</sup> An interval of execution is a contiguous sequence of dynamic instructions executed by a program. The goal of sampling is to simulate enough intervals of execution that, together, capture the time-varying behavior of a program. Sampling is used to estimate some program characteristics such as the average number of instructions per cycle (IPC). The number of samples and their length determines the accuracy of the sampling mechanism. If the program does not present much time-varying behavior throughout the execution, a small number of samples should capture its behavior. If the program presents a lot of variation in its behavior over time, more samples are needed to capture them all. In order to simulate the samples of execution for a given set of programs, techniques to choose and simulate those samples are needed. This section focuses on these two aspects and first discusses how to simulate a sample. There are two methods for doing this. The first executes simulation in a fast mode, called *fast-forwarding*, up until the start of the sample. At that point, the simulation switches to a detailed simulation mode and starts collecting statistics. The second collects checkpoints of the program execution at the beginning of the samples, and later loads them into the simulator. For both methods, the architectural state at the beginning

$<sup>^{3}</sup>$ Computer architects often refer to a sample as an interval of execution. A set of samples from a program is used to estimate statistics from that program. In statistics, however, a sample usually refers to a collection of sample units or measurements.

of the sample is not the same as it would be, had the program executed detailed simulation from the beginning. This results in bias for the simulation results. This section also discusses techniques to minimize the bias.

#### **II.C.1** Reaching the simulation samples

# **Fast-forwarding**