# **UC San Diego**

## **UC San Diego Electronic Theses and Dissertations**

#### **Title**

Tackling computation uncertainty through fine-grained and predictable execution adaptivity in multicore systems

#### **Permalink**

https://escholarship.org/uc/item/22w4j8gt

#### **Author**

Yang, Chengmo

#### **Publication Date**

2010

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA, SAN DIEGO

# Tackling Computation Uncertainty through Fine-grained and Predictable Execution Adaptivity in Multicore Systems

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy

in

**Computer Engineering**

by

Chengmo Yang

## Committee in charge:

Professor Alex Orailoglu, Chair Professor Fan Chung Graham Professor Keith Marzullo Professor Michael Taylor Professor Charles W. Tu

Copyright

Chengmo Yang, 2010

All rights reserved.

| The dissertation of Chengmo Yang is approved, and it is ac-   |

|---------------------------------------------------------------|

| ceptable in quality and form for publication on microfilm and |

| electronically:                                               |

|                                                               |

|                                                               |

|                                                               |

|                                                               |

|                                                               |

|                                                               |

|                                                               |

|                                                               |

|                                                               |

|                                                               |

| Chair                                                         |

University of California, San Diego

2010

## DEDICATION

To my grandmother.

## TABLE OF CONTENTS

| Signature Pag  | • • • • • • • • • • • • • • • • • • • •  | . iii        |

|----------------|------------------------------------------|--------------|

| Dedication .   |                                          | . iv         |

| Table of Cont  | nts                                      | . v          |

| List of Figure |                                          | . viii       |

| List of Tables |                                          | . x          |

| Acknowledge    | nents                                    | . xi         |

| Vita           |                                          | . xiii       |

| Abstract of th | Dissertation                             | . xv         |

| Chapter 1      | Introduction                             | . 3<br>. 5   |

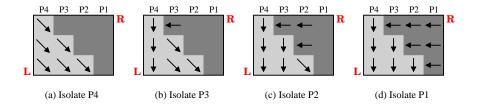

| Chapter 2      | Related Work                             | . 13<br>. 16 |

| Chapter 3      | Adaptive System Overview                 | . 23<br>. 26 |

| Chapter 4      | Core-level Reconfiguration               | . 33         |

|                | 4.2.1 PE Reordering: Problem Formulation | . 37<br>. 39 |

|                | 4.3.1 Applied to Arbitrary Task Graphs   | . 44<br>. 45 |

|           | 4.4  | Tolerating Multiple Resource Variations                   | 49  |

|-----------|------|-----------------------------------------------------------|-----|

|           |      | 4.4.1 Band Partition Extension                            |     |

|           |      | 4.4.2 Inter-task Dependence Constraints                   |     |

|           |      | 4.4.3 Core Binding Permutation                            |     |

|           |      | 4.4.4 Shiftable Core Identification                       |     |

|           | 4.5  | Algorithmic Implementation                                | 56  |

|           |      | 4.5.1 Initial Schedule Generation                         |     |

|           |      | 4.5.2 Adaptive Schedule Optimization                      |     |

|           | 4.6  | Experimental Results                                      |     |

|           |      | 4.6.1 Performance of single-core adaptive schedules       |     |

|           |      | 4.6.2 Performance of multi-core adaptive schedules        |     |

|           | 4.7  | Conclusions                                               |     |

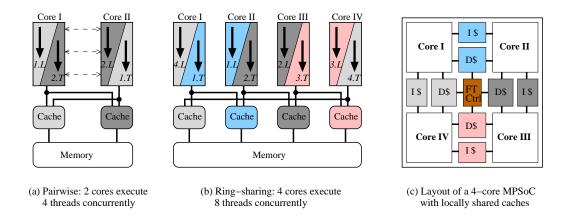

| Chapter 5 | Ada  | ptivity-aware System Topology                             | 71  |

| 1         | 5.1  | Reconfiguration-induced Sharing Requirement               |     |

|           | 5.2  | Locally Shareable Storage Organization                    |     |

|           | 5.3  | Physical Topology and Application Mapping                 |     |

|           | 0.0  | 5.3.1 Topology instances and the associated properties    |     |

|           |      | 5.3.2 Topology instance selection                         |     |

|           |      | 5.3.3 Task Placement Requirements                         |     |

|           | 5.4  | Communication Overhead Minimization                       |     |

|           | 3.1  | 5.4.1 Encoding-based Synchronization                      |     |

|           | 5.5  | Experimental Evaluation                                   |     |

|           | 3.3  | 5.5.1 Impact of Topology on Task Scheduling               |     |

|           |      | 5.5.2 Efficiency of Encoding-based Synchronization        |     |

|           | 5.6  | Conclusions                                               |     |

| Chapter 6 | Aral | nitectural-level Fault Resilience                         | 98  |

| Chapter 0 | 6.1  | Full Resilience within Low Overhead                       |     |

|           | 6.2  | Cache-based Fault Tolerance                               |     |

|           | 0.2  |                                                           |     |

|           |      | 6.2.1 Run-ahead Property for Workload Balance             |     |

|           |      | 6.2.2 Fault Detection                                     |     |

|           |      | 6.2.3 Execution Checkpointing                             |     |

|           |      | 6.2.4 Execution Recovery                                  |     |

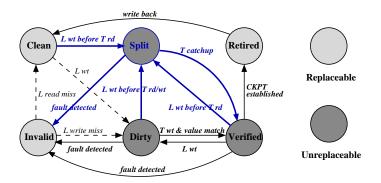

|           |      | 6.2.5 Cache State Extension                               |     |

|           |      | 6.2.6 Requirements on Memory Access Order                 |     |

|           | 6.3  | Execution Asynchronicity Enhancement                      |     |

|           |      | 6.3.1 Relaxed Thread Synchronization at Checkpoints       |     |

|           |      | 6.3.2 Selective Split Capability of Cache Blocks          |     |

|           |      | 6.3.3 Synchronization Condition Analysis                  |     |

|           | 6.4  | Fault Tolerant MPSoC Organization                         |     |

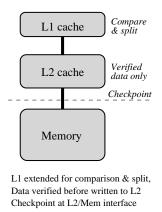

|           |      | 6.4.1 Checkpointing Tradeoffs in Multi-level Cache Design | 114 |

|           |      | 6.4.2 Checkpoint Coordination for Inter-thread Communi-   |     |

|           |      | cations                                                   | 115 |

|              |      | 6.4.3 Throughput Enhancement through Multi-threading 117 |

|--------------|------|----------------------------------------------------------|

|              | 6.5  | Cache Access Control Implementation                      |

|              |      | 6.5.1 Cache Access Control                               |

|              |      | 6.5.2 Implementation Efficiency                          |

|              | 6.6  | Simulation Results                                       |

|              |      | 6.6.1 Checkpointing and Writeback Frequencies 123        |

|              |      | 6.6.2 Thread performance                                 |

|              |      | 6.6.3 Impact of Fault Rate on Thread Performance 129     |

|              |      | 6.6.4 Checkpointing Tradeoffs for Memory Hierarchy 130   |

|              | 6.7  | Conclusions                                              |

| Chapter 7    | Com  | piler-Directed Heat Reduction                            |

|              | 7.1  | Challenges in Register Access Balance                    |

|              | 7.2  | Deterministic Register Shuffling                         |

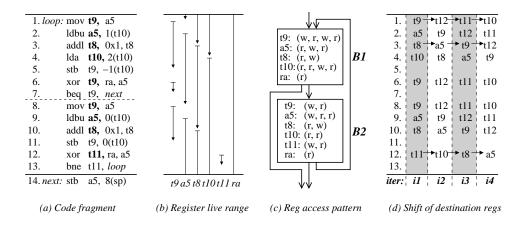

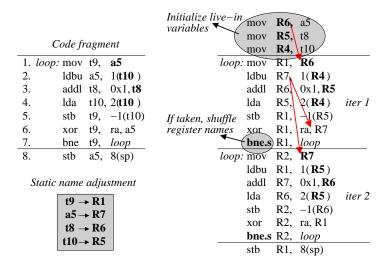

|              |      | 7.2.1 An illustrative example                            |

|              |      | 7.2.2 Destination register name adjustment 137           |

|              |      | 7.2.3 Loop-carried dependence preservation 139           |

|              |      | 7.2.4 Shiftable logical register identification 141      |

|              |      | 7.2.5 Physical register reallocability analysis 142      |

|              |      | 7.2.6 Functional Evaluation                              |

|              | 7.3  | Implementation                                           |

|              |      | 7.3.1 Static register name adjustment 146                |

|              |      | 7.3.2 Dynamic register name shuffling 147                |

|              | 7.4  | Simulation Results                                       |

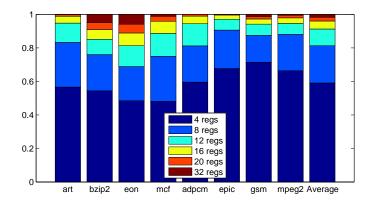

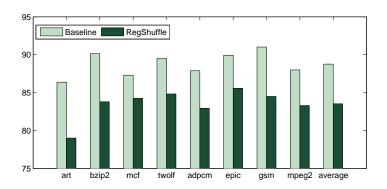

|              |      | 7.4.1 Register Access Results                            |

|              |      | 7.4.2 Temperature Results                                |

|              | 7.5  | Conclusions                                              |

| Chapter 8    | Cond | elusions                                                 |

| •            | 8.1  | Future Work Directions                                   |

| Bibliography |      |                                                          |

## LIST OF FIGURES

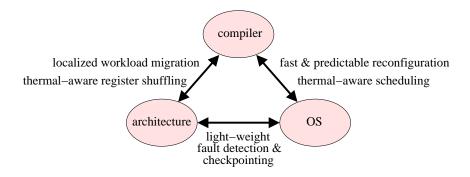

| Figure 3.1:  | Collaborative Optimization Framwork                                                                 | 24 |

|--------------|-----------------------------------------------------------------------------------------------------|----|

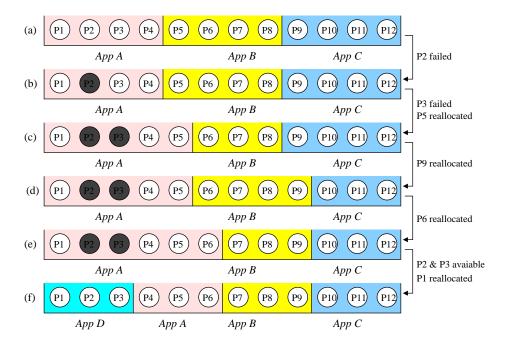

| Figure 3.2:  | Various scenarios for utilizing adaptive execution                                                  | 30 |

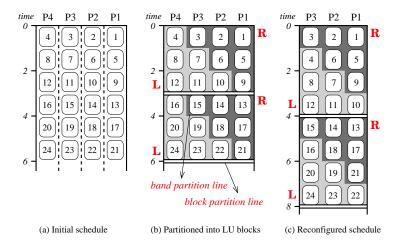

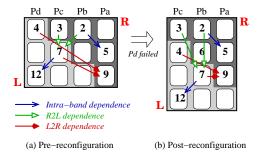

| Figure 4.1:  | Reconfigurable static schedules: band structure                                                     | 34 |

| Figure 4.2:  | Regularity in task reassignment                                                                     | 35 |

| Figure 4.3:  | Timing variations of inter-task dependences                                                         | 36 |

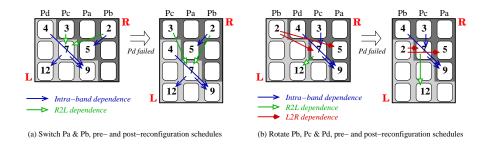

| Figure 4.4:  | Impact of PE reordering on dependence directions                                                    | 38 |

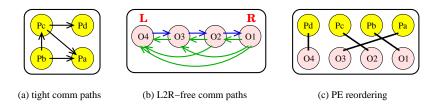

| Figure 4.5:  | PE reordering formulated as graph embedding                                                         | 39 |

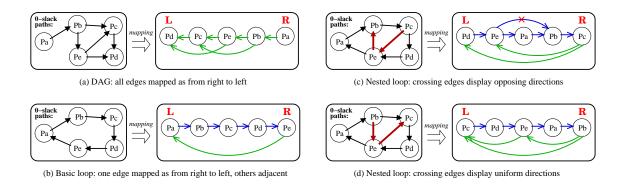

| Figure 4.6:  | L2R-free mapping of DAG, basic loop and nested loops                                                | 41 |

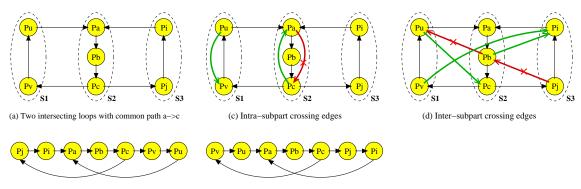

| Figure 4.7:  | Mapping constraints of intersecting loops                                                           | 43 |

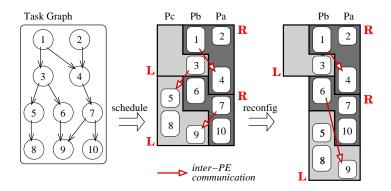

| Figure 4.8:  | An adaptive schedule for an arbitrary task graph                                                    | 45 |

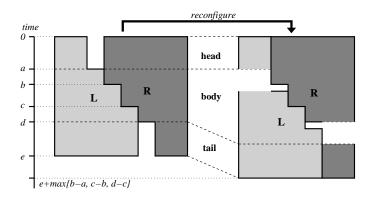

| Figure 4.9:  | Band structure extension: the head and tail regions                                                 | 46 |

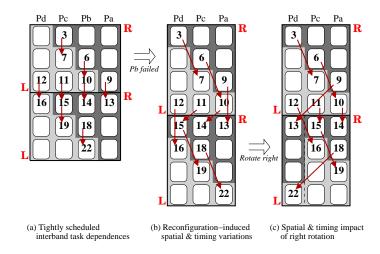

| Figure 4.10: | Impact of PE rotation on inter-PE communications                                                    | 48 |

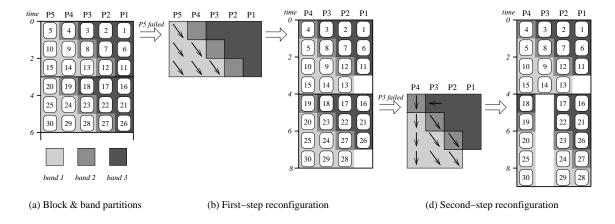

| Figure 4.11: | Multi-band partitioning for increased amount of adaptivity                                          | 50 |

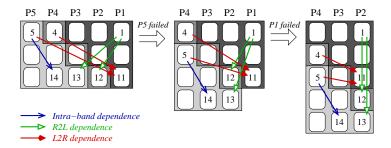

| Figure 4.12: | Inter-task dependence timing in a multi-band schedule                                               | 52 |

| Figure 4.13: | PE reordering in a multi-band schedule                                                              | 54 |

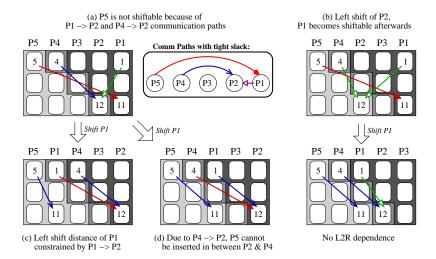

| Figure 4.14: | PE shiftability constraints and a indirectly shiftable case                                         | 55 |

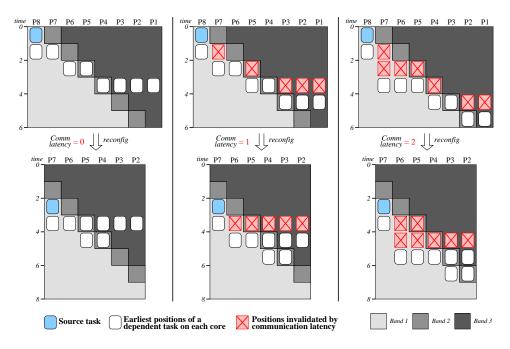

| Figure 4.15: | Impact of PE-distance and communication latency on the earliest start                               |    |

|              | time of a sink task                                                                                 | 59 |

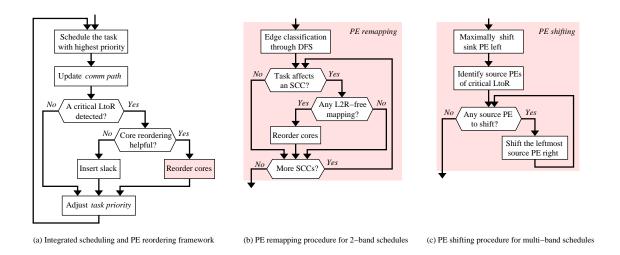

| Figure 4.16: | Integrated task scheduling and core reordering flow                                                 | 60 |

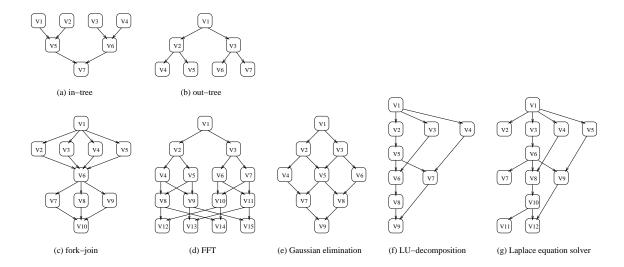

| Figure 4.17: | The benchmark task graphs                                                                           | 63 |

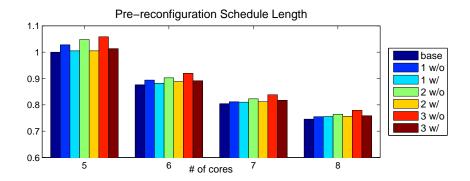

| Figure 4.18: | Impact of adaptivity degree and core reordering on <b>pre-</b> reconfiguration schedule length      | 68 |

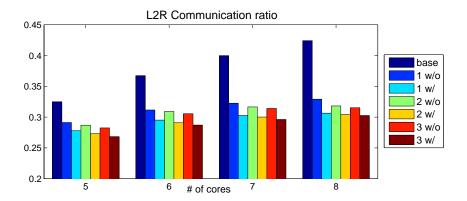

| Figure 4.19: | Impact of adaptivity degree and core reordering on the amount of                                    |    |

|              | L2R communications                                                                                  | 68 |

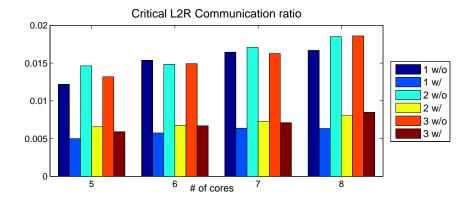

| Figure 4.20: | Impact of adaptivity degree and core reordering on the amount of <b>critical L2R</b> communications | 69 |

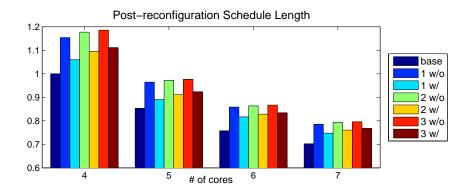

| Figure 4.21: | Impact of adaptivity degree and core reordering on <b>post-</b> reconfiguration                     | 0, |

| 118010       | schedule length                                                                                     | 69 |

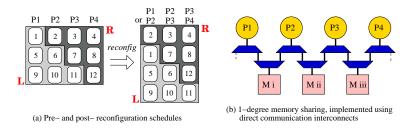

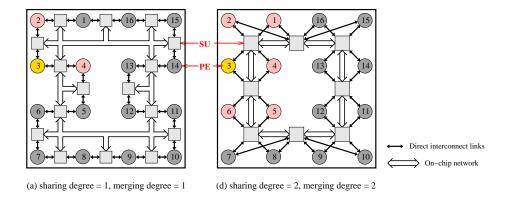

| Figure 5.1:  | Reconfiguration-induced sharing requirements                                                        | 72 |

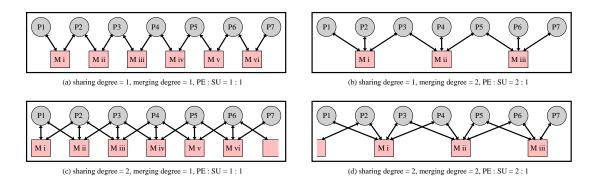

| Figure 5.2:  | Bipartite graph representation of various topologies with distinct val-                             |    |

|              | ues of sharing degree and merging degree                                                            | 74 |

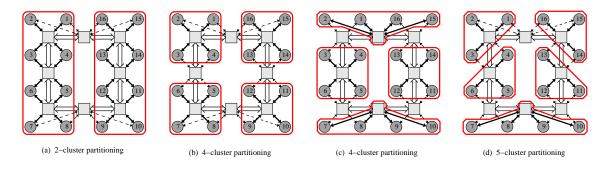

| Figure 5.3:  | Various 2-dimensional locally shareable MPSoC topologies                                            | 77 |

| Figure 5.4:  | Finer-grained cluster partitions and communication link utilization                                 | 79 |

| Figure 5.5:  | Reconfiguration-induced memory sharing and data placement                                           | 82 |

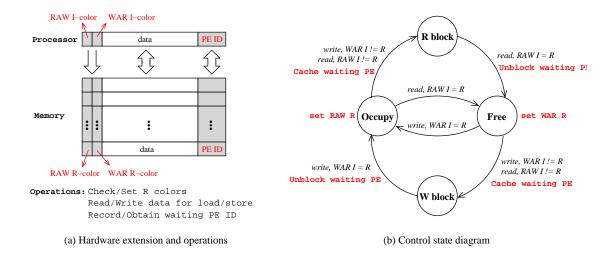

| Figure 5.6:  | Encoding of point-to-point inter-PE communications                                                  | 85 |

| Figure 5.7:  | Implementation of the encoding-based synchronization scheme                                         | 88 |

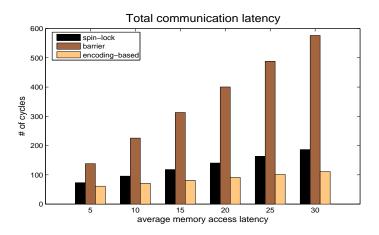

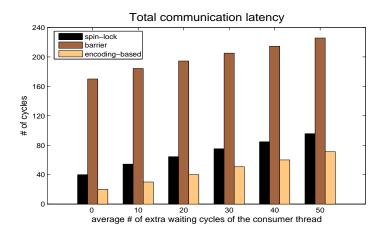

| Figure 5.8:  | Total communication latency, assuming the average number of extra                                   |    |

|              | cycles spent in waiting for the consumer thread of 50                                               | 95 |

| Figure 5.9:  | Total communication latency, assuming an average memory access                                      |    |

|              | latency of 10 cycles                                                                                | 96 |

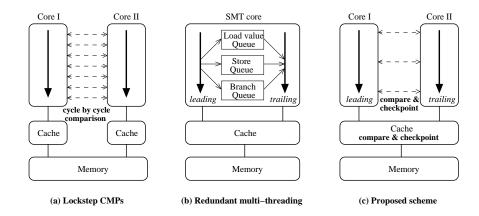

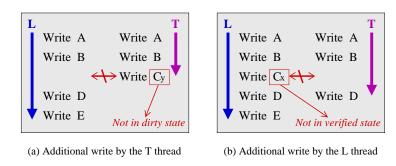

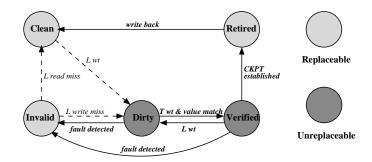

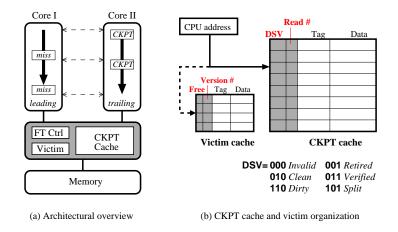

| Figure 6.1: | Differences between lockstep CMP, redundant multi-threading, and   |     |

|-------------|--------------------------------------------------------------------|-----|

|             | the proposed cache-based detection/checkpointing scheme            | 100 |

| Figure 6.2: | Inconsistent access pattern caused by faults in store addresses    | 103 |

| Figure 6.3: | Loop with cache block dependences                                  | 105 |

| Figure 6.4: | Cache states extended for fault detection and checkpointing        | 107 |

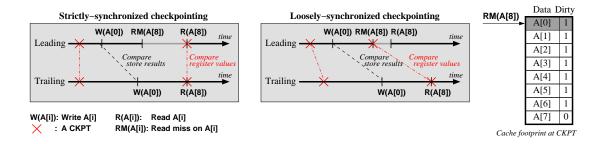

| Figure 6.5: | Strictly vs. loosely- synchronized checkpointing                   | 109 |

| Figure 6.6: | Adding a <i>split</i> state to cache state diagram                 | 111 |

| Figure 6.7: | Hybrid detection and checkpointing policy in multi-level caches    | 115 |

| Figure 6.8: | Applying the proposed shared cache organization to multi-core SoCs | 116 |

| Figure 6.9: | Hardware extension to traditional cache                            | 118 |

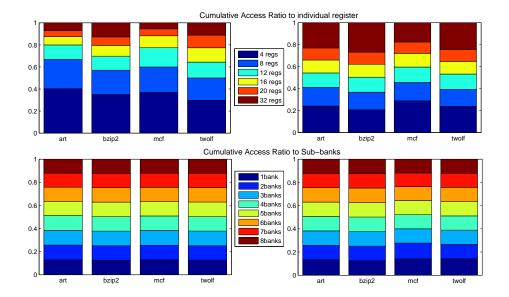

| Figure 7.1: | Cumulative register access ratio                                   | 134 |

| Figure 7.2: | A loop example obtained from <i>bzip2</i>                          | 135 |

| Figure 7.3: | Register name adjustment in two consecutive iterations             | 140 |

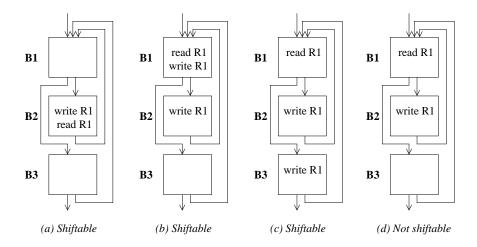

| Figure 7.4: | Shiftability analysis of register <i>R1</i>                        | 141 |

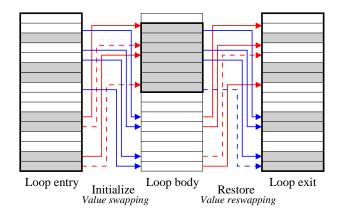

| Figure 7.5: | Building a shuffle window through swapping register values at loop |     |

|             | entry and exit                                                     | 144 |

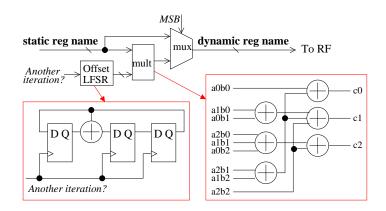

| Figure 7.6: | Gate-level logic for translating register names                    | 148 |

| Figure 7.7: | Reduction in peak temperature of the entire chip                   | 152 |

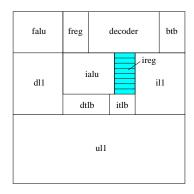

| Figure 7.8: | The processor floorplan used in simulation                         | 153 |

| Figure 7.9: | Reduction in peak temperature of the entire chip                   | 154 |

## LIST OF TABLES

| Table 4.1:  | <b>Pre-reconfiguration</b> schedule length                                       | 64  |

|-------------|----------------------------------------------------------------------------------|-----|

| Table 4.2:  | Impact of adaptivity on inter-PE communications                                  |     |

| Table 4.3:  | Impact of PE reordering on L2R communications                                    | 66  |

| Table 4.4:  | Post-reconfiguration schedule length                                             | 67  |

| Table 5.1:  | The dynamic check/set of the <i>R-colors</i> for communication synchro-          |     |

|             | nization                                                                         | 90  |

| Table 5.2:  | Impact of MPSoC topology on schedule length                                      | 91  |

| Table 5.3:  | Impact of MPSoC topology on task mapping                                         |     |

| Table 6.1:  | Impact of cache configuration on miss rate                                       | 122 |

| Table 6.2:  | Impact of cache configuration on checkpointing frequency                         | 123 |

| Table 6.3:  | Overall writeback rate                                                           | 124 |

| Table 6.4:  | Checkpointing-induced writeback increase                                         | 125 |

| Table 6.5:  | Impact of thread synchronization and block split on CPI increase (%):            |     |

|             | 16K-2way                                                                         | 126 |

| Table 6.6:  | Impact of thread synchronization and block split on CPI increase (%):            |     |

|             | 32K-4way                                                                         | 127 |

| Table 6.7:  | Cache Block Split Efficiency                                                     |     |

| Table 6.8:  | Impact of counter and victim cache sizes on CPI increase (%)                     |     |

| Table 6.9:  | Impact of fault rate on CPI increase (%)                                         |     |

| Table 6.10: | Memory hierarchy induced checkpointing tradeoffs                                 |     |

| Table 7.1:  | The use of the two shuffle functions to shift register names in the <i>bzip2</i> |     |

|             | example                                                                          | 139 |

| Table 7.2:  | Access pattern-based register classification                                     | 143 |

| Table 7.3:  | The design complexity of GF multipliers                                          |     |

| Table 7.4:  | The number of hot loops, their occupancy in execution time, and reg-             |     |

|             | ister usage information                                                          | 151 |

|             | <del>-</del>                                                                     |     |

#### **ACKNOWLEDGEMENTS**

I would like to express my deepest thanks to my advisor, Professor Alex Orailoglu, for the great guidance he provided during my PhD years. Through multiple drafts, many debates and many long nights, his guidance has proved to be invaluable. His enthusiasm and intelligence in research is always a model for me to follow in my future research work.

I would also express my special thanks to Professor Keith Marzullo, for his effort in teaching me ukulele. The days we spent together playing and singing have brought a lot of happiness to my PhD life.

Many thanks go to the other professors I have met during the seven years in UCSD, as well as my academic siblings in the *Architecture, Reliability, and Testing* (ART) group, including Baris Arslan, Garo Bournoutian, Mingjing Chen, Kwangyoon Lee, Wenjing Rao, Peter Petrov, and Ozgur Sinanoglu.

I also want to thank my friends, Zheng Wu, Shan Yan, Haichang Sui, Dayou Zhou, Yuzhe Jin, Min Li, Junwen Wu, and many others, for sharing with me the unforgettable life in San Diego.

In the end, I want to thank my parents and my grandparents, for always being there. Without their love, support, tolerance and advice, I would never have gone so far.

The text of Chapter 4, is in part a reprint of the material as it appears in *C. Yang and A. Orailoglu*, "Predictable Execution Adaptivity through Embedding Dynamic Reconfigurability into Static MPSoC Schedules," International Conference on Hardware/Software Codesign and System Synthesis (CODES-ISSS), October 2007; in C. Yang and A. Orailoglu, "Towards No-cost Adaptive MPSoC Static Schedules through Exploitation of Logical-tophysical Core Mapping Latitude," IEEE Design, Automation and Test in Europe (DATE), April 2009; and in C. Yang and A. Orailoglu, "Fully Adaptive Multicore Architectures through Statically-directed Dynamic Execution Reconfigurations," International Conference on VLSI and System-on-Chip (VLSI-SoC), September 2010. The dissertation author was the primary researcher and author of the publications [94], [97], and [98].

The text of Chapter 5, is in part a reprint of the material as it appears in C. Yang and A. Orailoglu, "Light-weight Synchronization for Inter-processor Communication Accel-

eration on Embedded MPSoCs," International Conference on Compilers, Architecture, and Synthesis for Embedded Systems (CASES), October 2007. The dissertation author was the primary researcher and author of the publication [93].

The text of Chapter 6, is in part a reprint of the material as it appears in *C. Yang and A. Orailoglu*, "A Light-weight Cache-based Fault Detection and Checkpointing Scheme for MPSoCs Enabling Relaxed Execution Synchronization," International Conference on Compilers, Architecture, and Synthesis for Embedded Systems (CASES), October 2008. The dissertation author was the primary researcher and author of the publication [95].

The text of Chapter 7, is in part a reprint of the material as it appears in *C. Yang and A. Orailoglu*, "Processor Reliability Enhancement through Compiler-Directed Register File Peak Temperature Reduction," International Conference on Dependable Systems and Networks (DSN), June 2009. The dissertation author was the primary researcher and author of the publication [96].

#### **VITA**

| 2003        | B. S. in Microelectronics, Peking University, China                                                     |

|-------------|---------------------------------------------------------------------------------------------------------|

| 2005        | M. S. in Computer Science, University of California, San Diego                                          |

| 2004 – 2010 | Teaching Assistant. Department of Computer Science and Engineering, University of California, San Diego |

| 2004 – 2010 | Research Assistant. Department of Computer Science and Engineering, University of California, San Diego |

| 2010        | Ph. D. in Computer Engineering, University of California, San Diego                                     |

#### **PUBLICATIONS**

#### Journal papers

- C. Yang and A. Orailoglu, "Full Fault Resilience and Relaxed Synchronization Requirements at the Cache-Memory Interface," to appear in *IEEE Trans. on Very Large Scale Integration Systems (TVLSI)*

- C. Yang, M. Chen, and A. Orailoglu, "Minimizing On-chip Code Storage in Microcoded IPs while Delivering High Decompression Speed," to appear in the special issue of the Journal on Design Automation for Embedded Systems

- C. Yang and A. Orailoglu, "Tackling Resource Variations through Adaptive MPSoC Execution Frameworks," submitted to *IEEE Trans. on Computers*

#### **Conference papers**

- C. Yang and A. Orailoglu, "Fully Adaptive Multicore Architectures through Statically-directed Dynamic Execution Reconfigurations," to appear in *International Conference on VLSI and System-on-Chip (VLSI-SoC)*, September 2010

- C. Yang, C. J. Xue, and A. Orailoglu, "Fine-grained Adaptive CMP Cache Sharing through Access History Exploitation" to appear in *International Conference on VLSI and System-on-Chip (VLSI-SoC)*, September 2010

- C. Yang, M. Chen, and A. Orailoglu, "Squashing Microcode Stores to Size in Embedded Systems while Delivering Rapid Microcode Accesses," in *International Conference on Hardware/Software Codesign and System Synthesis (CODES-ISSS)*, pp. 249-256, October 2009 (best paper nomination)

- C. Yang and A. Orailoglu, "Processor Reliability Enhancement through Compiler-Directed Register File Peak Temperature Reduction," in *International Conference on Dependable Systems and Networks (DSN)*, pp. 468-477, June 2009

- C. Yang and A. Orailoglu, "Towards No-cost Adaptive MPSoC Static Schedules through Exploitation of Logical-to-physical Core Mapping Latitude," in *IEEE Design, Automation and Test in Europe (DATE)*, pp. 63-68, April 2009

- C. Yang and A. Orailoglu, "A Light-weight Cache-based Fault Detection and Checkpointing Scheme for MPSoCs Enabling Relaxed Execution Synchronization," in *International Conference on Compilers, Architecture, and Synthesis for Embedded Systems (CASES)*, pp. 11-20, October 2008

- C. Yang and A. Orailoglu, "Predictable Execution Adaptivity through Embedding Dynamic Reconfigurability into Static MPSoC Schedules," in *International Conference on Hardware/Software Codesign and System Synthesis (CODES-ISSS)*, pp. 15-20, October 2007

- C. Yang and A. Orailoglu, "Light-weight Synchronization for Inter-processor Communication Acceleration on Embedded MPSoCs," in *International Conference on Compilers, Architecture, and Synthesis for Embedded Systems (CASES)*, pp. 150-154, October 2007

- C. Yang and A. Orailoglu, "Power-efficient Branch Prediction through Early Identification of Branch Addresses," in *International Conference on Compilers, Architecture, and Synthesis for Embedded Systems (CASES)*, pp. 169-178, October 2006

- C. Yang and A. Orailoglu, "Power-efficient Instruction Delivery through Trace Reuse," in the 15th International Conference on Parallel Architectures and Compilation Techniques (PACT), pp. 192-201, September 2006

#### Workshop paper

C. Yang and A. Orailoglu, "Accelerating Coupled Applications through Register Level Communication between Processing Elements," in *the 4th Workshop on Application Specific Processors (WASP)*, pp. 51-59, September 2005

#### ABSTRACT OF THE DISSERTATION

### Tackling Computation Uncertainty through Fine-grained and Predictable Execution Adaptivity in Multicore Systems

by

#### Chengmo Yang

Doctor of Philosophy in Computer Engineering

University of California, San Diego, 2010

Professor Alex Orailoglu, Chair

The continued scaling of silicon fabrication technologies has enabled the integration of dozens of processing cores on a single chip in the next computer generation. Our ability to exploit such computational power, however, is checkmated not only by limitations of parallelism extraction techniques, but furthermore by increasing levels of *execution uncertainty* within the system. As device feature sizes scale below 45nm, reliability has rapidly moved to the forefront of concerns for leading semiconductor companies, with the main challenge being the scaling of system performance while meeting power and reliability budgets. To make things worse, such an unreliable computational fabric is used to concurrently execute an increasing number of applications that constantly vie for execution resources, thus furthermore making the execution environment more dynamic and unpredictable.

The unreliability in the electronic fabric, in conjunction with the unpredictability in the execution process, has motivated the incorporation of **execution adaptivity** in future multicore systems, so that computational resources can be frequently renegotiated at run-time. The challenge, however, is to attain adaptivity in conjunction with the goals that designers already face, such as computation efficiency, power and thermal management, and predictability of worst-case performance. The traditional approaches of providing adaptivity at runtime dynamically will fail to scale as we move to systems of dozens of cores. Neither do static techniques that rely solely on compiler analysis deliver efficient adaptivity though. Instead, I have proposed a set of *compiler-directed run-time optimization* techniques that can combine the advantages of both, capable of reacting to unpredictable events while at the same time exploiting intensive program information to guide runtime decisions.

Technically, this thesis addresses the increasing levels of execution uncertainty in future multicore systems induced by device failures, heat buildups, or resource competitions from three aspects. It presents several tightly-coupled techniques to either 1) maximally mitigate a source of uncertainty, such as thermal stress, or 2) precisely detect resource variations, especially the ones induced by device failures, and then 3) quickly reconfigure the execution in a predictable manner with no reliance on spare units. These techniques are developed with the considerations of minimizing power and performance impact, localizing communication and migration so as to satisfy interconnect constraints, and ensuring high predictability so as to meet worst-case performance constraints of mission-critical applications. The successful incorporation of these techniques in future multicore systems, I believe, will engender adaptive, scalable architectures that can seamlessly reshape execution paths and schedules in an amortizable, high-volume, fixed-silicon fabric.

# Chapter 1

# Introduction

Over the past several decades, advances in silicon fabrication technologies have enabled dramatic advances in computer systems. Geometrical scaling of device sizes and die sizes has enabled the number of transistors per chip to double roughly every 24 months as stated in the well known Moore's law. The tremendous number of transistors imposes numerous technology challenges at the same time. Efficient utilization of the existing and ever increasing computational power necessitates the development of well organized systems that can efficiently extract the potential parallelism of applications. Meanwhile, technology scaling also makes devices more vulnerable to various failure mechanisms, imposing severe reliability challenges.

As single-processor systems built upon superscalar or very long instruction word (VLIW) architectures fail to respond to the well-known parallelism challenge, single-chip implementations of multiprocessor SoCs including CPUs, memories and communication architectures have become more and more popular. Examples include Stanford's Hydra [36], MIT's Raw [84], IBM's Cell [48], Sun's Niagara [50], and AMD's Opteron [52]. With the number of cores per die projected to double every two technology generations according to ITRS reports [2], chips of 100s to 1000s of cores are expected to be used even in common consumer applications of the next decade [2].

While currently multicore platforms are preferentially used for server and desktop systems, in the near future, they are expected [2] to be widely employed by various types of systems, including defense, consumer, medical, and networking/communication. The drastic increase in the number of available cores tempts designers to construct systems

that can run a large number of applications in parallel, while a dramatic increase in the diversity and the complexity of these applications is also expected. Efficient utilization of the ample hardware resources requires these applications to be decomposed into fine-grained concurrent tasks. Yet at different program phases, these applications typically exhibit diverse amounts of parallelism [92]. As a result, high levels of variability are expected both in the number of applications and in the number of cores an application needs. In such a dynamic execution environment, computation needs to be organized in an adaptive manner so that resource demands of various applications can be constantly renegotiated at run-time.

Yet the issue of application diversity is not the only aspect that is dictating the need for an adaptive organization of computations. The aforementioned degradation in device reliability may end up creating large variations in run-time resource availability, thus reinforcing the need for execution adaptivity. With the device shrinking projected to reach beyond 18nm in scale by 2015 [1], issues that were considered as second-order effects in the past, such as Soft-breakdowns (SBD) in device gate oxide, Negative Bias Temperature Instability (NBTI) in PMOS threshold voltage, Electro-Migration (EM) in copper interconnects, and dielectric breakdown in low-k materials [11], become clear threats for systems in near future technologies. These accentuated electronic effects may cause irreversible damage to a device, leading to permanent faults. Meanwhile, transient faults, which can be caused by alpha-particle strikes, cosmic rays, or radiation from radioactive atoms [47], are also expected to increase by orders of magnitude due to the reduced voltage and the resultant tighter noise margins. In fact, single event upset caused by cosmic particles has already been observed in large amounts in memory systems and sequential logic state elements. Similar transient faults have started to be observed in combinational logic as well [47, 78].

Not only is the fault rate projected to be high, but also a high variance in the duration of fault manifestation is to be expected in future computer systems. In particular, technology experts warn about an increase in *intermittent faults* – faults which occur frequently and irregularly for a period of time, commonly due to process variation or in-progress wear-out, combined with voltage and temperature fluctuations among other factors [12, 22]. These factors together cause the duration of fault manifestation to vary across a wide range of timescales. For instance, voltage fluctuations are typically

short-lived, on the order of several to hundreds of nanoseconds [12, 43]. Temperature fluctuations alter a device's timing characteristics over millisecond to second time scales [69]. Finally, as wear-out progresses over the course of days, it may even cause intermittent faults to become frequent enough to be classified as permanent [22]. Such a diverse behavior of fault manifestation brings further challenges to system designers. Fault tolerant solutions proposed solely for permanent or for transient faults become insufficient, as they rely on a fault to consistently manifest or never re-manifest itself. Instead, cost-effective solutions capable of uniformly detecting all faults, identifying the fault type, and then adaptively recovering the execution are necessitated.

The aforementioned reliability issues become even more severe when the impact of temperature is considered. While thermal buildup [55] even now is a significant concern, it will exacerbate as a result of the continuous scaling of circuit current, clock speed and device density. As higher temperature accelerates the chemical processes taking place inside the chip, the system will become more vulnerable to failure mechanisms such as electromigration and dielectric breakdown [11]. It has been reported that a mere  $10 - 15^{\circ}C$  rise in the operating temperature could halve the life span of the circuit [87]. Higher temperature also reduces the mobility of the charge carriers, thus diminishing the switching speed of the transistors. The amount of delay faults is expected to double [34] for every  $10^{\circ}C$  increase in temperature. Moreover, as every  $20^{\circ}C$  increase in temperature causes a 5-6% increase in Elmore delay in interconnects [5], clock skew problems also become noticeable for temperature spatial variations of around  $20^{\circ}C$  and above. Finally, these reliability and performance issues are worsened by the positive feedback loop between temperature and leakage power; leakage current is exponentially related to temperature, exacerbating further the effects of the positive feedback.

## 1.1 Need for Execution Adaptivity

The projected degradation in device reliability, in conjunction with the high variability in application resource utilization, imposes stringent requirements for future multicore and many-core systems to display *execution adaptivity*. In the face of failing cores, it will be out of necessity to suspend the failing computation. In the face of thermal stress, it is preferable to shut or cool down the cores approaching thermal buildup thresholds, thus

in turn diminishing the extent of the factors that contribute to fault occurrences. Finally, in the face of resource competitions, the reallocation of one application's resource in favor of another application will boost overall throughput of the system. Not only will future multicore platforms be adaptive in the sense of deallocating cores, but conversely they will be adaptive in the sense of pulling cores back into operation once the fault durations have elapsed, heat driven throttling needs have abated, or resource competition pressures have diminished.

Frequent renegotiation of resources is not the only capability an adaptive system needs to have, though. While renegotiation addresses runtime resource variations from a "recovery" perspective, techniques capable of "detecting" resource variations or even "precluding" their occurrences are also indispensable. Prevention and detection may be easily achievable for certain causes of variations, such as resource competitions, as they can be directly monitored by the operating system (OS). If a global view of the application resource requirements is available, the OS may even be able to pre-adjust resource footprints to prevent a potential competition. In an analogous manner, heat-induced resource variations can also be quickly detected, as long as on-chip temperature sensors have been pre-fabricated. Moreover, as temperature is a function of power density and floorplan characteristics [41], a potential thermal stress can be prevented through either reducing power consumption in the most-overheated components, or deterministically controlling their access activity to balance power density.

Compared to resource competitions and thermal stress, the occurrence of execution faults is completely unpredictable and cannot be directly prevented.<sup>1</sup> Instead, a highly efficient detection mechanism, capable of scaling to the projected high fault rate is necessitated. Given the highly variable fault duration, techniques proposed solely for permanent faults [7, 79] or for transient faults [66, 72, 73] are insufficient. Circuit level replication techniques, such as Razor [28], fail to respond to the challenges imposed by the highly variable manifestations of the faults given their high cost and inflexibility. Instead, an architectural-level technique, capable of delivering full fault detection capability within minimum performance and heat overhead is necessitated.

Finally, providing execution adaptivity, while a highly desirable goal, needs to

<sup>&</sup>lt;sup>1</sup>An indirect prevention of execution faults is possible, though. For instance, temperature-induced failures can be diminished through temporarily suspending the computation on a core that is sustaining thermal stress.

pay utmost attention to questions of performance, power, and system organization, if it is to be industrially relevant. Performance, which has always been of great importance, is becoming even more crucial given the projected high resource variations. Upon the detection of a variation, it is essential to minimize both the overhead in making reconfiguration decisions and the overhead in migrating computation, so as to reconfigure the execution before the next resource variation occurs. Power consumption also needs to be strictly controlled, since the solutions of variation detection and resource renegotiation should not create significant power overhead that may end up intensifying local heat buildup. Clearly, as performance, power and heat characteristics are largely determined by system organization, especially the underlying fabric topology, efficient adaptivity solutions also need to be topology-aware.

## 1.2 Challenges to be Addressed

Delivering the aforementioned execution adaptivity raises numerous technical challenges. In particular, the needs for resource renegotiation, reliability enhancement, and heat reduction should be attained in conjunction with the goals that designers already face, such as computation efficiency, power and thermal budget, and predictability of worst-case performance.

#### Fast, predictable, and localized execution reconfiguration

An adaptive multicore system should be able to reconfigure its execution to either withstand a core unavailability, or make use of a previously deallocated core once the cause of unavailability has been cleared. As variations of resource availability are expected to be frequent, the reconfiguration process should be as quick as possible. Predictability of worst-case performance also needs to be guaranteed, as multicore platforms are expected to be commonly used by deadline-driven realtime applications [2]. Meanwhile, as the interconnect cost becomes increasingly expensive in terms of both power and performance, workload migration should be confined within a neighborhood as well.

The strict requirement of fast and predictable reconfiguration cannot be straightforwardly attained through adopting pure run-time techniques [18, 26, 89]. Although these techniques naturally deliver adaptivity, the dynamic reactions waste significant com-

putation power and, due to their sub-optimal nature, unpredictably impact each application. Not only do these techniques need to collect workload information from every corner of the chip, but furthermore, the quality of reconfiguration decisions is determined by the complexity of the scheduling algorithms employed. The resultant communication and computation overhead drastically increases as the number of cores in the system grows, thus limiting the applicability of these techniques to systems of 100s of cores.

Neither do static techniques [21, 33, 44] that rely solely on compiler analysis deliver efficient adaptivity though. It is true that compared to pure run-time techniques, compiler-directed scheduling is more predictable and cost effective. Sophisticated application information can be extracted, and aggressive heuristics can be employed to globally balance the workload. However, the quality of static schedules degrades significantly in a dynamic environment. While it is possible for the compiler to generate multiple schedules that match diverse resource availability constraints, the numerous adaptivity needs are difficult to plan and compile for. The overall impact of a resource variation on a statically generated schedule is determined by the exact time at which a variation in resource availability occurs, which is essentially infeasible to predict statically.

Given the inability of pure run-time and pure compile-time techniques to deliver execution adaptivity efficiently, it is desirable to develop a *hybrid* approach that can combine the advantages of both, capable of reacting to unpredictable events while at the same time exploiting intensive program information to guide runtime decisions. Yet delivering this hybrid scheme also raises numerous technical challenges. What is the form of compiler analysis that embeds numerous reconfiguration possibilities in static schedules in a compact manner? How to localize task migration in the reconfiguration process? How is the reconfiguration process controlled by the runtime system? How to organize the underlying multicore fabric to minimize workload migration overhead? Addressing these questions requires the development of a collaborative framework between the OS, the compiler, and the architecture, with the constraint of adaptivity taking center stage in the design process.

#### Full variation detection capability within minimum overhead

To sense that an execution rearrangement is to be effected, an adaptive system also needs frugal technical support for detecting resource variations induced by faults, thermal stress, and resource competitions. Among these various issues, the detection of execution faults is most challenging. On one hand, the projected high fault rate [22, 34, 47] argues for solutions of maximal efficiency. As full fault coverage is still necessitated, however, techniques [32, 71, 88] that reduce fault detection overhead at the cost of significantly increased rates of undetectable faults are not applicable. On the other hand, the diverse behavior of fault manifestation argues for solutions capable of uniformly detecting all faults and then identifying the fault type. As the duration of fault manifestation varies over nanosecond to second time scales, detection mechanisms that rely on a fault to never re-manifest [66, 72, 73] or consistently manifest [7, 79] itself become insufficient.

Unlike regular storage structures that can be efficiently protected using Error Correcting Codes (ECC), computation at various pipeline stages typically exhibits irregular patterns, thus requiring the entire execution to be *duplicated* in order to detect arbitrary faults. Unfortunately, traditional duplication-based fault detection approaches impose significant overhead either in checking execution results, or in constantly synchronizing two computation copies for value checking [91]. While extra buffers [72, 62] can be inserted into the architecture to relax synchronization conditions, these centralized hardware structures need to be constantly accessed, thus possibly ending up becoming thermal hotspots.

The projected high fault rate additionally imposes strict requirements on the development of a light-weight checkpointing scheme. Whenever a fault is detected, the computation needs to be restarted from a previously saved clean state, i.e., a *checkpoint*. In order for the computation to progress, a new checkpoint should be established before the next fault occurs. The higher the fault rate is, the more frequently the computation needs to be checkpointed. Yet in order to checkpoint the computation more frequently, the associated computational overhead needs to be strictly controlled. Typically a checkpoint is imposed on the processor state and the corresponding memory footprint. Yet checkpointing the memory, as OS needs to be involved in, is usually a quite expensive process [13, 57] that induces significant context switch overhead. Accordingly, the development of a light-weight checkpointing scheme requires the memory to be strictly protected from being polluted by execution faults.

In summary, the development of an efficient fault detection scheme for future multicore systems of elevated rates and diverse types of faults imposes *three* requirements,

namely, attaining full detection capability within a minimum level of result comparison and hardware duplication, maximally relaxing checking-induced synchronization conditions with no reliance on any centralized hardware buffer, and minimizing checkpointing overhead through strictly protecting memory against execution faults.

#### **Maximum mitigation of thermal stress**

As the system fault rates exponentially increase as peak temperature rises, mitigation of thermal stress can in turn reduce resource unavailability induced by both heat buildup and execution faults. However, as overall system performance is still of great importance, temperature reduction should not be attained through globally stalling [15] or slowing down [80, 81] the computation of an overheated core.

As temperature is determined by power density as well as the heat dissipation speed, the temperature distribution on a chip is typically asymmetric. This asymmetry can be observed at both the core-level and the microarchitectural-level; not only may the tasks assigned to different cores exhibit diverse power behavior, but furthermore the various components of a core exhibit distinct size and access characteristics. This observation implies that peak temperature of the entire chip can be reduced through shifting computation from a hot resource to a relatively cool resource. In particular, in an adaptive system, execution schedules should be generated in such a way that the "hot" tasks are distributed across various cores at different time. Meanwhile, for each individual core, the peak temperature of the most overheated module should be strictly controlled as well.

To perform thermal-aware task scheduling, the scheduler needs to obtain extra information regarding system topology and power consumption characteristics of tasks [23]. The challenge, however, is for the scheduler to consider temperature constraints simultaneously with the other scheduling constraints, such as communication minimization, workload balance, and execution adaptivity. The resultant drastically increased scheduling complexity would impose significant computation overhead, if the scheduling process is to be performed at runtime. This observation in turn argues for a *hybrid* scheduling approach, wherein the compiler can exploit intensive program information to guide runtime decisions.

Controlling the peak temperature of each individual core requires the identification of the most overheated module. Previous research [81] indicates that the register file, due to its high utilization and relatively small area, is one of the hardware units most likely to overheat. Moreover, due to the fact that 90% of the execution time is spent on loops where only a small subset of registers is repetitively accessed, register file accesses also exhibit high asymmetry during program execution. This asymmetric register utilization may lead to considerable temperature differentials. Yet pure static register reassignment techniques [40, 100] cannot completely eliminate the access asymmetry to each individual register, since such asymmetry directly derives from the asymmetric variable utilization of the program.

Given the inability of the compiler to completely balance register accesses, a dynamic mechanism needs to be developed to physically remap heavily accessed logical registers prior to local heat buildup. Yet this task cannot be accomplished through the use of a hardware renaming table [77]. Not only does such a mapping table impose notable levels of of energy consumption, but more crucially, the table needs to be accessed using the skewed register names, at a frequency no lower than that of register file accesses, thus ending up itself becoming a temperature "hotspot". This observation indicates that the challenge for temperature-aware register remapping is to achieve this goal in a *table-free* manner; the system needs to deterministically keep track of run-time register usage and register mapping information. It is therefore necessary to establish an agreement between the compiler and the runtime remapping hardware, so that regularity can be embedded within consecutive register accesses.

#### 1.3 Contributions of This Thesis

The development of an adaptive execution framework for the next generation of computer systems is a challenging task. In particular, to address the technical challenges identified in the last section, the system needs aggressive technical support from the OS, the compiler, and the architecture. A collaborative optimization framework needs to be established.

In light of this observation, we establish in this thesis a *compiler-directed run*time optimization framework, capable of efficiently coupling static program information with runtime optimizations. Under this optimization framework, we furthermore introduce several tightly-coupled techniques that contribute to the development of reliable and adaptive multicore systems from the perspectives of *variation mitigation*, *variation detection*, *execution recovery*, as well as *architectural reorganization* for a cost-effective implementation of all these functions. The contributions of these techniques are summarized as follows:

- A compiler-directed task scheduling framework, capable of spawning regular, transformable, and high-quality execution schedules in the face of unpredictable runtime resource variations. The pre-optimized schedules can be adaptively applied upon runtime resource variations, thus delivering high-speed and low-cost reconfiguration without any rescheduling decisions needing to be made on the fly.

- A scalable and shareable storage organization, capable of delivering high-speed communications within a neighborhood. This organization enables the simultaneous migration of multiple tasks between distinct cores without inducing any interferences or network congestion. The inherent redundancy furthermore assures the connectivity of the entire platform in the case of core or interconnect failures.

- An efficient fault detection mechanism, capable of minimizing fault detection overhead while at the same time delivering full fault detection capability. Through performing fault detection and checkpointing at the cache-memory interface, two threads are able to run independently without constantly synchronizing for value checking, while the memory is strictly protected against execution faults.

- An approach to reduce system peak temperature, through exploiting useful application information to fine-tune a microarchitectural component intelligently. This technique balances power density in the most overheated components, to wit, the register file in each individual core, thus attaining temperature reduction and hence enhancing overall system reliability at almost no cost.

To ensure that adaptivity can be attained in conjunction with the goals that designers already face, all the aforementioned techniques are developed with the considerations of minimizing power and performance impact, ensuring high predictability of worst-case performance, and localizing communication and migration so as to fulfill interconnect constraints. The successful incorporation of these techniques in future multicore systems, I believe, will engender adaptive, scalable architectures that can seamlessly reshape execution paths and schedules in an amortizable, high-volume, fixed-silicon fabric.

## 1.4 Roadmap

The rest of the thesis is organized as follows. Chapter 2 reviews the current state-of-art and analyzes the limitations of existing solutions of resource management, fault tolerance, and heat reduction. Chapter 3 presents a system overview of the envisioned adaptive multicore framework, focusing on the collaboration between the OS, the compiler, and the architecture. Chapter 4 introduces a compiler-directed task scheduling framework, wherein adaptivity is directly embedded into static schedules and task migration is localized to satisfy interconnect constraints. The corresponding storage organization for minimizing migration overhead and accelerating neighborhood-centered communications is presented in Chapter 5. Chapter 6 presents an architectural fault detection and checkpointing scheme, wherein the cache design is extended to implement fault detection, checkpointing and recovery. Chapter 7 presents a compiler-directed register shuffling technique that effectively diminishes register access asymmetry with no reliance on any hardware renaming table, thus preventing local heat buildup. Finally, Chapter 8 summarizes the adaptive multicore framework and subsequently outlines a set of possible future research directions.

# Chapter 2

# **Related Work**

While the underlying computational fabrics become increasingly dynamic and unreliable, the applications to be held by these fabrics impose stricter requirements of durability and safety. Researchers therefore have started to address the increasing levels of computation uncertainty from various perspectives.

First of all, given the diversity of the possible causes of execution uncertainty, researchers have focused on the characterization of the various causes of uncertainty, including device failures and thermal stress, as well as the *modeling* of their effects on system execution. Various circuit-level fault models have been built, architectural thermal models have been constructed, and the system level fault manifestation behavior has been studied. Meanwhile, researchers have also developed various techniques to overcome execution uncertainty through either preventing a cause of uncertainty from occurring, or masking its effect, or detecting a cause and then recovering the system. The prevention strategy has been adopted for the control of chip-wide temperature, through the adjustment of the floorplan and the layout of various hardware modules, or through the adjustment of execution schedules to distribute "hot" tasks across diverse computational resources. The *masking* strategy has been adopted for the toleration of device failures at the circuit-level, while the *detection-recovery* strategy has mainly been adopted for the toleration of device failures at the architectural-level. Yet compared to thermal stress, the toleration of device failures is more challenging, particularly due to the diverse behavior in fault manifestation. A large number of fault detection mechanisms therefore have been developed. These techniques target either faults in specific components, such as storage

units or the control flow [65], or specific types of faults, such as transient faults [72] or permanent faults [79]. Additionally, once a fault has been precisely identified, it is necessary to isolate the corresponding components through a dynamic *reconfiguration* process. Researchers have therefore examined the various possibilities for reconfiguring the system at various levels, for instance, at the component level to mask permanent faults [3], or at the core level to migrate the workload [89].

Despite the existence of various types of solutions for overcoming execution uncertainty, these solutions fall short of addressing the challenges induced by not only an elevated rate, but furthermore a diverse behavior of execution uncertainty in future multicore and many-core systems. Due to the associated high overhead and the lack of predictability, these solutions fail to deliver the envisioned execution adaptivity in conjunction with the goals that designers already face, such as computation efficiency, power and thermal budget, and predictability of worst-case performance. A detailed review of the current state-of-art, as presented in the remaining parts of this chapter, clearly illustrates the limitations of existing resource renegotiation, reliability enhancement, and heat reduction techniques.

## 2.1 Resource Renegotiation

The increasing possibility of resource variations requires a reconsideration of the critical issue of scheduling the tasks of an application onto the cores of the target system. Traditionally task scheduling can be performed either dynamically at run time, or statically during compilation. The former approach delivers adaptivity straightforwardly, yet the associated high overhead challenges its scalability as we move to systems of 100s of cores and similar magnitude of concurrent tasks. The latter approach is more cost-effective and delivers worst-case predictability. Yet the numerous adaptivity needs are difficult to plan and compile for.

#### **Run-time solutions**

In dynamic scheduling, the OS is typically employed to monitor resource availability and schedule tasks (that are ready to be executed) only to available cores, thus naturally delivering resource reallocation upon runtime variations. In [18], upon a pro-

cessor failure, a *dynamic* rescheduling approach is employed to reassign its workload to the remaining available processors. A similar approach is employed in [89]. The OS is configured to use more virtual processors than the number of physical cores, thus tolerating variations in the availability of physical cores. The approach proposed in [26] adapts application execution to the varying CPU availability for the purpose of minimizing the energy-delay product (EDP). It relies on a helper thread, running in parallel with the application, to determine the ideal number of cores and the system configuration at any given point in execution.

While pure run-time techniques naturally deliver execution adaptivity, the dynamic reactions waste significant computation power and, due to their sub-optimal nature, unpredictably impact each application. More specifically, if a core becomes unavailable, its workload can be migrated either straightforwardly to its neighbor(s), or to the cores with minimum workload. The former ad-hoc decision incurs negligible overhead yet typically induces workload imbalance, since the adjacent cores may have already been assigned a significant amount of workload. In comparison, the latter decision displays more intelligence, yet imposes significant communication and computation overhead. First of all, to globally balance the workload, the dynamic scheduler needs to collect workload information from every corner of the chip. Clearly, the associated overhead drastically increases as the number of cores grows. Meanwhile, as the quality of migration decision is determined by the complexity of the scheduling algorithm employed, the generation of high quality decisions also introduces significant runtime scheduling overhead, at an amount superlinearly proportional to the number of concurrent tasks in the system. For example, the helper thread proposed in [26] needs to monitor the applications' EDP values through collecting performance counter information, and to determine the next system configuration through curve fitting methods. The resultant appreciable communication and computation overhead limits the applicability of these functions to future multi-core and many-core systems wherein the interconnect cost is projected to be high.

#### **Compile-time solutions**

Compared to pure run-time techniques, static scheduling is more cost effective, as it imposes neither run-time scheduling overhead nor communication overhead for collecting workload information. As scheduling is performed offline at compile time, not

only can sophisticated application information be extracted, but also aggressive heuristics can be employed to globally balance the workload. As a result, commercial embedded systems, such as MARS [51] and XBW [19], typically use static scheduling to ensure timing predictability and other safety-related properties, such as design simplicity and testability. However, the quality of traditional static schedules degrades significantly in a dynamic environment. In fact, when generated offline, static schedules are typically confined to the case of a fixed number of PEs, implying that a resource reduction usually dooms the entire schedule to uselessness.

To enable static schedules to tolerate resource variations, *redundancy* needs to be built within the system. As a result, traditional static scheduling techniques either keep spare processors [21] that can be used to replace failing ones, or back up each task [33, 44] so that upon the failure of the primary copy, the backup copy of the task can be invoked. The schedule should also have sufficient timing slack embedded [46, 61] so that upon a core variation, recovery and migration can be carried out before any of the tasks reaches its deadline.

Maintaining spare cores would be an efficient solution for fully connected systems, wherein one spare core is able to replace any of the remaining cores. Unfortunately, in future multicore systems of hundreds of cores, full connection is impossible, which in turn limits the replacement capability of spare cores. Computation on a failing core cannot be directly migrated to a spare core if the two are not physically adjacent. In such systems, it would be preferable to allocate more spare cores to regions of higher levels of resource variations. Unfortunately, such an allocation strategy is impossible to determine at compile time. As examined before, a core may become unavailable due to various reliability, thermal or resource competition reasons, with neither the occurrence nor the duration of unavailability being predictable *a priori*.

In the *primary-backup* approach, schedules should be generated in such a way that the primary and the backup copies are scheduled on distinct processors. To reduce the associated replication cost, backup overloading and backup deallocation are introduced in [75]. Backup copies of multiple independent tasks are allowed to be scheduled on the same or overlapping time intervals on a processor, and the resources reserved for a backup task are reclaimed when the corresponding primary tasks complete successfully. These techniques effectively improve resource utilization, while they are restricted to tolerating

only a single fault among the tasks with overlapped backup schedules.

In [58], a hierarchical scheduling approach is proposed. Task graphs are partitioned into disjoint regions, for which multiple schedules with diverse performance and power characteristics are generated. Such schedules are adaptive applied at runtime so as to explore energy-performance tradeoffs. At first sight, it seems that this approach can also be employed to overcome runtime resource variations, through the static generation of multiple schedules that match diverse resource availability constraints, followed up by a dynamic switch to a new schedule upon a variation in core availability. Unfortunately, the overhead for storing all these pre-optimized schedules in memory is quite high. More crucially, the numerous adaptivity needs are difficult to plan and compile for, since it is infeasible to predict a priori the exact time at which a variation in resource availability occurs. Due to this limitation, these pre-generated schedules exhibit no timing regularity; the execution order of tasks is not necessarily identical throughout the various schedules, implying that a switch between these schedules requires a search process for identifying the exact starting point. Neither do these schedules exhibit spatial regularity; a task may need to be shifted across multiple PEs during the reconfiguration process, thus inducing significant migration overhead and hence unpredictability of worst-case execution.

## 2.2 Reliability Enhancement

Increasing research attention has been paid to the incorporation of reliability enhancement solutions into computation systems, not only because of the elevation in fault rates, but also because durability and safety have been identified as an important design criterion for systems that hold server, defense, or medical applications. Semiconductor companies have started as well to incorporate reliability support into their newly-released designs, such as Intel *QuickPath*, and IBM *Power6* [59].

Given the severe power and cost constraints of modern multicore architectures, the need for maximally efficient fault tolerance methods becomes increasingly critical and urgent. It is thus essential to evaluate a technique not only by its *effectiveness* in detecting errors and recovering execution, but more importantly by its *efficiency* in terms of the associated performance, energy and hardware overhead.

#### **Fault detection**

In general, the detection of faults necessitates *redundancy*, at an amount inversely proportional to the regularity of the hardware components. Storage structures, such as caches and memory, have regular patterns, thus enabling the use of Error Correcting Codes (ECC) and parity bits. Faults in instructions or in control flow can also be effectively detected by *signature monitoring* techniques [65, 73] through exploiting internal redundancies. As a comparison, computation structures typically exhibit irregular patterns, thus requiring the entire execution to be *duplicated* in order to detect arbitrary faults at various pipeline stages.

Conventional duplication-based approaches employ either a *time redundancy* or a *spatial redundancy* strategy for fault detection. Time redundancy, achieved by executing a task on the *same* hardware multiple times, is only effective for transient fault detection. For instance, a number of software-based fault detection techniques replicate each instruction and add checking instructions to compare the results [73, 66]. These techniques offer the flexibility of turning redundancy on and off in the generated code, while at the same time imposing significant performance overhead due to the replication and checking of instructions. Some researchers have proposed a set of techniques [99] capable of reducing such overhead by 50%, yet at the cost of reduced fault coverage.

Space redundancy techniques, on the other hand, duplicate a single task on multiple processors. Not only transient, but furthermore intermittent and permanent faults can be detected, albeit at a cost of sizable hardware overhead. In the  $Compaq\ NonStop\ Himalaya$  system [91], each pair of redundant instructions is executed on two tightly-coupled cores on a cycle-by-cycle basis. An instruction cannot be committed until its correctness has been verified. The Dynamic Implementation Verification Architecture (DIVA) [7] employs k simple checker cores to detect errors in a k-wide superscalar processor. The BulletProof pipeline [79] uses built-in self-test to detect and precisely identify the faulty unit. As the technique relies on a fault to consistently manifest itself, it is only effective for permanent faults but not transient faults.

To attain full detection capability, previous techniques usually check all the store instructions, and hold an instruction off commitment until its correctness has been verified. This highly synchronized execution model significantly increases the latency of a

single instruction, thus delaying the release of hardware resources, such as physical registers and ROB entries in the architecture. Moreover, in the case when two redundant tasks are being executed on distinct cores [91], both copies incur mis-speculated branches and cache misses independently, leading to less efficient resource utilization and unnecessary power dissipation. To relax the lock-step execution model, extra buffers are necessitated so as to enable one thread to forward data to the other. For instance, the redundant multithreading approach (originally proposed in [72] for SMT cores and extended to CMPs in [62]) requires an *output comparator* to verify execution results, as well as an *input replicator* to ensure that both threads read identical input data. Typically these two components are implemented through two centralized shared structures, namely, a *Load Value Queue* and a *Store Queue*. However, even with these queues, the two threads still need to synchronize, as the leading thread needs to be stalled if either queue is full and the trailing thread needs to be stalled if either queue is empty.

To reduce duplication overhead, researchers have developed a set of *partial redundancy* techniques. Opportunistic Fault Tolerance [32] duplicates instructions only during periods of poor single-thread performance. ReStore [88] does not explicitly duplicate instructions yet considers mispredictions among highly confident branch predictions as symptoms of faults. Slipstream [71] combines partial duplication and confident predictions through creating a reduced alternate thread wherein many instructions are replaced with highly confident predictions. These techniques sizably reduce duplication overhead, however, at the cost of significantly increased rates of undetectable faults; faults in non-duplicated instructions cannot be detected, if they do not lead to branch mispredictions.

#### **Execution recovery**

In addition to fault detection, the achievement of fault resilience also necessitates *execution recovery* techniques, which should either preclude faults from modifying computation states, or roll the execution back to a previously saved clean state, i.e., a checkpoint upon a fault. The first strategy is typically employed together with highly-synchronized value checking. For instance, in both redundant multithreading cores [86] and lock-step multiprocessors [31], instruction results cannot be committed into registers or the cache until their correctness has been confirmed. In contrast, the *checkpointing and rollback* strategy allows results to be written into registers and the memory hierarchy

without being compared, yet needs to constantly check and save the computation state. Upon the detection of any fault, the system reloads the most recent checkpointed state to recover computation.

To establish a checkpoint, one set of techniques utilizes the virtual memory translation hardware [13], to create a backup copy before modifying any memory page. Another standard technique consists of the use of a recovery cache to record all the data written in memory that are part of a checkpoint state [57]. Every store to a memory location must be preceded by a load to maintain the data in the recovery cache. These hardware-oriented backup techniques impose not only storage but also performance overhead constantly on the system. To reduce such overhead, the CARER scheme [42] uses a normal cache with a writeback update policy to assist rapid rollback recovery. The work is subsequently extended to shared-memory multiprocessors through synchronizing the processors whenever one needs to take a checkpoint [45]. Software checkpointing [14] has also been proposed, yet at the cost of additional support required from the compiler and/or the OS.

While a single task can be checkpointed independently, a parallel application requires the coordination of dependent tasks in the checkpointing process. *Coordinated checkpointing* [17, 82] can be attained by stalling and validating all computations and communications in an ordered manner. *Uncoordinated checkpointing* [64], in contrast, is performed independently on each core. While this strategy eliminates the global synchronization requirement of coordinated checkpoints, multiple checkpoints need to be stored on each core, and the rollback process furthermore requires the identification of a checkpoint with a consistent state. To eliminate potential *domino effects* wherein no consistent checkpoint can be found, researchers have introduced extra constraints on checkpointing sequences based on, for example, the communication patterns [37] of applications.

Another set of techniques aim to continue to use a core despite permanent faults, through the use of finer-grained fault masking strategies. These techniques involve fine-grained testing, diagnosis [29], and recovery of core components. *Configurable isolation* [3] is a technique that performs reconfiguration at the micro-architectural level. When a component suffers a fault, processor resources are reallocated and partitioned dynamically so as to isolate the component and subsequently migrate its workload. *StageNetSlice* [35] is a processor core comprised of networked pipeline stages. It relies on a reconfig-

urable network of replicated processor pipeline stages to maximize the useful lifetime of the chip. In [68], the authors exploit cross-core redundancy, and use hardware to migrate offending threads to another core that can execute the operation. Clearly, the reconfigurability offered by these techniques is at the component level; the faulty functional unit, register, or cache block is isolated so that the core can still operate in a degraded performance mode.

#### 2.3 Heat Reduction

Modeling temperature and the effects of temperature on reliability is essential for the simulation and analysis of heat reduction policies. The adverse impact of operating temperature on system reliability has been studied extensively. Researchers have built either analytical or experimental models for temperature-induced fault rate increases, such as delay violations [34], negative bias temperature instability [53], neutron-induced latchup [27], and on-chip interconnect [5]. In comparison, thermal modeling is typically accomplished by constructing an equivalent RC network of the given chip. Heat flow is analogous to the current passing through a thermal resistance in the RC network. The transient behavior of temperature is modeled by means of the thermal capacitance. Architectural thermal models of this type, such as the *HotSpot* [41], have been developed for calculating transient temperature response, for the given floorplan, package, and power consumption characteristics of various components.

In general, temperature is determined by power density as well as the heat dissipation speed. A traditional approach to accelerating the latter factor is through packaging and cooling solutions. Yet such solutions have been typically targeted for the worst case peak temperature, resulting in an extremely expensive packaging cost with the ever rising temperatures (approximately \$10 per Watt above  $65^{\circ}C$ ). To keep the chip-wide temperature within the thermal capacity of the cooling package, researchers have proposed various architectural-level thermal management techniques to either reduce the access frequency to an overheated unit, or physically redistribute accesses before heat gets locally accumulated.

#### **Access frequency reduction**