# **Lawrence Berkeley National Laboratory**

# **Recent Work**

## **Title**

Low Power Shaper Amplifier for the EOS TPC Detector

## **Permalink**

https://escholarship.org/uc/item/2648g0t0

### **Authors**

Nakamura, M. Landis, D.A. Rai, G.

### **Publication Date**

1990-10-01

# Lawrence Berkeley Laboratory

UNIVERSITY OF CALIFORNIA

# Engineering Division

Presented at the IEEE Nuclear Science Symposium, Arlington, Virginia, October 23–26, 1990, and to be published in the Proceedings

# Low Power Shaper Amplifier for the EOS TPC Detector

M. Nakamura, D.A. Landis, and G. Rai

October 1990

# For Reference

Not to be taken from this room

### **DISCLAIMER**

This document was prepared as an account of work sponsored by the United States Government. While this document is believed to contain correct information, neither the United States Government nor any agency thereof, nor the Regents of the University of California, nor any of their employees, makes any warranty, express or implied, or assumes any legal responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by its trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof, or the Regents of the University of California. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof or the Regents of the University of California.

M. Nakamura, D.A. Landis, and G. Rai Lawrence Berkeley Laboratory University of California Berkeley, CA 94720

October 1990

This work was supported by the Director, Office of Energy Research, Office of High Energy and Nuclear Physics, Division of Nuclear Physics of the U.S. Department of Energy under Contract No. DE-AC03-76SF00098.

# LOW POWER SHAPER AMPLIFIER FOR THE EOS TPC DETECTOR

M. Nakamura, D.A. Landis and G. Rai

Lawrence Berkeley Laboratory University of California Berkeley, CA 94720

A shaper amplifier is described that is designed for low power and small size which are important requisites for the Equation of State (EOS) time projection chamber (TPC) detector. The shaper amplifier produces a semi-Gaussian pulse with a peaking time of 210 ns. It dissipates less than 35 mW and has a gain of 4.5. A unique driver circuit capable of driving large capacitive loads and yet requiring low standby current is introduced.

#### Introduction

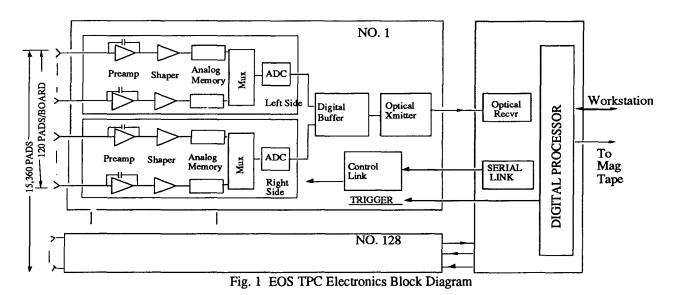

Figure 1 shows a simplified block diagram of the front end electronics for the EOS TPC [1]. There are 15,360 signal channels in the TPC detector which must be accommodated into a space approximately 1m x 1.5m x 0.1m just below the pad plane of the TPC. Temperature variations around the pad plane must be kept as low as possible for proper operation of the detector. Therefore, even though the electronics will be water cooled, the power dissipation of the electronics must be kept within the pad plane thermal load specification. These stringent requirements have been met by using integrated circuit preamplifiers, shaper amplifiers with minimal power consumption and an efficient switched capacitor array (SCA) [2] for the analog store.

# **Shaper Amplifier**

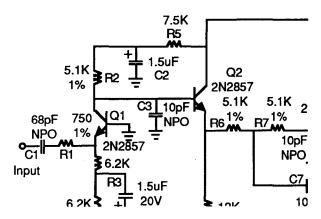

The shaper amplifier schematic is shown in Fig. 2. C1 and R1 differentiate the signal from the preamplifier with a 50 ns time constant. The signal is amplified by Q1 which has a standby current of approximately 0.35 mA and subsequently integrated by R2 and C3. Q2 and Q3 buffer the signal and along with R6, R7, C6 and C7 form a dual integrator network.

C11 and R11 couple the signal into Q4 for further amplification while C10 and R10 perform the correction for the chamber's 1/t tail characteristic. Because the emitters of Q3 and Q4 are low impedance nodes, the C10-R10 and C11-R11 circuits can be adjusted without interaction between the two circuits. This fact allowed us to fine tune the 1/t tail correction by controlling the ratio of values of R10 and R11. R11 determines the gain for the amplifier while R10 determines the amount of 1/t compensation along with its companion capacitor, C10. R15 and C13 perform the fourth integration. All of the integration time constants are 50 ns.

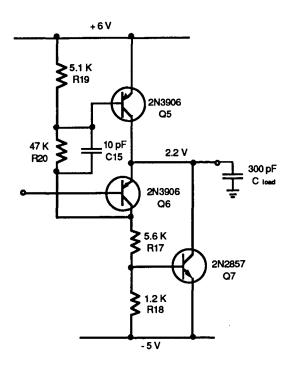

Because those shaper amplifiers located near the center of the detector must drive approximately 300 pF of motherboard trace capacitances to the outer portion of the detector, a special output driver circuit was designed to drive large capacitances while requiring very little standby power. Q5, Q6, Q7 and associated circuitry form the output driver circuit which we call a dual compound emitter follower.

-1-

Fig. 2 EOS TPC Shaper Amplifier

For clarity the output driver circuit is redrawn in Fig. 3. O6, O7 and R18 are used in what is sometimes called a compound emitter follower or White emitter follower where Q5 is replaced by a resistor, R17 is shorted out, and R19, R20 and C15 are not used. A negative going input pulse applied to the base of Q6 tries to drive a large capacitive load at the emitter of Q6. In the event the emitter cannot readily follow the input signal, additional current flows through Q6 and R18 causing Q7 to conduct more which effectively helps remove charge from the load capacitor allowing the emitter to correctly follow the input signal. However, when the negative going pulse begins its excursion back to its original baseline, the output voltage across the load capacitor does not follow because O6 tends to cut off if the current necessary to charge the capacitor load is insufficient. Normally, sufficient current would be supplied by a low valued resistor in place of Q5, but unfortunately, this leads to excessive power dissipation which defeats our objective. This is a problem inherent to all types of emitter followers with low standby current. For example, a 2 volt negative-going semi-Gaussian pulse with 210 ns peaking time and with 300 pF capacitive load would require at least 2.5 mA of standby current for the output voltage to properly follow the input signal. With the +6 volt and -5 volt power supplies used with the shaper amplifier, 2.5 mA of standby current represents 27.5 mW of power for the emitter follower alone. Our goal was to keep the total dissipation for a shaper amplifier to less than 35 mW.

The shortcoming of the compound emitter follower can be remedied by the addition of an on-demand current source which is activated by sensing the disparity between the input and the output signals during the excursion of the input pulse back to its baseline. This current source is comprised of Q5, R17, R19, R20 and C15. Now, when the input pulse begins to return to its baseline, Q6 tends to cut off and its collector voltage drops. This drop in collector voltage is reflected as a voltage drop at the base of Q5 via R17 and R20. This causes Q5 to draw more current. The additional current from Q5 helps charge the load capacitance allowing the output voltage to faithfully follow the input signal. C15 is added to improve the response time for the crcuit. Although the standby current in the dual compound emitter follower is only about 0.4 ma, the output drive circuit can drive a capacitive load of more than 300 pF for a 2 volt negative going pulse with a peaking time of 210 ns. The standby power for this circuit is only 4.4 mW - - a saving of more than 23 mW over a circuit with 2.5 mA of standby current.

Fig. 3 Dual Compound Emitter Follower

#### Performance Results

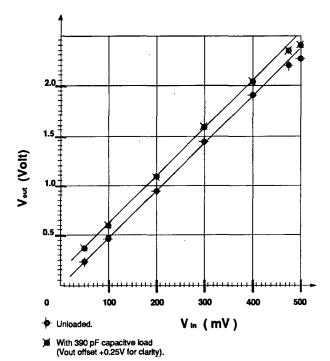

Figure 4 is a graph of output vs. input for the amplifier with no load and with a 390 pF capacitive load. The graph shows that there is very little change in the amplifier performance under the two load conditions. The integral non-linearity is less than 2% which ideally matches that of the

Fig. 4 Shaper Amplifier Linearity Test

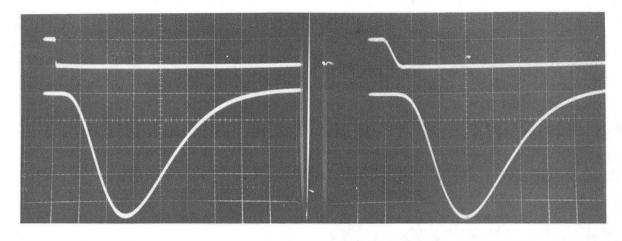

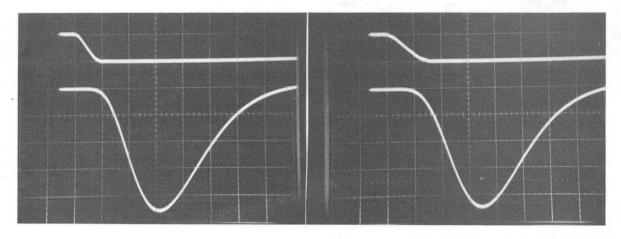

SCA. The response of the shaper amplifier to input pulses with different rise times is shown in Fig. 5. The

100 ns rise time

150 ns rise time

200 ns rise time

250 ns rise time

Shaper input = upper output = lower

= upper trace = .1V/div = lower trace = .1V/div

Time base

= 100 ns/div

Fig. 5 Effect of pre-amplifier output rise time on shaper amplifier.

photos show that the shaper amplifier is relatively immune to ballistic deficit. The peaking time for a signal is approximately 210 ns. The gain of the shaper amplifier is 4.5, and the maximum output swing of the shaper amplifier is just over 2 volts to conform to the SCA input requirements. The output swing is limited by the choice of R14.

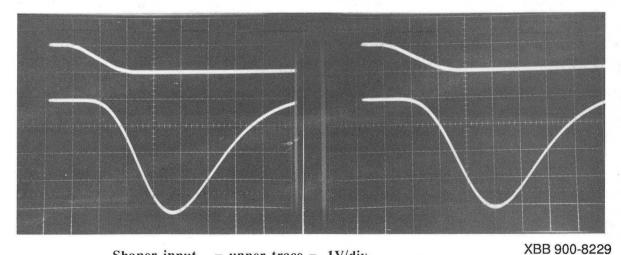

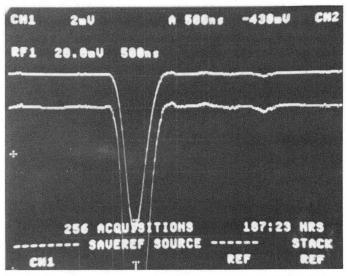

The 1/t tail correction for an actual detector signal is shown in Fig. 6 where the same output pulse is shown with vertical sensitivities of 20 mv/div and at 2 mv/div.

XBB 900-8228

Fig. 6 Shaper amplifier signal from actual chamber signal showing 1/t tail correction.

The noise at the output of the shaper amplifier is less than 0.3 mV rms. The amplifier's noise contribution to the front end electronics is negligible when added in quadrature. The total power dissipation for the shaper amplifier is less than 35 mW. As small as this may seem, this still constitutes a total power dissipation of over 500 watts for the 15,360 shaper amplifiers in the front end electronics.

The shaper response function and noise performance figures have been calculated analytically and simulated using the SPICE software package. The results are in good agreement with measurements. An impulse charge signal of 3 x 10<sup>4</sup> electrons applied to the preamplifier input provides an output signal of 42 mV with a peaking time of 210 ns and undershoot of -3.6 mV because of the 1/t compensation in the shaper. A simulated chamber input signal containing the same integrated charge in a modelled 1/t current pulse, however produces an output signal of 11 mV and corrects for the 1/t tail dependence to better than 0.3 mV. The pulse height deficit ratio is 0.262 (= 11 mV/42 mV). The shaper response function peaks at 1.6 MHz.

### Circuit Construction and Layout

A prototype of the shaper amplifier was constructed using hybrid circuit technology and has performed as expected. Because the shaper amplifier is designed with local feedback, there were no problems with oscillations in the prototype hybrid circuit and the layout of the amplifier was very straight forward. The success with the hybrid circuit showed that a shaper amplifier constructed with surface mount technology would work equally well because the layout is almost identical. A new layout for a shaper amplifier for surface mount construction has been done, and the space required for the amplifier is approximately 8 mm x 62 mm which is within its allotted space.

Sixty shaper amplifiers will be mounted on one side of a motherboard which is to be water cooled. Another sixty shaper amplifiers will be mounted on the other side of the same motherboard. One motherboard will accommodate 120 pad signals, and 128 motherboards in all will service the 15,350 pad signals from the pad plane.

### Acknowledgements

The technical assistance of H.K. Chen, J.B. Hunter and J.C. Lam is gratefully acknowledged. The challenge of accommodating all of the components in the allotted space for the shaper amplifier was skillfully met by K. Shimada.

This work was supported by the Director, Office of Energy Research, Office of High Energy and Nuclear Physics, Division of Nuclear Physics of the U.S. Department of Energy under Contract DE-AC03-76SF00098. Reference to a company or product name does not imply approval or recommendation of the product by the University or the U.S. Department of Energy to the exclusion of others that may be suitable.

#### References

- [1] G. Rai, et al, "A TPC Detector for the Study of High Multiplicity Heavy Ion Collisions", IEEE Trans. on Nucl. Science, NS-37, No. 2, pp. 56-64, April, 1990.

- [2] S.A. Kleinfelder, "A 4096 Cell Switched Capacitor Analog Waveform Storage Integrated Circuit", IEEE Trans. on Nucl. Science, <u>NS-37</u>, No. 3, pp. 1230-1236, June, 1990.