## UC Santa Barbara

**UC Santa Barbara Electronic Theses and Dissertations**

### Title

Wavelength-Selective Photonic Switches for Energy Efficient Reconfigurable Data Center Networks

Permalink https://escholarship.org/uc/item/2bx8b9bw

**Author** Hirokawa, Takako

Publication Date 2020

Peer reviewed|Thesis/dissertation

University of California Santa Barbara

## Wavelength-Selective Photonic Switches for Energy Efficient Reconfigurable Data Center Networks

A dissertation submitted in partial satisfaction of the requirements for the degree

> Doctor of Philosophy in Electrical and Computer Engineering

> > by

Takako Hirokawa

Committee in charge:

Professor Clint L. Schow, Chair Professor John E. Bowers Professor James F. Buckwalter Professor Adel A. M. Saleh

December 2020

The Dissertation of Takako Hirokawa is approved.

Professor John E. Bowers

Professor James F. Buckwalter

Professor Adel A. M. Saleh

Professor Clint L. Schow, Committee Chair

December 2020

## Wavelength-Selective Photonic Switches for Energy Efficient Reconfigurable Data Center Networks

Copyright  $\bigodot$  2020

by

Takako Hirokawa

#### Acknowledgements

There is a very large number of people that I would like to thank for helping me get through graduate school. First and foremost, I need to thank my advisor, Clint. I've learned a great many things both technical and non-technical alike from you over the years. Thank you for not only supporting my research endeavors but also encouraging my other non-technical grad school interests and activities. You created an environment in which I was unafraid to be ambitious and set me up for success.

Secondly, I'd like to thank my committee members. I'd like to thank John for guidance on the AIM projects that I worked early on in my graduate school days. Thank you to Jim for patiently explaining circuit concepts to someone who is nominally getting a degree in electrical engineering but doesn't know anything about circuits past Ohm's law. Thank you to Adel, who always made time to explain networking concepts in great detail and with many colors.

I would like to thank Dr. Roger Helkey for providing a lot of input and practical, helpful advice on the AIM projects on which I worked.

Next, I would like to thank my group who include Yujie, Hector, Steven, Aaron, Stephen, JQ, and Xinhong as well as my mentees, Garey, Amalu, Adi, Nano, Shayan, Uriel, and Sean. There's nothing like getting asked a "stupid" question to really make you think about what it is you're actually doing.

I'd like to thank those who weren't in my group but with whom I still worked both on AIM and ARPA-E projects. These people are Akhilesh, Andy, Navid, Mitra, Luis, Sergio, Robert, Fabrizio, Thomas, and Mario. Especially Akhilesh, with whom I was thrown in the deep end with the first AIM tape-out!

As someone who didn't have more senior group members to go talk to, I'd like to thank the following people for their advice when I had trouble navigating the grad school hoops and experiment woes: Alex, Tin, Minh, Tony, Eric, Paolo, Nicolas, Bowen, and Hongwei. In addition, I'd like to thank the ECE and IEE admin and staff who helped me with all the interstitial things that help move research along especially Val and Amanda.

As I write this, we are in the midst of the coronavirus pandemic, and I am wishing that I was back interacting with members of my office on a regular basis. Thank you to Brandon, Victoria (the OG officemates!), Joe, Michael, Fengqiao, Yujie, Hector, Steven, and Simone for providing much everyday color.

Or course, I have to thank those who have been involved in the Photonics Society over the years. It started as an escape from the lack of progress in my research as well as providing what felt like a tangibly productive outlet. These people include Victoria (again!), Philip, Andy (again!), Demis, Shereen, Caroline, Warren, Eric (again!), Tanya, and many more. Through the Photonics Society, I got to know the amazing staff at the Center for Science and Engineering Partnerships (CSEP), particularly Wendy, who have provided many opportunities in mentoring, outreach, and teaching that complemented my research.

I'd like to thank friends and roommates who haven't been mentioned already: Marissa, Daniel, Bess, Anisa, Kyle, David H., David V., Haw-Tyng, Danilo, and many more as well as my skating coach and friends. And of course, a thank you to my friends from pre-graduate school days for cheering me on from afar.

I'd like to thank my family for providing support and encouragement. I'd like to thank my mom for sending recipes, food, and updates of the dogs. I'd like to thank my dad who encouraged and helped foster my interest in math and science from a young age. I'd like to thank my brother who became my grad school 'twin' (though at a different university) after a childhood of being mistaken for being my biological one.

Last and certainly not least, I'd like to thank Josh. Thank you for being there for me every day no matter how close or how far.

### Curriculum Vitæ Takako Hirokawa

### Education

| 2020 | Ph.D. in Electrical and Computer Engineering (Expected), University of California, Santa Barbara. |

|------|---------------------------------------------------------------------------------------------------|

| 2016 | M.S. in Electrical and Computer Engineering, University of California, Santa Barbara.             |

| 2012 | B.S. in Engineering Physics, University of Colorado, Boulder.                                     |

| 2012 | B.S. in Applied Mathematics, University of Colorado, Boulder.                                     |

### Publications

- "Analog Coherent Detection for Energy Efficient Intra-Data Center Links at 200 Gbps per Wavelength," T. Hirokawa, S. Pinna, N. Hosseinzadeh, A. Maharry, H. Andrade, J. Liu, T. Meissner, S. Misak, G. Movaghar, L. Valenzuela, Y. Xia, S. Bhat, F. Gambini, J. Klamkin, A. A. M. Saleh, L. A. Coldren, J. F. Buckwalter, and C. L. Schow, Journal of Lightwave Technology, doi: 10.1109/JLT.2020.3029788.

- "A Wavelength-Selective Multiwavelength Ring-Assisted Mach-Zehnder Switch," T. Hirokawa, M. Saiedi, S. Pillai, A. Nguyen-Le, L. Theogarajan, A. A. M. Saleh, and C. L. Schow, Journal of Lightwave Technology, 32, 6292-6298, doi: 10.1109/JLT.2020.3011944.

- "Analysis and Monolithic Implementation of Differential Transimpedance Amplifiers," H. Andrade, A. Maharry, **T. Hirokawa**, L. Valenzuela, S. Pinna, C. L. Schow, and J. F. Buckwalter, Journal of Lightwave Technology. vol. 38, no. 16, pp. 4409-4418, 15 Aug.15, 2020, doi: 10.1109/JLT.2020.2990107.

- "Ring-Assisted Mach-Zehnder Interferometer Switch with Multiple Rings Per Switch Element", T. Hirokawa, M. Saeidi, L. Theogarajan, A. A. M. Saleh, C. L. Schow, Proc. SPIE 11286, Optical Interconnects XX, 1128612 (28 February 2020); doi: 10.1117/12.2546865

- "High-Speed Silicon Photonic Optical Interconnects for Cryogenic Readout," S. B. Estrella, T. Hirokawa, A. Maharry, D. S. Renner, C. L. Schow, Proc. SPIE 11286, Optical Interconnects XX, 112860B (March 2020)

- "Comparison of three monolithically integrated TIA topologies for 50 Gb/s OOK and PAM4," H. Andrade, A. Maharry, **T. Hirokawa**, L. Valenzuela, S. Simon, C. L. Schow, and J. F. Buckwalter, Proc. SPIE 11286, Optical Interconnects XX, 112860W (28 Feburary 2020); doi: 10.1117/12.2548762

- 7. "A Novel Architecture for a Two-Tap Feed-Forward Optical or Electrical Domain Equalizer Using a Differential Element," A. Maharry, H. Andrade, T. Hirokawa, J.F. Buckwalter, and C. L. Schow, IEEE Photonics Conference (2019), San Antonio, TX.

- "A 4 × 4 Electrooptic Silicon Photonic Switch Fabric with Net Neutral Insertion Loss," N. Dupuis, F. Doany, R. A. Budd, L. Schares, C. W. Baks, D. M. Kuchta, **T. Hirokawa**, and B. G. Lee, Journal of Lightwave Technology. doi: 10.1109/JLT.2019.2945678

- "A Spectrally-Partitioned Crossbar Switch with Three Drops per Cross-point Controlled with a Driver," T. Hirokawa, M. Saeidi, A. Maharry, R. Helkey, J. E. Bowers, L. Theogarajan, A. A. M. Saleh, and C. L. Schow, IEEE Photonics Conference (IPC) 2019, San Antonio, TX.

- "A Novel Architecture for a Two-Tap Feed-Forward Optical or Electrical Domain Equalizer using a Differential Element," A. Maharry, H. Andrade, T. Hirokawa, J. F. Buckwalter and C. L. Schow, 2019 IEEE Photonics Conference (IPC), San Antonio, TX, USA, 2019, pp. 1-2.

- "Demonstration of a Spectrally-Partitioned 4×4 Crossbar Switch with 3 Drops per Cross-point," T. Hirokawa, A. Maharry, R. Helkey, J. E. Bowers, A. A. M. Saleh, and Clint L. Schow, 2019 24th OptoElectronics and Communications Conference (OECC) and 2019 International Conference on Photonics in Switching and Computing (PSC), Fukuoka, Japan, 2019, pp. 1-3.

- "Energy Efficiency Analysis of Coherent Links for Datacenters," T. Hirokawa, S. Pinna, J. Klamkin, J. F. Buckwalter, and C. L. Schow, 2019 IEEE Optical Interconnects Conference (OI), Santa Fe, NM, USA, 2019, pp. 1-2.

- "High-Speed Optical Interconnect for Cryogenically Cooled Focal Plane Arrays," S. Estrella, D. Renner, **T. Hirokawa**, A. Maharry, M. Dumont, and C. L. Schow, (2019). GOMACTech 2019, (18-1, p. 311-314).

- 14. "Light-based educational outreach activities for pre-university students,", K. W. Hamdy, T. Hirokawa, P. Chan, W. Jin, V. Rosborough, E. Stanton, A. M. Netherton, M. Garza, W. Ibsen, D. D. John, and J. E. Bowers, Fifteenth Conference on Education and Training in Optics and Photonics: ETOP 2019, ETOP 2019 Papers (Optical Society of America, 2019), paper 11143071.

- 15. "A Nonblocking 4x4 Mach-Zehnder Switch with Integrated Gain and Nanosecond-Scale Reconfiguration Time," N. Dupuis, F. Doany, R. A. Budd, L. Schares, C. W. Baks, D. M. Kuchta, **T. Hirokawa**, and B. G. Lee, in Optical Figure Conference (OFC) 2019, OSA Technical Digest (Optical Society of America, 2019), paper W1E.2.

- "Monolithically-Integrated 50 Gbps 2pJ/bit Photoreceiver with Cherry-Hooper TIA in 250nm BiCMOS Technology," H. Andrade, **T. Hirokawa**, A. Maharry, A. Rylyakov, C. L. Schow, and J. F. Buckwalter, in Optical Fiber Communication Conference (OFC), 2019, OSA Technical Digest (Optical Society of America, 2019), paper M3A.5.

- 17. "On-chip Wavelength Locking for Photonics Switches," A. S. P. Khope, **T. Hi**rokawa, A. M. Netherton, M. Saeidi, Y. Xia, N. Volet, C. L. Schow, R. Helkey, L.

Theogarajan, A. A. M. Saleh, J. E. Bowers, and R. C. Alferness, in Opt. Lett., 42, 4934-4937 (2017).

- "Elastic WDM Optoelectronic Crossbar switch with On-Chip Wavelength Control," A. S. P. Khope, A. M. Netherton, **T. Hirokawa**, N. Volet, E. Stanton, C. Schow, R. Helkey, A. A. M. Saleh, J. E. Bowers, and R. C. Alferness, in Advanced Photonics 2017 (IPR, NOMA, Sensors, Networks, SPPCm, PS), OSA Technical Digest (online) (Optical Society of America, 2017), paper PTh1D.3.

- "Forward bias operation of silicon photonic Mach-Zehnder modulators for RF applications," R. L. Chao, J. W. Shi, A. Jain, **T. Hirokawa**, A. S. P. Khope, C. L. Schow, J. E. Bowers, R. Helkey, and J. F. Buckwalter, Opt. Express, 25, 23181-23190 (2017).

#### Abstract

## Wavelength-Selective Photonic Switches for Energy Efficient Reconfigurable Data Center Networks

by

#### Takako Hirokawa

Wavelength-selective switches have been proposed for datacenter use to enhance datacenter scalability and to aid in meeting ever-increasing traffic demands and the resulting energy consumption. In silicon photonics, photonic integrated circuit (PIC) designers can take advantage of the high contrast between silicon and silicon dioxide—the latter of which acts as the cladding for the silicon nanowire waveguides—to design compact microring resonators with large free spectral ranges (FSRs). Furthermore, as commercial silicon photonics foundry offerings become more widely available, the ability to produce larger and more complicated PICs has become easier, as well as providing a clearer path towards large-scale manufacturability and adoption of such technologies. Thus, ringbased wavelength-selective switches are a particularly well-suited application for silicon photonics. Another major design consideration for PICs is low energy consumption.

A discussion of simulation results from a model for next generation energy efficient photonic links for data centers motivates and the two wavelength-selective switch designs that are presented in this thesis. The first design is an N×N crossbar switch with L ring pairs to route up to L wavelengths at each cross-point. The second design is an N×N ring-assisted Mach-Zehnder interferometer (RAMZI) switch with L ring pairs per switch element. In both designs, multiple ring pairs of differently sized rings were utilized to partition the FSR such that any one ring pair does not have to move far in the spectrum to complete the switching, thus saving in the power consumption.

# Contents

| $\mathbf{C}_{\mathbf{I}}$ | urriculum Vitae                                                                                                                                                                | vi         |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| $\mathbf{A}$              | ostract                                                                                                                                                                        | ix         |

| Li                        | st of Figures                                                                                                                                                                  | xii        |

| 1                         | Introduction1.1Data Center Networks1.2Switches in the Data Center1.3Silicon Photonics1.4Overview                                                                               | . 4<br>. 6 |

| <b>2</b>                  | Energy Efficiency Analysis of Analog Coherent Links                                                                                                                            | 9          |

|                           | 2.1 Introduction $\ldots$                                                                     | . 9        |

|                           | 2.2 Coherent Link Energy Efficiency Model                                                                                                                                      | . 13       |

|                           | 2.3 Results and Discussion                                                                                                                                                     | . 21       |

|                           | 2.4 Discussion                                                                                                                                                                 | . 27       |

|                           | 2.5 Conclusion                                                                                                                                                                 | . 32       |

| 3                         | Crossbar Switches                                                                                                                                                              | <b>34</b>  |

|                           | 3.1 Ring-Based Switch Fundamentals                                                                                                                                             | . 34       |

|                           | 3.2 C-Band $4 \times 4$ Crossbar Switch $\ldots \ldots \ldots$ | . 43       |

|                           | 3.3 O-Band $4 \times 4$ Crossbar Switch $\ldots \ldots \ldots$ | . 48       |

| <b>4</b>                  | RAMZI Switches                                                                                                                                                                 | 56         |

|                           | 4.1 Introduction $\ldots$                                                                     | . 56       |

|                           | 4.2 Experimental Methods                                                                                                                                                       | . 61       |

|                           | 4.3 Scaling Up the Switch                                                                                                                                                      | . 68       |

|                           | 4.4 Conclusion and Future Work                                                                                                                                                 | . 72       |

| <b>5</b>                  | Summary and Outlook                                                                                                                                                            | <b>74</b>  |

|                           | 5.1 Future Directions                                                                                                                                                          | . 75       |

| $\mathbf{A}$ | Test Structures                                              | <b>78</b> |

|--------------|--------------------------------------------------------------|-----------|

|              | A.1 General Test Structures                                  | . 79      |

|              | A.2 Device-Specific Test Structures                          |           |

|              | A.3 Some Practical Considerations                            |           |

| в            | Crossbar Switch Practical Details                            | 88        |

|              | B.1 Wirebonding                                              | . 88      |

|              | B.2 Some Testing Considerations                              | . 91      |

|              | B.3 Some Design Considerations                               | . 91      |

| $\mathbf{C}$ | RAMZI Switch Tuning Operation                                | 95        |

|              | C.1 Wirebonding                                              | . 95      |

|              | C.2 Switching Operation                                      |           |

|              | C.3 Some Design Considerations                               |           |

| D            | Code listing                                                 | 107       |

|              | D.1 ACD Link Simulation Code                                 | . 107     |

|              | D.2 RAMZI $4 \times 4$ with 2 Ring Pairs Simulation Code     | . 126     |

|              | D.3 RAMZI $2 \times 2$ for an Add-Drop or All-Pass Ring Pair | . 133     |

| Bi           | bliography                                                   | 137       |

# List of Figures

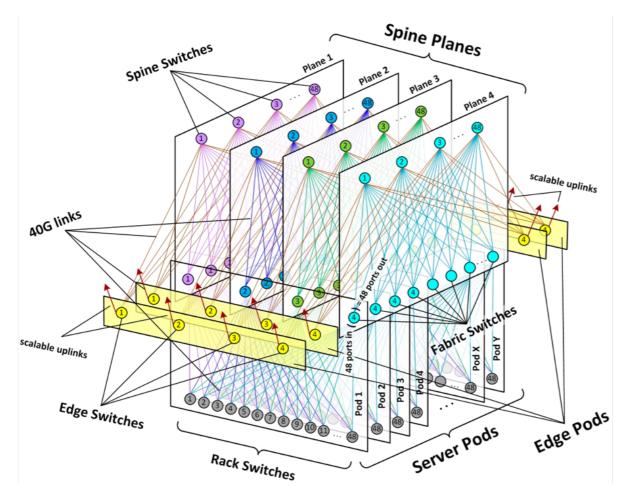

| 1.1 | A schematic of a fat-tree data center network architecture, as implemented<br>by Facebook, from Ref. [1]                                                                                                                                                                                                               | 4                |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

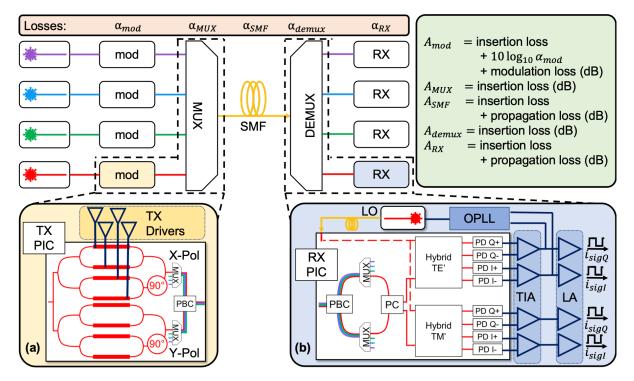

| 2.1 | This figure shows the link implementation for a QPSK link, where (a) shows the schematic for the QPSK transmitter (TX) considered in the model, while (b) shows the schematic for the receiver (RX), including the OPLL. Note that the MUX/DEMUX is included in the design for the TX and RX, respectively.            | 14               |

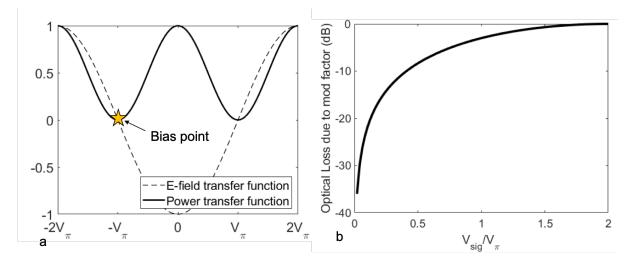

| 2.2 | (a) Electric field and associated output optical power of an MZM and the bias point of the MZM for QPSK modulation. (b) shows the modulation factor vs. the ratio of $V_{sig}/V_{\pi}$ in dB.                                                                                                                          | 15               |

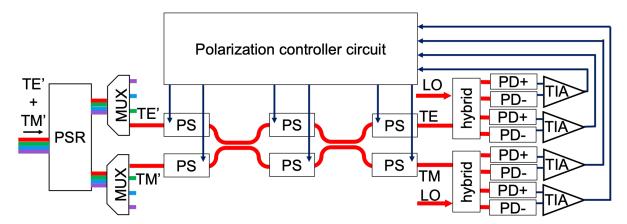

| 2.3 | Three-section polarization controller utilizing phase shifters (PS) after the polarization splitter rotator (PSR) with a polarization controller circuit.                                                                                                                                                              |                  |

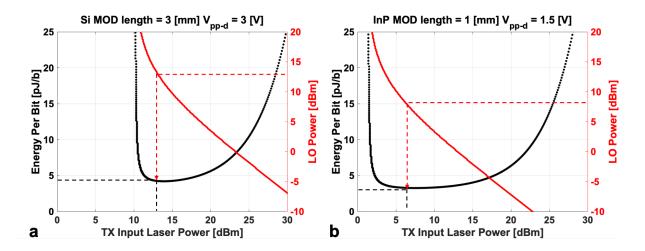

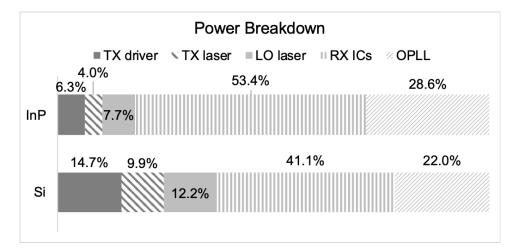

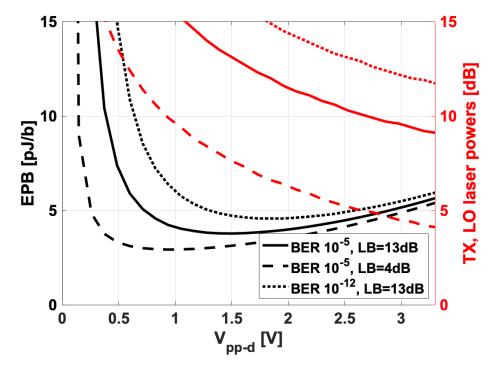

| 2.4 | This scheme would be implemented for each wavelength Simulation results for (a) a 3-mm-long Si Tx/Si Rx TW-MZM and (b) a 1-mm-long InP Tx/Si Rx TW-MZM. The EPB curve (black) and LO power curve (red) correspond to BER = $1 \times 10^{-5}$ , below the KR4-FEC threshold of $2.1 \times 10^{-5}$                    | 18<br>23         |

| 2.5 | The proportion of power taken up by each component in the link at the operating point indicated in Figure 2.4.                                                                                                                                                                                                         | <b>-</b> 0<br>24 |

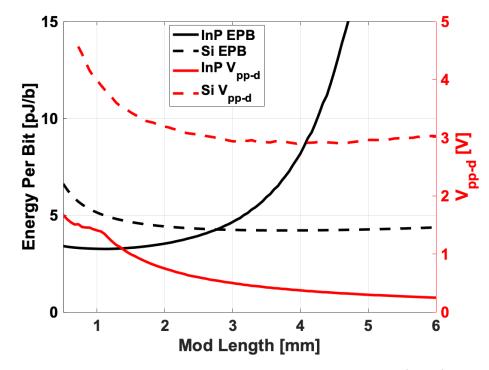

| 2.6 | Simulation results when we compare the minimum EPB (black) and drive voltage (red) for TW-MZMs in InP and Si. SEG-MZMs yield similar                                                                                                                                                                                   |                  |

|     | minimum EPB, and lower drive voltage                                                                                                                                                                                                                                                                                   | 25               |

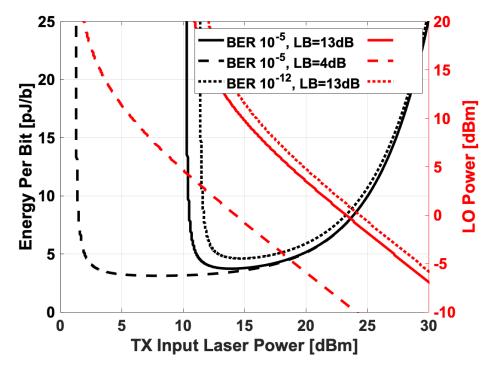

| 2.7 | Starting from the conditions used to generate the results for 3-mm-long<br>Si TWMZMs shown in Figure 2.4(a), LO power and EPB vs. TX power<br>for BER $10^{-5}$ with a 4 dB link margin and BER $10^{-12}$ with a 13 dB link<br>margin cases are shown. The drive voltage is set to 3 $V_{pp-d}$ . LB = link<br>budget | 27               |

|     | 5445000 · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                            |                  |

| 2.8  | Starting from the conditions used to generate the results for 3-mm-long Si TWMZMs shown in Figure 2.4(a), and taking the operating point where                                                                           |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | the TX and LO laser powers are equal, this plot shows how the EPB                                                                                                                                                        |     |

|      | changes for a given drive voltage and the required TX/LO laser powers to                                                                                                                                                 |     |

|      | close the link. $LB = link$ budget                                                                                                                                                                                       | 28  |

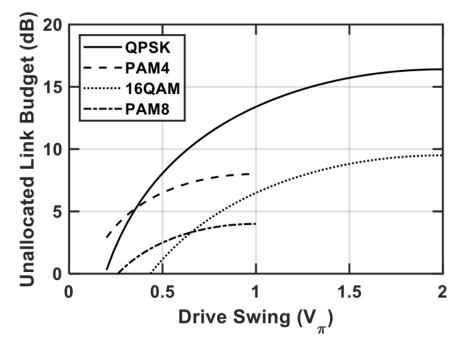

| 2.9  | Comparison of unallocated link margin in coherent and IMDD links, as-<br>suming MZM drive, and a target BER of $10^{-5}$ . The QPSK curve as-<br>sumes analog coherent link performance as described in this work, while |     |

|      | the other curves assume representative link performance projections for                                                                                                                                                  |     |

|      | next-generation IMDD and digital coherent links [2]                                                                                                                                                                      | 30  |

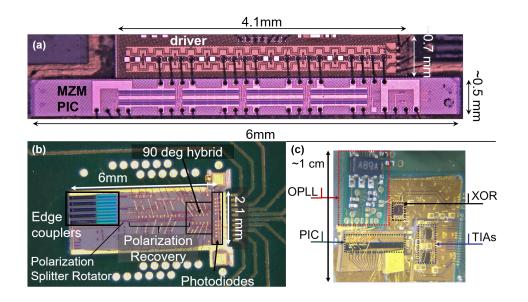

| 2.10 | Preliminary hardware for (a) a Si TX modulator and driver, (b) Si RX                                                                                                                                                     |     |

|      | PIC packaged with an OPLL.                                                                                                                                                                                               | 32  |

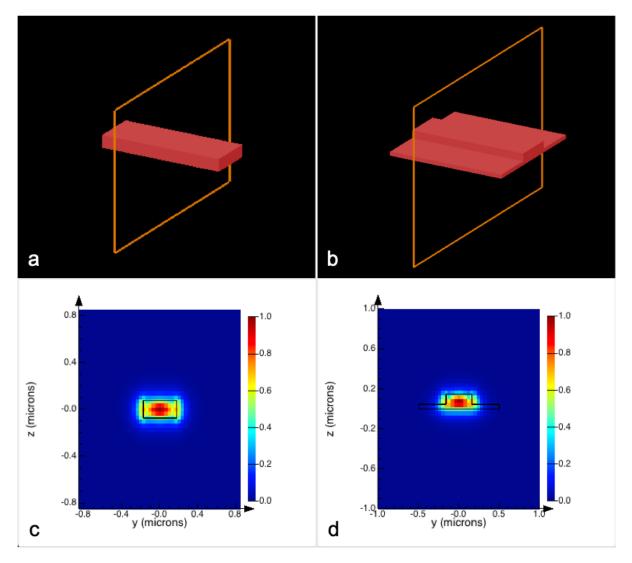

| 3.1  | (a) and (b) shows a perspective view of a strip and ridge waveguide, re-<br>spectively. (c) and (d) show the intensity distribution of the fundamental                                                                   |     |

|      | mode for the strip and ridge waveguides, respectively                                                                                                                                                                    | 35  |

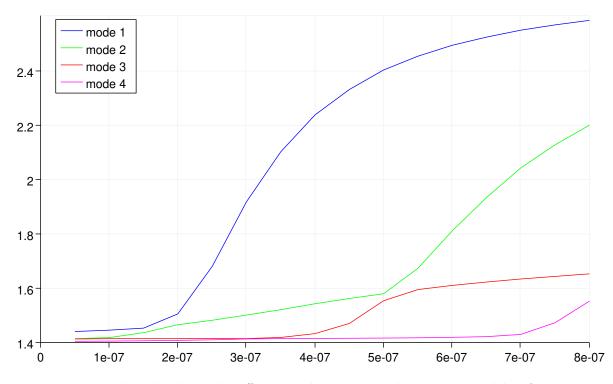

| 3.2  | This plot shows the effective index corresponding varying widths of waveg-                                                                                                                                               |     |

|      | uide for a given thickness. When the waveguide becomes wide enough, it                                                                                                                                                   |     |

|      | can support more than one mode                                                                                                                                                                                           | 37  |

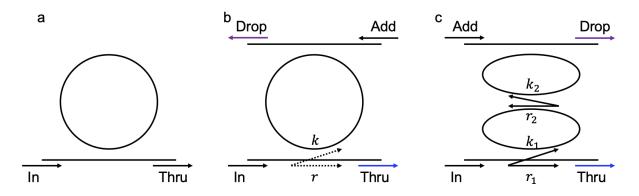

| 3.3  | (a) shows the schematic of an all-pass ring, while (b) shows a schematic                                                                                                                                                 |     |

|      | of an add-drop ring. (c) is a schematic of a two serially coupled add-drop                                                                                                                                               |     |

|      | ring configuration.                                                                                                                                                                                                      | 38  |

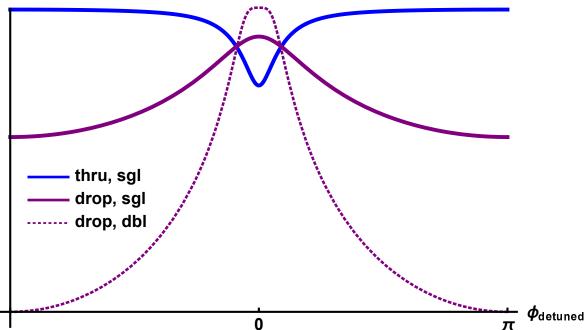

| 3.4  | The responses at the thru and drop ports for an add-drop ring                                                                                                                                                            | 39  |

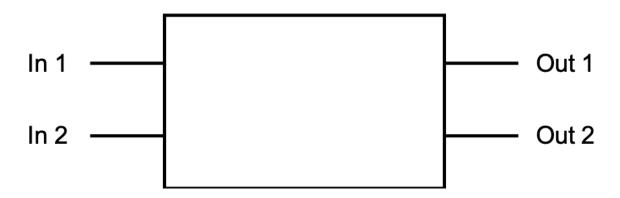

| 3.5  | A block diagram of a switch cell in which there are two inputs and two                                                                                                                                                   |     |

|      | outputs.                                                                                                                                                                                                                 | 42  |

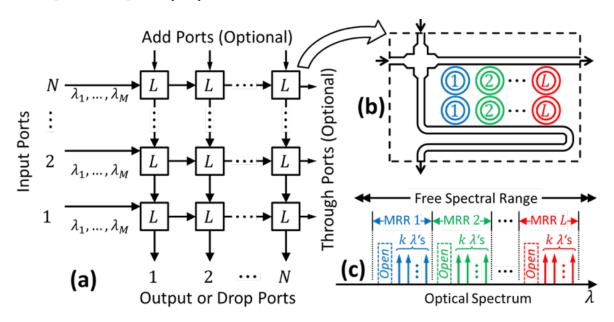

| 3.6  | A schematic diagram of a spectrally partitioned $N \times N$ crossbar switch with                                                                                                                                        |     |

|      | M wavelengths per port and up to $L$ wavelength drops per cross-point.                                                                                                                                                   |     |

|      | (a) A high-level block diagram of the switch. (b) Possible realization of $I_{\text{A}}$ MDP success point (c) Details of the successful participation.                                                                  | 11  |

| 27   | an <i>L</i> -MRR cross-point. (c) Details of the spectral partitioning (a) shows the experimental setup with the single-mode optical fiber while                                                                         | 44  |

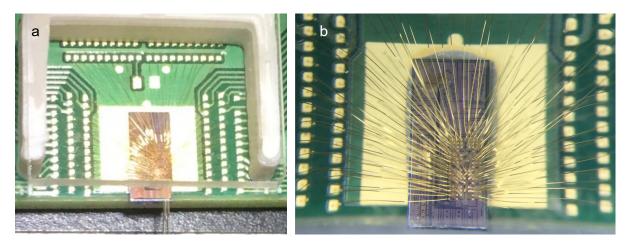

| 3.7  |                                                                                                                                                                                                                          | 46  |

| 3.8  | <ul><li>(b) shows a close-up of the wirebonded chip.</li><li>(a) shows the tuning spectrum of all three MRRs within each sub-band</li></ul>                                                                              | 40  |

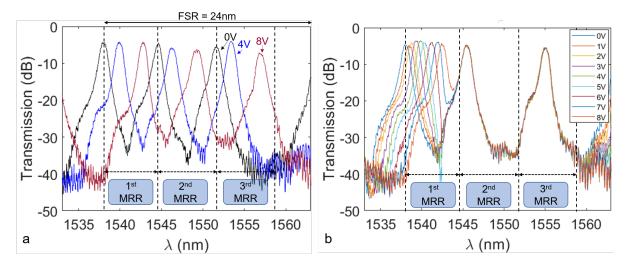

| 0.0  | using SMUs. Each ring is tuned with 0 V, 4 V, 8 V. Figure (b) shows                                                                                                                                                      |     |

|      | independent tuning of one ring with respect to the other rings. $\ldots$                                                                                                                                                 | 47  |

| 3.9  | (a) shows the tuning spectrum of all three MRRs within each sub-band.                                                                                                                                                    | 71  |

| 0.5  | Each ring is tuned with 0 V, 4 V, 8 V using a custom driver. Figure (b)                                                                                                                                                  |     |

|      | shows independent tuning of one ring with respect to the other rings                                                                                                                                                     | 47  |

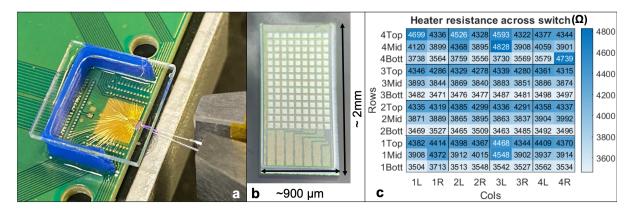

| 3.10 | (a) shows the switch wirebonded assembly, while (b) shows a close-up of                                                                                                                                                  | 11  |

| J.10 | the switch chip. (c) shows the resistance of the heaters across the switch                                                                                                                                               |     |

|      | chip                                                                                                                                                                                                                     | 49  |

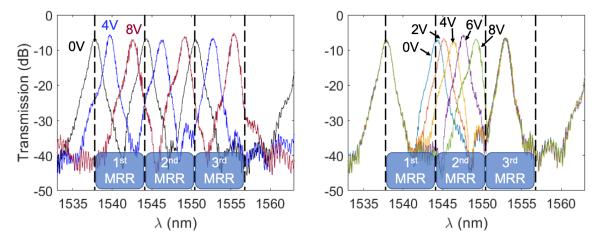

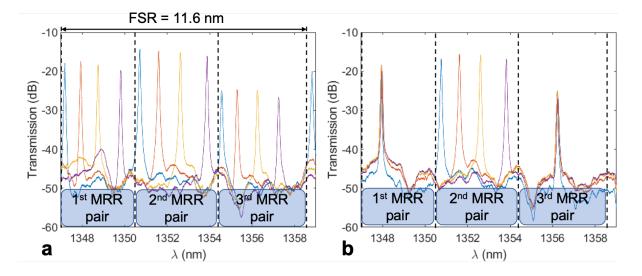

| 3.11 | (a) shows switch operation across one full FSR using the heaters, while (b)                                                                                                                                              | - 0 |

|      | shows the second MRR tuning independently of the first and third MRRs.                                                                                                                                                   | 51  |

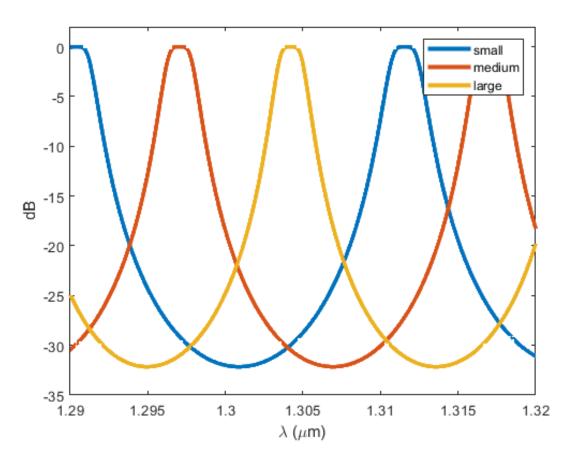

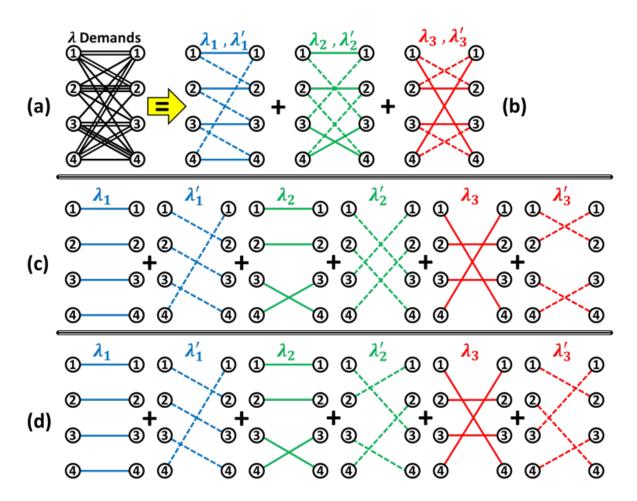

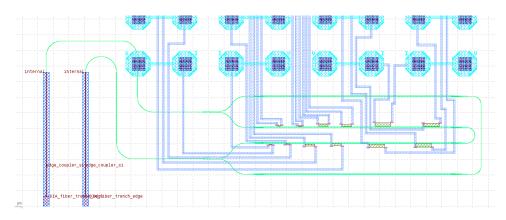

|      | The expected spectrum of the redesigned 1310 ring switch Description of our wavelength assignment algorithm. (a) A wavelength demand. (b) Resulting wavelength assignment using our algorithm, represented by simple 2-factor graphs. (c) Single-wavelength representation of (b). (d) A wavelength assignment using a standard algorithm, which would have required some of the MRRs to tune over the entire FSR | 52<br>54 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

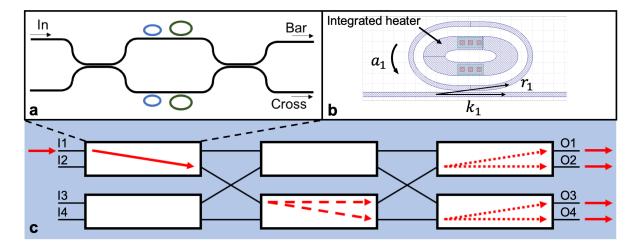

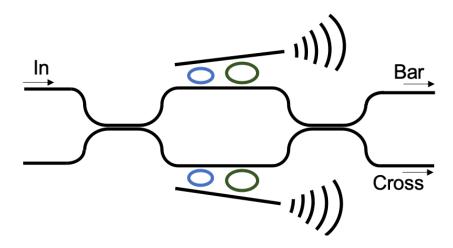

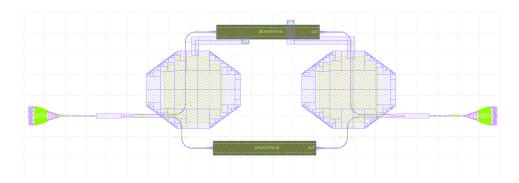

| 4.1  | (a) shows single RAMZI cell with two ring pairs, (b) shows a screenshot of the design for one of the rings, and finally, (c) shows an example of the paths taken through the switch.                                                                                                                                                                                                                              | 57       |

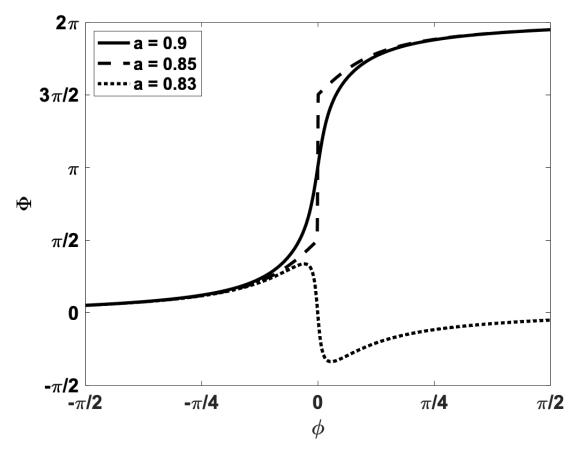

| 4.2  | The phase change across the resonance of a ring is shown for the over-<br>coupled $(r > a)$ , critically coupled $(r = a)$ , and undercoupled $(r < a)$                                                                                                                                                                                                                                                           | 57       |

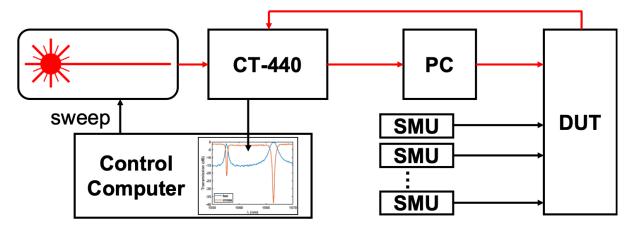

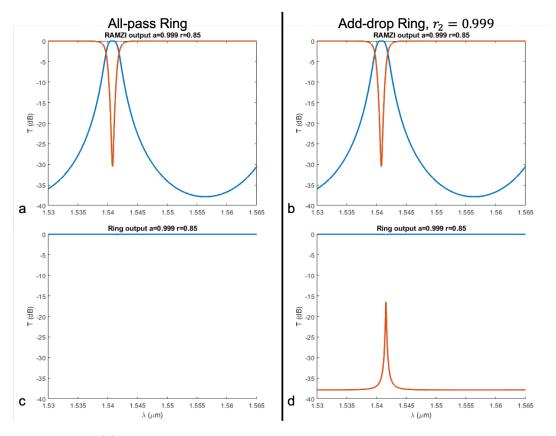

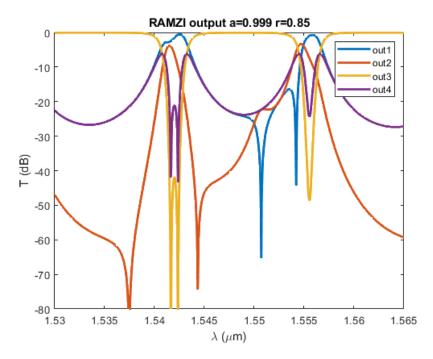

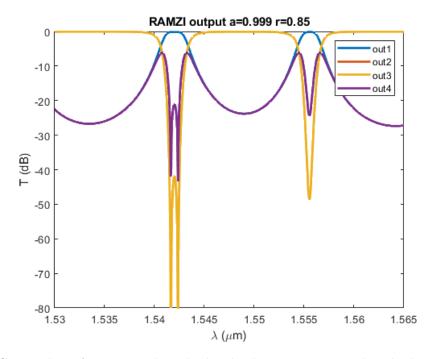

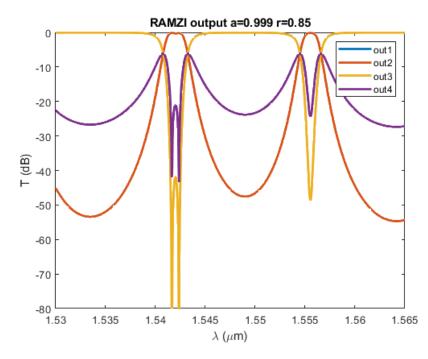

| 4.3  | conditions. To generate these plots, $r$ was set to 0.85                                                                                                                                                                                                                                                                                                                                                          | 59       |

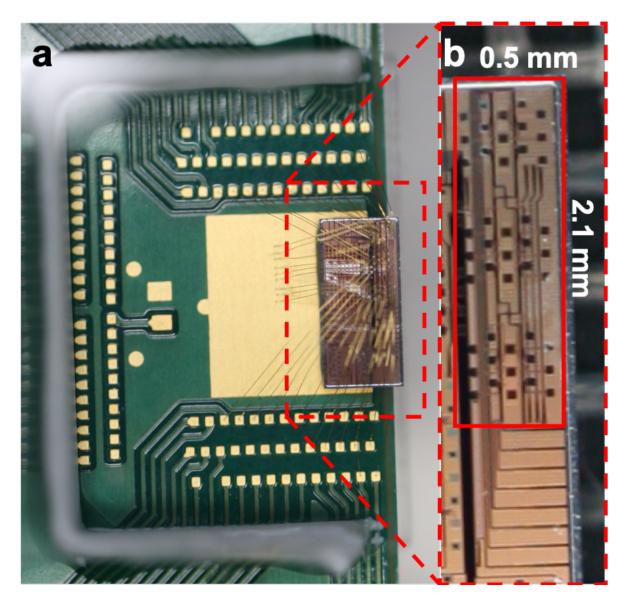

| 4.4  | all the electrical connections made in the experimental setup (a) shows the wirebonded switch on a custom PCB, while (b) shows a closeup of the chip on which the switch is located. In (b), the RAMZI switch area is outlined in red, while the area right below the box are the                                                                                                                                 | 61       |

| 4.5  | edge couplers                                                                                                                                                                                                                                                                                                                                                                                                     | 62       |

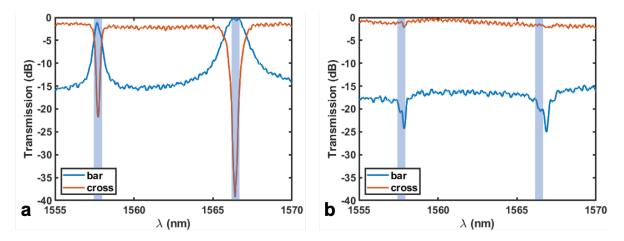

| 4.6  | are highlighted in blue                                                                                                                                                                                                                                                                                                                                                                                           | 64       |

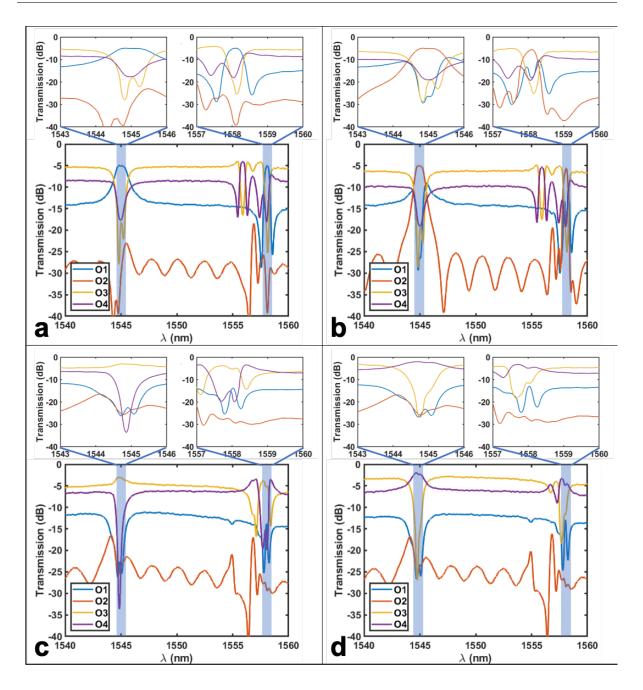

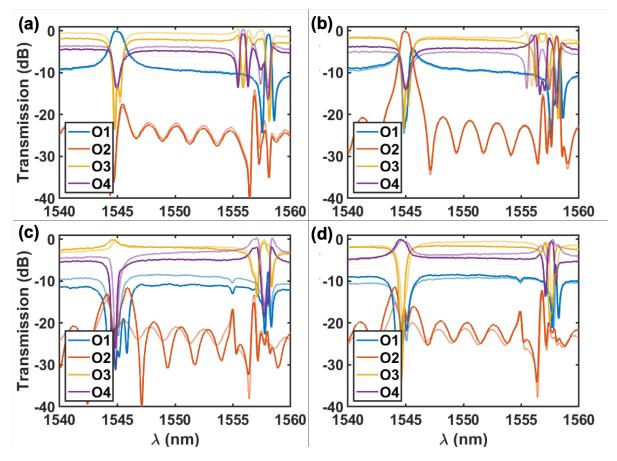

| 4.7  | shown. The data was obtained utilizing SMUs to tune the rings<br>The outputs of each of the switch states for both ring pairs is shown. The<br>wavelengths are routed from input 1 to (a) output 1, (b) output 2, (c)<br>output 3, and (d) output 4. The dark lines represent data taken with the<br>switch controlled with a driver, while the more transparent lines represent                                  | 66       |

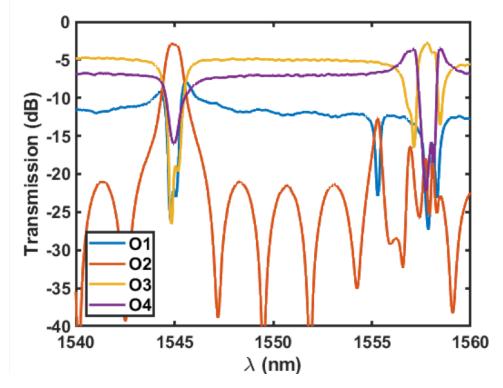

| 4.8  | data taken for the same switch state with the SMUs                                                                                                                                                                                                                                                                                                                                                                | 67       |

| 4.9  | rings from input 1 to two different outputs, ports 2 and 3 A $2 \times 2$ RAMZI cell with taps by converting the all-pass rings to add-drop rings. The taps can be routed to a grating coupler to monitor during the                                                                                                                                                                                              | 68       |

| 4.10 | initial calibration                                                                                                                                                                                                                                                                                                                                                                                               | 73       |

|      | coupling coefficient of the second bus waveguide is large. (c) and (d) show the ring response for the respective cases.                                                                                                                                                                                                                                                                                           | 73       |

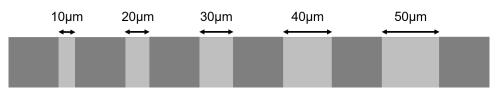

| A.1<br>A.2 | An example of a TLM design. The dark grey squares represent the pads,<br>while the lighter grey represent the doped silicon region. It is often easiest<br>to have one large piece of silicon under all of the pads in the TLM, with<br>highly doped regions right under the contacts | 79       |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

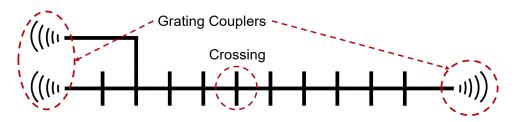

|            | crossing.                                                                                                                                                                                                                                                                             | 82       |

| A.3        | A heater test structure design is shown here. There are eight different heater designs, each routed to a pair of pads                                                                                                                                                                 | 84       |

| A.4        | A diode test structure design is shown here. There is a diode on each arm of the MZI.                                                                                                                                                                                                 | 85       |

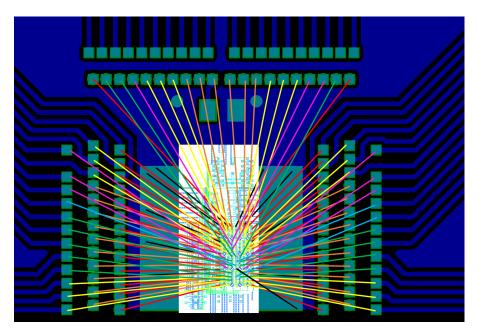

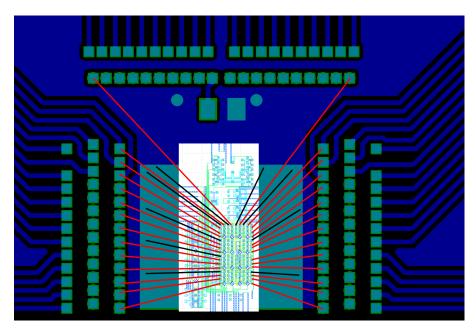

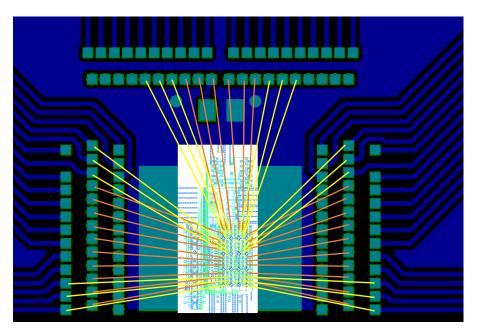

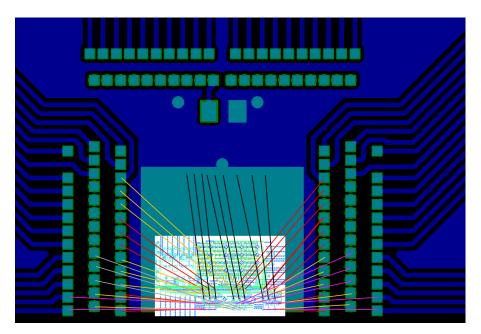

| B.1        | All of the wirebonds made for the crossbar switch mounted on a custom PCB. The large blue-green pad on which the chip is located is a ground plane, while the smaller blue-green squares represent pads on the PCB.                                                                   | 89       |

| B.2        | The first layers of the wirebonds made for the crossbar switch, as denoted<br>by the different colors. In this case, the black lines represent connections<br>from ground pads on the switch to the ground plane on the PCB, while                                                    | 09       |

|            | the red lines represent a layer of connections for signal pads                                                                                                                                                                                                                        | 89       |

| B.3        | The next layers of wirebonds made for the crossbar switch, as denoted<br>by the yellow and orange lines. These layers are above those depicted in                                                                                                                                     |          |

|            | figure B.2                                                                                                                                                                                                                                                                            | 90       |

| B.4        | The next layers of wirebonds made for the crossbar switch, as denoted by<br>the green and pink lines. These layers are above those depicted in figure                                                                                                                                 |          |

| B.5        | B.3                                                                                                                                                                                                                                                                                   | 90       |

| П¢         | the chip and PCB.                                                                                                                                                                                                                                                                     | 91       |

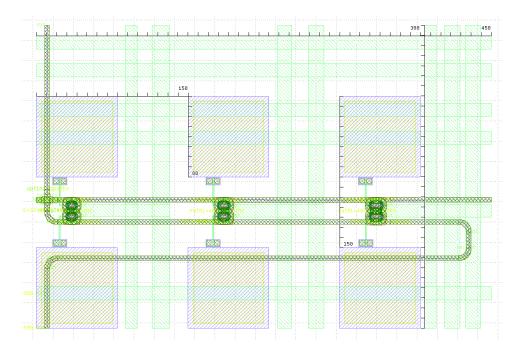

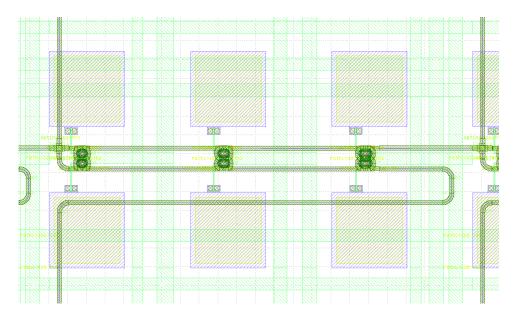

| B.6<br>B.7 | A single cell design of the crossbar switch                                                                                                                                                                                                                                           | 93<br>93 |

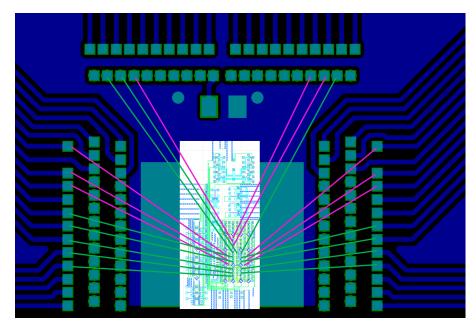

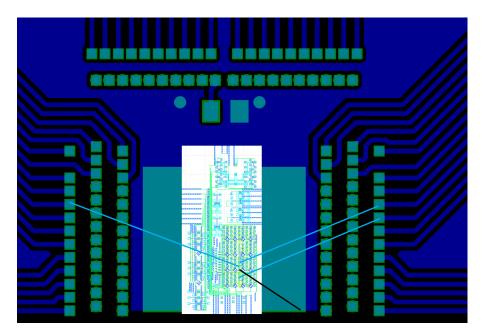

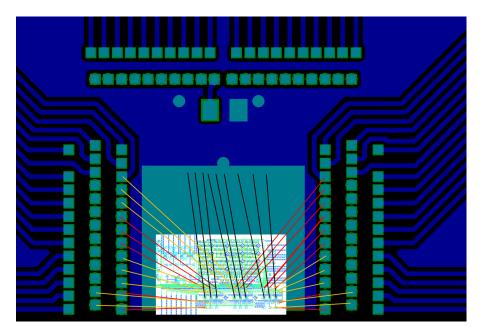

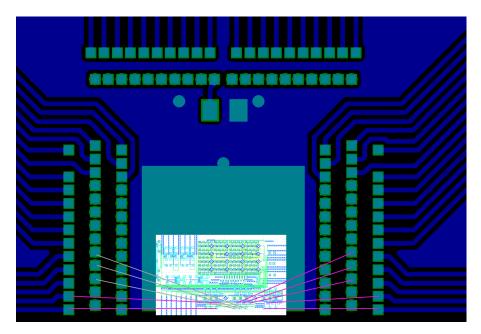

| C.1        |                                                                                                                                                                                                                                                                                       |          |

|            | plane, while the smaller blue-green squares represent pads on the PCB.                                                                                                                                                                                                                | 96       |

| C.2        | The first layers of the wirebonds made for the RAMZI switch, as denoted                                                                                                                                                                                                               |          |

|            | by the red, orange, and black. In this case, the black lines represent<br>connections from ground pads on the switch to the ground plane on the                                                                                                                                       |          |

| C.3        | PCB, while the red lines represent a layer of connections for signal pads.<br>The final layers of the wirebonds made for the RAMZI switch, as denoted                                                                                                                                 | 96       |

| 0.0        | by the grey and pink lines. These layers are above those depicted in figure C.2.                                                                                                                                                                                                      | 97       |

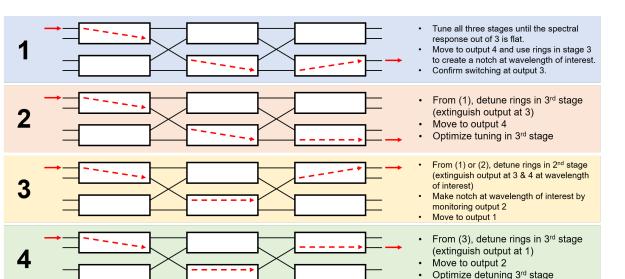

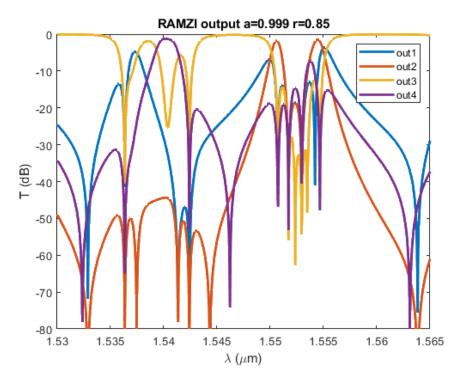

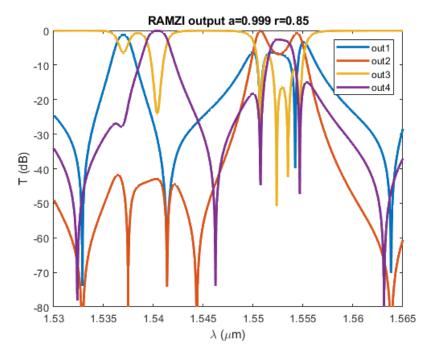

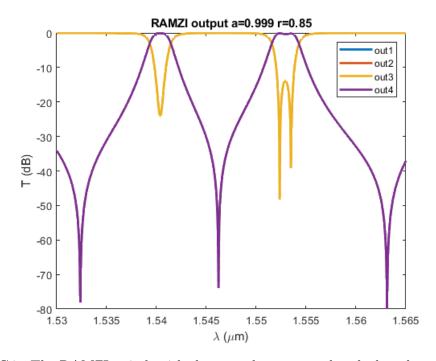

| C.4        | Procedure for testing the RAMZI.                                                                                                                                                                                                                                                      | 98       |

| C.5  | The RAMZI switch with a random phase put on each ring                       | 99  |

|------|-----------------------------------------------------------------------------|-----|

| C.6  | The RAMZI switch with the first stage tuned such that the resonances for    |     |

|      | the two ring pairs are matched.                                             | 100 |

| C.7  | The RAMZI switch with the second stage tuned such that the resonances       |     |

|      | for the two ring pairs are matched.                                         | 100 |

| C.8  | The RAMZI switch with the third stage tuned such that the resonances        |     |

|      | for the two ring pairs are matched and outputs to port 3                    | 101 |

| C.9  | The RAMZI switch with the third stage tuned such that the resonances        |     |

|      | for the two ring pairs are slightly detuned from one another and outputs    |     |

|      | to port 4                                                                   | 102 |

| C.10 | The RAMZI switch with the second stage tuned such that the resonances       |     |

|      | for the two ring pairs are slightly detuned from one another                | 102 |

| C.11 | The RAMZI switch with the second stage tuned such that the resonances       |     |

|      | for the two ring pairs are slightly detuned from one another                | 103 |

| C.12 | The RAMZI switch with the second stage tuned such that the resonances       |     |

|      | for the two ring pairs are matched. The resonance of the first ring pair in |     |

|      | the second stage is tuned to match the resonance of the first ring pair in  |     |

|      | second cell in the third stage. The second ring pair in the third stage is  |     |

|      | redshifted to match the resonance in the second stage                       | 104 |

| C.13 | The RAMZI switch with the third stage now tuned such that the reso-         |     |

|      | nances on each arm are matched and the outputs are directed to port         |     |

|      | 1                                                                           | 105 |

| C.14 | The RAMZI switch with the third stage now tuned such that the reso-         |     |

|      | nances on each arm are slightly detuned from one another and the outputs    |     |

|      | are directed to port 2                                                      | 106 |

| C.15 | A single cell design of the RAMZI switch.                                   | 106 |

# Chapter 1

# Introduction

The internet is one of the greatest technological inventions of the modern era, and have given rise to some of the largest corporations today, such as Google, Amazon Web Services, and Facebook. Most of data traffic today is handled within data centers [1,3]. Many of these large corporations have built and use so-called hyper-scale data centers to deliver their services to customers. Data centers are physical facilities dedicated to housing computer systems and associated infrastructure such as power supplies, cooling systems, and communications equipment, and are located around the world, with many built in the U.S. Data centers are immensely power-hungry facilities due to the large number of servers they must power in addition to the large number of interconnects. Like personal computers, servers generate their own heat which can compromise operation of some components. Thus, data centers must also find ways to cool the servers they house, further adding to the energy consumption. 50% of energy consumed by data centers goes to cooling, while 10% goes to network hardware [4]. Most mid-sized or larger companies have a data center [5], though many companies may choose to co-locate their data center with another company or buy space from another data center company. Data centers remain in operation almost all the time. Planned outages can range from almost 30 hours a year to four hours during a 5-year period depending on how sophisticated the facility is [5].

The energy consumption of data centers is unlikely to decrease in the coming years as demand for more bandwidth from the consumer continues to increase with every passing year [6]. In 2009, data centers consumed 1.5% of the total energy consumed in the U.S. [5]. In 2018, data centers contributed to 0.3% of the overall carbon emissions [7]. A group at Huawei projected that the energy consumption of data centers worldwide could increase from 1% of the global energy consumption in 2010 to between 3% (best case) and 13% (worst case) in 2030 [3]. Furthermore, they project that the energy consumption due to communication technology could contribute as much as 23% of greenhouse gases emissions worldwide by 2030. Within the U.S. as of 2016, the projected growth in electricity consumption between 2015 to 2020 decreased to only 4% from 24% largely due to significantly more energy efficient servers [8]. In addition, some data center companies are working towards utilizing more renewable energies specifically to power their data centers [9, 10]. It is thus of great interest to find more energy-efficient solutions for next generation data centers while being able to deliver on basic tenets of large-scale computing components—namely low cost and power, high reliability and yield, and small size—while being able to continue to increase capacity. While much work is being done to make more reliable computing chips, the energy density within a data center is continuing to increase.

Hyper-scale data centers refer to the ability to continue to scale the data centers to much larger number of servers. They are typically over 400,000 ft<sup>2</sup> and contain advanced cooling systems and redundant power [8]. These data centers arose when large companies such as Google and Amazon needed to deploy hundreds of thousands of servers. Due to the potential energy consumption associated with the size of hyper-scale data centers, data centers have been built to include bare-bones servers with no lights or video. Compared to typical data centers, hyper-scale are able to decrease the ratio of total energy for everything to computing energy by 40%. This ratio is known as the power usage efficiency and is typically about 2 for a traditional data center and 1.2 for hyper-scale data centers. Hyper-scale data centers made up about 20% of total data center electricity usage in 2018. [7]

## 1.1 Data Center Networks

Hyper-scale data centers must necessarily be connected with a well-defined network architecture that also accommodate the growing number of servers. A typical structure for hyper-scale data centers is a so-called fat-tree or Clos architecture [1, 11] as shown in figure 1.1. There are typically two or three layers of switches above the server racks. Within a server rack, there is the top of rack (ToR) or edge switch, which is connected to each server within the rack and to one or more second layer switch. Second layer or aggregation switches are connected to one or more so-called core or layer 3 switches above [1, 12]. The links below the ToR switches to the servers are typically electrical links, while links above the ToR between the switches are typically optical links and are operated at higher speeds than the links from ToR to servers. Since the second and third layer switches are not necessarily located close to other switches, the links connecting them can be as long as 2 km. Currently, optical links use some sort of intensity-modulated direct detection (IMDD) modulation scheme to transport data between switches, but as the data rate continues to grow, continuing the increase the bandwidth of the IMDD signals will no longer be a viable option from a cost perspective. As such, energy efficient links for higher data rates must be proposed and studied. This is the subject of chapter 2.

Figure 1.1: A schematic of a fat-tree data center network architecture, as implemented by Facebook, from Ref. [1]

## 1.2 Switches in the Data Center

Current switches in the data center convert the optical signal to an electrical signal to perform the switching and converted back to an optical signal, known as OEO conversion. While this possesses important advantages, such as the ability to monitor the health of the links, it is also a very power-hungry implementation. Datacenter switches such as the Mellanox EDR 100 Gb/s Infiniband Smart Switches consume 100s of pJ/bit [13]. Table 1.2 compares the energy efficiency of current commercial data center switches. A common metric to measure the energy efficiency of network components such as transceivers is the

| Vendor           | Switch Model                     | Power (W) | Max data rate    | $\mathrm{pJ/bit}$ | # ports | Ref. |

|------------------|----------------------------------|-----------|------------------|-------------------|---------|------|

| Mellanox         | EDR Infiniband Switch S7800      | 136       | 100 Gbps         | 1360              | 36      | [13] |

| Dell             | EMC PowerSwitch Z9332F-ON        | 900       | 25.6  Tbps       | 35                | 32      | [16] |

| HPE              | FlexFabric 5700 48G 4XG 2QSFP+   | 175       | $336 { m ~Gbps}$ | 520               | 48      | [17] |

| HPE              | FlexFabric 5700 40XG 2QSFP+      | 162       | $960 { m ~Gbps}$ | 168               | 40      | [17] |

| HPE              | FlexFabric 5700 32XGT 8WG 2QSFP+ | 350       | $960 { m ~Gbps}$ | 365               | 32      | [17] |

| Extreme Networks | ExtremeSwitching X465-24W        | 2485      | 316  Gbps        | 7864              | 24      | [18] |

| Extreme Networks | ExtremeSwitching X465-48T        | 176       | 364  Gbps        | 484               | 48      | [18] |

| Extreme Networks | ExtremeSwitching X465-48P        | 1746      | 364  Gbps        | 4797              | 48      | [18] |

| Extreme Networks | ExtremeSwitching X465-48W        | 4024      | 364  Gbps        | 2813              | 48      | [18] |

| Extreme Networks | ExtremeSwitching X465-24MU       | 1722      | $648 { m ~Gbps}$ | 2657              | 24      | [18] |

| Extreme Networks | ExtremeSwitching X465-24MU-24W   | 3941      | $696 { m ~Gbps}$ | 5662              | 24      | [18] |

| Extreme Networks | ExtremeSwitching X465-24S        | 173       | 316  Gbps        | 547               | 24      | [18] |

| Extreme Networks | ExtremeSwitching X465-24XE       | 207       | $888 { m ~Gbps}$ | 120               | 24      | [18] |

| Cisco            | Nexus 9316D-GX                   | 420       | 6.4 Tbps         | 66                | 16      | [19] |

| Cisco            | Nexus 93600CD-GX                 | 590       | 6.0  Tbps        | 98                | 16      | [19] |

| Juniper Networks | QFX5100-48S                      | 150       | 1.44  Tbps       | 66                | 16      | [20] |

| Juniper Networks | QFX5100-48T                      | 335       | 1.44  Tbps       | 233               | 6       | [20] |

| Juniper Networks | QFX5100-24Q                      | 161       | 2.56  Tbps       | 63                | 24      | [20] |

| Juniper Networks | QFX5100-24Q-AA                   | 175       | 2.56 Tbps        | 68                | 24      | [20] |

| Juniper Networks | QFX5100-96S                      | 263       | 2.56  Tbps       | 102               | 8       | [20] |

| Arista           | 7060CS2-32S                      | 187       | 6.4 Tbps         | 29                | 32      | [21] |

| Arista           | 7060SX2-48YC6                    | 240       | 3.6 Tbps         | 67                | 6       | [21] |

| Arista           | 7060CS-32S                       | 187       | 6.4 Tbps         | 29                | 32      | [21] |

| Arista           | 7260QX-64                        | 315       | 5.12  Tbps       | 62                | 64      | [21] |

| Arisa            | 7260CS-64                        | 1672      | 12.8 Tbps        | 130               | 64      | [21] |

Table 1.1: Commercial data center switch power, maximum data rate, and energy efficiency.

energy per bit, usually reported in pJ/bit. As can be seen from the table, many current data center switches are not necessarily optimized for energy efficient operation, with energy per bit metrics ranging from almost 30 pJ/bit to over 5 nJ/bit. As bandwidth demands increase, so, too does the power consumption of the switch. Furthermore, the power consumption of the switch application specific ICs (ASICs) are starting to reach the thermal limits for cooling ICs [14, 15].

Replacing some of the electronic switching layers with optical circuit switches can improve the energy efficiency, reduce the amount of OEO conversion (i.e., eliminating transceivers) and enhance the data center performance (by reducing the packet latency throughout the system. Data center network topology also affects the performance and energy efficiency of the whole system; implementing optical switches that allow for flexible switching could assist in flattening the network topology to reduce energy efficiency overall and enhance performance [22].

### **1.3** Silicon Photonics

Silicon photonics provides an attractive solution to implement next-generation all optical switches. Complementary metal-oxide-semiconductor (CMOS) fabrication technology that enables computer chip manufacturing can be exploited to manufacture a large number of silicon photonic chips for a relatively low cost. In addition to the mass manufacturing capabilities of CMOS, there is high index contrast between silicon and silicon dioxide. Therefore photonic components and photonic integrated circuits (PICs) on chip can be made compact due to the tight bends possible from the high confinement of the light in the silicon waveguides. Despite the advantages that silicon holds over many other materials, there are notable downsides. The primary disadvantage is that silicon possesses an indirect bandgap; thus, it cannot be used to generate light without significant phononic interaction—unlike other semiconductor materials that possess a direct bandgap like indium phosphide (InP) materials—making silicon a very poor material with which to fabricate a laser. Much work is being done to integrate III-V semiconductor materials, most notably InP, onto silicon in a standard silicon photonics process. Furthermore, silicon photonics has a comparably weaker electro-optic effect, making it a less efficient material than other III-V materials to be used in active devices such as modulators. In addition, significant challenges remain in packaging silicon PICs into packages. While the electronic packaging is not necessarily an issue due to the large electronic IC ecosystem, the optical packaging still presents a large hurdle towards mass adoption of photonic technologies. Typically, the light on chip is confined in a waveguide that is several hundred nanometers wide and no more than a couple hundred nanometers tall. Meanwhile, the mode of light at telecom wavelengths in single mode fiber is around 10  $\mu$ m in diameter [23]. Simply butt-coupling a waveguide to a single mode fiber results in significant loss due to the large mode mismatch. It is possible to make the waveguides larger. In fact, this has been proposed and demonstrated by Rockley Photonics [24] at the expense of the ability to make tight bends and therefore very compact photonic devices. Another notable effort towards packaging silicon photonic parts comes from IBM with the use of polymer waveguides [25, 26] When silicon became the material of choice for mass manufacturing of electronics, this spurred research interest in silicon as a material for photonic devices in the mid to late 1980s. There had previously been research efforts in other materials such as the aforementioned InP, as well as gallium arsenide (GaAs) and lithium niobate (LiNbO<sub>3</sub>) [27]. The interest in silicon photonics was driven primarily by the desire to integrate the photonics with the electronics [27, 28]. It was discovered that silicon is transparent to wavelengths above 1.2  $\mu$ m, including around 1.3  $\mu$ m and 1.5  $\mu$ m—wavelengths typically used for optical communications [28], motivating optical communications as an application for silicon photonics. Despite research activity beginning in the 1980s, it wasn't until 2001 that Luxtera was able to demonstrate the first commercial silicon photonic product [29, 30] manufactured in a commercial CMOS process. Today, there are currently several foundries that provide silicon photonic processes, often through a multi-project wafer (MPW) run. Table 1.3 provides a list of some of the current silicon photonics foundries. MPW runs are crucial for smaller organizations that cannot afford a full fabrication run, let alone maintain a manufacturing facility to be able to design silicon photonic devices, paving the way towards more so-called fab-less operation [29,30]. In this arrangement, the foundry provides access to the process to the customers who can their desired devices as long as they adhere to the design rules of the process. All of the silicon PICs presented in this thesis were designed in MPW runs.

| Foundry                     | Location   | Silicon Thickness | Wafer Size                        | Ref.     |

|-----------------------------|------------|-------------------|-----------------------------------|----------|

| GlobalFoundries             | New York   | —                 | 300  mm                           | [31]     |

| AIM Photonics               | New York   | 220  nm           | 300  mm                           | [32]     |

| TowerJazz                   | California | —                 | 200  mm                           | [33]     |

| <b>IHP</b> Microelectronics | Germany    | 220  nm           | 200  mm                           | [33, 34] |

| AMF                         | Singapore  | —                 | 200  mm                           | [35]     |

| imec                        | Belgium    | $220~\mathrm{nm}$ | $200~\mathrm{mm},300~\mathrm{mm}$ | [36]     |

Table 1.2: Select listing of commercial silicon photonic foundries that offer MPW services.

### 1.4 Overview

The rest of the thesis is organized as thus. The second chapter presents an energy efficiency model for next generation data center links. These links assume a link budget of 13 dB between transmitter and receiver, which can be used by a photonic switch. In Chapter 3, silicon photonic crossbar ring-based wavelength-selective switches are presented. These ring-based crossbar switches are relatively easy implementation of wavelength-selective switches but do not provide a good path towards large-scale wavelength-selective photonic switches. Thus in Chapter 4, an alternative approach to a wavelength-selective switch in silicon using ring-assisted Mach-Zehnder interferometers (RAMZIs) are proposed and demonstrated. I conclude and propose further research directions in Chapter 5. The appendices are organized as thus: Appendix A contains brief descriptions of test structures, Appendix B and C includes practical details when testing crossbar switches and RAMZI switches, including the wirebonding diagrams and tuning procedures, and Appendix D contains code listing for simulations presented throughout the thesis.

# Chapter 2

# Energy Efficiency Analysis of Analog Coherent Links

Work presented in this section has appeared in [37] and [38].

## 2.1 Introduction

With ever-increasing demand for cloud services, evaluating interconnect technology benefits and tradeoffs anticipates future deployments of the data center through scaling baud rates, higher order modulation formats with more bits/symbol, polarization multiplexing, and adding additional wavelength division multiplexed (WDM) channels. Current data center links rely on intensity-modulated direct detection (IMDD) schemes due to their relative simplicity and correspondingly relatively low cost and power consumption. However, scaling IMDD links to 200 Gbps/lane will require a large jump in complexity and power consumption. A recent study showed the potential of a 100 GBd PAM-4 link to operate over a 400 m link distance [39]. However, heavy equalization was required, with 71 feedforward equalizer (FFE) taps and 15 decision feedback equalizer (DFE) taps, just to achieve a pre-FEC (Forward Error Correction) bit error ratio (BER) slightly below the soft decision (SD-FEC) limit of  $2 \times 10^{-2}$ . With such power-hungry equalization, the required received optical power was > +7 dBm, likely demanding an unfeasible output power from the transmitter (TX) source laser [39]. The limited prospects for scaling IMDD links to 200 Gbps/lane and beyond have driven substantial interest in developing a new generation of energy-efficient coherent links designed specifically for intra-datacenter applications [2, 37, 40, 41]. A recent paper by authors from the Alibaba Group presents a detailed comparison of several variants of IMDD (PAM4, CAP16, DMT) against digital coherent (PDM-16QAM) for 400G links, backed up with experimental results, using metrics of minimizing laser and ASIC power consumption [41]. The authors conclude that coherent links have lower laser power requirements and comparable ASIC power dissipation and digital signal processing (DSP) complexity compared to the IMDD approaches. Recent work from Google provides a comparison up to 1.6 Tb/s, analyzing in detail multiple digital coherent (16, 32, 64QAM) and IMDD (PAM4, 6, 8) architectures [2]. The coherent links are projected to consume somewhat more power—on the order of 10-20%—but offer substantial advantages: greater tolerance to fiber impairments, higher spectral efficiency, and a large advantage in receiver (RX) sensitivity. For modulator drive swings less than 1V?, the gains in RX sensitivity are found to be mostly offset by large modulator losses and the PAM links are projected to achieve larger link budgets. The coherent links operate at 2X higher total bit rates, and with higher modulator drive voltages achieve 5-9 dB more link budget than the IMDD variants [2].

Digital coherent architectures commonly used in telecom interconnects are implemented with a free-running local oscillator (LO) which requires an RX chain consisting of a linear receiver front end followed by an analog-to-digital converter (ADC) to digitize incoming data. Doing so enables the DSP to perform functions such as carrier recovery, polarization demultiplexing and channel equalization to remove fiber propagation impairments such as chromatic dispersion (CD) and polarization mode dispersion (PMD). An alternative approach to coherent detection is analog coherent detection (ACD) which utilizes a highly integrated optical phase-locked loop (OPLL) to directly lock the frequency and phase of the LO laser to an incoming wavelength channel. Chip-scale integration enables low feedback loop delay and therefore high loop bandwidth, enabling the use of more easily integrated tunable LO lasers with MHz-scale linewidth [42–46] . Furthermore, the OPLL approach provides for the direct demodulation of complex signals at low uncorrected bit error rates (BER), with previous proof-of-concept demonstrations achieving BER <  $10^{-12}$  for BPSK modulation up to 35 Gb/s [45].

Although latency may not be especially critical for our primary target application of intra-datacenter links where the use of FEC is ubiquitous, the potential to construct FEC-free coherent links offers a substantial advantage for highly latency-sensitive applications such as high-performance computing (HPC), Another key benefit of OPLL-based coherent detection in general, and offered by our OPLL ACD architecture is inherent wavelength selectivity. When the LO is locked to an incoming wavelength channel, other channels are rejected by the RX. For example, if the system channel spacing is 200 GHz, when the LO is locked to one of the wavelength channels in the incoming optical signal, the locked signal is down-converted to the baseband while the other wavelength channels are converted to 200 GHz or higher—far above the operating bandwidth of the receiver electronics. This wavelength selectivity can be exploited to reduce crosstalk requirements for future networks that incorporate photonic routing/switching and eases channel crosstalk requirements of on-chip wavelength multiplexing/demultiplexing components.

It is widely accepted that much of the complexity of traditional coherent DSP can be removed for datacenter applications [2,41] where O-band operation of links up to 2 km present negligible fiber impairments. Consequently, the biggest power savings offered by ACD arises not through the elimination of DSP, but through the removal of linear RX frontends and ADCs. QPSK as a modulation format uniquely takes full advantage of the direct demodulation capability enabled by ACD. At the output of the 90° hybrids in an ACD receiver, the I and Q channels have been separated and low-power electronics using limiting amplifiers can be used to make a binary decision, just like in the most power efficient non-return to zero (NRZ) on-off keying (OOK) links [47]. State-of-the-art ADCs have been developed with sufficient sampling rate and effective number of bits (ENOB) for 224 Gbps DP-16QAM coherent receivers with power consumption ranging between 235 mW [48] to 702 mW [49]. A dual-polarization I-Q receiver would require four such ADCs, resulting in a total ADC power consumption between 940-2808 mW or 4.2-12.5 pJ/bit based upon the efficiencies reported in [48, 49]. Our QPSK link architecture does not require these power-hungry components and full-link energy efficiencies of less than 5 pJ/bit are feasible. The substantial power savings advantage for QPSK does not straightforwardly scale to higher order QAM formats which require multiple decision thresholds for both I and Q channels, driving the need for A/D conversion.

In this paper we present a multi-wavelength analog coherent detection (ACD) architecture utilizing a chip-scale OPLL and based on 50 GBd polarization-multiplexed QPSK (PM-QPSK) for an aggregate data rate of 200 Gbps/ $\lambda$ . In addition to the linklevel advantages in optical budget and power efficiency offered by QPSK-based ACD, we believe it will be advantageous to scale to bit rates of 800 Gb/s and beyond by using four or more WDM lanes, each carrying 200 Gb/s, as opposed to fewer lanes at higher per- $\lambda$  bit rates. The large optical loss budget enabled by ACD further opens a wider space for network architecture designs offering greater flexibility and scalability through the insertion of optical wavelength-level routing and/or circuit switching devices in the data center network. Keeping the per/ $\lambda$  bandwidth granularity lower expands opportunities for network architectures with substantial power savings and enhanced operational flexibility as discussed in Section 2.4.2.

### 2.2 Coherent Link Energy Efficiency Model

In this section, we present an ACD link model that supports a quantitative exploration of the design space of modulator length, drive voltage, and TX source and LO laser powers. For ease of reference, we refer to the operating baud rates as 50 GBd, but all simulations are conducted at 56 GBd to allow for coding and FEC overhead. Furthermore, although our link architecture is capable of operating at uncorrected BER  $< 10^{-12}$ , we assume a target BER of  $1 \times 10^{-5}$ , compatible with KR4-FEC (BER threshold =  $2.1 \times 10^{-5}$ ), and the KP4-FEC (BER threshold =  $2.2 \times 10^{-4}$ ) that is widely implemented in data center network switches [50]. The ACD link model consists of a quadrature phase-shift keying (QPSK) transmitter, a low-loss optical link (< 2 km), and a homodyne coherent receiver. Figure 2.1 illustrates a schematic of the dual-polarization QPSK (DP-QPSK) ACD link for the Si-based architectures. In Figure 2.1, the transmitter (TX) laser light is split into two single-mode waveguides and modulated with IQ modulators. We consider two modulator architectures and two photonic integrated circuit (PIC) platforms. The first modulator is based on a traveling wave modulator (TW-MZM) design [51], while the second utilizes a segmented modulator (SEG-MZM) [52]. Both modulators have been demonstrated in Si and InP platforms [53–62]. We find that the choice of TX architecture and PIC technology both have a significant impact on the overall link performance and power budget. Previous comparisons of SEG-MZMs and TW-MZMs have been made for high-bandwidth radio over fiber (RoF) photonic systems [60–62]. RoF links based on SEG-MZM generally showed improvements in gain and noise figure over TW-MZM implementations at high frequency, but at the expense of higher power consumption.

Considering a differential driving signal, a phase modulated signal is realized when

Figure 2.1: This figure shows the link implementation for a QPSK link, where (a) shows the schematic for the QPSK transmitter (TX) considered in the model, while (b) shows the schematic for the receiver (RX), including the OPLL. Note that the MUX/DEMUX is included in the design for the TX and RX, respectively.

an MZM is biased at its null point, where the electric field transmission is 0, as shown in Figure 2.2(a). At this bias point, the optical carrier undergoes a 180° phase shift when the input signal transitions from the logic 0 to 1 and vice versa even when the voltage swing is less than twice the full modulator half-wave voltage  $(V_{\pi})$  of the MZM. However, driving the modulator with a signal amplitude smaller than  $2V_{\pi}$  leads to increased loss. Such loss can be estimated using the modulation factor  $(F_M)$ , defined in linear units by:

$$F_M = \frac{1}{2} \left( 1 - \cos\left(\pi \frac{V_{sig}}{2V_\pi}\right) \right),\tag{2.1}$$

where  $V_{sig}$  is the peak-to-peak drive voltage. The optical loss due to the modulation factor with respect to the drive voltage is shown in Figure 2.2(b). A  $F_M$  of 1, which corresponds to a  $2V_{\pi}$  drive voltage swing, leads to no modulation-induced loss, while

Figure 2.2: (a) Electric field and associated output optical power of an MZM and the bias point of the MZM for QPSK modulation. (b) shows the modulation factor vs. the ratio of  $V_{sig}/V_{\pi}$  in dB.

$F_M$  of 0.5 corresponds to a  $V_{\pi}$  voltage swing and 3 dB of induced optical loss. The modulation factor therefore presents a fundamental power consumption tradeoff: larger drive voltages reduce modulation loss at the expense of higher power dissipation for the electrical modulator driver circuits. Conversely, lower drive voltages reduce driver power but increase optical losses that need to be compensated by higher source and/or LO laser power levels. The modulation loss is therefore controlled by the drive voltage amplitude and is independent of MZM insertion loss. The MZM length is also a key parameter that trades off optical propagation losses against electrical power dissipation in the driver circuits. The relationship between MZM length and optical propagation loss is given by:

$$P = P_{\rm in} e^{-\alpha_{opt} L_{MZM}},\tag{2.2}$$

where  $P_{in}$  is the input power,  $L_{MZM}$  is the active length of the modulator, and  $\alpha_{opt}$  is the loss per length of the active region. In InP, we measured this to be 4.34 dB/mm, while in Si we used a value of 1.5 dB/mm. Modulator  $V_{\pi}$  inversely depends on modulator length: longer modulators exhibit lower  $V_{\pi}$  and require relatively lower drive voltages at the expense of higher optical propagation losses; shorter modulators have lower optical losses but higher  $V_{\pi}$  with correspondingly higher drive voltage requirements and accompanying driver power consumption.

We assume differential drive for both SEG-MZM and TW-MZM transmitters and incorporate polarization multiplexing to increase the link capacity by a factor of two.  $V_{sig}$ was swept from 0 to  $V_{\pi}$ . In the TW-MZMs, we assume that the microwave and optical velocities are matched such that the phase shift induced by the traveling wave electrodes is integrated along the length of the MZM. If the optical and microwave velocities are not perfectly matched, there is a well-known degradation in bandwidth that would introduce an additional inter-symbol interference (ISI) power penalty. In the TW-MZMs, we account for electrode loss along the length of the modulator, which we estimated from simulations of traveling wave electrodes designed for operation above 50 GHz. The electrode loss was estimated to be 0.2 Np/mm and 0.4 Np/mm from simulations in Si and InP, respectively. For the SEG-MZMs, we assume that the driver accounts for the time delay between phase shifter sections and that the voltage delivered to each segment is the same for all segments.

For both driver power calculations, we consider only the power dissipation in the output stage. In both calculations, we assume a 45 nm CMOS technology and that  $\eta_{dr}$  is the efficiency of the driver. For the TW-MZM driver power consumption, we assume differential drive, current-mode logic operation, and that  $V_{sig}$  is the single-ended peak output voltage of the driver. The single-ended voltage swing delivered to the MZM is also dependent on the characteristic impedance of the transmission line ( $Z_0$ ) which was set to 40  $\Omega$  for Si and 30 $\Omega$  for InP. 40  $\Omega$  was chosen for Si based on typical values found in the literature [63–66], while 30  $\Omega$  for InP was measured from initial designs. Changing the TW-MZM impedance to say, 50  $\Omega$ , would not change the bandwidth or the phase

efficiency in the calculations, as this relationship is not captured by the model. The power consumption for the SEG-MZM is dependent on the length  $(l_{seg})$  and capacitance  $(C_{seg})$  of each segment, the number of segments being driven, and the baud rate  $(R_b)$ . Like the TW-MZM driver calculation,  $V_{sig}$  is the single-ended peak output voltage of the driver. To calculate the number of segments, we first assumed that the length of each segment was 200  $\mu$ m to ensure they would behave as lumped circuit elements under 50 GBd operation. The active length of the modulator was then divided by the segment length and rounded up to give an integer number of segments.  $C_{seg}$  was measured in initial test structures to be 0.27 fF/mm and 0.94 fF/mm for Si and InP, respectively. We define the driver efficiency as a ratio of the capacitance of each segment to the sum of the segment capacitance and the output capacitance of the driver. It is given by

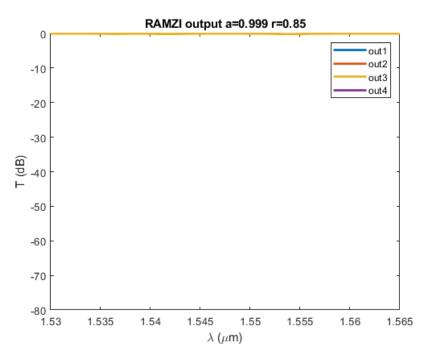

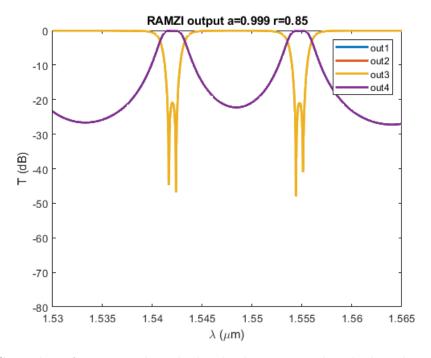

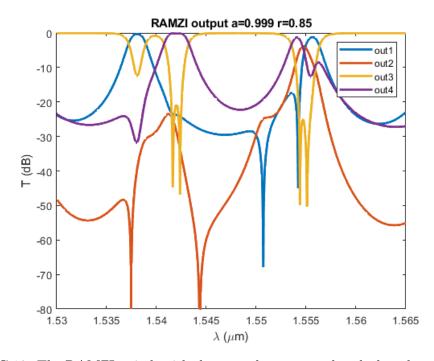

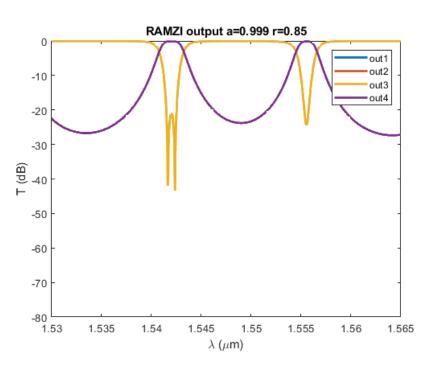

$$\eta_{dr,SEG} = 1 - G_C \frac{V_{sig}}{t_r},\tag{2.3}$$