# UC San Diego UC San Diego Electronic Theses and Dissertations

### Title

On-chip interconnect architectures : perspectives of layout, circuits, and systems

**Permalink** https://escholarship.org/uc/item/2cn126h3

**Author** Chen, Hongyu

Publication Date 2006

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA, SAN DIEGO

On-Chip Interconnect Architectures: Perspectives of Layout, Circuits, and Systems

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

Computer Science

by

Hongyu Chen

Committee in charge:

Professor Chung-Kuan Cheng, Chair Professor Ronald Graham Professor Te C. Hu Professor Andrew B. Kahng Professor Gabriel Rebeiz

Copyright Hongyu Chen, 2006 All rights reserved. The dissertation of Hongyu Chen is approved, and it is acceptable in quality and form for publication on microfilm:

Te C. the Chair

University of California, San Diego 2006

To the memory of my father

| TABLE OF CONTENTS |

|-------------------|

|-------------------|

|   | Signature Page                                                                                                                | i |

|---|-------------------------------------------------------------------------------------------------------------------------------|---|

|   | Dedication                                                                                                                    | V |

|   | Table of Contents                                                                                                             | v |

|   | List of Figures                                                                                                               | i |

|   | List of Tables                                                                                                                | x |

|   | Vita, Publications, and Fields of Study                                                                                       | i |

|   | Abstract                                                                                                                      | v |

| Ι | Introduction                                                                                                                  | 1 |

|   | A. On-Chip Interconnect: Challenges and Opportunities                                                                         | 1 |

|   | B. Previous Works                                                                                                             | 3 |

|   | 1. Non-Manhattan Routing Architectures                                                                                        | 3 |

|   | 2. High-Speed Clock Distribution                                                                                              | 4 |

|   | 3. High Performance On-Chip Interconnects                                                                                     | 6 |

|   | C. Our Approaches and Contributions                                                                                           | 6 |

|   | 0                                                                                                                             | 6 |

|   | 2. High-Speed Clock Distribution                                                                                              | 7 |

|   | 3. High Performance On-Chip Interconnects                                                                                     | 9 |

|   | D. Organization of the Dissertation                                                                                           | 9 |

| Π | Non-Manhattan Routing Architectures                                                                                           | 1 |

|   | A. Physical Planning of Interconnect Architectures                                                                            | 1 |

|   | 1. Introduction $\ldots$                     | 2 |

|   | 2. Problem Formulation $\ldots \ldots 14$ | 4 |

|   | 3. Routing Architectures                                                                                                      | 7 |

|   | 4. Experimental Results                                                                                                       | 1 |

|   | 5. Conclusions $\ldots \ldots 28$         | 8 |

|   | B. The Y-Architecture for On-Chip Interconnect:                                                                               |   |

|   | Analysis and Methodology                                                                                                      | 9 |

|   | 1. Introduction                                                                                                               | 0 |

|   | 2. Communication Throughput in Meshes                                                                                         | 2 |

|   | 3. Wirelength Reduction 3.                                                                                                    | 4 |

|   | 4. Y Clock Tree                                                                                                               |   |

|   | 5. Y Power Distribution                                                                                                       | 9 |

|   | 6. Routability in the Y-Architecture                                                                                          |   |

|   | 7. Conclusions                                                                                                                | 1 |

| III | High Speed Clock Distribution in the Presence of Parameter Variations 5                                                                                        | 53 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | A. A Multiple-Level Network Approach for Clock Skew Minimization                                                                                               |    |

|     | with Process Variations                                                                                                                                        | 53 |

|     | 1. Introduction $\ldots$ $\ldots$ $\ldots$ $\ldots$ 5                                                                                                          | 53 |

|     | 2. Problem Formulation                                                                                                                                         | 56 |

|     | 3. Skew Shunt Resistance Relations in A Simplified Circuit Model . 5                                                                                           | 59 |

|     | 4. Clock Skew on Meshes                                                                                                                                        | 61 |

|     | 5. Optimization of Multi-level Clock Networks                                                                                                                  | 68 |

|     |                                                                                                                                                                | 69 |

|     | 7. Discussions on Inductive Effect                                                                                                                             | 72 |

|     | 8. Conclusion and Future Directions                                                                                                                            | 73 |

|     | B. PVT Variations Aware Clock Tree Synthesis in the Presence of Rout-                                                                                          |    |

|     | ing Obstacles                                                                                                                                                  | 74 |

|     | 1. Introduction                                                                                                                                                | 74 |

|     | 2. Problem Statement                                                                                                                                           | 78 |

|     | 3. Overall flow of the methodology                                                                                                                             | 80 |

|     | 4. Initial tree topology generation                                                                                                                            | 80 |

|     | 5. Multi-level refinement and tree embedding                                                                                                                   | 86 |

|     | 6. Experimental Results                                                                                                                                        | 88 |

|     | 7. Conclusions and Future Directions                                                                                                                           | 89 |

|     | C. A Multi-Level Transmission Line Network Approach for Multi-Giga                                                                                             |    |

|     | Hertz Clock Distribution                                                                                                                                       | 91 |

|     | 1. Introduction $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                        | 92 |

|     | 2. Problem formulation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                          | 94 |

|     | 3. Skew reduction effect of transmission line shunts                                                                                                           | 98 |

|     | 4. Optimal sizing of multiple level spirals network                                                                                                            | )1 |

|     | 5. Experimental results $\ldots \ldots \ldots$ | )3 |

|     | 6. Conclusions $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ 10                                                             | )7 |

|     |                                                                                                                                                                |    |

| IV  | Distortionless Transmission Line for On-Chip Electrical Signaling 10                                                                                           |    |

|     | A. Introduction                                                                                                                                                |    |

|     | B. Theory of Distortionless Transmission Lines                                                                                                                 |    |

|     | 1. Distortion and ISI                                                                                                                                          |    |

|     |                                                                                                                                                                | 14 |

|     | 3. Sensitivity of Distortionless Transmission Lines to the Parameters                                                                                          | 10 |

|     | Variations                                                                                                                                                     |    |

|     | 1 0 1                                                                                                                                                          | 17 |

|     |                                                                                                                                                                | 19 |

|     | E. Conclusion $\ldots \ldots 12$                      | 21 |

| V   | Conclusion and Future Directions                                                                                                                               | 22 |

| Appendices                                                          |

|---------------------------------------------------------------------|

| A. Analysis of the "Virtuous Cycle" Wirelength Reduction Effect 124 |

| B. Approximation of Equation (II.4)                                 |

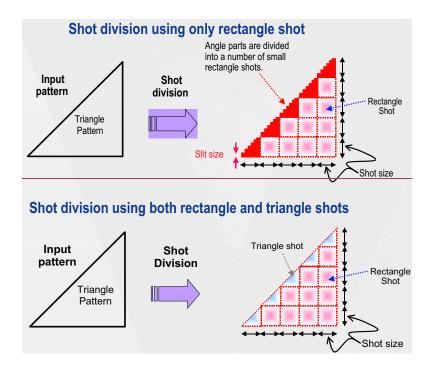

| C. Manufacturing and Other Issues                                   |

| D. Derivation of the skew expression                                |

| Bibliography                                                        |

### LIST OF FIGURES

| I.1          | Example of 45 degree mesh of $n = 4 \dots \dots \dots \dots \dots \dots \dots$                                              | 2        |

|--------------|-----------------------------------------------------------------------------------------------------------------------------|----------|

| II.1<br>II.2 | A 5 by 5 communication mesh and its graph representation Example of 45 degree mesh of $n = 4$                               | 15<br>19 |

| II.3         | A 90-degree and 45-degree mixed mesh of $n = 5$                                                                             | 20       |

| II.4         | A network flow model for multiplayer routing                                                                                | 21       |

| II.5         | Flow congestion for uniform edge capacities                                                                                 | 22       |

| II.6         | Optimal row width of 9 by 9 mesh to maximize total throughput                                                               | 23       |

| II.7         | Flow congestion in 45-degree mesh                                                                                           | 25       |

| II.8         | Explanation of throughput increase for a 45-degree mesh                                                                     | 26       |

| II.9         | Different routing directions assignments                                                                                    | 28       |

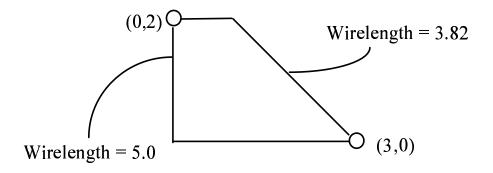

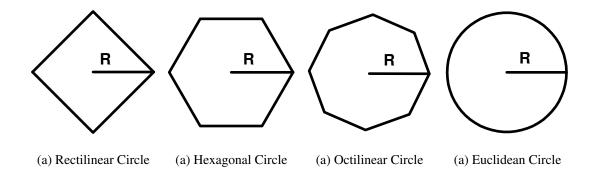

|              | Shortest path between two points on the plane                                                                               | 28       |

|              | $7 \times 7$ meshes with different interconnect architectures                                                               | 33       |

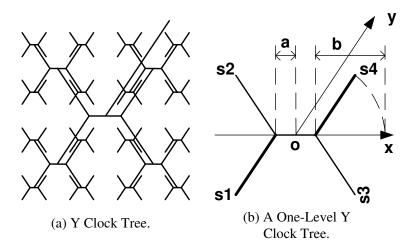

|              | Y Clock Tree.                                                                                                               | 38       |

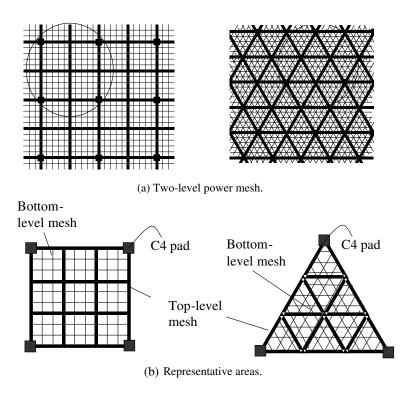

| 11.13        | Power distribution networks and representative areas for M- and                                                             | 10       |

| TT 1 4       | Y-architectures.                                                                                                            | 40       |

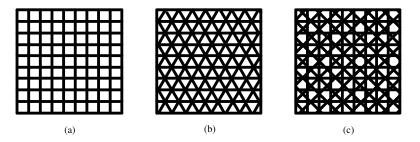

|              | Routing grids in M-, Y- and X-architectures                                                                                 | 47       |

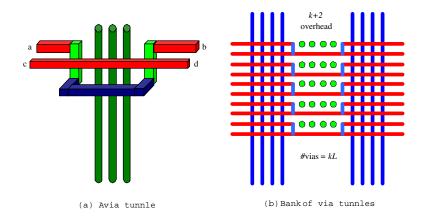

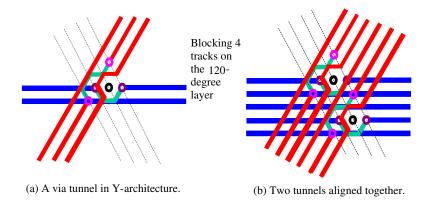

|              | Via tunnel and bank of via tunnels in the M-architecture                                                                    | 48<br>49 |

|              | Via tunnels with vias aligned in a line in Y-architecture                                                                   | 49<br>49 |

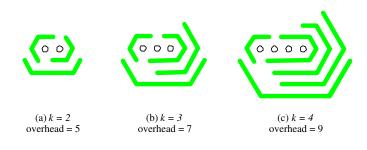

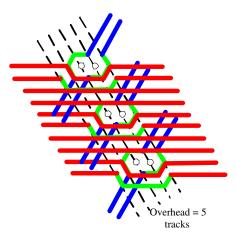

|              | Three tunnels with $k = 2$ aligned together                                                                                 | 49<br>50 |

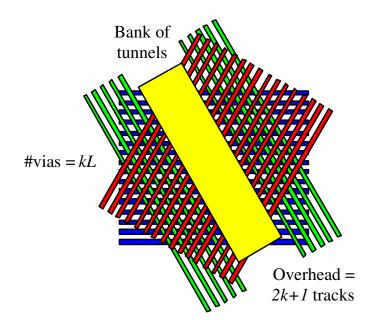

|              | Bank of via tunnels in Y-architecture                                                                                       | 50<br>51 |

| 11.10        |                                                                                                                             | 01       |

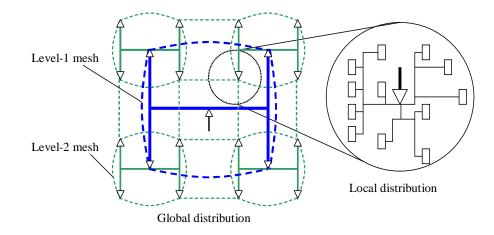

|              | global and local clock distribution networks                                                                                | 55       |

|              | An H-tree with A Two Level Mesh                                                                                             | 58       |

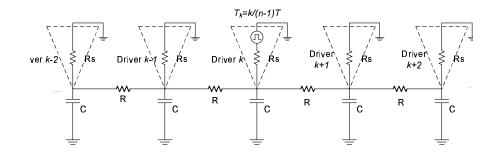

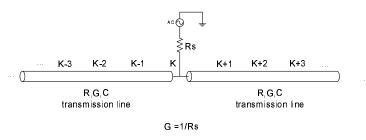

|              | simplified Circuit Model of RC Shunt                                                                                        | 60       |

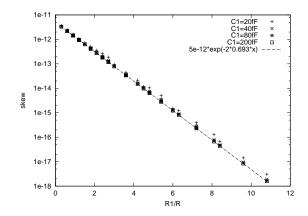

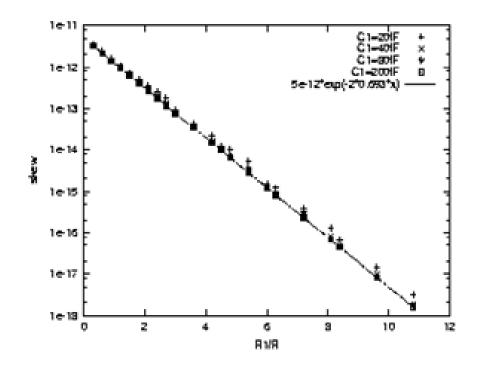

|              | Skew $R_s/R$ relation in the simplified $RC$ circuit model                                                                  | 62       |

| 111.5        | RGC transmission line approximation when only one driver takes                                                              |          |

|              | effect                                                                                                                      | 64       |

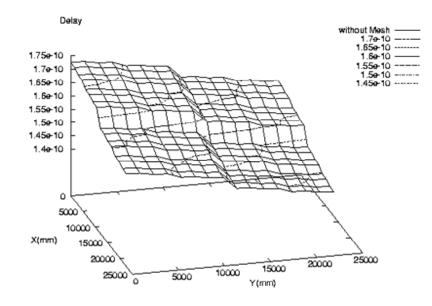

|              | Circuit model used to calculate the skew on a mesh                                                                          | 67<br>71 |

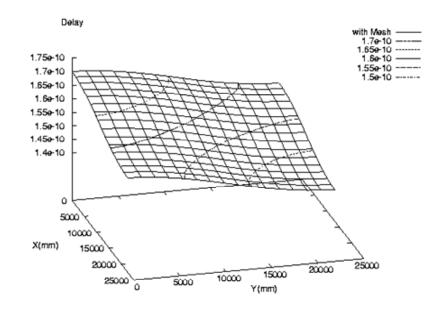

|              | Delay of leaf nodes on an H-tree without mesh                                                                               | 71<br>72 |

|              | Delay of leaf nodes on an H-tree with multilevel meshes                                                                     | 72<br>70 |

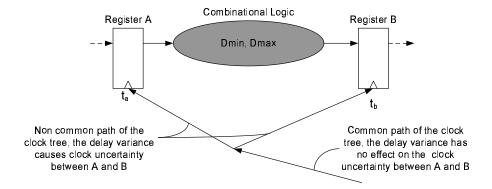

|              | Clock Uncertainties and Timing Constraints in Sequential Circuits .<br>0PVT Variations Aware Clock Tree Synthesis Algorithm | 79<br>81 |

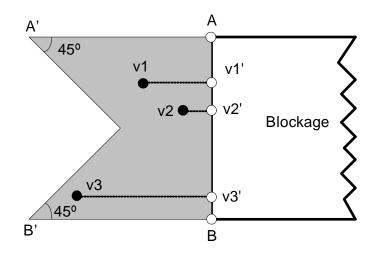

|              | 1 <i>Shadow region</i> and direct virtual node insertion                                                                    | 82       |

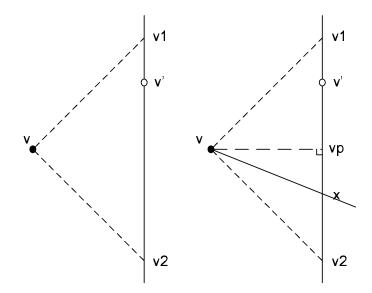

|              | 2Proof of Theorem 1                                                                                                         | 83       |

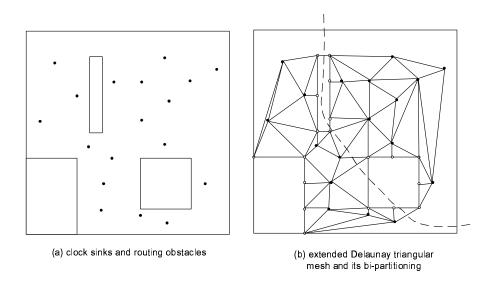

|              | 3Extended Delaunay Triangulization and a Bi-Partitioning of Trian-                                                          | 00       |

| 111.1        | gular Graph                                                                                                                 | 85       |

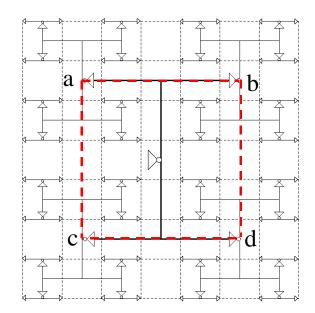

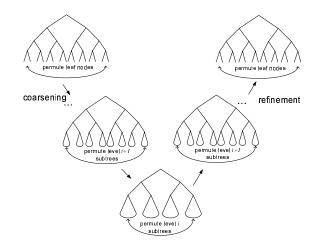

| III.1        | 4A v-cycle of multilevel clock tree refinement                                                                              | 86       |

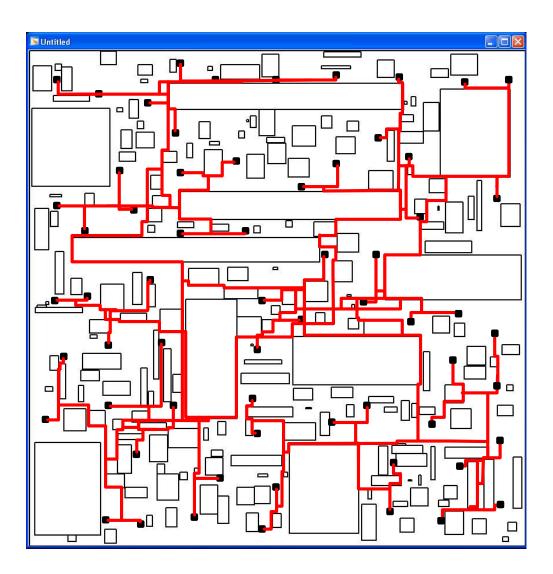

|              | 5Clock tree for a 200K flip-flops, 200 obstacles chip top level route                                                       | - •      |

|              | are shown, small black squares indicate the root of local routing trees                                                     | 90       |

|              |                                                                                                                             |          |

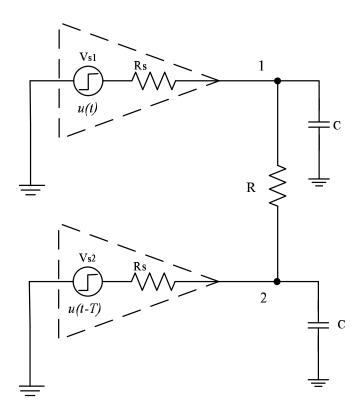

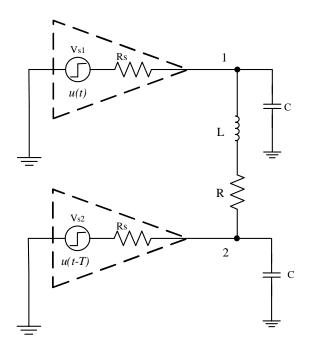

| III.16Two clock drivers shunted by a lumped RLC line                                                                                                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

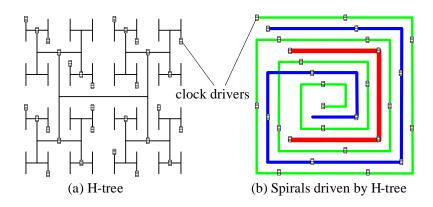

| III.17Multi-level Tansmission Line Spirals Network                                                                                                                                                                                                                                       |

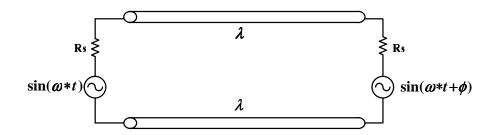

| III.18Two sinusoidal sources with phase shift shunted by a wavelength                                                                                                                                                                                                                    |

| long transmission line                                                                                                                                                                                                                                                                   |

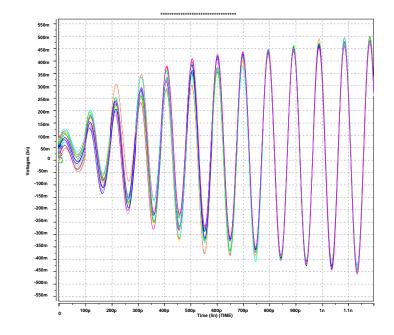

| III.19Simulated waveform of two sources shunted by one wavelength long                                                                                                                                                                                                                   |

| transmission line                                                                                                                                                                                                                                                                        |

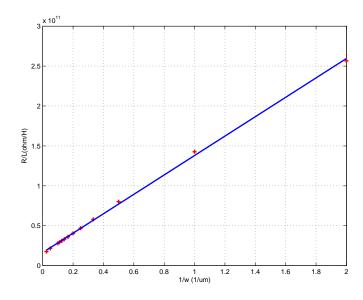

| III. $20R/L$ and $1/w$ relation at 10GHz                                                                                                                                                                                                                                                 |

| III.21Transient Waveforms on Bottom Level Spiral                                                                                                                                                                                                                                         |

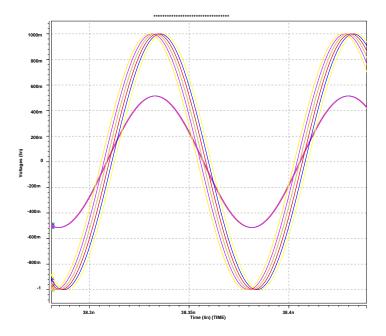

| III.22Steady States Waveforms on Bottom Level Spiral                                                                                                                                                                                                                                     |

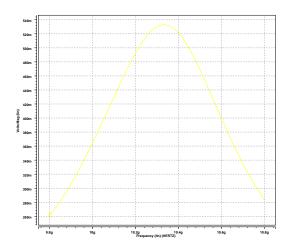

| III.23Frequency response of the transmission line network: voltage $\sim$ fre-                                                                                                                                                                                                           |

| quency relation                                                                                                                                                                                                                                                                          |

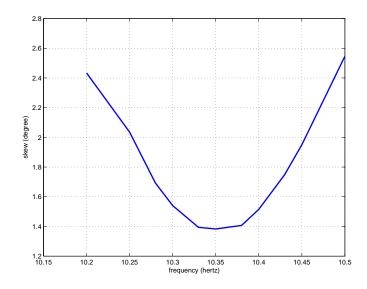

| III.24Frequency response of the transmission line network: skew $\sim$ fre-                                                                                                                                                                                                              |

| quency relation $\ldots \ldots \ldots$                                                                                                                                   |

|                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                          |

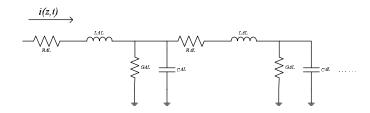

| IV.1 $RLGC$ model of a transmission line                                                                                                                                                                                                                                                 |

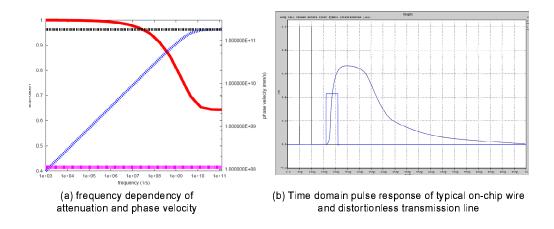

| $\operatorname{IV.2}$ The attenuation and phase velocity v.s. frequency for a on-chip wire $115$                                                                                                                                                                                         |

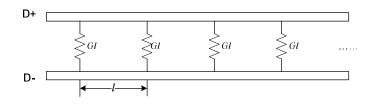

| IV.2 The attenuation and phase velocity v.s. frequency for a on-chip wire 115 IV.3 On-Chip Implementation of Surfliner                                                                                                                                                                   |

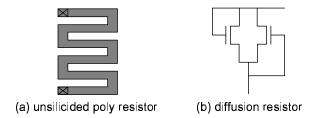

| IV.2 The attenuation and phase velocity v.s. frequency for a on-chip wire 115IV.3 On-Chip Implementation of SurflinerIV.4 Design of shunt conductorsIV.4 Design of shunt conductors                                                                                                      |

| <ul> <li>IV.2 The attenuation and phase velocity v.s. frequency for a on-chip wire 115</li> <li>IV.3 On-Chip Implementation of Surfliner</li></ul>                                                                                                                                       |

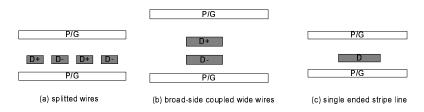

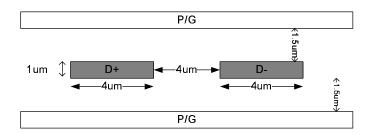

| IV.2 The attenuation and phase velocity v.s. frequency for a on-chip wire 115IV.3 On-Chip Implementation of SurflinerIV.4 Design of shunt conductorsIV.5 Wire configurations to increase the coupling between differential wiresIV.6 Implementation of WiresIV.6 Implementation of Wires |

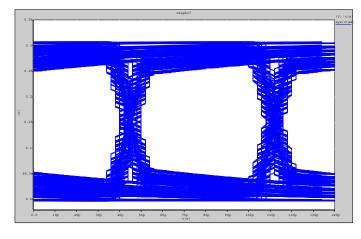

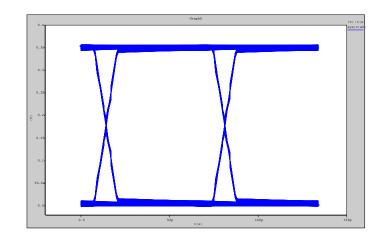

| <ul> <li>IV.2 The attenuation and phase velocity v.s. frequency for a on-chip wire 115</li> <li>IV.3 On-Chip Implementation of Surfliner</li></ul>                                                                                                                                       |

| IV.2 The attenuation and phase velocity v.s. frequency for a on-chip wire 115IV.3 On-Chip Implementation of SurflinerIV.4 Design of shunt conductorsIV.5 Wire configurations to increase the coupling between differential wiresIV.6 Implementation of WiresIV.6 Implementation of Wires |

| <ul> <li>IV.2 The attenuation and phase velocity v.s. frequency for a on-chip wire 115</li> <li>IV.3 On-Chip Implementation of Surfliner</li></ul>                                                                                                                                       |

| $ \begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                    |

| <ul> <li>IV.2 The attenuation and phase velocity v.s. frequency for a on-chip wire 115</li> <li>IV.3 On-Chip Implementation of Surfliner</li></ul>                                                                                                                                       |

### LIST OF TABLES

| II.1  | Results of uniform edge capacity mesh                                        | 22  |

|-------|------------------------------------------------------------------------------|-----|

| II.2  | Results of fixed total edge capacities                                       | 23  |

| II.3  | Optimal capacities for vertical edges in 6 by 6 mesh                         | 24  |

| II.4  | Results of 45-degree mesh                                                    | 25  |

| II.5  | Results of 90-degree and 45-degree mixed mesh                                | 27  |

| II.6  | Throughput with different routing layer assignments                          | 27  |

| II.7  | Normalized throughput (and improvement vs. M-architecture) in                |     |

|       | square meshes with Rentian demand                                            | 34  |

| II.8  | Average wirelength improvements for Non-Manhattan placement                  |     |

|       | and routing vs. Manhattan placement and routing (%).                         | 36  |

| II.9  | Total wirelength of instance "C2" with different combinations of             |     |

|       | placement and routing.                                                       | 36  |

| II.10 | Total wirelength of instance "Balu" with different combinations of           |     |

|       | placement and routing.                                                       | 37  |

| II.11 | Total wirelength of instance "Primary1" with different combinations          |     |

|       | of placement and routing.                                                    | 37  |

| II.12 | 2 Total wirelength of instance "C5" with different combinations of           |     |

|       | placement and routing.                                                       | 37  |

| II.13 | Path length and total wirelength of H-tree, X-tree and Y-tree                | 38  |

|       | Simulation results for worst-case IR-drop on the single-level power          |     |

|       | mesh in the Y-architecture, compared to estimated values (mV)                | 44  |

| II.15 | IR-drop improvements in single-level Y-mesh vs. M-mesh.                      | 45  |

|       |                                                                              |     |

|       | The calculated and simulated $k$ -values for one-dimensional meshes .        | 66  |

|       | $k$ -value of clock meshes for different input skew patterns $\ldots$ .      | 68  |

| III.3 | Optimal wire sizing of a 4-level clock network                               | 70  |

| III.4 | Skew comparison between single level and mutli-level meshes                  | 70  |

| III.5 | Skew comparison with supply voltage variations                               | 70  |

| III.6 | Comparisons between our method and DME                                       | 88  |

|       | Skew and frequency relation of a shunt segment $\ldots \ldots \ldots \ldots$ | 95  |

|       | Skew on a spiral from simulation and calculation                             |     |

| III.9 | Frequency dependant R and L at 10GHz                                         | 101 |

| III.1 | 00ptimized wire width of each level spiral                                   | 104 |

| III.1 | 1Power Consumption Comparisons                                               | 105 |

| III.1 | 2Skew comparison in the presence of voltage variations                       | 106 |

| IV 1  | Jitter and silicon area usage                                                | 119 |

|       | power consumption w/ different wire width and separation                     |     |

|       |                                                                              |     |

VITA

| 2000      | B.S. in Computer Science and Technology<br>Tsinghua University, Beijing, China |

|-----------|--------------------------------------------------------------------------------|

| 2002      | M.S. in Computer Science<br>University of California, San Diego                |

| 2000-2005 | $Research \ Assistant, \ University \ of \ California, \ San \ Diego$          |

| 2006      | PhD in Computer Science and Engineering<br>University of California, San Diego |

### PUBLICATIONS

B. Yao, H. Chen, C. K. Cheng, and R. Graham, "Floorplan Representations: Complexities and Connections," in *ACM Trans. on Design Automation of Electronic Systems*, vol.8(1), pp.55-80, February, 2003.

H. Chen, C. K. Cheng, A. B. Kahng, I. Măndoiu, Q. Wang, and B. Yao, "The Y-Architecture for On-Chip Interconnect: Evaluations and Methodologies," accepted for publication by *IEEE Trans. on Computer Aided Design of Integrated Circuits and Systems.*

H. Chen, M. Mori, B. Yao, and C. K. Cheng, "A Multi-level Network Approach for Clock Skew Minimization Under Process Variations," submitted to *IEEE Trans.* on Computer Aided Design of Integrated Circuits and Systems.

H. Chen, C. Y. Yeh, S. M. Reddy, G. Wilke, H. V. Nguyen, and W. W. Walker, "A Sliding Window Scheme for Accurate Clock Mesh Analysis," to appear in *International Conference on Computer Aided Design* 2005.

H. Chen, R. Shi, C. K. Cheng, and D. M. Harris, "Distortionless Electrical Signaling for Speed of Light On-Chip Communications," to in *International Conference* on Computer Design, 2005.

Y. Hu, H. Chen, Y. Zhu, A. Chien, and C. K. Cheng, "Physical Synthesis of Energy Efficient Network-On-Chip Through Topology Exploration and Wire Style Optimization," to appear in *International Conference on Computer Design* 2005.

B. Yao, H. Chen, C. K. Cheng, N. C. Chou, L. T. Liu, and P. Suaris, "Unified Quadratic Programming Approach for Mixed Mode Placement," in *International Symposium on Physical Design* 2005.

H. Chen and C. K. Cheng, "A Multi-Level Transmission Line Network Approach for Multi-Giga Hertz Clock Distribution," in *Asia and South Pacific Design Automation Conference*, January 2005. R. Shi, H. Chen, C. K. Cheng, D. Beckman, and D. Huang, "Layer Count Reduction for Area Array Escape Routing", in *IMAPS International Conference and Exhibition on Device Packaging*, March, 2005.

M. Mori, H. Chen, B. Yao, and C. K. Cheng, "A Multi-Level Network Approach for Clock Skew Minimization Under Process Variations," in *Proceedings of Asia* and South Pacific Design Automation Conference, pp. 263-268, January 2004.

H. Chen, C. K. Cheng, A. B. Kahng, and Q. Wang, "Optimal Planning for Mesh-Based Power Distribution," in *Proceedings of Asia and South Pacific Design Automation Conference*, pp. 444-449, January 2004.

H. Chen, C. K. Cheng, A.B. Kahng, Ion Măndoiu, Q. Wang, and B. Yao, "The Y-Architecture for On-Chip Interconnect: Analysis and Methodologies," in *Proceedings of International Conference on Computer Aided Design*, pp. 13-19, November 2003.

H. Chen, C. K. Cheng, N. C. Chou, A. B. Kahng, J. MacDonald, B. Yao, and Z. Zhu, "An Algebraic Multigrid Solver for Analytical Placement with Layout Based Clustering," in *Proceedings of Design Automation Conference*, pp. 794-799, June, 2003.

H. Chen, C. K. Cheng, A. B. Kahng, I. Măndoiu, and Q. Wang, "Estimation of Wirelength Reduction for  $\lambda$ -Geometry vs. Manhattan Placement and Routing," in *Proceedings of ACM/IEEE International Workshop on System Level Interconnect Prediction*, pp. 71-76, April, 2003.

H. Chen, B. Yao, F. Zhou, and C. K. Cheng, "Y-architecture: Yet Another On-Chip Interconnect Solution," in *Proceedings of Asia and South Pacific Design Automation Conference*, pp.840-846, January, 2003.

H. Chen, B. Yao, F. Zhou, and C. K. Cheng, "Physical Planning of On-Chip Interconnect Architectures," in *Proceedings of IEEE International Conference on Computer Designs*, pp.30-35, September 2002.

H. Chen, C. Qiao, F. Zhou, and C. K. Cheng, "Refined Single Trunk Tree: A Rectilinear Steiner Tree Generator for Interconnect Prediction," in *Proceedings* of ACM/IEEE International Workshop on System Level Interconnect Prediction, pp.85-89, April, 2002.

B. Yao, H. Chen, C. K. Cheng, and R. Graham, "Revisiting Floorplan Representations," in *Proceedings of ACM International Symposium on Physical Design*, pp.138-143, April, 2001.

### FIELDS OF STUDY

Major Field: Computer Science and Engineering Studies in Computer Aided Design of Very Large Integrated Circuits. Professor Chung-Kuan Cheng

### ABSTRACT OF THE DISSERTATION

On-Chip Interconnect Architectures: Perspectives of Layout, Circuits, and Systems

by

Hongyu Chen Doctor of Philosophy in Computer Science University of California, San Diego, 2006 Professor Chung-Kuan Cheng, Chair

With exponentially increasing integration densities and shrinking characteristic geometries on a chip, the wires, rather than devices, become the dominant factor in deciding the performance, power consumption, and reliabilities of VLSI systems. Previous researches on interconnect centric design methodologies mainly concentrate on optimizing individual nets. Instead of searching for the best algorithm to optimize each individual net, we take a view of the on-chip interconnection architectures, and improve the system performance by considering both geometrical arrangements of wires, electrical behaviors of global distribution networks, as well as adopting innovative interconnect circuit styles.

Traditional Manhattan routing restricts the wires on horizontal and vertical tracks. This artificial restriction causes excessive wirelength overhead over the Euclidean optimum and thus decreases the efficiency of the interconnect system. We investigated the optimal way to utilize the on-chip routing layers through non-Manhattan routing. We adopted multi-commodity flow models to measure the throughput of different on-chip interconnect architectures. Through careful analysis of the bottlenecks of the on-chip communication traffic, we found that the Y-architecture (3-directional routing) enjoys a lot of nice properties over other routing architectures. We developed a design methodology for Y-architecture, including power and clock distribution and a novel way to hide the via blockage effect.

Clock distribution network is one of the most important interconnect on a chip. We studied the high speed clock distribution in the presence of parameter variations. We proposed a spectrum of solutions for circuits working at different frequencies: A variations aware clock tree synthesis algorithm for high-end ASICs, a multi-level mesh approach for microprocessors, and a transmission line network approach for future multi-giga hertz chips. Simulation results suggest that these approaches significantly improve clock distribution networks' resilience against process, voltage and temperature variations.

We proposed a novel scheme to implement distortionless transmission lines for on-chip electrical signaling. By introducing intentional leakage conductance between the wires of a differential pair, the distortionless transmission line eliminates dispersion caused by the resistive nature of on-chip wires and achieves speed of light transmission. We show that it is feasible to construct distortionless transmission line with conventional silicon process. Simulation results show significant improvements in both speed and power consumption over conventional RCwires with repeated buffers.

## Ι

# Introduction

### I.A On-Chip Interconnect: Challenges and Opportunities

With the advance of the processing technology, interconnect is becoming the dominant factor in deciding the power consumption, performance, reliability, and cost of VLSI systems. This fact has been widely recognized in both academia and industry. As evidenced in the SRC Roadmap, the scalability of interconnect is remarked as a "principal challenge" to the continua of Moore's Law.

Interconnect power consumption grows with each technology node generation. The dynamic power is proportional to  $fCV^2$ , where f is the frequency of data activity, C is the total capacitance, and V is the supply voltage. As design rules shrink, frequency f increases. The total capacitance C per unit area also increases since we have more, finer pitch wires in the same area while the wire capacitance per unit length remains fairly constant [73, 74]. However, the supply voltage V does not scale much (Table 47a of [90]) due to the limit of threshold voltage. Consequently, the dynamic interconnect power increases. In [76], Magen, et al. at Intel found that interconnect power alone accounted for half the total dynamic power in a  $0.13\mu m$  microprocessor that was designed for power efficiency.

At the technology nodes beyond 65nm, the leakage power constitutes a significant portion of total power consumption. In order to achieve the delay

Figure I.1: Example of 45 degree mesh of n = 4

and slew rate specification, traditional RC wires require a substantial number of repeaters inserted. According to the estimation of [87], at 45nm node, the repeaters can account to over 30% of overall chip area in a high performance microprocessors. These repeaters consume a great amount of static power due to leakage current. As a result, interconnect power consumption can potentially be a limiting factor of Moore's law.

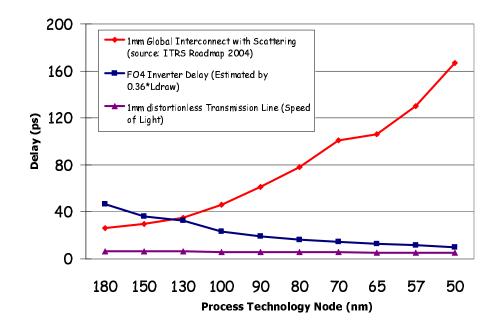

Interconnect delay dominans the system performance. In Figure I.1, we depict the gate and interconnect delay scaling trends according to the SRC roadmap. The delay of a 1mm Cu global interconnect at minimum pitch increases from 46ps at the 100nm node to 167ps at the 50nm node, assuming added resistance due to width dependent scattering and a conformal barrier of thickness (Table 81a of [71]). The fanout-of-4 (FO4) inverter delay is estimated using the equation  $0.36ns/\mu m \times L_{drawn}$  proposed by Horowitz [75], where  $L_{drawn}$  is the printed channel length for the given technology. The curve at the bottom describes a transmission line carrying the differential signal as an electromagnetic wave. For an ideal transmission line, the wave propagates at the speed of light, which reduces from

5ps/mm at the 100nm node to 4ps/mm at 50nm node due to the reduction of effective dielectric constant. Since the speed of light is the physical limit of the given technologies, one of our ultimate goals is to achieve this speed.

In Ultra-Deep-Sub-Micron processes, process variations presents great challenges to the yield and reliability of a design. One of the most vulnerable components subject to the process and other parameters variations is the clock distribution network. As the clock frequency continuously getting higher, the clock uncertainty caused by the variations consumes increasing portion of clock period time. At the same time, clock distribution is one major consumer of the dynamic power. For high speed circuit, the clock

Facing all the challenges discussed above, it is imperative to identify solutions which address global wiring scaling issues. In this thesis, we optimized the on-chip interconnect architectures from different perspectives, including, optimal geometrical arrangement through non-Manhattan routing, variations aware clock distribution architectures, and an innovative on-chip signaling scheme.

### I.B Previous Works

This section gives an overview of the previous works on the three problems we are studied.

### I.B.1 Non-Manhattan Routing Architectures

With rapid technology scaling, the interconnect becomes one most precious resource on a chip. Traditional Manhattan interconnect architecture organizes wires on two orthogonal routing directions, 0-degree and 90-degree directions, for the simplicity of routing embedding and design rule checking. However, its artificial restriction on routing directions adds significant wire length over the Euclidean optimum and thus decreases the communication capability of the onchip interconnects. In the past decade, many researchers have explored the possibility of using non-rectilinear wires to improve the efficiency of on-chip interconnects.[4] Most of these work discussed about how to introduce 45-degree short jogs to improve the routability of the chip in the detailed routing stage. Majority of the wires on the chip are still routed on either 0-degree or 90-degree direction.

Recently, Teig et. al. [7] proposed a new on-chip interconnect architecture named the X-architecture, which is targeting at the designs with 5 or more routing layers. In the X-architecture, the wires are organized in 0-degree, 45-degree, 90degree and 135-degree directions. The experimental results from the first industrial design [91] show that it achieves a chip performance improvement of 10% and power reduction of 20% than Manhattan architecture for a high performance design.

### I.B.2 High-Speed Clock Distribution

Clock distribution has been widely studied in the past twenty years. A wealth of literature can be found on both CAD algorithms and clock distribution architectures.

The median and mean method (MMM) proposed by Jackson et *al.* [11] recursively partition the clock sinks on a plane according to the locations. This method produces a well balanced topology. However, it does not consider routing obstacles.

The geometric matching [12] and greedy-DME [6], uses bottom -up matching to construct the tree topology. These methods depend on the dynamic nearest neighbor queries, which is computationally expensive in the presence of routing obstacles. In a Manhattan plane without obstacles, the shortest path query only takes O(1) time, while with obstacles, the fastest algorithms have a time complexity of at least  $O(m \log m)$ , where m is the number of corner nodes of all obstacles.

Ellis et *al.*[7] and Chou et *al.* [5] both used simulated annealing to search for the optimal tree topology. Multiple objectives are optimized simultaneously in the simulated annealing framework. Recently, several works target at the variations aware clock tree synthesis. Velenis et *al.* [21] first noticed that not all datapath have the same sensitivity to the clock uncertainty, and use a sequential merging scheme to construct the clock tree topology. Their method does not use any physical proximity information. It may results in excessively large total wire length, and the tree topology may be very unbalanced.

In [10], Hu et *al.* extended the DME [2] algorithm to accommodate the permissible clock uncertainty constraints for a given clock tree topology. This method can significantly reduce the timing violations caused by the process variations on the interconnect. However, since the tree topology is generated by the non-variations-aware DME algorithm, it could not reduce the clock uncertainties caused by the voltage variations on the clock buffers, which is believed to be one main cause of clock uncertainties. In [3], the clock sinks are partitioned into groups, the algorithm reduces the wirelength by only minimizing intra-group skew values.

Clock mesh has been applied to high performance microprocessors to achieve low skew distribution, one exemplary design is DEC Alpha Series [91,92,93]. A recent trend is to use the hybrid structure of a mesh and a symmetric buffer tree for the global clock network. For example, the global clock distribution of Intel Pentium $4^{TR}$  microprocessor consists three spines each driven by a balanced binary buffer tree [1]. The bottom-level spines can be deemed as a "one dimensional" mesh structure. Restel et *al.* proposed a two-level hybrid clock network. The top level is an H-tree, and the bottom level is a uniform mesh that connects all of the leaves of the top level H-tree. This clock network structure has been successfully applied to six designs[1], including the latest Power4 microprocessors [9][14]. The measurements from the real produced chips proved that this hybrid tree and mesh structure accomplishes low clock skew under process variations.

One drawback of the dense mesh for clock distribution is its high power consumption. A transmission line network with a properly tailored length can achieve low power low skew distribution. Galton et al. [7] showed that when the wire length is shorter than one quarter wavelength, the transmission line can synchronize oscillators both in phase and magnitude. Several other researches utilized the synchronization capability of the transmission line in clock distribution by connecting the distributed PLLs together with transmission lines [8,9,20]. In order to compensate the lossy nature of the on-chip transmission lines, [14] used distributed transconductors along the transmission line to generate the standing wave.

### I.B.3 High Performance On-Chip Interconnects

Buffer insertion has been used to improve the speed of on-chip interconnect in deep sub-micron technologies. [24] gives a complete survey of the buffer insertion techniques.

In [25], pre-emphasizing and de-emphasizing along with data aliasing are used to modulate the input wave form. In [20], Afshari and Hajimiri adopted a non-linear transmission line approach to generate solitary wave propagation and thus compensate for the dispersion. In [23], a high frequency carrier modulates the input waveform and shifts the spectrum of transmitted signal to a less frequency sensitive region. In [27], a clocked discharging scheme is adopted to erase the data dependant delay variations. In [30], an adaptive equalization scheme is used to compensate the propagation loss.

### I.C Our Approaches and Contributions

Our approaches to solve the three problems in the physical planning are summarized in this section. Our contributions are highlighted.

### I.C.1 Non-Manhattan Routing Architectures

We developed mathematical models to measure the throughput of different on-chip interconnect architectures. Through careful analysis of the bottlenecks of the on-chip communication traffic, we found that the Y-architecture (3-directional routing) enjoys a lot of nice properties over other routing architectures. We develop a design methodology for Y-architecture, including power and clock distribution and a novel way to hide the via blockage effect.

Our contributions include:

- 1. A multi-commodity flow (MCF) model to evaluate the throughput of different routing architectures and a combinatorial approximation scheme to find the optimal routing resource allocation under the MCF model

- 2. Y-Architecture and its associated design methodologies

- 3. Via tunnels and via tunnel banks to minimize the via blockage effects

### I.C.2 High-Speed Clock Distribution

We studied the high-speed clock distribution in the presence of process, voltage, and temperature (PVT) variations. Our research addresses a spectrum of needs for variation tolerant clock distribution networks, including, a PVT variations aware clock tree synthesis algorithm, a multi-level mesh architecture, and a transmission line network architecture.

### Process, voltage, and temperature variations aware clock tree synthesis in the presence of routing obstacles

Clock tree synthesis has been a classic problem in the CAD community because of its clean mathematical formulation. However, in industry practices, there are various engineering challenges. Two of them are the existence of routing obstacles and the requirement to minimizing clock uncertainties introduced by parameter variations. In this study, we minimize the clock tree wire length in the presence of routing obstacles and clock uncertainty constraints.

We extend the Delaunay triangular mesh to represent the physical proximity of clock sinks in the presence of rectilinear routing obstacles. Combining the Delaunay triangular mesh and clock uncertainty constraint graph, we adopt graph partitioning technique to generate a clock tree topology, which balances the wirelength and timing. We further use a multilevel algorithm to optimize the tree topology and embedding.

Experimental results show significant improvement on PVT variations tolerances with very minor wire length overhead.

# Multi-level mesh for clock skew minimization in the presence of process variations

In high performance systems, mesh structures has been used for low skew clock distribution. However, there is no design guideline on choosing the optimal mesh granularity and wire sizes. We investigate the skew reduction effect of shunt connections and seek for the best mesh structures for given total routing area.

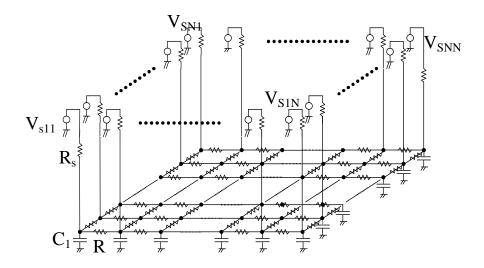

We derive an analytical expression of the skew reduction effect of resistive shunts. Based on this theoretical study, we propose a multi-level mesh structure for process variations tolerant clock distribution. We adopt a convex programming approach to optimize the proposed clock network. Simulation results demonstrate more than 70% reduction on the clock skew comparing with widely adopted single level mesh structure.

### Transmission line network for multi-giga hertz clock distributions

With the clock frequency thrusting into multi-giga hertz range, the shunt effect of RC wire diminishes because of the inductive effect. On the other hand, the transmission line has its unique property to lock the oscillators together. We study how to construct an extreme low skew clock distribution network which tailors the natural frequency of transmission lines.

We design a multiple level transmission line network which can work in the multiple giga-hertz range. We derive the analytical expression of phase locking capabilities of on-chip transmission lines. Based on the this expression, we use mathematical programming technique to optimize the network. Simulation results suggest great improvement of variations tolerance and power consumption.

### I.C.3 High Performance On-Chip Interconnects

We devised a novel scheme to implement distortionless transmission lines for on-chip electrical signaling. By introducing intentional leakage conductance between the wires of a differential pair, the distortionless transmission line eliminates dispersion caused by the resistive nature of on-chip wires and achieves speed of light transmission. We show that it is feasible to construct distortionless transmission line with conventional silicon process. Simulation results show that using 65nm technology, the proposed scheme can achieve 15Gbits/s bandwidth over a 20mm on-chip serial link without any equalization. This approach offers a six times improvement in delay and 85% reduction in power consumption over a conventional RC wire with repeated buffers.

### I.D Organization of the Dissertation

The following chapters of the dissertation are organized as follows:

Chapter II discusses Non-Manhattan Routing Architectures. The chapter has two parts. Section II.A presented our research on the physical planning of onchip interconnect architectures. After that, we discussed the Y-architecture and associated design methodologies in Section II.B.

Chapter III is on the high-speed clock distributions. In includes three parts. In Section III.A, a PVT variations aware clock tree algorithm is presented. In Section III.B, a multi-level mesh architecture is proposed. In Section III.C, a transmission line network approach is shown.

Chapter IV describes a distortionless transmission line approach for highspeed, low-power on-chip communications.

Chapter V draws the conclusions. Several possible directions on extending

the works in this dissertation are also given.

## Π

# Non-Manhattan Routing Architectures

In this chapter, we discuss the use of Non-Manhattan routing architectures to improve the efficiency of on-chip interconnects. We studied both the physical planning of the interconnect architectures and the design methodologies associated with the Y-architecture (3-directional routing).

### **II.A** Physical Planning of Interconnect Architectures

Interconnect architecture plays an important role in determining the throughput of meshed communication structures. We assume a mesh structure with uniform communication demand for communication. A multi-commodity flow (MCF) model is proposed to find the throughput for several different routing architectures. The experimental results reveal several trends: 1. The throughput is limited by the capacity of the middle row and column in the mesh, simply enlarging the congested channel cannot produce better throughput. A flexible chip shape provides around 30% throughput improvement over a square chip of equal area. 2. A 45-degree mesh allows 17% throughput improvement over 90-degree mesh and a 90-degree and 45-degree mixed mesh provides 30% throughput improvement. 3. To achieve maximum throughput on a mixed Manhattan and diagonal intercon-

nect architecture, the best ratio of the capacity for diagonal routing layers and the capacity for Manhattan routing layers is 5.6. 4.Incorporating a simplified via model, interleaving diagonal routing layers and Manhattan routing layer is the best way to organize the wiring directions on different layers.

### **II.A.1** Introduction

Mesh is a common routing architecture for many reconfigurable computing systems. Both conventional FPGAs[12] and recently proposed on-chip multiprocessors systems[7] [6] use mesh networks as communication backbones. With rapid technology scaling, wires become one most precious resource on a chip. Unreasonable distribution of wire resources will result in bottlenecks that stall the data flows, meanwhile leave other routing resources wasted. Simply enlarging the channel capacity of the whole array is by no means an effective solution.

Our goal is to allocate channel capacities in the mesh routing architecture to maximize its communication capability. The communication capability is measured by the throughput, the amount of information that every pair of nodes can exchange simultaneously. Throughput is a function of channel capacity and the dimension of the processor array.

Khalid and Betz investigated the channel allocation problems for FPGAs in [5] [2]. They applied placement and routing to benchmark circuits on FPGAs with different routing track distributions. They conclude that uneven track distribution do not improve the routability of FPGA interconnects.

Multi-commodity flow (MCF) is a natural way to model the communication network traffic. Many previous works used MCF in studying the wide area communication network traffic [10]. Due to the high computing complexity of MCF, most of these works [10] adopted heuristic methods to approximate the MCF solution.

Recent advance in MCF algorithm [4] allows us to compute MCF more efficiently. In this paper, we choose MCF to model communication traffic. We extend the MCF algorithm in [4] to solve various MCF problems. Solution of MCF finds the optimal throughput for a given routing architecture. In our MCF model, the routing demand is equal for every pair of nodes. Thus, the result is independent of test cases. Moreover, the result of MCF is independent of placement and routing.

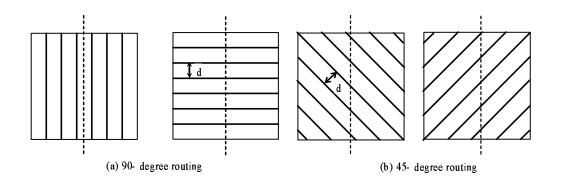

In [9], Mutsunori et al. demonstrated that on-chip diagonal routing is feasible based on state-of-the-art technologies. The progress of diagonal routing technology provides another opportunity to explore different arrangements of interconnect structure. We compare the throughput of three different mesh structures, the 90-degree mesh, the 45-degree mesh, and the 90-degree and 45-degree mixed mesh. Experimental results show that a 45-degree mesh can achieve better throughput than a 90-degree mesh. Moreover, 90-degree and 45-degree mixed mesh can further improve the throughput. Mixed 90-degree and 45-degree mesh allows more freedom on routing directions. We explore the allocation of routing resources and the arrangement of routing resources of routing directions between 90-degree and 45-degree wires. We propose a simplified via model to derive the optimal solution.

Our contributions include:

- We use MCF model to analyze the detailed communication traffic on mesh interconnect networks. We find the exact traffic bottlenecks of the network and the throughput of communications in the mesh structure. This provides a feasible upper bound of communication.

- We extend the flow approach [4] to compute the optimal routing resource allocation for mesh interconnect structures with reasonable sizes. The results reveal some basic trends of throughput related to the scale and structure of the communication mesh:

- For uniform capacity mesh, the congested edges lie in the center rows and columns. The total throughput of each node is inversely propor-

tional to the dimension of the mesh

- The re-arrangement of capacities between different columns or rows will not improve the throughput if we keep the total capacity of the columns or rows a constant.

- A flexible chip shape provides a throughput improvement of around 30% over a square chip of equal area.

- A 45-degree mesh structure produces a 17% more throughput than a 90-degree mesh for a processor array of 144 nodes.

- A mixture of 90-degree and 45-degree mesh structure can achieve even a 30% more throughput. To achieve maximum throughput, the ratio of resources allocated to the 45-degree routing layers verses those to the 90-degree routing layers approaches 5.6 as number of nodes increases.

- In the 90-degree and 45-degree mixed routing, interleaving the diagonal routing layer and Manhattan routing layers can reduce the number of vias and hence increase the communication throughput.

The rest of this paper is organized as follows: Section 2 presents the problem formulation in MCF model. Section 3 introduces six different interconnect structures we consider. Section 4 gives the experimental results and our observations. We draw conclusion in section 5.

### **II.A.2** Problem Formulation

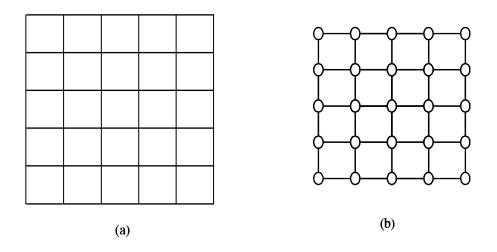

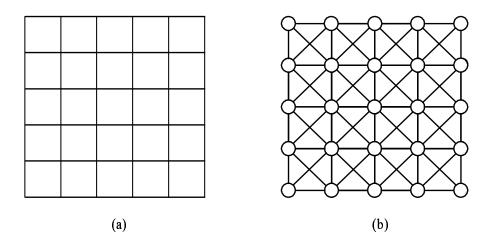

We decompose the communication resources into an array of n n slots. Each slot contains a communication terminal, say, a processor. The slots are aligned in rows and columns. The slot array forms a 90-degree mesh structure. Figure 1(a) illustrates an example of a 90-degree mesh structure with 25 slots. Each square tile represents a slot. The mesh structure can be mapped to a graph  $G = \{V, E\}$  according the following rules:

1. Each slot corresponds to a node in the graph.

Figure II.1: A 5 by 5 communication mesh and its graph representation

- 2. The adjacency between two slots is represented by an edge connecting two corresponding nodes.

- 3. The edge capacity is proportional to the length of the line segment separating the adjacent slots, and the number of routing layers.

Figure II.1(b) describes the graph corresponding to the mesh in Fig.II.1(a).

We assume a uniform communication requirement, *i.e.* every pair of nodes communicate with an equal demand. All communications happen at the same time. Note that the model can be extended to various communication demands, *e.g.*, Poisson distribution, Rents rule, *etc.*, depending on specific applications. In this paper, the uniform pairwise communication model is adopted because of its simplicity and genericalness. Moreover, the communication demand represents an unbiased symmetry, which makes the solution independent of the test cases, placement, and routing.

We define the throughput, z, to be the maximum amount of communication flow between every pair of nodes. We try to find the throughput using a multi-commodity flow model. The flow that starts from node i is deemed as commodity i. Commodity i starts from node i with the amount of  $z \cdot (N - 1)$ , where  $N = n^2$  is the number of nodes in the graph, to each of the rest nodes with the amount of z. We solve the multi-commodity flow problem to find the maximum value of z. We can use following linear program to express the above MCF problem:

$$Max: z$$

(II.1)

S.t. For each commodity v , on each node i

$$\sum_{j \in \text{neighbor of } i} (f_{ji}^v - f_{ij}^v) = a \tag{II.2}$$

for each edge (i, j) in the graph,  $\sum_{v=1}^{n^2} (f_{ji}^v - f_{ij}^v) \le c_i j$

In this linear program, flow variable  $f_{ij}^v$  represents the flow amount of commodity v on edge (i, j). The edge capacity  $c_{ij}$  represents the flow capacity of edge (i, j). We set that the flow injecting to a node is positive and the flow ejecting from a node is negative.

The linear program includes two sets of constraints. Constraint (1) describes the flow conservation of each commodity v at each node i. Constraint (2) denotes that the total amount of flow on each edge is no more than the capacity of that edge.

In subsections 3.3, 3.4 and 3.5, we allow edge capacity to be changed. Thus, the edge capacities become variables in the linear constraints. Thus, allows us to optimize the capacities under the area constraints.

In [4], a fast combinatorial  $(1+\epsilon)$ -approximation algorithm was introduced to solve the MCF problem. We extend the approach to incorporate edge capacities as variables.

According to the algorithm in [4], we adopt the primal-dual structure of the linear program. The algorithm assigns a nonnegative shadow cost [12] to each edge according to the congestion level on that edge. Initially, all the shadow costs are set to be equal. Then, the algorithm proceeds in iterations. In each iteration,

(II.3)

we reroute a fixed amount of flow along the shortest path for every commodity. At the end of each iteration, we adjust the capacity of every edge and its shadow cost according to the dual linear program.

In our model, we all fractional flows. Note that the throughput,  $Z_f$ , of the fractional flow model, is an upper bound of the throughput,  $Z_i$ , of the integer flow model [3]<sup>1</sup>. In [8], Motwani and Raghavan showed that by randomized rounding, with the probability of  $1-\epsilon$ , we can find  $Z_i$  approaches  $Z_f$  with inequality  $Z_f \geq Z_i/1 + \Delta^+(1/Z_f, \epsilon/2N)$ , where N is the number of nodes in the mesh,  $\epsilon$  is any real number between 0 and 1, and  $\Delta^+(1/Z_f, \epsilon/2N)$  is the value of *delta* such that  $[e^{\delta}/(1+\delta)^{(1+\delta)}]^{\frac{1}{2}} = \epsilon/2N$ .

### **II.A.3** Routing Architectures

We construct six routing architectures with different capacities and routing orientations. The first three structures are 90-degree meshes with different edge capacities. In the first architecture, every edge has a unit capacity. In the second architecture, edges on the same row or column have equal capacity. In the third architecture, edge capacities are flexible but the sum of the capacities of all the edges is fixed. The fourth architecture is a 45-degree mesh where interconnection goes in 45 degree. The fifth is a mixture of 90-degree and 45-degree mesh. And the last one is the mixed 90-degree and 45-degree mesh with different routing direction assignments.

### Uniform Edge Capacity

For the model of uniform edge capacity, All the edge capacity is set to a unit, i.e.  $c_{i,j} = 1$  for all edges (i, j) in the graph. This case is the basis of our experiments. We assume that the  $n \times n$  array of slots is evenly distributed in a square area.

<sup>&</sup>lt;sup>1</sup>For packet switching network in RAW and Smart Memories, we do not require the flow to be integer. For wire switching network in FPGAs, the flow amounts can be interpreted as the number of wires, which needs to be integers.

### Uniform row and column capacity

In the second structure for interconnection, edge capacities ce are set as variables. However, the capacities of edges in the same row are set to be equal. Likewise, the vertical capacities of edges in the same column are set to be equal. The sum of the vertical edge capacities in a row is set to be n, and the sum of the horizontal edge capacities in a column is also set to be n. In other words, we assume that the height and the width of the array remain to be n.

Let  $c_{Hi}$  be the capacity of horizontal edges in the *i*-th row, and  $c_{Vi}$  be the capacity of vertical edges in the *i*-th column. We add the 2n variables,  $c_{H1}, c_{H2}, \ldots, c_{Hn}, c_{V1}, c_{V2}, c_{Vn}$ , to the linear program. The height and width constraints of the array can be expressed as:

$\sum_{i=1}^{n} C_{Hi} = n$  and  $\sum_{i=1}^{n} C_{Vi} = n$ .

For this structure, we assume that we can adjust the row height and the column width of the array of processors.

#### Fixed total edge capacity

For the third structure we give the program more freedom to choose the best edge capacities. We require only that the total capacity of all edges to be a constant. This structure represents the best edge capacity we can allocate for a 90-degree mesh. The resultant throughput is an upper bound of a 90-degree mesh architecture.

We set the edge capacities,  $c_{ij}$ , as variables. The total capacity constraint is expressed as:  $\sum_{\text{for all edges } (i,j)} c_{ij} = 2(n^2 - n).$

Note that  $2(n^2 - n)$  is the number of edges in an n mesh.

For this structure, we assume that the area of each slot is flexible. We adjust the height and width of each individual slot so that the total area remains the same.

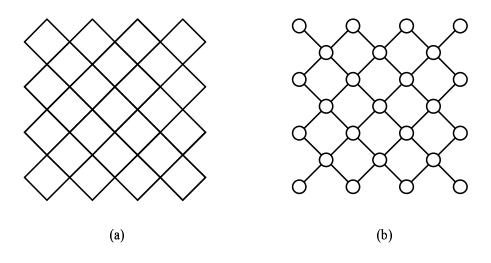

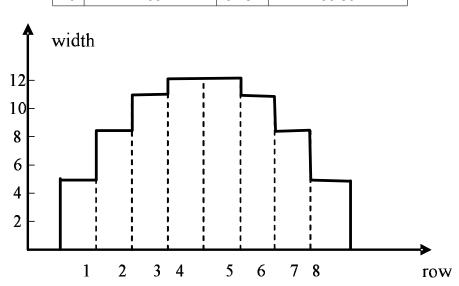

Figure II.2: Example of 45 degree mesh of n = 4

### 45-degree mesh

The fourth structure adopts a 45-degree mesh. All wires are oriented in 45 degree or 135 degree. The size of the mesh increases with n. For a 45-degree mesh of n, the number of nodes is  $n^2 + (n-1)^2$  and the number of edges is  $4(n-1)^2$ .

Figure II.2(a) shows an example of 45-degree mesh of n = 5. Figure II.2(b) illustrates the corresponding graph to the mesh. In this structure, we assume that the slots are shaped in diamonds (a square rotated by 45-degree) and are aligned in 45-degree and 135-degree directions. Thus, the edge capacity remains to be a unit, i.e.  $c_{ij} = 1$ .

### 90-degree and 45-degree mixed mesh

In the fifth structure, we add 45-degree channels to the 90-degree mesh. Figure II.3 illustrates an example of the mixed mesh for n = 5. Figure II.3(a) shows the slots arrangement. For an n by n mixed mesh, the number of nodes is  $n^2$  and the number of edges is  $2(n-1)^2 + 2(n^2 - n)$ .

In Figure II.3(b), the edges are oriented in 0, 90, 45 or 135-degree angle. All nodes are aligned in rows and columns. Thus the channels for 45- and 135degree wires are scaled by . In other words, for a pair of routing layers, if we can

Figure II.3: A 90-degree and 45-degree mixed mesh of n = 5

allocate a capacity of x to 0- and 90-degree edges, we can only allocate a capacity of  $x/\sqrt{2}$  to 45- and 135- edges. Let  $c_1$  be the capacity of horizontal and vertical edges,  $c_2$  be the capacity of diagonal edges. The area constraints can be expressed as  $c_1 + \sqrt{2}c_2 = 1$ . Thus, the total area is equal to the area of uniform structure.

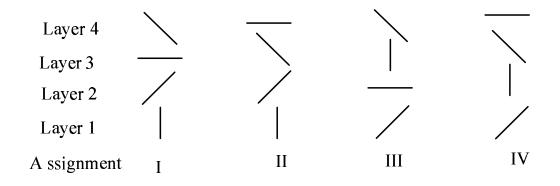

### **Routing direction Assignment**

Vias become an important concern when number of routing layers increases. In [1] a global routing graph with via edges is used to model the multiplayer routing. In that model vias are not considered as routing blockages.

We propose a network flow model shown in Fig. II.4 to take vias into. Our basic assumption is that each via will block one routing track. For each slot, we set an upper bound on the total number of vias and wires across the node.

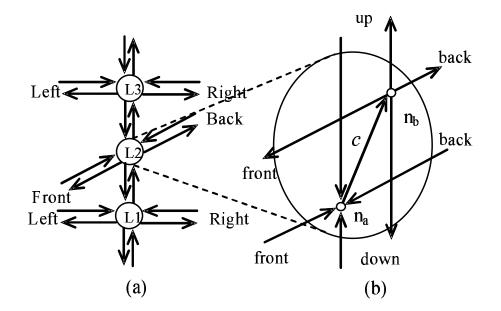

Suppose there are k routing layers. Each slot is now represented by k routing cells (Fig. II.4(a)). Each routing cell consists of two nodes (Fig. II.4(b)):  $n_a$  and  $n_b$ . Node  $n_a$  takes all the incoming edges from the neighboring routing cells, and node  $n_b$  ejects edges to neighboring routing cells. An edge with capacity c direct from node  $n_a$  to node  $n_b$ . This edge is used to restrict the total number of vias and wires crossing the routing cell. Using this flow model, we compare the

Figure II.4: A network flow model for multiplayer routing

communication throughput with different routing layer assignments.

#### **II.A.4** Experimental Results

We first use Matlab's linear program package on a Sun Ultra10 workstation to compute MCF solutions. For the case with 100 nodes, the run time exceeds 24 hours. We then implement the MCF algorithm [4] using C programming language. The MCF algorithm derives the MCF solutions for cases with up to 319 nodes within 12 hours.

#### Results for uniform edge capacity mesh

Table II.1 describes the results of uniform edge capacity meshes with n = 2 to 10. We list the number of nodes and the throughput z.

From the experimental result, we have the following observations:

- 1. The throughput is 1/n when n is odd and  $(n^2 1)/n^3$  when n is even.

- 2. The throughput is limited by edges on the middle column and row. When n

| n  | Number of nodes | Z      |

|----|-----------------|--------|

| 2  | 4               | 0.3750 |

| 3  | 9               | 0.3333 |

| 4  | 16              | 0.2343 |

| 5  | 25              | 0.2000 |

| 6  | 36              | 0.1620 |

| 7  | 49              | 0.1429 |

| 8  | 64              | 0.1229 |

| 9  | 81              | 0.1111 |

| 10 | 100             | 0.0990 |

Table II.1: Results of uniform edge capacity mesh

Figure II.5: Flow congestion for uniform edge capacities

is an even number, edges in the central row and column form the bottleneck of the flow. When n is an odd number, the two columns and two rows form the bottleneck.

Figure II.5 shows the bottleneck of communication flow for n = 4 and 5. The congested edges are marked with bold lines. Note that the bottleneck form the horizontal and vertical cut sets. The cut lines are shown with dashed lines.

#### Results of uniform row and column capacity mesh

For equal n, the throughput of a 90-degree mesh with uniform row and column capacities is exactly the same as that of the 90-degree mesh with fixed edge

| 10 | tole 11.2. Results of | inxeu to | tai euge capacities |

|----|-----------------------|----------|---------------------|

| n  | Number of nodes       | z        | improvement on $z$  |

| 2  | 4                     | 0.375    | 0.00                |

| 3  | 9                     | 0.333    | 0.00                |

| 4  | 16                    | 0.281    | 20.01               |

| 5  | 25                    | 0.240    | 20.00               |

| 6  | 36                    | 0.208    | 28.57               |

| 7  | 49                    | 0.185    | 28.56               |

| 8  | 64                    | 0.169    | 33.32               |

| 9  | 81                    | 0.148    | 33.35               |

| 10 | 100                   | 0.134    | 36.36               |

Table II.2: Results of fixed total edge capacities

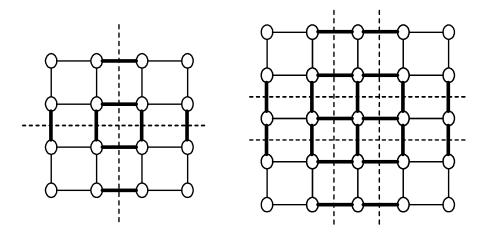

Figure II.6: Optimal row width of 9 by 9 mesh to maximize total throughput

capacities. We obtain no throughput improvement because the total capacity of the edges in each column and row is fixed.

#### Results for fixed total edge capacities mesh

For n = 2 to 10, Table II.2 shows the results of 90-degree mesh with fixed total edge capacities. The fourth column provides the throughput improvement compared to that of 90-degree mesh with uniform edge capacity. As we no longer limit the total capacity of each row or column, the average throughput improves 29.7% for n = 4 to 10.

| (Row—Col) | 1    | 2    | 3    | 4    | 5    | 6    | Sum  |

|-----------|------|------|------|------|------|------|------|

| 1         | 0.60 | 0.74 | 0.79 | 0.79 | 0.74 | 0.61 | 4.28 |

| 2         | 0.95 | 1.19 | 1.27 | 1.28 | 1.19 | 0.96 | 6.85 |

| 3         | 1.07 | 1.34 | 1.44 | 1.44 | 1.34 | 1.07 | 7.71 |

| 4         | 0.95 | 1.19 | 1.27 | 1.27 | 1.19 | 0.96 | 6.85 |

| 5         | 0.60 | 0.74 | 0.79 | 0.79 | 0.74 | 0.60 | 4.28 |

Table II.3: Optimal capacities for vertical edges in 6 by 6 mesh

The results also show that all edges are congested. The optimal edge capacity is no longer uniform. The capacity is larger for the edges in the middle row and column. Table II.3 shows the optimal edge capacities for all the vertical edges in a 6 by 6 mesh. We list the sum of all the capacities of each row. Figure II.6 illustrates the optimal sums of the rows in a 9 by 9 mesh. Note that there are eight rows of vertical edges in a 9 by 9 mesh. The chip area is no longer a square, but a convex area as is shown in Figure II.6.

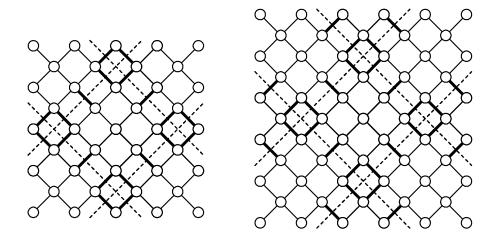

#### Results for 45-degree mesh

Table II.4 shows the results of 45-degree mesh for n = 2 to 12. To compare the results in table 4 and table 1, we use the cases with almost the same number of nodes. For instance, both the case of n = 4 in table 4 and the case of n = 5 in table 1 contain 25 nodes. The case with 45-degree mesh achieves the throughput of 0.209, which gains a 4.18 percent improvement. Also we compare the case of n = 7 in table 5 with the case of n = 9 in table 1. The case in table 5 contains 85 nodes, which has 4 more nodes than the case in table 1. The throughput of the 45-degree mesh case is 0.1260, which is 13.16% more than that of the 90-degree mesh case.

The congested edges also present a different pattern: they form 4 cut sets at four corners. Figure II.7 shows the flow congestion in 45-degree mesh for n = 5 and n = 6. The congested edges are in bold lines and the cut lines are in dashed lines.

Fig.II.8 explains why 45-degree routing is better than 90-degree routing.

|    |                 | 0      |

|----|-----------------|--------|

| n  | Number of nodes | z      |

| 2  | 5               | 0.250  |

| 3  | 13              | 0.250  |

| 4  | 25              | 0.209  |

| 5  | 41              | 0.174  |

| 6  | 61              | 0.147  |

| 7  | 85              | 0.126  |

| 8  | 113             | 0.106  |

| 9  | 145             | 0.101  |

| 10 | 181             | 0.0828 |

| 11 | 221             | 0.0759 |

| 12 | 265             | 0.0673 |

|    |                 |        |

Table II.4: Results of 45-degree mesh

Figure II.7: Flow congestion in 45-degree mesh

Assume that we have a square shaped chip with two routing layers. Figure II.8(a) illustrates the case of 90-degree routing and Fig. 8(b) depicts the case of 45-degree routing. We draw a cut line for the horizontal congested edges in dashed lines in Figure II.8(a). Only the wires on the horizontal routing layer could cross the cut line and the number of wires across the cut line is d/D, where d is the wire pitch and D is the dimension of the chip. We then draw a similar cut line on Fig.II.8 (b). The number of edges across the cut line in each layer is  $d/\sqrt{2}D$ . The total number of wires crossing the cut line for the two layers in Fig. II.8(b) is  $\sqrt{2}d/D$ . Thus the upper bound of throughput increase to  $\sqrt{2} = 1.414$ . However, the

Figure II.8: Explanation of throughput increase for a 45-degree mesh

throughput is now limited by the cut edges at four corners.

#### Results for 90-degree and 45-degree mixed mesh