# UCLA UCLA Electronic Theses and Dissertations

## Title

Raising an Abstraction Level of Compilation and Optimization for Customized Computing

**Permalink** https://escholarship.org/uc/item/2g1726gw

Author

Yu, Hao

Publication Date 2019

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA

Los Angeles

Raising an Abstraction Level of Compilation and Optimization for Customized Computing

> A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Computer Science

> > by

Hao Yu

2019

© Copyright by Hao Yu 2019

#### ABSTRACT OF THE DISSERTATION

Raising an Abstraction Level of Compilation and Optimization for Customized Computing

by

Hao Yu

Doctor of Philosophy in Computer Science University of California, Los Angeles, 2019 Professor Jingsheng Jason Cong, Chair

The demand for scalable, high-performance computing has increased as the size of datasets has grown in recent years. However, the breakdown of Dennard's scaling [DGR74] has led to energy efficiency becoming an important concern in datacenters, and spawned exploration into using power-efficient processors such as GPUs (Graphic Processing Units) and FPGAs (Field-Programmable Gate Arrays) as accelerators in datacenters. In particular, the FPGA's low power consumption and the re-programmability allow datacenters to use FPGAs as highly energy-efficient accelerators for a variety of application. On the other hand, FPGA has poor programmability compared to instructions-based architectures like CPU and GPU. To facilitate the process of implementing and deploying FPGA accelerators, High-Level Synthesis (HLS) [CLN11] that generates functional-equivalent RTL from C-based programming languages attracts more and more attention since past decades. Nowadays, both FPGA vendors have their commercial HLS products – Xilinx SDx [SDX] and Intel FPGA SDK for OpenCL [INT]. However, modern HLS is still not friendly for software designers who have limited FPGA domain knowledge. Since the hardware architecture inferred from a syntactic C implementation could be ambiguous, current commercial HLS tools usually generate architecture structures according to specific HLS C code patterns. As a result, even though the authors in [CLN11] have illustrated that the HLS tool is capable of generating FPGA designs with competitive performance as the one in RTL, designers must manually reconstruct the HLS C kernel with specific code patterns to achieve high performance. This problem becomes one of the main impediments to consolidating the FPGA community on cooperation and developments.

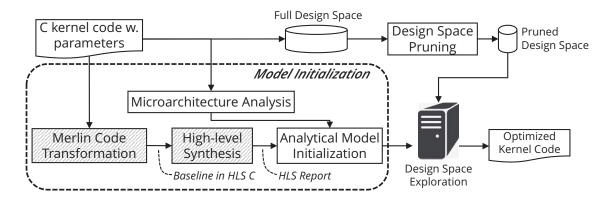

In this dissertation, we first present an automated framework that frees human efforts from code reconstruction and design space exploration (DSE). The framework creates a more comprehensive micro-architecture design space from user-written C-based kernel with the Merlin compiler [CHP16a], so the design point should cover the design point with better performance when compared to the HLS-pragma-based design space. To efficiently identify the best design configuration in the tremendous design space, we first propose efficient design space pruning processes that reduce the design space by  $24.65 \times$ . Accordingly, we develop and evaluate several approaches, including multi-armed bandit hyper heuristic approach, gradient-based approach, and design bottleneck optimization approach. The evaluation result shows that our DSE framework is able to identify the design point that achieves on average (using geometric mean) 93.78% QoR compared to the corresponding manual design.

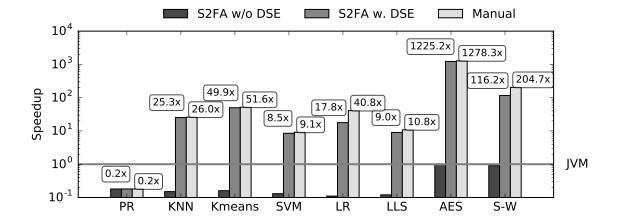

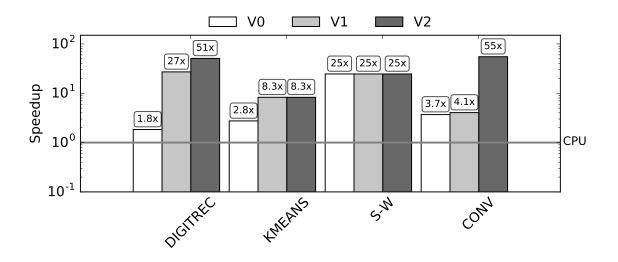

Based on the proposed DSE framework, we further support automated design optimization for high level domain specific languages (DSLs). Since DSLs might not explicitly provide interfaces for users to specify design configurations, automatic DSE becomes even more important when supporting DSLs for FPGAs. Specifically, we adopt Merlin C [CHP16a], an OpenMP-like [OMP] C-based programming model, as the intermediate representation (IR) and implement DSL-to-Merlin frontend compilers while preserving the semantic and domain-specific information such as parallel patterns, systolic patterns, and scheduling functions. We first implement Spark-to-Merlin front-end compiler that translates Spark applications in Scala to Merlin C for FPGA acceleration. By leveraging parallel patterns as scheduling hints, the generated accelerators are able to achieve  $50 \times$  speedup on geometric mean for a set of machine learning kernels. In addition, we also demonstrate that our DSE framework can be even more practical for the DSLs with plenty scheduling functions. Specifically, we implement HeteroCL-to-Merlin front-end that takes HeteroCL [LCH19] programming model embedded in Python. Our DSE framework is capable of exploring a subset of HeteroCL scheduling primitives and let users focus on the platform independent loop transformations. With the help from the DSE framework, we achieve  $27.62 \times$  speedup on geometric mean over a CPU core for a variety of compute-intensive kernels (chapter 3).

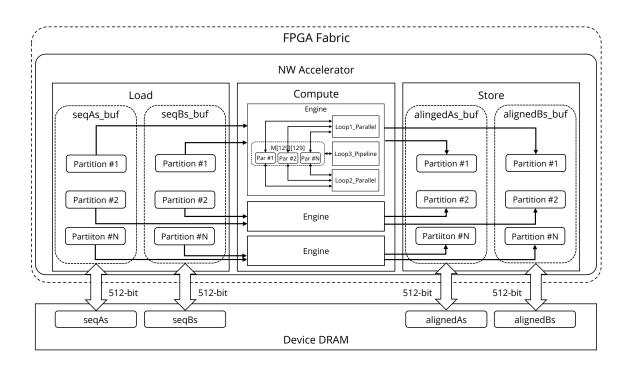

On the other hand, a main challenge of performing design space exploration for a design with arbitrary functionality is the lack of the assumption to underlying micro-architectures. As we will illustrate in the dissertation, the cost of evaluating the quality of a design point is extremely expensive (15-60 minutes) so only a limited number of design points can be explored. In addition, due to the uncertainty of vendor tool behaviors, the development of performance and resource modeling is also unrealistic. As a result, we propose composable, parallel and pipeline (CPP) architecture template to limit the design space to a certain region that is more practical and has less exceptions (chapter 4). With the CPP architecture, we are able to derive an incremental analytical model, which only requires a few HLS run to be initialized, to facilitate the DSE process. In the last part of this dissertation, we use convolutional neural network (CNN) to demonstrate that the HLS runtime cost can be totally saved with the use of a more domain specific architecture (chapter 5). Specifically, we leverage a systolic array architecture template for CNN accelerator generation. By mapping a CNN model to the pre-defined systolic array template, we can guarantee the model accuracy and DSE efficiency. The experimental result shows that our analytical model for the architecture template achieves 96% accuracy, and the mapped CNN model achieves up to 1.2 Tops throughput on an Intel Arria 10 FPGA.

The dissertation of Hao Yu is approved.

Glenn D. Reinman

Jens Palsberg

Quanquan Gu

Jingsheng Jason Cong, Committee Chair

University of California, Los Angeles

2019

To my family and fiancée.

### TABLE OF CONTENTS

| 1        | Intr | roduct | ion                                          | 1  |

|----------|------|--------|----------------------------------------------|----|

| <b>2</b> | Bac  | kgrou  | $\mathbf{nd}$                                | 11 |

|          | 2.1  | FPGA   | A and High-Level Synthesis C/C++             | 11 |

|          | 2.2  | Merlir | 1 Compiler                                   | 14 |

|          | 2.3  | Relate | ed Work                                      | 17 |

|          |      | 2.3.1  | Automated DSE Framework for Hardware Designs | 17 |

|          |      | 2.3.2  | Domain Specific Frameworks for FPGAs         | 20 |

| 3        | An   | Auton  | nated Design Optimization Framework          | 22 |

|          | 3.1  | Overv  | iew                                          | 22 |

|          | 3.2  | Versio | n 1: An Initial Framework                    | 25 |

|          |      | 3.2.1  | Framework Overview                           | 25 |

|          |      | 3.2.2  | Design Space Identification                  | 27 |

|          |      | 3.2.3  | Meta-Heuristic Optimization Methods          | 29 |

|          |      | 3.2.4  | Experimental Results                         | 33 |

|          |      | 3.2.5  | Insights and Summary                         | 40 |

|          | 3.3  | Versio | on 2: Framework Optimization                 | 40 |

|          |      | 3.3.1  | Framework Overview                           | 41 |

|          |      | 3.3.2  | Design Space Partition                       | 42 |

|   |      | 3.3.3    | Seed Generation                                  | 44 |

|---|------|----------|--------------------------------------------------|----|

|   |      | 3.3.4    | Early Stopping Criteria                          | 45 |

|   |      | 3.3.5    | Experimental Results                             | 47 |

|   |      | 3.3.6    | Insights and Summary                             | 49 |

|   | 3.4  | Versic   | n 3: Stability Optimization                      | 51 |

|   |      | 3.4.1    | Gradient Descent with Finite Difference Method   | 52 |

|   |      | 3.4.2    | Graph-based Design Space Pruning                 | 54 |

|   |      | 3.4.3    | Design Space Partition                           | 56 |

|   |      | 3.4.4    | Adaptive Line Search                             | 57 |

|   |      | 3.4.5    | Multiscale V-Cycles                              | 58 |

|   |      | 3.4.6    | Putting It All Together                          | 60 |

|   |      | 3.4.7    | Experimental Results                             | 63 |

|   |      | 3.4.8    | Insights and Summary                             | 69 |

|   | 3.5  | Versio   | n 4: Scalability Optimization                    | 70 |

|   |      | 3.5.1    | Comprehensive Design Space Representation        | 70 |

|   |      | 3.5.2    | Performance Bottleneck Analysis                  | 73 |

|   |      | 3.5.3    | Bottleneck Optimization Approach                 | 76 |

|   |      | 3.5.4    | Experimental Results                             | 80 |

|   |      | 3.5.5    | Experimental Results on a Different Platform     | 85 |

|   | 3.6  | Concl    | usion                                            | 90 |

| 4 | Bai  | sing D   | esign Abstraction for Domain Specific Frameworks | 92 |

| - | Four | ~····5 D | sign restruction for Domain Specific Humeworks   |    |

|   | 4.1 | S2FA:    | A Spark-to-FPGA Accelerator Framework                    |

|---|-----|----------|----------------------------------------------------------|

|   |     | 4.1.1    | Overview                                                 |

|   |     | 4.1.2    | Preliminary: Blaze Runtime System                        |

|   |     | 4.1.3    | S2FA Framework                                           |

|   |     | 4.1.4    | Class/Object Transformation                              |

|   |     | 4.1.5    | Experimental Evaluation                                  |

|   | 4.2 | A Sen    | ni-Automatic DSE Support to HeteroCL                     |

|   |     | 4.2.1    | Overview                                                 |

|   |     | 4.2.2    | Preliminary: HeteroCL                                    |

|   |     | 4.2.3    | Semi-Automated Design Space Exploration                  |

|   |     | 4.2.4    | Experimental Evaluation                                  |

|   | 4.3 | Concl    | usion $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $124$ |

| 5 | Des | ign Sn   | ace Exploration with Architecture Templates 126          |

|   | 5.1 | <b>·</b> | iew                                                      |

|   | 5.2 |          | Accelerator Design Template                              |

|   |     | 5.2.1    | Problem Formulation                                      |

|   |     | 5.2.2    | CPP Micro-architecture                                   |

|   |     | 5.2.3    | Design Space Analysis                                    |

|   | 5.3 | Analy    | tical Models                                             |

|   | -   | 5.3.1    | Performance Modeling                                     |

|   |     | 5.3.2    | Resource Modeling                                        |

|   |     |          |                                                          |

|   | 5.4 | Design Space Exploration                                                                                                       | 38 |

|---|-----|--------------------------------------------------------------------------------------------------------------------------------|----|

|   | 5.5 | Evaluation Results                                                                                                             | 10 |

|   |     | 5.5.1 The Framework                                                                                                            | 11 |

|   |     | 5.5.2 Experimental Setup                                                                                                       | 11 |

|   |     | 5.5.3 Evaluation Results                                                                                                       | 12 |

|   | 5.6 | $Conclusion \dots \dots$ | 14 |

| 6 | Des | gn Optimization for Systolic Array Template                                                                                    | 6  |

|   | 6.1 | <b>Overview</b>                                                                                                                | 16 |

|   | 6.2 | Systolic Array Architecture                                                                                                    | 19 |

|   | 6.3 | Challenges                                                                                                                     | 52 |

|   | 6.4 | Analytical Models                                                                                                              | 55 |

|   |     | 6.4.1 Architecture Abstraction                                                                                                 | 55 |

|   |     | 6.4.2 Feasible Mapping to Systolic Array                                                                                       | 57 |

|   |     | 6.4.3 Resource Utilization Modeling                                                                                            | 59 |

|   |     | 6.4.4 Performance Modeling                                                                                                     | 30 |

|   |     | 6.4.5 Putting It All Together                                                                                                  | 31 |

|   | 6.5 | Design Space Exploration                                                                                                       | 32 |

|   | 6.6 | Implementation and Experiments                                                                                                 | 34 |

|   |     | 6.6.1 An Automation Flow                                                                                                       | 34 |

|   |     | 6.6.2 Experimental Setup                                                                                                       | 36 |

|   |     | 6.6.3 Results and Analysis                                                                                                     | 36 |

|   | 6.7 Conclusion | <br> | <br>• | <br> | • | • | <br>• | 171 |

|---|----------------|------|-------|------|---|---|-------|-----|

| 7 | 7 Conclusion   | <br> |       | <br> |   |   | <br>• | 172 |

| R | References     | <br> | <br>• | <br> |   |   | <br>  | 174 |

### LIST OF FIGURES

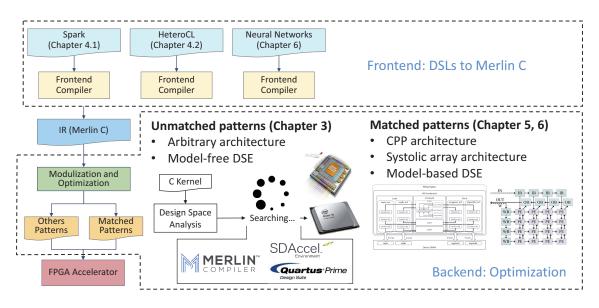

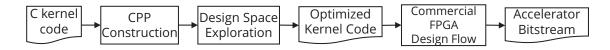

| 1.1  | The Proposed Framework                                                    | 8  |

|------|---------------------------------------------------------------------------|----|

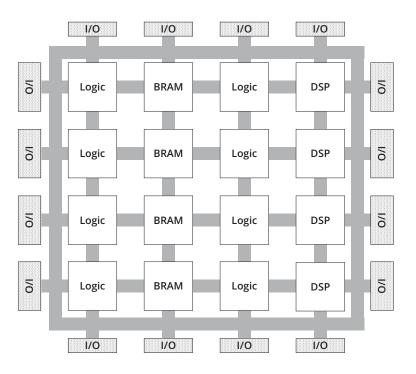

| 2.1  | A Common FPGA Architecture                                                | 12 |

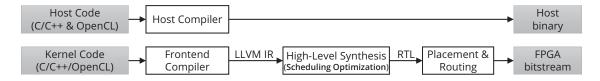

| 2.2  | Commercial HLS Tool Design Flow                                           | 13 |

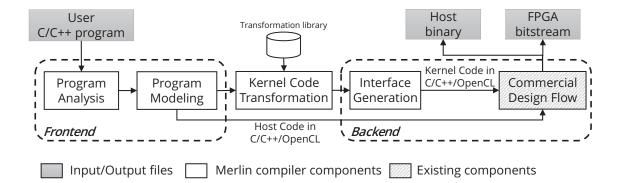

| 2.3  | The Merlin Compiler Execution Flow                                        | 15 |

| 3.1  | HLS Cycles of N-W with Different Factors on Loops                         | 23 |

| 3.2  | The Framework based on OpenTuner [AKV14]                                  | 27 |

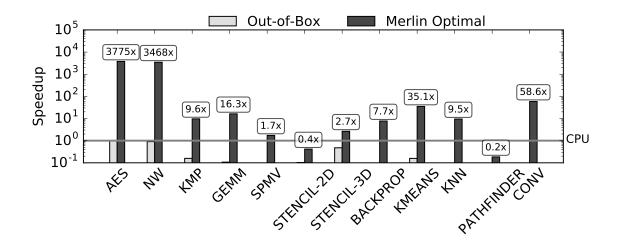

| 3.3  | Benchmark Speedup with Manual Merlin Pragma Optimization. Note            |    |

|      | that the Out-of-Box performance of some cases may be too poor to be       |    |

|      | visualized                                                                | 35 |

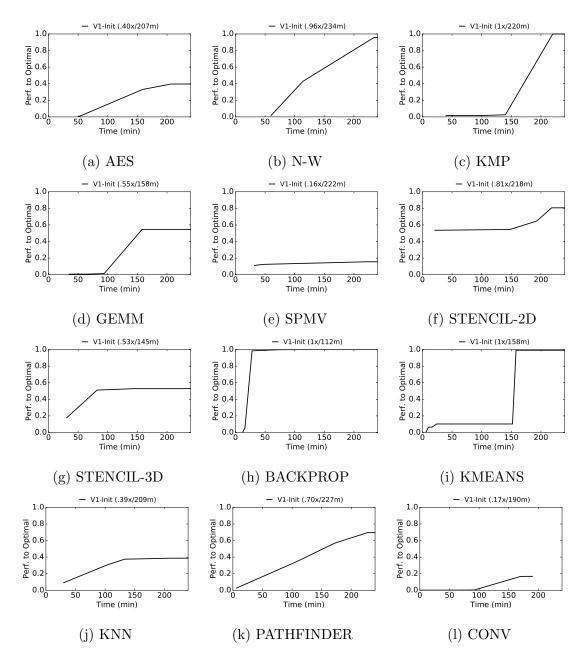

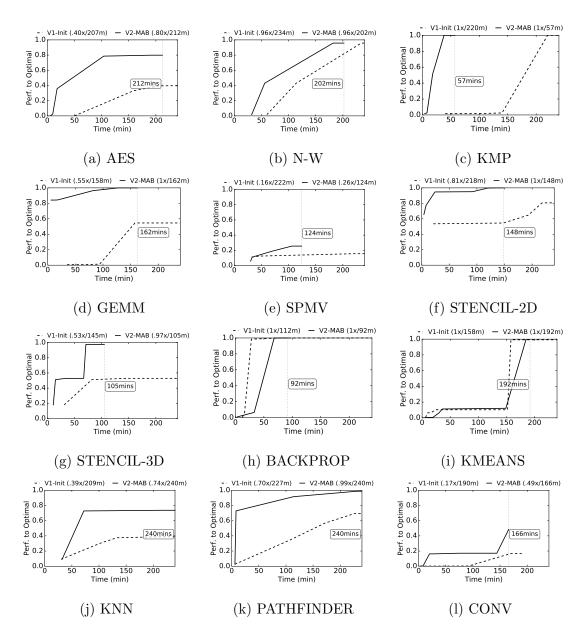

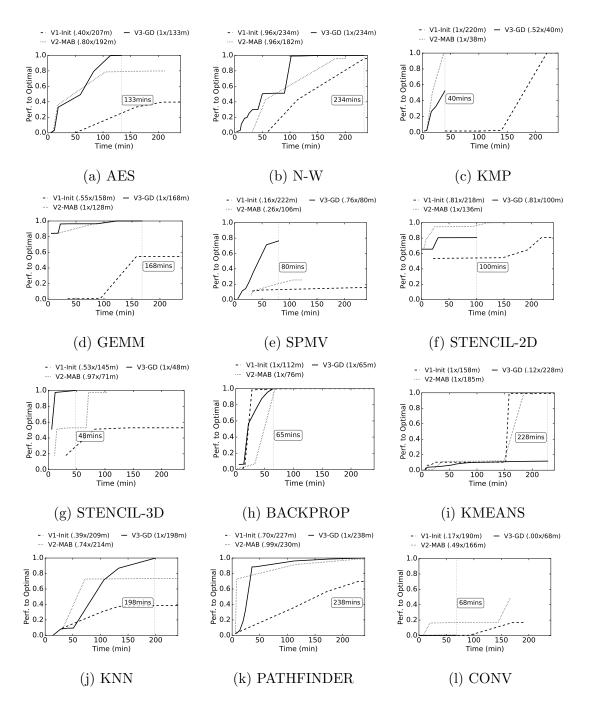

| 3.4  | Design Space Exploration with OpenTuner [AKV14]. The legend notes         |    |

|      | the best speedup over the manual design and the time to achieve it        | 39 |

| 3.5  | The Improved Parallel Exploration Framework                               | 42 |

| 3.6  | Design Space Exploration of the Improved Framework. The legend notes      |    |

|      | the best speedup over the manual design and the time to achieve it        | 50 |

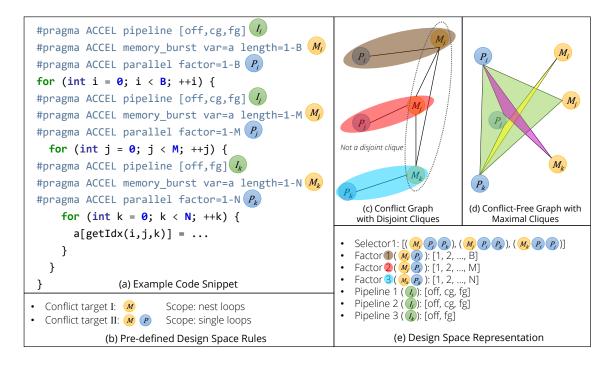

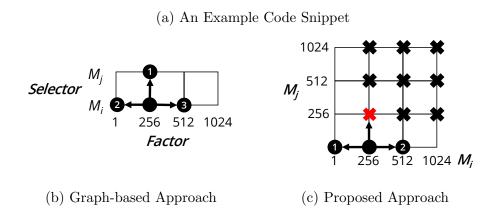

| 3.7  | Graph-based Design Space Building Approach                                | 55 |

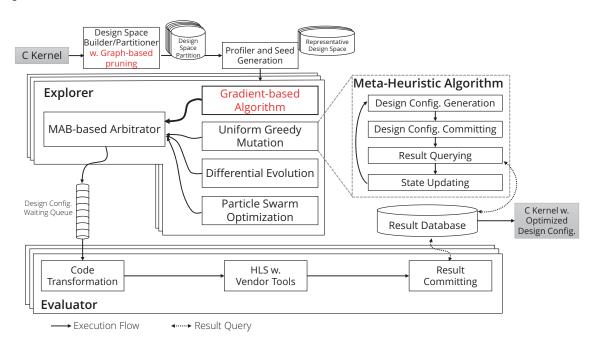

| 3.8  | The Framework with Gradient-based Approach                                | 62 |

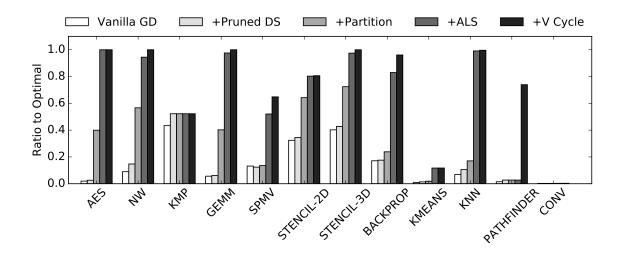

| 3.9  | Step-by-Step Performance Improvement with Gradient Approach               | 64 |

| 3.10 | Design Space Exploration with Gradient-based Algorithm. The legend        |    |

|      | notes the best speedup over the manual design and the time to achieve it. | 68 |

| 3.11 | Different Design Space Representations and Their Impact on DSE        | 71  |

|------|-----------------------------------------------------------------------|-----|

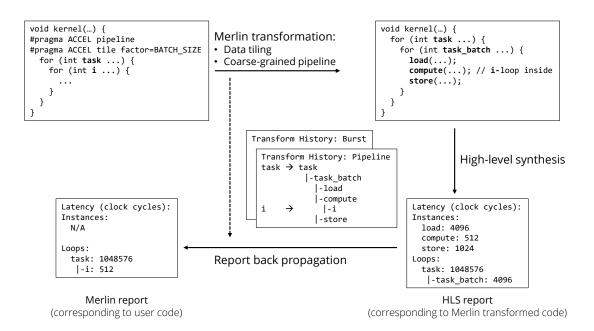

| 3.12 | Merlin Compiler Report Generation                                     | 73  |

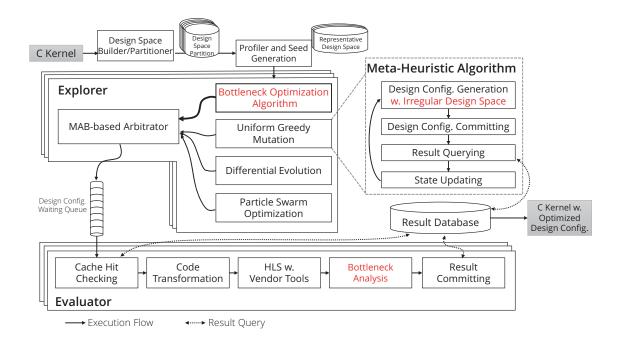

| 3.13 | The Framework with Hotspot Optimization Approach                      | 79  |

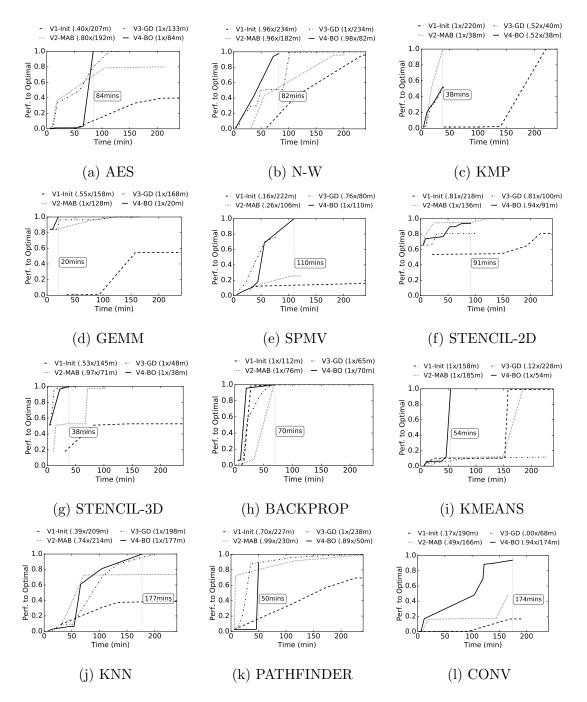

| 3.14 | DSE with Bottleneck Optimization Algorithm. The legend notes the best |     |

|      | speedup over the manual design and the time to achieve it             | 84  |

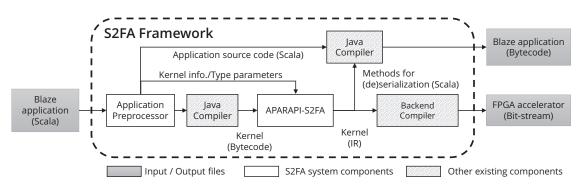

| 4.1  | Framework Overview                                                    | 102 |

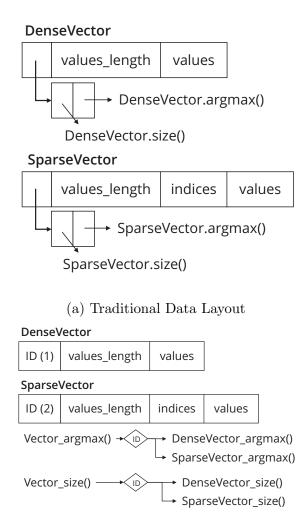

| 4.2  | Data Layouts for Class Serialization                                  | 109 |

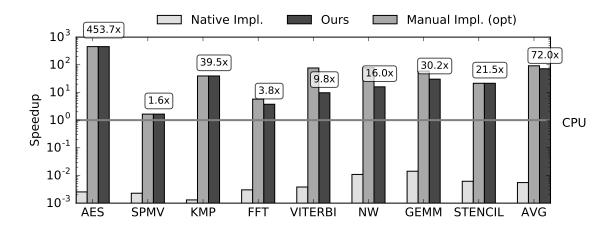

| 4.3  | Speedup of S2FA Designs over JVMs                                     | 114 |

| 4.4  | Overall Performance Comparison with CPU Baseline                      | 123 |

| 5.1  | N-W Accelerator under CPP Micro-architecture                          | 130 |

| 5.2  | Design Space Exploration Flow                                         | 138 |

| 5.3  | Framework Overview                                                    | 141 |

| 5.4  | Speedup over an Intel Xeon CPU Core                                   | 144 |

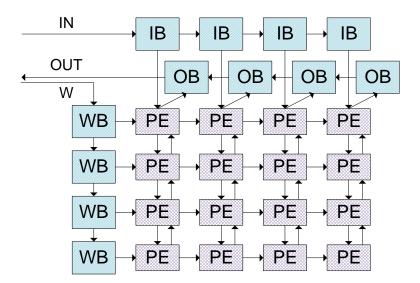

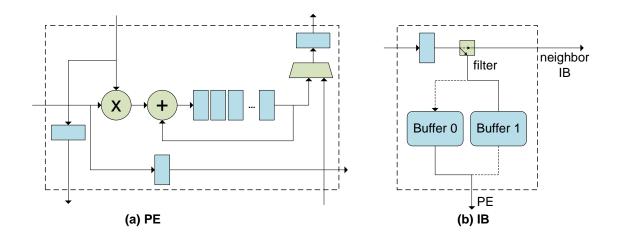

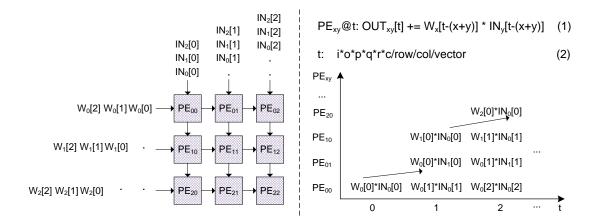

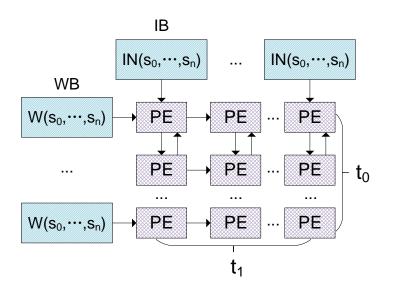

| 6.1  | Systolic Array Architecture                                           | 149 |

| 6.2  | Structure of PE and Input Buffer (IB)                                 | 150 |

| 6.3  | Cycle-Level Schedule of Systolic Array                                | 151 |

| 6.4  | The Mapped Systolic Array Architecture                                | 156 |

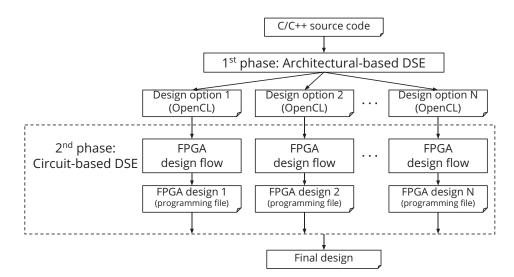

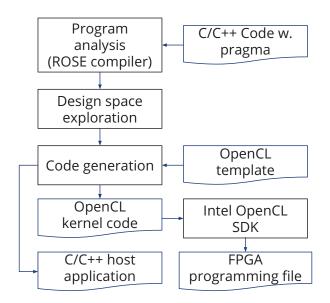

| 6.5  | Two-Phase Design Space Exploration                                    | 163 |

| 6.6  | The Execution flow                                                    | 165 |

| 6.7  | Pruned Design Space for AlexNet Layer 5                               | 167 |

### LIST OF TABLES

| 1.1  | Analysis of Poor Performance in Code 1.1                                                                                                | 7  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1  | Merlin Pragmas with Architecture Structures                                                                                             | 15 |

| 3.1  | Merlin Pragma Formed Design Space                                                                                                       | 28 |

| 3.2  | Benchmark Description and Lines-of-Code (LOC)                                                                                           | 34 |

| 3.3  | Overall Comparison to CPU and Manual Designs and the Dominated<br>Heuristic (GM: Greedy Mutation, EV: Differential Evolution, PSO: Par- |    |

|      | ticle Swarm Optimization.)                                                                                                              | 36 |

| 3.4  | FPGA Resource Utilization                                                                                                               | 38 |

| 3.5  | Overall Comparison to CPU and Manual Designs                                                                                            | 48 |

| 3.6  | FPGA Resource Utilization                                                                                                               | 49 |

| 3.7  | Overall Comparison to CPU and Manual Designs                                                                                            | 65 |

| 3.8  | FPGA Resource Utilization                                                                                                               | 66 |

| 3.9  | Overall Comparison to CPU and Manual Designs                                                                                            | 81 |

| 3.10 | FPGA Resource Utilization                                                                                                               | 82 |

| 3.11 | Overall Comparison to CPU and Manual Designs on Intel FPGA                                                                              | 86 |

| 3.12 | FPGA Resource Utilization                                                                                                               | 87 |

| 3.13 | Best Design Point on Xilinx FPGA                                                                                                        | 88 |

| 3.14 | Best Design Point on Intel FPGA                                                                                                         | 89 |

| 4.1 | 1 Development Time of FPGA Accelerators from Scala and Speedup Com-  |     |  |  |  |

|-----|----------------------------------------------------------------------|-----|--|--|--|

|     | parison with One Spark Executor                                      | 94  |  |  |  |

| 4.2 | Big Data Frameworks with Code Generation for Heterogeneous Platforms | 97  |  |  |  |

| 4.3 | Programmability Summary of the Heterogeneous Frameworks              | 98  |  |  |  |

| 4.4 | Scala Application I/O Types for the Experiments                      | 112 |  |  |  |

| 4.5 | Resource Utilization (%) and Clock Frequency (MHz)                   | 114 |  |  |  |

| 4.6 | HeteroCL Scheduling Primitives                                       | 119 |  |  |  |

| 4.7 | Step-by-Step Loop Transformation Application                         | 122 |  |  |  |

| 5.1 | Configuration of Hardware and Software                               | 142 |  |  |  |

| 5.2 | Error Rates Between Model and On-board Results                       | 143 |  |  |  |

| 6.1 | Impact of Systolic Array Shape to Performance                        | 154 |  |  |  |

| 6.2 | Frequency and Resource Utilization                                   | 168 |  |  |  |

| 6.3 | Results of AlexNet                                                   | 169 |  |  |  |

| 6.4 | Results of VGG                                                       | 169 |  |  |  |

| 6.5 | Comparison to State-of-the-art Implementations                       | 170 |  |  |  |

#### ACKNOWLEDGMENTS

Pursing a Ph.D. degree has always been my dream and I feel fortunate that I could make it happen. I would like to first express my sincerest gratitude to my advisor, Professor Jason Cong, for his trust, constant support, professional advice, and guidance during my Ph.D. life at UCLA. As a new Ph.D. student with computer-aided design background but not high-level synthesis and FPGAs, Professor Cong guides me into this field. More importantly, the way to systematically address research problems I learned from Professor Cong levels up my research capability and would be one of the most valuable things I got during my research life at UCLA. It is my great honor to have Professor Cong as my advisor.

I wish to express my appreciation to my doctoral committee members, Professor Tyson Condie, Professor Quanquan Gu, Professor Jens Palsberg, Professor Glenn Reinman, for their interest, patient, and advise to improve the quality of this dissertation. I especially wish to thank Professor Palsberg for his inspiration to the Spark to FPGA compilation framework.

I wish to thank the staffs at UCLA that help me a lot during this time. Thanks Alexandra Loung for her help on various paper works and service. Thanks Janice Martin-Wheeler for her help on editing the language of my papers. I cannot imagine what my Ph.D life would be without your helps.

I wish to thank to many of my colleagues for their supports and collaborations. I would like to thank Yu-Ting Chen for his recommendation to this research group and his guidance to research, career, and life experience. Thanks Peng Wei for our collaborations that became a role model to other members in the group. The collaborated work such as CPP architecture contributes a part of this dissertation. Thanks also go to Di Wu, Muhuan Huang, Peipei Zhou, Po-Tsang Huang, Max Grossman (Rice University), and Sean Lai (Cornell University) for their collaborations; Hui Huang, Bingjun Xiao, Young-Kyu Choi, Yuchen Hao, Zhenman Fang, Chen Zhang for technical discussions and shared experiences; Yuze Chi and Jie Wang for being not only co-workers together for a project but also great gossiping partners and roommates; Zhe Chen, Weikang Qiao, Zhenyuan Ruan, Tong He, Licheng Guo, Jason Lau, Karl Marrett, Atefeh Sohrabizadeh for being great lab mates.

In addition, most research in this dissertation are done when I was an intern at Falcon Computing Solutions, so I would also like to express my gratitude to all the sponsors and partners at Falcon, especially to Peng Zhang, Xuechao Wei, Han Hu and Youxiang Chen, and Yuxin Wang for their supports.

Finally, I would like to quote a speech (with some adaptions) given by Dr. Sheldon Copper from the very last episode of my favorite TV series, The Big Bang Theory, which also coincidentally finishes its journey in May 2019: "I was under a misapprehension that my accomplishments were mine alone, but nothing could be further from the truth. I have been encouraged, sustained, inspired and tolerated not only by my family, but by the greatest fiancée Wan-Yu anyone ever had."

The research studies in this dissertation are partially supported by the Center for Domain-Specific Computing under the NSF InTrans Award CCF-1436827, funding from CDSC industrial partners including Google, Huawei, Intel, Mentor Graphics and VMWare; C-FAR, one of the six centers of STARnet, a Semiconductor Research Corporation program sponsored by MARCO and DARPA; grants from NIH U54EB020404 Big Data to Knowledge (BD2K) progam.

#### VITA

2011 B.S. (Computer Science), National Tsing Hua University, Taiwan.

2013 M.S. (Computer Science), National Tsing Hua University, Taiwan.

#### PUBLICATIONS

Y.-H. Lai, Y. Chi, Y. Hu, J. Wang, <u>Cody H. Yu</u>, Y. Zhou, J. Cong, Z. Zhang, "HeteroCL: A Multi-Paradigm Programming Infrastructure for Software-Defined Reconfigurable Computing", *FPGA*, 2019. (Best paper award)

J. Cong, Z. Fang, M. Huang, P. Wei, D. Wu, <u>Cody H. Yu</u>, "Customizable Computing– From Single Chip to Datacenters," *Proceedings of the IEEE*, 2019.

X. Wei, Y. Liang, X. Li, <u>Cody H. Yu</u>, P. Zhang, J. Cong, "TGPA: Tile-grained Pipeline Architecture for Low Latency CNN Inference," *ICCAD*, 2018.

J. Cong, P. Wei, <u>Cody H. Yu</u>, "From JVM to FPGA: Bridging Abstraction Hierarchy via Optimized Deep Pipelining," *HotCloud*, 2018.

J. Cong, P. Wei, <u>Cody H. Yu</u>, and P. Zhou, "Latte: Locality Aware Transformation for High-Level Synthesis," *FCCM*, 2018. J. Cong, P. Wei, <u>Cody H. Yu</u>, and P. Zhang, "Automated Accelerator Generation and Optimization with Composable, Parallel and Pipeline Architecture," *DAC*, 2018.

Cody H. Yu, P. Wei, P. Zhang, M. Grossman, V. Sarker, and J. Cong, "S2FA: An Accelerator Automation Framework for Heterogeneous Computing in Datacenters," *DAC*, 2018.

J. Cong, P. Wei, <u>Cody H. Yu</u>, and P. Zhou, "Bandwidth Optimization Through On-Chip Buffer Restructuring for HLS," *DAC*, 2017.

X. Wei, <u>Cody H. Yu</u>, P. Zhang, Y. Chen, Y. Wang, H. Hu, and J. Cong, "Automated Systolic Array Architecture Synthesis for High Throughput CNN Inference on FPGAs," *DAC*, 2017. (Best paper nominee)

M. Huang, D. Wu, <u>Cody H. Yu</u>, Z. Fang, M. Interlandi, T. Condie, and J. Cong, "Programming and Runtime Support to Blaze FPGA Accelerator Deployment at Datacenter Scale," *SoCC*, 2016.

J. Cong, M. Huang, D. Wu, and <u>Cody H. Yu</u>, "Invited - Heterogeneous Datacenters: Options and Opportunities," *DAC*, 2016. (Invited)

M.-C. Frank Chang, Y.-T. Chen, J. Cong, P.-T. Huang, C.-L. Kuo, and <u>Cody H. Yu</u>, "The SMEM Seeding Algorithm Acceleration for DNA Sequence Alignment," *FCCM*, 2016.

J. Cong, and <u>Cody H. Yu</u>, "Impact of Loop Transformations on Software Reliability," *ICCAD*, 2015.

# CHAPTER 1

# Introduction

The demand for scalable, high-performance computing has increased as the size of datasets has grown in recent years. In 2004, Google introduced the MapReduce [DG08] programming framework, a framework for efficiently managing tens of thousands to millions of servers in datacenters with a simple programming model. Inspired by Google MapReduce, open source big data analytic systems such as Apache Hadoop [HAD] and Spark [ZCF10] have developed and evolved rapidly. However, the breakdown of Dennard's scaling [DGR74] has led to energy efficiency becoming an important concern in datacenters, and spawned exploration into using powerefficient processors such as GPUs (Graphic Processing Units) and FPGAs (Field-Programmable Gate Arrays) as accelerators in datacenters.

In particular, the FPGA's low power consumption and the re-programmability allow datacenters to use FPGAs as highly energy-efficient accelerators for a variety of application. Applications with a large fraction of computationally-intensive kernels containing small amounts of control flow, such as string matching [CCL15], searching [PCC14] and sorting [CSP15, HLC14], are suitable to be accelerated using FPGAs. In addition, adopting FPGAs in private datacenters has recently garnered attention from the community. For example, IBM deploys FPGAs for its larger NoSQL data stores [BRH15]. Microsoft has adopted CPU-FPGA systems in its datacenter to help accelerate the Bing search engine [PCC14]. Moreover, the acquisition of Altera by Intel in 2015 promises continued development of closely-integrated CPU-FPGA platforms; the compute instance with FPGAs in Amazon EC2 introduced in 2016 enables the FPGA platform in the public datacenter. As a result, datacenters with FPGAs are expected to be widely used in the near future.

On the other hand, FPGA has poor programmability compared to instructionsbased architectures like CPU and GPU. Traditionally, Register-Transfer Level (RTL) description languages, such as VHDL and Verilog HDL, are the most widely used languages for FPGA design implementation. The use of these hardware description languages leads to the fact that the development concept of FPGA is circuit design instead of software implementation. According to the desired functionality, the designer comes up with a high-performance architecture, including finite state machine, data flow, and modules, and then implement the circuit in RTL. However, the design usually needs to be refined and improved iteratively, and each iteration takes a great deal of time and effort. To facilitate the process of implementing and deploying FPGA accelerators, High-Level Synthesis (HLS) [CLN11] that generates functional-equivalent RTL from C-based programming languages attracts more and more attention since past decades. Nowadays, both FPGA vendors have their commercial HLS products – Xilinx SDx [SDX] and Intel FPGA SDK for OpenCL [INT]. For example, Code 1.1 shows an intuitive HLS C implementation of Needleman-Wunsch (N-W) algorithm [NW70], a 2-D dynamic programming algorithm for string matching, for Xilinx FPGAs. Xilinx SDx is able to generate 9,694 lines of RTL kernel from Code 1.1 with the same functionality. As a result, it is much more efficient for designers to evaluate and improve their architectures in HLS C than RTL.

Code 1.1: N-W HLS C Code Snippet

```

1 void kernel(int batch, char seqAs[] (1), char seqBs[] (1),

2

char alignedAs[] (1), char alignedBs[] (1)) {

3 #pragma HLS INTERFACE m_axi port=seqAs offset=slave

4 #pragma HLS INTERFACE m_axi port=seqBs offset=slave

5 #pragma HLS INTERFACE m_axi port=alignedAs offset=slave

6 #pragma HLS INTERFACE m_axi port=alignedBs offset=slave

7 #pragma HLS INTERFACE s_axilite port=seqAs offset=control

8 #pragma HLS INTERFACE s_axilite port=seqBs offset=control

9 #pragma HLS INTERFACE s_axilite port=alignedAs offset=control

10 #pragma HLS INTERFACE s_axilite port=alignedBs offset=control

11

for (int i=0; i<batch; i++) { (4)</pre>

12

int M[129][129];

13

. . .

for(i=0; i<129; i++) (5) { M[0][i]=seqAs[...] (2) (3)}</pre>

14

for(j=0; j<129; j++) (5) {M[j][0]=...}</pre>

15

for(i=1; i<129; i++) (5) {</pre>

16

17

for(j=1; j<129; j++) (5) { M[i][j]=... }</pre>

18

}

19

// Skip ~170 lines of N-W algorithm implementation.

20

}

21 }

```

The primary programming model of commercial HLS tools is based on pragmas. Specifically, users are required to insert tool-dependent pragmas to the kernel code properly in order to trigger certain optimization such as parallel and pipeline. Along with the pragma-based programming model, a number of research work [SW12a, PG02, HKR07, SW12a, MPZ12, XPZ15, SFP11, LC13, FAP18b, FAP18a] attempt to automate the process of identifying the best pragma combination, in terms of pragma positions and values, for user applications. However, all of them target to the design space formed by HLS pragmas, which may fail to cover high-performance design points in many cases (see Chapter 2 for details). The main reason that simply inserting HLS pragmas to user kernel code cannot achieve high-performance is that modern commercial HLS tools generate architecture structures, such as dataflow, processing element replication, memory burst, and so forth, according to not only pragmas but also specific, clear HLS C code patterns, because the hardware architecture inferred from a syntactic C implementation could be ambiguous. As a result, even though the authors in [CLN11] have illustrated that the HLS tool is capable of generating FPGA designs with competitive performance as the one in RTL, designers must manually reconstruct the HLS C kernel with specific code patterns to achieve high performance, as demonstrated in [CFH18]. In fact, the generated FPGA accelerator from Code 1.1 is  $5 \times$  slower than a single-thread CPU.

Code 1.2: N-W HLS C Code Snippet with Manual Optimization

```

1 void NW(...) {

int M[129][129];

2

3 #pragma HLS array_partition variable=M cyclic factor=4 dim=1

4

for(i=0; i<129; i++) { (5)</pre>

5

6 #pragma HLS pipeline

7 #pragma HLS unroll factor=8

8

M[0][i] = ...,;

}

9

10

for(j=0; j<129; j++) { (5)</pre>

11 #pragma HLS pipeline

12 #pragma HLS unroll factor=8

13

M[j][0] = ...;

14

}

15

for(i=1; i<129; i++) {</pre>

for(j=1; j<129; j++) { (5)</pre>

16

17 #pragma HLS pipeline

18 #pragma HLS unroll factor=8

19

M[i][j] = ...

20

}}

21

. . .

22 }

23 void compute(char seqAs[32][16][8], char seqBs[32][16][8],

char alignedAs[32][8][32] char alignedBs[32][8][32]) {

24

```

```

25 #pragma HLS inline off

for (int i=0; i<32; i++) { ④</pre>

26

27 #pragma HLS unroll

NW(seqAs[i], seqBs[i], alignedAs[i], alignedBs[i]);

28

29 }}

30 void load(...) { ... } // off-chip data load

31 void store(...) { ... } // off-chip data store

32 void kernel(int batch, ap_uint<512> (1) seqAs[], ap_uint<512> (1) seqBs[],

33

ap_uint<512> (1) alignedAs[], ap_uint<512> (1) alignedBs[]) {

34 #pragma HLS INTERFACE m_axi port=seqAs offset=slave

35 #pragma HLS INTERFACE m_axi port=seqBs offset=slave

36 #pragma HLS INTERFACE m_axi port=alignedAs offset=slave

37 #pragma HLS INTERFACE m_axi port=alignedBs offset=slave

38 #pragma HLS INTERFACE s_axilite port=seqAs offset=control

39 #pragma HLS INTERFACE s_axilite port=seqBs offset=control

40 #pragma HLS INTERFACE s_axilite port=alignedAs offset=control

41 #pragma HLS INTERFACE s_axilite port=alignedBs offset=control

42

43

char seqAs_buf_0[32][16][8]; ③

44 #pragma HLS array_partition var=seqAs_buf_0 complete dim=1

45 #pragma HLS array_partition var=seqAs_buf_0 complete dim=3

46

// the declarations for the other buffers are omitted

for (int i=0; i<batch/32+2; i++) {</pre>

47

if (i \% 2 == 0) {

48

49

load(/* seqAs_buf_0 <= seqAs, seqBs_buf_0 <= seqBs */); (2)</pre>

compute(seqAs_buf_1, seqBs_buf_1, alignedAs_buf_1, alignedBs_buf_1)

50

store(/* alignedAs_buf_0 <= alignedAs, alignedBs_buf_0 <= alignedBs</pre>

51

*/); ② ③

52

}

53

else {

54

load(/* seqAs_buf_1 <= seqAs, seqBs_buf_1 <= seqBs */); (2)</pre>

55

compute(seqAs_buf_0, seqBs_buf_0, alignedAs_buf_0, alignedBs_buf_0)

store(/* alignedAs_buf_1 <= alignedAs, alignedBs_buf_1 <= alignedBs</pre>

56

*/); 2 3

57 }}

```

We analyze the performance bottleneck in Code 1.1 and propose a proper architecture structure in Table 1.1. The optimized code is demonstrated in Code 1.2, which has about  $2 \times$  lines of code compared to Code 1.1 we modified from. As can be seen in Code 1.2, in order to let the HLS tool generate the desired architecture, we need to manually rewrite the C code with very specific structures. Although the N-W accelerator of Code 1.2 is able to achieve around  $1,236 \times$  speedup on FPGA over a single-thread CPU, the effort of code reconstruction makes the iterative refinement process time-consuming.

In order to reduce the performance gap that caused by HLS-based code reconstruction, a number of automated frameworks have been developed to perform user code analysis and transformation [CZZ12, WLZ13, SYZ16, PZS13, CHZ14, LBC15, LWC16, TLZ15]. Those frameworks contain one or many optimization techniques to make HLS C programming more intuitively for software programmers. In addition, introducing new domain-specific languages (DSLs) is another widely considerable direction [ABC10, ARV03, BVR12, KPZ16, MPA16, SBC15, SPA16, LCH19], because a DSL is designed for only a domain of applications so it implies more semantic information than HLS C and can apply more specific optimization to further improve the QoR. However, current HLS C optimization frameworks and FPGA DSLs are too distinct to benefit each other in terms of architecture-based optimization and design space exploration strategies. This problem becomes one of the main impediment to consolidating the FPGA community on cooperation and developments.

In this dissertation, we present a unified compilation framework for raising an abstraction level of FPGA acceleration. Figure 1.1 illustrates the proposed framework. In Chapter 3, we first present an automated design space exploration framework for Merlin C [CHP16a, CHP16b] on FPGAs. We choose Merlin C because it is syntactic C with a concise set of useful pragmas for automatic code transformations. As we will introduce in Chapter 2, this concise set of pragmas serves a much higher design space coverage and results in higher possibility of achieving the optimal per-

| Table 1.1: Analysis of Poor Performance | $\mathrm{in}$ | Code $1.1$ |

|-----------------------------------------|---------------|------------|

|-----------------------------------------|---------------|------------|

| Mark                                                                                        | Reason of Poor Performance                                                                                                       | Required Architecture Structure |  |  |  |  |  |

|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--|--|--|--|--|

| Corresponding HLS Pragma with Required Code Changes                                         |                                                                                                                                  |                                 |  |  |  |  |  |

| 1                                                                                           | ① Low bus bit-width utilization Memory coalescing                                                                                |                                 |  |  |  |  |  |

| Manually use HLS built-in type \texttt{ap_int} with proper bit-width.                       |                                                                                                                                  |                                 |  |  |  |  |  |

| 2                                                                                           | 2 Low DRAM bandwidth utilization Memory burst                                                                                    |                                 |  |  |  |  |  |

| Manua                                                                                       | ally allocate local buffer and use memcpy funct                                                                                  | ion to copy data.               |  |  |  |  |  |

| 3                                                                                           | ③ Sequential communication and computation Coarse-grained pipeline                                                               |                                 |  |  |  |  |  |

|                                                                                             | Use \texttt{#pragma HLS pipeline} at a non-innermost loop and manually create load/compute/store functions and double buffering. |                                 |  |  |  |  |  |

| 4                                                                                           | (4) Lack of parallelism Coarse-grained parallelism                                                                               |                                 |  |  |  |  |  |

| Manually create a function to wrap the loop and set the correct<br>memory partition factor. |                                                                                                                                  |                                 |  |  |  |  |  |

| 5                                                                                           | 5 Sequential execution Fine-grained pipeline                                                                                     |                                 |  |  |  |  |  |

| Use \texttt{#pragma HLS pipeline} at an innermost loop.                                     |                                                                                                                                  |                                 |  |  |  |  |  |

| 5                                                                                           | Sequential execution                                                                                                             | Fine-grained parallelism        |  |  |  |  |  |

| Use \texttt{#pragma HLS unroll} with proper array partition factor.                         |                                                                                                                                  |                                 |  |  |  |  |  |

formance. Accordingly, our design space is composed of combinations of valid options for Merlin C pragmas in a user program. In order to efficiently search for the best configuration in tremendous design points, we first adapt an open-source framework, OpenTuner [AKV14], to perform design space exploration using multi-armed bandit approach with a set of meta-heuristic algorithms. However, since we leverage commercial HLS tools to evaluate the QoR of design points, our evaluation cost is extremely expensive (15 to 60 minutes for one design point). It results in low search efficiency with meta-heuristics. To further improve the search efficiency, we develop a gradient-based approach as well as a design bottleneck optimization algorithm by considering the characteristics of HLS programming model. Our experimental result shows that the proposed DSE framework is able to find the design point that achieves on geometric mean 93.78% to the corresponding manual design.

Figure 1.1: The Proposed Framework

Based on the DSE framework, we further design and implement two front-end compilers in Chapter 4 to illustrate how could the proposed framework benefit highlevel DSLs. We first target to Apache Spark [ZCD12] in Scala, a widely adopted big-data analytic runtime system in recent years. Specifically, we build a Scala-to-Merlin compiler that guarantees functional correctness. Although the user-defined functions (UDFs) in Sparks do not have any scheduling information specified by users so our DSE framework has to create a large design space for every possible pragma combinations, we can leverage Spark parallel patterns (e.g. map, reduce) to prune the design space.

Our second target DSL is HeteroCL [LCH19], a programming infrastructure for FPGAs. Since HeteroCL front-end compiles its DSL to Halide IR [RBA13] which is an in-memory dataflow representation, we implement a HalideIR-to-Merlin compiler to support HeteroCL. Due to the fact that HeteroCL programming model provides prolific scheduling functions to users, our DSE framework automates a part of them and let users focus only on the platform independent loop transformations. Consequently, the development process could be much more efficient.

Instead of supporting arbitrary HLS designs and leveraging commercial HLS tool as an evaluation methodology, sacrificing a degree of generalization could actually make the design space exploration more systematic and stable. In Chapter 5, we propose composable, parallel and pipeline (CPP) micro-architecture template by considering general optimization methodologies as we analyzed in Table 1.1. Although CPP micro-architecture cannot fit arbitrary applications, it is sufficient to support a board class of applications that are suitable to be accelerated on FPGAs. With a fixed micro-architecture template, we are capable of deriving an analytical model for performance and resource utilization. By running only few times of HLS to obtain the design and platform dependent constant values for model initialization, the CPP analytical model can estimate the design quality without HLS tool during the DSE process. The experimental result shows that the DSE process finds the best design configuration under CPP micro-architecture within an hour. On the other hand, while adopting a generic micro-architecture for a broad class of general designs, we can actually leverage the strengthen of domain specific microarchitectures such as systolic arrays [KUN88] to achieve higher performance for specific applications such as convolutional neural networks (CNNs) without running HLS tool. In Chapter 6, we implement a systolic array architecture template as the accelerator design for CNNs, and we then extend our DSE framework to map a CNN to the architecture template. According to the architecture, we develop a high accurate analytical model for performance and resource estimation. We will demonstrate in Chapter 6 that the DSE can be even more efficient and systematic with an analytical model of a more domain specific architecture.

The remainder of the dissertation is organized as follows. Chapter 2 introduces the background of high-level synthesis (HLS) as well as the Merlin compiler [CHP16a, MER, CHP16b], followed by the motivation of developing an automated DSE framework accordingly and the summary of related work. We then propose the framework in Chapter 3. We first propose a working but inefficient framework based on OpenTuner [AKV14], and gradually improve its design space representation and search algorithms. With the optimized DSE framework, we demonstrate its usability in Chapter 4 by supporting two infrastructures with domain specific languages in Scala and Python, respectively. On the other hand, we demonstrate in Chapter 5 that we can trade generalization with DSE efficiency by proposing a micro-architecture to cover board but not all classes of applications. Finally, we use a CNN case study to illustrate a different but efficient design space exploration approach with limited application domains in Chapter 6. Consequently, the conclusion of this dissertation is given in Chapter 7.

# CHAPTER 2

# Background

In this chapter, we first introduce the FPGA architecture and the commercial HLS tool for FPGAs, with key focus on required code reconstruction to achieve high performance. Then, we introduce the Merlin compiler [MER, CHP16a, CHP16b] that eases code reconstruction efforts and yet leaves a tremendous design space to users. Finally, we summarize state-of-the-art technologies related to this problem.

### 2.1 FPGA and High-Level Synthesis C/C++

A field-programmable gate array (FPGA) is a reconfigurable integrated circuit. A typical FPGA architecture [KTR08] is shown in Figure 2.1. Logic blocks, digital processing units (DSPs), and interconnects are reprogrammable to an arbitrary function. Short latency, programmable on-chip block RAMs (BRAMs) also allow developers to implement customized caches and FIFOs with different sizes and bit-widths. This hardware-level customizability allows FPGAs to achieve a significant energy efficiency improvement relative to CPUs and GPUs, as fewer FPGA transistors must be dedicated to control logic.

Researchers have foreseen the opportunity of applying FPGAs into modern datacenters for performance and energy improvement, but the programmability issue

Figure 2.1: A Common FPGA Architecture

emerges as a serious impediment against the adoption of FPGAs to datacenter application developers. In order to design an efficient FPGA kernel, the developer must have a comprehensive understanding of the underlying FPGA architecture. The FPGA kernel is usually implemented in hardware description languages (HDL) such as Verilog and VHDL, which are cycle-sensitive. The learning-curve for FPGAs is usually steep for new programmers.

Fortunately, high-level synthesis languages (HLS) [CLN11] have been developed in recent years to allow programmers to use C-based languages to implement FPGA kernels. Commercial HLS tools such as Xilinx SDAccel [SDX] and Intel FPGA SDK for OpenCL [INT] have been released and widely used to fast prototype userdefined functionalities expressed in high-level languages (e.g., C/C++ and OpenCL) on FPGAs without involving register-transfer level (RTL) descriptions. The design flows used in these tools are similar, as shown in Figure 2.2. First, a user input program is compiled to the LLVM Intermediate Representation (IR) [LLV07], along with the construction of its control data flow graph (CDFG). Then, the IR-to-HDL (hardware description language) code transformation is performed to map the IR to an RTL design with scheduling optimization. This completes the HLS process that maps the behavioral description of a design to its RTL description. Subsequently, the conventional FPGA design automation flow is launched to generate the design's bitstream file that contains the configuration data for FPGA's logic and RAM blocks.

Figure 2.2: Commercial HLS Tool Design Flow

The core HLS code transformation and optimization happens after the LLVM IR is obtained, indicating that the quality of an HLS design highly depends on its IR structure. In other words, two programs with the same functionality but different coding styles (leading to different IR structures) may result in a significant performance difference. In fact, this difference can be up to several orders of magnitude based on our experiences. As a consequence, programmers have to pay attention to every detail that may affect the generated IR structure, which often requires profound understanding of the FPGA architecture and circuit design.

In summary, HLS technologies improve the FPGA programmability by leveling it up from register-transfer level to behavioral level, but do not relieve the burden of manual code transformation that requires hardware design expertise.

# 2.2 Merlin Compiler

To alleviate the manual effort of heavy code reconstruction when improving a HLS C program, Merlin compiler [MER, CHP16a, CHP16b], a source-to-source transformation tool for FPGA acceleration based on the CMOST [ZHX15] compilation flow, was developed at Falcon Computing Solutions [FCS]. The Merlin compiler provides a set of pragmas with prefix "**#pragma ACCEL**" to represent optimization from the perspective of architecture design. According to user-specified Merlin pragmas, the compiler applies the corresponding architecture structure to the program by invoking abstract syntax tree (AST) analysis, vendor pragma insertion, and source-to-source code transformation. Table 2.1 illustrates the most commonly used Merlin pragmas with corresponding architectures. Note that the flatten option in the coarse-grained loop pipeline mode refers to the code transformation that tries to apply fine-grained pipelining to a nested loop by fully unrolling all its sub-loops.

Based on the transformation library, Figure 2.3 presents the Merlin compiler execution flow. It leverages the ROSE compiler infrastructure [ROS] and polyhedral framework [ZLC13] for abstract syntax tree (AST) analysis and transformation. The frontend stage analyzes the user program and separates host and computation kernel. The kernel code transformation stage then applies multiple code transformations according to user-specified pragmas. Note that the Merlin compiler will perform all necessary code reconstructions to make a transformation effective. For example, when performing loop unrolling, the Merlin compiler not only unrolls a loop but also conducts memory partitioning for the sake of avoiding bank conflict [CJL11]. Finally, the backend stage takes the transformed kernel and uses the HLS tool to generate the FPGA bit-stream.

| Keyword      | Target    | Available Options    | Architecture Structure |  |

|--------------|-----------|----------------------|------------------------|--|

| memory_burst | Interface | length= <int></int>  | Large DRAM bandwidth   |  |

| coalescing   | Interface | bitwidth= $<2^n>$    | Memory coalescing      |  |

| parallel     | CG loop   | factor = <int></int> | CG parallelism         |  |

| parallel     | FG loop   | factor = <int></int> | FG parallelism         |  |

| pipeline     | CG loop   | off,on,flatten       | CG/FG pipeline         |  |

| pipeline     | FG loop   | N/A                  | FG pipeline            |  |

Table 2.1: Merlin Pragmas with Architecture Structures

CG: Coarse-grained; FG: Fine-grained

Figure 2.3: The Merlin Compiler Execution Flow

We demonstrate the usability of Merlin compiler pragmas in Code 2.1. As can be seen, by adding a few line of pragmas, the Merlin compiler is able to transform Code 2.1 to Code 1.2 automatically. It means that we can achieve the same performance as the manual optimized HLS C program with less human efforts, and it is much easier for human to explore the best design configuration by simply changing the pragma factors.

Code 2.1: N-W Code Snippet in Merlin C

```

1 void kernel(int batch, char seqAs[], char seqBs[],

2

char alignedAs[], char alignedBs[]) {

3 #pragma ACCEL coalescing var=seqAs bitwidth=512

4 #pragma ACCEL coalescing var=seqBs bitwidth=512

5 #pragma ACCEL coalescing var=alignedAs bitwidth=512

6 #pragma ACCEL coalescing var=alignedAs bitwidth=512

8 #pragma ACCEL pipeline

9 #pragma ACCEL parallel factor=32

10

for (int i=0; i<batch; i++) {</pre>

11

int M[129][129];

12

. . .

13 #pragma ACCEL pipeline

14 #pragma ACCEL parallel factor=8

for(i=0; i<129; i++) { M[0][i]=seqAs[...] }</pre>

15

16 #pragma ACCEL pipeline

17 #pragma ACCEL parallel factor=8

for(j=0; j<129; j++) { M[j][0]=...}</pre>

18

19 #pragma ACCEL pipeline

20 #pragma ACCEL parallel factor=8

for(i=1; i<129; i++) {</pre>

21

22

for(j=1; j<129; j++) { M[i][j]=... }</pre>

}

23

24

. . .

25 }}

```

Although Merlin pragmas eliminates the manual code reconstruction, a designer still has to manually search for the best option for each pragma, including position, type, and factors. In fact, the N-W design in Code 2.1 has  $\sim 10^{10}$  design configurations in terms of Merlin pragma combinations. It motivates this thesis to develop an automation framework to find the best configuration efficiently.

## 2.3 Related Work

#### 2.3.1 Automated DSE Framework for Hardware Designs

Previous studies have attempted to propose various solutions to address individual design optimization problems. For example, [PSK15] focus on the problem of on-chip memory partitioning; [CHZ14] deal with processing element duplication; [CWY17] handles the improvement of off-chip bandwidth utilization. While these studies model the trade-offs between different design choices and realize the optimal choice via automatic design space exploration, they do not take inter-strategy trade-offs into consideration. In contrast, a number of recent studies have started paying attention to the interaction of different optimization strategies. [WHZ16] and [ZMS16] provide valuable guidance for hardware designers to make good use of various optimization strategies. However, since they do not come up with an automation solution, accelerator developers still have to manually conduct design space exploration.

On the other hand, there are a number of previous work that proposes an automated framework to explore the HLS design space by considering multiple optimization in a design space. We summarize them to two categories according to their search approaches and evaluation methodologies.

**Model-based DSE**: The first category builds a model using sampled data to realize the performance and resource utilization for each explored design point without actual running the HLS, and use the model to guide the DSE. The authors in [OMC08] use artificial neural networks and linear regression to build performance models for fast design quality estimation. Similarity, authors in [ZKM12] build a regression model based on Gaussian processes to model area and throughput. Authors in [STW09] and [SW12b] adapt simulated annealing and pattern matching algorithms as search approaches. To the same end, authors in [LC16] leverage transfer-learning to predict design qualities based on the knowledge transferred from the sampled data. Although this approach eliminates the human efforts of porting the framework to another platform since the model training process could be automated, it does not guarantee if the selected learning model fits the target HLS tool or not. For example, the suitable layer numbers and sizes of a neural network for a specific platform may not suitable for another. Even worst, the coverage of training features may not be held for different platforms. Migrating the framework to another HLS tool may violate the assumption and result in a low accuracy of the model.

In addition, another group of work build an analytical model by carefully studying the target HLS tools. [ZPL16, ZFS17] provides a more comprehensive model with the consideration of DSPs and BRAMs, but the author in [ZPL16, ZFS17] does not model the consumption of LUTs which can also be the resource bottleneck in FPGA designs in many cases. In addition, [ZPL16, ZFS17] aim to improve the performance by realizing the optimal HLS directives without code transformation. As a result, its qualify of results highly depends on the structure and coding style of the user input kernel code. [KPZ16, ZPW17] leverage machine learning to model the LUT consumption. However, the model has to be trained for each specific tool implementation, which means the model has to be retrained once the tool is changed or updated. In summary, although those frameworks are able to realize the best design point by searching thousands of design points in a short time, it is hard to port them to another HLS tool in different version or vendor, as the model assumes the underlying architecture and HLS tool implementation are fixed. Model-free DSE: On the other hand, the other category treats HLS tool as a block box and develops iterative refinement searching algorithms by referring HLS reported result qualities. Most of them first randomly samples a set of design points and find a Pareto set as their starting points, and then apply different algorithms to improve the Pareto set on the fly. The authors in [SW12a], [PG02] and [HKR07] build a predictive model using a sampled data set and use genetic algorithm to refine it. In addition, the design space coverage for those work is relatively low. For example, the design space in [SW12a] only includes loop unroll factor, function scheduling and array resource types, which is insufficient to cover the optimal solution for a board class of applications. [MPZ12, XPZ15, SFP11] adopts response surface models (RSM) and spectral analysis to predict the quality of design points without actual running HLS, but it is hard to guarantee the implementation changes of vendor HLS tools can always be captured by the model.

In addition, the authors in [LC13] proposes a framework that utilizes random forest and randomized transductive experimental design (RTED) to select representative points for training a predictive model that can be used to approximate a Pareto set. However, RTED is failing to random sampling when the design space is too large, so the overall mechanism is not scalable. [FAP18a] resolves this problem by proposing a clustering approach that selects only few clusters of configurations. On the other hand, the author in [FAP18a] also proposes another approach [FAP18b] that groups the design space only based on the variance of design points. They first analyze the design space using principle component analysis (PCA) and claim that the Pareto efficient design points can be clustered with small variances of their configurations. Accordingly, their exploration algorithm randomly selects a neighbor design point of the current Pareto efficient point as the next target. Based on their claim, once the algorithm finds a global Pareto efficient point, other global Pareto efficient points can be easily explored. This approach, however, might not be efficient with a more complicate and large design space like we have adopted in this dissertation. For example, the design space formed by Merlin pragmas include coarse-grained pipeline and parallelism. Coarse-grained pipeline and parallelism have more uncertainty to the performance and area and it is hard to prove that the global Pareto efficient points are always clustered. Moreover, when the design space is tremendous large (e.g., the scale of  $10^{10}$  to  $10^{30}$ ), the cost of initial sampling is not negligible. Even it only samples 1% in the design space, it means  $10^8$  to  $10^{28}$  design points. Without enough samples, however, the exploration process may not cover the entire design space. For example, in order to explore the design point that has two different parameter values, the proposed algorithm has to reach another design point to the current point. If the dominate point cannot be reached by changing one parameter, the exploration terminates immediately.

#### 2.3.2 Domain Specific Frameworks for FPGAs

There has been a fair amount of previous work that generates FPGA code from highlevel programming languages. Vivado HLS [VIV, CLN11] is a commercial tool that performs high-level synthesis to generate FPGA kernel code from C-based languages. CHiMPS [PBD08] takes ANSI C code as an input and generates VHDL blocks for FPGAs. However, using C-based programming languages to describe parallelism is not trivial because their execution model and design logic are fundamentally sequential. In contrast, the domain-specific language [BVR12, ARV03, ABC10] leverages specialized programming models to guide the compiler for more optimizations.

In addition, some FPGA-based frameworks are developed for a specific application domain such as machine learning [MPA16] and SQL queries [CDL13]. Since these frameworks map user programs to pre-defined hardware templates with specific functionality, they only support limited kernels. On the other hand, [PKB16] develops a parallel pattern language for FPGAs and compiles the source code to DHDL [KPZ16], an intermediate representation language for FPGAs. The DHDL kernel is able to be transformed to an FPGA design with hardware template and design space exploration. However, [PKB16] is designed for single node applications and does not consider programmability as well as system integration.

Furthermore, some other work performs FPGA code generation in the context of datacenter runtime systems. [SMC14] integrates AMD APARAPI [APA] into Apache Hadoop [HAD] and targets FPGAs. However, this work only supports primitive types, and requires manual design optimization. Their followed work, SparkCL [SCN15], extended the framework to Spark but a detail evaluation is missing. Melia [WZH16] is a MapReduce framework that automatically generates FPGA kernels in OpenCL from user-written functions, and optimizes the generated kernels by leveraging an analytical performance model [WHZ16]. The generated FPGA kernel is invoked by the Melia runtime system. However, the source language in Melia is still a syntactically C language, so programmability is limited. In addition, Melia is not compatible with any widely used big data analytics frameworks, so users must rewrite their applications using the Melia programming model in order to adopt this framework.

# CHAPTER 3

# An Automated Design Optimization Framework

## 3.1 Overview

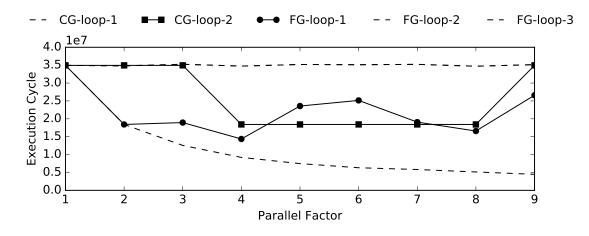

As we have elaborated in Chapter 1 and Chapter 2, the HLS programming models for modern commercial tools require manual code reconstructions to help the tool realize certain architecture patterns such as dataflow, processing element replication, memory burst, and so on. There have some existing work [ZVL14, ZFS17] that have proposed automation frameworks to free humans from the tedious code reconstruction process in development cycles by more or less fixing the architecture patterns and building analytical models. [ZVL14] uses a simple analytical mode to estimate performance and area of loops in the kernel, and decides whether the dataflow architecture should be enabled or not accordingly. [ZFS17] also proposes an analytical model for performance estimation and applies dataflow architecture to user designs when applicable. Unfortunately, their models are based on the assumption that an individual design parameter will affect the performance/area in a smooth and/or monotonic way, which is not true in general with latest HLS tools as well as the larger design space used in this thesis. For instance, Figure 3.1 depicts the execution cycle of the N-W algorithm with different parallel factors for its 5 loops synthesized by Xilinx SDAccel [SDX]. Although the performance trend of CG-loop-1, FG-loop-2, and  $FG-loop-3^1$  are ideal (so we use the same dash line in the figure), the rest 2 loops (CG-loop-2 and FG-loop-1) are not. Note that these behaviors may differ from version to version; therefore it is impractical to maintain an analytical model for DSE.

Figure 3.1: HLS Cycles of N-W with Different Factors on Loops

On the other hand, the main challenge of using vendor HLS tools for DSE to capture all vendor tool behaviors is the evaluation cost, since vendor HLS tools usually take 15-60 minutes to generate RTL and estimate the performance, and it usually takes a longer time if the design has a high performance. As a result, general iterative learning approaches are unstable to find the high quality of result (QoR) design configuration in a reasonable amount of time. To improve the DSE efficiency, in this chapter, we propose a comprehensive design space representation that only includes meaningful design point while preserving a regular design space shape. By explicitly representing the design space with application-specific knowledge, we are able to avoid the meaningless design points and improve the DSE efficiency. In

<sup>&</sup>lt;sup>1</sup>CG and FG mean coarse-grained and fine-grained, respectively.

addition, based on the design space we study the effectiveness of multi-armed bandit approach [FDS10] with meta-heuristic optimization algorithms and further propose new algorithms to facilitate the search process. In summary, this chapter makes the following contributions:

- We propose an efficient but comprehensive design space representation to support dependent design space parameters.

- We use multi-armed bandit approach with evolutionary algorithms [BNK98] and particle swarm optimization [GSZ18] for DSE and analyze their challenges.

- Based on the insights from multi-armed bandit approach, we develop a gradient search algorithm that leverages finite difference method to approximate gradient values for systematically approaching to high-QoR design points.

- By reasoning the gradient search process, we further improve the gradient approach with performance bottleneck analysis to improve the search efficiency.

Our experimental result shows that the proposed DSE framework is able to find the design point that achieves on geometric mean 92.56% to the corresponding manual design.

The rest of this chapter is organized as follows. Section 3.2 presents the initial version of our framework that contains working flow with the use of multi-armed bandit approach for several meta-heuristic optimization methods. Then, Section 3.3 shows an improved framework with HLS DSE specific optimization to its execution flow. In order to reason the DSE process for resolving the low QoR issue for certain designs, Section 3.4 proposes an algorithm to statically prune the design space, as well

as a gradient-based search algorithm to systematically identify better design points. Finally, Section 3.5 further presents a comprehensive design space representation and an improved gradient-based search algorithm. Finally, the summary is given in Section 3.6.

## 3.2 Version 1: An Initial Framework

## 3.2.1 Framework Overview

Traditionally, numerical approaches such as linear programming are widely used for performing DSE. Unfortunately, it is inapplicable to our case because such approaches require at least an analytical form to evaluate the design quality. Since our goal is to cover the difference of commercial HLS tools, we treat the evaluation function as a black-box and only accepts its outputs (QoR report) by feeding design points. As a result, our initial idea is to use a set of meta-heuristic algorithms, such as evolution genetic algorithms [BNK98], and particle swarm optimization [GSZ18], to perform DSE.

However, a well-tuned meta-heuristic algorithm is usually too specific to cover a board class of applications. In order to assemble multiple meta-heuristic algorithms to improve the generalization, hyper-heuristic, which searches for an optimal solution by selecting one of the meta-heuristic algorithms in a pool iteratively, is proposed. Hyper-heuristic usually uses an exploitation versus exploration (EvE) approach as follows to rank a meta-heuristic algorithm a for specific applications:

$$Score(a) = Exploitation(a) + c \times Exploration(a)$$

(3.1)

where the former term guarantees the meta-heuristic with better performance will be selected more frequently; while the latter term leaves opportunities to other metaheuristics. c is a constant for exploitation-exploration dilemma.

We use OpenTuner [AKV14], an open-source auto-tuning framework for software programs as the hyper-heuristic engine to explore the design space. OpenTuner leverages multi-armed bandit (MAB) approach [FDS10] with sliding window area under curve (AUC) credit assignment [PAA12]. Every meta-heuristic in the MAB approach is an arm with a dynamic EvE credit as its score. The credit of a metaheuristic m is defined as:

$$C_m = AUC_m + c \times \sqrt{\frac{2log|H|}{H_m}}$$

(3.2)

where  $AUC_m$  is the quantified performance (exploitation) of meta-heuristics while  $\sqrt{\frac{2log|H|}{H_m}}$  is the quantified uncertainty (exploration). In addition,  $H_m$  is the number of times that m has been selected during a history sliding window with length |H|. At each iteration, the MAB selects the meta-heuristic with the highest credit and updates creates based on the result. Consequently, the meta-heuristic that can efficiently finds high-quality design points will be rewarded and activated more frequently by the MAB, and vice versa.

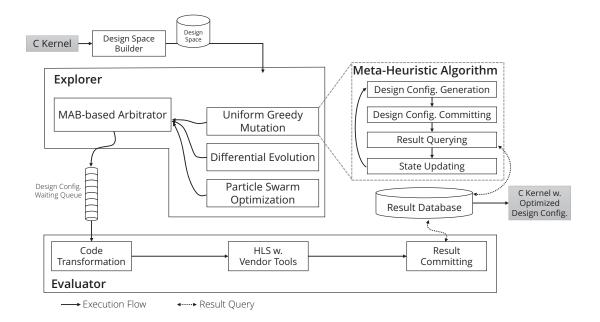

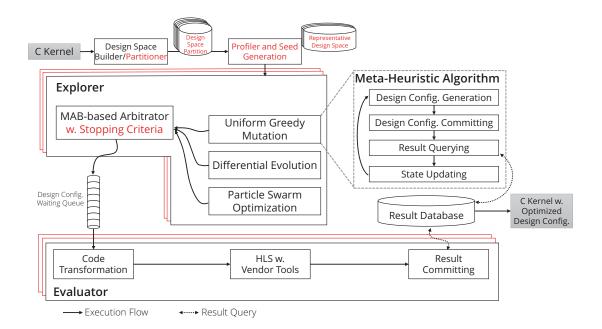

Figure 3.2 shows an initial framework based on OpenTuner. The framework accepts a user-written C kernel as input and first performs static code analysis to identify the design space (Section 3.2.2), which is composed of Merlin pragmas and their valid options. The design space is then explored using MAB approach with several meta-heuristic algorithms (Section 3.2.3). Every design point generated by search algorithms will apply corresponding Merlin source-to-source code transforma-

Figure 3.2: The Framework based on OpenTuner [AKV14]

tions and be evaluated using commercial HLS tools. The evaluation result is stored in a shared result database that can be accessed by all algorithms so that populationbased meta-heuristic algorithms could go through a shortcut by taking others better results anytime. Finally, when the exploration is terminated due to the time limit, the framework outputs the so far best design point to continue the rest accelerator generation process. In the rest of this section, we detail introduce the design space as well as the meta-heuristic we adopted in the framework.

## 3.2.2 Design Space Identification

We formulate the problem of identifying a design space in a C program as follows: Given a C program  $\mathcal{P}$  as the FPGA accelerator kernel, find a set  $\mathbb{S}_{\mathcal{P}}$  that contains possible combinations of Merlin pragmas for  $\mathcal{P}$  as design configurations.

| Factor            | Design Space (Values)                                                                                                                    |  |  |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Memory coalescing | $\{b \mid b = bw(B) \in \mathbb{B}, 8 < b = 2^n < 512\}$                                                                                 |  |  |  |

| Memory burst      | $\{t \mid t = T(L) \in \mathbb{L}, 1 < t < TC(L)\}$                                                                                      |  |  |  |

| CG-loop parallel  | $\{u \mid u = UF(L) \in \mathbb{L}, 1 < u < TC(L)\}$                                                                                     |  |  |  |

| FG-loop parallel  | $\left\{ u \mid u = UF(L) \in \mathbb{L}, \begin{cases} 1 < u < TC(L),  TC(L) > 16 \\ u = TC(L),  \text{otherwise} \end{cases} \right\}$ |  |  |  |

| CG-loop pipeline  | $\{p \mid p = P(L) \in \mathbb{L}, p \in \{off, on, flatten\}\}$                                                                         |  |  |  |

| FG-loop pipeline  | $\{p \mid p = P(L) \in \mathbb{L}, p = fg\}$                                                                                             |  |  |  |

Table 3.1: Merlin Pragma Formed Design Space

CG: Coarse-grained; FG: Fine-grained; TC: Loop trip-count

We list available design spaces based on Merlin pragmas in Table 3.1. We identify the design space for each kernel by analyzing the kernel AST using the ROSE compiler infrastructure [ROS] and polyhedral framework [ZLC13] to realize loop tripcounts, available bit-widths, and so on. In addition, since vendor HLS tools usually schedule fine-grained loops well, we only explore the parallel factor of fine-grained loops when its trip-count is larger than 16; otherwise, we simply apply fully unroll and pipeline to small fine-grained loops to reduce the design space. As can be seen, it is impractical to explore this tremendous design space exhaustively. For example, the design space of the N-W example contains more than a 10<sup>13</sup> design points. This illustrates the importance of search algorithm efficiency for reaching a near-optimal solution in a few iteration.

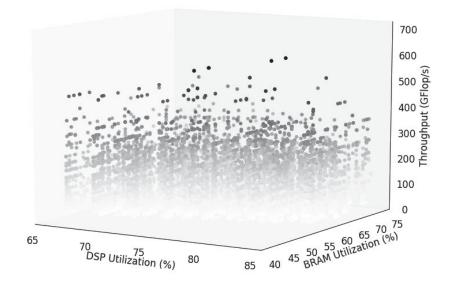

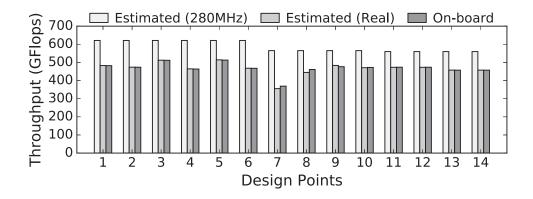

## 3.2.3 Meta-Heuristic Optimization Methods