### UNIVERSITY OF CALIFORNIA, IRVINE

Exascalable Communication for Modern Supercomputing

### DISSERTATION

submitted in partial satisfaction of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

in Computer Engineering

by

Rohit Zambre

Dissertation Committee: Associate Professor Aparna Chandramowlishwaran, Chair Professor Athina Markopoulou Assistant Professor Ardalan Amiri Sani

© 2020 Rohit Zambre

# DEDICATION

To my parents, Shahaji and Ujwala Zambre for their immense sacrifices, and to serendipity.

# TABLE OF CONTENTS

|    |                                                           | P                                                                                                                                                                                                                                                                                                                        | Page                                                                                                                  |

|----|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| LI | ST O                                                      | F FIGURES                                                                                                                                                                                                                                                                                                                | vi                                                                                                                    |

| LI | ST O                                                      | F TABLES                                                                                                                                                                                                                                                                                                                 | ix                                                                                                                    |

| A  | CKN                                                       | OWLEDGMENTS                                                                                                                                                                                                                                                                                                              | x                                                                                                                     |

| VI | TA                                                        |                                                                                                                                                                                                                                                                                                                          | xii                                                                                                                   |

| Al | BSTR                                                      | ACT OF THE DISSERTATION                                                                                                                                                                                                                                                                                                  | xiv                                                                                                                   |

| 1  | <b>Intro</b><br>1.1<br>1.2<br>1.3                         | oduction<br>Background and Architecture Trends                                                                                                                                                                                                                                                                           |                                                                                                                       |

| 2  | <ul><li>2.1</li><li>2.2</li><li>2.3</li><li>2.4</li></ul> | lytical Models of Communication         Background         2.1.1         Communication Components         2.1.2         PCIe Express         2.1.3         Mechanisms of a High-Performance Interconnect         Evaluation Setup         Measurement Methodology         Definitions         Overall Injection Overhead | <ol> <li>9</li> <li>11</li> <li>11</li> <li>12</li> <li>13</li> <li>15</li> <li>16</li> <li>17</li> <li>18</li> </ol> |

|    | 2.5<br>2.6                                                | Overall Injection Overhead                                                                                                                                                                                                                                                                                               | <ol> <li>18</li> <li>18</li> <li>21</li> <li>29</li> <li>29</li> <li>29</li> <li>29</li> </ol>                        |

|    | 2.7                                                       | Simulated Optimizations                                                                                                                                                                                                                                                                                                  | 34<br>35<br>38                                                                                                        |

|    | 2.8                                                       | Concluding Remarks                                                                                                                                                                                                                                                                                                       | 39                                                                                                                    |

| 3 | Mu          | ltithrea        | ded Communication Capabilities on Modern Networks | 41        |

|---|-------------|-----------------|---------------------------------------------------|-----------|

|   | 3.1         |                 | round                                             | 43        |

|   |             | 3.1.1           | RDMA's Software Stack                             | 43        |

|   |             | 3.1.2           | Verbs Communication Objects                       | 43        |

|   |             | 3.1.3           | RDMA Operational Features                         | 44        |

|   | 3.2         | Comn            | nunication Resources                              | 46        |

|   | 3.3         | Resou           | rce-Sharing Opportunities                         | 48        |

|   | 3.4         | Exper           | iment setup                                       | 49        |

|   | 3.5         | Resou           | rce-Sharing Analysis                              | 51        |

|   |             | 3.5.1           | Memory Buffer Sharing                             | 52        |

|   |             | 3.5.2           | Device Context Sharing                            | 53        |

|   |             | 3.5.3           | Protection Domain Sharing                         | 56        |

|   |             | 3.5.4           | Memory Region Sharing                             | 56        |

|   |             | 3.5.5           | Completion Queue Sharing                          | 57        |

|   |             | 3.5.6           | Queue Pair Sharing                                | 59        |

|   |             | 3.5.7           | Summary of Lessons Learned                        | 60        |

|   | 3.6         | Resou           | rce-Sharing Model                                 | 61        |

|   |             | 3.6.1           | Demonstration                                     | 63        |

|   | 3.7         | Concl           | uding Remarks                                     | 65        |

|   |             |                 | r man 1 x + 1                                     |           |

| 4 |             |                 | I+Threads Library                                 | <b>67</b> |

|   | 4.1         | 4.1.1           | elism in the Current MPI-3.1 Standard             | 68        |

|   |             | 4.1.1<br>4.1.2  | Point-to-Point Communication                      | 68<br>70  |

|   | 4.2         |                 |                                                   | 70<br>71  |

|   | 4.2<br>4.3  |                 | are and Testbeds                                  | 71        |

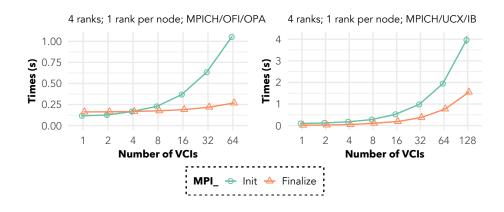

|   | 4.3<br>4.4  |                 | ializing Access to the MPI Library                | 72<br>74  |

|   | 4.4         | гаят г<br>4.4.1 | Optimizing multi-VCI communication                | 74        |

|   | 4.5         |                 |                                                   | 82        |

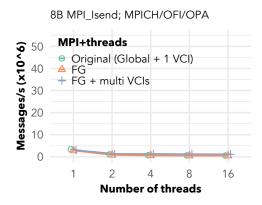

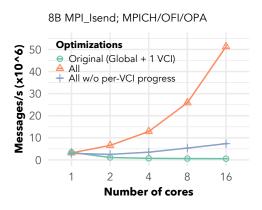

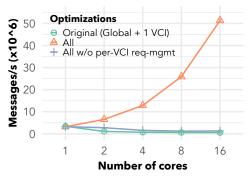

|   | 4.5         | 4.5.1           | benchmark Analysis                                |           |

|   |             | 4.5.1           | Point-to-point communication                      |           |

|   |             | 4.5.2           | Thread-safety costs                               | 86        |

|   | 4.6         |                 | nunication Pattern Analysis with Mini-Apps        | 87        |

|   | 4.0         | 4.6.1           | Halo Communication in Stencil Applications        | 88        |

|   |             | 4.6.2           | Remote Data Fetches in OpenMC                     | 90        |

|   |             | 4.6.3           | Block-Sparse Matrix Multiplication in NWChem      | 90<br>93  |

|   | 4.7         |                 | d Work                                            | 95<br>95  |

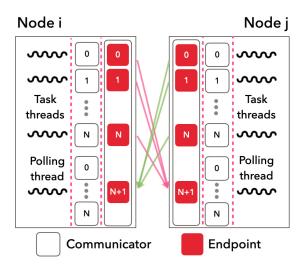

|   | <b>1</b> ./ | 4.7.1           | MPI Endpoints demonstration                       | 95<br>96  |

|   |             | 4.7.1           |                                                   | 90<br>96  |

|   |             | 4.7.2           | Open MPI                                          | 90<br>97  |

|   | 4.8         |                 |                                                   |           |

|   | <b>H.</b> O | Conci           | uding Remarks                                     | 20        |

| 5                                                              |                                                     |         | MPI+Threads Applications with Logically Parallel Communication |       |  |

|----------------------------------------------------------------|-----------------------------------------------------|---------|----------------------------------------------------------------|-------|--|

|                                                                | 5.1                                                 |         | ation Testbeds                                                 |       |  |

|                                                                | 5.2                                                 |         | inisms to Expose Logical Parallelism                           |       |  |

|                                                                |                                                     | 5.2.1   | User-Visible Endpoints                                         |       |  |

|                                                                |                                                     | 5.2.2   | Existing MPI Mechanisms                                        |       |  |

|                                                                |                                                     | 5.2.3   | Mapping Mechanisms to Network Parallelism                      |       |  |

|                                                                |                                                     | 5.2.4   | Microbenchmark evaluation                                      |       |  |

|                                                                | 5.3                                                 | Applic  | cation Case Studies                                            |       |  |

|                                                                |                                                     | 5.3.1   | Uintah and hypre                                               | . 108 |  |

|                                                                |                                                     | 5.3.2   | WOMBAT                                                         | . 114 |  |

|                                                                |                                                     | 5.3.3   | Legion                                                         |       |  |

|                                                                | 5.4                                                 | Conclu  | uding Remarks                                                  | . 124 |  |

| 6                                                              | If N                                                | ot MPI  | Endpoints, How About MPI Rankpoints?                           | 126   |  |

|                                                                | 6.1                                                 | Design  | n Comparison of Mechanisms                                     | . 128 |  |

|                                                                |                                                     | 6.1.1   | Point-to-Point Operations                                      |       |  |

|                                                                |                                                     | 6.1.2   | RMA Operations                                                 | . 136 |  |

|                                                                |                                                     | 6.1.3   | Collectives                                                    |       |  |

|                                                                |                                                     | 6.1.4   | Portability                                                    | . 139 |  |

|                                                                | 6.2                                                 | Conclu  | uding Remarks                                                  |       |  |

| 7                                                              | Con                                                 | cluding | g Remarks                                                      | 141   |  |

|                                                                | 7.1                                                 |         | ary                                                            | . 141 |  |

|                                                                | 7.2                                                 |         | directions                                                     |       |  |

|                                                                |                                                     | 7.2.1   | Studying different ways of GPU-to-GPU communication            | . 143 |  |

|                                                                |                                                     | 7.2.2   | Logically parallel communication for deep learning             |       |  |

|                                                                |                                                     | 7.2.3   | User-friendly abstractions to use existing MPI mechanisms      |       |  |

| Bi                                                             | bliog                                               | raphy   |                                                                | 145   |  |

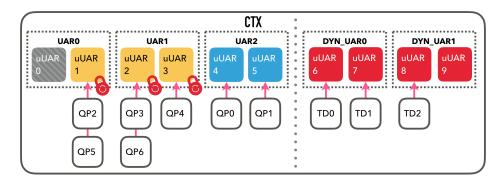

| Appendix A User Access Region in Mellanox Network Adapters 154 |                                                     |         |                                                                | 154   |  |

| Ar                                                             | Appendix B Mellanox's QP-to-uUAR Mapping Policy 156 |         |                                                                |       |  |

| I                                                              | $\sim$ 11 5 $^{\circ}$                              |         |                                                                |       |  |

# **LIST OF FIGURES**

## Page

| 1.1<br>1.2 | Network utilization in the state of the art                                                         | 5         |

|------------|-----------------------------------------------------------------------------------------------------|-----------|

|            | where                                                                                               | 6         |

| 2.1        | Communication performance comparison between HPC vendors                                            | 9         |

| 2.2<br>2.3 | Components involved in the transmission of a message                                                | 11        |

| 2.5        | wire.                                                                                               | 14        |

| 2.4        | Two-node setup with PCIe analyzer on node 1                                                         | 15        |

| 2.5        | PCIe trace of downstream PCIe transactions for UCX's RDMA-write injection-                          |           |

| •          | rate benchmark (put_bw).                                                                            | 16        |

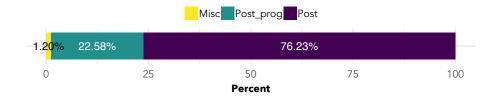

| 2.6        | Injection overhead observed by the NIC.                                                             | 20<br>24  |

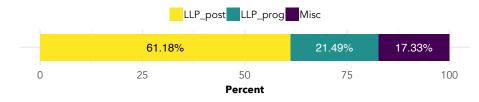

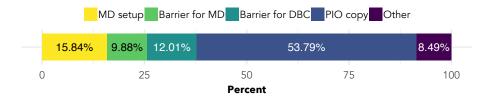

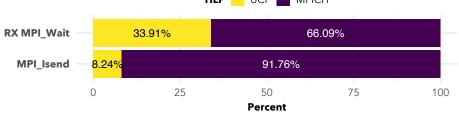

| 2.7<br>2.8 | Breakdown of injection overhead with the LLP                                                        | 24        |

| 2.0        | counter).                                                                                           | 24        |

| 2.9        | Distribution of the observed injection overhead (maximum value is an out-                           | <b>41</b> |

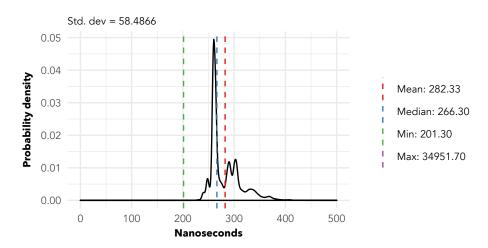

| 2.9        | lier)                                                                                               | 24        |

| 2.10       | Breakdown of time in HLP.                                                                           | 26        |

| 2.11       | Breakdown of the overall injection overhead.                                                        | 28        |

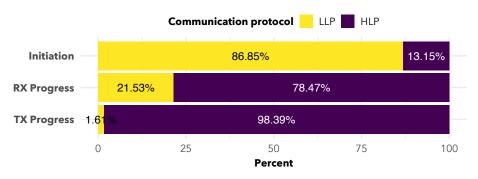

| 2.12       | Breakdown of time in HLP and LLP during the initiation and progress of                              |           |

|            | communication.                                                                                      | 28        |

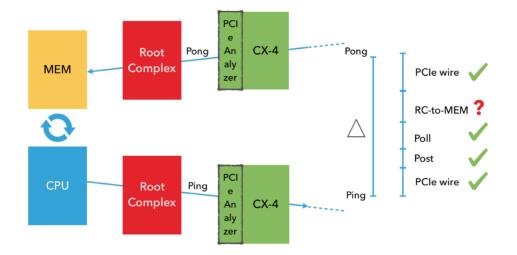

| 2.13       | Measuring <i>RC-to-MEM</i> ( <i>xB</i> ) using the time delta between an inbound pong               |           |

|            | and outbound ping on node 1                                                                         | 31        |

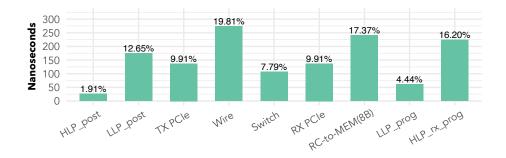

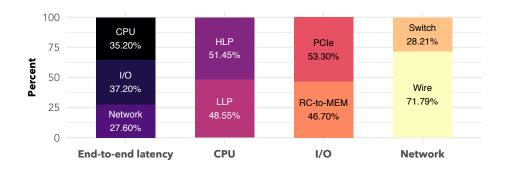

|            | Breakdown of the end-to-end latency.                                                                | 33        |

|            | High-level breakdown of the end-to-end latency.                                                     | 33        |

|            | Breakdown of time spent on node.                                                                    | 33        |

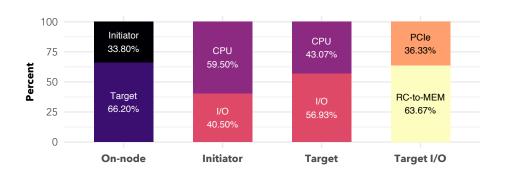

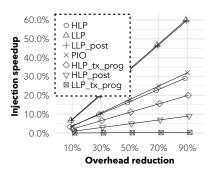

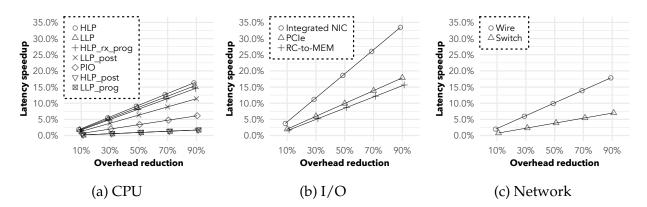

|            | Simulated speedups in overall injection by reducing CPU overheads                                   | 38        |

| 2.10       | Simulated speedups in end-to-end latency by reducing overheads of CPU, I/O, and network components. | 38        |

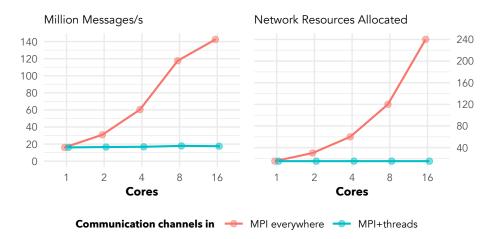

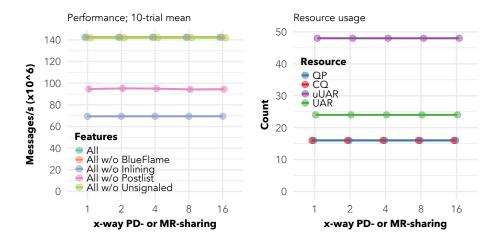

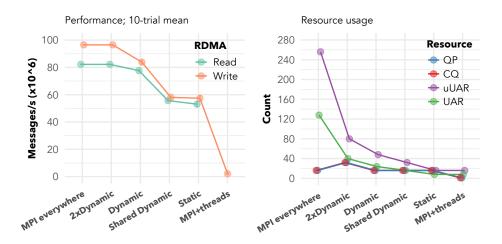

| 3.1        | Throughput (higher is better) and network resource usage (lower is bet-                             |           |

|            | ter) in state-of-the-art communication channels on Mellanox's ConnectX-4                            |           |

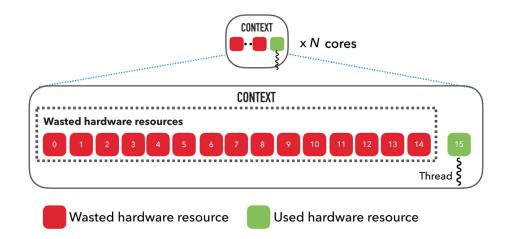

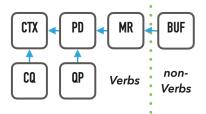

| 3.2        | adapter                                                                                             | 42<br>47  |

|            |                                                                                                     |           |

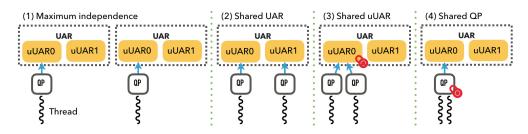

| 3.3                                                                                                                                                         | Four levels of thread-to-network-resource mapping in mlx5 between inde-                                                                                           |                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

|                                                                                                                                                             | pendent threads.                                                                                                                                                  | 49                                                                                                 |

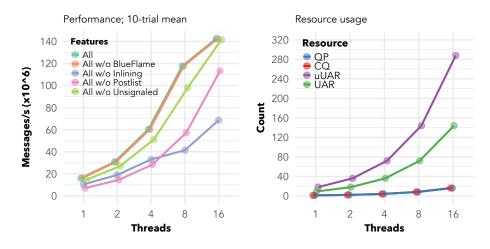

| 3.4                                                                                                                                                         | Performance (left) and resource usage (right) scalability with a CTX per thread.                                                                                  | 50                                                                                                 |

| 3.5                                                                                                                                                         | Hierarchical relation between the various Verbs objects (the arrow points                                                                                         | 00                                                                                                 |

|                                                                                                                                                             | to the parent); each object can have multiple children but only one parent                                                                                        | 51                                                                                                 |

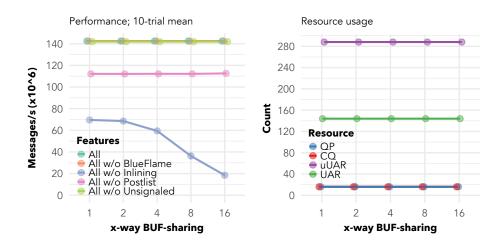

| 3.6                                                                                                                                                         | Message rate (left) and communication resource usage (right) with increas-<br>ing BUF sharing across 16 threads.                                                  | 52                                                                                                 |

| 3.7                                                                                                                                                         | Effects on (a) message rate and (b) PCIe reads with and without cache-                                                                                            | 53                                                                                                 |

| 20                                                                                                                                                          | aligned buffers.                                                                                                                                                  | 55                                                                                                 |

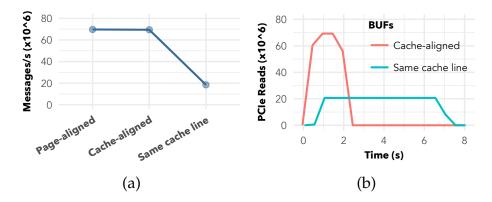

| 3.8                                                                                                                                                         | Message rate (left) and communication resource usage (right) with increas-                                                                                        | <b>F</b> 4                                                                                         |

| 20                                                                                                                                                          | ing CTX sharing across 16 threads.                                                                                                                                | 54                                                                                                 |

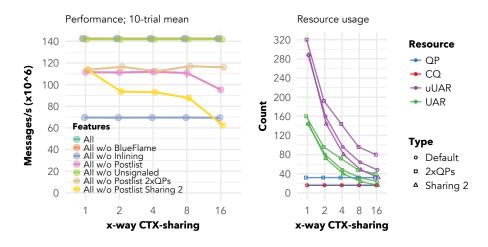

| 3.9                                                                                                                                                         | Message rate (left) and communication resource usage (right) with increas-                                                                                        | _ /                                                                                                |

|                                                                                                                                                             | ing PD or MR sharing across 16 threads.                                                                                                                           | 56                                                                                                 |

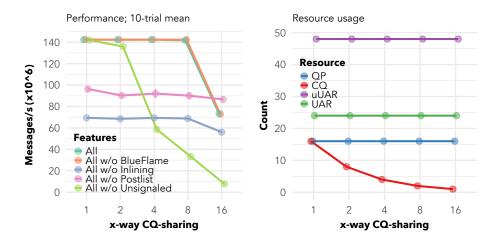

| 3.10                                                                                                                                                        | Message rate (left) and communication resource usage (right) with increas-                                                                                        |                                                                                                    |

|                                                                                                                                                             | ing CQ sharing across 16 threads                                                                                                                                  | 57                                                                                                 |

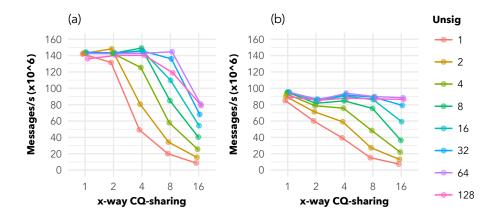

|                                                                                                                                                             | (a) Postlist size of 32, (b) Postlist size of 1                                                                                                                   | 58                                                                                                 |

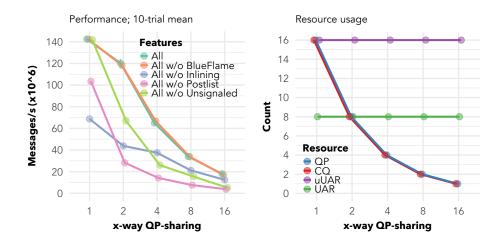

| 3.12                                                                                                                                                        | Message rate (left) and communication resource usage (right) with increas-                                                                                        |                                                                                                    |

|                                                                                                                                                             | ing QP sharing across 16 threads                                                                                                                                  | 59                                                                                                 |

| 3.13                                                                                                                                                        | Scalable communication channels for the global array kernel with 16 threads.                                                                                      |                                                                                                    |

|                                                                                                                                                             | Left: Communication throughput. Right: Communication resource usage .                                                                                             | 64                                                                                                 |

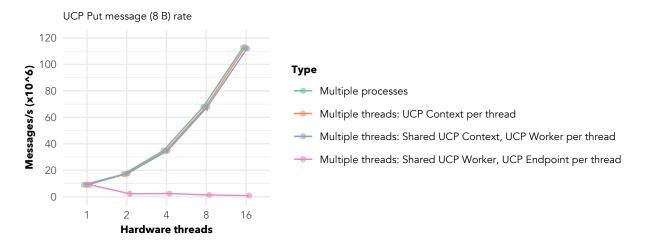

| 3.14                                                                                                                                                        | Performance of different levels of resource sharing in UCX                                                                                                        | 66                                                                                                 |

|                                                                                                                                                             | C C C C C C C C C C C C C C C C C C C                                                                                                                             |                                                                                                    |

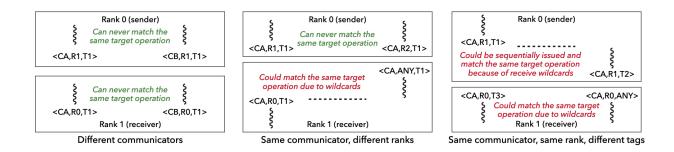

| 4.1                                                                                                                                                         | Different combinations of (comm,rank,tag) tuples demonstrating point-to-<br>point parallelism in MPI-3.1. Dashed horizontal lines represent thread bar-           | 60                                                                                                 |

|                                                                                                                                                             | Different combinations of (comm,rank,tag) tuples demonstrating point-to-<br>point parallelism in MPI-3.1. Dashed horizontal lines represent thread bar-<br>riers. | 69                                                                                                 |

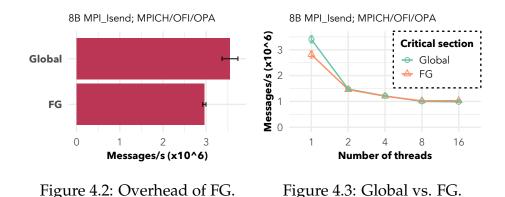

| 4.2                                                                                                                                                         | Different combinations of (comm,rank,tag) tuples demonstrating point-to-<br>point parallelism in MPI-3.1. Dashed horizontal lines represent thread bar-<br>riers. | 73                                                                                                 |

| 4.2<br>4.3                                                                                                                                                  | Different combinations of (comm,rank,tag) tuples demonstrating point-to-<br>point parallelism in MPI-3.1. Dashed horizontal lines represent thread bar-<br>riers  | 73<br>73                                                                                           |

| 4.2<br>4.3<br>4.4                                                                                                                                           | Different combinations of (comm,rank,tag) tuples demonstrating point-to-<br>point parallelism in MPI-3.1. Dashed horizontal lines represent thread bar-<br>riers  | 73<br>73<br>75                                                                                     |

| 4.2<br>4.3<br>4.4<br>4.5                                                                                                                                    | Different combinations of (comm,rank,tag) tuples demonstrating point-to-<br>point parallelism in MPI-3.1. Dashed horizontal lines represent thread bar-<br>riers  | 73<br>73                                                                                           |

| 4.2<br>4.3<br>4.4                                                                                                                                           | Different combinations of (comm,rank,tag) tuples demonstrating point-to-<br>point parallelism in MPI-3.1. Dashed horizontal lines represent thread bar-<br>riers  | 73<br>73<br>75<br>76                                                                               |

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6                                                                                                                             | Different combinations of (comm,rank,tag) tuples demonstrating point-to-<br>point parallelism in MPI-3.1. Dashed horizontal lines represent thread bar-<br>riers  | 73<br>73<br>75<br>76<br>78                                                                         |

| <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> </ul>                                                                    | Different combinations of (comm,rank,tag) tuples demonstrating point-to-<br>point parallelism in MPI-3.1. Dashed horizontal lines represent thread bar-<br>riers  | 73<br>73<br>75<br>76<br>78<br>78                                                                   |

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6                                                                                                                             | Different combinations of (comm,rank,tag) tuples demonstrating point-to-<br>point parallelism in MPI-3.1. Dashed horizontal lines represent thread bar-<br>riers  | 73<br>73<br>75<br>76<br>78<br>78<br>80                                                             |

| <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> <li>4.8</li> <li>4.9</li> </ul>                                          | Different combinations of (comm,rank,tag) tuples demonstrating point-to-<br>point parallelism in MPI-3.1. Dashed horizontal lines represent thread bar-<br>riers  | 73<br>73<br>75<br>76<br>78<br>78                                                                   |

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10                                                                                                | Different combinations of (comm,rank,tag) tuples demonstrating point-to-<br>point parallelism in MPI-3.1. Dashed horizontal lines represent thread bar-<br>riers  | 73<br>73<br>75<br>76<br>78<br>78<br>80                                                             |

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11                                                                                        | Different combinations of (comm,rank,tag) tuples demonstrating point-to-<br>point parallelism in MPI-3.1. Dashed horizontal lines represent thread bar-<br>riers  | 73<br>73<br>75<br>76<br>78<br>78<br>80<br>81                                                       |

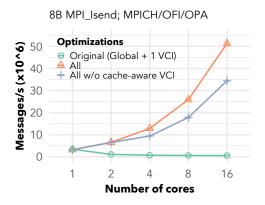

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11                                                                                        | Different combinations of (comm,rank,tag) tuples demonstrating point-to-<br>point parallelism in MPI-3.1. Dashed horizontal lines represent thread bar-<br>riers  | 73<br>73<br>75<br>76<br>78<br>78<br>80<br>81<br>83                                                 |

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11<br>4.12                                                                                | Different combinations of (comm,rank,tag) tuples demonstrating point-to-<br>point parallelism in MPI-3.1. Dashed horizontal lines represent thread bar-<br>riers  | 73<br>73<br>75<br>76<br>78<br>78<br>80<br>81<br>83<br>83                                           |

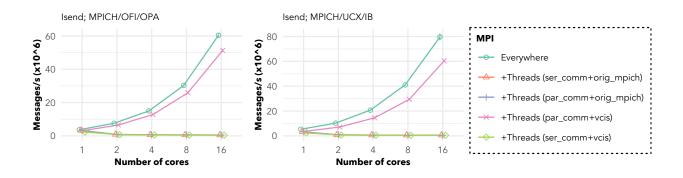

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11<br>4.12<br>4.13                                                                        | Different combinations of (comm,rank,tag) tuples demonstrating point-to-<br>point parallelism in MPI-3.1. Dashed horizontal lines represent thread bar-<br>riers  | 73<br>73<br>75<br>76<br>78<br>78<br>80<br>81<br>83<br>83<br>83                                     |

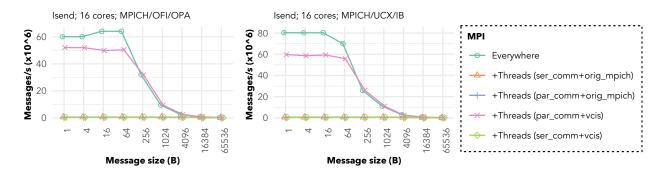

| $\begin{array}{c} 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \\ 4.6 \\ 4.7 \\ 4.8 \\ 4.9 \\ 4.10 \\ 4.11 \\ 4.12 \\ 4.13 \\ 4.14 \\ 4.15 \end{array}$                         | Different combinations of (comm,rank,tag) tuples demonstrating point-to-<br>point parallelism in MPI-3.1. Dashed horizontal lines represent thread bar-<br>riers  | 73<br>75<br>76<br>78<br>80<br>81<br>83<br>83<br>85<br>85                                           |

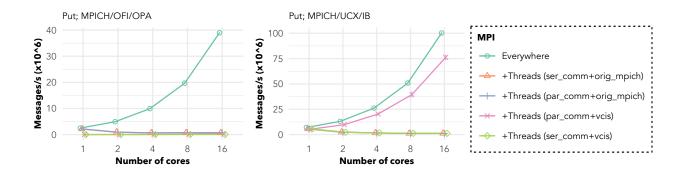

| $\begin{array}{r} 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \\ 4.6 \\ 4.7 \\ 4.8 \\ 4.9 \\ 4.10 \\ 4.11 \\ 4.12 \\ 4.13 \\ 4.14 \\ 4.15 \\ 4.16 \end{array}$                 | Different combinations of (comm,rank,tag) tuples demonstrating point-to-<br>point parallelism in MPI-3.1. Dashed horizontal lines represent thread bar-<br>riers  | 73<br>75<br>76<br>78<br>78<br>80<br>81<br>83<br>83<br>85<br>85<br>85<br>86                         |

| $\begin{array}{r} 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \\ 4.6 \\ 4.7 \\ 4.8 \\ 4.9 \\ 4.10 \\ 4.11 \\ 4.12 \\ 4.13 \\ 4.14 \\ 4.15 \\ 4.16 \end{array}$                 | Different combinations of (comm,rank,tag) tuples demonstrating point-to-<br>point parallelism in MPI-3.1. Dashed horizontal lines represent thread bar-<br>riers  | 73<br>75<br>76<br>78<br>78<br>80<br>81<br>83<br>83<br>85<br>85<br>86<br>86                         |

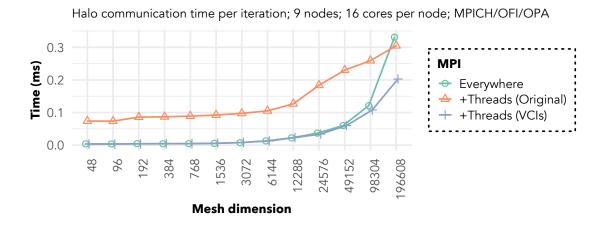

| $\begin{array}{r} 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \\ 4.6 \\ 4.7 \\ 4.8 \\ 4.9 \\ 4.10 \\ 4.11 \\ 4.12 \\ 4.13 \\ 4.14 \\ 4.15 \\ 4.16 \\ 4.17 \\ 4.18 \end{array}$ | Different combinations of (comm,rank,tag) tuples demonstrating point-to-<br>point parallelism in MPI-3.1. Dashed horizontal lines represent thread bar-<br>riers  | 73<br>75<br>76<br>78<br>78<br>80<br>81<br>83<br>83<br>85<br>85<br>86<br>86<br>86<br>87<br>88<br>88 |

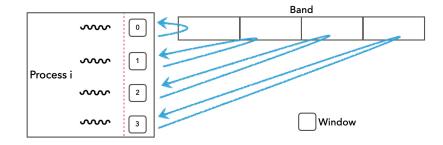

|                | Communication parallelism in MPI+threads EBMS                                                    | 90  |

|----------------|--------------------------------------------------------------------------------------------------|-----|

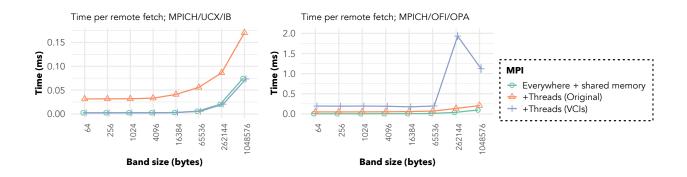

| 4.21           | UCX/IB (left) and OFI/OPA (right).                                                               | 91  |

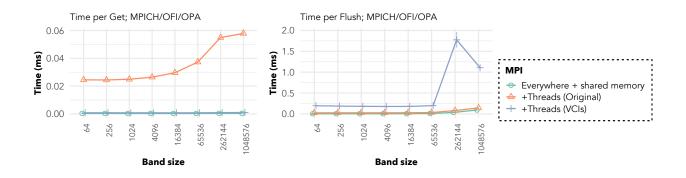

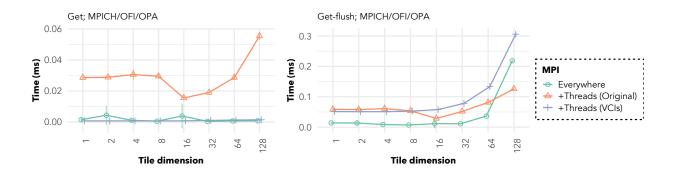

| 4 22           | Get and flush time across varying band sizes on OFI/OPA.                                         |     |

|                | Logical parallelism in MPI+threads BSPMM.                                                        |     |

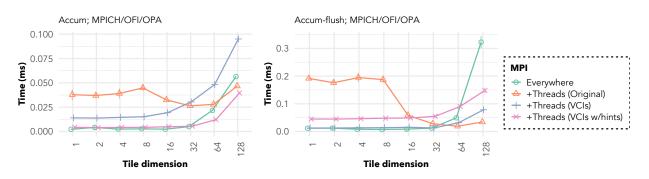

|                | BSPMM Get communication performance on Intel Omni-Path.                                          |     |

|                | BSPMM Accumulate communication performance on Intel Omni-Path                                    |     |

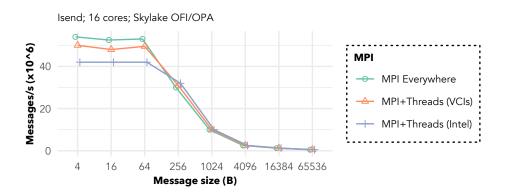

|                | VCIs compared against Intel MPI.                                                                 |     |

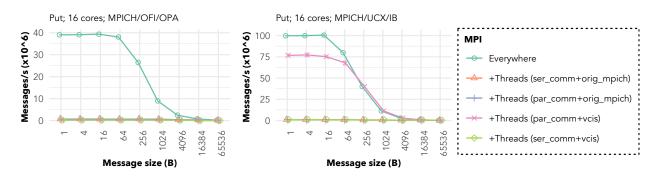

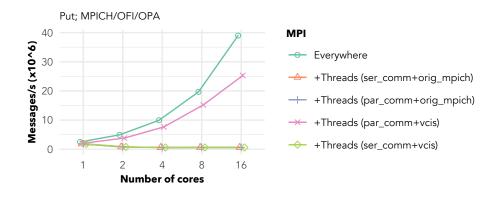

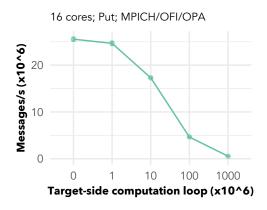

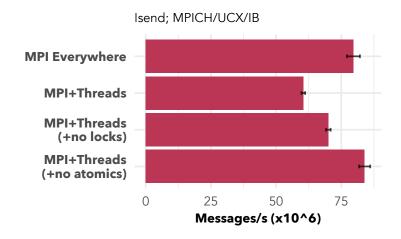

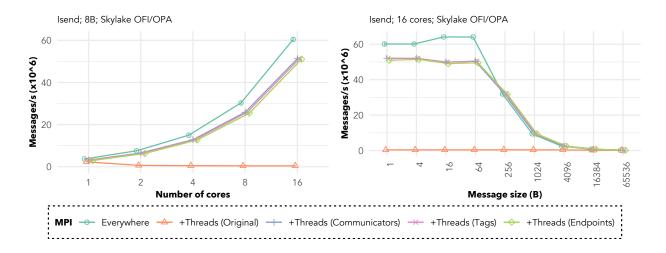

| 5.1            | Microbenchmark performance comparison of mechanisms to expose logi-                              |     |

|                | cally parallel point-to-point operations.                                                        | 106 |

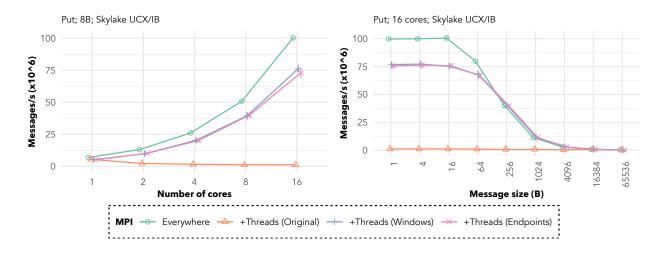

| 5.2            | Microbenchmark performance comparison of mechanisms to expose logi-                              | 10/ |

|                | cally parallel RMA operations.                                                                   |     |

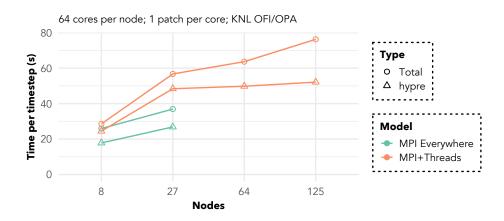

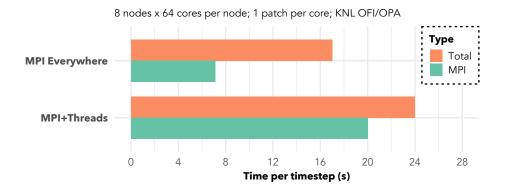

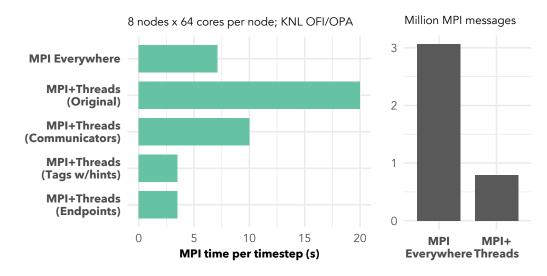

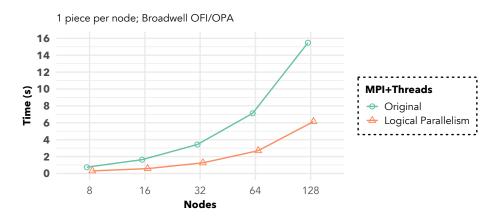

| 5.3            | MPI everywhere vs. MPI+threads in Uintah.                                                        |     |

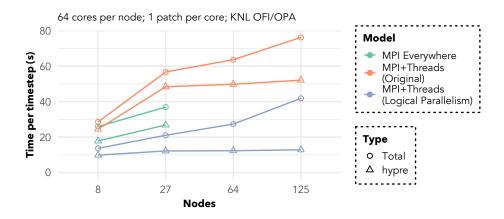

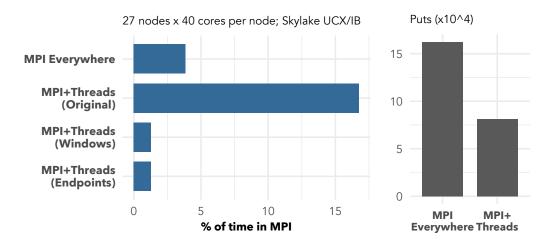

| 5.4<br>5.5     | Higher MPI time in MPI+threads hypre.                                                            | 110 |

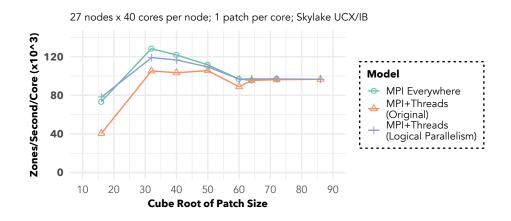

| 5.5            | Different mechanisms of exposing logical communication parallelism for hypre (1 patch per core). | 112 |

| 5.6            | MPI communication volume per node.                                                               |     |

| 5.7            | Uintah with logically parallel communication.                                                    |     |

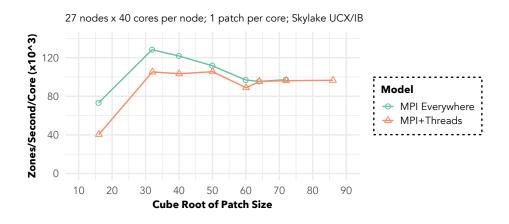

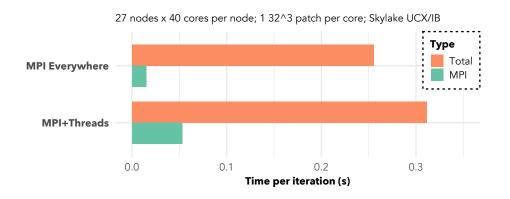

| 5.8            | MPI everywhere vs. MPI+threads WOMBAT.                                                           | 115 |

| 5.9            | Higher MPI time in MPI+threads WOMBAT.                                                           | 116 |

| 5.10           |                                                                                                  |     |

|                | WOMBAT (1 32 <sup>^</sup> 3 patch per core)                                                      | 117 |

| 5.11           | MPI Puts per node.                                                                               | 117 |

|                | Scientific throughput of WOMBAT with logically parallel communication.                           |     |

| 5.13           | Limiting existing MPI semantics compared to user-visible endpoints for                           |     |

|                | the communication pattern in Legion applications                                                 | 121 |

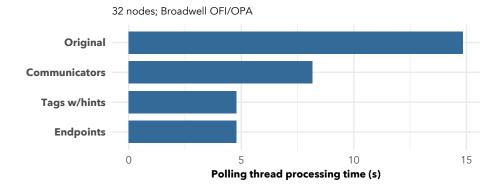

|                | Polling thread processing on Circuit's critical path                                             |     |

| 5.15           | Circuit simulation performance with logically parallel communication                             | 123 |

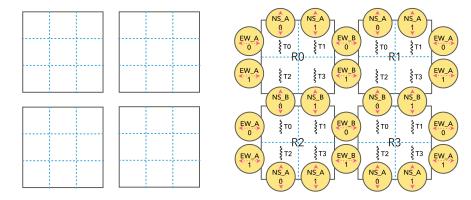

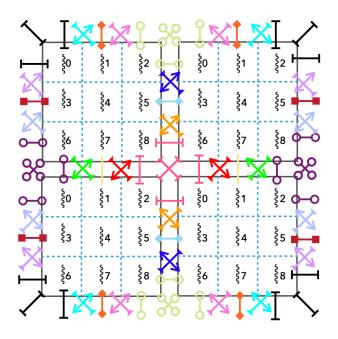

| 6.1            | Ideal communicator usage for a 2D 9-point stencil. Each box represents a                         |     |

|                | process with 9 threads. Each thread has 1 patch. Each color-shape combi-                         | 100 |

| $(\mathbf{n})$ | nation represents a communicator. Numbers represent thread IDs.                                  | 129 |

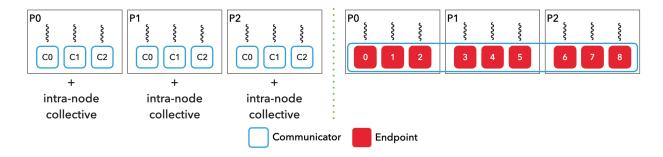

| 6.2            | Existing mechanisms vs. user-visible endpoints for collective communica-                         | 120 |

|                | tion                                                                                             | 139 |

# LIST OF TABLES

## Page

| 2.2 | Measured times of low-level software components                                                             | 26  |

|-----|-------------------------------------------------------------------------------------------------------------|-----|

| 3.1 | Memory (bytes) used by Verbs resources                                                                      | 46  |

| 4.1 | Summary of locks on the critical path of initiation and progress operations in different critical sections. | 80  |

| 6.1 | Summary of design choices to expose logically parallel communication                                        | 140 |

# ACKNOWLEDGMENTS

My Ph.D. journey consists of many serendipitous events that have impacted both my academic and personal lives in significant ways. I am extremely thankful for their occurences.

First and foremost, I would like to thank Aparna for beleiving in me and taking me on as her student. I am extremely grateful to her technical, writing, and personal advices throughout my Ph.D. Her lessons have taught me to never lose sight of the bigger picture both in research and in life. Her constant motivation helped me push through the toughest of times. Thank you, Aparna, for your guidance in navigating my Ph.D. journey and always encouraging me to strive for the best.

I thank Pavan Balaji from Argonne National Laboratory (ANL) for supporting my Ph.D. and providing me with the opportunity to work on an important problem that allowed me to experience research first-hand at a national-lab setting. I thank him for pushing the boundaries of my capabilities and teaching me how to conduct incremental and in-depth research. His technical advices and detailed help on papers have been invaluable. Thank you, Pavan.

I thank Pasha (Pavel Shamis) from Arm Research for providing me with a unique opportunity to play with super expensive PCIe analyzers and experience research at an industry-research environment. His playful enthusiasm about network technologies and emphasis on work-life balance was refreshing to witness. Thank you, Pasha, for the very interesting and rewarding opportunity.

I thank Athina Markopoulou and Ardalan Amiri Sani for always being there to support me, and for taking the time to serve on both my candidacy and thesis committees.

I am extremely grateful to have had the best of labmates both at UC Irvine and at ANL. Shintaro at ANL played an integral role in my learning phase and I am thankful for the countless discussions, lessons, and pointers, that he patiently provided me with. Thanks to Kaiming for the fruitful research discussions and for patiently listening to me during tough times. Giuseppe, Kavitha, and Sridutt at ANL have been both great mentors and friends and I thank them for their support and fun times. I have made very fond memories with my HPC Forge labmates—Laleh, Bahareh, Behnam, Shu-Mei, Octavi, and Hengjie—both in and out of lab. From paintball to skiing to just goofing around in the lab and at conferences, I thank them for all the invaluable memories.

My friends at UCI have kept me refreshed throughout my Ph.D. Thanks to Ronit for showing me around Orange County and Los Angeles, for always introducing me to great music, and for all the phone calls and voicemails. Thanks to Nikhil for the good times in Irvine, for showing me around Austin, and for teaching me the ropes of negotiating a job offer. Thanks to Primal and Anirudh for being my first Ph.D. friends at UCI and for introducing me into their circle of friends—Dhrub, Nitin, Roberto, and Pele. The many hiking trips we took together have been key highlights of my time at UCI. Thanks to Marwen for being a great friend throughout the Ph.D. and for graciously hosting me with top-notch breakfasts during my brief stays in Irvine. Special thanks to Primal for helping me get through the beginning phases of the pandemic and for taking me grocery shopping when I didn't have a car. Special thanks also to Tanya, Prabhat, and Aishwarya for the pandemic movie nights and memorable birthday celebrations.

I am thankful to have met my friends Chanpreet, Preet, and Rohan in Chicago who not only showed me around, but also helped me get through the windy city's long winters. The road trips and parties were excellent stress relievers. Special thanks to them for introducing me to Jeni's ice cream, my go-to for any celebration now.

Through my internships, I have made long-lasting friendships and that have supported me continuously throughout the Ph.D. Thanks to Anthony (whom I met at Arm) for always coming out to support me be it at a virtual recorded presentation or a live defense. Thanks to Martin (whom I met at Argonne) for his continued support from France.

A big thanks to Lucy for sticking by my side through all the stressful paper deadlines, and for helping me move across the country on various occasions. Without her help, sympathy and support, my Ph.D. journey wouldn't have had as many happy moments as it did. Thank you, Lu. Special thanks to Lucy's parents—John and Jackie—for hosting me at their home and giving me a comfortable place to stay as I wrote this dissertation.

Thank you Mama and Baba for your immense sacrifices over the years, and thank you for supporting my freedom in pursuing a Ph.D. Special thanks to my little sister, Mrunal, for her support and for regularly paying me visits no matter where I was located.

## VITA

### **Rohit Zambre**

#### **EDUCATION**

| <b>Doctor of Philosophy in Computer Engineering</b>  | <b>2020</b>      |

|------------------------------------------------------|------------------|

| University of California, Irvine                     | Irvine, CA       |

| Master of Science in Computer Engineering            | <b>2017</b>      |

| University of California, Irvine                     | Irvine, CA       |

| <b>Bachelor of Science in Electrical Engineering</b> | <b>2015</b>      |

| Iowa State University                                | Ames, IA         |

| RESEARCH EXPERIENCE                                  |                  |

| Graduate Research Assistant                          | <b>2015–2020</b> |

| University of California, Irvine                     | Irvine, CA       |

| <b>Visiting Student</b>                              | <b>2017–2020</b> |

| Argonne National Laboratory                          | Lemont, IL       |

| Research Intern                                      | Summer 2018      |

Arm Research

**Research Aide** Argonne National Laboratory

**Research Assistant** Mozilla Research

#### **TEACHING EXPERIENCE**

**Graduate Teaching Assistant** University of California, Irvine

**Peer Mentor** Iowa State University

**Undergraduate Teaching Assistant** Iowa State University Summer 2018 Austin, TX

Summer 2017 Lemont, IL

Summer 2016 Irvine, CA

> **Fall 2016** *Irvine, CA*

**2012–2015** Ames, IA

**Fall 2013** *Ames, IA*

### ENGINEERING EXPERIENCE

| Hackathon Participant                   | <b>January 2020</b> |

|-----------------------------------------|---------------------|

| Intel Corporation                       | Austin, TX          |

| Intern SSD Modeling Engineer            | <b>Summer 2014</b>  |

| Micron Technology, Inc.                 | Longmont, CO        |

| NAND Product Engineering Intern         | <b>Summer 2013</b>  |

| Micron Technology, Inc.                 | Boise, ID           |

| <b>REFEREED CONFERENCE PUBLICATIONS</b> |                     |

| How I Learned To Stop Worrying about User-Visible End-<br>points and Love MPI<br>34th ACM International Conference on Supercomputing (ICS)                    | June 2020                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| <b>Breaking Band: A Breakdown of High-Performance Com-<br/>munication</b><br>48th ACM International Conference on Parallel Processing (ICPP)                  | August 2019                           |

| Scalable Communication Endpoints for MPI+Threads Applications<br>24th IEEE International Conference on Parallel and Distributed System                        | December 2018<br>ns (ICPADS)          |

| ParallelPerformance-EnergyPredictiveModelingofBrowsers:Case Study of Servo.23rd IEEEInternational Conference on High Performance Computing,<br>alytics (HiPC) | <b>December 2016</b><br>Data, and An- |

## ABSTRACT OF THE DISSERTATION

Exascalable Communication for Modern Supercomputing

By

Rohit Zambre

Doctor of Philosophy in Computer Engineering University of California, Irvine, 2020 Associate Professor Aparna Chandramowlishwaran, Chair

Supercomputing applications rely on strong scaling to achieve faster results on a larger number of processing units. But, at the strong-scaling limit, where communication is a relatively large portion of an application's runtime, today's state-of-the-art hybrid MPI+threads applications perform slower than their traditional MPI everywhere counterparts. This slowdown is primarily due to the supercomputing community's outdated view: the network is a single device. NICs of modern interconnects feature multiple network hardware contexts. These parallel interfaces into the network are not utilized in MPI+threads applications today because MPI libraries still use conservative approaches to maintain MPI's ordering constraints. MPI libraries do so because domain scientists today do not do a good job exposing logically parallel communication in their multithreaded MPI communication even though the existing MPI standard provides them with opportunities to do so. Only when domain scientists and MPI developers take a step forward together can we eliminate the communication bottleneck in MPI+threads applications.

This dissertation eliminates the communication bottleneck by bridging the two ends of the HPC stack—MPI library developers and domain experts—that typically do not talk to each other directly. Through collaborations with system researchers and MPI library developers, we develop a fast MPI+threads library capable of achieving scaling communication throughput similar to that of MPI everywhere and make high-speed multithreaded communication a reality. Through collaborations with domain scientists, we use various designs to expose logically parallel communication to the fast MPI+threads library on exemplar applications targeted to run on the upcoming exascale systems. Our conversations with the end-users—the domain experts—educate us on the usability aspects of the various designs. Hence, in addition to the performance comparisons of the various design recommendation for the supercomputing community. Through such collaborations on both ends of the HPC stack, we unlock the true potential of the MPI+threads programming model. Prominent modern applications and computational frameworks, such as Uintah, WOMBAT, and Legion, now perform significantly faster (up to 2x) at the strong-scaling limit.

# Chapter 1

# Introduction

Multiple national-level efforts across the globe are striving to reach the next frontier in computing: exascale computing. In the pursuit of achieving an exaflop, that is, 10<sup>18</sup> floating point operations per second, the architectures of supercomputers have critically evolved over the last decade, jeopardizing the traditional models of programming them. Even with modern programming models, however, domain scientists rely on the efficient use of a larger number of parallel processing units to achieve faster scientific productivity (strong scaling) [76, 47]. At the limits of strong scaling, the workload per processing unit is small and the communication between the units occupies a significant portion of an application's runtime. We can witness this behavior in both the scientific computing and AI domains. Scientific computing typically consists of stencil-style workloads with neighborhood communication that takes up a large fraction of the runtime at scale [102, 103, 91], and communicating gradients in deep learning is a major bottleneck for distributed DNN training at scale [104, 65]. Hence, as we inch towards exascale computing, it is critical that applications are able to achieve high parallel efficiencies with scalable communication performances using modern programming models.

## 1.1 Background and Architecture Trends

The Message Passing Interface (MPI) has been the de facto standard for programming supercomputers and it is typically used in a SIMD fashion by launching a process per core. This approach is commonly referred to as MPI everywhere since it enables the domain scientist to transparently utilize both the core-level and node-level parallelism on large-scale distributed systems. The traditional MPI everywhere programming model has served the community well for decades, but it is no longer a good fit for modern processors, and it is not enough to program modern supercomputers. Two architecture trends have primarily imperiled MPI everywhere.

**Trend 1.** As the serial throughput of a CPU has stagnated, vendors have increased the number of cores per processor over the last decade to achieve high aggregate computational throughput. This trend remains to continue on the upcoming exascale supercomputers (e.g., 64 cores on the Frontier exascale machine of the US) [6, 97]. An important aspect of this trend is that the processor's other resources, such as memory, have not increased proportionally to the increase in the number of cores. We can witness this trend even on the world's fastest supercomputer (as of November 2020), Fugaku, where the ratio of memory to core is less than one (48 cores with 32 GB RAM per node). The MPI everywhere model falters on today's many-core processors because of its high memory requirements [86]. In domain decomposition scenarios, for example, the halo regions of processes contain duplicated data, which increases with the increase in the domain's dimensionality. More important, the static split of resources with MPI everywhere on such many-core processors leads to inefficient resource usage because of resource wastage [106].

**Trend 2.** The second, more recent trend, has been the move towards heterogeneous computing environments through multiple accelerators per node. The Sierra and Summit

supercomputers, for example, feature 4 and 6 GPUs per node, respectively. More important, all the upcoming US exascale supercomputers—El Capitan, Frontier, and Aurora will feature multiple GPUs per node. To fully utilize the computational capability of a modern supercomputer, domain scientists must program both processors and GPUs, and hence cannot rely on using only MPI everywhere, that is, they must use a GPU programming model (e.g. CUDA) to utilize the massive parallelism within a GPU. Additionally, modern GPU-based distributed applications use MPI to utilize the GPU-level parallelism by using multiple processes to drive the multiple GPUs on the node [70, 63, 69, 28]. The MPI everywhere approach used in such distributed GPU-based applications, however, suffers from the same scaling problems resulting from trend 1.

### **1.2** The Problem with Modern Programming Models

To utilize the modern many-core processors in a scalable fashion, domain scientists have introduced a "new normal" in their programming model of choice: MPI+threads (e.g., MPI+OpenMP). In this approach, the user spawns a process per node or NUMA domain and a thread per core, enabling core-level parallelism through threads and node-level parallelism through MPI processes. The MPI+threads model is a better fit than MPI everywhere for modern processors that feature a decreased share of resources per core because it allows applications to efficiently share the processor's resources between cores. Additionally, it has lesser memory requirements—in the example of domain decomposition scenarios, MPI+threads eliminates the duplication of data on a node and reduces the amount of memory required by a factor of the number of threads compared to MPI everywhere. As a result, many applications that have ported their codes to use the MPI+threads programming model are able to scale to a large number of nodes on modern systems [35, 42]. Evidently, MPI+threads is a critical model to program the many-core

processors of exascale machines in a scalable fashion.

Although MPI+threads helps applications to scale, in practice, the MPI+threads version of an application tends to perform slower than the application's MPI everywhere counterpart [64, 38, 55]. MPI+threads programming includes many challenges over MPI everywhere. These include mitigating synchronization overheads of the shared-memory programming model [54, 88, 61], and preventing performance-degrading memory accesses (e.g., false-sharing effects). But the most important challenge is the dismal communication performance of an MPI+threads application that is most visible at the strong-scaling limit. The MPI+threads version of the hypre solver [29], for instance, spends 2.81× more time in MPI than does its corresponding MPI everywhere version. This drastically slow multithreaded MPI performance is also the reason why GPU-based applications use multiple processes instead of threads to drive the communication for distinct GPUs. The problem lies in the multithreaded issue of MPI communication operations from a single process.

State-of-the-art MPI libraries use conservative approaches, such as a global critical section, to maintain thread safety and MPI's ordering constraints which severely limit the overall performance of MPI+threads applications. Several research efforts aim to mitigate thread contention in the MPI library through fine-grained critical sections, software combining, and dedicated communication threads [31, 27, 26, 100], but such efforts do not improve the scalability of multithreaded communication performance. The root of this limiting communication performance scalability stems from an outdated view held by the supercomputing community: the network is a single device.

**Trend 3.** A trend that has been overlooked by the supercomputing community is the increase in network parallelism available on a single node of a supercomputer. The network interface cards (NICs) of modern interconnects, such as Nvidia-Mellanox InfiniBand and HPE Cray Slingshot, feature multiple network hardware contexts. These contexts serve as

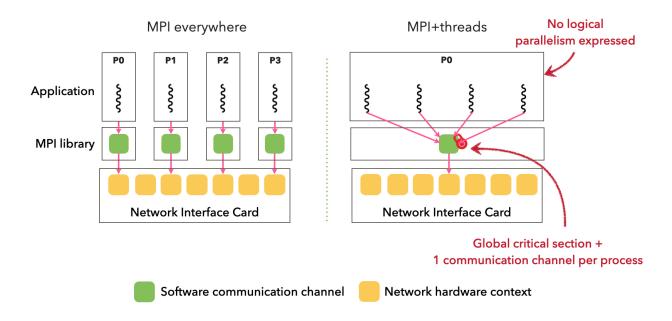

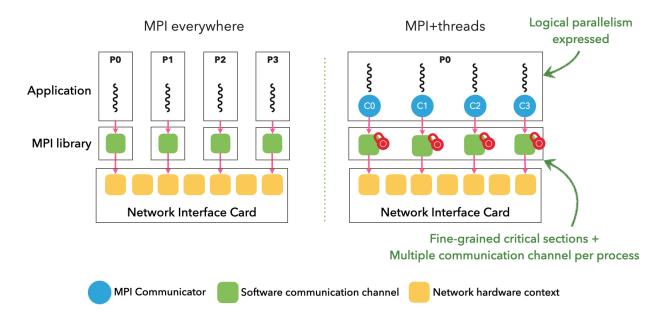

Figure 1.1: Network utilization in the state of the art.

parallel interfaces into the network from a single node. Looking forward, as we approach the physical limits of a single network link's throughput, the only way to increase the aggregate throughput from a node is through the use of multiple NICs, implying another dimension to network parallelism. The Summit supercomputer, for example, already features dual-rail Mellanox EDR InfiniBand on each of its nodes.

The outdated view does not hurt MPI everywhere applications because each MPI process transparently maps to a distinct network hardware context and utilizes the available network parallelism (see Figure 1.1). But the same outdated view hurts multithreaded MPI communication drastically—MPI libraries today map to only a single network hardware context and do not capitalize on the available network parallelism with MPI+threads. More important, domain scientists today do not do a good job exposing the independence between the MPI communication from multiple threads even though the existing MPI standard provides them with opportunities to do so.

## **1.3 Research Approach and Contributions**

To effectively utilize the available network parallelism in MPI+threads applications, domain scientists must expose the communication independence in their MPI+threads applications through *logically parallel communication*—operations that are not subject to MPI's ordering constraints. Only once applications expose such information can the MPI library map the logically parallel communication to the underlying network parallelism. Of course, this mapping is possible only when the MPI library establishes parallel communication channels and enables efficient multithreaded access to the library's software resources. Unlike the other challenges of MPI+threads programming that can be addressed by the application developer alone, the challenge of efficient multithreaded MPI communication requires efforts from the supercomputing community as a whole, as we can see in Figure 1.2.

To achieve the goal in Figure 1.2, this dissertation bridges the two ends of the HPC stack— MPI library developers and domain experts—that typically don't talk to each other di-

Figure 1.2: Goal of network utilization in MPI+threads matching that of MPI everywhere.

rectly. Only when both domain scientists and MPI developers take a step forward together can we observe a formidable impact on MPI+threads applications. We study each level of the HPC stack with a bottom-up approach and provide solutions for the problems at each level. This bottom-up approach was necessary since the MPI library sits in between the applications and network hardware. To accommodate the performance needs of an application, the MPI library first needs to be aware of the capabilities of modern hardware. Through collaborations with system researchers and MPI library developers, we make high-speed multithreaded MPI communication a reality. And through collaborations with application developers, we expose the applications' logically parallel communication to the fast MPI+threads library. Through both collaborations targeted to run on the upcoming exascale systems. To that end, this dissertation makes the following contributions.

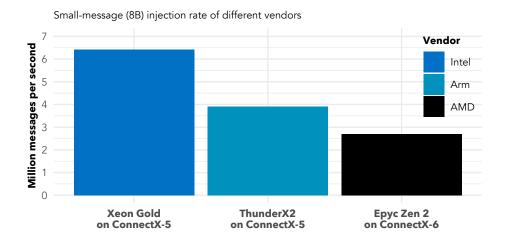

- 1. Analytical communication models. Motivated by the onset of new prominent vendors, such as Arm and AMD, in HPC, we discovered that the communication performance of the new vendors is slower than that of traditional vendors such as Intel. To guide the optimization efforts of system engineers in this regard, we provide models to analyze and generate a breakdown for a system's communication performance in Chapter 2. We provide a detailed measurement methodology to measure the time spent in each component so that researchers can analyze the communication performance of any system of their interest. This work is the first of its kind for an Arm-based server.

- 2. Modern network hardware capabilities. Creating multiple communication channels for MPI+threads requires understanding the performance capabilities of modern NICs with respect to multithreaded communication. Compared to an MPI everywhere environment, an MPI+threads environment allows cores to share re-

sources efficiently. In Chapter 3, we analyze the performance impact of sharing communication resources between threads and provide a resource-sharing model that captures the tradeoff space between communication throughput and resource efficiency.

- 3. A fast MPI+threads library. Using the lessons learned from our modeling studies, we establish parallel communication streams inside the MPI library and utilize the underlying network parallelism. Our designs do not sacrifice correctness for performance. Chapter 4 details how our designs yield MPI+threads communication performance similar to that of MPI everywhere. This work is the first to achieve scaling multithreaded communication throughput for both point-to-point and RMA operations without any extensions to the MPI standard.

- 4. Application case studies. Using our fast MPI+threads library, we showcase how applications can, through logically parallel communication, achieve not only high scalability, but also high performance with MPI+threads. In Chapter 5, we compare the performance differences of the different mechanisms—user-visible endpoints and existing MPI mechanisms—of exposing logical communication parallelism for three applications from different domains: Uintah (CFD), WOMBAT (astrophysics), and Legion (data-centric programming system) applications. Exposing logical communication parallelism can boost performance by up to 2×.

- 5. Listening to domain scientists. The end-users of designs that express logically parallel communication are domain scientists. Hence, it is imperative to pay attention to the concerns of the domain scientists with respect to each design. In Chapter 6, we summarize the opinions, thoughts and concerns that we have gathered from our collaborations with several domain scientists who represent different types of MPI+threads applications.

# Chapter 2

# **Analytical Models of Communication**

Internode communication is the crux of supercomputing. Modern supercomputers feature new vendors such as Arm, AMD, and Nvidia in addition to the traditional players such as Intel and IBM. How do the communication performances of non-traditional vendors fare? Figure 2.1 shows a performance comparison between three server-class CPUs from three different vendors for a communication-intensive microbenchmark on the same Mellanox InfiniBand network. An Intel core injects messages into the network  $2.38 \times$  faster than an AMD core and  $1.64 \times$  faster than an Arm-based core.

Figure 2.1: Communication performance comparison between HPC vendors.

While non-traditional vendors are better than traditional vendors at other aspects, such as memory bandwidth, they are not at par with existing machines with respect to communication performance. Finding the causes of slowdowns in communication performance is not an easy task since the critical path of communication involves all components of a system: CPU, I/O, and network. Blindly optimizing each component is impractical considering the technical challenges associated with each and the wide variety of use cases. How should system engineers then organize their optimization efforts? A detailed breakdown showing the contribution of each component to the overall communication performance of a system would provide system researchers and engineers with a holistic picture and guide their optimization efforts.

To break down high-performance communication, we study and develop analytical models for the injection overhead and end-to-end latency of a system. These models detail the time spent in all components of a system. Specifically, we focus on the communication performance of small messages because at the limits of strong scaling lies fine-grained communication of small messages. Moreover, modern networks feature optimized mechanisms for small-message communication. We use our models to break down the communication performance of a system of two Arm-based ThunderX2 servers interconnected with Mellanox InfiniBand. We choose to study an Arm-based server because the Arm architecture powers Fugaku, the fastest supercomputer in the world(as of November 2020), and we choose Mellanox InfiniBand since it occupies the highest interconnect performance share on the TOP500. This work is the first of its kind for an Arm-based server.

We learn from our study that CPU, I/O, and network components equally contribute to the communication performance of small messages; the times spent in each of the categories are on the same order of magnitude. Hence, optimizations of each category's constituents would be beneficial. This raises the question: *how much will optimizing component X improve the overall communication performance*? The answer to this question can

guide the research and engineering efforts for not just the Arm-based server but also of the HPC community at large. We answer this question through a what-if analysis of the impact of optimizations on the overall communication performance.

### 2.1 Background

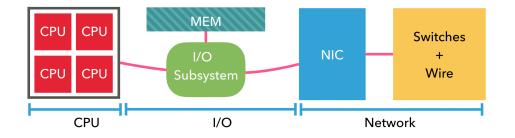

### 2.1.1 Communication Components

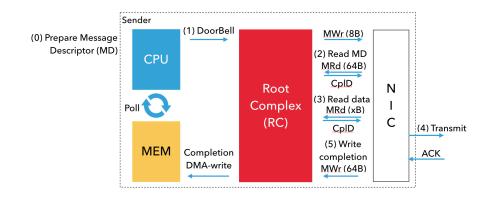

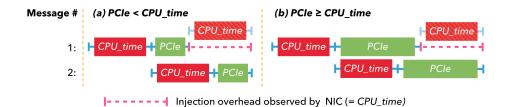

We can classify the various components involved in sending a message into one of three categories: CPU, I/O, or network fabric, as shown in Figure 2.2. Software stacks on the CPU include the Message Passing Interface (MPI) and the communication protocol processing in the underlying communication frameworks. I/O encompasses subsystems on the processor chip such as PCI Express (PCIe). Network components are the high-performance interconnects switches and physical wire. Each of these components on the critical path of communication poses an opportunity for optimization. Depending on the use case, however, the share of time spent in different components can vary. For example, the latency of sending a large message is driven by the time spent in the network components, in which case, optimizing the software stack would be a futile effort. On the other hand, the time spent in the software stack during the propagation of a small message is a considerable portion of the overall latency and, hence, optimizing the time spent in the

Figure 2.2: Components involved in the transmission of a message.

CPU would be beneficial. Therefore, it is important to understand where researchers and engineers should focus their optimization efforts.

### 2.1.2 PCIe Express

The Network Interface Cards (NICs) of modern interconnects are typically connected to the processor chip on the node as a PCI Express (PCIe) device. The main conductor of the PCIe subsystem is the Root Complex (RC). It connects the processor and memory to the PCIe fabric. The peripherals connected to the PCIe fabric are called PCIe endpoints. The PCIe protocol consists of three layers: the Transaction layer, the Data Link layer, and the Physical layer. The first, the upper-most layer, describes the type of transaction occurring. In this paper, two types of Transaction Layer Packets (TLPs) are relevant: MemoryWrite (MWr) and Memory Read (MRd). Unlike the standalone MWr TLP, the MRd TLP is coupled with a Completion with Data (CplD) transaction from the target PCIe endpoint which contains the data requested by the initiator. A MWr TLP is categorized as a *posted* transaction, meaning that the initiator of the TLP need not maintain any state regarding the transaction after issuing it. On the other hand, a MRd TLP is categorized as a non-posted transaction, meaning that the initiator will receive a Completion with Data (CplD) transaction from the target PCIe endpoint with the requested data. The Data Link layer ensures the successful execution of all transactions using Data Link Layer Packet (DLLP) acknowledgements (ACK/NACK) and a credit-based flow-control mechanism. An initiator can issue a transaction as long as it has enough credits for that transaction. Its credits are replenished when it receives Update Flow Control (UpdateFC) DLLPs from its neighbors. Such a flow-control mechanism allows the PCIe protocol to have multiple outstanding transactions.

### 2.1.3 Mechanisms of a High-Performance Interconnect

From a CPU programmer's perspective, there exists a *transmit queue* (TxQ) and a *completion queue* (CQ). The user posts their message descriptor (MD) to the transmit queue, after which they poll on the CQ to confirm the completion of the posted message. The user could also request to be notified with an interrupt regarding the completion. However, the polling approach is performance-oriented since there is no context switch to the kernel in the critical path. The actual transmission of a message over the network occurs through coordination between the processor chip and the NIC using memory mapped I/O (MMIO) and direct memory access (DMA) reads and writes. We describe these steps below using Figure 2.3.

- 0. The user first enqueues an MD into the TxQ. The network driver then prepares the device-specific MD that contains headers for the NIC, and a pointer to the payload.

- Using an 8-byte atomic write to a memory-mapped location, the CPU (the network driver) notifies the NIC that a message is ready to be sent. This is called *ringing the DoorBell*. The RC executes the *DoorBell* using a MWr PCIe transaction.

- 2. After the *DoorBell* ring, the NIC fetches the MD using a DMA read. A MRd PCIe transaction conducts the DMA read.

- 3. The NIC will then fetch the payload from a registered memory region using another DMA read (another MRd TLP). Note that the virtual address has to be translated to its physical address before the NIC can perform DMA-reads.

- 4. Once the NIC receives the payload, it transmits the read data over the network. Upon a successful transmission, the NIC receives an acknowledgment (ACK) from the target-NIC.

Figure 2.3: PCIe transactions and mechanisms on sender node to transmit data over wire.

5. Upon the reception of the ACK, the NIC will DMA-write (using a MWr TLP) a completion (64 bytes in Mellanox InfiniBand) to the CQ associated with the TxQ. The CPU will then poll for this completion to make progress.

In summary, the critical data path of each post entails one MMIO write, two DMA reads, and one DMA write. The DMA-reads translate to round-trip PCIe latencies which are expensive.

**Network optimizations for small messages.** A faster way to send a message that eliminates the PCIe round-trip latencies is *Programmed I/O (PIO)*. With PIO, the CPU copies the MD as a part of the *DoorBell*. Thus, the NIC doesn't need to DMA-read the MD. Another feature for small payloads is *inlining* which means that the payload is a part of the MD. Hence, when the NIC receives the MD, it does not need to DMA-read the payload. Typically, communication frameworks, such as UCX, combine PIO with inlining. This eliminates both the DMA-reads (steps (2) and (3)). In Mellanox InfiniBand, the PIO occurs in 64-byte chunks. Note that the CPU does more work in PIO (64-byte copy instead of an 8-byte write) and inlining (memcpy). However, the increase in CPU's work compared to the benefit gained from elimination of PCIe round-trip latencies is minimal.

## 2.2 Evaluation Setup

To measure the breakdown of time spent in communication components we use a system of two nodes, node 1 and node 2, that are connected to each other using a highperformance interconnect. Node 1 plays the role of the initiator in our following experiments. We use the CPU's timers to measure the time spent in software. To measure the time spent in other components, we use traces from a PCIe analyzer. Note that one can use this analysis infrastructure for any CPU or interconnect of interest.

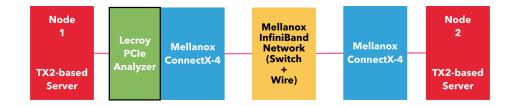

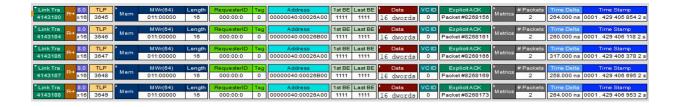

The nodes in our setup are ThunderX2-based (TX2) servers and are connected with the TOP500-popular Mellanox InfiniBand [24] high-speed interconnect. Specifically, we use ConnectX-4, a recent Mellanox InfiniBand adapter, and attach it to the node through a PCIe slot. A Lecroy PCIe analyzer sits just before the NIC on node 1, as shown in Figure 2.4. The overhead of the PCIe analyzer is negligible as we did not observe any difference in performance with and without it. Larsen et al. observe the same [67]. The analyzer is a passive instrument that allows data to pass through fully unaltered [19].

For our software stack, we use the CH4 device of MPICH [87] with Unified Communication (UCX) [93] as the underlying communication framework. Specifically, we use UCX's accelerated *rc\_x* transport which is UCX's implementation of the data-path operations, such as posting to the transmit queue and polling from the completion queue, for modern Mellanox InfiniBand adapters.

Figure 2.4: Two-node setup with PCIe analyzer on node 1.

## 2.3 Measurement Methodology