# **UC San Diego**

# **UC San Diego Electronic Theses and Dissertations**

### **Title**

Accelerating Data Movement at Different Granularities in Datacenters

### **Permalink**

https://escholarship.org/uc/item/2g60g8tf

### **Author**

Wang, Shu-Ting

### **Publication Date**

2024

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA SAN DIEGO

### **Accelerating Data Movement at Different Granularities in Datacenters**

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy

in

Computer Science

by

Shu-Ting Wang

### Committee in charge:

Professor Steven Swanson, Chair Professor George C. Papen Professor Geoffrey M. Voelker Professor Jishen Zhao

Copyright

Shu-Ting Wang, 2024

All rights reserved.

The dissertation of Shu-Ting Wang is approved, and it is acceptable in quality and form for publication on microfilm and electronically.

University of California San Diego

2024

## **DEDICATION**

To Olivia, my mother, and late father

### TABLE OF CONTENTS

| Dissertation A  | pprov                    | al Page                                                                          |                                                                                                                                                                                                   | iii                                                                        |

|-----------------|--------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Dedication      |                          |                                                                                  |                                                                                                                                                                                                   | iv                                                                         |

| Table of Conte  | ents .                   |                                                                                  |                                                                                                                                                                                                   | V                                                                          |

| List of Figures | ·                        |                                                                                  |                                                                                                                                                                                                   | /iii                                                                       |

| List of Tables  |                          |                                                                                  |                                                                                                                                                                                                   | хi                                                                         |

| Acknowledger    | nents                    |                                                                                  |                                                                                                                                                                                                   | xii                                                                        |

| Vita            |                          |                                                                                  |                                                                                                                                                                                                   | xiv                                                                        |

| Abstract of the | Disse                    | ertation                                                                         |                                                                                                                                                                                                   | ΧV                                                                         |

| Chapter 1       | Intro                    | duction                                                                          |                                                                                                                                                                                                   | 1                                                                          |

| Chapter 2       | Daro 2.1 2.2 2.3         | Backgr<br>2.1.1<br>2.1.2<br>Challer<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.2.5 | Microsecond load balancing at scale  Load knowledge  Stale information  Information traffic reduction  Heterogeneous rack configurations  on design  Microbursts  Packet flow  Logarithmic Gossip | 4<br>6<br>7<br>8<br>8<br>9<br>10<br>11<br>11<br>12<br>13<br>14<br>15<br>19 |

|                 | 2.4<br>2.5<br>2.6<br>2.7 | Implen<br>Evalua<br>2.5.1<br>2.5.2<br>2.5.3<br>2.5.4<br>2.5.5<br>Discus          | tion                                                                                                                                                                                              | 21<br>22<br>23<br>23<br>25<br>27<br>28<br>30<br>31                         |

|           | 2.8  | Conclusion                                        |

|-----------|------|---------------------------------------------------|

|           | 2.9  | Sources for Material Presented in This Chapter    |

| Chapter 3 | Fian | chetto: Accelerating Data Motion Across the Board |

| _         | 3.1  | Preliminaries and Motivation                      |

|           |      | 3.1.1 Data Restructuring Operations               |

|           |      | 3.1.2 Data Motion Overheads                       |

|           | 3.2  | Fianchetto: Accelerating the Data Motion          |

|           | 3.3  | DRX Placement                                     |

|           | 3.4  | Data Restructuring Accelerator (DRX) Design       |

|           |      | 3.4.1 Data Restructuring Characterization         |

|           |      | 3.4.2 DRX Hardware Architecture                   |

|           | 3.5  | System Integration and Programmability            |

|           | 3.6  | Experimental Methodology                          |

|           | 3.7  | Experimental Results                              |

|           |      | 3.7.1 End-to-end Performance Improvement          |

|           |      | 3.7.2 DRX Placement Analysis 61                   |

|           |      | 3.7.3 Sensitivity Studies                         |

|           | 3.8  | Related Work                                      |

|           | 3.9  | Conclusion                                        |

|           | 3.10 | Sources for Material Presented in This Chapter    |

| Chapter 4 | Aure | elia: Scalable CXL fabric                         |

| 1         | 4.1  | Motivation and Background                         |

|           |      | 4.1.1 What is Different with CXL Fabric?          |

|           |      | 4.1.2 Use Cases of CXL Fabric                     |

|           | 4.2  | Challenges                                        |

|           |      | 4.2.1 Addressing and Routing Challenges           |

|           |      | 4.2.2 Transport-level Challenges                  |

|           | 4.3  | Design of Aurelia                                 |

|           |      | 4.3.1 Addressing & Flow                           |

|           |      | 4.3.2 Routing                                     |

|           |      | 4.3.3 End-to-end Congestion Control 85            |

|           | 4.4  | Evaluation of Aurelia's Design                    |

|           |      | 4.4.1 Packet-level Simulation using ns-3          |

|           |      | 4.4.2 Simulation of Large Model Inference 89      |

|           |      | 4.4.3 Simulation Results on YCSB Benchmarks 90    |

|           | 4.5  | Discussion                                        |

|           | 4.6  | Conclusion                                        |

|           | 4.7  | Sources for Material Presented in This Chapter    |

| Chapter 5    | Conclusion | <br> |  | • | • | <br> |  |  | <br>• | • |  | • | • |  | • |  | • | 95 |

|--------------|------------|------|--|---|---|------|--|--|-------|---|--|---|---|--|---|--|---|----|

| Bibliography |            | <br> |  |   |   | <br> |  |  | <br>  |   |  |   |   |  |   |  |   | 97 |

### LIST OF FIGURES

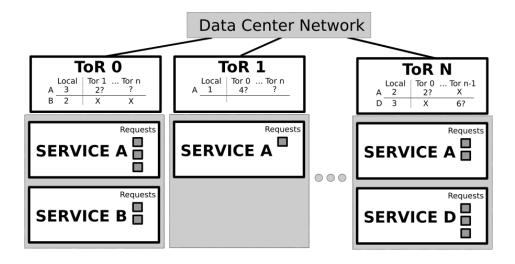

| Figure 2.1: | High-level overview of Daronpon. Each ToR tracks outstanding request for services running in its rack, and maintains approximate counters for remote ToRs hosting shared replicated services               | 13 |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

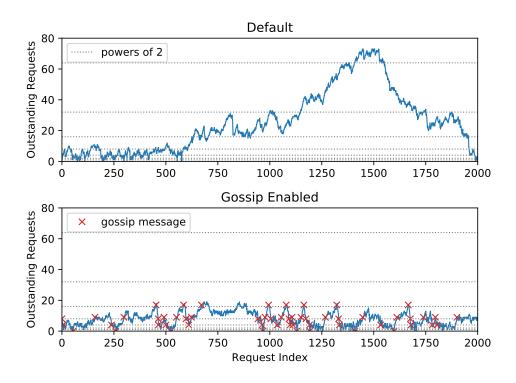

| Figure 2.2: | Microburst with no mitigation (top) vs. with logarithmic gossip load balancing enabled (bottom)                                                                                                            | 15 |

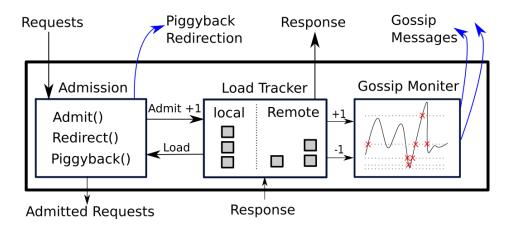

| Figure 2.3: | Key functionality and message flow of Daronpon                                                                                                                                                             | 16 |

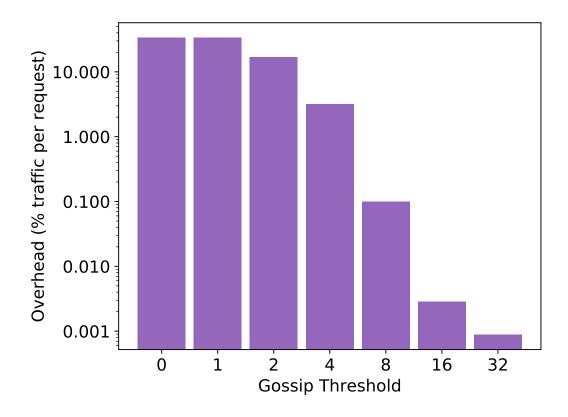

| Figure 2.4: | The percentage of gossip messages generated by a logarithmic gossip mechanism as a percentage of overall traffic. Collected from runs of 96 KRPS                                                           | 17 |

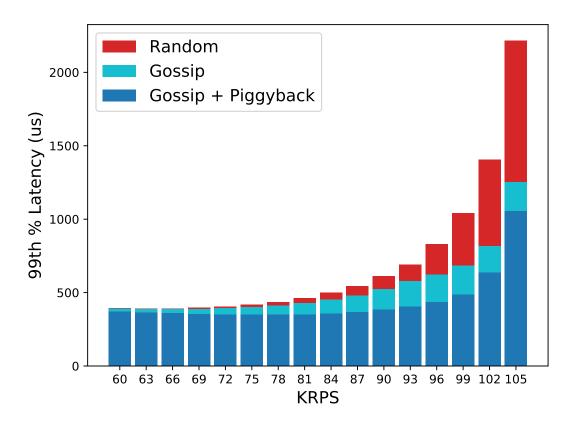

| Figure 2.5: | Performance breakdown of gossip and piggyback mechanisms. Lower values are better.                                                                                                                         | 20 |

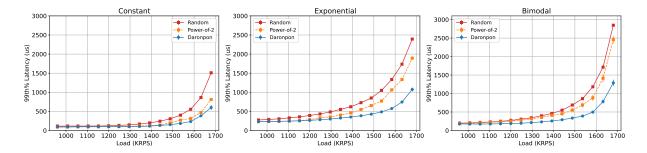

| Figure 2.6: | 99th percentile latency improvements on three common service distributions (Constant, Bimodal, Exponential). Each server is provisioned with homogeneous processing power.                                 | 25 |

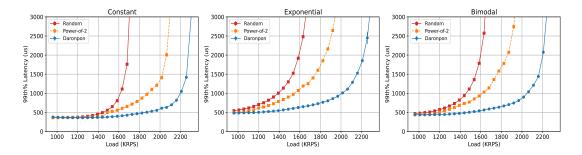

| Figure 2.7: | Throughput and latency improvements with skewed processing capacity in a heterogeneous server configuration. Daronpon scales linearly with with the aggregate processing capacity available                | 27 |

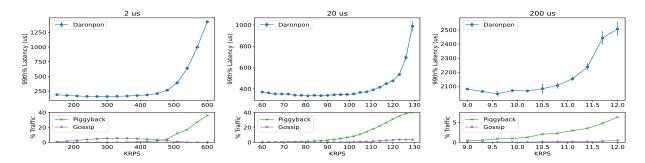

| Figure 2.8: | Service times across three orders of magnitude (2us, 20us, 200us). Daronpon provides relative improvements with similar overheads in terms of piggyback and gossip messages at each service time.          | 28 |

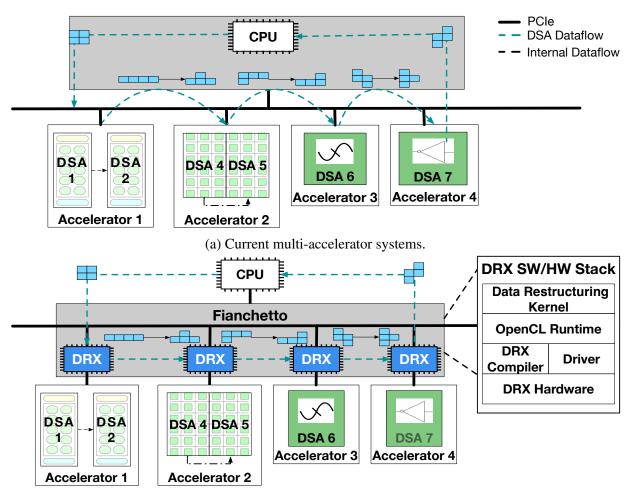

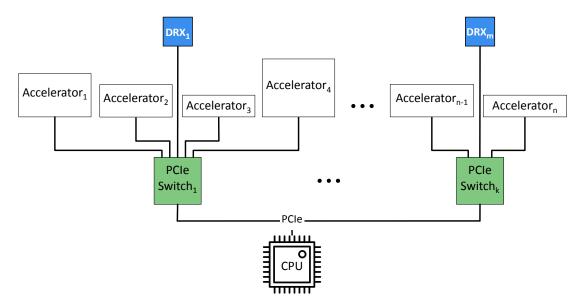

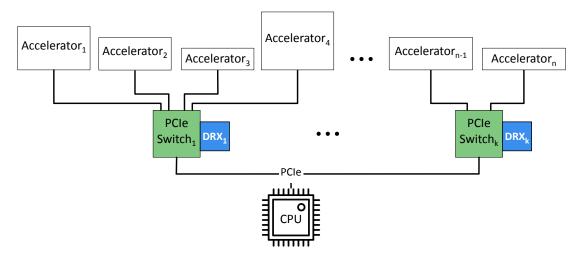

| Figure 3.1: | Current multi-acceleration systems rely on CPU for accelerator chaining                                                                                                                                    | 34 |

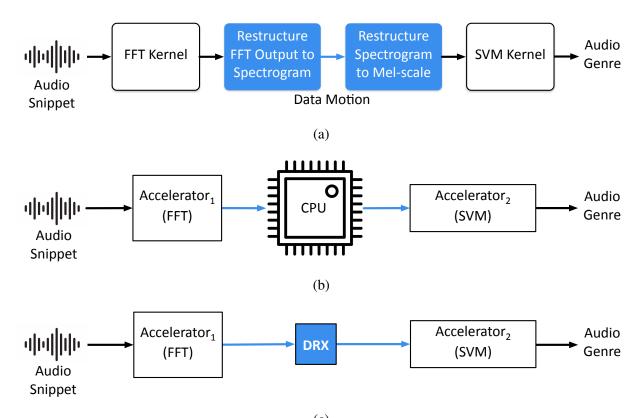

| Figure 3.2: | Data motion stands between two application kernels, i.e., Fast Fourier Transform and Support Vector Machine, of an end-to-end application                                                                  | 38 |

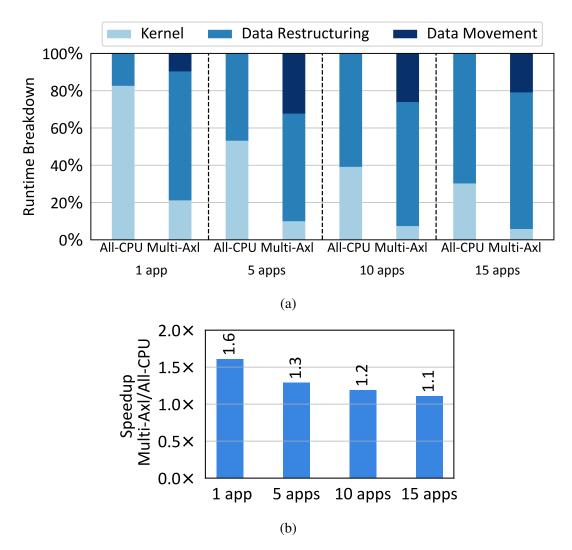

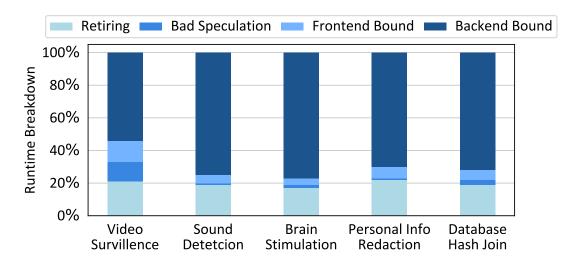

| Figure 3.3: | (a) Runtime breakdown when running applications on CPU or multiple accelerator setup that uses CPU for data motion. (b) Multi-acceleration speedup and scalability are constrained by data motion overhead | 39 |

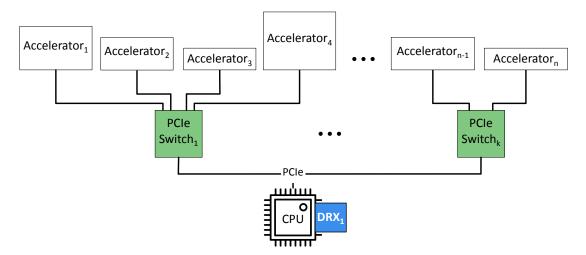

| Figure 3.4: | Integrated DRX                                                                                                                                                                                             | 43 |

| Figure 3.5: | Standalone DRX. Number of DRX units in Standalone placement is configurable, and the illustration represents just one possible configuration                                                               | 44 |

| Figure 3.6:  | PCIe-Integrated DRX                                                                                                                                                                                                         | 45 |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

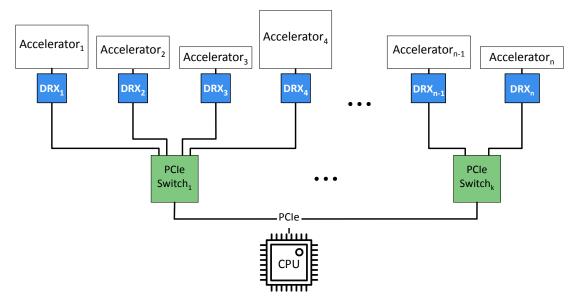

| Figure 3.7:  | Bump-in-the-Wire DRX                                                                                                                                                                                                        | 45 |

| Figure 3.8:  | Top-down breakdown of stall cycles for data restructuring operations                                                                                                                                                        | 46 |

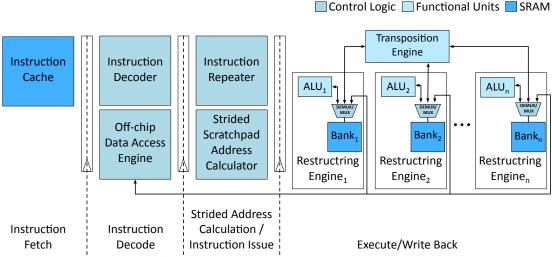

| Figure 3.9:  | DRX Hardware Architecture                                                                                                                                                                                                   | 49 |

| Figure 3.10: | DRX instruction types                                                                                                                                                                                                       | 49 |

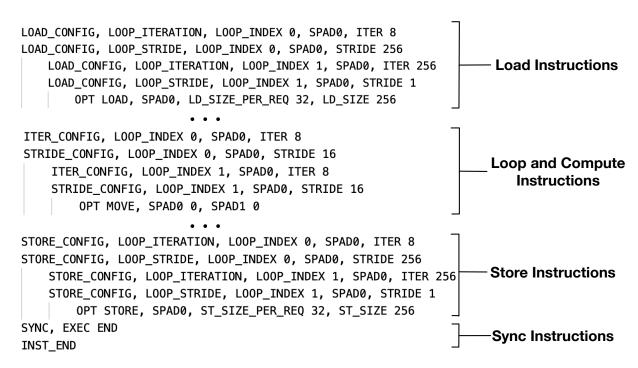

| Figure 3.11: | Sample DRX kernel                                                                                                                                                                                                           | 52 |

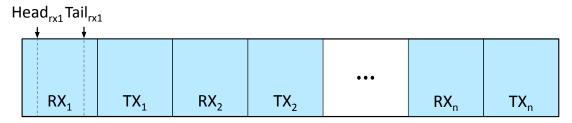

| Figure 3.12: | RX/TX data queue pair architecture in Bump-in-the-Wire DRX                                                                                                                                                                  | 52 |

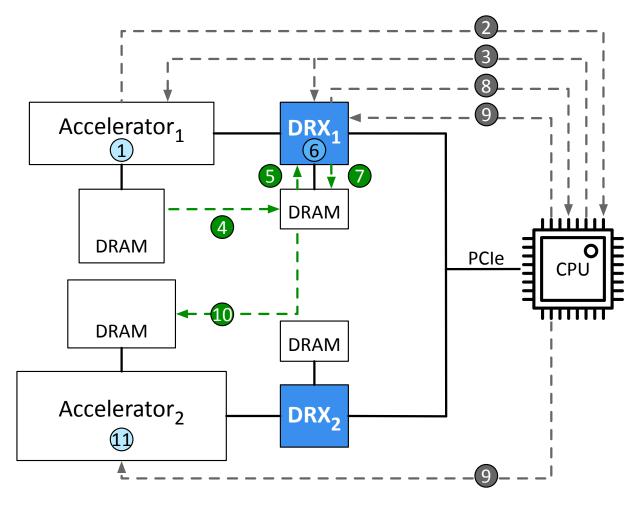

| Figure 3.13: | Point-to-point DMA workflow involves two accelerators and the sending side DRX                                                                                                                                              | 53 |

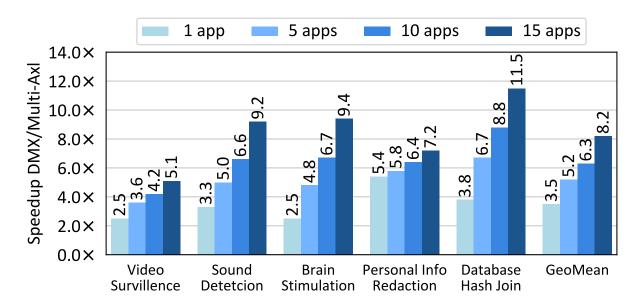

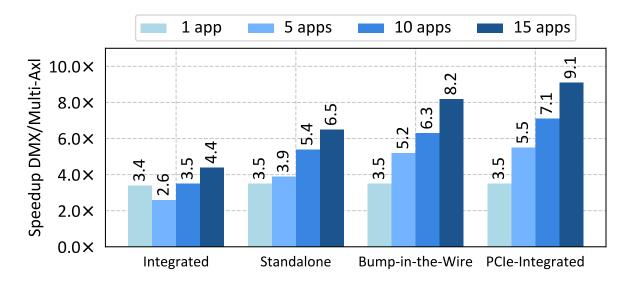

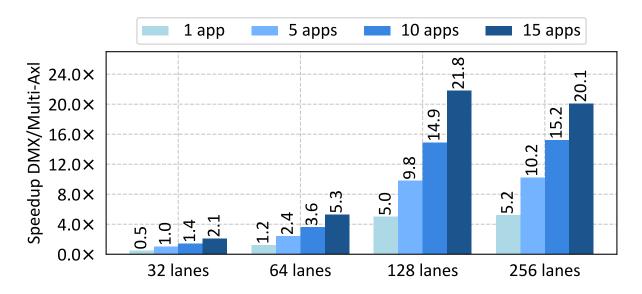

| Figure 3.14: | Fianchetto speedup over <i>Multi-Axl</i> configuration that uses CPU for data motion between accelerators. Fianchetto performance scales with the number of concurrent applications by using Bump-in-the-Wire DRX placement | 58 |

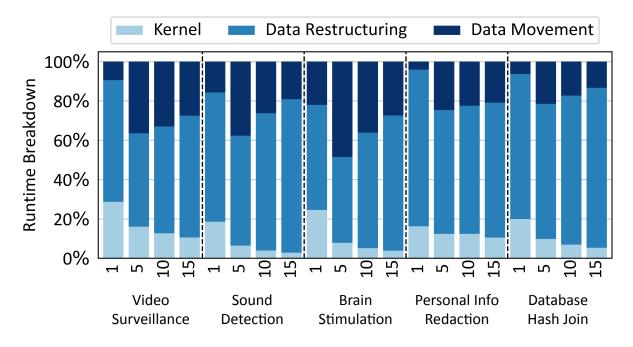

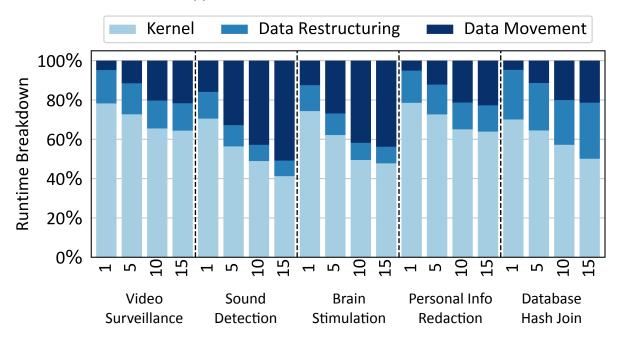

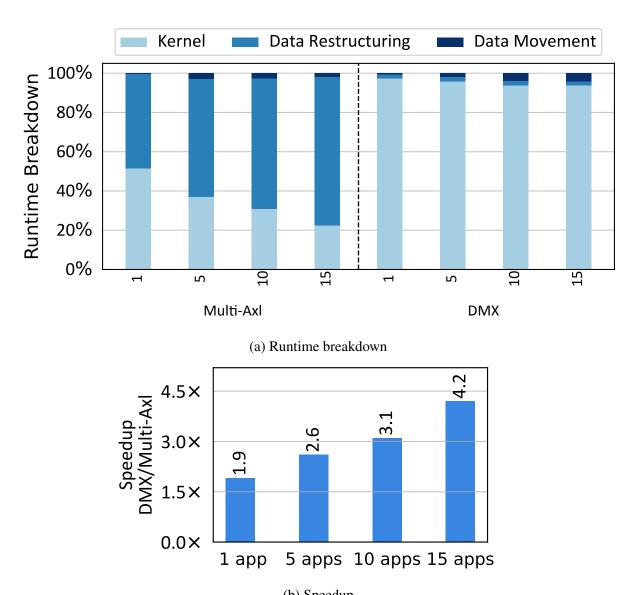

| Figure 3.15: | The latency breakdown of the <i>Multi-Axl</i> baseline and Fianchetto. Fianchetto shrinks data restructuring ratio from 64.1% to 14.1% in average                                                                           | 59 |

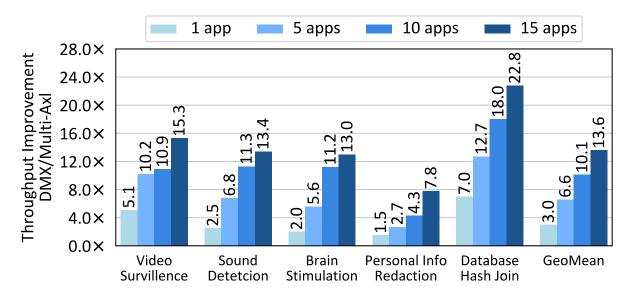

| Figure 3.16: | Fianchetto throughput improvement over <i>Multi-Axl</i> . Fianchetto resolves the throughput bottleneck of data restructuring and shifts the throughput bottleneck to the accelerated kernel                                | 60 |

| Figure 3.17: | Comparison of end-to-end latency speedup with different DRX placements.                                                                                                                                                     | 62 |

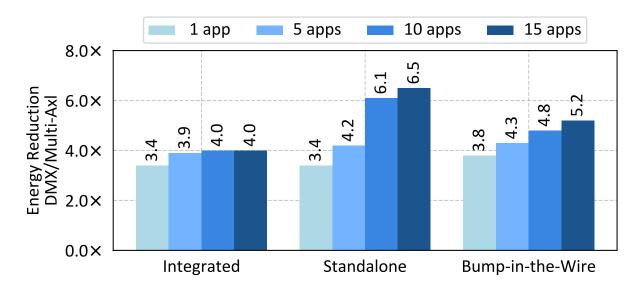

| Figure 3.18: | System-wide energy reduction, including host CPU cores, accelerators, and DRXs                                                                                                                                              | 63 |

| Figure 3.19: | Fianchetto reduces data motion overhead to less than 5% for Personal Info Redaction benchmark extended with Named Entity Recognition kernel                                                                                 | 65 |

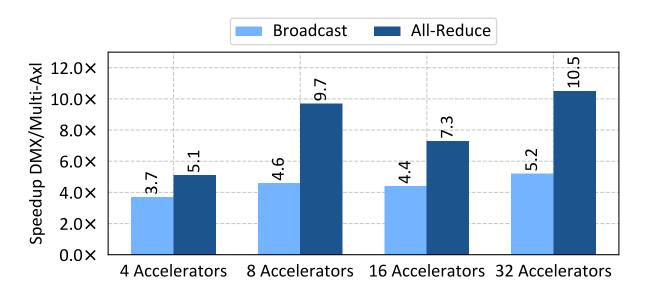

| Figure 3.20: | Fianchetto eliminates redundant DMA transfers and performs DMA in parallel for broadcast and all-reduce on multi-accelerator setup                                                                                          | 67 |

| Figure 3.21: | Data restructuring latency speedup with different numbers of RE lanes on DRX. The increase of speedup is limited after 128 lanes. which is our default configuration.                                                       | 67 |

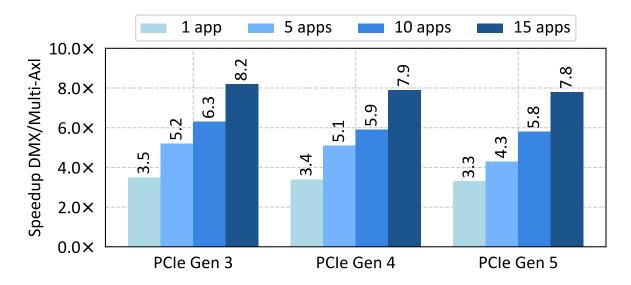

| Figure 3.22: | Fianchetto speedup across generations of PCIe. PCIe Gen4 and Gen5 result in a slight decrease of speedup because their corresponding <i>Multi-Axl</i> baselines improve more than their Fianchetto counterparts | 68 |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

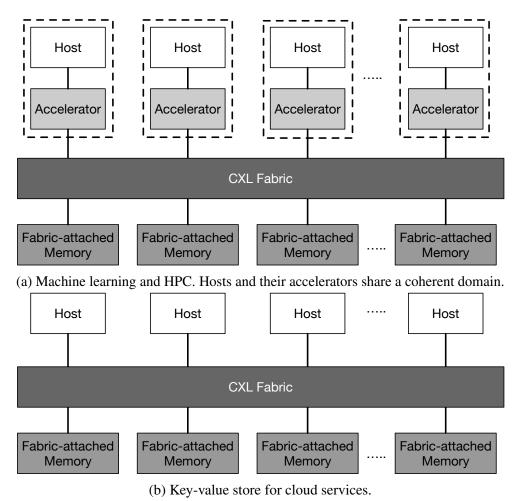

| Figure 4.1:  | CXL fabric abstractive topology. Each solid line connecting to CXL fabric is 16 lanes of PCIe 5 or PCIe 6 with a total bandwidth of 128 GB/s or 256 GB/s.                                                       | 77 |

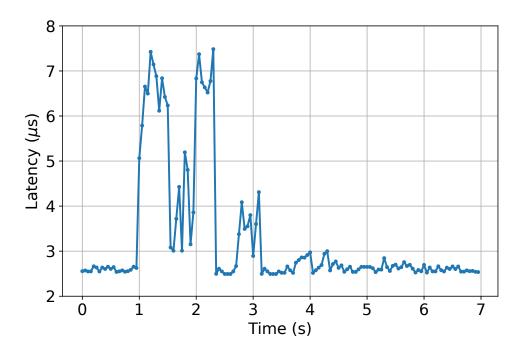

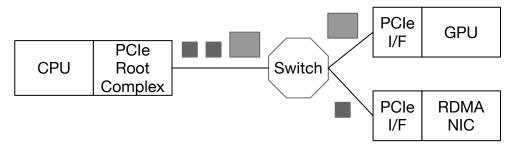

| Figure 4.2:  | Congestion on a shared PCIe switch port causes latency spikes of RDMA writes going through the port.                                                                                                            | 79 |

| Figure 4.3:  | Experimental setup for PCIe congestion                                                                                                                                                                          | 80 |

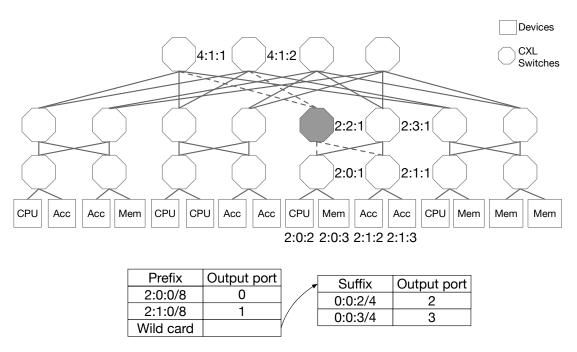

| Figure 4.4:  | CXL fabric as a fat-tree using 12-bit FAN-ID address <i>X:Y:Z</i> , which X, Y, and Z are hexadecimal values. Dash lines represent the routes from switch 2:2:1's routing table                                 | 82 |

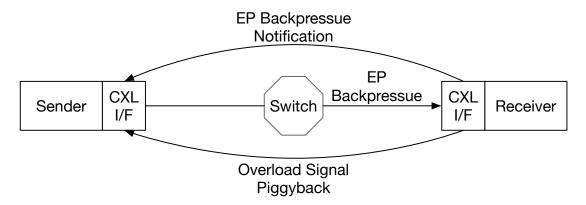

| Figure 4.5:  | Aurelia uses EP Backpressure notification to resolve congestions and overload signal for flow control to avoid overrunning the buffer on the device                                                             | 84 |

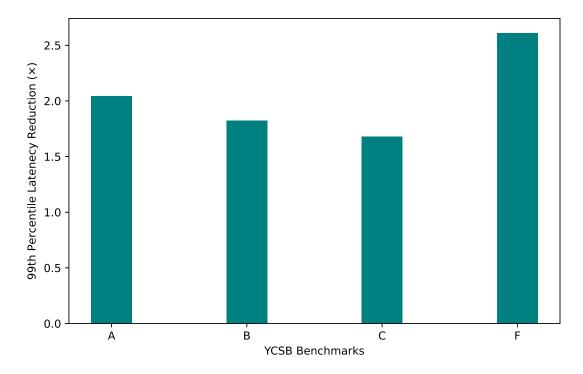

| Figure 4.6:  | YCSB benchmarks with higher ratio of writes demonstrate more improvement.                                                                                                                                       | 91 |

### LIST OF TABLES

| Table 3.1: | End-to-end benchmarks | 54 |

|------------|-----------------------|----|

|            |                       |    |

|            |                       |    |

|            |                       |    |

|            |                       |    |

|            |                       |    |

#### **ACKNOWLEDGEMENTS**

I want to thank Olivia, my significant other and soon-to-be lifelong partner, for supporting me through my PhD journey. It is a wild ride and thank you to be always on my side.

I want to thank all faculty members who invested their time mentoring me, Prof. George Porter for the first four years of advising that significantly shapes my taste and capability to do research, Prof. Steve Swanson for chairing my committee and giving me the last push to finish the dissertation, Prof. Geoff Voelker for being on my committee and his wonderful operating system class, Prof. George Papen for being on my committee and his insights on networking and optics, Prof. Alex Snoeren on all the critiques on my figures during weekly meetings, and Prof. Jishen Zhao for being willing to serve on my committee.

To Rajdeep, Yibo, Nishant, Stew, Audrey, Anil, Ariana, Alex, and all other tenants of room 3140, thanks for hanging out with me and being my friends. The camaraderie is invaluable, and I will bear that in mind when I embark on my next journey.

To Rohan, Byung Hoon, and Amin, thanks for all the long talks and chats about research and the time of questioning of our life choices while still working on research.

To Pierre-Louis, Weitao, and Dan, thanks for sharing my research interest on CXL and other topics. I really enjoy all the online chats and meetings and the idea of I am not in this alone pushes me to finish the last chapter of this dissertation.

To Dr. Yiting Xia, Jialong, Yiming, and Federico, thanks for hosting me at MPI-INF in Saarbrücken while I am working on this dissertation.

To Fujimak, SmallGGRen, HakkaFish and StanfordSneaky, I really enjoy our time on Mario cart racing and chatting about lives and politics. I will keep your real names in private in case other people scoop you folks from me.

I want to thank Yin Chin Foundation for their scholarship helping me for conference travel and supporting myself during finical instable times.

Coffee as the fuel for any research output is essential. I want to thank the great coffee

shops and roasters in San Diego: Bird Rock coffee, the Art of Espresso, and Finjin.

At last, I want to thank all my collaborators and co-authors, who are listed next. Chapter 2, in part, reprints material as it appears in a draft titled: "Daronpon: Datacenter-scale Sub-RTT Replica Selection for Low-latency Applications" by Shu-Ting Wang, Stewart Grant, Keerthana Ganesan, George Porter, and Alex C. Snoeren. The dissertation author was the primary researcher and author of this material.

Chapter 3, in part, reprints material as it appears in a paper titled: "Data Motion Acceleration: Chaining Cross-Domain Multi Accelerators" by Shu-Ting Wang, Hanyang Xu, Amin Mamandipoor, Rohan Mahapatra, Byung Hoon Ahn, Soroush Ghodrati, Krishnan Kailas, Mohammad Alian, and Hadi Esmaeilzadeh [WXM<sup>+</sup>24]. The dissertation author was the primary researcher and author of this material.

Chapter 4, in part, reprints material as it appears in a published WORD'23 workshoppaper titled: "Aurelia: CXL Fabric with Tentacle" by Shu-Ting Wang and Weitao Wang [WW23]. The dissertation author was the primary researcher and author of this material.

#### **VITA**

| 2013      | B. S. in Computer Science, National Tsing Hua University, Taiwan                        |

|-----------|-----------------------------------------------------------------------------------------|

| 2015      | M. S. in Computer Science, National Tsing Hua University, Taiwan                        |

| 2016      | Information System Technician, Civil Service Training and Protection Commission, Taiwan |

| 2017      | Research Assistant, National Taiwan University, Taiwan                                  |

| 2021      | Hardware Systems Foundation Engineer Intern, Meta                                       |

| 2024      | Visiting Ph. D. student, Max Planck Institute for Informatics, Germany                  |

| 2017-2024 | Ph. D. in Computer Science, University of California San Diego                          |

#### **PUBLICATIONS**

Rohan Mahapatra, Soroush Ghodrati, Byung Hoon Ahn, Sean Kinzer, **Shu-Ting Wang**, Hanyang Xu, Lavanya Karthikeyan, Hardik Sharma, Amir Yazdanbakhsh, Mohammad Alian, Hadi Esmaeilzadeh, "In-Storage Domain-Specific Acceleration for Serverless Computing" in Proceedings of the 29th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, Volume 2 (ASPLOS), 2024

**Shu-Ting Wang**, Hanyang Xu, Amin Mamandipoor, Rohan Mahapatra, Byung Hoon Ahn, Soroush Ghodrati, Krishnan Kailas, Mohammad Alian, and Hadi Esmaeilzadeh, "Data Motion Acceleration: Chaining Cross-Domain Multi Accelerators" in Proceedings of 2024 IEEE International Symposium on High-Performance Computer Architecture (HPCA), 2024

**Shu-Ting Wang** and Weitao Wang, "Aurelia: CXL Fabric with Tentacle," in Proceedings of the 4th Workshop on Resource Disaggregation and Serverless (WORDS), 2023

Rohan Mahapatra, Byung Hoon Ahn, **Shu-Ting Wang**, Hanyang Xu, and Hadi Esmaeilzadeh, "Exploring Efficient ML-based Scheduler for Microservices in Heterogeneous Clusters," in Proceedings of 2022 MLArchSys Workshop, 2022

#### ABSTRACT OF THE DISSERTATION

### **Accelerating Data Movement at Different Granularities in Datacenters**

by

Shu-Ting Wang

Doctor of Philosophy in Computer Science

University of California San Diego, 2024

Professor Steven Swanson, Chair

The dissertation investigates redundant communication between servers for large-scale web and cache requests and redundant data movement between accelerators for compute-intensive applications. Redundancy is an impending and critical issue for data centers designed for hardware accelerators and disaggregated resources. The dissertation makes the following three contributions to address this. The first contribution of the dissertation is Daronpon. Daronpon dynamically load-balances and reroutes large-scale requests of web and cache applications on a microsecond timescale. Daronpon prevents these requests, stranded on busy servers with network congestion and long queuing delays, from being processed. Daronpon shows improvement in various service time characterizations of different applications. The second contribution of the

dissertation is Fianchetto. Fianchetto acts as a compute-enabled bypass for inter-accelerator communication. Fianchetto accelerates the data restructuring needed between accelerators and saves the data movement between accelerators and CPUs for compute-intensive applications. Fianchetto shows improvement in a series of benchmarks involving different application domains. The third contribution of the dissertation is Aurelia. Aurelia leverages the emerging interconnect of CXL to investigate the design of a scalable fabric for accelerators and fabric-attached memory expansion. Aurelia improves routing and transport based on the current specification of CXL and shows performance improvement on machine learning and key-value store applications.

# Chapter 1

# Introduction

Modern datacenters are warehouse-scale computers [BCH13]. These warehouse-scale computers serve as the foundation of cloud computing, e.g. IaaS, SaaS, and serverless. They host commodity servers equipped with many general-purpose CPU cores. The servers are interconnected with 100 Gbps or faster network connections. They are clustered into fleets for different functions. For example, one serve the web requests, another one serve as data storage, and the other one serve as an in-memory cache for frequently accessed objects. Communication and data movement between servers are frequent and demonstrate diverse patterns depending on the mix of traffic from different functions [NFG<sup>+</sup>, KDH<sup>+</sup>15, HBB<sup>+</sup>18, azu].

Moreover, hardware accelerators are introduced into the datacenters for compute-intensive applications because of the effective end of Dennard scaling [DGR<sup>+</sup>74] and the dark silicon phenomenon [EBA<sup>+</sup>11, HFFA11]. These accelerators include GPUs, TPUs, video codec accelerators, and other accelerators deployed in the production datacenters nowadays [JYP<sup>+</sup>17, RSC<sup>+</sup>21, KDH<sup>+</sup>15, awsb, awsa]. The introduction of these accelerators demonstrates a monumental shift towards a heterogeneous hardware landscape beyond a massive number of homogenous CPU cores. The accelerators accelerate specific compute-intensive workloads, such as video encoding and decoding, scientific computation, and large-scale machine learning applications. They are

integrated with the system and operate on data moved from the host memory and return the results to it. Thus, efficient data movement ensures that these dedicated accelerators are well-utilized.

In addition to the heterogeneous hardware landscape, resource disaggregation aims at efficient resource provision in the datacenters. Resource disaggregation allocates resources, such as CPU cores, memory capacity, and storage capacity, located on different physical machines in a logically unified manner [SHCZ18, ABAL+20, MC20, RSAB20, ZWL+22, LMC+22]. The rationale behind disaggregation is to satisfy users with diverse requests for different resources. Disaggregation, while aiming at efficient provision of resources, exposes the communication and data movement between CPU and memory/devices through a network fabric connecting the resources [CIP+21, Sha23, MWD+23, LBN+23, WW23]. The externalized communication and data movement motivate the need for a scalable network fabric to serve a resource-disaggregated datacenter.

The current datacenters demonstrate diverse communication and data movement patterns on different scales with their corresponding applications. We are, in particular, interested in the data movement of the following scenarios:

- 1. RPC communication for web and cache applications. The data movement is on the scale of a few packets to a few MBs in total size.

- 2. Compute-intensive applications with the use of non cache-coherent accelerators. The data movement is with chunks of data on the scale of up to 100s of MBs.

- 3. Key-value store on disaggregated memory modules. The data movement operates on cacheline granularity to KBs in total size.

In short, we hypothesize that the conventional design of control and data plane demonstrating inefficient communication and redundant data movement between servers for large scale web/cache requests and between accelerators for compute-intensive applications. We argue that this inefficiency is an impending and critical issue for datacenters designed for hardware accelerators and disaggregated resources. This thesis proposes to intelligently redirect the communication and

| data movement to bypass congestion and reduce redundant movement with a minimal addition | of |

|------------------------------------------------------------------------------------------|----|

| control logic.                                                                           |    |

|                                                                                          |    |

# Chapter 2

# **Daronpon: Datacenter Load Balancing**

# **Across Racks**

To improve both performance and fault tolerance, datacenter applications are provisioned to scale horizontally, with replicated instances frequently spread across multiple racks of servers. These replicas must be carefully managed to meet strict service-level objectives (SLOs) for both throughput and latency [BMPR17, DB]. These requirements have birthed an architectural paradigm of highly replicated microservices that can (nearly) arbitrarily fan out to deliver everhigher throughput, and whose functionality is scoped to provide microsecond-timescale responses with low latency even in the tail.

Realizing this design pattern in practice poses multiple engineering challenges, however. Microsecond-timescale services must be resilient to low-level system and network perturbations and short-lived congestion events to achieve consistent performance [ZLZK]. These events arise within the operating system, runtime, and application software as well as due to network-level incast events, where many clients send to a common destination server, causing in-network buffering and substantial queuing delays [NFG<sup>+</sup>13]. Moreover, the potential impact of these so-called "microbursts" increases with network bandwidth. Large bursts can lead to packet drops

and necessitate end-to-end retransmissions.

Experience shows that a responsive and effective load-balancing strategy is key to managing overall service latency. Given the ultra-low service times of many modern datacenter services, end-to-end approaches driven by the clients and servers themselves are unlikely to meet demands, as many component services (i.e., computation) times are smaller than datacenter-wide network latencies. Instead, we focus on in-network load balancing techniques carried out by network switches or middle boxes—often generally referred to as *dispatchers*. Recent work has shown the benefits of load balancing with a server rack, for example R2P2 [KPG<sup>+</sup>] and Racksched [ZKC<sup>+</sup>]. These approaches take into account server load balancing, building upon prior approaches to core scheduling in individual servers [BPP<sup>+</sup>16, KCH<sup>+</sup>19, OFB<sup>+</sup>19, WCB]. Further, Vargaftik et al. [VKO20] show that, for the multiple-dispatcher environments that we target, a stable and highly efficient load balancing approach is possible through a carefully controlled exchange of status updates between servers and dispatchers.

We present Daronpon, an inter-rack load balancer targeting services with round-trip time dominating the overall response time and service time on microsecond timescales. Daronpon periodically exchanges service-load information between dispatchers, either through explicit gossip messages or piggybacked onto redirected application requests. We employ a logarithmic threshold approach to minimize the network overhead of state-exchange messages while ensuring that application requests are forwarded to replicas with good performance. Our system decreases the 99th-percentile tail latency by up to a factor of two over random replica selection across a variety of workloads, enables scaling across heterogeneous server configurations, and provides performance gains for service times as low as two microseconds. <sup>1</sup>

<sup>&</sup>lt;sup>1</sup>Services are assumed to be replicated throughout Chapter 2, thus replica and services are used interchangeable.

# 2.1 Background

Modern datacenter applications are replicated [roc21, Mem21, Mon21] to provide fault tolerance, scalability and flexible response to load fluctuations. Often, individual application components are replicated on the order of three times for fault tolerance. In the case of sharding for scalability, however, the number of replicas can be many orders of magnitude higher and even grow dynamically [fac20, AMH<sup>+</sup>, KXH<sup>+</sup>] as needed to service demand.

## 2.1.1 Datacenter load balancing

Traditional application or *layer-4* load balancers operate across the set of back-end services and maintain connection consistency for long-lived flows. They are generally implemented in software using commodity servers [BTY<sup>+</sup>, EYC<sup>+</sup>, OAVR, PBY<sup>+</sup>], although some have explored using switches with hardware support [GLH<sup>+</sup>, MZK<sup>+</sup>]. While effective at responding to end-host-driven load imbalances, they are ill-positioned to address transient variations in service times.

Conversely, conventional *layer-3* load-balancing techniques focus on dispersing traffic load in the network, and do not address server imbalance. For example, equal-cost multi-path routing (ECMP) load balances flows using a hash of their 5-tuple. ECMP is widely deployed due to the benefits it gains from average-case statistical multiplexing. It is well known, however, to cause load imbalance due to hash collisions and when links fail. A variety of improvements to ECMP have been proposed, many using the concept of flowlets [AED<sup>+</sup>, KGH<sup>+</sup>, KHK<sup>+</sup>, VPA<sup>+</sup>]: a group of packets within the same flow separated from others by a large enough time interval. Other schemes load balance per packet [GYG<sup>+</sup>, KVHD, ZZB<sup>+</sup>]. Each of these in-network techniques are complementary to our work, as they load balance exclusively based on the state of the network and not the end-host applications.

### 2.1.2 Microsecond timescales

Despite practitioners' attempts to spread demand evenly across both servers and network fabrics [RZB<sup>+</sup>], a certain degree of variability is inevitable. Indeed, as links speeds of 100 and 400-Gbps become the norm, hosts and switches can experience significant traffic bursts over short periods of time. These bursts, while lasting only a few microseconds, can cause congestion, lead to increased jitter, and result in packet drops [ZLZK]. As a concrete example, a switch with 64 MB of packet memory will overflow in 1.9 ms at 100 Gbps [tof20] under incast scenarios. While these events originate in the network, the effect of that queuing cascades at the application. Congestion impacts performance directly as batches of requests are delivered in very short time periods. Existing end-to-end techniques struggle to react to microbursts effectively as the durations of the microbursts are shorter than the network RTT which bounds the response time of any end-host approach.

Daronpon targets microsecond-timescale services which do not involve long-lived connections. (We support any request/response service on top of a connection-less transport or one with migration ability [KIB, LRW<sup>+</sup>].) Techniques for dispatching such microsecond-duration requests within an end-host operating system have been explored recently [BPP<sup>+</sup>16, KCH<sup>+</sup>19, MdKA<sup>+</sup>19, OFB<sup>+</sup>19, PKB]. These end-host-based approaches use load-aware schedulers to direct requests to CPU cores and to quickly rebalance those allocations. Extensions to these techniques demonstrate similar scheduling performance at the scope of a entire server racks [KPG<sup>+</sup>, ZKC<sup>+</sup>]. These efforts make use of programmable switches to track end-host load at the rate of millions of requests per second [tof20]. Both R2P2 [KPG<sup>+</sup>] and Racksched [ZKC<sup>+</sup>] are confined to services which operate entirely within a single rack due to a single control point within the ToR switch. This limits the applicability of these schemes for the majority of replicated applications which are distributed throughout the datacenter.

Researchers have also explored explicitly integrating different replication techniques with programmable switching hardware to avoid RTT delays, including chain replication [JLZ<sup>+</sup>],

Raft [KB], and Paxos [LMS<sup>+</sup>]. In-network replication techniques have also been proposed to alleviate read/write conflicts [ZBL<sup>+</sup>19] and contention [LNM<sup>+</sup>]. Daronpon operates under the assumption that replicas are interchangeable for all requests; our techniques could be extended to support any of these protocols, however Daronpon would require protocol-specific information to operate.

# 2.2 Challenges

Theoretically, optimal load balancing is attainable with centralized algorithms [Win77] that maintain full knowledge of the global instantaneous system load. A proven-optimal algorithm, join-the-shortest-queue (JSQ), ensures requests experience minimal queuing delay. Unfortunately, centralization prevents cross-rack sharding and scale-out designs. In contrast, fully decentralized approaches (e.g. client-based power-of-two designs [Mit01]) either require network-wide message round trips to measure load or rely on out-of-date information from previous response. As the service time of requests approaches that of an RTT, both approaches provides little benefit on acquiring more up-to-date information. Further, these approaches struggle to react quickly to congestion given these long network-wide round-trips. Load-balancing decisions made with information which has aged by at least an RTT cannot react to microburst events which occur on sub-RTT timescales.

## 2.2.1 Microsecond load balancing at scale

An ideal solution for microsecond load balancing at scale will therefore be decentralized to avoid bottlenecks, designed to reduce probing overheads, and designed to react nearly instantaneously to bursts. Vargaftik et al. [VKO20] demonstrated theoretically that distributed load balancing for datacenter scale is possible. Their proposal, LSQ, has many desirable properties such as a bounded measurement difference between true server load and the load observed by a

load balancer, which receives load updates as messages using a variety of mechanisms [VKO20].

We investigated via simulation an implementation of LSQ in which we placed LSQ load balancers on core routers within a fat tree network. Using core switches satisfies LSQ's theoretical assumptions with regard to how each load balancer sees sever load by forcing all packets through the core of the network to ensure that every request is visible. In this core-switch realization of LSQ, we find some practical limitations. The first of which is its (lack of) response to microbursts. When requests target the same server, the available bandwidth on the egress port of that server's associated top-of-rack (ToR) switch is stressed, leading to drops [ZLZK]. These bursts occur due to lack of coordination between core routers; they can be prevented by making load-balancing decisions at the ToR instead.

Hence, we propose to load balance on leaf ToRs directly. This alteration has a variety of implications on LSQ's theoretical approach. First, LSQ has approximate knowledge of all server queues. By moving our load balancer to ToRs we lose instantaneous knowledge of remote queues but gain up-to-date load information for all the servers of a rack beneath a ToR. While this updated knowledge gives us tremendous insight into the state of that single rack as shown in R2P2 and Racksched [KPG<sup>+</sup>, ZKC<sup>+</sup>], it leaves the dispatchers unaware to the load of services running on remote racks. A key challenge in this work is designing a ToR-based load-balancing approach for datacenter scale by maintaining accurate estimations of the load of other servers at remote ToRs in the absence of periodic updates.

# 2.2.2 Load knowledge

At datacenter scale, any centralized load balancer is proned to be a performance bottleneck. This is true not only in terms of traffic, but also in terms of the per-application state that the load balancer needs to track. In the absence of centralized knowledge, load information must be distributed among load balancers. While the potential benefit of making decisions locally with even out-of-date information is substantial, the hazards of load balancing in ignorance are

documented in the literature [Dah00, Mit00]. The question of how to efficiently disseminate timely state information in practice remains open.

Updates issued periodically between load balancers leads to a predictable overhead in terms of bandwidth and number of messages, but admits (potentially unbounded) errors in the estimates at remote load balancers. Assuming that events arrive with a Poisson or exponential distribution, many events can occur between load information message exchanges. Alternatively, state updates could be disseminated in relation to the request rate, with updates being issued for every request or perhaps some fraction of the total number of requests. This too suffers as the number of messages issued during bursts of requests can cause an increase in update traffic at the worst possible time. The choice of how to disseminate load in a way that provides up-to-date information in a non-obstructive way is crucial to Daronpon's design.

### 2.2.3 Stale information

The following experiments show that the frequency at which load is updated has a significant effect on the quality of the decisions. However, there is a trade-off in terms of traffic overheads to keeping information up to date. As the number of services increases, so too does the number of messages needed to keep the information fresh.

Given imperfect, or stale, information about remote servers, the question becomes: when is redirecting requests a good course of action? We submit that given reasonably predictable, but potentially erratic, request patterns, the correct course of action is to act conservatively when conditions are manageable, and to react quickly and decisively when request loads spike, i.e., in microburst scenarios. These constraints dictate a compromise between inflating traffic and making sub-optimal decisions with poor information.

### 2.2.4 Information traffic reduction

Determining how often and when to send load information requires careful consideration. If an update were to be propagated for every request, that would be ideal from a decisions making perspective, but the overall number of messages sent could inflate by the total replication factor  $(2 \times \text{ or } 3 \times \text{ in many cases})$ . Such overheads are unacceptable for systems with requests in the thousands or millions of requests per second as the cost of the information quickly surmounts the goodput traffic. A key challenge in designing a distributed in-network load balancer approach is to identify the most critical information to send which ideally only produces a small overhead in terms of state exchange messages.

Network operators generally want predictable behavior within their networks. Given that distributed load balancing requires information to be spread, it raises the risk of adding unpredictability to the network, specifically in terms of overhead. An ideal load-balancing strategy would spread information efficiently while allowing operators to set an overhead budget in terms of bandwidth or messages which would correlate to a comparable increase in performance. Predictability is highly important in heterogeneous systems where multiple applications require guarantees about their apportioned network share.

## 2.2.5 Heterogeneous rack configurations

At datacenter scale the configuration for any application may vary wildly. Individual service replicas may be co-located with resource-hungry applications. Due to configuration differences applications might have varying processing powers. Many applications are placed in VMs which execute on differently powered hardware. Indeed, in the datacenter there is no guarantee that any set of replicas is equally provisioned. Therefore, any load-balancing strategy must take into account this heterogeneity and apportion requests in response to the real processing rate.

# 2.3 Daronpon design

The Daronpon design resides within the ToR at each rack and is designed to track server load by counting the number of outstanding requests for each service running on that rack. Figure 2.1 illustrates the role that ToRs play in our load balancing scheme. When a request arrives at a ToR it makes a load balancing decision. It either *Admits* the request, or it *Redirects* it to another replica. Requests are redirected in FIFO without specific priority. The choice to either admit or redirect is subject to the local load the service is currently experiencing under the ToR (as understood by Daronpon), and an estimation of the load each replica has on remote ToRs.

A ToR can only directly keep an up-to-date counter for the services running in its rack. To make good load balancing decisions, fresh knowledge, and more importantly knowledge of bursty behavior, is necessary. Determining the mechanisms for disseminating this load information is non-trivial.

We designed and tested a variety of different options for disseminating load information in simulation and on an Amazon Web Services (AWS) testbed. One design gossiped load information periodically based on wall clock time, and another gossiped on a per-request basis. Our results in simulation and on our test setup demonstrate that both of these techniques require extremely high overheads in terms of messages sent. For example, our best results with periodic message exchanges required updates polled every 25us. This resulted in over a 2x overhead in terms of messages. Most of the information spread in this case was redundant, and does not aid in mitigating bursts. Further, it adds congestion to the network, which reduces the maximum throughput, especially during bursts, which is the opposite of our goal. An ideal load dissemination design would quickly react to bursts while simultaneously generating little overhead during burst events.

Daronpon consists of two distinct but complementary messaging mechanisms. The first mechanism is logarithmic gossip that guarantees the reactive spread of load information

when bursts occur, while generating little overhead otherwise. The second one is opportunistic piggybacking that spreads load information between ToRs when requests are redirected. We find in our evaluation that our log gossip approach prevents large queue build-ups, while our piggyback approach reduces latency.

**Figure 2.1**: High-level overview of Daronpon. Each ToR tracks outstanding request for services running in its rack, and maintains approximate counters for remote ToRs hosting shared replicated services.

### 2.3.1 Microbursts

Figure 2.2 (top) shows an example of a microburst. In this case, requests are issued at a Poisson arrival rate by multiple clients. The peaks show outstanding requests from the perspective of a ToR instrumented to track request counts. In this case, when requests queue, that queue grows without bound, even though other replicated services are available to process this influx of requests. This has a dramatic impact on the tail latency of the requests in the burst, and also the overall mean request time. A typical request incurs longer wait times due to decreased overall system throughput.

In Figure 2.2 (bottom) the queue builds up with our logarithmic gossip mechanism enabled. Each red X's on the chart represents a point at which the load on the server is gossiped. Note that

when peaks occur, and a gossip is sent, the load is quickly spread to other servers. This increases overall system throughput and decreases tail latency. This strategy, however, is not perfect. At low load the benefit of redirecting requests is minimal. For example, when the number of outstanding requests is just one or two above a remote service, and so redirection reduces overall performance.

The age of the gossiped information complicates the act of redirecting. The remote information on remote hosts is at least a few microseconds out of date. Given the few microsecond budget our requests have to begin with, the benefit of redirection quickly evaporates if even a few requests arrive from the point in time at which the load information is sent. This leads to unnecessary redirections and high overheads in terms of gossip messages which do not ultimately deliver useful information. This overhead can be mitigated by adding a threshold which prevents gossip messages from being sent until the number of outstanding requests has exceeded a given threshold. Our proposed log gossip technique for curtailing this overhead is described in the following section.

### 2.3.2 Packet flow

The Daronpon load balancers are stateful and act per request. Figure 2.3 provides a high level message flow diagram of this system. When requests arrive, Daronpon executes the admission protocol. Requests are admitted only if the local service has the minimum observable global load. A load tracker keeps counters for each global service. Local counters are up-to-date, while remote counters are learned via gossip and piggyback messages. When a request is admitted, the ToR increments its load counter corresponding to that service. When a response passes back through the ToR, that service has its local counter decremented. If, when a request arrives, the local load of a service is not the global minimum, the request is redirected. The redirected request is then sent to the service with the lowest load, based on the ToRs' local load tracker (see Section 2.3.4). Redirected requests have load information attached to them. The attached load consists of request counters for the intersection of services the ToRs share. Therefore, the

**Figure 2.2**: Microburst with no mitigation (top) vs. with logarithmic gossip load balancing enabled (bottom)

overhead per redirected request is variable as per the systems' configuration.

Increments and decrements in local load are tracked by a gossip monitor (see Section 2.3.3). The job of the gossip monitor is two-fold. First, it identifies bursts. When load spikes the monitor broadcasts gossip messages to let other ToRs know it is experiencing high load. Second, it identifies valleys. Load balancing schemes which use potentially stale information are known to exhibit herding behavior, a condition which leads to sub-optimal queuing behavior [Dah00, Mit00]. When load drops sharply, gossip messages are also generated to announce that a service has spare processing capacity.

# 2.3.3 Logarithmic Gossip

Daronpon generates gossip messages aiming to reacting quickly to bursts while consuming little overhead in terms of additional messages. In an earlier design, ToRs gossiped load

**Figure 2.3**: Key functionality and message flow of Daronpon. Incoming requests are either admitted or redirected. Redirected requests spread load information via piggyback. Load is updated upon admission, and response. Gossip messages are issues when load breaks a logarithmic threshold.

information every 25  $\mu$ s. This logarithmic gossip approach has the advantage of providing highly updated load information, but it incurred scalability bottlenecks as the number of ToR increased, since the 25  $\mu$ s gossip contends with request goodput for link bandwidth.

To compress the number of messages, Daronpon's gossip messages are sent on exponential changes in load. Daronpon uses powers of two as the interval. Daronpon chooses two for its ease of computation requiring only bit shift operations because no commodity programmable switch, to our knowledge, is able to compute floating point arithmetic [GLY<sup>+</sup>].

Each step increases the bounds in which server load can fluctuate prior to a gossip message being issued. For instance, if the load were to increase from 1 to 2, a gossip message would be broadcast to all other servers with the replicated service that crossed this threshold. In this message, load information for all other shared services is added. When the boundary of two is crossed, and the value of two is sent, this ToR will not issue another gossip message until the load on the service rises by a power of two to four outstanding requests, or falls back down by a power of two to one.

Logarithmic gossip has several benefits. First, it sorts microbursts by magnitude without

**Figure 2.4**: The percentage of gossip messages generated by a logarithmic gossip mechanism as a percentage of overall traffic. Collected from runs of 96 KRPS.

adding significant packet overhead. Given that small fluctuations may occur at rapid pace, it is important to give priority to bursts with larger magnitudes.

Second, logarithmic gossip reduces the number of gossip messages sent during bursts, which reduces the overall strain on the system when resources are at their tightest. This is an issue with gossip strategies that operate periodically (e.g. at preordained wall clock times) or are issued at some constant ratio to requests (e.g gossip every 5 requests). When request rates are low, gossip messages are automatically sent with a higher frequency per number of requests which allows for better decision-making at lower request rates. ToRs have the advantage of being an aggregator for the load of an entire rack. Were we to implement our solution on end hosts, each host would need to gossip its load to every other host. Using ToRs, the load of each server in a rack is known explicitly and is gossiped in its entirety, assuming the rack sees both requests and

the associated responses.

Other approaches which use load information collected from end hosts themselves suffer from additional delays in responding to load spikes, as the knowledge of load must be transmitted to the balancer before it can react. Daronpon's logarithmic gossip mechanism reacts to load as soon as a request is admitted. This allows for precise load balancing decisions to be made at sub-RTT time scales. For instance, in a Fat-Tree with two ToRs connected by a single aggregate switch, the distance traveled by load updates is halved in comparisons to a host based solutions (e.g. Tor-Agg-Tor vs Host-Tor-Agg-Tor-Host). This approach is not limited to Fat-trees, as many networks use ToRs, however our ToR-based approach always results in two hops less than an host based approach.

Daronpon's logarithmic gossip estimates server load on the ToR with counters instead of requiring precise and up-to-date measures of load on the host, which we can only get with precise application level knowledge and host control, This imposes lower tracking overhead, and performs nearly as well as highly tuned approaches which report server load directly [ZKC $^+$ , Figure. 15 (proactive)]. This algorithm decreases the number of gossip messages significantly, and can be greatly improved by carefully considering a lower bound at which to disable the mechanism entirely. For example, setting a lower threshold such as t implies that below an outstanding request count of t a ToR will not gossip information. The threshold is determined by an exponential weighted moving average and a floor value that the threshold does not go beneath it.

Figure 2.4 shows the percentage of messages gossiped relative to the requests processed for different threshold values. Note that the default values of 0 and 1 have an overhead of around 30% of the request rate. Redirections of requests at these levels of outstanding request sees little benefit in terms of performance as at any reasonably high request rate, the depth of remote queues have changed since the remote data was received making the choice stale. By increasing the threshold to four, the overhead in gossip messages is reduced by a factor of ten down to

around 2% when our system is around 70% saturation. This suggests four is a good floor value for the gossip threshold setting. See Section 2.5.5 for a comprehensive evaluation of gossip overhead. Increasing the gossip threshold beyond four significantly reduces overhead down to around 0.02%, however this comes at the cost of only identifying bursts of size eight and greater which significantly effects our reductions in 99th percentile tail latencies.

Logarithmic gossip, however, provides no liveness guarantees to the freshness of the load information announced despite all the aforementioned benefits. For instance, a server which maintains an outstanding number of requests between 4 and 16 for *n* requests will not issue a gossip until either threshold is crossed. While this is unlikely in practice due to the small range and short duration of requests, there is no guarantee. This can become an issue for extended periods of load when the number of outstanding requests is deep (e.g. 128 to 512).

### 2.3.4 Piggyback

Beyond using logarithmic gossip, the redirect requests also able to propagate load information by making load information riding with these requests heading to remote ToRs. With gossip enabled, the percentage of redirected requests is 22%. Each of these redirected requests is sent from the redirected ToR to the receiving one, and therefore has the ability to report the load information on the ToR that performed the redirection. We refer to this method of attaching load information to redirected requests as piggyback, and using redirection to spread information provides significant advantages in the common case. Piggybacking depends on a threshold called load delta indicating the difference between the load on local replica and the load information on remote replica. Load delta determines the triggering of redirection and controls the aggressiveness of redirection. It is determined by an exponential weighted moving average as a threshold to adapt for different workload patterns.

In contrast to the centralized approaches in both Racksched and R2P2 [ZKC<sup>+</sup>, KPG<sup>+</sup>] piggybacking information load on requests is not a sufficient mechanism for learning about

**Figure 2.5**: Performance breakdown of gossip and piggyback mechanisms. Lower values are better.

remote load. This is because our load balancer is decentralized, which means that our load balancers do not see load information updates from every request. Unlike our logarithmic gossip mechanisms, it provides no guarantees about its operational bounds. Using gossip messages exclusively provides no guarantees that any specific server will have information propagated to it as only the server which is redirected to receive fresh information.

In the case of these centralized solutions, each request returns some information to the scheduler. In the distributed case, there is no liveness guarantee with regard to redirections, and indeed, information can become arbitrarily stale. We therefore consider our piggyback algorithm to opportunistic, only aiding in the common case when load is low, but when making precise redirections will still improve throughput and provide lower latency.

Piggybacking load has the advantage that it is responsive proportional to the request

rate of the system. As the number of requests per second increases so to does the rate at which information is spread between ToRs. Furthermore, it has the advantage of introducing a small amount of overhead. Rather than incurring the cost of an entire load information update, this only adds a few bytes to a custom header injected at the ToR.

Figure 2.5 shows a performance breakdown of the two pillars of Daronpon's design: logarithmic gossip and piggyback compared to a baseline of performing random selection on the client alone. At low request rates the logarithmic gossip does not provide much of a performance benefit in relation to the piggyback method. However, as the request rate, and variability, of the system rises (e.g. to 102 and 105 thousand requests per second), the logarithmic gossip provides the majority of the gains as it detects the peaks which increase tail latencies the most.

## 2.4 Implementation

We deployed Daronpon on the AWS cloud with instances hosted in VMs connected via Elastic Network Adapter (ENA) virtual NICs. These instances use the Data Plane Development Kit (DPDK).

Components: Our deployment consists of three components: DPDK ToRs, DPDK clients, and servers with default Linux networking stacks relying on UDP for application messaging. DPDK is a kernel bypass networking library which allows for high throughput and low latency packet processing in user space [DPD21]. DPDK ToRs emulate ToR switches with limited latency overhead (< 1 microsecond). Ideally, we would implement our algorithm on P4 switches, however to our knowledge no cloud providers allow for customers to offload custom programs to programmable switches at this time. Considering that programmable P4 switches have not been widely deployed in datacenters, Daronpon could also be offloaded to SmartNICs, reducing packet processing latency through dedicated hardware without interrupting the main CPU cores We implement our clients using DPDK for lower latency and precisely controllable request rates.

These traits are important as AWS's ENA NICs do not have hardware timestamping available to users. Our DPDK clients can generate hundreds of thousands of requests per second with a single virtual core. These UDP-based servers represent services relying on the standard Linux networking stack. We choose to use UDP as the transport because it allows us to redirect request atomically without connecting multiple packets together and redirecting as a group, though this could be supported as future work.

**Daronpon DPDK ToRs:** DPDK ToRs use an arbitrary number of cores to forward requests/responses and a single core to gossip load information. Redirecting involves header manipulation, tracking load information using hashtable table lookups, and counter increment/decrement operations. The operations we used in these DPDK ToRs are carefully chosen to be simple, and within the capabilities of programmable switches to compute.

Custom packet headers: Daronpon appends a custom header after the IPv4 UDP header. The header consists of a unique request ID for each request, which is used to track lost packets and measure end-to-end latency. A service type field differentiates services, e.g. Memcached and RocksDB. Additionally, the IP and ports describe addresses of replicas which implement other copies of the service. We assume that clients know the server replica addresses by asking the cluster-level replication manager, e.g., Google's Slicer or Facebook's Shard manager [fac20, AMH<sup>+</sup>, KXH<sup>+</sup>]. Gossip messages are also based on UDP, and load information is appended after the UDP header. The header contains a list of server addresses, load counters, and its corresponding service types for all servers under a ToR switch.

### 2.5 Evaluation

We evaluate Daronpon in on the Amazon Web Services cloud (AWS us-west-2 region) using c5n instances. In this section, we describe the experiments and the resulting conclusions.

#### 2.5.1 Experimental Setup

We use 6 instances as servers, 6 as clients, and 3 as software ToRs. All instances are placed in a cluster placement group for predictable low latency. The mean RTT latency between every instance is 50 microseconds. In this setup, we configure 6 servers, 6 clients, and 3 software ToRs. This configuration emulates a datacenter network of 3 ToRs that each ToR has 2 services running underneath it. Services are deployed to servers using the stock Linux networking stack. While this does incur higher latencies as compared to DPDK-based kernel bypass stack, we note that it is representative of many datacenter applications.

We implement the *random* and *Power-of-2 choices* as the baselines. Both of them select the replica of the service on the client side. *Random* baseline selects a replica of a service regardless of any load information. *Power-of-2 choices* for service selection is another baseline that selects a replica of a service based on load information available to the client. The power-of-2 choices [Mit01] randomly chooses two random replicas of services and picks the one with lower load out of the two ones. The load information used for service selection is stale when it reaches the client because the actual load may have changed. The load information is obtained with active probing the servers or from the response of a previous request. We compare Daronpon to random and power-of-2 choice in the experiments.

#### 2.5.2 Workloads

We evaluate our load balancing approach with request-response based applications, in which the time spent on the server is emulated based on different statistical distributions. In our evaluation, we generate requests according to two statistical distributions, one of which generates application-level requests and is run on DPDK-based clients, and another which generates emulated service times. Clients generate requests based on open-loop Poisson arrival using the standard random library. Servers distributions are split into different distribution categories, each

of which has its own separate parameters. These include constant time, bimodal, and exponential distributions.

Each server is loaded with an equal number of requests (in expectation) drawn from common request rate distributions, as described next. Our goal in using these distributions is to demonstrate that using outstanding requests (blind to the underlying service distribution) works in general, without the need to tune our load balancer for each application. Both our gossip and piggyback mechanisms are enabled in each experiment. The lower threshold on the gossip mechanism is initialized as 4.

Constant: In this configuration, all requests compelte in 25  $\mu$ s on the server. On the server, a work thread busy-polls the time until 25  $\mu$ s has passed to emulate application-level service times. This type of workload is indicative of many highly tuned key-value stores with strict SLOs [Mem21, roc21]. The servers experience additional latency overheads from the Linux networking stack. Our choice of this constant latency is intended to be representative of a performance-tuned microservice which performs a fixed amount of work per request. To provide a sensitivity analysis to this choice of constant, Section 2.5.5 provides an overview of Daronpon's performance across constant service times

**Exponential:** To generate an exponential distribution we use the standard C++ random library. We set the mean to 25  $\mu$ s with a standard distribution of 40,000. These parameters generate tails of up to 400  $\mu$ s which is indicative of many applications that may be subject to blocking, such as occasional writes to disk or the invocation of a blocking RPC to another machine.

**Bimodal:** Our bimodal service times are distributed into two categories. 90% of the requests take 13  $\mu$ s and 10% are 130  $\mu$ s. We choose this distribution as the mean value is close to 25  $\mu$ s. This distribution is aimed at emulating longer and less frequent tasks such as writes and scans in certain key-value store workloads or even garbage collection events in the runtime.

**Figure 2.6**: 99th percentile latency improvements on three common service distributions (Constant, Bimodal, Exponential). Each server is provisioned with homogeneous processing power.

### 2.5.3 End-to-end experiments

We test the effectiveness of our load balancing technique by running it against random replica selection alternatives on the aforementioned workloads. Figure 2.6 shows the relative performance gains across these workloads at the 99th percentile latency. In this configuration, each of the servers has identical processing capacity for each service. We consider this idealized and homogeneous configuration because of its simplicity.

Daronpon demonstrates the most relative gain over random when skew in the workloads is common. At high loads, request variation occurs at higher degrees for multiple reasons. First, the Poisson arrival process on our clients has a higher probability of generating bursty sequences of events at higher load. Second, hypervisor and NIC hardware on AWS contributes to the bursty arrival of requests because of the underlying batching behavior. These forms of burstiness is largely out of our control as we do not have direct access to AWS's hardware configuration. Finally, as rates increase, more batching happens in the Linux kernel networking stack. This leads to sharp decreases in the number of outstanding requests.

Daronpon demonstrates observable benefits in the bimodal and exponential distributions and the long service times cause significant and frequent queuing on the end hosts. Daronpon's logarithmic gossip design reacts quickly to these changes under load and steers requests away from the servers which are running long average request times. In our homogeneous experiments,

the average value for number of outstanding requests is four in our constant distribution, with frequent peaks of up to 80 outstanding requests when Daronpon is disabled.

Constant: Figure 2.6-left shows our approach provide benefit on tail latency starting at 1248 Krps (kilo-requests per second). This constant workload gives Daronpon the fewest opportunities to load balance effectively as the random distribution of requests, each with a static service time, should be approximately even. In this distribution, the benefit is found in the load fluctuations. At high request rates, other mechanisms such as Linux's request batching, have more of an effect on queuing. At the highest request rate that a single vCPU core can handle, the latency improvements of Daronpon over the random and power-of-2 choice baselines are  $0.60 \times \text{and } 0.25 \times \text{at the } 99\text{th}$  percentile with the highest request rate. The improvement over power-of-2 choices is less because the evenly distributed requests given the same constant service times. This remediates the stale information and makes the performance of power-of-2 choices relatively close to Daronpon.

**Exponential:** Figure 2.6-middle shows the throughput and latency gains on an exponential server distribution. The benefits are most noticeable here as the exponential distribution leads to the fastest disparity in load. In this case, a single request on the exponential distribution can lead to significant queuing on a given server. Daronpon's latency improvements over the random and power-of-2 choice baselines are  $0.54 \times \text{and } 0.43 \times \text{at the 99th percentile}$ .

**Bimodal:** In Figure 2.6-right, we see the disparity between random service selection and Daronpon. The service time dispersion provided by bimodal distribution causes noticeable request queuing when a long service time request occupying a service. Logarithmic gossip messages are ideal in this case as they quickly react to the skew in load. Further, in this distribution the probability of finding an under-utilized replica is relativity high. The difference of 99th percentile latency between random and power-of-2 choices shrinks compared to the case of the constant and exponential service time. The 99th percentile latency of power-of-2 choices moves closer to random as the queuing penalty of selecting the congested replica could be as large as  $130 \mu s$ .

**Figure 2.7**: Throughput and latency improvements with skewed processing capacity in a heterogeneous server configuration. Daronpon scales linearly with with the aggregate processing capacity available.

### 2.5.4 Heterogeneous server configurations

The placement of replicated services is subject to the cluster scheduler [fac20, AMH<sup>+</sup>, KXH<sup>+</sup>]. The placement of individual services may be tightly coupled to a single rack, or distributed to multiple racks. Additionally, not all replicated services may be configured using identically powered instances. Some may be provisioned with different core counts, memory, and potentially different OS versions. Finally, should rack-level scheduling be utilized such as Racksched or R2P2, the individual rack level throughput may differ below the operating domain of Daronpon.

To show the generality of our approach in situations where replicated applications differ in their throughput capabilities, we configure one out of our three servers to run using three times the processing capacity, i.e.,  $3 \times \text{number of CPU}$  cores rather than one. In this setup, clients otherwise operate identically to the homogeneous configuration.

Figure 2.7 shows the performance gains from enabling Daronpon on our heterogeneous testbed. In this test, the server with twice the processing power of the other processes requests twice as quickly. Our random client takes no measure of queue depth, and therefore does not adjust to this excess compute power. Its performance is only marginally better in this case, as the request which it probabilistically sends to the doubly provisioned server are processed more quickly.

Daronpon apportions load to servers in precise relation to their processing power. Our results from this test show that Daronpon exhibits good scaling with more computation in this configuration. Daronpon is able to process  $1.4 \times in$  the case of the constant service time. When running in a heterogeneous configuration, the proportion of gossip and piggyback request remains approximately the same as in the homogeneous case. The gossip mechanism is triggered periodically as the request on the faster servers drains below its current threshold, however this periodic variance occurs on the same order as the natural fluctuations in load. Redirections also occur at approximately the same rate, however they are almost entirely directed at the over provisioned server.

Ideally, we would demonstrate the scalability of Daronpon across many racks with more services. We see this heterogeneous result as a proof of concept that our approach can scale approximately linearly with available processing power. We expect this result to hold as our approach is similar in style to theoretical approaches for distributed load balancing which are proven to provide linear scaling while using incomplete local information to balance load [VKO20].

### 2.5.5 Gossip and Piggyback Overhead

**Figure 2.8**: Service times across three orders of magnitude (2us, 20us, 200us). Daronpon provides relative improvements with similar overheads in terms of piggyback and gossip messages at each service time.

To investigate Daronpon's sensitivity on service time and the related overhead, we vary

constant service times by three orders of magnitude across three experiments:  $2 \mu s$ ,  $20 \mu s$ , and  $200 \mu s$ . This helps us to understand the overhead of our logarithmic gossip mechanism, the redirected proportion of messages with piggybacked load information under different service times. First, constant service times stress the servers more because it makes the servers to process more requests per second. With more incoming requests, the number of outstanding requests on the switches is also higher. Second, we set up aggressive redirection that does not require the load of a remote replica to be lower than that of the local one. In this experiment, the load delta between remote and local replica is set to 0, which means that the minimum replica is always selected regardless of the performance impact. Choosing delta above 0 resulted in a lower number of redirections, with a delta of 8 resulting in piggyback messages being generated for only 6% of all requests. The aggressiveness of redirection is a trade-off of performance, resulting in lower tail latencies at the cost of the bandwidth.

Figure 2.8 shows the tail latency and the corresponding overhead of Daronpon. At 2  $\mu$ s (Figure 2.8-left), the 99th percentile latency increases wit higher request rate as expected. Interestingly, Daronpon gossips more frequently between 200 and 400 Krps and shows a bump peaks at 330 Krps. The frequent trigger of gossip is because gossiping thresholds are based on power of two numbers, e.g. 2, 4, 8, 16, etc. Statically, gossiping thresholds are more frequently met when the number of outstanding requests is lower. For example, an increase of outstanding requests from 1 to 8 triggers 3 gossip messages while an increase from 8 to 17 triggers a single message. At ranges of 64 and above, Daronpon gossips when encountering bursts of incoming requests. Daronpon gossips less frequently during higher request rates when piggyback takes over gossip as the main mechanism to propagate load information.