# **UC Santa Barbara**

# **UC Santa Barbara Electronic Theses and Dissertations**

### **Title**

Facilitating Emerging Non-volatile Memories in Next-Generation Memory System Design: Architecture-Level and Application-Level Perspectives

### **Permalink**

https://escholarship.org/uc/item/2g6962cg

#### **Author**

Chi, Ping

## **Publication Date**

2016

Peer reviewed|Thesis/dissertation

## University of California Santa Barbara

# Facilitating Emerging Non-volatile Memories in Next-Generation Memory System Design: Architecture-Level and Application-Level Perspectives

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy in Electrical and Computer Engineering

by

Ping Chi

### Committee in charge:

Professor Yuan Xie, Chair

Professor Kwang-Ting (Tim) Cheng

Professor Malgorzata Marek-Sadowska

Professor Dmitri Strukov

Professor Mary Jane Irwin, Pennsylvania State University

Professor Wang-Chien Lee, Pennsylvania State University

| The Dissertation of Ping Chi is approved.                |

|----------------------------------------------------------|

|                                                          |

| Professor Kwang-Ting (Tim) Cheng                         |

| Professor Malgorzata Marek-Sadowska                      |

| Professor Dmitri Strukov                                 |

| Professor Mary Jane Irwin, Pennsylvania State University |

| Professor Wang-Chien Lee, Pennsylvania State University  |

| Professor Yuan Xie Committee Chair                       |

# Facilitating Emerging Non-volatile Memories in Next-Generation Memory System Design: Architecture-Level and Application-Level Perspectives

Copyright © 2016

by

Ping Chi

This dissertation is dedicated to my parents Yuqin Qiu and Yijiang Chi, for their love, encouragement, and support throughout my life.

# Acknowledgements

Many people have offered me great help during my journey to pursue a Ph.D. degree.

First of all, I thank Prof. Yuan Xie, my Ph.D. advisor, for his guidance and support that lead to my academic progress and achievement. He is my role model of a researcher. I could not show more respect for his enthusiasm and perseverance in academic pursuits, his broad and insightful vision on our research areas, and his diligent and energetic working style. Moreover, he is always helpful throughout my Ph.D. study. He provided me hands-on help when I was in my early years, and encouraged me when I was not confident of my research ideas. It will always be my honor to have worked with him.

Many professors from University of California Santa Barbara (UCSB) and the Pennsylvania State University (Penn State) have given me helpful advice and instructions. I am grateful to Prof. Kwang-Ting (Tim) Cheng, Prof. Malgorzata Marek-Sadowska, and Prof. Dmitri Strukov for serving on my dissertation committee at UCSB and providing me with insightful suggestions on my research work. I reserve my sincere gratitude for Prof. Wang-Chien Lee and Prof. Mary Jane Irwin who continue serving as my dissertation committee members even after I transferred from Penn State to UCSB. I learned a lot from Prof. Lee about how to do research since he co-advised my first research project and revised my first paper submission word by word. Prof. Irwin is my role model of a successful female researcher. I appreciate her constructive advice on my research work and also on my career plan, and her encouragement and support that brought me selfconfidence during my entire Ph.D. study. I also thank Prof. Vijaykrishnan Narayanan, Prof. John Sampson, and Prof. Zhiwen Liu who used to serve on my dissertation committee at Penn State and gave me useful feedbacks at my early stage. Prof. Narayanan was always friendly to me. He welcomed me to be seated among his students and encouraged us to learn from each other, offering me the opportunity to learn various interesting research topics from his research group.

Moreover, I sincerely thank Dr. Paolo Faraboschi and Dr. Qiong Cai for hosting my internship at Hewlett-Packard Labs. Their rich research experience and in-depth knowledge taught me a memorable lesson.

Furthermore, I wish to thank my friends and colleagues at UCSB and Penn State who have made my life vivid and beautiful over these years. Many senior group members helped me a lot when I was new to the U.S. and our lab. I am grateful to Guangyu Sun, Jin Ouyang, Jing Xie, Hsiang-yun Cheng, Qiaosha Zou, Jishen Zhao, Jue Wang, Xiangyu Dong, Dimin Niu, Yibo Chen, and Matt Poremba. I especially thank Tao Zhang and Cong Xu, who are my good "mentors" and friends, always generous with their time and knowledge, helping me on my research projects as well as in my personal life. Also, I have been very fortunate to work with my nice and brilliant group comrades, Jia Zhan, Hang Zhang, Kaisheng Ma, Shuangchen Li, Ziyang Qi, Itir Akgun, Peng Gu, Maohua Zhu, Liu Liu, Dylan Stow, Linuo Xue, and Russell Barnes.

Most importantly, I would like to thank my parents, Yuqin Qiu and Yijiang Chi, who raised and educated me, and always love me. I also thank my brother, Cheng Chi, and my entire extended family, for their continuous support.

# Curriculum Vitæ Ping Chi

#### Education

| 2016 Ph.D. in Computer Engineering | (Expected), University of Califor- |

|------------------------------------|------------------------------------|

|------------------------------------|------------------------------------|

nia, Santa Barbara, USA.

2011 M.S.E. in Electronic Science and Technology, Tsinghua University,

Beijing, China.

2008 B.Eng. in Information Electronics and Engineering, Tsinghua Uni-

versity, Beijing, China.

#### **Publications**

- [C1] **Ping Chi**, Shuangchen Li, Cong Xu, Tao Zhang, Jishen Zhao, Yongpan Liu, Yu Wang, Yuan Xie. "A Novel Processing-in-memory Architecture for Neural Network Computation in ReRAM-based Main Memory", in *Proc. of the 43rd International Symposium on Computer Architecture (ISCA)*, June 2016, Seoul, Korea. (To appear.)

- [C2] **Ping Chi**, Shuangchen Li, Yuanqing Cheng, Yu Lu, Seung H. Kang, Yuan Xie. "Architecture Design with STT-RAM: Opportunities and Challenges", in *Proc. of Asia and South Pacific Design Automation Conference (ASP-DAC)*, Jan. 2016, Macao, China. Invited paper.

- [C3] Shuangchen Li, **Ping Chi**, Jishen Zhao, Kwang-Ting Cheng, Yuan Xie. "Leveraging Nonvolatility for Architecture Design with Emerging NVM", in *Proc. of Non-Volatile Memory System and Applications Symposium (NVMSA)*, Aug. 2015, Hong Kong, China. Invited paper.

- [C4]. **Ping Chi**, Cong Xu, Tao Zhang, Xiangyu Dong, Yuan Xie. "Using Multi-Level Cell STT-RAM for Fast and Energy-Efficient Local Checkpointing", in *Proc. of International Conference on Computer-Aided Design (ICCAD)*, Nov. 2014, San Jose, USA. (Best Paper Award Front End.)

- [C5] **Ping Chi**, Wang-Chien Lee, Yuan Xie. "Making B<sup>+</sup>-tree Efficient in PCM-Based Main Memory", in *Proc. of International Symposium on Low Power Electronics and Design (ISLPED)*, Aug. 2014, La Jolla, USA.

- [C6] **Ping Chi**, Cong Xu, Xiaochun Zhu, Yuan Xie. "Building Energy-Efficient Multi-Level Cell STT-MRAM Based Cache Through Dynamic Data-Resistance Encoding", in *Proc. of International Symposium on Quality Electronic Design (ISQED)*, Mar. 2014, Santa Clara, USA.

- [J1] **Ping Chi**, Wang-Chien Lee, Yuan Xie. "Adapting B+-Tree for Emerging Non-volatile Memory Based Main Memory", in *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD)*. (To appear.)

- [J2] Jishen Zhao, Cong Xu, **Ping Chi**, Yuan Xie. "Memory and storage system design with nonvolatile memory technologies", in *IPSJ Transactions on System LSI Design Methodology (TSLDM)*, 8:2-11, 2015. Invited paper.

#### Abstract

Facilitating Emerging Non-volatile Memories in Next-Generation Memory System

Design: Architecture-Level and Application-Level Perspectives

by

#### Ping Chi

As technology scales, the increasing leakage power dissipation and the degraded reliability of conventional SRAM and DRAM technologies cause growing concern. Emerging non-volatile memory (NVM) technologies have shown great potential to build next-generation memory systems, by combining low leakage power, good scalability, fast speed, and high density. As they are maturing, it is important for computer architects to understand their pros and cons and leverage them in future computer system design.

This dissertation focuses on three types of emerging NVMs, spin-transfer torque RAM (STT-RAM), phase change memory (PCM), and metal-oxide resistive RAM (ReRAM). STT-RAM has been identified as the best replacement of SRAM to build large-scale and low-power on-chip caches and also an energy-efficient alternative to DRAM as main memory. PCM and ReRAM have been considered to be promising technologies for building future large-scale and low-power main memory systems. This dissertation investigates two aspects to facilitate them in next-generation memory system design, architecture-level and application-level perspectives. First, multi-level cell (MLC) STT-RAM based cache design is optimized by using data encoding and data compression. Second, MLC STT-RAM is utilized as persistent main memory for fast and energy-efficient local check-pointing. Third, the commonly used database indexing algorithm, B+tree, is redesigned to be NVM-friendly. Forth, a novel processing-in-memory architecture built on ReRAM based main memory is proposed to accelerate neural network applications.

# Contents

| $\mathbf{C}$ | furriculum Vitae                                                                                                                                                                                                     | vii                                    |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| A            | bstract                                                                                                                                                                                                              | viii                                   |

| 1            | Introduction                                                                                                                                                                                                         | 1                                      |

| <b>2</b>     | Technology Background                                                                                                                                                                                                | 5                                      |

| 3            | Optimize MLC STT-RAM Cache Design Using Data Encoding and Data Compression  3.1 The Basics of MLC STT-RAM                                                                                                            | 9<br>9<br>12<br>23                     |

| 4            | Using MLC STT-RAM for Efficient Local Checkpointing 4.1 Motivation                                                                                                                                                   | 40<br>40<br>43<br>45<br>47<br>53<br>61 |

| 5            | Making B+tree Efficient for Emerging NVM Based Main Memory           5.1 Motivation            5.2 Related Work            5.3 Cost Model            5.4 Algorithms            5.5 Evaluation            5.6 Summary | 63<br>64<br>66<br>67<br>81<br>87       |

|              | 5.6 Summary                                                                                                                                                                                                          | ,                                      |

| 6  | Acc   | elerating Neural Network Computation in ReRAM Based Main | <u>.</u> |

|----|-------|----------------------------------------------------------|----------|

|    | Men   | nory                                                     | 98       |

|    | 6.1   | Motivation                                               | 98       |

|    | 6.2   | The Basics of Using ReRAM for NN Computation             | 101      |

|    | 6.3   | Related Work                                             | 102      |

|    | 6.4   | The Proposed Design                                      | 105      |

|    | 6.5   | Evaluation                                               | 109      |

|    | 6.6   | Summary                                                  | 115      |

| 7  | Con   | clusion                                                  | 117      |

| Bi | bliog | raphy                                                    | 121      |

# Chapter 1

# Introduction

In contemporary computer architecture design, SRAM based on-chip caches, DRAM based off-chip main memory, and solid state drive (SSD) and/or hard disk drive (HDD) based storage, are the major components of the memory hierarchy. The importance of the memory embodiments increases with the rapid advance in microprocessor performance, especially for many-core and large-scale computing systems. However, as technology scales, the conventional SRAM and DRAM technologies suffer from increasing leakage power dissipation and degraded reliability. Also, as DRAM density increases, the refresh penalty becomes nontrivial and can result in significant performance degradation [1]. Moreover, NAND flash SSD suffers from the notorious endurance issue.

In recent years, we have seen many emerging non-volatile memory (NVM) technologies which have better scalability and zero leakage power and have been considered as promising alternatives to conventional memory technologies. A lot of effort has been made on the research and development of these NVM technologies by both academia and industry. Recently, Intel and Micron announced their 3D XPoint technology which is a new class of NVM and promises  $1000 \times 1000 \times 1000$  lower latency and higher endurance than NAND flash. As these emerging memory technologies are maturing, it is important

Introduction Chapter 1

for computer architects to understand their pros and cons and leverage them in nextgeneration memory system design to improve the performance, power, and reliability of future computing systems.

This dissertation is one of such efforts. It is focused on three types of emerging NVM technologies, Spin-Transfer Torque Random Access Memory (STT-RAM), Phase Change Memory (PCM), and metal-oxide Resistive RAM (ReRAM). It tries to facilitate these emerging NVM technologies in next-generation memory system design from two perspectives: architecture-level and application-level. STT-RAM, PCM, and ReRAM, all have non-volatility, low leakage power, asymmetric read and write latency, and asymmetric read and write energy. STT-RAM can achieve SRAM-similar or DRAM-similar read latency and read energy under the same capacity, with its cell size between DRAM's and SRAM's. Therefore, it has been identified as a promising replacement of SRAM to build large-size and low-power on-chip caches and also as an energy-efficient alternative to DRAM. PCM and ReRAM have higher densities than DRAM, and better endurance than NAND flash, and can achieve DRAM-similar read latency and read energy. Therefore, they have been considered as potential candidates to build large-size and low-power main memory and high-performance storage. The multi-level cell (MLC) technology can improve their densities. Currently, STT-RAM can achieve 2 bits/cell, while PCM and ReRAM can achieve 4 or more bits/cell. Besides their nice features, they also have disadvantages. For example, they all suffer from long write latency and high write energy. Although they have better endurance than NAND flash, they still have limited lifetimes.

First, it is necessary to propose solutions to mitigate their disadvantages, such as high write energy. MLC STT-RAM have even higher write energy than single level cell (SLC). Based on the observation that the write energy consumption has great value dependency, a dynamic data-resistance encoding mechanism is proposed to reduce the write energy of MLC STT-RAM based last level cache (LLC), which encodes more frequent data values

Introduction Chapter 1

to more energy-efficient resistance states at runtime. However, this dynamic encoding technique incurs a slight performance degradation due to the encoding overhead. To eliminate the performance degradation while to save the write energy, the MLC STT-RAM cache design is optimized by using data compression. By compressing a cache line data to half the size, it can be fit into the fast-read and fast-write soft-bit region of series MLC STT-RAM cells, which requires only one-step read and write operations, avoiding the high energy consumption and long latency of two-step read and write accesses. Furthermore, by exploiting the saved space from data compression to store more data, the increased effective cache capacity can improve system performance. The techniques proposed above are architectural solutions. This dissertation also addresses the challenges from application-level perspectives. For main memory databases (MMDBs) built on emerging NVMs, the nice features of NVMs, such as non-volatility, low power, and high density of PCM and ReRAM, will bring great benefits to the system. However, the assumptions that have served as the basis to design conventional database algorithms are changed by the unique characteristics of NVMs such as asymmetric read and write latency and energy. The widely used database indexing algorithm, B<sup>+</sup>tree, is redesigned with the new design goal to reduce more expensive write accesses, even at the cost of increasing read accesses.

Second, it is beneficial to take advantage of their unique features in system design. For one example, MLC provides an in-cell multi-versioning opportunity for local checkpointing, since each cell can store two or more bits. An efficient local checkpointing scheme is proposed which leverages MLC STT-RAM as main memory. Different from MLC PCM or MLC ReRAM which adopts the program-and-verify scheme in write operations, MLC STT-RAM has write schemes that contain two steps at most. In the MLC STT-RAM main memory design, the working data are mapped to the soft-bits and the checkpoint data to the hard-bits, so that only one-step write operations are incurred during the en-

Introduction Chapter 1

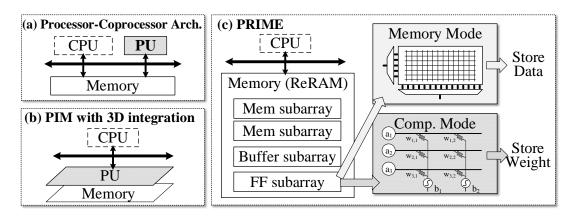

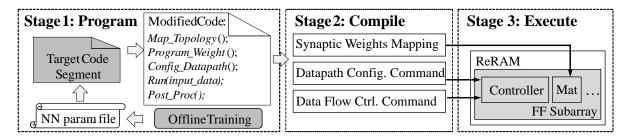

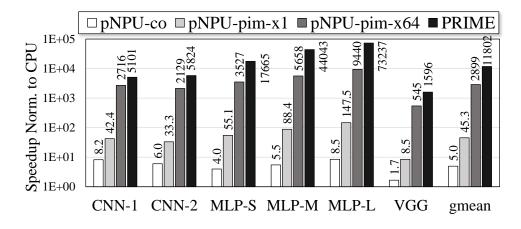

tire execution time including the checkpoint and recovery periods. By replacing the data transfer between the main memory and the backup storage with the data transfer between two bits of the memory cells which only requires one-step writes, the proposed scheme efficiently reduces the performance and energy overhead of local checkpointing. For another example, ReRAM has the analog computation capability with a crossbar structure besides the data storage capability. It can execute matrix-vector multiplications very efficiently, and has been widely studied to accelerate neural network (NN) computations that involve a large amount of matrix-vector multiplications. A processing-in-memory (PIM) architecture built on ReRAM crossbar main memory is proposed to accelerate NN computation. In the ReRAM main memory design, a small portion of ReRAM crossbar arrays are enabled to perform NN computation by additional peripheral circuit support, and they can work as NN accelerators and also as normal memory. By reducing the cost of the data movement between the processing units and the off-chip memory in NN computation, the proposed PIM architecture can improve system performance and energy efficiency significantly for NN applications. The above two proposals are both novel architecture design for specific applications.

The remainder of this dissertation is organized as follows. Chapter 2 introduces the technology background of STT-RAM, PCM and ReRAM. Then, Chapter 3 presents the proposals to optimize MLC STT-RAM cache design using data encoding and data compression, and Chapter 4 discusses the project to use MLC STT-RAM for efficient local checkpointing. Next, Chapter 5 introduces the redesign of the B<sup>+</sup>-tree algorithm for emerging NVM based main memory systems. Then, Chapter 6 presents the proposal to accelerate NN computation in ReRAM based main memory. Finally, Chapter 7 concludes this dissertation.

# Chapter 2

# Technology Background

This chapter introduces the basics of STT-RAM, PCM, and ReRAM. They are all resistive random access memories, a type of NVM that uses the cell resistance to store the information by changing it between a high-resistance state (HRS) and a low-resistance state (LRS). It is known as ReRAM or RRAM for short. However, ReRAM typically refers to metal-oxide ReRAM, a subset using metal oxides as resistive switches. In this dissertation, the term "ReRAM" is used for metal-oxide ReRAM in a typical way.

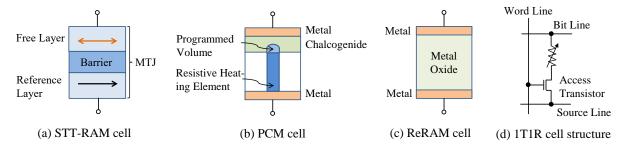

STT-RAM is a new generation of magnetic RAM, using spin-transfer torque to switch memory states. Figure 2.1 (a) shows a magnetic tunnel junction (MTJ), the key component to store the bit information in a STT-RAM cell. An MTJ consists of two ferromagnetic layers and one oxide barrier layer (e.g. MgO) that separates them. The magnetization direction of one ferromagnetic layer (i.e. reference layer) is fixed, called reference layer; while that of the other ferromagnetic layer (i.e. free layer) can be changed by applying a large enough spin polarized current through MTJ, either in parallel or antiparallel with the fixed direction of the reference layer. "Parallel" indicates MTJ in an LRS; in contrast, "anti-parallel" means HRS. The magnetization directions of the MTJs in Figure 2.1 (a) are in-plane, and they can also be made perpendicular [2]. As the

technology node scales, perpendicular MTJ based STT-RAM demonstrates better characteristics than in-plane MTJ based STT-RAM. It requires a lower switching current and can maintain high thermal stability for a longer retention time. STT-RAM adopts the one-transistor-one-resistor (1T1R) cell structure, as shown in Figure 2.1 (d). It is called one-transistor-one-MTJ (or 1T1J) cell structure for STT-RAM. Like a DRAM cell, each STT-RAM cell has an access transistor to prevent the disturbance with other cells.

PCM exploits the unique behavior of phase change material, e.g., chalcogenide glass, which enters two different states under different heating temperatures and durations [3]. These two states, termed as amorphous state (HRS) and crystalline state (LRS), have significantly different electrical resistivities, and thus they can represent "0" and "1", respectively. Moreover, as this material can achieve several distinct intermediate states, it has the ability to represent multiple bits in a single cell. Figure 2.1 (b) depicts a PCM cell. PCM also adopts the 1T1R cell structure as shown in Figure 2.1 (d).

Figure 2.1: The basics of NVM cell structures (not to scale). (a) STT-RAM cell; (b) PCM cell; (c) ReRAM cell; (d) 1T1R cell structure.

Figure 2.1 (c) presents the metal-insulator-metal structure of a ReRAM cell. It contains a top metal layer, a bottom metal layer, and a metal-oxide layer in the middle as resistive switches. There are various oxide materials and metal choices, and the cell switching behavior depends on their interfacial properties [4]. According to the widely accepted filamentary model, during a SET operation, nanoscale conductive filaments (CFs) are formed and the cell is in an LRS; during a RESET operation, the CFs are

cut off and the cell is in a HRS. Like PCM, ReRAM can achieve the MLC characteristic by controlling the switching current/voltage to obtain several intermediate resistance levels. [5]. ReRAM has the 1T1R cell structure as shown in Figure 2.1 (d). To reduce the cost, ReRAM also supports a cross-point architecture, which eliminates the access transistor, using a bidirectional diode as a selector or even no selector at all to achieve the theoretical smallest cell size of  $4F^2$ .

Despite of different materials and technologies, PCM, STT-RAM, and ReRAM have some common characteristics. First, all have asymmetric read and write performance and energy. The reason is that the READ current/voltage they use is smaller and with a shorter duration than WRITE so as not to perturb the cell state. Table 2.1 compares PCM, STT-RAM, and ReRAM with DRAM. Their write latency is several times longer than their read latency, and their write energy consumption is several times higher than their read energy consumption. Second, they all have the write endurance problem, *i.e.*, each cell will be worn out after a limited number of writes. PCM suffers from the most severe endurance issue. ReRAM is two or three orders of magnitude better than PCM in endurance; Although STT-RAM has the best endurance among these three emerging NVMs, it is not free of this issue. Moreover, they are all non-volatile and have low idle power.

Table 2.1: Compare STT-RAM, PCM, and ReRAM with DRAM [6, 7, 8, 9, 10]

|               | DRAM       | STT-RAM             | PCM               | ReRAM              |

|---------------|------------|---------------------|-------------------|--------------------|

| Retention     | refresh    | non-volatile        | non-volatile      | non-volatile       |

| Density       | $1 \times$ | $0.4 - 0.8 \times$  | $2-4\times$       | $2-4\times$        |

| Endurance     | $10^{16}$  | $10^{12} - 10^{15}$ | $10^{8}$          | $10^{12}$          |

| Idle power    | high       | low                 | low               | low                |

| Read latency  | $1 \times$ | $0.5-2\times$       | $2-8\times$       | $0.5 - 10 \times$  |

| Write latency | 1×         | $1-8\times$         | $10 - 100 \times$ | $1-100\times$      |

| Read energy   | $1 \times$ | $0.5-2\times$       | $2-6\times$       | $0.5-5\times$      |

| Write energy  | 1×         | $0.5 - 10 \times$   | $5-50\times$      | $0.2 - 100 \times$ |

A lot of research studies has been conducted to tackle their challenges and make them more feasible memory replacements. Some studies improve their lifetime by using wear leveling strategies [3, 11, 12]. Some deal with the long write latency by using a small buffer at the architecture level [3]. Reducing redundant writes [13, 11, 14] can improve both system performance and NVM lifetime.

# Chapter 3

# Optimize MLC STT-RAM Cache Design Using Data Encoding and Data Compression

This chapter presents two projects that optimize MLC STT-RAM cache design, one using dynamic data-resistance encoding and the other using data compression. Before introducing these two projects, the basics of MLC STT-RAM are given first.

# 3.1 The Basics of MLC STT-RAM

The cell in Figure 2.1 (a) stores a single logic bit, called single level cell (SLC). To enhance the density of STT-RAM, multi-level cell (MLC) structures have been proposed, holding multiple logic bits in a single cell.

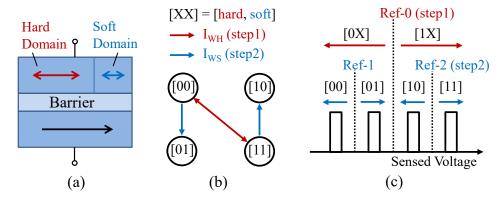

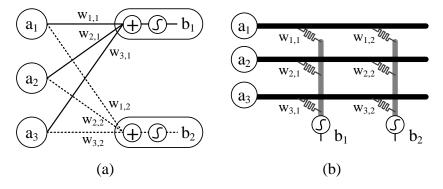

There are two categories of MLC MTJ designs, parallel [15] and series [16]. In parallel MLC MTJs, the free layer has two domains to achieve four resistance states by the combinations of their magnetization directions, as shown in Figure 3.1 (a); while series

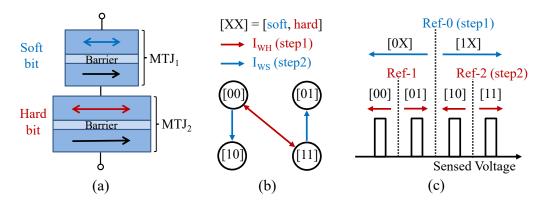

MLC STT-RAM stacks two MTJs to represent two logic bits, as shown in Figure 3.2 (a). Parallel MLC requires relatively smaller switching current density and owns higher tunneling magneto resistance (TMR) ratio. Series MLC is easier to be fabricated. A recent study demonstrates that series MLC STT-RAM is more feasible than parallel, because parallel MLC STT-RAM design is only applicable to in-plane MTJ technology while series design is compatible with advanced MTJ technologies such as perpendicular MTJ and has overwhelming advantage in read and write reliability [17].

Figure 3.1: (a) Parallel MLC MTJ structure; (b) 2-step write operation; (c) 2-step read operation.

Figure 3.2: (a) Series MLC MTJ structure; (b) 2-step write operation; (c) 2-step read operation.

Figure 3.1 (a) depicts the parallel MLC MTJ structure. The two domains in the free layer have different areas so as to represent two logic bits. The bit stored in the soft domain is called soft-bit, and the bit stored in the hard domain is called hard-bit. For a write operation, the write current passes through both the hard domain and the soft domain at runtime. However, the hard domain requires a larger switching current than the soft domain  $(I_{C,hard} > I_{C,soft})$ . By encoding LRS as "0" and HRS as "1", in a 2-bit cell, there are four different levels: "00", "01", "10", and "11". In parallel MLC, the most significant bit (MSB) is the hard-bit, and the least significant bit (LSB) is the soft-bit. Figure 3.1 (b) and (c) illustrate the write and read operations of parallel MLC STT-RAM. They both have two steps. As shown in Figure 3.1 (b), in a write operation, first a large current  $I_{WH}$  ( $I_{WH} > I_{C,hard}$ ) is applied to switch both the hard-bit and the soft-bit; next a smaller current  $I_{WS}$  ( $I_{C,soft} < I_{WS} < I_{C,hard}$ ) is used to flip only the soft-bit. As shown in Figure 3.1 (c), a read operation based on voltage sensing requires three reference voltages (Ref-0, Ref-1, and Ref-2) and two comparisons. The MSB (hard-bit) is first detected by comparing the sensing voltage with Ref-0; then based on the result, the LSB (soft-bit) is read by comparing the sensing voltage with either Ref-1 or Ref-2.

Figure 3.2 (a) presents the series MLC MTJ structure. The two MTJs have different areas in order to distinguish two logic bits. The bit stored in the smaller MTJ<sub>1</sub> is called soft-bit, and the bit stored in the bigger MTJ<sub>2</sub> is called hard-bit. The same with the parallel MLC MTJ structure, given a constant critical switching current density, the hard-bit requires a larger switching current than the soft-bit, i.e.  $I_{C,hard} < I_{C,soft}$ . However, different from the parallel MLC MTJ structure, the soft-bit in series MLC has a larger resistance, and it is the MSB while the hard-bit is the LSB. Figure 3.2 (b) and (c) demonstrate the write and read operations of series MLC STT-RAM. They both have two steps, similar to those of parallel MLC.

Since MLC STT-RAM can promise a higher density than SLC STT-RAM, we have seen a lot of studies that use it to build large-scale on-chip caches recently [18, 19, 20, 21]. Compared with SLC STT-RAM, MLC STT-RAM has more complex read and write

operations, and thus has even longer read and write latencies and consumes even higher read and write energy, which may degrade system performance and energy efficiency despite its capacity benefits.

# 3.2 Improving Write Energy through Dynamic Data-Resistance Encoding

This section presents a dynamic data-resistance encoding technique for MLC STT-RAM based cache [22]. First, the write energy model and the existing static data-resistance encoding algorithm are introduced, and then the dynamic encoding algorithm is proposed that aims to efficiently reduce the energy consumption in MLC STT-RAM write operations. Furthermore, the encoder and decoder designs and the modified architecture of MLC STT-RAM cache bank are presented. Next, after discussing the hardware overhead, the experimental setup and results are shown before this project is summarized.

This project is focused on energy-efficient parallel MLC STT-RAM, with the assumption that the basic direct data mapping is used for MLC STT-RAM based cache.

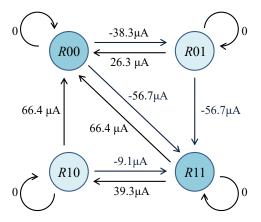

# 3.2.1 Write Energy Model and Data-Resistance Encoding

As described in Section 3.1 and Figure 3.1 (b), a typical write operation of a parallel MLC STT-RAM cell takes two steps. Figure 3.3 demonstrates the switching currents required for resistive state transitions of a parallel MLC at  $45 \ nm$  technology node. The sign of the current value (in  $\mu A$ ) denotes its direction: "positive" means from the free layer to the reference layer while "negative" means the reverse direction. It is obvious that changing states or writing data has significantly value-dependent energy consumption, classified by the following four categories:

- A: Neither bit is changed. No write current is required.

- B: Only LSB is flipped, i.e. "00"  $\leftrightarrow$  "01" and "10"  $\leftrightarrow$  "11". In this case only a small write current is needed.

- C: MSB is switched and in the new value MSB and LSB are the same, i.e. "11" (or "10")→"00" and "00" (or "01")→"11". In this case, a large write current is required to flip MSB.

- D: MSB is flipped and in the new value MSB and LSB are different, i.e. "00" (or "01")→"10" and "11" (or "10")→"01". This is the worst case in terms of both write latency and energy since direct switch is infeasible and a two-step write is needed. A large current is applied to flip MSB before a small one is employed to process LSB.

Figure 3.3: The switching currents for parallel MLC STT-RAM state transitions at  $45\ nm$  technology node. [19]

In the typical two-step write scheme, many unnecessary state transitions are induced. To reduce them, a hybrid write scheme has been proposed [18]. A read operation is conducted first, and based on the values of the original data and new data, the optimized type of write operation is chosen according to Figure 3.3. In  $case\ A$  if data are not

changed, the write operation is completely skipped. In  $cases\ B$  and C, only one step is needed by applying either a small or large current. In  $case\ D$ , two steps are unavoidable. This project assumes that the energy-efficient hybrid write scheme is employed in this project.

The write energy consumption of every state transition with the hybrid write scheme in parallel MLC STT-RAM at 45 nm technology node is calculated based on the reported data [15, 18], by assuming that 10 ns pulse duration is applied. The result is shown in Table 3.1. The last row is the average energy to write each resistance state given that the possibilities of the original state to be one of the four options are equal. Therefore, the resistance states "11" and "00" are more energy-efficient in which "11" is the most energy-efficient one, and "01" and "10" are both high energy consumption states.

Table 3.1: Write energy of every state transition with hybrid write scheme at 45 nm technology node (in pJ)

| PO )    |       |       |       |       |

|---------|-------|-------|-------|-------|

| To From | R00   | R01   | R10   | R11   |

| R00     | 0     | 0.045 | 0.185 | 0.120 |

| R01     | 0.021 | 0     | 0.194 | 0.128 |

| R10     | 0.144 | 0.189 | 0     | 0.001 |

| R11     | 0.164 | 0.209 | 0.065 | 0     |

| Avg.    | 0.082 | 0.111 | 0.111 | 0.062 |

By profiling write data in benchmarks, logic state "00" contributes about 37% of the total write operations, which indicates mapping logic data "L00" to resistance level "R11" is a beneficial way for saving energy. The optimal encoding is  $\{L00 \mapsto R11, L01 \mapsto R10, L10 \mapsto R01, L11 \mapsto R00\}$  [19]. However, their data-resistance encoding scheme is static, in which the mapping is determined by the general write patterns abstracted from a wide range of benchmarks. In this project, a dynamic data-resistance encoding technique is proposed which decides the mapping at runtime and turns out to be more application-specific and energy-efficient.

# 3.2.2 Dynamic Data-Resistance Encoding Algorithm

Given a 64-byte cacheline, 256 2-bit cells in one bank are activated all together for a write operation. There exists an optimal data-resistance encoding solution that minimizes the energy consumption of switching original data to new values in a cacheline since the total 4! = 24 encoding schemes can be enumerated. However, to find the optimal one is too costly to implement due to the limited on-chip resources. The proposed encoding algorithm can efficiently reduce write energy with minor overheads.

First, five terms are defined for future discussion, including three resistance states based on the write energy model (Table 3.1) and two logic states based on their frequencies in a cacheline writing:

- MEES: the most energy-efficient resistance state, i. e. "R11";

- SEES: the second-most energy-efficient resistance state, i. e. "R00";

- LEESs: the two least energy-efficient resistance states, including "R01" and "R10";

- MFLS: the most frequent logic state when writing a cacheline;

- SFLS: the second-most frequent logic state when writing a cacheline.

The key idea of the proposed encoding algorithm is to increase the frequency of energy-efficient states (i. e. MEES and SEES) and to decrease that of energy-inefficient states (LEESs) when writing new data to a cacheline. The algorithm ensures that MFLS in new data is mapped to MEES, and SFLS to SEES. Since the two LEESs have little difference in energy consumption, it is unnecessary to distinguish them when mapping the other two logic states to them. Therefore, there are  $A_4^2 = 12$  mapping types, and thus four additional bits (that is, two 2-bit cells) are needed to record the mapping type code for each cacheline. The algorithm also avoids using energy-inefficient LEESs in

mapping type codes, so "0101", "0110", "1001" and "1010" are excluded. The mapping type lookup table demonstrates the encoding algorithm, as shown in Table 3.2. The area overhead to store the mapping type code in each cacheline is about 0.78% of the area of MLC STT-RAM arrays, given the cacheline size being 64 bytes. Additionally, the storage overhead of the mapping type lookup table is negligible.

Table 3.2: The mapping type lookup table.

| Type   Manning MEI C   Manning CEI C   Manning the other two |                   |                   | o other trre          |                   |

|--------------------------------------------------------------|-------------------|-------------------|-----------------------|-------------------|

| Type                                                         | Mapping MFLS      | Mapping SFLS      | Mapping the other two |                   |

| Code                                                         | to MEES           | to SEES           | logic states          | s to LEESs        |

| 00 00                                                        | $L00 \mapsto R11$ | $L01 \mapsto R00$ | $L10 \mapsto R01$     | $L11 \mapsto R10$ |

| 00 01                                                        | $L00 \mapsto R11$ | $L10 \mapsto R00$ | $L01 \mapsto R01$     | $L11 \mapsto R10$ |

| 00 10                                                        | $L00 \mapsto R11$ | $L11 \mapsto R00$ | $L01 \mapsto R01$     | $L10 \mapsto R10$ |

| 00 11                                                        | $L01 \mapsto R11$ | $L00 \mapsto R00$ | $L10 \mapsto R01$     | $L11 \mapsto R10$ |

| 01 00                                                        | $L01 \mapsto R11$ | $L10 \mapsto R00$ | $L00 \mapsto R01$     | $L11 \mapsto R10$ |

| 01 11                                                        | $L01 \mapsto R11$ | $L11 \mapsto R00$ | $L00 \mapsto R01$     | $L10 \mapsto R10$ |

| 10 00                                                        | $L10 \mapsto R11$ | $L00 \mapsto R00$ | $L01 \mapsto R01$     | $L11 \mapsto R10$ |

| 10 11                                                        | $L10 \mapsto R11$ | $L01 \mapsto R00$ | $L00 \mapsto R01$     | $L11 \mapsto R10$ |

| 11 00                                                        | $L10 \mapsto R11$ | $L11 \mapsto R00$ | $L00 \mapsto R01$     | $L01 \mapsto R10$ |

| 11 01                                                        | $L11 \mapsto R11$ | $L00 \mapsto R00$ | $L01 \mapsto R01$     | $L10 \mapsto R10$ |

| 11 10                                                        | $L11 \mapsto R11$ | $L01 \mapsto R00$ | $L00 \mapsto R01$     | $L10 \mapsto R10$ |

| 11 11                                                        | $L11 \mapsto R11$ | $L10 \mapsto R00$ | $L00 \mapsto R01$     | $L01 \mapsto R10$ |

# 3.2.3 Encoder and Decoder Design

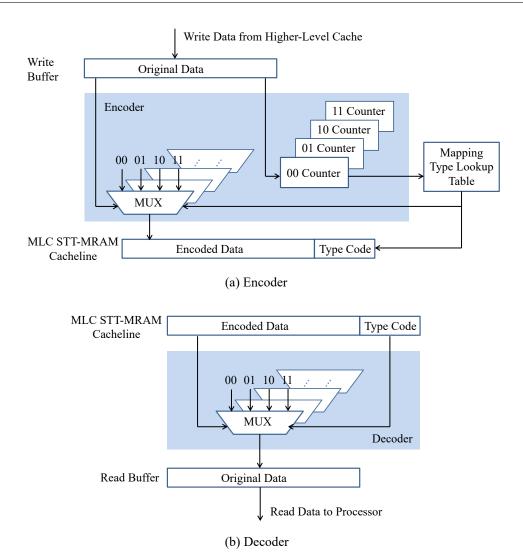

The data flows of the encoder and decoder are shown in Figure 3.4 (a) and (b). To write data to a MLC STT-RAM cacheline, the original data are first stored in the write buffer. Then the number of each 2-bit logic state in the original data is counted by the encoder to determine which mapping type is selected by searching the mapping type lookup table. At last the data are encoded by parallel 2-bit 4-to-1 multiplexers (MUX) whose modes are controlled by the mapping type code, before they are written to the corresponding cacheline. For example, if MFLS in the original data is "10" and SFLS is "00", the mapping type with code "1000" is chosen as the mapping type lookup table

Figure 3.4: The data flow diagrams of the encoder and the decoder: (a) in write operations, data from higher-level cache are encoded before written to MLC STT-RAM cache; (b) in read operations, data in MLC STT-RAM cache are decoded before read out.

indicates, and the data are encoded in accordance with the rule:  $\{L10 \mapsto R11, L00 \mapsto R00, L01 \mapsto R01, L11 \mapsto R10\}$ . Since different mapping types may be chosen at each time based on data values, the data-resistance encoding is dynamic.

The data flow of the decoder is simpler, as Figure 3.4 (b) shows. To read a MLC STT-RAM cacheline, the data are just decoded by parallel 4-to-1 multiplexers under the control of its type code.

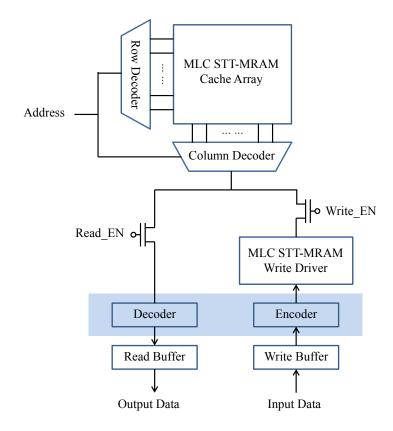

With additional components (the encoder and the decoder), the MLC STT-RAM cache bank architecture needs to be modified, illustrated in Figure 3.5. In a write operation, write data must be encoded before enter the write driver; in a read operation, data can be read out only after the decoding.

Figure 3.5: MLC STT-RAM cache bank architecture design with encoder and decoder.

### 3.2.4 Overhead Estimation

The hardware overhead of the encoder and decoder (as shown in Figure 3.4) is evaluated. Mishra and Akashe have designed a high-performance and low-power 4-to-1 MUX by using the CMOS transmission gate logic (TGL) in 45 nm technology, which operates at up to 200 Gb/s with the power dissipation of 1.887 nW and the area of 6.175  $\mu m^2$  [23]. Based on their reported data, the encoder and the decoder in the proposed technique

is estimated to consume about 0.000012~pJ and 0.000010~pJ extra energy per cacheline access respectively. The total area overhead is  $0.007~mm^2$ , which is negligible to the area of MLC STT-RAM arrays (it is reported that a 45nm 64MB SLC STT-RAM chip can have an area of  $3.06~mm^2$  with device-architecture co-optimization [24]). The encoding process would induce delay to the original write latency. The decoding process is fairly simple and fast. Later, the experimental results will show that the small extra delay from the encoder and the decoder has insignificant impact on overall performance.

# 3.2.5 Experimental Methodology

A pin-based multi-core x86 simulator, Sniper [25], is used in the experiments. The core and memory configurations are summarized in Table 3.3. A CMP is modeled with four 4-issue, out-of-order cores running at 2GHz. Each core has private 32KB I-L1 and 32KB D-L1 caches, which are 4-way associative SRAM. Each core has an 8MB L2 cache, which is 16-way associative MLC STT-RAM with asymmetric read and write latencies. In addition, cacheline size is set to 64 bytes and write-back policy is employed. The capacity of DRAM main memory is 4GB in the simulation. There is one channel, one rank and eight banks in the DRAM main memory, and close-page policy is adopted.

Table 3.3: Baseline configurations in the simulation.

| Processor   | 4-core CMP, $x86$ , $2GHz$ , out-of-order, 4-issue, |

|-------------|-----------------------------------------------------|

| 1 100ess01  | 128-entry reorder buffer                            |

| L1 cache    | private, 32KB I-L1 & 32KB D-L1 SRAM, LRU,           |

| L1 cache    | 64B line, 4-way, 2-cycle access, write back         |

| L2 cache    | private, 8MB MLC STT-RAM, LRU, 64B line,            |

| Lz cache    | 16-way, 5-cycle read, 37-cycle write, write back    |

| Main memory | 4GB DRAM, 300-cycle access latency,                 |

| Main memory | 1 channel, 1 rank, 8 banks, close-page              |

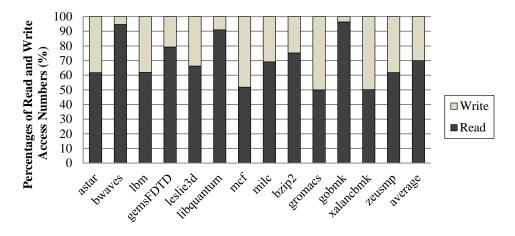

Thirteen workloads are evaluated from SPEC CPU2006 benchmarks [26] including both integer and floating point applications. Four copies of each benchmarks were simultaneously executed on four cores in the simulations. For each workload, the cache is warmed up with the initial 10M instructions and simulated using the next 500M instructions. There are different read and write access numbers across these workloads, as shown in Figure 3.6. mcf, gromacs and xalancbmk can be categorized as write-intensive applications, while bwaves, libquantum and gobmk are read-intensive benchmarks.

Figure 3.6: The percentages of read and write access numbers.

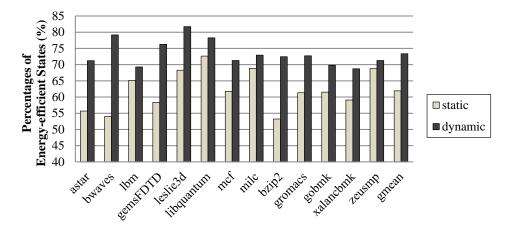

# 3.2.6 Experimental Results

By dynamically mapping resistance and logic states, the ratios of energy efficient states (including MEES and SEES) should increase compared with the static encoding scheme [19]. Figure 3.7 presents the result. As expected, the increasing percentages vary a lot across different applications, from 2.5% (zeusm) up to 25.2% (bwaves). The average (gmean) is 11.5% among the thirteen evaluated workloads, with four above 15%, five between 8% and 15% and four below 8%. Such dramatic variance comes from the great dissimilarity of data that are written in those applications. In lbm, libquantum, milc, and zeusmp, the ratios of energy-efficient states are already as large as over 65%, and in most write operations, L00 and L11 are the dominant proportion of write data. In such cases, the dynamic encoding algorithm would probably suggest the same mapping

method as the static encoding scheme does. Therefore, there is limited improvement in these applications. In astar, bwaves, gemsFDTD and bzip2, write data have varying patterns, and dynamic encoding has the flexibility to handle such cases, and thus shows better results than the static mapping.

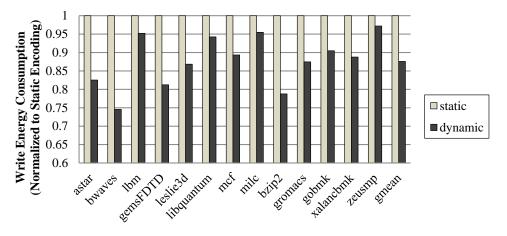

Figure 3.7: Percentages of energy-efficient states (including MEES and SEES) in static data-resistance encoding and dynamic encoding.

Figure 3.8: Write energy reduction of dynamic data-resistance encoding compared with static encoding.

Figure 3.8 shows write energy reduction by the dynamic data-resistance encoding compared with the static scheme. From Figure 3.8, there is 12.4% on average (gmean) and up to 25.4% (bwaves) decrease in total write energy consumption, which is in accor-

dance with the increase trend of the percentages of energy-efficient states in Figure 3.7.

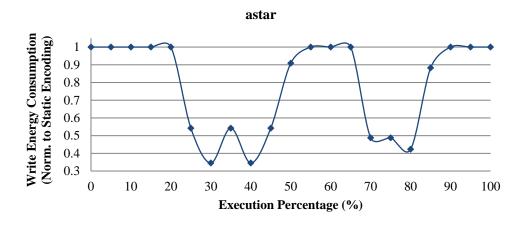

Figure 3.9: Write energy of dynamic encoding over execution time.

Figure 3.10: Performance degradation of dynamic encoding.

Figure 3.9 describes how dynamic encoding overwhelms the static technique in write energy consumption over execution time. During the execution process of *astar*, there are some phases when the dynamic scheme is comparable to static (0%–20%, 50%–65% and 85%–100%), and there are other phases when the dynamic encoding displays its advantages over the static scheme (20%–50% and 65%–85%). In the latter phases, the write data patterns are more random; hence dynamic encoding can achieve more energy saving by optimizing the data-resistance mapping at runtime.

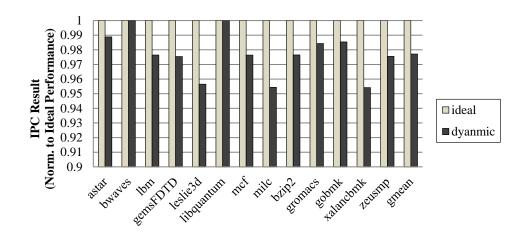

It is also evaluated how much the dynamic data-resistance encoding technique affects the overall performance, as shown in Figure 3.10. Due to the extra delay induced by the encoder and the decoder, there is 2.3% on average and up to 4.6% degradation in instructions per cycle (IPC) compared with the ideal case in which there is no time overhead. From Figure 3.8 and Figure 3.10, the proposed dynamic data-resistance encoding technique can efficiently save write energy with very limited negative effect on performance.

# 3.2.7 Summary

Previous work has shown that STT-RAM has great potential to replace SRAM as future cache technology. MLC STT-RAM can provide even higher density than SLC STT-RAM, and is a promising technology to build large on-chip caches in CMP systems. However, MLC STT-RAM suffers from high write energy because its write operations are complex and require very large write currents. This project proposes a dynamic data-resistance encoding scheme to reduce the write energy consumption in MLC STT-RAM cache with limited degradation of overall performance. Compared with the optimal static data-resistance encoding, this dynamic encoding scheme can achieve 12.4% reduction in write energy consumption with 2.3% degradation of IPC on average.

# 3.3 Optimizing Energy and Performance with Data Compression

This section presents the optimized MLC STT-RAM cache design utilizing data compression. It first discusses the data mapping methods for MLC STT-RAM cache, and then introduces the cache design based on the interleaved mapping method, including the

data compression algorithm used and two proposed techniques using data compression. The overhead estimation of the proposed techniques is presented before the experimental setup and results. Finally, this project is summarized.

This project is focused on the easily fabricated series MLC STT-RAM. For series MLC STT-RAM, reading the soft-bit (MSB) takes only one step, and writing the soft-bit requires only a small switching current which will not flip the hard-bit. Therefore, series MLC STT-RAM can perform like SLC by working only on the soft-bits, which improves the access speed but reduces the capacity.

# 3.3.1 Data Mapping for MLC Based Cache

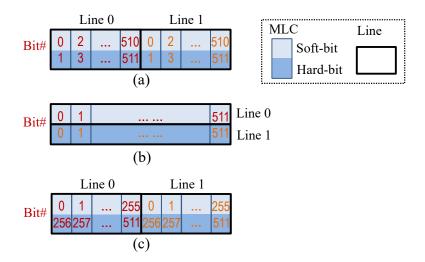

To adopt MLC STT-RAM for cache, one key design issue is how to map the data bits of a cache line to MLCs. A straight-forward method is direct mapping (DM), as shown in Figure 3.11 (a). Given a 64B (512-bit) cache line, it uses 256 2-bit MLCs to hold a line and each cell stores two adjacent bits. Thanks to its simplicity, DM has been adopted in some previous work [18, 22]. However, since DM does not differentiate soft-bit and hard-bit regions, the read and write latencies are the worst-case two-step latencies no matter which word of a line is accessed.

To take advantage of the fact that soft-bit region is fast, Bi et al. proposed cell split mapping (CSM) [20] as shown in Figure 3.11 (b), in which a cache line is stored either in all the soft-bits or in all the hard-bits of the cells. The soft-bit line and the corresponding hard-bit line are a fast way and a slow way respectively of the same set. To make best use of fast ways, a data migration mechanism is designed including an inter-cell swapping scheme and the migration policies. To further improve the access speed, they also propose an application-aware speed enhancement (ASE) mode for MLC STT-RAM based caches, in which MLC STT-RAM can work as fast SLC at a set level

Figure 3.11: MLC data mapping methods for a 64-byte (512-bit) cache line: (a) direct mapping; (b) cell split mapping; (c) interleaved mapping.

of granularity when applications do not benefit much from the large capacity of each set offered by MLC. Each cache set can dynamically halve or double the number of ways by switching between MLC mode and ASE mode according to the result of a mode-predictor.

Interleaved mapping (IM) is another data mapping method [21]. As illustrated in Figure 3.11 (c), the lower half of the data bits of a line are stored in the soft-bit region while the higher half are put in the corresponding hard-bit region. Based on IM, Wang et al. proposed a dynamic block size technique (DBS) to optimize MLC STT-RAM based caches. Each cache set can operate in two modes: large block mode (LBM) and small block mode (SBM), as shown in Figure 3.12 (a). LBM is a normal mode, utilizing both the soft-bit region and the hard-bit region to store each line, while SBM uses only the soft-bit region to store the hot data chunks of a line which has half the size of a line. Therefore, SBM is faster and consumes less energy than LBM. The dynamic block size mechanism can reconfigure the block sizes of each cache set at runtime according to their proposed block size reconfiguration policy. Their experiment results show that, the dynamic LBM-SBM switching mechanism based on IM surpasses the dynamic MLC-ASE mode switching mechanism based on CSM [20], achieving about 1% more IPC

improvement and 5% more energy saving over the LBM only baseline.

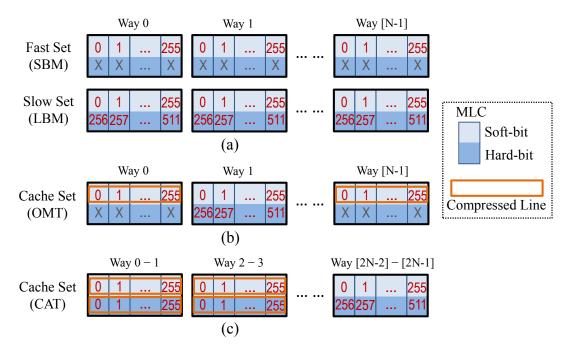

Figure 3.12: (a) The previous dynamic block size technique (DBS); (b) the proposed overhead minimized technique (OMT); (c) the proposed capacity augmented technique (CAT).

# 3.3.2 Design Overview

In the MLC STT-RAM cache design, the interleaved mapping method (Figure 3.11 (c)) is adopted for data mapping. However, unlike the previous work using dynamic block sizes [21], this work fixes the data block size, and employs data compression to fit a compressible line into only the soft-bit region or the hard-bit region of the cells.

Two techniques based on data compression are proposed. One is the Overhead Minimized Technique (OMT) as shown in Figure 3.12 (b), in which a compressible line is put only into the soft-bit region and the corresponding hard-bit region is not used so that the change of the cache management and the modification of the tag arrays are minimized. The other is the Capacity Augmented Technique (CAT) as shown in Figure 3.12 (c), in

which a compressible line can be put into the soft-bit region as well as the hard-bit region so that the capacity of the cache is enhanced thanks to data compression. Compared with the dynamic block size technique (DBS) as shown in Figure 3.12 (a), OMT supports a finer granularity of fast and slow ways. It does not require one whole cache set to operate in either fast way mode (SBM) or slow way mode (LBM); however, each way in a cache set can be a fast way as long as the data can be compressed into half the size and fit into the soft-bit region. Moreover, OMT is more lightweight than DBS by avoiding the hardware and scheduling overheads of dynamic block size reconfiguration. Compared with DBS, OMT and CAT provide a larger cache capacity, because the soft-bit region can store all the data of a line in a compressed fashion and in CAT the left hard-bit region can be used to store another compressible line.

## 3.3.3 Data Compression

The effectiveness of the proposed techniques depends on how many cache lines are compressible. In this work, a line is "compressible" specifically means that it can be compressed into half its size so that it can be fit into only the soft-bit region or the hard-bit region. A number of cache compression schemes have been proposed which exploit various data compression methods to expand the effective cache capacity. For example, Zero-Content Augmented caches represent zero-value lines in a very compact way [27]. Also, Frequent Value Compression [28] and Frequent Pattern Compression [29] have been proposed and utilized in cache designs. Additionally, Base-Delta-Immediate ( $B\Delta I$ ) Compression [30] has been widely adopted as a practical data compression method for on-chip caches thanks to its high compression ratio, low decompression latency, and modest hardware complexity. Huffman coding based statistical compression has also been explored for cache compression [31].

The proposed techniques for MLC STT-RAM cache design do not rely on any specific compression method. This project takes the state-of-the-art B $\Delta$ I compression as an example, and integrate it into the cache design. B $\Delta$ I compression leverages the fact that the values within a cache line have a low dynamic range, and therefore presents a cache line using one or multiple base values and an array of differences ("deltas") whose combined size is smaller than the original cache line [30]. Two bases are used, one of which is default zero, according to the suggested best option. Assuming that the cache line size is 64 bytes, the B $\Delta$ I encoding is defined in Table 3.4.

Table 3.4:  $B\Delta I$  encoding.

| Name              | Base | $\Delta$ | Size | Encoding |

|-------------------|------|----------|------|----------|

| Zeros             | 1B   | 0B       | 1B   | 00       |

| Base8- $\Delta 1$ | 8B   | 1B       | 17B  | 01       |

| Base8- $\Delta 2$ | 8B   | 2B       | 25B  | 10       |

| No Compression    | N/A  | N/A      | 64B  | 11       |

The compressor consists of three compression units: one zero compression unit, one 8-byte-base 1-byte-delta (Base8- $\Delta$ 1) compression unit, and one 8-byte-base 2-byte-delta (Base8- $\Delta$ 2) compression unit. Therefore, the encoding needs 2 bits, as shown in Table 3.4, and they are attached to the corresponding tag for each cache line. All these compression units operate in parallel, and a selection logic chooses the optimal one if multiple compression options are available for a cache line. In the previous B $\Delta$ I compressor design [30], it contains other B $\Delta$ I compression units of different base and delta sizes, e.g. 8-byte-base 4-byte-delta, 4-byte-base 1-byte-delta, and so on. The reasons why only Base8- $\Delta$ 1 and Base8- $\Delta$ 2 are chosen are: i) they can compress a cache line into half the size; ii) they can achieve almost the best compression ratio of B $\Delta$ I compression; and iii) the hardware overhead is greatly reduced. In Table 3.4, the compressed cache line size for Base8- $\Delta$ 1 is 17 bytes, including one 8-byte base, eight 1-byte deltas, and one byte each bit of which indicates the base for each segmentation (or delta) is either the default

zero base or the other base. Similarly, the compressed cache line size for Base8- $\Delta 2$  is 25 bytes.

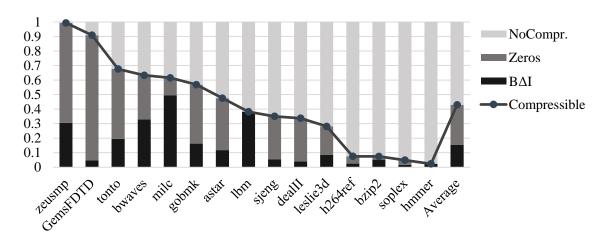

A 3-level cache hierarchy as described in Table 3.5 is simulated, and the data in the last level cache are profiled over the SPEC CPU2006 benchmarks. Figure 3.13 shows the percentages of the compressible lines and the breakdowns of the compression schemes across 15 selected benchmarks. On average, 42% of the target cache line data are compressible. From the breakdown results it can be found that, for some benchmarks such as zeusmp and GemsFDTD, more lines are compressed by the "Zeros" scheme encoded as "00", and for some other benchmarks such as milc and lbm, more lines are compressed by the B $\Delta$ I schemes including Base8- $\Delta$ 1 and Base8- $\Delta$ 2 encoded as "01" and "10".

Figure 3.13: The profiling results over SPEC CPU2006 benchmarks: the percentages of compressible lines and the breakdowns of compression schemes.

## 3.3.4 The Overhead Minimized Technique

As shown in Figure 3.12 (b), with OMT, each way in a cache set can be a fast way or a slow way, depending on whether the data line can be compressed into half the size. As mentioned above, a 2-bit compression scheme code is attached to the tag for each cache line which indicates whether the line is compressed and which compression scheme

is used.

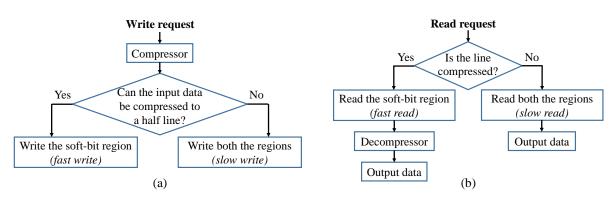

Figure 3.14 describes how OMT processes write and read requests. For a write request, as shown in Figure 3.14 (a), first the input data are processed by the compressor. Then, based on the compression scheme code, it is determined whether the input data have been compressed. If yes, the compressed input data are written into the soft-bit region, and it is a fast and energy-efficient write operation; otherwise, the input data are written into both the soft-bit and the hard-bit regions, and it is a slow and energy-consuming write operation. The corresponding compression scheme code in the tag arrays is also updated. For a read request, as shown in Figure 3.14 (b), first the compression scheme code in the tag arrays is checked to determine whether the line is compressed or not. If yes, the compressed data are read out from the soft-bit region through a fast read operation, and then decompressed by the decompressor according to the compression scheme code before output; otherwise, the data are read out from both the soft-bit and the hard-bit regions through a slow read operation, and then output.

Figure 3.14: The algorithms of OMT to process (a) a write request and (b) a read request.

# 3.3.5 The Capacity Augmented Technique

As presented above, OMT takes advantage of data compression to reduce the access latency and energy to MLC STT-RAM. However, it does not leverage the capacity

benefits from data compression. Therefore, CAT is proposed, which increases the cache capacity by using the saved hard-bit regions to accommodate more compressible lines of data. As shown in Figure 3.12 (c), two compressible lines can reside in the soft-bit region and the hard-bit region of the cells simultaneously. Therefore, the maximum number of ways that each cache set can hold doubles.

To fully utilize the capacity benefits requires doubling the tags, which incurs a considerable overhead. To reduce the tag overhead, the maximum number of ways of each cache set can be limited. According to the profiling results of the percentage of compressible lines as shown in Figure 3.13, increasing the tags by 50% is a reasonable choice. A simple tag-data mapping based on the conventional one is proposed, in which the original tags are directly mapped to the original data positions while the added tags can be mapped to any hard-bit region of the cache set. Therefore, each added tag needs to store its data position. For example, it requires 4 additional bits per added tag to store 16 possible hard-bit region positions in an originally 16-way cache. Moreover, the cache replacement policy needs to be modified since some ways are compressed while others are not. The very simple least recently used (LRU) policy is applied, which chooses the LRU compressed line or the LRU in-compressed line for replacement according to whether the incoming line is compressible or not. The study of more intelligent cache policies are left for the future work.

## 3.3.6 Overhead Estimation

The hardware overhead of the proposed techniques using data compression include the compressor and the decompressor. The B $\Delta$ I compressor and decompressor are implemented using Verilog, and synthesized with Synopsys Design Compiler at 45nm technology node. The estimated area cost is  $0.0018mm^2$ , which is negligible to the entire chip area. Besides the compressor and decompressor overhead, OMT and CAT also incur some tag overheads. As discussed above, OMT has very small tag overhead, only 2-bit compression scheme code for each cache line; CAT uses 50% more tags to support a larger effective cache capacity.

Data compression also increases the cache access latency and energy. With the system simulation configurations (as shown Table 3.5), compression increases the read latency by 1 cycle, and decompression increases the write latency also by 1 cycle. Moreover, compressing a cache line consumes 0.003nJ on average, and decompressing a cache line consumes 0.001nJ on average.

## 3.3.7 Experimental Methodology

In this project, the evaluation is based on the gem5 full system simulator [32] with modification to the cache implementation to simulate the architectural design. The modification to gem5 includes an asymmetric cache read/write latency model and integrated (de)compression unit. The processor and memory configurations are summarized in Table 3.5. Both single-core and four-core systems are simulated with DDR3-1600 as the referenced memory model.15 benchmarks from the SPEC CPU2006 benchmark suite are chosen for single-core simulation. In addition, 10 benchmarks with a wide range of different compression ratio are selected and mixed into 10 groups of 4 for multi-programmed workload simulation as shown in Table 6.1. The accesses per kilo instructions (APKI) is used as a metric to measure the access behavior of LLC, and the APKIs of different workloads are listed in Table 6.1. In the simulation, one billion instructions are fast-forwarded before 5 billion instructions are executed. Note that at least one benchmark with high compressibility is selected for each multi-programmed workload.

Four STT-RAM LLC designs are compared:

Table 3.5: Processor and Memory Configurations.

|             | į č                                                    |

|-------------|--------------------------------------------------------|

| Processor   | 1-/4-core, alpha ,4 <i>GHz</i> , out-of-order, 8-issue |

| L1 cache    | private, 32KB I/D, 64B line, 4-way                     |

| SRAM        | 2-cycle latency                                        |

| L2 cache    | private, 256KB, 64B line, 8-way                        |

| SRAM        | 5-cycle latency                                        |

| L3 cache    | shared, 64B line, 16-way                               |

| STT-RAM     | 4MB SLC, $8MB$ MLC                                     |

| Main memory | 8 <i>GB</i> , DDR3-1600, 64bit I/O, 8 banks            |

| DRAM        | tCL-tRCD-tRP-tWR: 11-11-11-12                          |

Table 3.6: Evaluated workloads.

| No | Benchmark | APKI  | No    | Benchmark  | APKI  |

|----|-----------|-------|-------|------------|-------|

| 1  | GemsFDTD  | 19.38 | mix1  | 4,5,11,15  | 13.59 |

| 2  | astar     | 0.96  | mix2  | 3,6,8,13   | 9.69  |

| 3  | bwaves    | 16.66 | mix3  | 5,11,14,15 | 10.17 |

| 4  | bzip2     | 9.52  | mix4  | 4,6,8,13   | 10.77 |

| 5  | dealII    | 1.73  | mix5  | 3,9,11,14  | 13.39 |

| 6  | gobmk     | 2.92  | mix6  | 4,5,8,15   | 9.89  |

| 7  | h264ref   | 1.92  | mix7  | 3,6,9,13   | 23.73 |

| 8  | hmmer     | 4.52  | mix8  | 3,5,8,11   | 9.56  |

| 9  | lbm       | 55.63 | mix9  | 4,6,13,15  | 25.69 |

| 10 | leslie3d  | 11.97 | mix10 | 3,4,5,14   | 10.68 |

| 11 | milc      | 9.42  |       |            |       |

| 12 | sjeng     | 0.60  |       |            |       |

| 13 | soplex    | 18.52 |       |            |       |

| 14 | tonto     | 0.73  |       |            |       |

| 15 | zeusmp    | 11.50 |       |            |       |

• SLC: the SLC STT-RAM cache.

• MLC: the baseline conventional MLC STT-RAM cache.

• OMT: the proposed MLC cache design with overhead-minimized technique.

• CAT: the proposed MLC cache design with capacity-augmented technique.

The STT-RAM LLC configurations are summarized in Table 3.7, where the circuit-level parameters of latency, energy, and leakage power are generated from NVSim [33].

| Table 3.7: STT-RAM LLC Parameters. |       |       |                    |  |

|------------------------------------|-------|-------|--------------------|--|

|                                    | SLC   | MLC   | OMT                |  |

| Read latency (cycle)               | 13    | 19    | S: 14, H: 20       |  |

| Write latency (cycle)              | 49    | 90    | S: 50, H: 95       |  |

| Read energy (nJ)                   | 0.415 | 0.424 | S: 0.427, H: 0.579 |  |

| Write energy (nJ)                  | 0.876 | 1.859 | S: 1.084, H: 2.653 |  |

| Leakage power (mW)                 |       |       | 80.8               |  |

## 3.3.8 Experimental Results

#### **Energy Results**

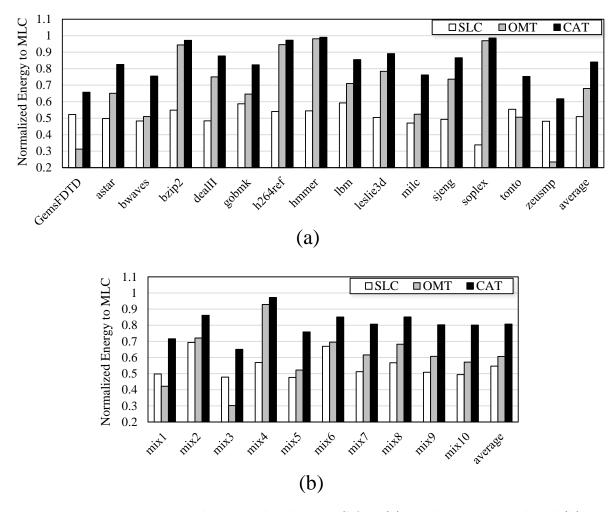

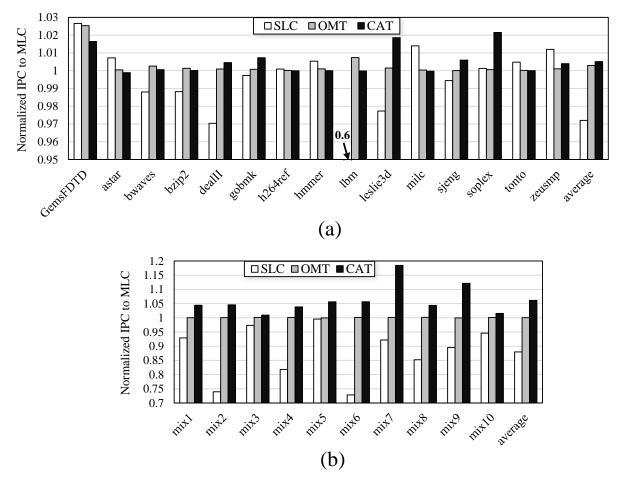

Figure 3.15 shows the energy consumption normalized to MLC design for single-programmed workloads and multi-programmed workloads respectively. As indicated, SLC design has the lowest energy consumption due to its one-step operation. As shown in Figure 3.15 (a), the OMT scheme reduce system energy by 32.0% on average and up to 70.0% for benchmarks with high compressibility and APKI, e.g. zeusmp and GemsFDTD. Figure 3.15 (b) shows that the energy consumption for multi-programmed workloads is further reduced by 39.4% on average. This is because applications running on a multi-core system cause more accesses on LLC. Fortunately, OMT avoids compressible cache lines being written into the hard-bit region, which leads to significant energy savings. While CAT design reduce energy by 19.3% on average, since energy saving is traded for potential better performance. Only dynamic energy is considered because the major difference of energy consumption comes from dynamic cache accesses and different cache designs share the similar peripheral circuit.

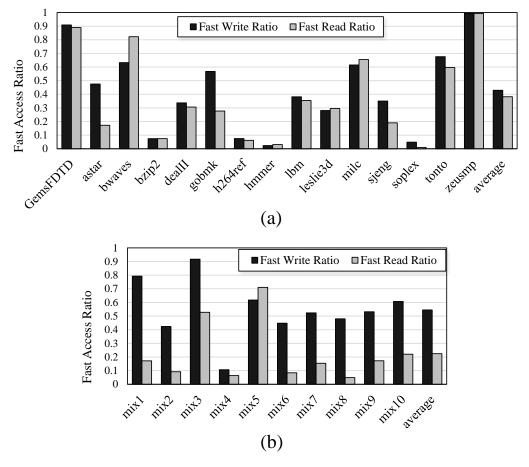

A major source of energy saving is the write energy reduction from two-step operation to one-step soft-bit only operation. In Figure 3.16, the Fast Write Ratio is the percentage of saved one-step write accesses over total write accesses on LLC and demonstrate that the proposed cache design avoids on average 54.5% of normal two-step writes to one-step

Figure 3.15: Energy results normalized to MLC for: (a) single-programmed and (b) multi-programmed workloads.

programming for shared LLC.

## Performance Results

The Instruction Per Cycle (IPC) is used as the metric to evaluate system performance, and the overall throughput ( $\sum$ IPC) is employed for multi-programmed workloads. First, the effectiveness of MLC design over SLC design is demonstrated. As shown in Figure 3.17 (a), for single-programmed simulation, the SLC design with half of the capacity than MLC design incurs on average 2.8% performance degradation compared with the

Figure 3.16: Fast access ratio results for: (a) single-programmed and (b) multi-programmed workloads.

baseline MLC design. While the performance benefit of employing MLC design differs among different applications. Compared with SLC design, the system performance of some benchmarks, e.g. omnetpp and hmmer, actually degrades due to the increased access latency of MLC design, and these benchmarks have a smaller working set on LLC and cannot take much advantage of the increased cache capacity. On the other hand, Figure 3.17 (b) shows that for multi-programmed workloads, the performance of SLC design degrades by 12.1% on average, which comes from the heavier pressure on LLC. Therefore, even though the SLC design consumes the lowest energy, it potentially degrades system performance due to the reduced capacity.

Figure 3.17: IPC results normalized to MLC for: (a) single-programmed and (b) multi-programmed workloads.

The proposed OMT design has the system performance benefit of larger capacity enabled by MLC structure over SLC design. Compared with the baseline MLC design, OMT reduces the energy consumption but incurs no performance degradation. Slightly performance improvement (up to 2.5%) is observed for OMT design since a certain amount of read/write accesses to hard-bit region are eliminated. The performance improvement is insignificant because the target cache is the level-3 cache, which is insensitive to write latency, and the optimization on read latency only has limited impact on system performance. However, it is demonstrated that on average 22.5% (38.2% for single-programmed workloads) of total read accesses are optimized to one-step operation as the Fast Read

Ratio results show in Figure 3.16. Better performance improvement is expected when OMT is applied at higher level of cache hierarchy or when the system is loaded with cache intensive workloads.

Figure 3.17 shows that the CAT design improves system performance by 0.5% for single-programmed benchmarks and by 6.1% for multi-programmed benchmarks, both on average. The effectiveness of the CAT design relies on both compressibility and APKI of different workloads. For workloads with high compressibility and APKI, e.g. mix7 and mix9, it is observed that the performance is improved by over 10.0%. The effective cache capacity is increased when equipped with CAT since the saved hard-bit region can store additional cache lines. Consequently, it reduces memory accesses and improves system performance. While other workloads show little impact on performance, which is due to either low compressibility or insensitive access latency impact on LLC.

## 3.3.9 Summary

MLC STT-RAM has been widely studied as a replacement of SRAM for constructing large-scale and energy-efficient on-chip cache. However, the two-step read/write accesses of MLC cause energy overhead and system performance degradation. This project proposes two techniques leveraging data compression to optimize series MLC STT-RAM based LLC design. The OMT technique avoids slow and energy-inefficient two-step accesses on both hard-bit and soft-bit regions to one-step accesses on soft-bit region only by applying data compression. The CAT technique increases the effective cache capacity by fitting a second compressible cache line into the saved hard-bit region of STT-RAM cells. The experimental results on the evaluated multi-programmed workloads show that, the cache design with OMT reduces the dynamic energy consumption of LLC by 39.4% on average without performance degradation, while the cache design with CAT improves

Optimize MLC STT-RAM Cache Design Using Data Encoding and Data Compression Chapter 3

system performance by 6.1% and reduces the dynamic energy consumption by 19.3% on average.

# Chapter 4

# Using MLC STT-RAM for Efficient Local Checkpointing

This chapter presents a project that utilizes MLC STT-RAM for fast and energy-efficient local checkpointing [9]. It is organized as follows. First, the motivation of this project is introduced, and then the related work and the basics of checkpointing. Next, the details of the proposed checkpointing mechanism is presented, where MLC STT-RAM is utilized as main memory for efficient local checkpointing. Next, the experimental methodology and evaluation results are shown before this project is summarized.

## 4.1 Motivation

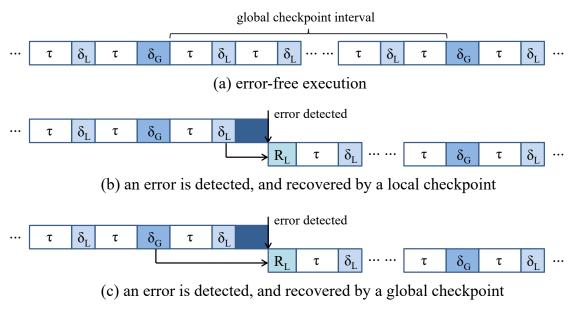

In modern large-scale computing systems, high reliability, availability and service-ability (RAS) have been mandatory. However, it becomes more and more challenging to sustain sufficient RAS quality as the node count keeps increasing. Although each component has been designed for a long mean time to failure (MTTF), the entire system encounters a failure every few days or even several hours [34]. As the exascale

era approaches, the MTTF of future large-scale systems is predicted to be only a few minutes [35].

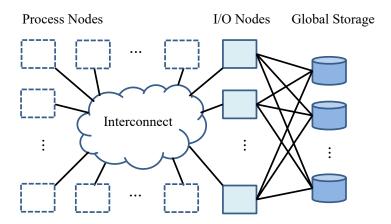

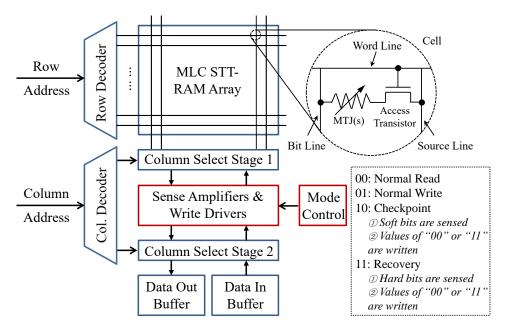

As a well-known error recovery mechanism, checkpointing has been widely used to protect those systems from unexpected failures [36]. In the typical organization of a contemporary supercomputer as shown in Figure 4.1, the process nodes usually deploy DRAM as their main memory, and access the global storage via the I/O nodes. The global storage is permanent storage, usually built with NAND flash based solid state drives (SSDs) or conventional hard disk drives (HDDs), but DRAM is volatile memory and hence vulnerable to errors. One state-of-the-art checkpointing approach is to save the entire process address space to the non-volatile global storage periodically. However, the limited data transfer bandwidth between DRAM and the global storage and the centralized checkpointing topology prevent the performance scaling in future large-scale computing systems. As the application size grows and the system failure rate increases, larger-size and more frequent checkpoints are required, and consequently a significant portion of execution time will be spent writing checkpoints. For instance, checkpointing may incur over 50% performance overhead in a petaFLOPS system [37].

Figure 4.1: The typical organization of a contemporary supercomputer [36].

To address the scalability issue, local/gloabl hybrid checkpointing [38] and multi-level

checkpointing [39] have been proposed as scalable solutions, which combine frequent and fast local checkpoints to local storage with less frequent and slow global/remote checkpoints to global storage. The effectiveness of these approaches is determined by how many failures can be recovered from fast local checkpoints. In fact, most transient errors affect only the failure node, and the system can be simply recovered by rebooting the failure node with its local checkpoint. Dong et al. made an estimation for a petaFLOPS system that 83.9% of failures only need local checkpoints [38].

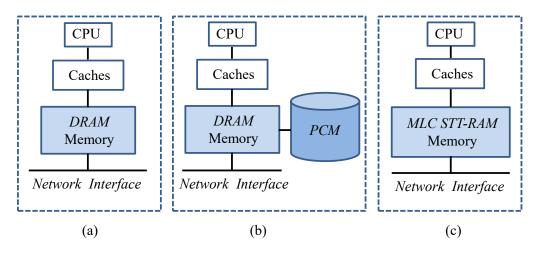

To achieve better performance and higher power efficiency in local checkpointing, some recent work has proposed to utilize the emerging non-volatile memories (NVMs), such as PCM and STT-RAM, as the local storage of each process node thanks to their non-volatility, fast random read access and zero standby leakage power [38, 40].

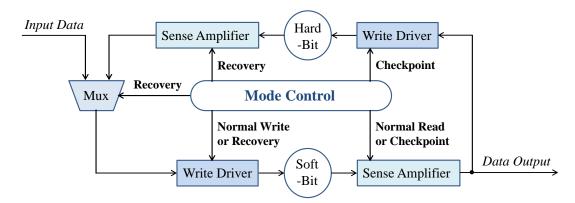

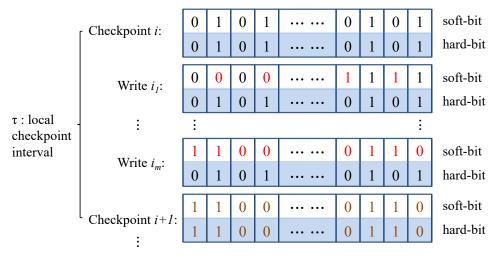

This project proposes to leverage MLC STT-RAM as the main memory for fast local checkpointing. MLC opens up an inherent multi-versioning opportunity for checkpointing since each cell can store both the working data and the checkpoint data simultaneously [41]. Consequently, the system can be easily recovered from the local checkpoint by moving data within memory cells, which substantially eliminates the data transfer overhead between main memory and backup storage. Previous work has also considered using MLC PCM for in-memory local checkpointing [41]. However, MLC PCM write operations adopt the program-and-verify (P&V) technique, which iteratively apply partial set pulses and verify if a specified precision criterion is met [42], to achieve desirable intermediate resistance levels. Due to the P&V process, MLC PCM has even longer write latency, higher write energy, and lower program throughput than SLC PCM; hence using MLC PCM as main memory would significantly degrade system performance. Different from MLC PCM, writing MLC STT-RAM is relatively simple, taking two steps at most [18]. This proposal takes advantage of the unique characteristics of MLC STT-RAM write operations and ensures that only one-step writes occur during the entire execution

time (including checkpoint and recovery). The evaluation results demonstrate the great potential of using MLC STT-RAM as main memory for fast and energy-efficient local checkpointing.

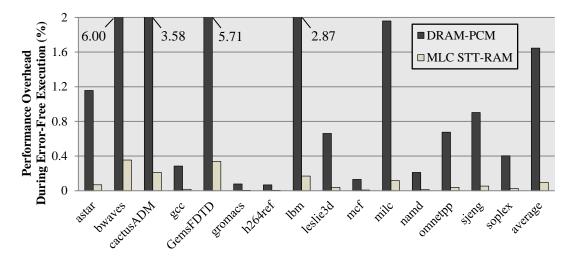

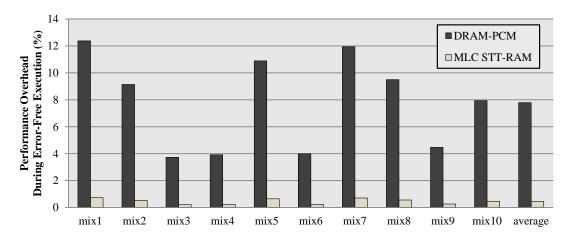

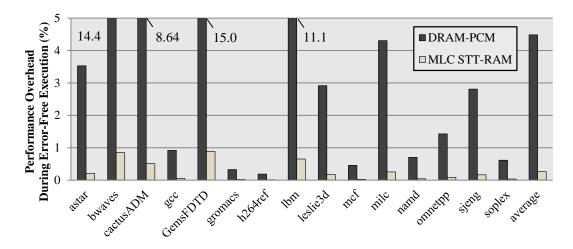

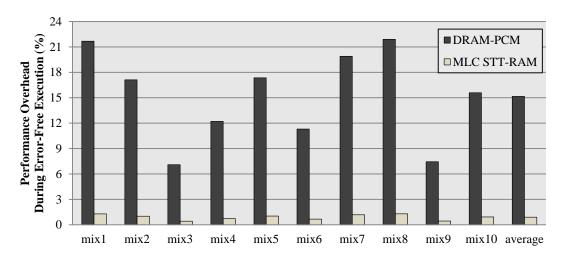

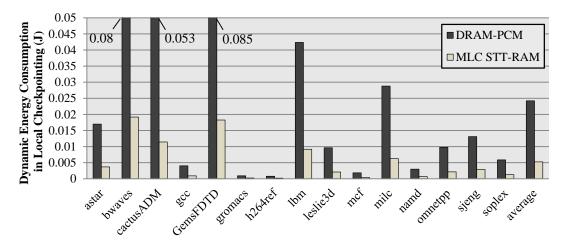

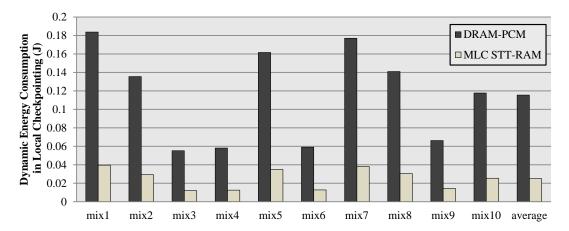

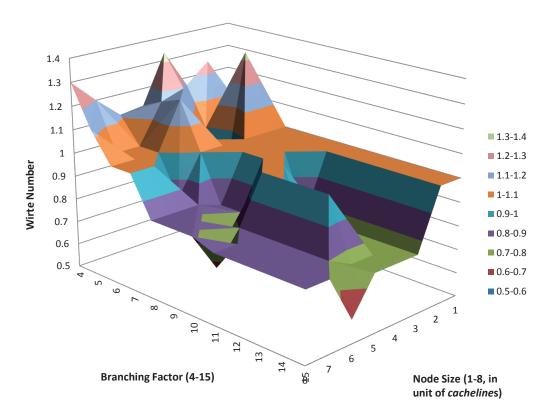

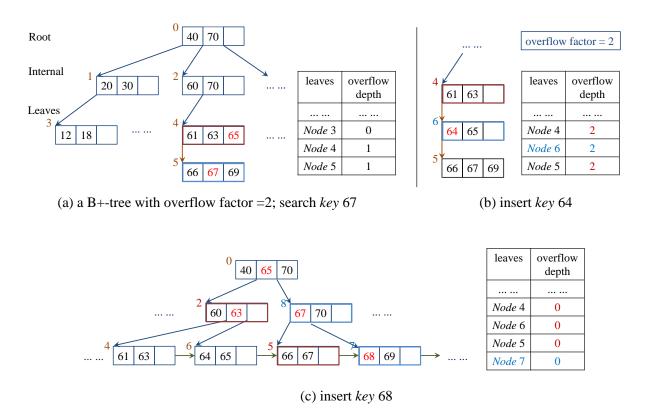

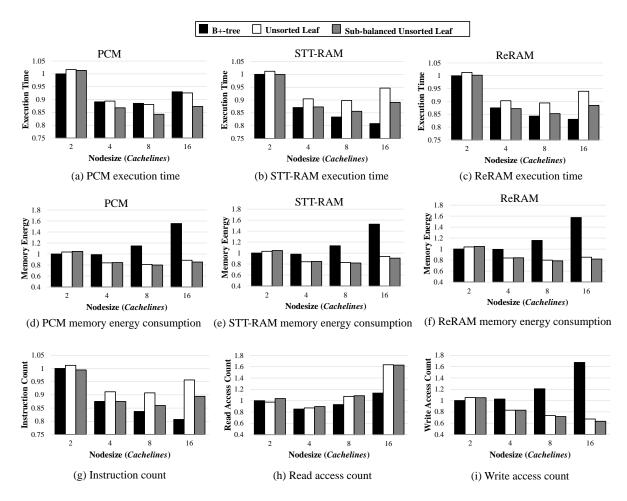

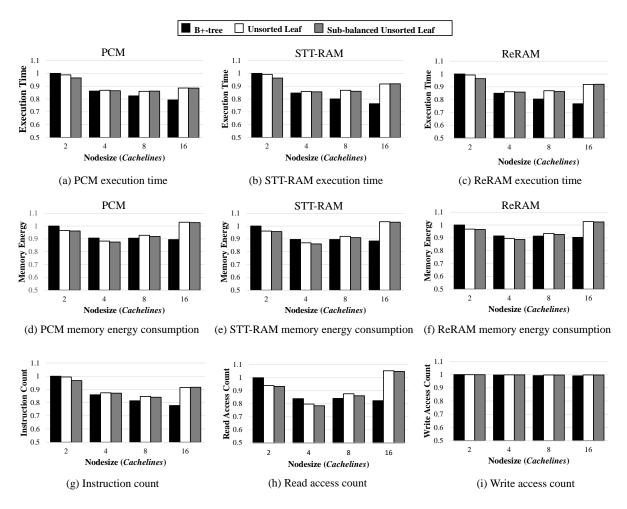

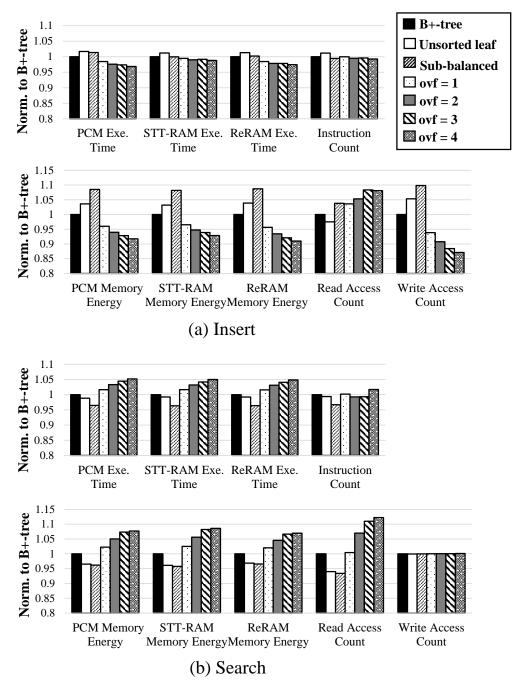

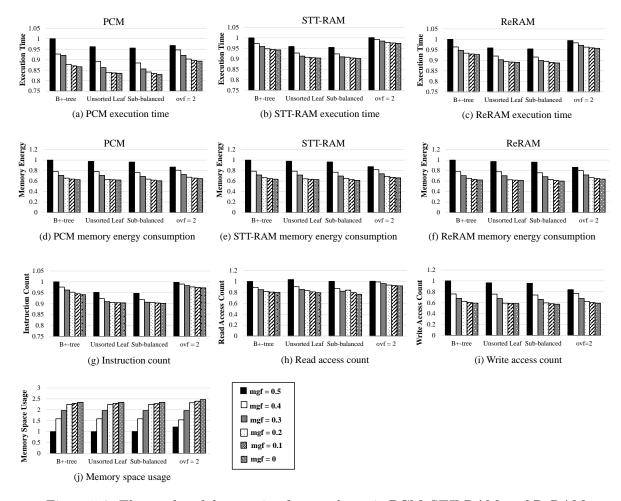

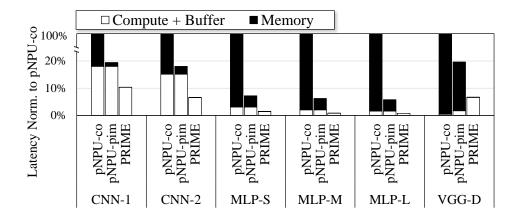

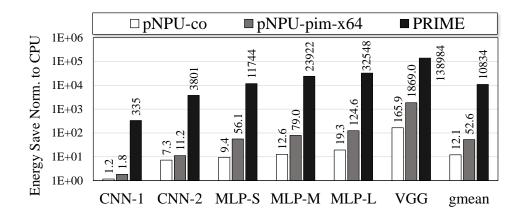

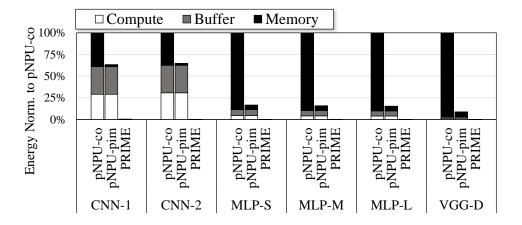

## 4.2 Related Work