# UC San Diego UC San Diego Electronic Theses and Dissertations

# Title

Spur reduction techniques for fractional-N PLLs

**Permalink** https://escholarship.org/uc/item/2gs1v1xv

Author Wang, Kevin Jia-Nong

Publication Date 2010

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA, SAN DIEGO

Spur Reduction Techniques for Fractional-N PLLs

# A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

Electrical Engineering (Electronic Circuits and Systems)

by

Kevin Jia-Nong Wang

Committee in charge:

Professor Ian Galton, Chair Professor James Buckwalter Professor William S. Hodgkiss Professor Lawrence E. Larson Professor Thomas T. Liu

2010

Copyright Kevin Jia-Nong Wang, 2010 All rights reserved. The dissertation of Kevin Jia-Nong Wang is approved, and it is acceptable in quality and form for publication on microfilm and electronically:

Chair

University of California, San Diego

2010

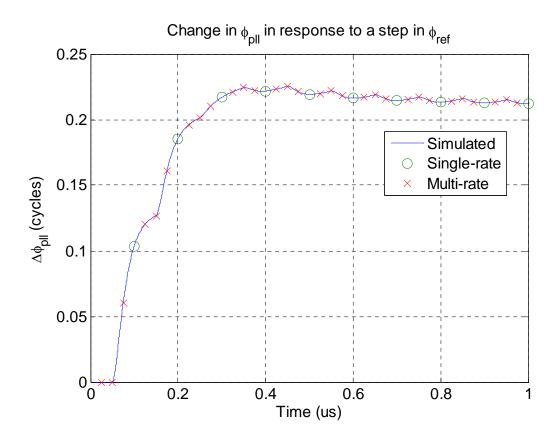

DEDICATION

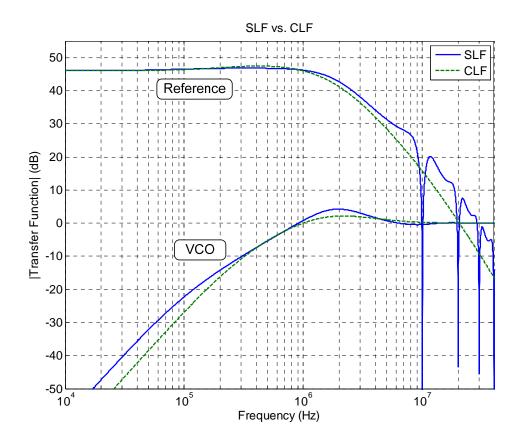

To my family and friends

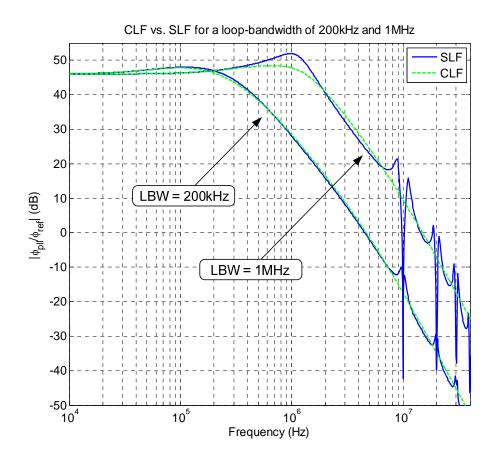

# TABLE OF CONTENTS

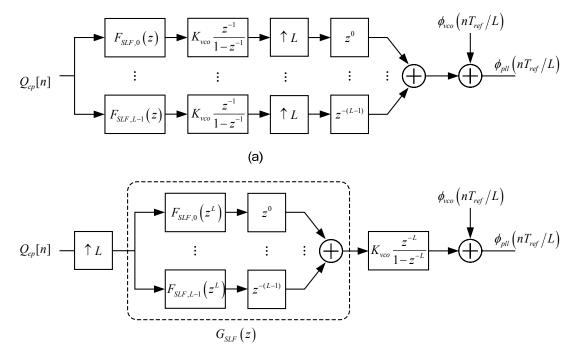

| Signature Page                                                                | . iii |

|-------------------------------------------------------------------------------|-------|

| Dedication                                                                    | . iv  |

| Table of Contents                                                             | V     |

| List of Figures                                                               | . vi  |

| List of Tables                                                                | . ix  |

| Acknowledgements                                                              | X     |

| Vita                                                                          | . xi  |

| Abstract of the Dissertation                                                  | xii   |

| Chapter I: Spurious Tone Suppression Techniques Applied to a Wide-Bandwidth   |       |

| 2.4GHz Fractional-N PLL                                                       | 1     |

| Chapter II: A Discrete-Time Model For the Design of Type-II PLLs with Passive |       |

| Sampled Loop Filters                                                          | 35    |

| Chapter III: A 2.5GHz Realigned PLL with Spur Calibration                     | 69    |

# LIST OF FIGURES

| Fig. 1: Block diagram of a typical fractional-N PLL                                                            |

|----------------------------------------------------------------------------------------------------------------|

| Fig. 2: Example of a nonlinear coupling path in the PFD                                                        |

| Fig. 3: (a) A second-order digital $\Delta\Sigma$ modulator, and (b) an example in which $s[n]$ is             |

| free of spurious tones but a nonlinearly distorted version of $s[n]$ contains                                  |

| spurious tones9                                                                                                |

| Fig. 4: Structures that are both equivalent to that of Figure 3a 11                                            |

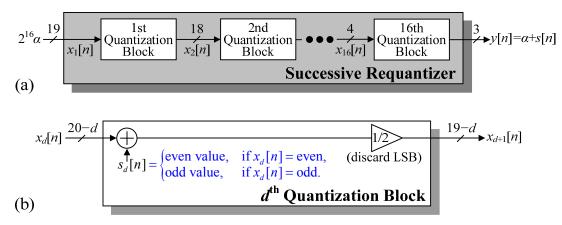

| Fig. 5: High-level diagram of an example successive requantizer                                                |

| Fig. 6: Implementation of each quantization block for a successive requantizer with                            |

| $s^{p}[n], p = 1, 2, 3, 4, 5, \text{ and } t^{p}[n], p = 1, 2, 3, \text{ that are free of spurious tones.}$ 15 |

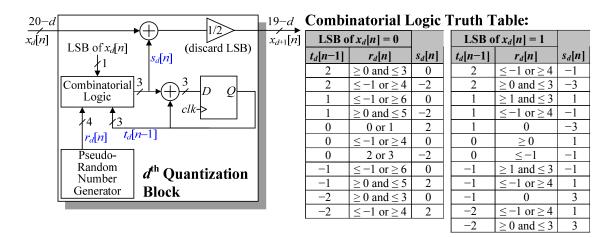

| Fig. 7: The phase-frequency detector, charge pump, offset pulse generator and the                              |

| associated timing diagram                                                                                      |

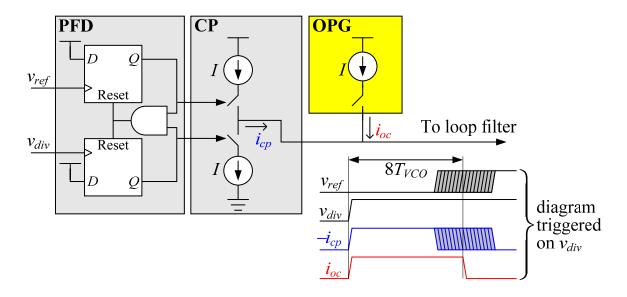

| Fig. 8: The sampled loop filter and the associated timing diagram                                              |

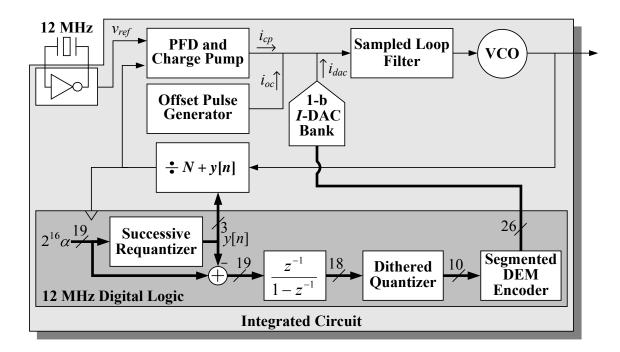

| Fig. 9: High-level diagram of the integrated circuit prototype                                                 |

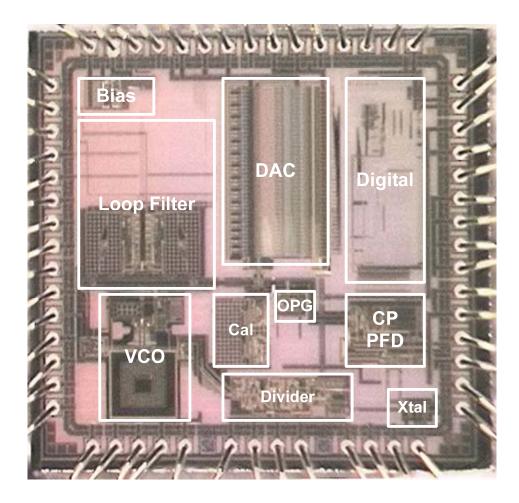

| Fig. 10: Die photograph23                                                                                      |

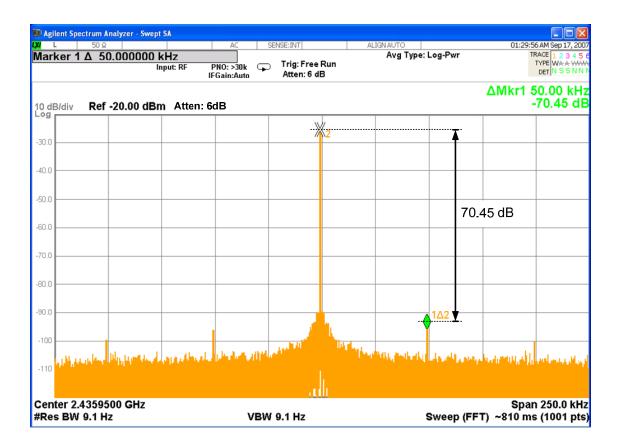

| Fig. 11: Representative measured close-in output spectrum for the case of $\alpha f_{ref} = 50$                |

| kHz                                                                                                            |

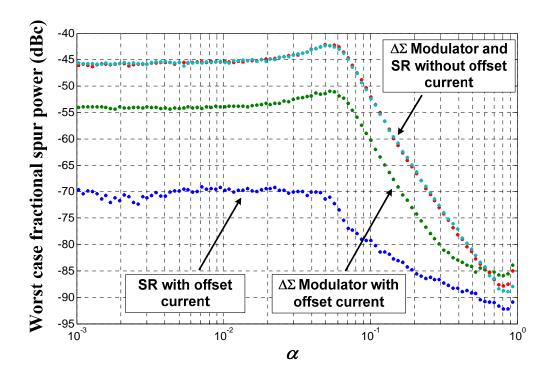

| Fig. 12: Power levels of the largest measured fractional spurs with and without the                            |

| enhancements enabled for 100 PLL frequency offsets in the range $0 < \alpha f_{ref} <$                         |

| 12MHz                                                                                                          |

| Fig. 13: Representative measured spectra with the sampled loop filter enabled and                              |

|          | disabled                                                                       |

|----------|--------------------------------------------------------------------------------|

| Fig. 14: | Block diagram of a typical (a) integer-N PLL and (b) fractional-N PLL 38       |

| Fig. 15: | Circuit diagram of (a) a continuous time loop filter with the VCO and (b) a    |

|          | sampled loop filter with VCO and (c) the timing of $V_{switch}(t)$             |

| Fig. 16: | Single rate discrete-time, linearized model of a SLF-PLL with noise sources.   |

|          |                                                                                |

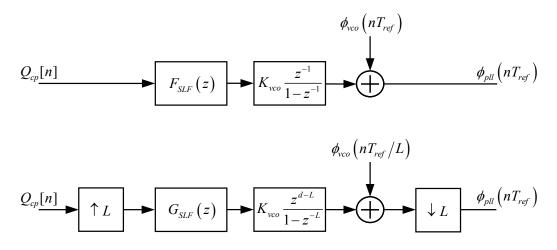

| Fig. 17: | Model of the SLF and VCO for the (a) single rate and (b) multi-rate cases. 44  |

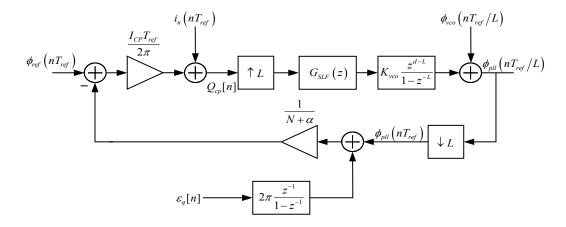

| Fig. 18: | Multi-rate discrete-time, linearized model of a SLF-PLL with noise sources.    |

|          |                                                                                |

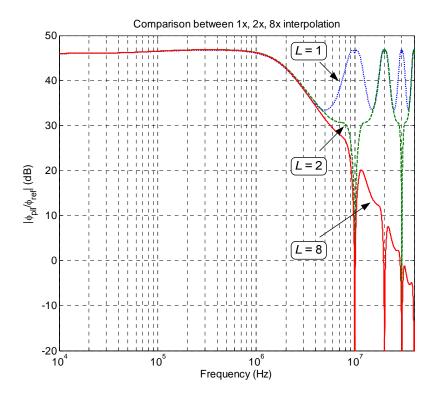

| Fig. 19: | Comparison between the transfer function for the single-rate ( $L=1$ ) and the |

|          | transfer functions for the multi-rate ( $L=2$ , $L=8$ ) cases                  |

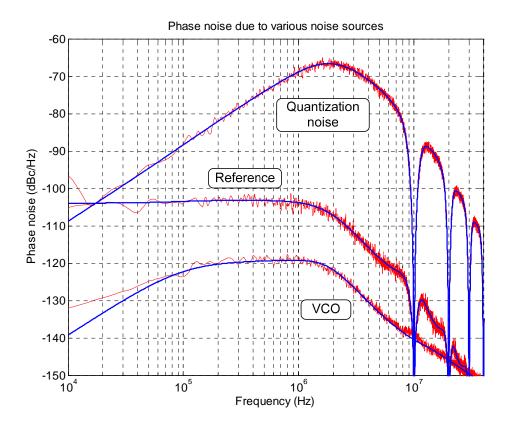

| Fig. 20: | Comparison between the model and simulated results for various noise           |

|          | sources for a fractional- <i>N</i> PLL. ( <i>L</i> =8)                         |

| Fig. 21: | Simulated VCO output phase of the SLF-PLL corresponding to a reference         |

|          | signal phase step, and the corresponding sample values predicted by the        |

|          | model                                                                          |

| Fig. 22: | Reference and VCO phase noise transfer functions of the original CLF-PLL       |

|          | and the SLF-PLL obtained via the synthesis procedure                           |

| Fig. 23: | Reference phase noise transfer functions of the CLF-PLL and SLF-PLL for        |

|          | low and high loop-bandwidth (LBW)                                              |

| Fig. 24: | Model for the multi-rate SLF and transformation to $G_{SLF}(z)$                |

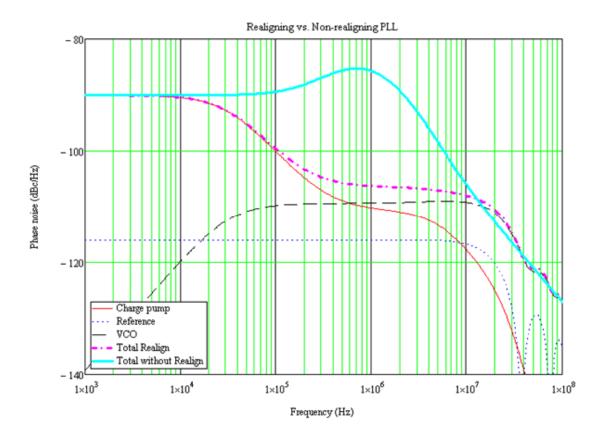

| Fig. 25: | Block diagram of a conventional RAPLL                                          |

| Fig. 26: | Comparison between the phase noise of a realigning PLL and a traditional      |    |

|----------|-------------------------------------------------------------------------------|----|

|          | non-realigning PLL.                                                           | 71 |

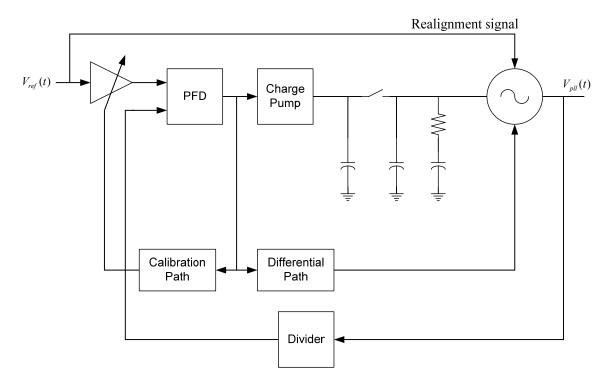

| Fig. 27: | Block diagram of the proposed RAPLL                                           | 73 |

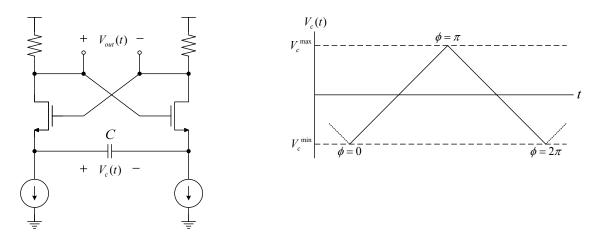

| Fig. 28: | Schematic of a relaxation oscillator and the voltage across the timing        |    |

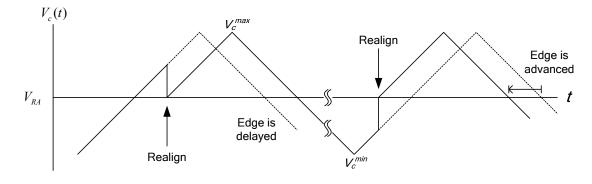

|          | capacitor                                                                     | 73 |

| Fig. 29: | Illustration of realignment in a relaxation oscillator                        | 74 |

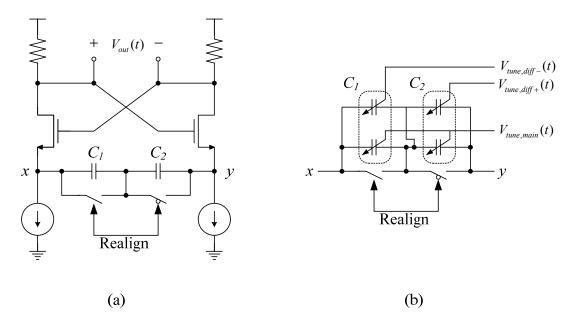

| Fig. 30: | Modified relaxation oscillator to support realignment                         | 75 |

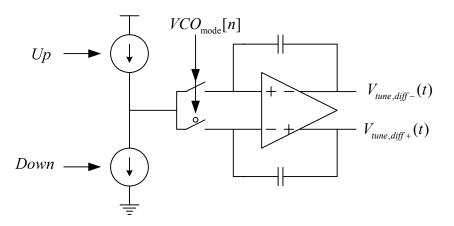

| Fig. 31: | Block diagram of the differential control path for the VCO.                   | 76 |

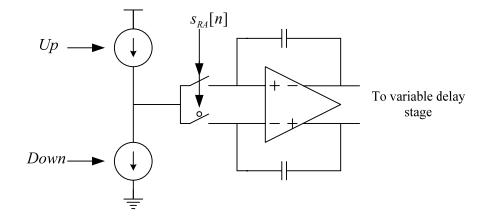

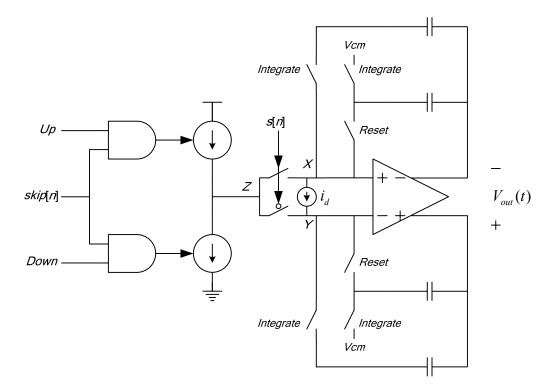

| Fig. 32: | Block diagram of the calibration path.                                        | 78 |

| Fig. 33: | Detailed diagram of the calibration circuit.                                  | 79 |

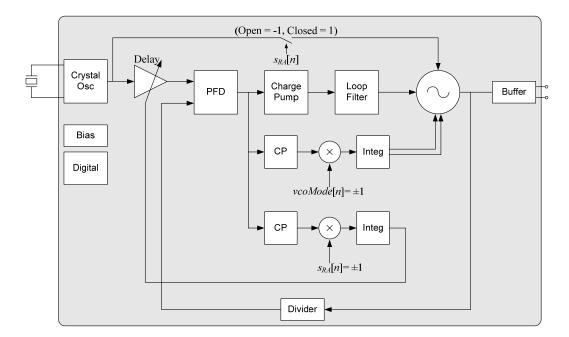

| Fig. 34: | Block diagram of the IC                                                       | 81 |

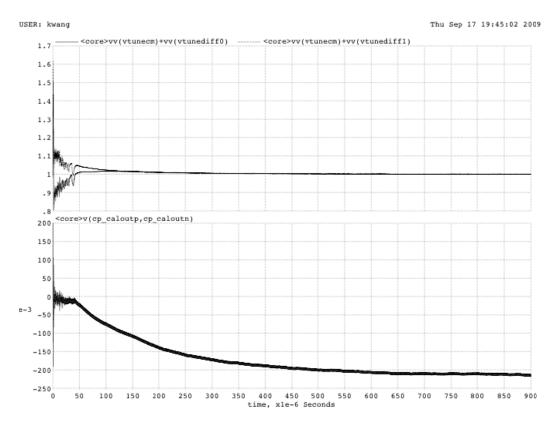

| Fig. 35: | Transient response showing the locking of the RAPLL. The top curve show       | 'S |

|          | the loop filter voltages while the bottom shows the output of the calibration | l  |

|          | loop                                                                          | 82 |

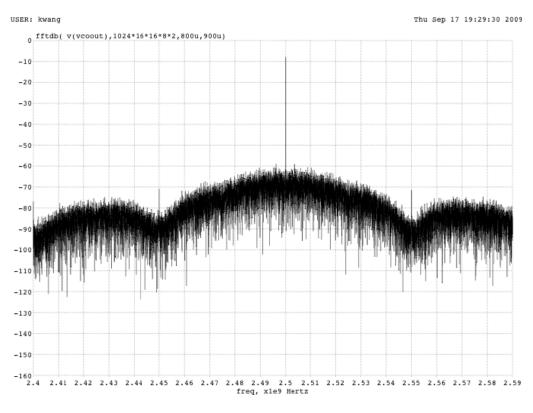

| Fig. 36: | FFT of the VCO output.                                                        | 83 |

## LIST OF TABLES

| Table 1: Performance table. Spur measurements represent the worst case results over |       |

|-------------------------------------------------------------------------------------|-------|

| the four ICs tested                                                                 | 29    |

| Table 2: Comparison of reference spur performance to the previously published st    | ate-  |

| of-the-art                                                                          | 30    |

| Table 3: Comparison of fractional spur performance to the previously published s    | tate- |

| of-the-art                                                                          | 31    |

| Table 4: Comparison of this RAPLL with other works.                                 | 83    |

### **ACKNOWLEDGEMENTS**

I would like to thank Professor Ian Galton for his many years of encouragement and guidance. His enthusiasm and faith in this work even during the most difficult times led to the results presented here.

I would also like to acknowledge and thank all those who shared the lab with me during my stay. I will miss the serious discussions, the not-so-serious discussions, and the many breaks that we had.

Finally, I want to thank my family and Xixiao for their unending support and patience.

Chapter 1, in full, is a reprint of the material as it appears in the Journal of Solid State Circuits, vol. 43, pp. 2787-2797, Dec. 2008. The dissertation author is the primary investigator and author of this paper. Professor Ian Galton supervised the research which forms the basis for this paper.

Chapter 2, in full, has been submitted for review to the IEEE Transactions on Circuits and Systems I: Regular papers. The dissertation author is the primary investigator and author of this paper. Professor Ian Galton supervised the research which forms the basis of this paper.

# VITA

| 1995        | Bachelor of Science, Cornell University                   |

|-------------|-----------------------------------------------------------|

| 1995 – 1996 | Teaching Assistant, University of California, Berkeley    |

| 1996 – 1998 | Research Assistant, University of California, Berkeley    |

| 1998        | Master of Science, University of California, Berkeley     |

| 1998 - 2003 | Member of Staff, Silicon Wave                             |

| 2003 - 2010 | Research Assistant, University of California, San Diego   |

| 2010        | Doctor of Philosophy, University of California, San Diego |

### ABSTRACT OF THE DISSERTATION

Spur Reduction Techniques for Fractional-N PLLs

by

Kevin Jia-Nong Wang

# Doctor of Philosophy in Electrical Engineering (Electronic Circuits and Systems)

University of California, San Diego, 2010

Professor Ian Galton, Chair

Fractional-*N* phase locked loops (PLL) are widely used in modern communication systems to synthesize a highly pure frequency from a lower reference frequency. Stringent requirements are often placed on the spectral purity of the synthesized frequency so that overall system-level requirements are met. Unfortunately, spurious tones are inevitable in the output signals of fractional-*N* PLLs, and in conventional designs they can be attenuated only with design tradeoffs that degrade other aspects of performance.

This dissertation presents a PLL that utilizes a successive requantizer in conjunction with an offset current technique to suppress both the fractional and reference spurs. A passive, type-II, sampled loop filter (SLF) is also introduced to mitigate the increased reference spurs that result from the use of an offset current.

Chapter 1 describes a phase-noise cancelling, fractional-*N* PLL utilizing the techniques mentioned above. It details the system level and circuit level design and presents measured results.

Chapter 2 presents a discrete-time model for a PLL utilizing the passive SLF described in Chapter 1. A mathematical basis for the model is also presented.

Chapter 3 describes an integer-*N*, realigning PLL utilizing a relaxation oscillator and a calibration scheme to suppress the realignment spur. Realignment can suppress the noise of the voltage controlled oscillator (VCO) and hence finds application in systems utilizing non-LC based VCOs. However, implementation challenges exist with regard to the VCO and many previously published designs suffer from a large realignment spur. The use of a relaxation oscillator and the calibration scheme address these two challenges.

### **Chapter I:**

# Spurious Tone Suppression Techniques Applied to a Wide-Bandwidth 2.4GHz Fractional-N PLL

Abstract—This paper demonstrates that spurious tones in the output of a fractional-N PLL can be reduced by replacing the  $\Delta\Sigma$  modulator with a new type of digital quantizer and adding a charge pump offset combined with a sampled loop filter. It describes the underlying mechanisms of the spurious tones, proposes techniques that mitigate the effects of the mechanisms, and presents a phase noise cancelling 2.4GHz ISM-band CMOS PLL that demonstrates the techniques. The PLL has a 975kHz loop bandwidth and a 12MHz reference. Its phase noise has a worst-case reference spur power of -70dBc and a worst-case in-band fractional spur power of -64dBc.

### I. INTRODUCTION

Most wireless communication systems require local oscillators for up-conversion and down-conversion of their transmitted and received signals. Usually, the spectral purity of the local oscillator is a critical factor in overall transceiver performance, so communication standards explicitly or implicitly stipulate stringent spectral purity requirements on the local oscillators [1-2]. In addition to dictating the maximum acceptable phase noise power in various frequency bands, most standards require that spurious tones in the local oscillator's output be highly attenuated, particularly in critical frequency bands.

Local oscillators in such applications are often implemented as fractional-N

phase-locked loops (PLLs). Unfortunately, spurious tones are inevitable in the output signals of fractional-*N* PLLs, and in conventional designs they can be attenuated only with design tradeoffs that degrade other aspects of performance. Generally, spurious tone power can be reduced by increasing the linearity of key circuit blocks such as the charge pump and divider, restricting the choice of reference frequencies, and reducing the loop bandwidth. Unfortunately, increasing linearity tends to increase power consumption and circuit area, restricting the choice of reference frequencies reduces design flexibility, and reducing the loop bandwidth increases in-band phase noise, settling time, susceptibility to oscillator pulling, and loop filter size [1]. Furthermore, these methods of spurious tone reduction become less effective as CMOS circuit technology is scaled into the sub-100 nanometer regime. Therefore, the spurious tone problem negatively affects power consumption, cost, and manufacturability of wireless transceivers, and the problem gets worse as CMOS circuit technology scales with Moore's Law.

This paper presents a 2.4 GHz ISM band fractional-*N* PLL that achieves state-ofthe-art spurious tone suppression enabled by techniques that avoid the tradeoffs mentioned above [3]. One of the techniques is the use of a new type of digital quantizer, called a *successive requantizer*, in place of the digital delta-sigma ( $\Delta\Sigma$ ) modulator used in conventional fractional-*N* PLLs [4]. The other technique involves the combination of a charge pump offset and a sampled loop filter.

The paper consists of four main sections. Section II describes the mechanisms by which the two types of spurious tones, reference spurs and fractional spurs, arise in fractional-*N* PLLs. Section III describes the successive requantizer. Section IV describes the charge pump offset and sampled loop filter. Section V presents additional circuit details and measurement results.

### II. SPURIOUS TONES AND THEIR CAUSES IN FRACTIONAL-NPLLS

### A. Fractional-N PLL Overview

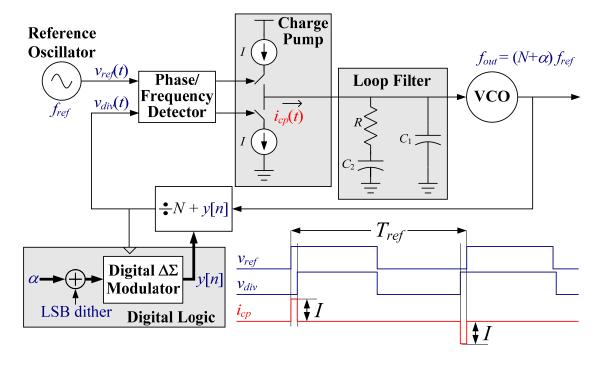

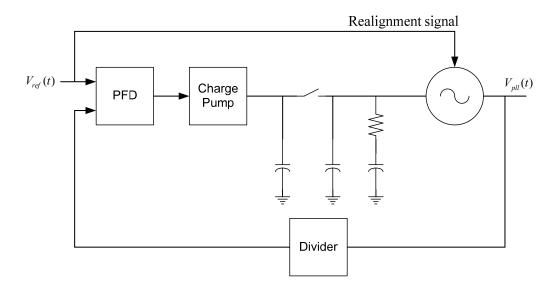

The purpose of a fractional-NPLL is to generate a periodic output signal with frequency  $f_{out} = (N + \alpha)f_{ref}$ , where N is an integer,  $\alpha$  is a fractional value between 0 and 1, and  $f_{ref}$  is the frequency of a reference oscillator (e.g., the crystal frequency). As shown in Figure 1, a typical fractional-N PLL consists of a phase-frequency detector (PFD), a charge pump, a loop filter, a voltage controlled oscillator (VCO), a frequency divider, and a digital  $\Delta\Sigma$  modulator clocked by the divider output [5-7]. The divider output is a twolevel signal in which the *n*th and (n+1)th rising edges are separated by N + y[n] periods of the VCO output, where y[n] is an integer-valued sequence from the  $\Delta\Sigma$  modulator. As indicated in the figure for the case where the PLL is locked, if the *n*th rising edge of the reference signal,  $v_{ref}(t)$ , occurs before that of divider output,  $v_{div}(t)$ , the charge pump generates a current pulse of nominal amplitude I and a duration equal to the time difference between the two edges. Otherwise, the situation is similar except the polarity of the current pulse is reversed. The PLL's feedback adjusts the output frequency so as to zero the DC component of the charge pump output. This causes the output frequency to settle to  $f_{ref}$  times the sum of N and the average of y[n].

Fig. 1: Block diagram of a typical fractional-N PLL.

If y[n] could be set to  $\alpha$  directly, then the output frequency of the PLL would settle to  $(N + \alpha)f_{ref}$ , thereby achieving the goal of the fractional-*N* PLL. Unfortunately, this is not possible. The divider can only count integer VCO cycles so y[n] is restricted to integer values whereas  $\alpha$  is a fractional value. To circumvent this problem y[n] is designed to be a sequence of integers that *average* to  $\alpha$ . The input to the  $\Delta\Sigma$  modulator is  $\alpha$ plus pseudo-random least significant bit (LSB) dither, so its output has the form  $y[n] = \alpha$ + s[n], where s[n] is a zero-mean sequence consisting of spectrally shaped  $\Delta\Sigma$  quantization noise and LSB dither. As proven in [8], the dither prevents s[n] from containing spurious tones that would otherwise show up as spurious tones in the PLL's output. Hence, the output frequency settles to an average  $(N + \alpha)f_{ref}$ , as desired, although s[n] introduces phase noise.

The s[n] sequence causes an amount of charge equal to  $T_{VCO} \cdot I \cdot t[n]$  to be added to

the *n*th charge pump pulse, where  $T_{VCO}$  is the period of the VCO output (for a given value of  $\alpha$ ,  $T_{VCO}$  is well-modeled as a constant) and

$$t[n] = \sum_{k=0}^{n} s[k]$$

(1)

is the *running sum* of s[n]. Hence, the PLL's phase noise contains a lowpass filtered version of t[n]. The bandwidth of the lowpass filtering operation is called the *loop bandwidth* of the PLL. Usually, the quantization noise transfer function of the  $\Delta\Sigma$  modulator is highpass shaped with at least one zero at DC. Therefore, t[n] is bounded and shaped with an order of one less than that of the  $\Delta\Sigma$  modulator's quantization noise transfer function. Provided the loop bandwidth is sufficiently low, the resulting phase noise is suppressed below that from other noise sources in the PLL. Alternatively, a DAC can be used to cancel t[n] prior to the loop filter, thereby minimizing its contribution to the PLL's phase noise so that a much larger loop bandwidth can be used [9-13]. Such fractional-*N* PLL's are called *phase noise cancelling* fractional-*N* PLLs.

#### B. Reference Spurs

Reference spurs are spurious tones in the PLL's output that occur at multiples of  $f_{ref}$  from  $f_{out}$ . They result mainly from periodic disturbances of the loop filter voltage introduced by the charge pump. Therefore, the loop bandwidth and the reference frequency both affect the power of the reference spurs. Widening the loop bandwidth for a given reference frequency or decreasing the reference frequency for a given loop bandwidth both have the effect of reducing the loop filter's attenuation of the disturbances, thereby increasing the power of the reference spurs.

Mismatches between the positive and negative current sources in the charge pump are the primary causes of the disturbances that cause reference spurs. A typical PFD turns on both current sources in the charge pump each reference period for a minimum duration,  $T_D$ , where  $T_D$  is large enough to ensure that both current sources fully settle before they are turned off. Each reference period the PFD turns on the positive current source when the reference edge occurs and the negative current source when the divider edge occurs, and turns them both off simultaneously  $T_D$  seconds after the later of the two edges. The difference between the positive and negative current pulses is the charge pump output current pulse. By ensuring that both current sources have time to settle, a major source of charge pump nonlinearity is avoided [14]. However, inevitable transient and amplitude mismatches between the two current sources give rise to an error component in each charge pump pulse that is constant from period to period. Although the PLL's feedback nulls out the DC component of constant error pulse by adjusting the phase of the VCO, the result is a zero-mean periodic disturbance of the VCO's control voltage which causes a reference spur.

In theory, the disturbance and, therefore, the reference spur could be eliminated by performing an ideal sample-and-hold operation between the loop filter and the VCO once per reference period. The sampled loop filter presented in Section IV provides a practical means of achieving this result to a high degree of accuracy.

### C. Fractional Spurs

Fractional spurs are spurious tones in the PLL's output that occur at multiples of

$af_{ref}$  from  $f_{out}$ .<sup>†</sup> Typically, the most significant fractional spurs are the result of disturbances on the loop filter voltage introduced through the charge pump. Therefore, the power of a fractional spur usually depends on both its frequency and the loop bandwidth. In conventional fractional-*N* PLLs, fractional spurs within the loop bandwidth tend to be large, typically well above -60dBc, while fractional spurs at higher frequencies usually are attenuated by the loop filter. Hence, the power of the fractional spur at  $af_{ref}$  can be reduced by reducing the loop bandwidth for any given values of  $f_{ref}$  and  $\alpha$ . In conventional fractional-*N* PLLs the application's spurious tone suppression requirements typically dictate restrictions on the choice of reference frequency and loop bandwidth so as to ensure that  $af_{ref}$  is sufficiently outside the loop bandwidth for every desired output frequency.

As described in the remainder of this section, fractional spurs arise from two distinct mechanisms. The techniques presented in Sections III and IV respectively address each mechanism to reduce the power of the fractional spurs.

### Fractional Spur Mechanism 1

It is well known that nonlinear parasitic coupling between the VCO output signal and harmonics of the reference signal result in fractional spurs. For example, if the *N*th harmonic of the reference signal intermodulates with the VCO output signal through a parasitic coupling path in the circuit, the intermodulation product is a spurious tone at  $\alpha f_{ref}$ .

<sup>&</sup>lt;sup>†</sup> A fractional spur in the PLL output at a frequency of  $f_{out} + f_{spur}$  is often said to occur at frequency  $f_{spur}$  because it appears at frequency  $f_{spur}$  in a phase noise plot. This terminology is used in the remainder of the paper.

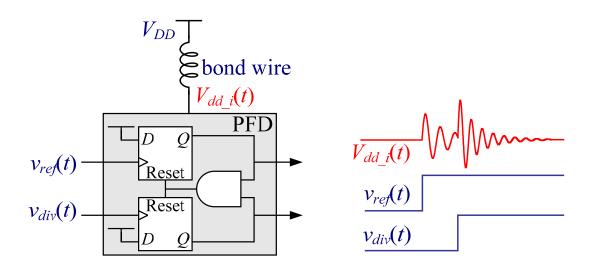

The potential for such coupling is greatest in the PFD and charge pump, as these blocks handle signals aligned with the reference signal as well as those aligned with the VCO output [10]. The hard-switching that occurs within these blocks induces disturbances on the local power supply lines because of the bond wire inductance. This modulates the switching threshold of the digital gates powered by these supplies. As illustrated in Figure 2, the two flip-flops in the PFD capture the phase difference between the divider and reference edges. For small phase differences, the disturbance induced by the earlier edge does not have time to die out before the later edge arrives, so it can modulate the delay through the flip-flop of the later edge, thereby corrupting the phase difference measurement. The resulting error contains intermodulation products of the VCO output and reference signal which are injected into the loop filter and cause fractional spurs. Similar coupling effects occur within the charge pump circuitry.

Fig. 2: Example of a nonlinear coupling path in the PFD

Surprisingly, the digital  $\Delta\Sigma$  modulator in a fractional-*N* PLL is a fundamental source of spurious tones in the PLL's output [3, 4, 9, 15]. This is true even though dither is used to prevent spurious tones in the  $\Delta\Sigma$  modulator's output. Regardless of how dither is applied, spurious tones are induced when the  $\Delta\Sigma$  modulator's quantization noise is subjected to nonlinear distortion. This is particularly problematic in fractional-*N* PLLs wherein the output sequence from the  $\Delta\Sigma$  modulator is converted to analog form and both s[n] and its running sum, t[n], are subjected to nonlinear operations because of non-ideal circuit behavior.

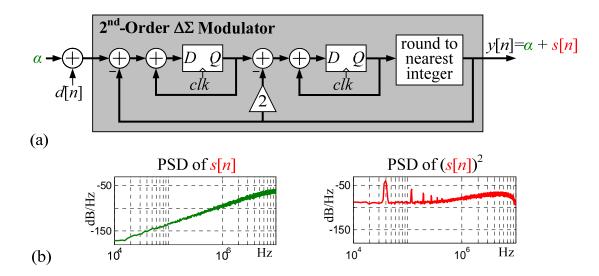

Fig. 3: (a) A second-order digital  $\Delta\Sigma$  modulator, and (b) an example in which s[n] is free of spurious tones but a nonlinearly distorted version of s[n] contains spurious tones.

A digital  $\Delta\Sigma$  modulator often used in fractional-*N* PLLs is shown in Figure 3a as a demonstration vehicle. It is an all-digital structure consisting of two accumulators, a

round-to-the-nearest-integer quantizer, and two negative feedback paths. It is well known that if the  $\Delta\Sigma$  modulator input is kept between 0 and 1, then the output is restricted to the integers: {-1, 0, 1, 2}, and  $s[n] = d[n-2] + e_q[n] - 2e_q[n-1] + e_q[n-2]$ , where  $e_q[n]$  is additive error from the round-to-the-nearest-integer operation of the quantizer. Therefore,  $e_q[n]$  is subjected to the equivalent of a three tap FIR filter with a pair of zero-frequency zeros.

As shown in [8], if the dither sequence, d[n], is an equiprobable two-level, white, random sequence of any non-zero magnitude, then  $e_q[n]$  is guaranteed to be asymptotically white and zero mean. In this case,  $e_q[n]$ , and, hence, s[n], are guaranteed to be free of spurious tones. Moreover, the three tap FIR filtering causes the power spectral density (PSD) of the quantization noise component of s[n] to increase at 12 dB per octave in frequency. For example, the simulated PSD of s[n] is shown in the left plot in Figure 3b for the case where  $\alpha = 0.002$ , d[n] is a white pseudo-random sequence that takes on values of 0 and  $2^{-17}$  with equal probability, and the sample rate is 20 MHz. In this case, the magnitude of the dither is sufficiently small that it is not visible in the PSD plot, yet its presence ensures that spurious tones are avoided in s[n]. However, as shown in the right plot of Figure 3b, spurious tones are clearly present in the PSD of  $(s[n])^2$ . Similar results occur for other types of nonlinear distortion and all other  $\Delta\Sigma$  modulators and dither methods known to the authors. For example, the problem occurs even if the dither sequence is white with a triangular probability density function that extends from -1 to 1 and is added directly to the input of the quantizer.

If it seems counter-intuitive that spurious tones can occur when a spur-free sequence is subjected to nonlinear distortion, consider a random sequence given by

$$q[n] = \begin{cases} \pm 1 \text{ (chosen randomly),} & \text{if } n \text{ is even,} \\ 0, & \text{if } n \text{ is odd.} \end{cases}$$

(2)

It is easy to verify that q[n] is white and, hence, free of spurious tones. However,  $(q[n])^2$  is 1 for even values of *n* and 0 for odd values of *n*, so  $(q[n])^2$  is nothing but a spurious tone at half the sample rate and a constant offset. In this simple case, q[n] has "sufficient randomness" to avoid spurious tones in the absence of nonlinear distortion but not when subjected to even-order nonlinear distortion.

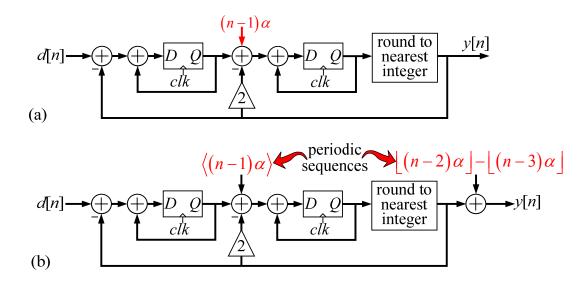

Fig. 4: Structures that are both equivalent to that of Figure 3a.

The situation is conceptually similar, but more complicated, for the case of a  $\Delta\Sigma$  modulator. The interaction of the constant input and the first accumulator gives rise to "hidden periodicities" as indicated in Figure 4. Both structures in Figure 4 are equivalent to that of Figure 3a in that they generate the same y[n] sequence. The structure of Figure 4a differs from that of Figure 3a in that in Figure 4a the  $\alpha$  input has been replaced by its

delayed running sum,  $(n - 1)\alpha$ , added after the first accumulator. This sequence can be written as

$$(n-1)\alpha = \lfloor (n-1)\alpha \rfloor + \langle (n-1)\alpha \rangle \tag{3}$$

where  $\lfloor x \rfloor$  denotes the largest integer less than or equal to *x*, and  $\langle x \rangle$  denotes the fractional part of *x*. The round-to-the-nearest-integer quantizer has no effect on integer-valued components of its input, and the transfer function from the input of the second accumulator to the output of the  $\Delta\Sigma$  modulator is  $z^{-1}(1-z^{-1})$  so the integer-valued component of (3) can be moved after the feedback loops as shown in Figure 4b. The significance is that both additive sequences in Figure 4b associated with  $\alpha$  are periodic with a period that depends on  $\alpha$ , so they are each made up entirely of spurious tones (i.e., their Fourier series components). The dither provides sufficient randomness to avoid spurious tones in s[n] as proven in [8], but not to avoid spurious tones when s[n] is subjected to nonlinear distortion as demonstrated in Figure 3b.

### III. A DELTA-SIGMA MODULATOR REPLACEMENT

The fractional-*N* PLL presented in this paper uses a successive requantizer in place of a  $\Delta\Sigma$  modulator to circumvent fractional spur mechanism 2 [4]. The successive requantizer performs coarse quantization with spectrally shaped quantization noise like a  $\Delta\Sigma$  modulator, but its quantization noise is less susceptible to nonlinearity-induced spurious tones as described below.

Fig. 5: High-level diagram of an example successive requantizer.

A high-level view of successive requantizer is shown in Figure 5. It quantizes a 19-bit input sequence by 16 bits to generate a 3-bit output sequence [3-4]. By design convention, the input and output of the successive requantizer are integer-valued. For the fractional-*N* PLL application, the goal is to quantize  $\alpha$ , which is a fractional value between 0 and 1, and in this design  $\alpha$  is taken to be a constant multiple of  $2^{-16}$ . Therefore,  $\alpha$  is scaled by  $2^{16}$  prior to the successive requantizer to convert it into an integer. As explained below, the 3-bit integer-valued output of the successive requantizer is  $y[n]=\alpha+s[n]$ , where s[n] is quantization noise.

As shown in Figure 5a the successive requantizer consists of 16 *quantization blocks*, each of which simultaneously halves its input and quantizes the result by one bit every sample period. The general form of each quantization block is shown in Figure 5b wherein all variables are integer-valued two's complement numbers. The output of the *d*th quantization block is  $x_{d+1}[n]=(x_d[n]+s_d[n])/2$ , where  $s_d[n]$  a sequence generated within the quantization block. At each time *n*,  $s_d[n]$  is chosen such that  $x_d[n]+s_d[n]$  does not exceed the range of a (20-d)-bit two's complement integer, and the parity of  $s_d[n]$  is the same as that of  $x_d[n]$ . The parity restriction ensures that  $x_d[n]+s_d[n]$  is an even number so its LSB is zero. Discarding the LSB simultaneously halves the quantization block's input value and quantizes the result by one bit. The resulting quantization noise is  $s_d[n]/2$ , so the successive requantizer's overall quantization noise is

$$s[n] = \sum_{d=1}^{16} 2^{d-17} s_d[n].$$

(4)

Therefore, s[n] is a linear combination of the  $s_d[n]$  sequences, so it inherits the properties of the  $s_d[n]$  sequences.

A key feature of the successive requantizer is that the properties of its quantization noise can be engineered by appropriate design of the  $s_d[n]$  sequences. So far, the only restriction on the  $s_d[n]$  sequences is that they must be chosen such that  $x_d[n]+s_d[n]$  is a (20-d)-bit two's complement even integer for each n and d. This leaves considerable flexibility in the design of the  $s_d[n]$  sequences which is exploited to achieve the desired quantization noise properties.

The successive requantizer partially exploits this flexibility to ensure that the running sum of each  $s_d[n]$  sequence, i.e.,

$$t_d[n] = \sum_{k=0}^n s_d[k],$$

(5)

is bounded for all *n*, and each  $s_d[n]$  has a smooth PSD that increases monotonically with frequency. This implies that s[n] is highpass shaped quantization noise that is free of spurious tones and the PSD of s[n] is zero at  $\omega = 0$ .

This still leaves flexibility in the design of the  $s_d[n]$  sequences which is exploited

as described below to ensure that the sequences

$$(s[n])^{p}$$

for  $p = 1, 2, 3, 4, 5$ , and  $(t[n])^{p}$  for  $p = 1, 2, 3,$  (6)

are free of spurious tones, where t[n] is the running sum of s[n] given by (1). The objective is to ensure that the successive requantizer's quantization noise does not introduce significant spurious tones when subjected to the degree of nonlinear distortion expected from the analog circuits within the PLL. Circuit simulations were used during the PLL's design to verify that preventing spurious tones from occurring in the sequences given by (6) is sufficient to achieve this objective.

Fig. 6: Implementation of each quantization block for a successive requantizer with  $s^{p}[n]$ , p = 1, 2, 3, 4, 5, and  $t^{p}[n]$ , p = 1, 2, 3, that are free of spurious tones.

The register transfer level details of the *d*th quantization block are shown in Figure 6. Each value of  $s_d[n]$  is calculated via the combinatorial logic shown in the figure as a function the previous value of  $t_d[n]$ , the parity of the current value of  $x_d[n]$ , and the current value of a 4 bit pseudo-random sequence,  $r_d[n]$ , where  $\{r_d[n], d = 1, 2, ..., 16, n = 0, 1, 2, ...\}$  well-approximate independent identically distributed random variables. For this

design the range of values taken on by  $s_d[n]$  and  $t_d[n]$  are

$$s_d[n] \in \{-3, -2, -1, 0, 1, 2, 3\},$$

and  $t_d[n] \in \{-2, -1, 0, 1, 2\},$  (7)

It can be verified that  $t_d[n]$  is a discrete-valued Markov random sequence conditioned on the parity of  $x_d[n]$ . Whenever  $x_d[n]$  is odd the one-step state transition matrix for  $t_d[n]$  is given by

$$\mathbf{A}_{\mathbf{o}} = \left[ P\{t_d[n] = T_j \mid t_d[n-1] = T_i, o_d[n] = 1\} \right]_{5 \times 5}$$

(8)

and whenever  $x_d[n]$  is even the one-step state transition matrix for  $t_d[n]$  is given by

$$\mathbf{A}_{\mathbf{e}} = \left[ P\{t_d[n] = T_j \mid t_d[n-1] = T_i, o_d[n] = 0\} \right]_{5\times 5}$$

(9)

where  $P\{X \mid Y\}$  denotes the conditional probability of event *X* given event *Y*,  $o_d[n]$  is the LSB of  $x_d[n]$ , and  $T_1 = -2$ ,  $T_2 = -1$ ,  $T_3 = 0$ ,  $T_4 = 1$ ,  $T_5 = 2$ . The specific state transition matrices corresponding to the quantization block shown in Figure 5 are

$$\mathbf{A}_{o} = \begin{bmatrix} 0 & 3/4 & 0 & 1/4 & 0 \\ 3/16 & 0 & 3/4 & 0 & 1/16 \\ 0 & 1/2 & 0 & 1/2 & 0 \\ 1/16 & 0 & 3/4 & 0 & 3/16 \\ 0 & 1/4 & 0 & 3/4 & 0 \end{bmatrix} \text{ and } \mathbf{A}_{e} = \begin{bmatrix} 1/4 & 0 & 3/4 & 0 & 0 \\ 0 & 5/8 & 0 & 3/8 & 0 \\ 1/8 & 0 & 3/4 & 0 & 1/8 \\ 0 & 3/8 & 0 & 5/8 & 0 \\ 0 & 0 & 3/4 & 0 & 1/4 \end{bmatrix}.$$

(10)

As derived in [4], these state transition matrices ensure that the sequences in (6) are free of spurious tones because each is a random process whose autocorrelation function converges to a constant as its time spread increases. Furthermore, the PSD of  $s_d[n]$  has a zero at  $\omega = 0$  and increases at 6 dB per octave as  $\omega$  increases from zero. In this respect, the quantization noise shaping of this version of the successive requantizer is comparable to that of a first-order  $\Delta\Sigma$  modulator.

Successive requantizers with higher than first-order quantization noise shaping

can also be designed. For example, second-order quantization noise shaping can be achieved by quantization blocks that calculate  $s_d[n]$  as a function the running sum of  $t_d[n]$ in addition to  $t_d[n]$ , a random sequence, and the parity of  $x_d[n]$ . However, the fractional-*N* PLL in this work is a phase noise cancelling fractional-*N* PLL, so higher than first-order shaping is not necessary because most of the quantization noise is removed prior to the loop filter via a DAC.

A drawback of the quantization block shown in Figure 6 is that its reduced susceptibility to nonlinearity-induced spurious tones comes at the expense of increased quantization noise power. For example, if it is desired to have quantization noise with a first-order highpass spectral shape, but it is not necessary to prevent nonlinear distortion from inducing spurious tones in the quantization noise and its running sum, a quantization block that implements

$$s_{d}[n] = \begin{cases} 0, & \text{if } x_{d}[n] = \text{even} \\ p_{d}[n], & \text{if } x_{d}[n] = \text{odd and } t_{d}[n-1] = 0, \\ 1, & \text{if } x_{d}[n] = \text{odd and } t_{d}[n-1] = -1, \\ -1, & \text{if } x_{d}[n] = \text{odd and } t_{d}[n-1] = 1, \end{cases}$$

(11)

can be used, where  $p_d[n]$  is an independent random sequence that takes on the values 1 and -1 with equal probability. In this case  $s_d[n]$  takes on values of -1, 0, and 1, whereas the  $s_d[n]$  generated by the quantization block of Figure 6 takes on values of -3, -2, -1,..., 3. Consequently, the power of the quantization noise from a quantization block based on (11) is significantly lower than that from the quantization block of Figure 6.

This example suggests what is likely to be a fundamental tradeoff: reduced susceptibility to nonlinearity-induced spurious tones comes at the expense of increased quantization noise power. The tradeoff has yet to be proven theoretically, but it is exhibited by all variants of the successive requantizer developed to date by the authors. In each case, generating  $s_d[n]$  sequences with reduced susceptibility to nonlinearity-induced spurious tones has required choices to be made that increase the power of the  $s_d[n]$  sequences. This is not a significant problem in phase noise cancelling fractional-*N* PLLs, but it is likely to be an issue in fractional-*N* PLLs without phase noise cancellation. Analytical quantification of the tradeoff and its effect on the performance of fractional-*N* PLLs without phase noise cancellation are ongoing subjects of research.

### IV. A CHARGE PUMP OFFSET AND SAMPLED LOOP FILTER

The fractional-*N* PLL presented in this paper injects a constant current pulse into the loop filter each reference period as a means of mitigating fractional spur mechanism 1 [10]. As shown in Figure 7, an offset pulse generator in parallel with the charge pump introduces a positive current pulse of amplitude *I* starting from the rising edge of the divider output and extending for 8 VCO periods. The offset current pulses cause a fixed VCO phase shift such that in each reference period the divider edge always occurs at least 6 VCO periods prior to the reference edge. Separating the edges in this fashion gives the power supply disturbance described in Section III time to die out between the edges, thereby alleviating the coupling problem.

Fig. 7: The phase-frequency detector, charge pump, offset pulse generator and the associated timing diagram.

Unfortunately, the offset current pulse technique has a severe side-effect if used with a conventional loop filter: transient and amplitude mismatches between the current source in the offset pulse generator and the negative current source in the charge pump add significant power to the reference spur. The effect is more severe than that caused by mismatches between the positive and negative charge pump current sources in a conventional configuration because of the increased duration of the pulses.

Fig. 8: The sampled loop filter and the associated timing diagram.

The side-effect is avoided in this work by the sampled loop filter shown in Figure 8. It differs from the conventional loop filter shown in Figure 1 only in that the  $C_1$  capacitor has been split into two parallel half-sized capacitors separated by a CMOS transmission gate switch. Thus, it reduces to a conventional loop filter when the switch is closed. As indicated in Figure 8, the switch is opened once per reference period for a duration of approximately 25 ns starting 4 VCO periods prior to the rising edge of the divider. This ensures that it is open whenever the loop filter's input current is non-zero. Once the PLL has settled, the voltage across the switch just before it closes each reference period depends only on circuit noise and quantization noise from the successive requantizer. Therefore, to the extent that the switch is ideal, closing the switch each period does not inject periodic disturbances at the reference frequency so reference spurs are avoided. As with other sampled loop filter designs, this design also eliminates reference spurs caused

by mismatches between the current sources in the charge pump [11,16].

The switch is implemented as a transmission gate with half size dummy transmission gates on either side as shown in Figure 8. The dummy transmission gates are shorted and driven in opposite polarity to the main transmission gate. Their purpose is to cancel charge injection from the main transmission gate that would otherwise cause a reference spur.

One way to ensure precise cancellation of the charge injection in such a switch configuration is to design the loop filter and surrounding circuitry so the impedances from the two switch terminals to ground are equal. This could have been achieved by placing a series resistance of 2R and capacitance of  $C_2/2$  from each side of the switch to ground instead of the series resistance of R and capacitance of  $C_2$  on just the right side of the switch as shown in Figure 8. However, doing so would have prevented the voltage on the left side of the switch from settling to a constant each reference period prior to closing the switch, thereby negating the reference frequency suppression property of the sampling process.

Fortunately, the charge injection is well cancelled despite the asymmetry from the series combination of R and  $C_2$ . The edges of the signals that control the transmission gates are sharp, so the charge injected by each MOS transistor is in the form of shortduration, and, hence, high-bandwidth pulses of current. For such a pulse, the impedance of the  $\frac{1}{2}C_1$  capacitors is much lower than that of the resistor except over a small lowfrequency portion of its bandwidth. Therefore, the resistor acts approximately like an open circuit with respect to charge injection pulses, so the series combination of R and  $C_2$  has little effect with respect to charge injection.

## V. ADDITIONAL CIRCUIT DETAILS AND MEASUREMENT RESULTS

A simplified functional diagram of the phase noise cancelling fractional-*N* PLL IC prototype is shown in Figure 9 and a die photograph of the IC is shown in Figure 10. Its reference frequency is 12 MHz, and its output frequency range covers the 2.4 GHz ISM band. The phase noise cancellation enables a loop bandwidth of 975 kHz which is close to the  $f_{ref}/10$  loop bandwidth upper limit for stability [17].

Fig. 9: High-level diagram of the integrated circuit prototype.

Fig. 10: Die photograph.

The IC is a modified version of that presented in [13]. The primary modifications are that the successive requantizer shown in Figures 5 and 6, the offset pulse generator shown in Figure 7, and the sampled loop filter shown in Figure 8 have been included. The other circuit blocks of the PLL described in [13] have been reused with relatively minor changes. For comparison, the PLL includes the  $\Delta\Sigma$  modulator shown in Fig. 2a which can optionally be used instead of the successive requantizer, the offset pulse generator can be enabled or disabled, and the loop filter's sampling can be enabled or disabled. With sampling disabled, the loop filter reduces to a conventional loop filter.

The divider is similar to that presented in [13] except with minor changes to provide timing signals that control the offset current generator and open the loop filter switch each reference period. As described in [13] the necessary timing signals are obtained by a chain of flip-flops clocked at half the VCO frequency. The timing signal used to close the loop filter switch each reference period could similarly have been derived within the divider block, but an RC one-shot circuit with a nominal duration of 25 ns is used instead for simplicity because the length of time the switch is left open is not critical. Provided the switch is open when the loop filter's input current is non-zero, the PLL dynamics are relatively insensitive to the length of time it is open.

A representative close-in PSD plot of the PLL's output with the successive requantizer, offset pulse generator, and sampled loop filter enabled and  $\alpha$  chosen such that  $\alpha f_{ref} = 50$  kHz is shown in Figure 11. As expected fractional spurs occur at multiples of 50 kHz. Although the fractional spurs are well inside the 975 kHz loop bandwidth, they are all below -70 dBc in power.

Fig. 11: Representative measured close-in output spectrum for the case of  $af_{ref} = 50$  kHz.

To evaluate the fractional spur performance of the PLL comprehensively it is necessary to perform the measurement shown in Figure 11 for many values of  $\alpha$  ranging between 0 and 1. Figure 12 presents the results of such measurements for four cases: 1) the  $\Delta\Sigma$  modulator enabled and the offset pulse generator disabled, 2) the successive requantizer enabled and the offset pulse generator disabled, 3) the  $\Delta\Sigma$  modulator enabled and the offset pulse generator enabled, and 4) the successive requantizer enabled and the offset pulse generator enabled. For each case, the figure shows the measured power of the largest spurious tone in the PLL's phase noise for each of 100 values of  $\alpha$  ranging between 0 and 1.

Fig. 12: Power levels of the largest measured fractional spurs with and without the enhancements enabled for 100 PLL frequency offsets in the range  $0 < a f_{ref} < 12$ MHz.

As shown in Figure 12, the fractional spur powers for the two cases in which the offset pulse generator is disabled are almost identical, and are much higher than the corresponding fractional spur powers for the two cases in which the offset pulse generator is enabled. This suggests that fractional spur mechanism 1 is dominant over fractional spur mechanism 2. With the  $\Delta\Sigma$  modulator, enabling the offset pulse generator reduces the fractional spur powers by a maximum of 9 dB, and with the successive requantizer, enabling the offset pulse generator reduces the fractional spur powers by a maximum of 27 dB. This suggests that once fractional spur mechanism 1 is circumvented, fractional spur mechanism 2 becomes significant. By circumventing fractional spur mechanism 2, the successive requantizer results in a maximum fractional spur power reduction of 18 dB relative to the  $\Delta\Sigma$  modulator case.

As indicated in Figure 12, in each case the fractional spur powers are relatively constant for small values of  $\alpha$  but decrease as  $\alpha$  increases above about 0.055. This is expected because the frequencies of the fractional spurs increase with  $\alpha$ , so after a point they move outside the loop bandwidth and are attenuated. An unusually large loop bandwidth has been used in this work to provide a worst-case scenario in which to demonstrate the spurious tone suppression techniques presented in the paper. The roll-offs shown in Figure 12 would start at smaller values of  $\alpha$  if the loop bandwidth were decreased.

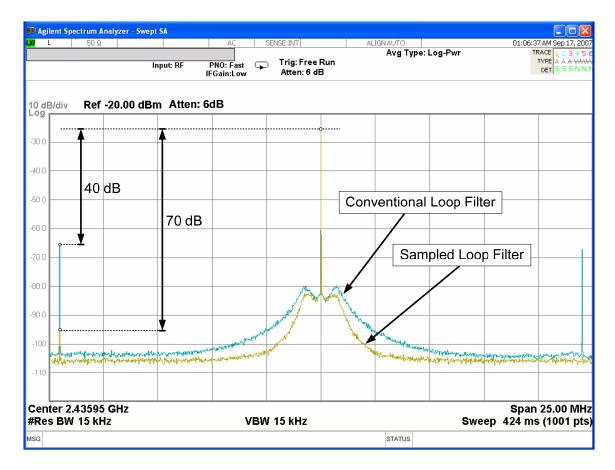

Fig. 13: Representative measured spectra with the sampled loop filter enabled and disabled.

Representative measured PSD plots of the PLL output over a 25 MHz span are

shown in Figure 13 for the PLL with the sampled loop filter and the PLL with the conventional loop filter. With the conventional loop filter the reference spur power is -40 dBc, which is large because of the large loop bandwidth and low reference frequency. With the sampled loop filter, the reference spur drops to -70 dBc.

Furthermore, it can be seen in Figure 13 that the phase noise away from the carrier is lower for the case of the sampled loop filter than for the case of the conventional loop filter. This is expected [18]. As described in [9], practical circuit limitations dictate that the current pulses from the charge pump have a fixed amplitude but variable widths whereas those from the DAC have a fixed width but variable amplitudes. Hence, even with perfect matching the component of the voltage corresponding to quantization noise at the node where the DAC and charge pump are connected can only be cancelled perfectly between the DAC and charge pump current pulses. When the pulses are non-zero, imperfectly cancelled current associated with quantization noise disturbs the node. Without sampling, the disturbance modulates the VCO, thereby increasing the phase noise. With sampling, the VCO is shielded from the disturbance.

| Design Details                                                 |                                        |         |  |  |  |  |

|----------------------------------------------------------------|----------------------------------------|---------|--|--|--|--|

| Technology                                                     | 0.18 um 1P6M CMOS                      |         |  |  |  |  |

| Package and Die area                                           | 32 pin TQFN,                           |         |  |  |  |  |

|                                                                | $2.2 \text{ mm} \times 2.2 \text{ mm}$ |         |  |  |  |  |

| Vdd                                                            | 1.8 V                                  |         |  |  |  |  |

| Reference frequency                                            | 12 MHz                                 |         |  |  |  |  |

| Output frequency                                               | 2.4 – 2.5 GHz                          |         |  |  |  |  |

| Measured loop bandwidth                                        | 975 kHz                                |         |  |  |  |  |

| Measured Current Consumption                                   |                                        |         |  |  |  |  |

| VCO and Divider Buffer                                         | 5.9 mA                                 |         |  |  |  |  |

| Divider                                                        | 7.3 mA                                 |         |  |  |  |  |

| Charge Pump, PFD, and Buffers                                  | 8.6 mA                                 | Core    |  |  |  |  |

| Offset Current                                                 | 0.6 mA                                 | 27.1 mA |  |  |  |  |

| Digital                                                        | 1.9 mA                                 |         |  |  |  |  |

| DAC                                                            | 2.8 mA                                 |         |  |  |  |  |

| Bandgap Bias Generator                                         | 5.4 mA                                 |         |  |  |  |  |

| Crystal Buffer                                                 | 2.7 mA                                 | 9.8 mA  |  |  |  |  |

| External Buffer                                                | 1.7 mA                                 |         |  |  |  |  |

| Measured Integer-N Performance                                 |                                        |         |  |  |  |  |

| Phase Noise at 100 kHz                                         | -103 dBc/Hz                            |         |  |  |  |  |

| Phase Noise at 3 MHz                                           | -125 dBc/Hz                            |         |  |  |  |  |

| Reference spur without sampling enabled                        | -58 dBc                                |         |  |  |  |  |

| Reference spur with sampling enabled                           | nce spur with sampling enabled -70 dBc |         |  |  |  |  |

| Measured Fractional-N Performance                              |                                        |         |  |  |  |  |

| Phase Noise at 100 kHz                                         | -98 dBc/Hz                             |         |  |  |  |  |

| Phase Noise at 3 MHz                                           | -121 dBc/Hz                            |         |  |  |  |  |

| Worst case in-band fractional spur with $\Delta\Sigma$ modula- | -45 dBc                                |         |  |  |  |  |

| tor                                                            |                                        |         |  |  |  |  |

| Worst case in-band fractional spur with SR                     | -64 dBc                                |         |  |  |  |  |

| Reference spur without sampling enabled                        | -40 dBc                                |         |  |  |  |  |

| Reference spur with sampling enabled                           | -70 dBc                                |         |  |  |  |  |

Table 1: Performance table. Spur measurements represent the worst case results over the four ICs tested.

Four copies of the IC were tested. Table 1 shows the worst-case measurements taken from the four ICs. The fractional spur results for one of the ICs are shown in Figure 12, and two other of the ICs exhibited very similar results. However, one of the ICs exhibited a worst case fractional spur power of -64 dBc at a small number of frequencies

near the edge of the loop bandwidth. At all other frequencies, it behaved similarly to the other three ICs.

An IC wiring mistake disabled the DAC calibration circuitry described in [13], so the measurements described above were made after a one-time manual adjustment of the DAC gain. To confirm the diagnosis of the mistake, it was corrected in one copy of the IC by FIB microsurgery, but with the anticipated side effect of a coupling path that increased the measured in-band phase noise, 3MHz phase noise, and largest in-band fractional spur by 10dB, 3dB, and 3dB, respectively, above those shown in Table 1.

| Reference | Loop      | Reference spur | Normalized     |           |

|-----------|-----------|----------------|----------------|-----------|

| frequency | bandwidth | magnitude      | reference spur | Reference |

| (MHz)     | (kHz)     | (dBc)          | (dBc)          |           |

| 12        | 975       | -70            | -70            | This work |

| 8         | 120       | -81            | -52            | [19]      |

| 50        | 1000      | -74            | -50            | [11]      |

| 12        | 730       | -53            | -48            | [13]      |

| 1         | 40        | -62            | -50            | [16]      |

Table 2: Comparison of reference spur performance to the previously published state-of-the-art.

Table 2 compares the PLL's reference spur performance to the previously published state-of-the-art. To a good approximation, the loop filter disturbance that causes reference spurs in a PLL is attenuated by -40dB per decade in frequency above the loop bandwidth. Therefore, to compare the reference spur powers of any two PLLs meaningfully, the difference between their reference-frequency-to-loop-bandwidth ratios must be considered. For each PLL, Table 2 shows both the measured reference spur power as well as the *normalized reference spur power*, which is the power that the reference spur would have had had the reference frequency-to-loop-bandwidth ratio been 12 MHz/975 kHz as in this paper. As shown the in table, the reference spur performance of the PLL

| Reference Loop     |                    | Reported fractional spur |                    | Equivalent<br>in-band    | Deferrere    |

|--------------------|--------------------|--------------------------|--------------------|--------------------------|--------------|

| frequency<br>(MHz) | bandwidth<br>(kHz) | Frequency<br>(kHz)       | Magnitude<br>(dBc) | fractional spur<br>(dBc) | Reference    |

| 12                 | 975                | 50                       | -70                |                          | This work    |

| 50                 | 1000               | "In-band"                | -45                |                          | [11]         |

| 35                 | 700                | 8.5                      | -60                |                          | [10]         |

| 50                 | 500                | 400                      | -42                |                          | [20]         |

| 50                 | 390                | 98                       | -48                |                          | [21]         |

| 12                 | 730                | 1000                     | -47                | -42                      | [13]         |

| 25                 | 1000               | 3125                     | -55                | -36                      | [22]         |

| 33                 | 200                | 257                      | -40                | -36                      | [23]         |

| 26                 | 35                 | 2080                     | -100               | -20                      | [15, 24, 25] |

presented in this paper exceeds the previous state-of-the-art by 18 dB.<sup>†</sup>

Table 3: Comparison of fractional spur performance to the previously published state-of-the-art.

Table 3 compares the PLL's fractional spur performance to the previously published state-of-the-art. Unfortunately, comprehensive fractional spur measurement results such as shown in Figure 12 are rare in the previously published literature. In most cases, fractional spur powers are only reported for a small number of frequencies, often above the loop bandwidth. In cases where the power of a fractional spur within the loop bandwidth has been reported, the value is shown in Table 3 and it is assumed to be representative of all fractional spurs within the loop bandwidth. In cases for which the power of a fractional spur within the loop bandwidth is not reported, Table 2 provides an *equivalent in-band fractional spur power* obtained by adding the attenuation imposed by the PLL on the fractional spur given its position relative to the loop bandwidth. As in the case of the reference spur, the attenuation is taken to be -40dB per decade in frequency above the

<sup>&</sup>lt;sup>†</sup> A JSSC paper by A. Maxim reports a PLL with a normalized reference spur of -73dBc. However, it has recently been determined by the Editor-in-Chief of the JSSC that this result is fraudulent, so it has not been included in the table.

loop bandwidth. As shown in the table, the fractional spur performance of the PLL presented in this paper exceeds the previous state-of-the-art by 10 dB.

#### ACKNOWLEDGEMENT

Chapter 1, in full, is a reprint of the material as it appears in the Journal of Solid State Circuits, vol. 43, pp. 2787-2797, Dec. 2008. The dissertation author is the primary investigator and author of this paper. Professor Ian Galton supervised the research which forms the basis for this paper.

## REFERENCES

- [1] B. Razavi, *Phase-Locking in High-Performance Systems: From Devices to Architectures*, Wiley-Interscience, 2003.

- [2] T. H. Lee, *The Design of CMOS Radio-Frequency Integrated Circuits*, Second Edition, Cambridge University Press, 2003.

- [3] K. Wang, A. Swaminathan, I. Galton, "Spurious-tone suppression techniques applied to a wide-bandwidth 2.4GHz fractional-N PLL", *IEEE International Solid-State Circuits Conference*, Digest of Technical Papers, February 2008.

- [4] A. Swaminathan, A. Panigada, E. Masry, I. Galton, "A digital requantizer with shaped requantization noise that remains well behaved after non-linear distortion," *IEEE Transactions on Signal Processing*, vol. 55, no. 11, pp. 5382-5394, November 2007.

- [5] B. Miller, B. Conley, "A multiple modulator fractional divider," *Annual IEEE Symposium on Frequency Control*, vol. 44, pp. 559-568, March 1990.

- [6] B. Miller, B. Conley, "A multiple modulator fractional divider," *IEEE Transactions*

on Instrumentation and Measurement, vol. 40, no. 3, pp. 578-583, June 1991.

- [7] T. A. Riley, M. A. Copeland, T. A. Kwasniewski, "Delta-sigma modulation in fractional-N frequency synthesis," *IEEE Journal of Solid-State Circuits*, vol. 28, no. 5, pp. 553-559, May, 1993.

- [8] S. Pamarti, J. Welz, I. Galton, "Statistics of the quantization noise in 1-bit dithered single-quantizer digital delta-sigma modulators," *IEEE Transactions on Circuits* and Systems - I: Regular Papers, vol. 54, no. 3. pp. 492-503, March 2007.

- [9] S. Pamarti, L. Jansson, I. Galton. "A wideband 2.4GHz ΔΣ fractional-N PLL with 1 Mb/s in-loop modulation," *IEEE Journal of Solid-State Circuits*, vol. 39, no. 1, pp. 49-62, January 2004.

- [10] E. Temporiti, G. Albasini, I. Bietti, R. Castello, M. Colombo. "A 700kHz Bandwidth ΣΔ Fractional Synthesizer with Spurs Compensation and Linearization Techniques for WCDMA Applications," *IEEE Journal of Solid-State Circuits*, vol. 39, no. 9, pp. 1446-1454, September 2004.

- [11] S. E. Meninger, and M. H. Perrott. "A 1MHz bandwidth 3.6GHz 0.18um CMOS fractional-N synthesizer utilizing a hybrid PFD/DAC structure for reduced broadband phase noise," *IEEE Journal of Solid-State Circuits*, vol. 41, no. 4, pp. 966-980, April 2006.

- [12] M. Gupta and B. S. Song. "A 1.8GHz spur cancelled fractional-N frequency synthesizer with LMS based DAC gain calibration," *IEEE Journal of Solid-State Circuits*, vol. 41, no. 12, pp. 2842-2851, Dec. 2006.

- [13] A. Swaminathan, K. Wang, I. Galton, "A wide-bandwidth 2.4GHz ISM-band fractional-N PLL with adaptive phase-noise cancellation," *IEEE Journal of Solid-State Circuits*, pp. 2639-2650, Dec. 2007.

- [14] B. Razavi, Design of Analog CMOS Integrated Circuits, McGraw Hill, 2001.

- [15] B. De Muer, M. Steyaert. "A CMOS Monolithic ΔΣ-Controlled Fractional-N Frequency Synthesizer for DCS-1800," *IEEE Journal of Solid-State Circuits*, vol. 37, no. 7, July 2002.

- [16] B. Zhang, P. E. Allen, J. M. Huard, "A fast switching PLL frequency synthesizer with an on-chip passive discrete-time loop filter in 0.25-µm CMOS," *IEEE Journal* of Solid-State Circuits, vol. 38, pp. 855 – 865, June 2003.

- [17] F. M. Gardner, "Charge-pump phase-lock loops," IEEE Transactions on Communi-

cations, vol. COM-28, pp. 1849-1858, November 1980.

- [18] L. Liu, B. Li, "Phase Noise Cancellation for a  $\Sigma$ - $\Delta$  Fractional-*N* PLL Employing a Sample-and-hold Element," Asia-Pacific Microwave Conference, December 2005.

- [19] C. Liang, H. Chen, S. Liu, "Spur-Suppression Techniques for Frequency Synthesizers," *Circuits and Systems II: Express Briefs, IEEE Transactions on*, vol. 54, no. 8, pp. 653-657, Aug. 2007.

- [20] C.-M. Hsu, M. Z. Straayer, M. H. Perrott., "A Low-Noise, Wide-BW 3.6Ghz Digital ΔΣ Fractional-N Frequency Synthesizer with a Noise-Shaping Time-to-Digital Converter and Quantization Noise Cancellation," *IEEE International Solid-State Circuits Conference*, Digest of Technical Papers, pp. 340-341, 617, February 2008.

- [21] K. Tajima, R. Hayashi, T. Takagi, "New suppression scheme of ΔΣ fractional-N spurs for PLL synthesizers using analog phase detectors," *Microwave Symposium Digest, 2005 IEEE MTT-S International*, pp. 4, 12-17 June 2005.

- [22] C. Park, O. Kim, B. Kim, "A 1.8-GHz self-calibrated phase-locked loop with precise I/Q matching," *IEEE Journal of Solid-State Circuits*, vol. 36, no. 5, pp.777-783, May 2001.

- [23] Y.-C. Yang, S.-A. Yu, Y.-H. Liu, T. Wang, S.-S. Lu, "A Quantization Noise Suppression Technique for ΔΣ Fractional-N Frequency Synthesizers," *IEEE Journal of Solid-State Circuits*, vol. 41, no. 11, pp. 2500-2511, November 2006.

- [24] B. De Muer, M. S. J. Steyaert, "On the analysis of  $\Delta\Sigma$  fractional-N frequency synthesizers for high-spectral purity," *Circuits and Systems II: Analog and Digital Signal Processing, IEEE Transactions on*, vol. 50, no.11, pp. 784-793, November 2003.

- [25] B. De Muer, M. Steyaert, CMOS Fractional-N Synthesizers, Design for High Spectral Purity and Monolithic Integration, Kluwer, Norwell, MA, 2003.

# **Chapter II:**

# A Discrete-Time Model For the Design of Type-II PLLs with Passive Sampled Loop Filters

*Abstract*—Type-II charge pump PLLs are used extensively in electronic systems for frequency synthesis. Recently, a passive sampled loop filter (SLF) was shown to offer major benefits over the conventional continuous-time loop filter (CLF) traditionally used in such PLLs. These benefits include greatly enhanced reference spur suppression, elimination of charge pump pulse-position modulation nonlinearity, and, in the case of phase noise cancelling fractional-*N* PLLs, improved phase noise cancellation. The main disadvantage of the SLF to date has been the lack of a linear time-invariant (LTI) model with which to perform the system-level design of SLF-based PLLs. Without such a model, designers are forced to rely on trial and error iteration supported by lengthy transient simulations. This paper presents an accurate LTI model of SLF-based Type-II PLLs that eliminates this disadvantage.

# **INTRODUCTION**

Integer-*N* and fractional-*N* phase locked loops (PLLs) are used extensively in electronic systems to synthesize higher frequency signals from lower-frequency references. The majority of these PLLs are charge pump based Type-II PLLs [1].

Recently, sampled loop filters (SLFs) have been shown to offer advantages over continuous-time loop filters (CLFs) in PLLs. SLFs can greatly reduce reference spurs in both integer-*N* and fractional-*N* PLLs, [2, 3]. They eliminate charge pump pulse-position modulation distortion in fractional-*N* PLLs [4, 5], and they improve phase noise cancellation in phase noise cancelling fractional-*N* PLLs [5, 6]. Moreover, SLFs eliminate the large reference spur that would otherwise arise as a side effect of the charge pump offset current method for reducing fractional spurs in fractional-*N* PLLs [3, 7].

Several different types of SLFs for PLLs have been published. In [4] an active SLF is implemented by preceding a CLF with an op-amp based sample-and-hold circuit. In [2] a passive switched-capacitor SLF is implemented for a type-I PLL. In [3], a passive SLF is implemented with the addition of a transistor switch within an otherwise conventional CLF.

The SLF presented in [3] offers a major benefit over the other SLFs: it is the only published passive SLF applicable to Type-II PLLs. The sampling operation involves only a single switch, so it consumes very little power and circuit area beyond those of a comparable CLF. Its applicability to Type-II PLLs is important because such PLLs are by far the most widely used PLLs at present. Furthermore, the SLF has been demonstrated in a fractional-*N* PLL with record-setting reference and fractional spur performance.

The main drawback to date of the SLF presented in [3] has been the lack of a linear, time-invariant (LTI) model with which to perform the system-level design of PLLs based on the SLF. Without such a model, designers are forced to rely on trial and error iteration and lengthy transient simulations as their primary design tools.

Despite its implementation simplicity, the SLF presented in [3] is more difficult to analyze than the other published SLFs because it behaves as a time-varying continuoustime filter. Therefore, it cannot be well-approximated as a continuous-time LTI system. Nevertheless, as proven in this paper, PLLs based on the SLF can be modeled accurately as discrete-time LTI systems. The paper derives such an LTI model, and demonstrates how it enables the system-level design of PLLs without the need to resort to computer simulation. Hence, the results of the paper eliminate the drawback described above.

The model yields equations which accurately predict the transfer functions, bandwidth, and phase margin of the PLL in terms of its component values. While the equations are not simple, they each have closed form. They can be implemented easily in a tool such as Matlab and used to rapidly generate results that heretofore required lengthy transient simulations. The PLL design process is inherently iterative, so not having to simulate the PLL at each iteration step significantly speeds up the design process.

The paper is organized such that all the information required to use the model to design PLLs is presented separately from the derivation of the model. This allows readers to use the model prior to understanding its derivation. The information required to use the model is presented in Sections II-III and Appendix A, and the detailed mathematical derivation of the model is presented in Section IV and Appendix B.

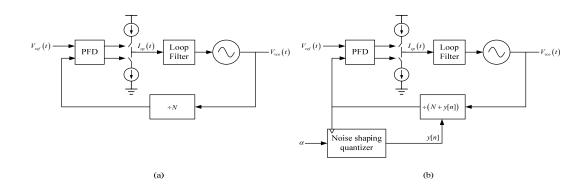

#### OVERVIEW OF THE SAMPLED LOOP FILTER PLL

The block diagram of a typical charge-pump based integer-*N* PLL is shown in Fig. 14a [1]. Its purpose is to generate a spectrally pure periodic output signal with a frequency of  $Nf_{ref}$ , where *N* is a positive integer, and  $f_{ref}$  is the frequency of the reference signal,  $V_{ref}(t)$ . It consists of a phase-frequency detector (PFD), a charge pump (CP), a lowpass loop filter (LF), a voltage controlled oscillator (VCO), and a digital divider.

Fig. 14: Block diagram of a typical (a) integer-N PLL and (b) fractional-N PLL.

The divider output is a two-level signal in which the *n*th and (n+1)th rising edges, for n = 0, 1, 2, ..., are separated by *N* periods of the VCO output. The PFD compares the positive-going edges of the reference signal to those of the divider's output signal and causes the charge pump to drive the loop filter with current pulses whose widths are proportional to the phase difference between the two signals. The pulses are lowpass filtered by the loop filter and the resulting waveform drives the VCO.

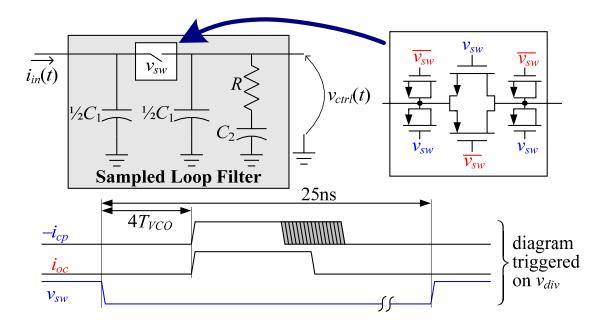

Fig. 15a shows a continuous-time loop filter, and Fig. 15b shows the sampled loop filter addressed in this paper. The SLF differs from the continuous-time LF only in that it includes a switch which splits  $C_p$  into  $\lambda C_p$  and  $(1-\lambda)C_p$ , where  $0 < \lambda < 1$ . For example, in [3],  $\lambda = 0.5$ . The switch is opened and closed once per reference period such that when the PLL is locked,  $\lambda C_p$  and  $(1-\lambda)C_p$  are disconnected whenever  $I_{cp}(t) \neq 0$ . As explained and experimentally demonstrated in [3], this significantly reduces the reference spur compared to the conventional LF.

Fig. 15: Circuit diagram of (a) a continuous time loop filter with the VCO and (b) a sampled loop filter with VCO and (c) the timing of  $V_{switch}(t)$ .

The switch is controlled by the two-level signal  $V_{switch}(t)$ ; it is closed when  $V_{switch}(t)$  is high, and open when  $V_{switch}(t)$  is low. A typical waveform for  $V_{switch}(t)$  is shown in Fig. 15c. The *n*th reference period is defined as the time interval between the *n*th and (n + 1)th rising edges of the reference signal. In the case of a noise-free reference signal, these edges occur at times  $nT_{ref}$  and  $(n + 1)T_{ref}$ , respectively, where  $T_{ref} = 1/f_{ref}$ . As indicated in Fig. 15c, during each reference period, the switch is first open for a duration of  $t_{op1}$ , then closed for a duration of  $t_{cl}$ , and then open for a duration of  $t_{op2}$ , where  $t_{op1}$ ,  $t_{cl}$ , and  $t_{op2}$  are constants chosen by the designer. Together with the loop filter components, these constants define the behavior of the SLF.

As described in Section III and suggested by the model equations in Appendix A, decreasing  $t_{cl}$  has the effect of decreasing the phase margin of the PLL whereas the values of  $t_{op1}$  and  $t_{op2}$  for any given value of  $t_{cl}$  have little effect on the dynamics of the PLL. Therefore,  $t_{op1}$ ,  $t_{cl}$ , and  $t_{op2}$  should be chosen such that  $t_{cl}$  is as large as possible subject to

the requirement that the switch be open whenever  $I_{cp}(t) \neq 0$  once the PLL is locked.

The block diagram of a typical charge-pump based fractional-*N* PLL is shown in Fig. 14b [1]. Its purpose is to generate a spectrally pure periodic output signal with a frequency of  $(N + \alpha)f_{ref}$ , where *N* is again a positive integer and  $\alpha$  is a fractional value between 0 and 1. The fractional-*N* PLL differs from the integer-*N* PLL only in that the *n*th and (*n*+1)th rising edges of the divider output, for n = 0, 1, 2, ..., are separated by N + y[n] periods of the VCO output, where y[n] is the integer-valued output sequence from a noise-shaping quantizer with input  $\alpha$ . Typically, the noise-shaping quantizer is a digital delta-sigma modulator, but other types of quantizers such as a successive requantizer can also be used [3].

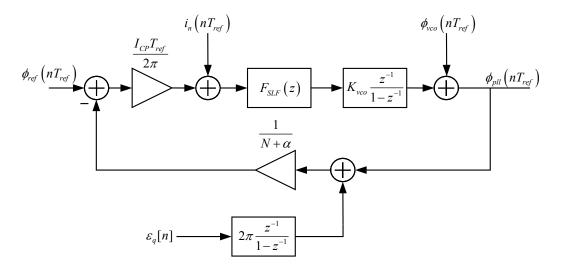

#### DESCRIPTION AND APPLICATION OF THE PLL MODEL

This section describes the proposed model of the PLLs shown in Fig. 14 with the SLF of Fig. 15b, and explains how the model can be used to analyze and design such PLLs. The mathematical derivations that underlie the models are deferred to Section IV and Appendix B.

#### Model Description

The phase of the fractional-*N* PLL's output signal at time *t* can be written as

$$2\pi (N+\alpha) f_{ref} t + \phi_{pll}(t) \tag{12}$$

where  $\phi_{pll}(t)$  represents the PLL's phase error, i.e., the difference between the actual phase and ideal phase of the PLL output signal at time *t*.

The purpose of a PLL model is to provide a simple means of evaluating  $\phi_{pll}(t)$  in terms of the PLL's design parameters and error signals such as circuit noise, assuming

the PLL is already locked. PLLs are neither linear nor time-invariant, but when locked they can be approximated as linear time-invariant (LTI) systems. For example, the most commonly used model for PLLs with conventional loop filters is a continuous-time LTI system that accurately models the locked behavior of such PLLs [8, 9, 12]. Discrete-time LTI models have also been developed for such PLLs [8, 10, 11].

The model presented in this section is a discrete-time LTI system applicable to the SLF-PLL. As described in the next section, the sampling operation of the SLF would result in a time-varying continuous-time model which would be difficult to analyze, and this problem is avoided by using a discrete-time model.

Two versions of the model are presented: a single-rate version and a multi-rate version. The single-rate version provides samples of  $\phi_{pll}(t)$  at a sample-rate of  $f_{ref}$ . The multi-rate version provides samples of  $\phi_{pll}(t)$  at a sample-rate of  $Lf_{ref}$ , where  $L \ge 2$  is a positive integer.

The two versions of the model are identical in terms of how they represent the PLL's feedback behavior, but the latter performs interpolation to obtain an extra L - 1 output samples per reference period. When  $\phi_{pll}(t)$  has most of its power concentrated at frequencies with magnitudes less than  $f_{ref}/2$ , the single-rate version of the model is sufficient. The multi-rate version, although more complicated than the single-rate version, is useful in cases where  $\phi_{pll}(t)$  has enough power at frequencies with magnitudes above  $f_{ref}/2$  that it is necessary to sample  $\phi_{pll}(t)$  at a higher sample-rate than  $f_{ref}$ .

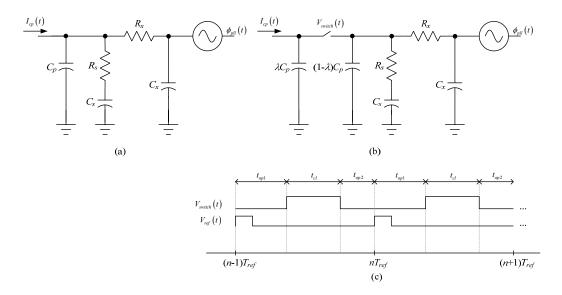

Fig. 16: Single rate discrete-time, linearized model of a SLF-PLL with noise sources.

The single-rate version of the model is shown in Fig. 16, where  $I_{CP}$  is the magnitude of current pulses sourced and sunk by the charge pump,  $i_n(nT_{ref})$  is charge pump noise sampled at  $nT_{ref}$ ,  $\phi_{ref}(nT_{ref})$  is the reference signal's phase noise sampled at  $nT_{ref}$ ,  $\phi_{vco}(nT_{ref})$  is the open-loop VCO phase noise sampled at  $nT_{ref}$ ,  $\varepsilon_q[n] = y[n] - \alpha$  is the quantization noise from the noise-shaping quantizer,

$$F_{SLF}(z) = K \frac{(1 - \gamma_1 z^{-1})(1 - \gamma_2 z^{-1})(1 - \gamma_3 z^{-1})}{(1 - z^{-1})(1 - \beta_2 z^{-1})(1 - \beta_3 z^{-1})}$$

(13)