# **UC Berkeley**

# **UC Berkeley Electronic Theses and Dissertations**

### **Title**

Empowering Large Language Models with Efficient and Automated Systems

### **Permalink**

https://escholarship.org/uc/item/2kp379f3

### **Author**

Li, Zhuohan

### **Publication Date**

2024

Peer reviewed|Thesis/dissertation

### Empowering Large Language Models with Efficient and Automated Systems

By

### Zhuohan Li

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Ion Stoica, Chair Associate Professor Joseph E. Gonzalez Associate Professor Matei Zaharia Professor Eric P. Xing

Summer 2024

# Empowering Large Language Models with Efficient and Automated Systems

Copyright 2024

by

Zhuohan Li

#### Abstract

Empowering Large Language Models with Efficient and Automated Systems

by

#### Zhuohan Li

Doctor of Philosophy in Computer Science

University of California, Berkeley

Professor Ion Stoica, Chair

Large Language Models (LLMs) have shown remarkable capabilities in a variety of tasks, including chatting, programming, and searching. However, the high costs of LLMs are preventing these models from being deployed for the vast majority of applications. In this dissertation, we focus on building efficient and automated systems to reduce costs and democratize access to large language models.

We first introduce systems to optimize computational efficiency and reduce the engineering overhead for distributed LLM training. We develop *TeraPipe*, which proposes a new dimension to perform pipeline parallel training for LLMs, and also *Alpa*, the world's first compiler capable of automatically distributing arbitrary neural networks with all existing parallelization methods.

While training is typically a one-time cost, deploying and serving an LLM requires running LLM inference continuously, which is the top blocker for the real-world deployment of LLMs. We improve the serving scalability with *AlpaServe* through model parallelism, and increase the memory utilization and the LLM inference throughput with a new attention algorithm, *PagedAttention*, and an end-to-end serving system, *vLLM*.

Overall, these systems provide comprehensive solutions that significantly improve both training and inference efficiency for large language models. Together, these systems lower the high costs associated with large language models, democratizing their deployment across various real-world applications.

To my family.

# Contents

| Co | onter | ats                                                             | i                         |

|----|-------|-----------------------------------------------------------------|---------------------------|

| Li | st of | Figures                                                         | $\mathbf{v}^{\mathrm{i}}$ |

| Li | st of | Tables                                                          | х                         |

| 1  | Intr  | oduction                                                        | 1                         |

|    | 1.1   | Towards Fully-Automated Parallelization for LLM Training        |                           |

|    | 1.2   | Scalable and High-Throughput LLM Inference and Serving          |                           |

|    | 1.3   | Real-World Impact and Future Work                               | 3                         |

| 2  | Tera  | aPipe: Token-Level Pipeline Parallelism for Training Large Lang | guage                     |

|    | Mo    | dels                                                            | 5                         |

|    | 2.1   | Introduction                                                    |                           |

|    | 2.2   | Related Work                                                    | 8                         |

|    | 2.3   | Method                                                          |                           |

|    |       | 2.3.1 Language Modeling and Transformers                        |                           |

|    |       | 2.3.2 Pipeline Parallelism Within a Sequence                    |                           |

|    |       | 2.3.3 Selecting Optimal Slicing Scheme                          |                           |

|    |       | 2.3.4 Combining with Other Parallel Training methods            |                           |

|    | 2.4   | Implementation                                                  |                           |

|    | 2.5   | Evaluation                                                      |                           |

|    |       | 2.5.1 Main Results                                              | 19                        |

|    |       | 2.5.2 Dynamic Programming                                       |                           |

|    |       | 2.5.3 Longer Sequence Length                                    |                           |

|    | 2.6   | Conclusion                                                      |                           |

|    | 2.7   | Appendix: Detailed Experiment Results                           |                           |

| 3  | Aln   | a: Automating Inter- and Intra-Operator Parallelism for Distrib | outed                     |

| 3  | _     | p Learning                                                      | 24                        |

|    |       | Introduction                                                    |                           |

|    | 3.2   | Background: Distributed Deep Learning                           |                           |

|   |      | 3.2.1         | Conventional View of ML Parallelism                                                                                           |  |  |  |  |  |  |  |  |

|---|------|---------------|-------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

|   |      | 3.2.2         | Intra- and Inter-Operator Parallelisms                                                                                        |  |  |  |  |  |  |  |  |

|   | 3.3  | Overv         | iew                                                                                                                           |  |  |  |  |  |  |  |  |

|   | 3.4  | Intra-        | Operator Parallelism                                                                                                          |  |  |  |  |  |  |  |  |

|   |      | 3.4.1         | The Space of Intra-Operator Parallelism                                                                                       |  |  |  |  |  |  |  |  |

|   |      | 3.4.2         | ILP Formulation                                                                                                               |  |  |  |  |  |  |  |  |

|   | 3.5  | Inter-0       | Operator Parallelism                                                                                                          |  |  |  |  |  |  |  |  |

|   |      | 3.5.1         | The Space for Inter-Operator Parallelism                                                                                      |  |  |  |  |  |  |  |  |

|   |      | 3.5.2         | DP Formulation                                                                                                                |  |  |  |  |  |  |  |  |

|   | 3.6  | Paralle       | elism Orchestration                                                                                                           |  |  |  |  |  |  |  |  |

|   | 3.7  | Limita        | ations and Discussion                                                                                                         |  |  |  |  |  |  |  |  |

|   | 3.8  | Evalua        | ation                                                                                                                         |  |  |  |  |  |  |  |  |

|   |      | 3.8.1         | End-to-End Performance                                                                                                        |  |  |  |  |  |  |  |  |

|   |      | 3.8.2         | Intra-Op Parallelism Ablation Study                                                                                           |  |  |  |  |  |  |  |  |

|   |      | 3.8.3         | Inter-Op Parallelism Ablation Study                                                                                           |  |  |  |  |  |  |  |  |

|   |      | 3.8.4         | Compilation Time                                                                                                              |  |  |  |  |  |  |  |  |

|   |      | 3.8.5         | Cross-Mesh Resharding                                                                                                         |  |  |  |  |  |  |  |  |

|   |      | 3.8.6         | Case Study: Wide-ResNet                                                                                                       |  |  |  |  |  |  |  |  |

|   | 3.9  | Relate        | ed Work                                                                                                                       |  |  |  |  |  |  |  |  |

|   | 3.10 | 10 Conclusion |                                                                                                                               |  |  |  |  |  |  |  |  |

|   | 3.11 | Apper         | ndix: Proof of Submesh Shape Covering                                                                                         |  |  |  |  |  |  |  |  |

|   | 3.12 | Apper         | ndix: Model Specifications                                                                                                    |  |  |  |  |  |  |  |  |

|   | 3.13 | Apper         | ndix: Extra Case Study                                                                                                        |  |  |  |  |  |  |  |  |

|   |      | ~             |                                                                                                                               |  |  |  |  |  |  |  |  |

| 4 | _    |               | : Statistical Multiplexing with Model Parallelism for Deep                                                                    |  |  |  |  |  |  |  |  |

|   |      | _             | Serving 57                                                                                                                    |  |  |  |  |  |  |  |  |

|   | 4.1  |               | uction                                                                                                                        |  |  |  |  |  |  |  |  |

|   | 4.2  | _             | round                                                                                                                         |  |  |  |  |  |  |  |  |

|   | 4.0  |               | Model Parallelism in Model Serving                                                                                            |  |  |  |  |  |  |  |  |

|   | 4.3  |               | ation and Tradeoff Analysis                                                                                                   |  |  |  |  |  |  |  |  |

|   |      |               | Case Study: A Two-model Example                                                                                               |  |  |  |  |  |  |  |  |

|   |      |               | When is Model Parallelism Beneficial                                                                                          |  |  |  |  |  |  |  |  |

|   |      | 4.3.3         | Overhead of Model Parallelism                                                                                                 |  |  |  |  |  |  |  |  |

|   |      | 4.3.4         | Queueing Theory Analysis                                                                                                      |  |  |  |  |  |  |  |  |

|   | 4.4  | Metho         |                                                                                                                               |  |  |  |  |  |  |  |  |

|   |      | 4.4.1         | Automatic Parallelization for Inference                                                                                       |  |  |  |  |  |  |  |  |

|   |      | 4.4.2         | Placement Algorithm                                                                                                           |  |  |  |  |  |  |  |  |

|   | , _  | 4.4.3         | Runtime Scheduling                                                                                                            |  |  |  |  |  |  |  |  |

|   | 4.5  | -             | mentation $\dots \dots \dots$ |  |  |  |  |  |  |  |  |

|   | 4.6  |               | ation                                                                                                                         |  |  |  |  |  |  |  |  |

|   |      | 4.6.1         | Experiment Setup                                                                                                              |  |  |  |  |  |  |  |  |

|   |      | 4.6.2         | End-to-end Results with Real Workloads                                                                                        |  |  |  |  |  |  |  |  |

|   |                | 4.6.3   | Serving Very Large Models                               |

|---|----------------|---------|---------------------------------------------------------|

|   |                | 4.6.4   | Robustness to Changing Traffic Patterns                 |

|   |                | 4.6.5   | Benefits of Dynamic Batching                            |

|   |                | 4.6.6   | Ablation Study                                          |

|   | 4.7            | Relate  | d Work                                                  |

|   | 4.8            | Conclu  | asion and Future Work                                   |

| 5 | $\mathbf{vLL}$ | M: Eff  | icient Memory Management for Large Language Model Serv- |

|   |                |         | PagedAttention 87                                       |

|   | 5.1            | Introd  | uction                                                  |

|   | 5.2            | Backgr  | round                                                   |

|   |                | 5.2.1   | Transformer-Based Large Language Models                 |

|   |                | 5.2.2   | LLM Service & Autoregressive Generation                 |

|   |                | 5.2.3   | Batching Techniques for LLMs                            |

|   | 5.3            | Memor   | ry Challenges in LLM Serving                            |

|   |                | 5.3.1   | Memory Management in Existing Systems                   |

|   | 5.4            | Metho   |                                                         |

|   |                | 5.4.1   | PagedAttention                                          |

|   |                | 5.4.2   | KV Cache Manager                                        |

|   |                | 5.4.3   | Decoding with PagedAttention and vLLM                   |

|   |                | 5.4.4   | Application to Other Decoding Scenarios                 |

|   |                | 5.4.5   | Scheduling and Preemption                               |

|   |                | 5.4.6   | Distributed Execution                                   |

|   | 5.5            | Impler  | nentation                                               |

|   |                | 5.5.1   | Kernel-level Optimization                               |

|   |                | 5.5.2   | Supporting Various Decoding Algorithms                  |

|   | 5.6            | Evalua  | ation                                                   |

|   |                | 5.6.1   | Experimental Setup                                      |

|   |                | 5.6.2   | Basic Sampling                                          |

|   |                | 5.6.3   | Parallel Sampling and Beam Search                       |

|   |                | 5.6.4   | Shared prefix                                           |

|   |                | 5.6.5   | Chatbot                                                 |

|   | 5.7            | Ablati  | on Studies                                              |

|   |                | 5.7.1   | Kernel Microbenchmark                                   |

|   |                | 5.7.2   | Impact of Block Size                                    |

|   |                | 5.7.3   | Comparing Recomputation and Swapping                    |

|   | 5.8            | Discus  | sion                                                    |

|   | 5.9            | Relate  | d Work                                                  |

|   | 5.10           | Conclu  | sion                                                    |

| 6 | Con            | clusion | a and Future Work                                       |

|   | 6.1            | Other   | Work During the Construction of This Dissertation       |

|         | Lessons Learned in Open-Source Development |     |

|---------|--------------------------------------------|-----|

| 6.3     | Future Work                                | 118 |

| Bibliog | graphy                                     | 121 |

# List of Figures

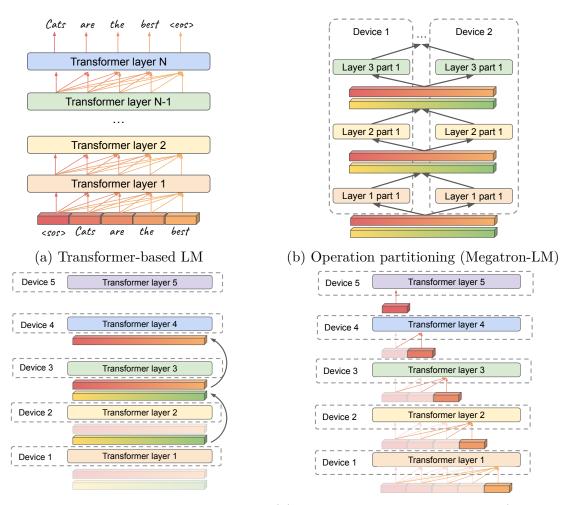

| 2.1 | Different approaches of model parallel training of Transformer-based LMs. (a)            |    |

|-----|------------------------------------------------------------------------------------------|----|

|     | shows a standard multi-layer Transformer LM. In each layer, each position only           |    |

|     | takes only its previous positions as input. (b) shows operation partitioning [125].      |    |

|     | An allreduce operation is required to synchronize the results of each layer. (c)         |    |

|     | shows microbatch-based pipeline parallelism [57], which allows different micro-          |    |

|     | batches (red and green bars) to be executed on different layers of the DNN in            |    |

|     | parallel. (d) show TeraPipe (our work), which pipelines along the token dimension.       | 6  |

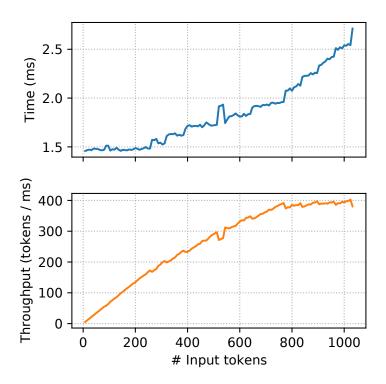

| 2.2 | Execution timeline for different pipelining methods. Grey blocks indicate GPUs idle      |    |

|     | time (a.k.a. pipeline bubbles). (a) Microbatch-based pipeline parallelism (e.g. GPipe).  |    |

|     | Each color corresponds to a microbatch. (b) Microbatch-based pipeline parallelism with   |    |

|     | longer sequence (hence smaller minibatch size due to fixed GPU memory). Pipeline         |    |

|     | bubbles significantly increase. (c) TeraPipe. Pipeline bubbles are substantially reduced |    |

|     | because of the improved pipelining granularity                                           | 10 |

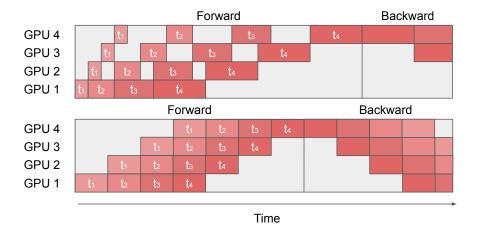

| 2.3 | Forward propagation time and throughput for a single layer of GPT3-1B model              |    |

|     | with a single input sequence with different number of input tokens on a single           |    |

|     | NVIDIA V100 GPU, averaged by 30 independent runs. <b>Top:</b> Time per forward           |    |

|     | propagation. <b>Bottom:</b> Throughput measured by number of tokens per millisecond.     | 13 |

| 2.4 | Execution timeline for inputs for uniform sequence split with non-uniform run-           |    |

|     | ning time (top) and non-uniform sequence split with uniform running time (bot-           |    |

|     | tom). The total latency of a pipeline is determined by its slowest stage, and thus       |    |

|     | splits with non-uniform running time result in larger pipeline bubbles and inferior      |    |

|     | pipeline efficiency                                                                      | 14 |

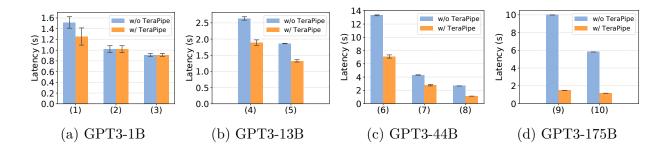

| 2.5 | Training iteration latency for all configurations with and without TeraPipe. De-         |    |

|     | tails for each configuration are listed in Table 2.1                                     | 17 |

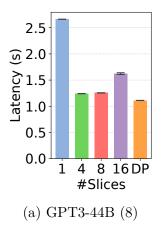

| 2.6 | Training iteration latency of TeraPipe with uniform slicing scheme with different        |    |

|     | number of slices and the optimal slicing scheme find by the dynamic programming          |    |

|     | algorithm                                                                                | 19 |

| 2.7 | Training iteration latency of TeraPipe with different input sequence length for          |    |

|     | the GPT3-13B model                                                                       | 21 |

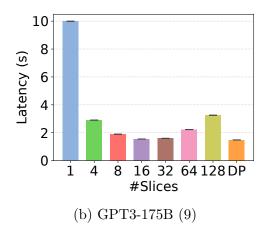

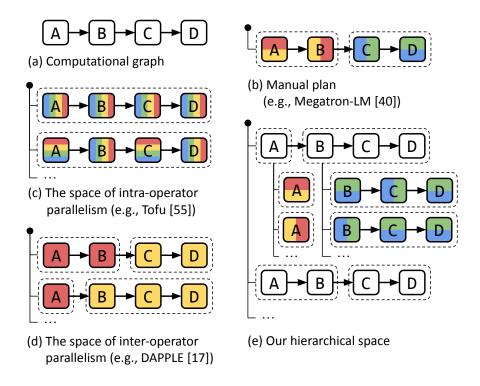

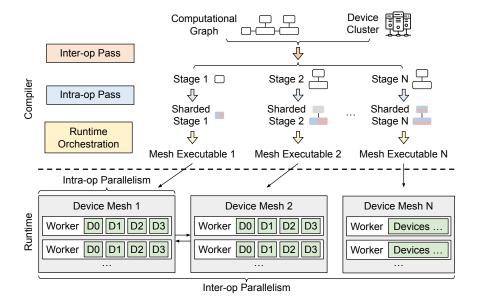

| 3.1  | Generation of parallelization plans for a computational graph shown in (a). Different colors represent different devices, dashed boxes represent pipeline stages.           |            |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|      | (b) creates the plan manually. (c) and (d) automatically generate plans using                                                                                               |            |

|      | only one of intra- and inter-operator parallelisms. (e) shows our approach that creates a hierarchical space to combine intra- and inter-operator parallelisms              | 27         |

| 3.2  | Common parallelization techniques for training a 2-layer Multi-layer Perceptron                                                                                             | 41         |

|      | (MLP). Only the forward pass is shown. "x" is the input data. "w1" and "w2"                                                                                                 | റ          |

| 3.3  | are two weight matrices                                                                                                                                                     | 28         |

| 0.0  | with the sharding specs generated by intra-op pass                                                                                                                          | 31         |

| 3.4  | An example to demonstrate Alpa's API for Jax. The developers uses a Python                                                                                                  | 01         |

|      | decorator Oparallelize to annotate functions that need to be parallelized. The                                                                                              |            |

|      | rest of the program is kept intact                                                                                                                                          | 32         |

| 3.5  | Illustration of the total latency of a pipeline, which is determined by two parts: the total latency of all stages $(t_1 + t_2 + t_3 + t_4)$ and the latency of the slowest |            |

|      | stage $((B-1)\cdot t_3)$                                                                                                                                                    | 38         |

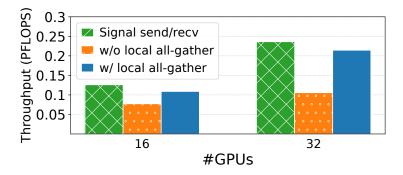

| 3.6  | Cross-mesh resharding. Red arrows denote send/recv on slow connections. Green                                                                                               |            |

|      | arrows denote all-gather on fast connections. (a) The scatter-gather optimization for equal mesh shapes in Megatron-LM. (b) The naive send/recv for unequal mesh            |            |

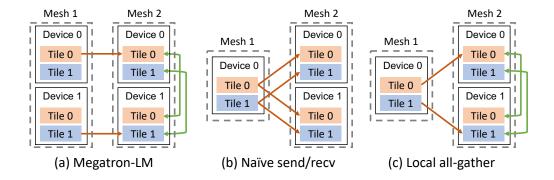

|      | shapes. (c) The generalized local all-gather optimization for unequal mesh shapes.                                                                                          | 42         |

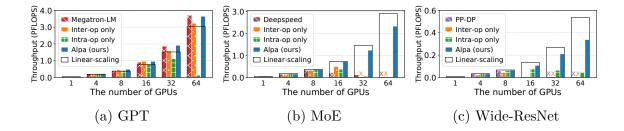

| 3.7  | End-to-end evaluation results. "×" denotes out-of-memory. Black boxes repre-                                                                                                | 12         |

|      | sent linear scaling.                                                                                                                                                        | 44         |

| 3.8  | Intra-operator parallelism ablation study. "×" denotes out-of-memory. Black                                                                                                 |            |

|      | boxes represent linear scaling                                                                                                                                              | 47         |

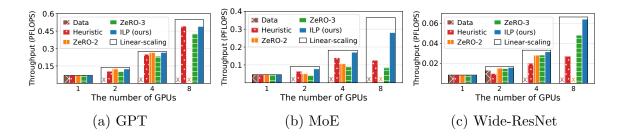

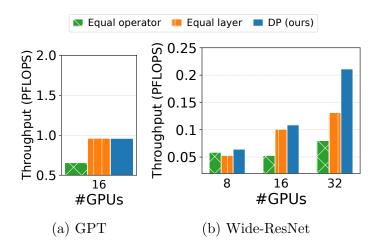

| 3.9  | Inter-operator parallelism ablation study                                                                                                                                   | 49         |

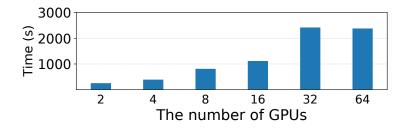

| 3.10 | Alpa's compilation time on all GPT models. The model size and #GPUs are                                                                                                     | <b>F</b> 0 |

| 2 11 | simultaneously scaled                                                                                                                                                       | 50<br>51   |

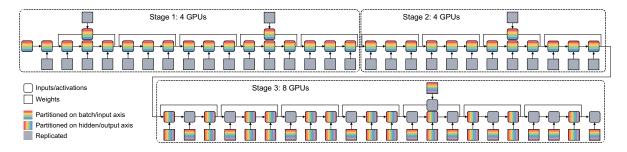

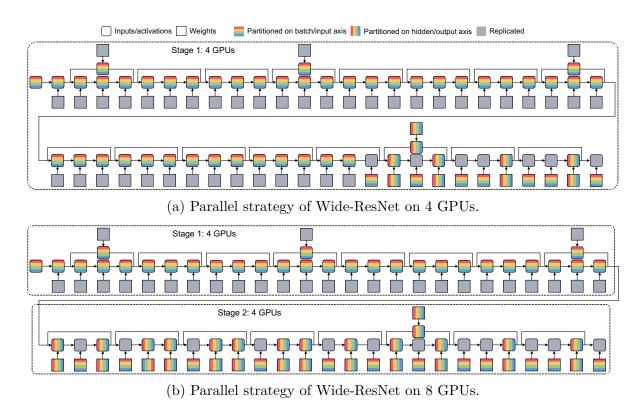

|      | Visualization of the parallel strategy of Wide-ResNet on 16 GPUs. Different                                                                                                 | 91         |

| 0.12 | colors represent the devices a tensor is distributed on. Grey blocks indicate a                                                                                             |            |

|      | tensor is replicated across the devices. The input data and resulting activation of                                                                                         |            |

|      | each convolution and dense layer can be partitioned along the batch axis and the                                                                                            |            |

|      | hidden axis. The weights can be partitioned along the input and output channel                                                                                              |            |

|      | axis                                                                                                                                                                        | 51         |

| 3.13 | Visualization of the parallel strategy of Wide-ResNet on 4 and 8 GPUs. Different                                                                                            |            |

|      | colors represent the devices a tensor is distributed on. Grey blocks indicate a                                                                                             |            |

|      | tensor is replicated across all devices. The input data and resulting activation of<br>each convolution or dense layer can be partitioned along the batch axis and the      |            |

|      | hidden axis. The weights can be partitioned along the input and output channel                                                                                              |            |

|      | axis                                                                                                                                                                        | 56         |

|      |                                                                                                                                                                             |            |

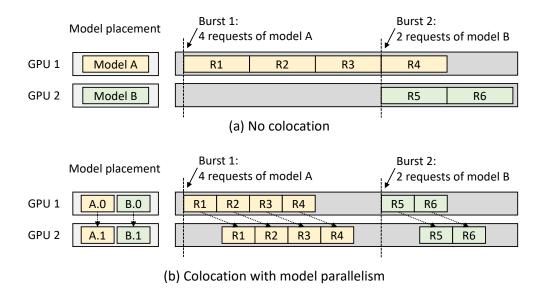

| 4.1  | Two placement strategies for serving two models on two GPUs. In each subfigure, the left part shows the model placements and the right part shows the timeline |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | for handling bursty requests. At the time of "Burst 1", 4 requests of model A                                                                                  |    |

|      | come at the same time. Colocation with model parallelism can reduce the average                                                                                |    |

|      | completion time of bursty requests                                                                                                                             | 58 |

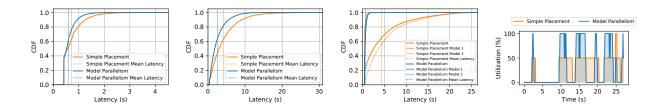

| 4.2  | Latency CDF and cluster utilization in the 2-model example                                                                                                     | 61 |

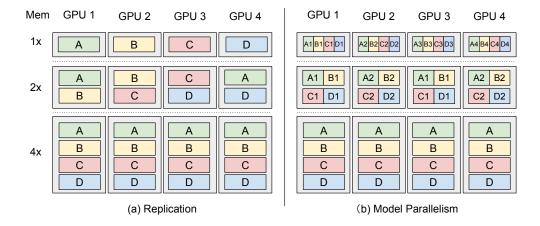

| 4.3  | Replication and model parallel placement illustration with different memory bud-                                                                               |    |

|      | gets, where the memory budgets are set to be multiples of a single model's size.                                                                               | 63 |

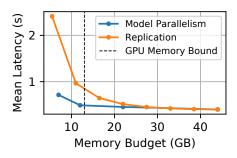

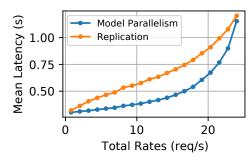

| 4.4  | Serving performance with changing per-GPU memory budgets. Model parallelism                                                                                    |    |

|      | is beneficial for limited memory budget. The dashed vertical line is the real per-                                                                             |    |

|      | GPU memory bound of a 16GB V100. The value is around 13GB due to the need                                                                                      |    |

|      | to store activations and other runtime context.                                                                                                                | 64 |

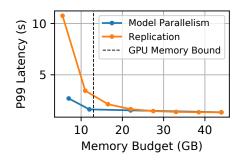

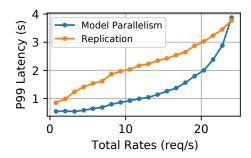

| 4.5  | Serving performance with changing arrival rates. Model parallelism is beneficial                                                                               |    |

|      | for smaller rates                                                                                                                                              | 64 |

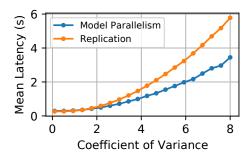

| 4.6  | Serving performance with changing CVs. Model parallelism is beneficial for larger                                                                              |    |

|      | CVs                                                                                                                                                            | 65 |

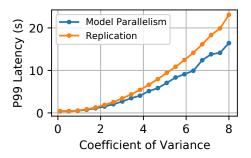

| 4.7  | SLO attainment with changing SLOs. Model parallelism is beneficial for smaller                                                                                 |    |

|      | SLOs.                                                                                                                                                          | 66 |

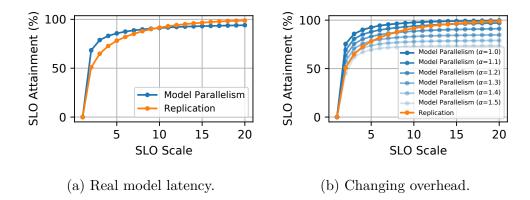

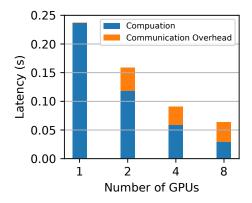

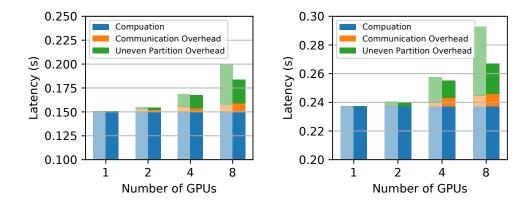

| 4.8  | The overhead decomposition. The overhead of inter-op parallelism mainly comes                                                                                  |    |

|      | from uneven partition while the overhead of intra-op parallelism comes from com-                                                                               | ۵. |

| 4.0  | munication                                                                                                                                                     | 67 |

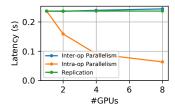

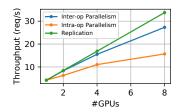

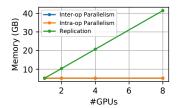

| 4.9  | The latency, throughput and memory usage vs. #GPUs for inter-op parallelism,                                                                                   |    |

|      | intra-op parallelism, and replication. In subfigure (c), the lines for inter-op and                                                                            | 67 |

| 4.10 | intra-op parallelism overlap                                                                                                                                   | 07 |

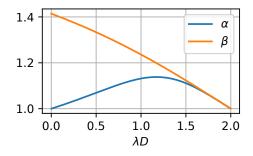

| 4.10 | $W_{pipeline} \leq W_{simple}$ as a function of total utilization $\lambda D$                                                                                  | 69 |

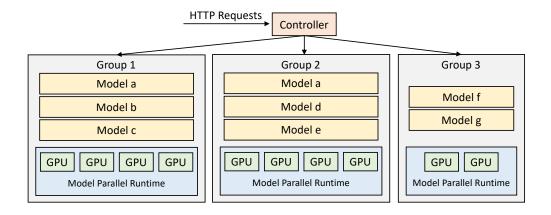

| 4 11 | AlpaServe Runtime System Architecture                                                                                                                          | 70 |

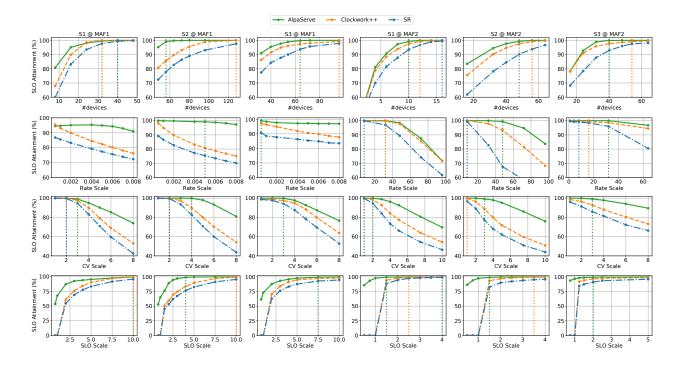

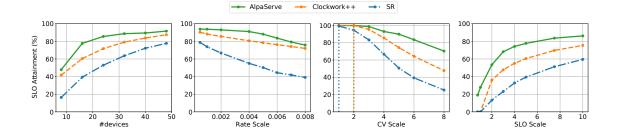

|      | SLO attainment under various settings. In column S1@MAF1, we replay the                                                                                        | •  |

| 1.12 | MAF1 trace on the model set S1, and so on. In each row, we focus on one specific                                                                               |    |

|      | metric mentioned in §4.6.2 to see how its variation affects the performance of                                                                                 |    |

|      | each serving system. If any, the dotted vertical line shows when the system can                                                                                |    |

|      | achieve 99% SLO attainment.                                                                                                                                    | 79 |

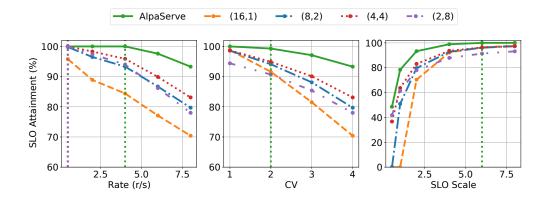

| 4.13 | SLO attainment as we vary the rate, CV, and SLO scale. (8,2) means 8-way                                                                                       |    |

|      | inter-op parallelism and in each pipeline stage using 2-way intra-op parallelism.                                                                              | 81 |

| 4.14 | The actual arrival traffic for AlpaServe and SR is different from what their algo-                                                                             |    |

|      | rithms are assumed, while Clockwork++ runs directly on the actual traffic                                                                                      | 82 |

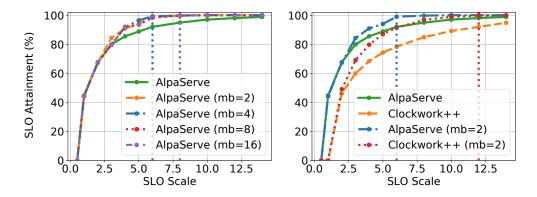

| 4.15 | SLO Attainment when batching is enabled. mb=2 means the maximum batch                                                                                          |    |

|      | size is 2                                                                                                                                                      | 82 |

| 4.16 | Comparison of the model parallel overhead between manual partition (lighter                                                                                    |    |

|      | color) and the partition found by the automatic algorithm (darker color)                                                                                       | 84 |

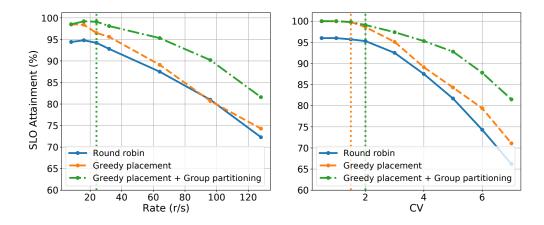

| 4.17 | Ablation study of placement algorithms                                                                                                                         | 85 |

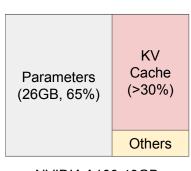

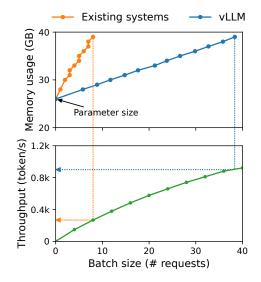

| 5.1  | Left: Memory layout when serving an LLM with 13B parameters on NVIDIA A100. The parameters (gray) persist in GPU memory throughout serving. The memory for the KV cache (red) is (de)allocated per serving request. A small |      |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|      | amount of memory (yellow) is used ephemerally for activation. Right: vLLM                                                                                                                                                   |      |

|      | smooths out the rapid growth curve of KV cache memory seen in existing sys-                                                                                                                                                 |      |

|      | tems [96, 153], leading to a notable boost in serving throughput                                                                                                                                                            | 88   |

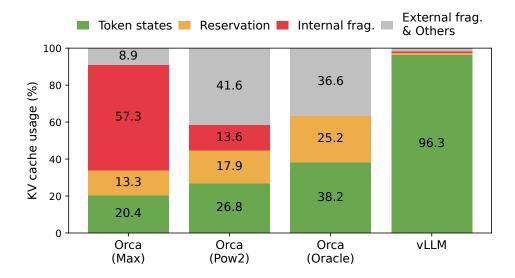

| 5.2  | Average percentage of memory wastes in different LLM serving systems during                                                                                                                                                 |      |

| 0.2  | the experiment in §5.6.2                                                                                                                                                                                                    | 89   |

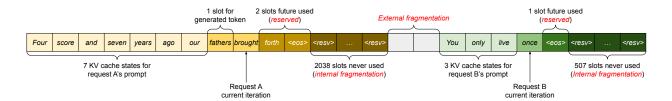

| 5.3  | KV cache memory management in existing systems. Three types of memory                                                                                                                                                       | 00   |

| 0.0  | wastes – reserved, internal fragmentation, and external fragmentation – exist                                                                                                                                               |      |

|      | that prevent other requests from fitting into the memory. The token in each                                                                                                                                                 |      |

|      | memory slot represents its KV cache. Note the same tokens can have different                                                                                                                                                |      |

|      | KV cache when at different positions                                                                                                                                                                                        | 93   |

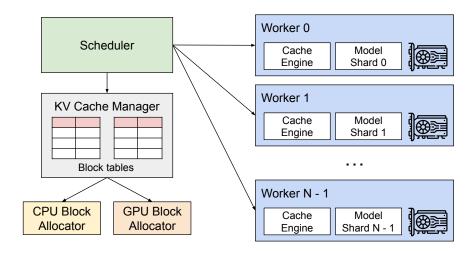

| 5.4  | vLLM system overview.                                                                                                                                                                                                       | 95   |

| 5.5  | Illustration of the PagedAttention algorithm, where the attention key and values                                                                                                                                            |      |

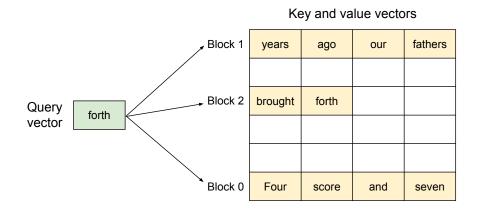

| 0.0  | vectors are stored as non-contiguous blocks in the memory                                                                                                                                                                   | 97   |

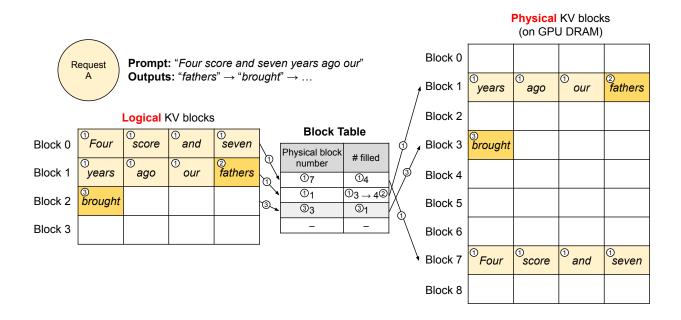

| 5.6  | Block table translation in vLLM                                                                                                                                                                                             | 98   |

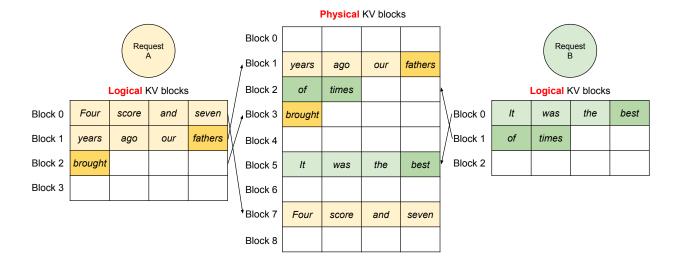

| 5.7  | Storing the KV cache of two requests at the same time in vLLM                                                                                                                                                               | 99   |

| 5.8  | Parallel sampling example                                                                                                                                                                                                   | 101  |

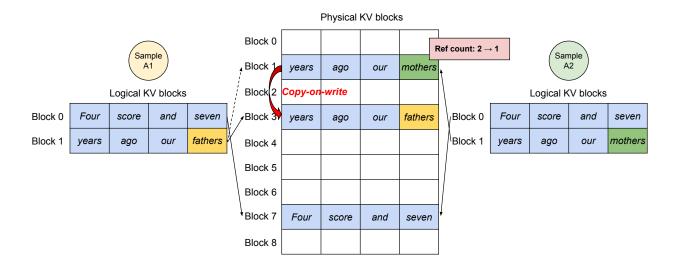

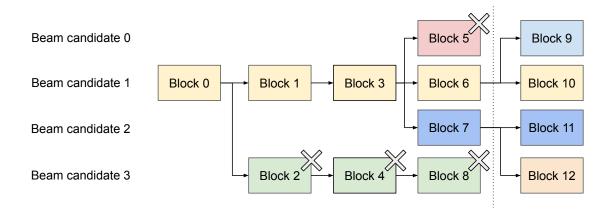

| 5.9  | Beam search example                                                                                                                                                                                                         | 101  |

| 5.10 |                                                                                                                                                                                                                             |      |

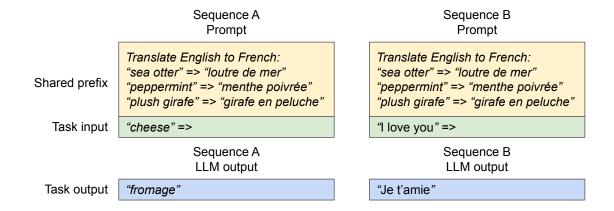

|      | from [18]                                                                                                                                                                                                                   | 103  |

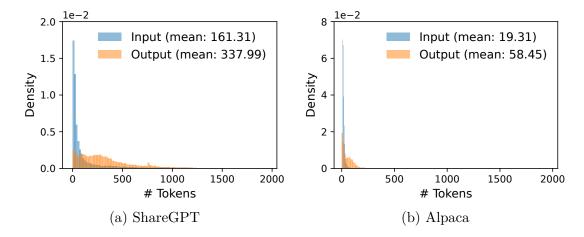

| 5.11 | Input and output length distributions of the (a) ShareGPT and (b) Alpaca datasets                                                                                                                                           | .106 |

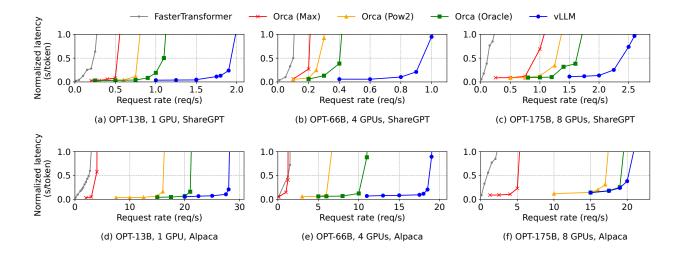

| 5.12 | Single sequence generation with OPT models on the ShareGPT and Alpaca dataset                                                                                                                                               | t107 |

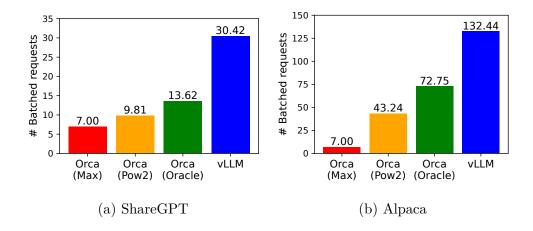

| 5.13 | Average number of batched requests when serving OPT-13B for the ShareGPT                                                                                                                                                    |      |

|      | (2  reqs/s) and Alpaca $(30  reqs/s)$ traces                                                                                                                                                                                | 107  |

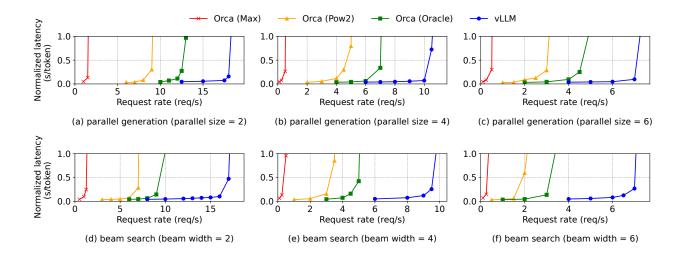

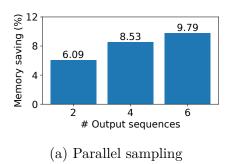

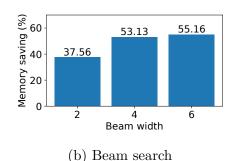

| 5.14 | Parallel generation and beam search with OPT-13B on the Alpaca dataset                                                                                                                                                      | 108  |

| 5.15 | Average amount of memory saving from sharing KV blocks, when serving OPT-                                                                                                                                                   |      |

|      | 13B for the Alpaca trace                                                                                                                                                                                                    | 110  |

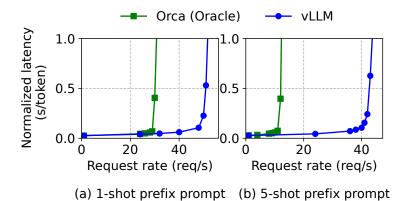

| 5.16 | Translation workload where the input prompts share a common prefix. The prefix                                                                                                                                              |      |

|      | includes (a) 1 example with 80 tokens or (b) 5 examples with 341 tokens                                                                                                                                                     | 111  |

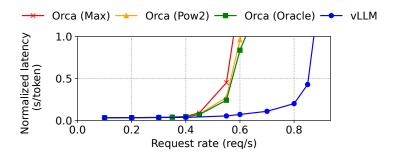

| 5.17 | Performance on chatbot workload                                                                                                                                                                                             | 111  |

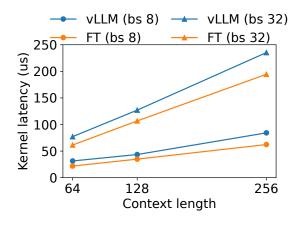

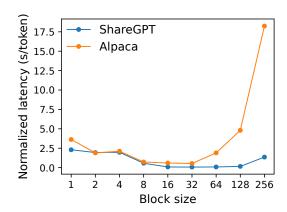

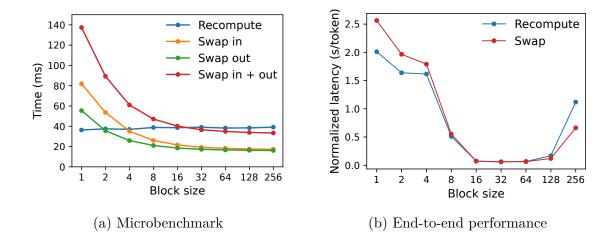

| 5.18 | Ablation experiments                                                                                                                                                                                                        | 112  |

| 5.19 | (a) Overhead of recomputation and swapping for different block sizes. (b) Per-                                                                                                                                              |      |

|      | formance when serving OPT-13B with the ShareGPT traces at the same request                                                                                                                                                  |      |

|      | rate.                                                                                                                                                                                                                       | 113  |

# List of Tables

| 2.1 | Model settings and parallel training setups used in the evaluation. $N$ : Number of Transformer layers. $H$ : Hidden state size. $\#$ Params: Number of total parameters. $L$ : Input sequence length. $\#$ GPUs: Total number of GPUs. $B$ : Batch                                                                                                |          |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|     | size. #Data: Number of data parallel shards. #Pipe: Number of pipeline stages. #Op: Number of GPUs used for operational partitioning by each Transformer                                                                                                                                                                                           |          |

| 2.2 | layer                                                                                                                                                                                                                                                                                                                                              | 16<br>22 |

| 2.3 | Detailed numbers and slicing schemes in ablation studies on the effectiveness of the dynamic programming algorithm (Figure 2.6 in the main chapter)                                                                                                                                                                                                | 22       |

| 2.4 | Detailed numbers and slicing schemes in experiments with longer sequence lengths (Figure 2.7 in the main chapter)                                                                                                                                                                                                                                  | 23       |

| 3.1 | Sharding specs of a 2-dimentional tensor on a $2 \times 2$ device mesh. $A$ is a $(N, M)$ tensor. The device mesh is [[Device 0, Device 1], [Device 2, Device 3]]. Each device stores a partition of $A$ . The first column is the name of the sharding spec. The latter columns use Numpy syntax to describe the partitions stored on each device | 36       |

| 3.2 | Several cases of resharding. $all$ -gather $(x, i)$ means an all-gather of $x$ bytes along the $i$ -th mesh axis. $M$ is the size of the tensor. $(n_0, n_1)$ is the mesh shape                                                                                                                                                                    | 34       |

| 3.3 | Several parallel algorithms for a batched matmul $C_{b,i,j} = \sum_k A_{b,i,k} B_{b,k,j}$ . The notation all-reduce $(x,i)$ means an all-reduce of $x$ bytes along the $i$ -th mesh axis. $M$ is the size of the output tensor. $(n_0, n_1)$ is the mesh shape                                                                                     | 35       |

| 3.4 | Models used in the end-to-end evaluation. $LM = language model$ . $IC = image$                                                                                                                                                                                                                                                                     |          |

|     | classification.                                                                                                                                                                                                                                                                                                                                    | 45       |

| 3.5 | Compilation time breakdown of GPT-39B                                                                                                                                                                                                                                                                                                              | 51       |

| 3.6 | GPT-3 Model Specification                                                                                                                                                                                                                                                                                                                          | 55       |

| 3.7 | GShard MoE Model Specification                                                                                                                                                                                                                                                                                                                     | 55       |

| 2 8 | Wide ResNet Model Specification                                                                                                                                                                                                                                                                                                                    | 5.5      |

| 4.1 | The first three columns list the sizes and inference latency of the models. The |     |

|-----|---------------------------------------------------------------------------------|-----|

|     | latency is measured for a single query with a sequence length of 2048 on a sin- |     |

|     | gle GPU. BERT-104B's latency is reported using a minimal degree of inter-op     |     |

|     | parallelism. The latter columns list the number of instances for each model in  |     |

|     | different model sets named as S1-S4                                             | 77  |

| 4.2 | Comparison of the SLO attainment reported by the simulator and the real system  |     |

|     | under different SLO scales                                                      | 78  |

| 5.1 | Model sizes and server configurations                                           | 105 |

### Acknowledgments

I feel incredibly fortunate to have received support from so many individuals during my PhD journey at Berkeley. Their guidance has profoundly impacted my professional career and personal growth, making these five years a truly unique experience.

First and foremost, I would like to express my gratitude to my advisor, Ion Stoica. Over time, I have come to realize how fortunate I am to have had Ion guiding me throughout my five-year PhD journey. He gave me the freedom to pursue my interests while providing unwavering support for all of my projects. As a highly successful and experienced academic and entrepreneur, Ion offered invaluable guidance on research direction, execution plans, open-source project management, career paths, and life in general. Contrary to what many might expect, we meet almost weekly throughout my entire PhD journey. His unwavering support and mentorship have played a pivotal role in shaping both my academic and personal growth, for which I will always remain deeply grateful.

A special note of gratitude goes to Joey Gonzalez. Joey has been a great mentor and collaborator, contributing to nearly all of my papers throughout my Ph.D. He consistently offers unique insights into research problems, often providing a perspective distinct from Ion's. Their discussions establish a democratic foundation for all research dialogues in my projects, encouraging me to critically evaluate and determine the best path forward. I would also like to thank Matei Zaharia and Eric Xing for being part of my committee and for providing valuable feedback on this dissertation, my research, and my career.

At Berkeley, we often take for granted just how talented our peers are. I am fortunate to have worked with some of the brightest minds in computer science throughout my PhD:

For Hoplite and Terapipe, I collaborated with Siyuan Zhuang, Danyang Zhuo, and Stephanie Wang. Before my Ph.D., I had no experience in systems research. Siyuan, Danyang, and Stephanie showed me how to build a solid system and conduct innovative systems research, laying a strong foundation for my PhD journey.

For Alpa and AlpaServe, I spent two wonderful years with Lianmin Zheng and Hao Zhang. In retrospect, the Alpa project is an engineering marvel that achieved something unimaginable without collaboration. I learned immensely from them throughout our partnership. I was also fortunate to work with Yonghao Zhuang and Yinmin Zhong, two brilliant interns who are now successful PhD students in the field.

For vLLM and PagedAttention, I was privileged to work with Woosuk Kwon to build what I had dreamed of since the beginning of my PhD study: an open-source system widely adopted around the world. We spent countless days and nights refining every aspect of the project together. I am also grateful to have worked with Simon Mo, who took the initiative to become the project's product manager and elevate vLLM to the next level. Thank you to the other vLLM team members, Xiaoxuan (Lily) Liu and Kaichao You, for the fantastic

collaboration. What makes vLLM special is the strong support from its vibrant open-source community. I want to thank Antoni Baum, SangBin Cho, Cade Daniel, Nick Hill, Richard Liaw, Philipp Moritz, Robert Shaw, Chen Shen, Roger Wang, and many others for their contributions. The dedication of these contributors keeps the vLLM project thriving.

Beyond the projects mentioned above, I would like to especially thank Eric Wallace, Sheng Shen, and Kevin Lin, with whom I collaborated on scaling law research even before large language models took the world by storm; Zhanghao Wu, for being an excellent roommate and friend over the past three years; and Wei-Lin Chiang and Frank Sifei Luan, my snowboarding companions and wonderful friends.

In the last three years of my PhD, I am fortunate to be a part-time research intern at Google DeepMind. I thank my intern hosts Yanping Huang and Zhifeng Chen for their invaluable insights into my research. I was also fortunate to collaborate with Yuanzhong Xu and Yu (Emma) Wang. Their mentorship and collaboration significantly enriched my experience, broadening my perspective and deepening my understanding of the field.

During my PhD study, I have been fortunate to meet and learn from the following individuals: Shiyi Cao, Xinyun Chen, Audrey Cheng, Xinyang Geng, Linyuan Gong, Shiyuan Guo, Zhiyang He, Xin Jin, Daniel Kang, Kurt Keutzer, Dacheng Li, Eric Liang, Hao Liu, Vincent Liu, Michael Luo, Wenlong Mou, Robert Nishihara, Hongyu Ren, Ying Sheng, Dawn Song, Shangyin Tan, Sijun Tan, Cody Hao Yu, Hexu Zhao, Ruiqi Zhong, and many other bright individuals.

Before joining Berkeley, I was fortunate to begin my research career alongside a wonderful group of advisors and friends. I would like to thank my undergraduate advisors, Liwei Wang and Di He at Peking University, for introducing me to research. My gratitude also extends to Tao Qin, Fei Tian, and Li Yi for their mentorship during my undergraduate years. Additionally I am grateful to my lifelong friends, now spread across various corners of the world: Xinna Chen, Chongming Ni, Luyao Ren, Yuhao Zhang, and many more. Their unwavering support have been instrumental in shaping my academic journey, providing me with a solid foundation and a network of lifelong connections.

Most importantly, I would like to express my deepest gratitude to my family. I am profoundly thankful to my mother, Zhangdong Yu, and my father, Zicun Li, for raising me in the best possible environment and providing me with unconditional love. In the fourth year of my PhD, my family faced the greatest challenge we had ever encountered: my mother's medical emergency, which eventually led to her passing. Thank my extended family—grandparents, uncles, aunts, cousins, and family friends—for their unwavering support during that incredibly difficult time. Lastly, my heartfelt appreciation goes to my partner and best friend, Zi Lin, for the joy, encouragement, and inspiration she has brought to my life and for the support in my hardest time. This dissertation is dedicated to my family, whose love and support made it all possible.

# Chapter 1

# Introduction

Large language models (LLMs) have brought remarkable advancements to the computing industry. Applications like conversational chatbots like ChatGPT [101] and programming assistants like GitHub Copilot [46] have been heavily involved in people's daily lives.

However, a high barrier exists between the LLMs and the vast majority of researchers and practitioners, brought by the engineering challenges with the enormous model sizes and the substantial compute requirements. LLMs are often large neural networks with hundreds of billions of parameters. For example, the GPT-3 model [18] has 175 billion parameters, meaning that it takes more than 350 GB memory if stored in half floating point precision. The most advanced GPUs on the market still only have 40-80 GB of memory, which is significantly less than the memory required for the LLMs. To execute these LLMs efficiently, distributed execution of these models, sometimes to a scale of thousands of GPUs, becomes a necessity. However, distributed execution requires careful partitioning and scheduling of the model execution. This additional complexity greatly raises the bar of deploying these models in real-world applications.

In this dissertation, we design algorithms and build systems to improve computational efficiency and reduce the engineering overhead when training and deploying LLMs. In the following sections, we will introduce the contributions of this dissertation in LLM training and LLM inference, respectively. In the end, we will discuss the real-world impact of the systems introduced in this thesis.

# 1.1 Towards Fully-Automated Parallelization for LLM Training

Popular deep learning frameworks such as TensorFlow [1], PyTorch [104], and JAX [17] have greatly simplified the process of training models on a single GPU. However, the complexity will increase considerably with distributed training, i.e., training a model across multiple

GPUs. Especially when a model exceeds the memory capacity of a single GPU, *model* parallelism, the technique that partitions a single model across multiple GPUs, introduces further overheads and makes achieving optimal performance even more challenging.

We start on this problem by **designing new algorithms to improve distributed training efficiency**. One significant inefficiency comes from the computation overhead of underutilized GPUs due to the dependency within the parallel algorithm. To reduce computation overhead, we focus on *pipeline parallelism*, where a model is partitioned into multiple pipeline stages. In this case, the inefficiency comes from the so-called *pipeline bubbles*, which is caused by not having enough data slices to fulfill all the pipeline stages. In **TeraPipe** (chapter 2), we discover a new dimension to perform pipeline parallelism for LLMs: we show that one can fine-grainedly pipeline different tokens within a single sequence with high GPU utilization, leading to a 5x speedup when training GPT-3 scale models.

Although algorithmic innovations like TeraPipe improve the efficiency of different model parallel algorithms, there is no universally optimal algorithm for every scenario. Picking the optimal algorithm tightly depends on the LLM's architecture and the computing cluster's configuration. This is challenging even for system experts, let alone other LLM researchers and engineers.

To this end, we develop Alpa (chapter 3), the world's first compiler capable of automatically distributing arbitrary neural networks with all existing parallelization methods, including data, tensor, and pipeline parallelism. Alpa organizes these existing parallelization methods into a hierarchical space, corresponding to the hierarchical structure of the compute cluster, allowing it to derive efficient parallel execution plans at each parallelism level automatically. As a result, with no modification to the model code, Alpa can transform any neural network into a distributed version with a near-optimal model-parallel strategy. This not only simplifies the engineering effort for model parallelism, but also brings new capacities—Alpa can generate parallelization plans that match or outperform hand-tuned model-parallel training systems and generalize to new models that cannot be parallelized by existing systems.

# 1.2 Scalable and High-Throughput LLM Inference and Serving

While training has been a major focus in deep learning, a model actually spends most of its time on inference instead of training: A model is typically trained once but can be used for inference over a long period to serve numerous requests. This has motivated me to extend my research towards addressing practical challenges in LLM inference and serving, optimizing the *scalability* and *speed*.

Scalable serving with model parallelism. Scaling an inference system to serve multiple models on a distributed cluster faces unique challenges. A major one is the *bursty requests*: a model might experience a surge of requests within a certain timeframe while others receive none. Existing systems often implement complex request scheduling and swapping policies to handle these bursts.

In AlpaServe (chapter 4), we leverage model parallelism, the technique originally designed for partitioning models larger than a single GPU, to increase cluster utilization. With model parallelism, the models can be partitioned into smaller parts, and each GPU can hold multiple model parts. In this case, a burst to one model can be jointly handled by multiple GPUs, which effectively statistically multiplexes the GPUs across the models. AlpaServe navigates the tradeoff space among different parallelization and placement strategies with an automated search algorithm. It can serve 6x burstier traffic compared to previous systems and is the first work to show that model parallelism can also benefit small models that can fit into a single GPU.

High-throughput inference with paged memory. LLM's structure has inherently limited its inference to one token at a time, which makes parallel processors like GPU underutilized. To improve the inference throughput, more requests need to be processed in a batch. However, the batch size is bottlenecked by memory. Specifically, to generate a new token, LLMs require the cached states of all previous tokens, known as the KV cache. The KV cache is large and dynamic: a single request's KV cache can take GBs of memory, and its exact size depends on input requests' diverse sequence lengths. As a result, efficiently managing the KV cache presents a significant challenge: the static allocation scheme in existing systems causes up to 80% of memory to be wasted.

To address this issue, we developed **PagedAttention** (chapter 5), an attention algorithm inspired by *virtual memory and paging* in operating systems. PagedAttention allows storing the KV cache in non-contiguous memory blocks. Thus, the KV cache can be allocated ondemand and also shared across requests. PagedAttention reduces the memory waste from above 80% to under 4% and eventually improves the throughput by up to 4x, reaching state-of-the-art. Based on PagedAttention, we build **vLLM**, an end-to-end LLM inference and serving engine. Compared to previous state-of-the-art, vLLM achieved up to **4x higher throughput**.

## 1.3 Real-World Impact and Future Work

The systems we build in this dissertation go beyond research artifacts and are ready for real-world deployment. The open-source projects built on top of the techniques introduced in this dissertation have gained considerable attention and are actively used across the industry:

- Alpa has been productionized by <u>Google</u> and has been integrated into the popular deep learning framework JAX and its compiler XLA.

- vLLM has become the most popular open-source LLM serving system in the world, with 23K+ GitHub stars and 460+ contributors worldwide. It has become the default LLM server on Microsoft Azure and has been used and deployed in companies including Anyscale, Apple, AWS, Baidu, ByteDance, Databricks, Google Cloud, IBM, Meta, Microsoft, Scale, Spotify, Uber, and more. Thanks to its industrial impact, vLLM was selected as the first cohort of a16z open-source AI Grants.

The wide user community of these projects not only validates the ideas, but also opens up exciting, continuous pathways of first-hand research challenges, presenting numerous opportunities for exploration in the future. In chapter 6, we conclude this dissertation by summarizing the contributions and discussing future directions for research to realize a future where the most advanced LLMs are accessible to everyone in the world.

# Chapter 2

# TeraPipe: Token-Level Pipeline Parallelism for Training Large Language Models

Model parallelism has become a necessity for training modern large-scale deep language models. We start the dissertation by designing new algorithms to improve the efficiency of model parallel training for large language models.

In this chapter, we identify a new and orthogonal dimension from existing model parallel approaches: it is possible to perform pipeline parallelism within a single training sequence for Transformer-based language models thanks to its autoregressive property. This enables a more fine-grained pipeline compared with previous work. With this key idea, we design TeraPipe [83], a high-performance token-level pipeline parallel algorithm for synchronous model-parallel training of Transformer-based language models. We develop a novel dynamic programming-based algorithm to calculate the optimal pipelining execution scheme given a specific model and cluster configuration. We show that TeraPipe can speed up the training by 5.0x for the largest GPT-3 model with 175 billion parameters on an AWS cluster with 48 p3.16xlarge instances compared with state-of-the-art model-parallel methods.

## 2.1 Introduction

Transformer-based language models (LMs) have revolutionized the area of natural language processing (NLP) by achieving state-of-the-art results for many NLP tasks, including text classification, question answering, and text generation [18, 109]. The accuracy of a Transformer-based LM grows substantially with its model size, attributing to the fact that they can be *unsupervisedly* trained on almost *unlimited* text data. Today, a large LM, such as GPT-3 [18], can have more than 175B parameters, which amounts to 350 GB, assuming 16-bit floating-point numbers. This significantly exceeds the memory capacity of existing

(c) Microbatch-based pipeline parallelism (d) Token-based pipeline parallelism (TeraPipe) (GPipe)

Figure 2.1: Different approaches of model parallel training of Transformer-based LMs. (a) shows a standard multi-layer Transformer LM. In each layer, each position only takes only its previous positions as input. (b) shows operation partitioning [125]. An allreduce operation is required to synchronize the results of each layer. (c) shows microbatch-based pipeline parallelism [57], which allows different microbatches (red and green bars) to be executed on different layers of the DNN in parallel. (d) show TeraPipe (our work), which pipelines along the token dimension.

hardware accelerators, such as GPUs and TPUs, which makes model-parallel training a necessity, i.e., partitioning the model on multiple devices during the training process.

Because of the demands for efficient LM training, many researchers and industry practitioners have proposed different ways for model parallel training. One approach is to partition the weight matrices and dispatch smaller matrix operations to parallel devices [Figure 2.1b; 125, 122]. Another approach is to split a batch of training data into many microbatches and then evenly pipeline the layer computations across different microbatches and devices [Figure 2.1c; 57]. Unfortunately, these approaches either introduce excessive communication overheads between compute devices, or lead to reduced efficiency due to pipeline "bubbles" (i.e. device idle time, see Section 2.2 and 2.3.2 for details).

Our key observation in this chapter is that Transformer-based language models have a key property: the computation of a given input token only depends on previous tokens, but not on future tokens. This lack of dependency on future tokens provides new opportunities for pipeline parallel training.<sup>1</sup> In particular, it allows us to create a fine-grained pipeline within a single training sequence for Transformer-based LMs, by parallelizing the computation of the current token on the current layer with the computation of the previous token on the next layer of the model. For example, in Figure 2.1d, we can pipeline the execution across all 5 devices within a single input sequence. Similar to other synchronous model parallel training methods, e.g., Gpipe [57], Megatron-LM [125], we do not change the underlying optimization algorithm, so the resulting model has exactly the same accuracy.

However, leveraging the token dimension for efficient model parallel training raises several challenges. First, if the partitioning along the token dimension is too fine-grained, it leads to under-utilization on devices that require large blocks of data for efficient processing (e.g., GPU). Second, since each token position in the sequence depends on all previous tokens, different positions in a transformer layer exhibit uneven computation loads. This means that uniformly partitioning along the token dimension might cause uneven load across devices, and degenerate the training efficiency.

To this end, we design and implement *TeraPipe*, a high-performance synchronous model parallel training approach for large-scale Transformer-based language models, which exploits the token dimension to pipeline the computation across devices. TeraPipe uses a small number of simple workloads to derive a performance model and then uses a novel dynamic programming algorithm to compute the optimal partitioning of the token dimension for the pipeline. TeraPipe is orthogonal to previous model-parallel training methods, so it can be used together with these methods to further improve the training performance. Our evaluation shows that for the largest GPT-3 model with 175 billion parameters, TeraPipe achieves a 5.0x speedup improvement over the state-of-the-art synchronous model-parallel training methods on an AWS cluster consisting of 48 p3.16xlarge instances.

<sup>&</sup>lt;sup>1</sup>In this chapter, we focus on unidirectional autoregressive language models (e.g., GPT [109, 18]) but not bidirectional models like masked language models (e.g., BERT [34]).

Our chapter makes the following contributions:

- We propose a new dimension, token dimension, for pipeline-parallel training of Transformer-based LMs.

- We develop a dynamic programming algorithm to compute a partition along the token dimension to maximize pipeline parallelism.

- We implement TeraPipe and show that we can increase the synchronous training throughput of the largest GPT-3 model (with 175 billion parameters) by 5.0x over the previous state-of-the-art model-parallel methods.

### 2.2 Related Work

**Data parallelism** scales ML training by partitioning training data onto distributed devices [169, 72, 49, 110]. Each device holds a model replica, works on an independent data partition, and synchronizes the updates via *allreduce* [72] or a parameter server [78]. Data parallelism alone is not enough to train large-scale DNNs due to two main reasons: (1) every device has to have enough memory to store the model and the gradients generated during the training process; (2) communication can be a performance bottleneck to synchronize model parameters.

**Model parallelism** allows for training models larger than the memory capacity of a single device, by partitioning the model (e.g., layers) into disjoint parts and executing each on a dedicated device. Existing model parallel training approaches can be roughly categorized as: operation partitioning and pipeline parallelism.

**Operation partitioning.** One way to split the model is to partition and parallelize computational operations across multiple devices. For example, the computation of matrix multiplications (matmul) XAB can be spitted across multiple devices by partitioning A and B along its rows and columns, respectively.

$$XAB = X \cdot \begin{bmatrix} A_1 & A_2 \end{bmatrix} \cdot \begin{bmatrix} B_1 \\ B_2 \end{bmatrix} = XA_1B_1 + XA_2B_2.$$

This means we can have one device calculate  $XA_1B_1$  and another device calculate  $XA_2B_2$  in parallel. After that, cross-device communication is needed to compute the sum of these two parts.

Many existing works [63, 66, 143, 122] study how to optimize the partitioning schemes for different operations to maximize throughput and minimize communication overheads, among which, Megatron-LM [Figure 2.1b; 125] designs partitioning schemes specifically for large-scale Transformers. However, due to the excessive communication required to collect partial

results after each layer, it is not efficient when the bandwidth between devices is limited [125]. Flexflow [63] proposes a framework to find the optimal operation partitioning, but it cannot model the new dimension proposed in our work.

**Pipeline parallelism** partitions a DNN into layers and put different layers onto different devices [Figure 2.1c; 107]. Each device computes the input on a given layer and sends the result to the next device. Pipeline parallelism significantly reduces communication between devices, because only devices holding neighboring layers need to communicate and they only need to communicate the activations on a particular layer.

Previous pipeline parallel training methods are based on *microbatch* pipelining, e.g., GPipe [57]. This means the computation for a given microbatch in a minibatch on a layer can run in parallel with the next microbatch in the same minibatch on the previous layer. However, microbatch-based pipeline parallelism still cannot achieve high efficiency due to its pipeline bubbles. This is because the start of the forward propagation on a minibatch requires the backward propagation of the previous minibatch to complete (Figure 2.2a). This problem becomes more severe when model sizes increase (see Section 2.3.2). [53] propose using an asynchronous training algorithm to mitigate the effect of pipeline bubbles in microbach-based pipeline parallel training, but asynchronous training introduces uncertainty in model accuracy and is thus not widely adopted for training DNNs.

Wavefront parallelism is a variant of pipeline parallelism, broadly applied in shared-memory multiprocessors [128, 86]. In deep learning, it has been used to accelerate the computation of multi-layer RNNs on a single GPU [3], where different input positions of different layers can execute in parallel in a wavefront fashion to maximize the utilization of the GPU. However, wavefront parallelism cannot accelerate the execution of Transformers because there is no dependency between different input positions within a single Transformer layer to begin with. In addition, wavefront parallelism uses fine-grained per-word pipelining due to the temporal data dependency in RNNs, while too fine-grained pipelining in TeraPipe would lead to inferior pipeline efficiency (see Section 2.3.2 and 2.3.3).

## 2.3 Method

In this section, we briefly introduce language modeling and Transformers. Based on their structures, we identify new opportunities for performing pipelining along the input sequence (which we will notate as the *token dimension* in the rest of the chapter). With that, we derive the optimal slicing scheme over the token dimension to maximize pipeline efficiency using a dynamic programming algorithm. Finally, we show how to combine our new method with existing parallel training techniques.

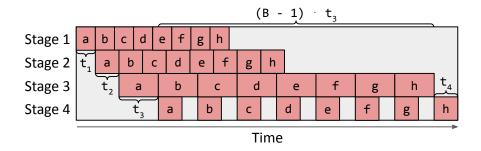

Figure 2.2: Execution timeline for different pipelining methods. Grey blocks indicate GPUs idle time (a.k.a. pipeline bubbles). (a) Microbatch-based pipeline parallelism (e.g. GPipe). Each color corresponds to a microbatch. (b) Microbatch-based pipeline parallelism with longer sequence (hence smaller minibatch size due to fixed GPU memory). Pipeline bubbles significantly increase. (c) TeraPipe. Pipeline bubbles are substantially reduced because of the improved pipelining granularity.

### 2.3.1 Language Modeling and Transformers

The task of language modeling is usually framed as unsupervised distribution estimation of a text corpus  $\mathcal{X}$ , where each example  $x \sim \mathcal{X}$  is a variable length sequence of tokens  $(x_1, x_2, \ldots, x_L)$ . Since language has a natural sequential ordering, it is common to factorize the joint probability over the tokens as the product of conditional probabilities [a.k.a. autoregressive decomposition; 13]:

$$P(x) = \prod_{t=1}^{L} P(x_t | x_1, \dots, x_{t-1}).$$

(2.1)

Transformer [138] is the state-of-the-art architecture for modeling these conditional probabilities. As visualized in Figure 2.1a, a Transformer-based LM F takes the sequence

$(\langle sos \rangle, x_1, \ldots, x_{L-1})$  as input, where  $\langle sos \rangle$  represents the start of a sentence, and outputs a probability distributions  $p_t$  at each position t that models the conditional probability  $P(x_t|x_1, \ldots, x_{t-1})$  as in Eq. 2.1. In practice, F is stacked with many Transformer layers  $F = f_N \circ f_{N-1} \circ \cdots \circ f_1$  [138, 109]:  $f_1$  takes the embedding of the original sequence as input, while  $f_i$  (i > 1) takes the output of  $f_{i-1}$  as input. The main components of a Transformer layer f contain a self-attention layer and a position-wise feed-forward network layer:

SelfAtt

$$(h_t; h_1, \dots, h_{t-1}) = \sum_{s=1}^t \alpha_{ts} \cdot (W_V h_s),$$

where  $\alpha_{ts} = \operatorname{softmax} \left( \frac{(W_Q h_t)^\top (W_K h_s)}{\sqrt{H}} \right);$  (2.2)

FFN $(h_t) = W_2 \sigma(W_1 h_t + b_1) + b_2.$  (2.3)

$h_1, \ldots, h_L \in \mathbb{R}^H$  are hidden states correspond to each position of the input sequence, W and b are learnable parameters, and  $\sigma$  is the nonlinear activation function. An important note here: for each  $h_t$ , Eq. 2.2 takes only the hidden states before position t as inputs and Eq. 2.3