# **UCLA**

UCLA Electronic Theses and Dissertations

Title

Next-generation AI: From Algorithm to Device Perspectives

Permalink

https://escholarship.org/uc/item/2nv5c93j

Author

Lee, Albert

Publication Date

2021

Peer reviewed|Thesis/dissertation

# UNIVERSITY OF CALIFORNIA

Los Angeles

Next-generation AI: From Algorithm to Device Perspectives

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical and Computer Engineering

by

Albert Lee

© Copyright by

Albert Lee

2021

### ABSTRACT OF THE DISSERTATION

Next-generation AI: From Algorithm to Device Perspectives

by

#### Albert Lee

Doctor of Philosophy in Electrical and Computer Engineering

University of California, Los Angeles, 2021

Professor Kang L. Wang, Chair

In recent years, neural networks have contributed significantly to the advancement of machine learning, achieving state-of-the-art over a broad range of challenging tasks. The world right now is seeing a global artificial intelligence (AI) revolution involving academic and industry alike: tech giants like Google and Microsoft are applying machine learning in their commercial products, while professors from every discipline- computer science, engineering, mathematics, biology, transportation - scramble to apply these methods to advance their research. Stock analysts are using AI to analyze and predict stock prices, medical experts to diagnose and develop new drugs, while game developers create sophisticated, human-like behavior in characters. At the national level, all sponsored research agencies, both NSF and DARPA have identified AI as one of the major national research directions.

Our research targets the advancement of next-generation AI from three vertical aspects along the computing hierarchy: At the algorithm level, we propose the use of application-

specific, bio-inspired neural networks for information processing. We develop models of special signal-processing neurons that are compatible with today's machine learning algorithms; and optimize neural architectures containing these neurons to understand their role in creating an efficient network. At the hardware level, we address the memory bottleneck in AI accelerators. We propose two schemes to overcome limitations caused by variations in critical paths and fabrication processes. At the single device level, we recognize the significant performance gain from devices that compose AI computation via physical mechanisms. We propose two spintronic structures capable of computing convolutions that achieve orders of magnitude higher efficiency than state-of-the-art technology. These innovations provide the foundation for higher performance and more efficient AI at different time scales throughout the coming decades: in the short term, algorithms that can be implemented immediately; in the mid-term, hardware designs that can be realized in a few years; and in the long term, new device technologies to be adopted as the fabrics of AI computation.

The dissertation of Albert Lee is approved.

Yingnian Wu

Ken Yang

Puneet Gupta

Kang Lung Wang, Committee Chair

University of California, Los Angeles

2021

To my family

# TABLE OF CONTENTS

| CHAPTER 1                                | 1  |

|------------------------------------------|----|

| 1.1 History of Neural Networks           | 2  |

| 1.2 Neural Network Hardware Accelerators | 7  |

| 1.3 Spintronic Technology                | 9  |

| CHAPTER 2                                | 13 |

| 2.1 Motivation                           | 14 |

| 2.2 Neuron Models                        | 15 |

| 2.2a Max Neurons                         | 16 |

| 2.2b Coincidence Neurons                 | 17 |

| 2.2c Model Algorithm                     | 17 |

| 2.3 Neural Architecture Search Algorithm | 20 |

| 2.3a Mutation NAS Algorithm              | 23 |

| 2.3b Growth-based NAS Algorithm          | 28 |

| 2.3c Pruning NAS Algorithm               | 31 |

| 2.4 Experiment Setup                     | 33 |

| 2.4a Data Preparation                    | 34 |

| 2.4a.1 Visual Recognition Datasets       | 35 |

| 2.4a.2 Speech Recognition Datasets       | 37 |

| 2.4b NAS and Training Setup              | 39 |

| 2.5 Experimental Results                 | 43 |

| 2.5b Growth-based NAS                    | 46 |

| 2.5c Pruning-based NAS                   | 47 |

| 2.5d Specialized Network Design          | 49 |

| CHAPTER 3                                | 53 |

|                                          |    |

| 3.1 Motivation                           |    |

| 3.2 Background                           |    |

| 3.2a Memory Array Architecture           |    |

| 3.2b Variation Sources                   |    |

| 3.3 The 2D Calibration Scheme            |    |

| 2 22 2D Calibration Schomo               | 62 |

|    | 3.3b Circuit Implementation                                                    | 64  |

|----|--------------------------------------------------------------------------------|-----|

|    | 3.3c Simulation Results                                                        | 66  |

| 3. | .4 The Dual-Dataline Sensing Scheme                                            | 72  |

|    | 3.4a Dual-Dataline Sensing Scheme                                              | 72  |

|    | 3.4b Circuit Implementation                                                    | 76  |

|    | 3.4c Simulation Results                                                        | 78  |

| CH | APTER 4                                                                        | 84  |

| 1  | .1 Motivation                                                                  | 01  |

|    |                                                                                |     |

| 4. | .2 Background                                                                  |     |

|    | 4.2a Convolution Operation                                                     | 85  |

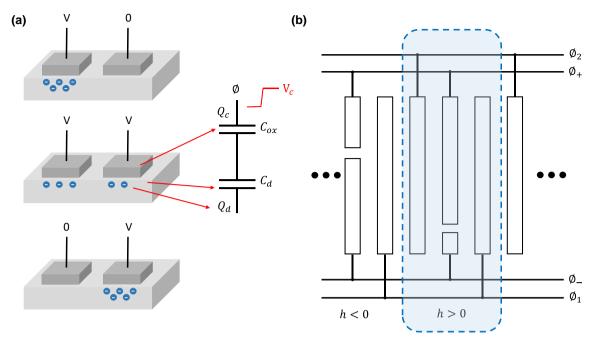

|    | 4.2b Charge-based Convolution Devices                                          | 86  |

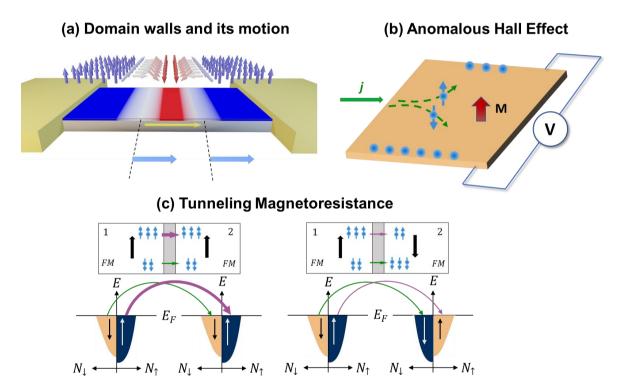

|    | 4.2c Spintronic Mechanisms for Computing                                       | 89  |

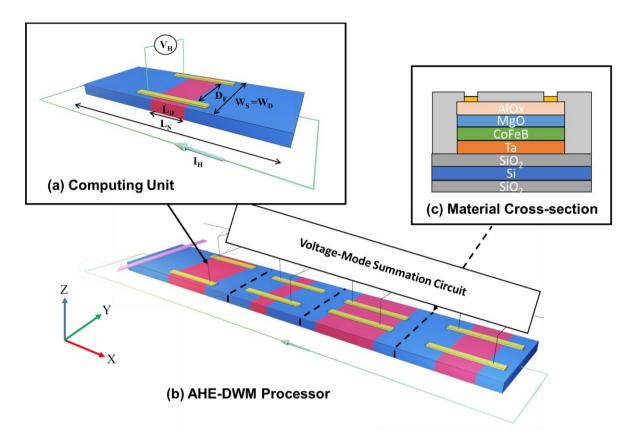

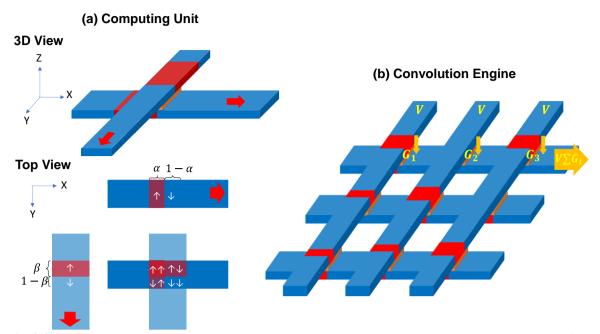

| 4. | .3 Anomalous Hall -Domain Wall Motion(AHE-DWM) Convolution Engine              | 92  |

|    | 4.3a Device Structure                                                          | 92  |

|    | 4.3b Performance Analysis                                                      | 95  |

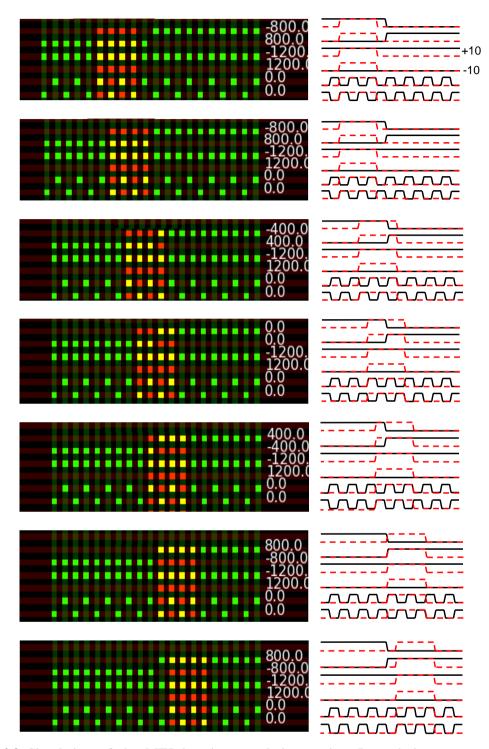

|    | 4.3c Experiments                                                               | 101 |

| 4. | .4 Magnetic Tunneling Junction-Domain Wall Motion (MTJ-DWM) Convolution Engine | 107 |

|    | 4.4a Device Structure                                                          | 107 |

|    | 4.4b Performance Analysis                                                      | 110 |

|    | 4.4c Simulation                                                                | 112 |

| СП | ADTED 5                                                                        | 115 |

# LIST OF FIGURES

| _         | Biological neuron and the McCulloch-Pitts model                                      |     |

|-----------|--------------------------------------------------------------------------------------|-----|

|           | Speedup of various AI platforms on a GPU                                             |     |

| Fig.1.2.2 | Physical implementation of matrix multiplication                                     | 8   |

| _         | MRAM operation mechanisms                                                            |     |

| Fig.1.3.2 | Illustration of spin-based nonvonventional computing methods                         | .12 |

|           | Firing activity of grid cells                                                        |     |

| Fig.2.1.2 | Common activation functions used in today's neural networks                          | .15 |

| Fig.2.2.1 | The distinct features and behavior of <i>max</i> and <i>coincidence</i> neurons      | .16 |

| Fig.2.2.2 | Modelling algorithm of the specialized neurons                                       | .18 |

|           | Obtaining a second feature map from the first                                        |     |

| Fig.2.3.3 | Illustration of the evolutionary process and the mutation NAS search method          | .26 |

| _         | Pseudo code of the mutation NAS algorithm                                            |     |

| _         | The mutation of an architecture                                                      |     |

|           | The network architecture of our growth-based NAS                                     |     |

|           | Pseudocode of the growth NAS algorithm                                               |     |

| _         | The network architecture of our pruning NAS                                          |     |

|           | Pseudocode of the pruning NAS.                                                       |     |

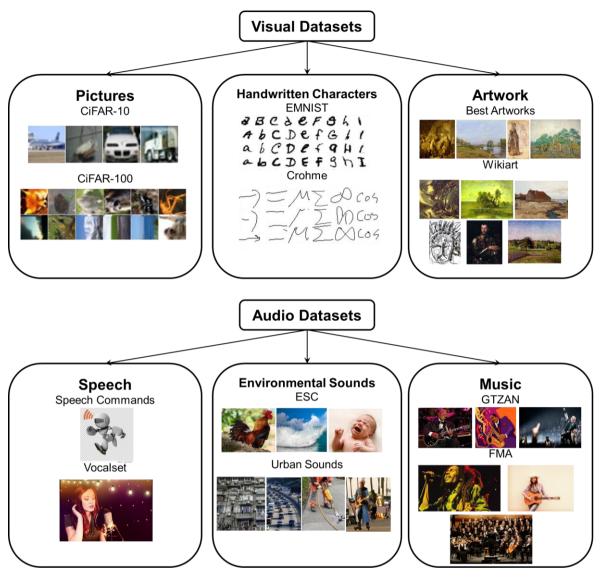

|           | List of datasets used in this research. I                                            |     |

| _         | Scatter plot of network performance of the initial and final population              |     |

| _         | Structural organization of the top performing networks discovered by mutation        |     |

| _         | Structural composition of top performing networks found by mutation                  |     |

| _         | Structural organization of the top performing networks discovered by growth          |     |

|           | Structural composition of top performing networks found by the growth                |     |

|           | Importance of neurons in the network during pruning on the CiFAR-10 dataset          |     |

|           | Pruning NAS results on the audio datasets                                            |     |

| _         | <b>0</b> Scatter plot of the normalized performance of various network architectures |     |

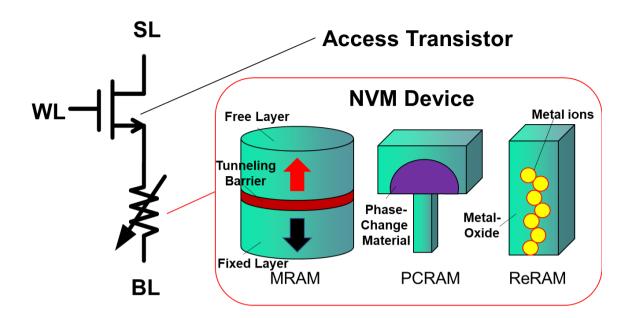

|           | Structure of a 1T-1R memory cell                                                     |     |

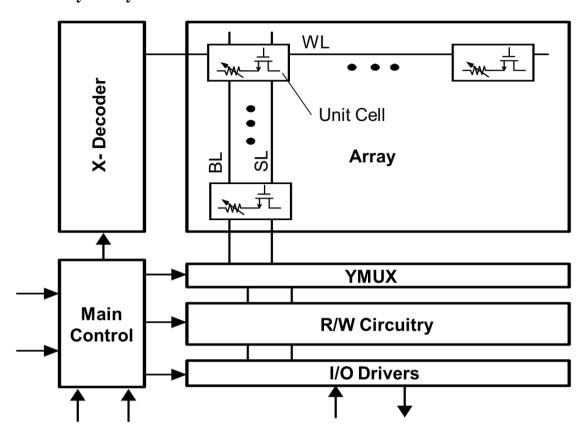

|           | Structure of a memory macro.                                                         |     |

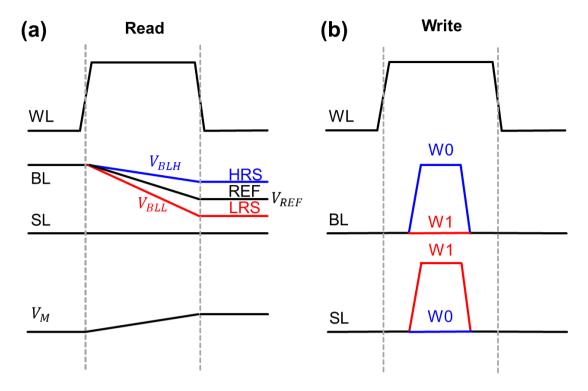

| _         | Read and write waveforms of a memory array                                           |     |

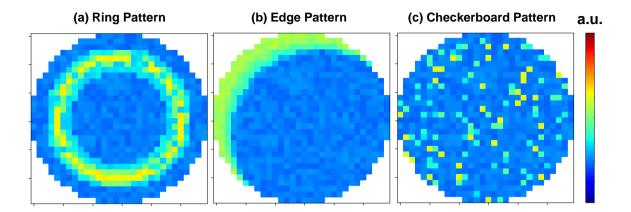

| Fig.3.2.4 | Common wafer variation patterns,                                                     | .59 |

|           | Delay variations caused by critical path.                                            |     |

| _         | Illustration of the 2D calibration scheme                                            |     |

|           | Algorithm to find calibration values.                                                |     |

|           | Read and write design modifications for the 2D calibration.                          |     |

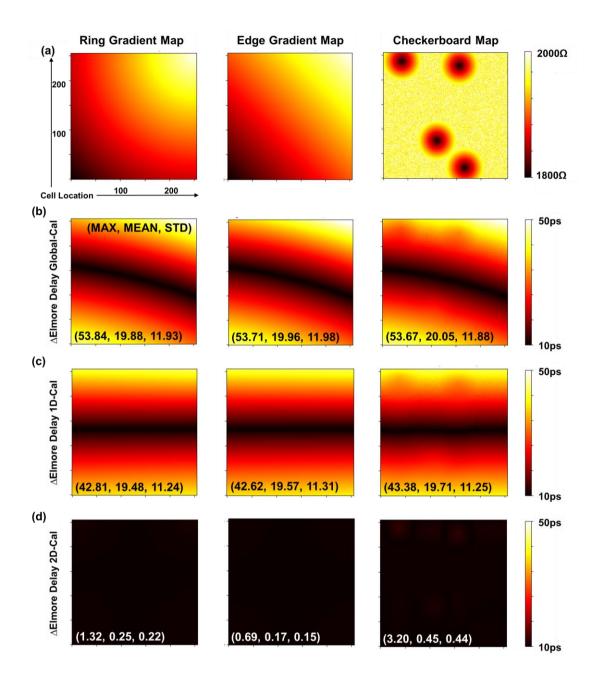

| _         | Performance of global, 1D, and 2D calibrations on various wafer patterns             |     |

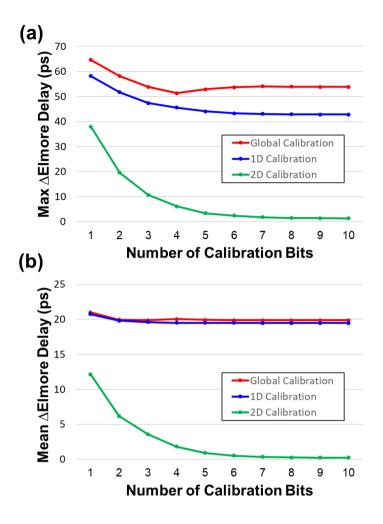

| _         | Performance of different calibration methods to the number of calibration bits       |     |

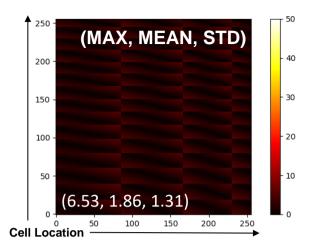

| _         | A post-calibration heatmap of 2D calibration with $ncal = 4$                         |     |

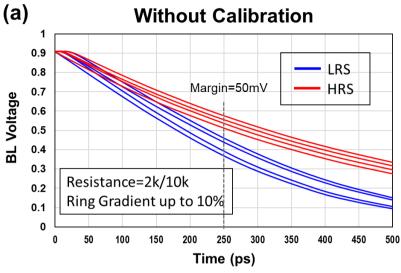

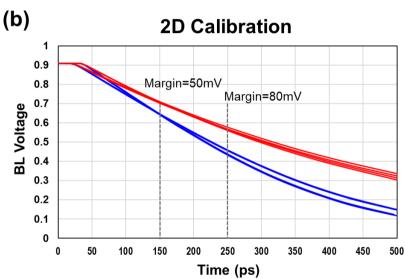

| _         | BL waveforms of the worst-case cells during read with 2D calibration                 |     |

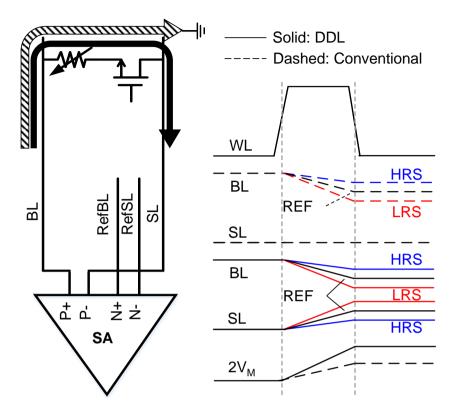

| _         | . Illustration of the DDL scheme                                                     |     |

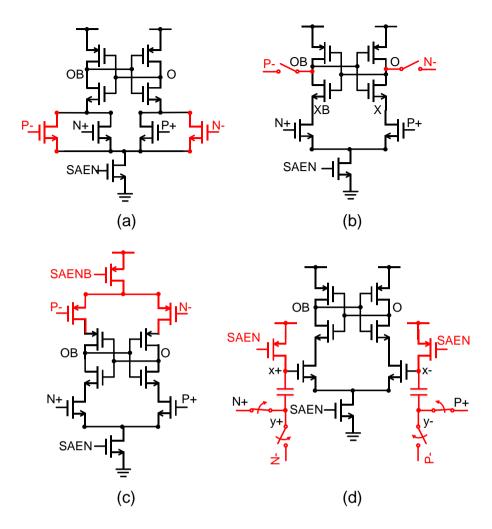

| _         | Sense amplifier designs to utilize the DDL scheme.                                   |     |

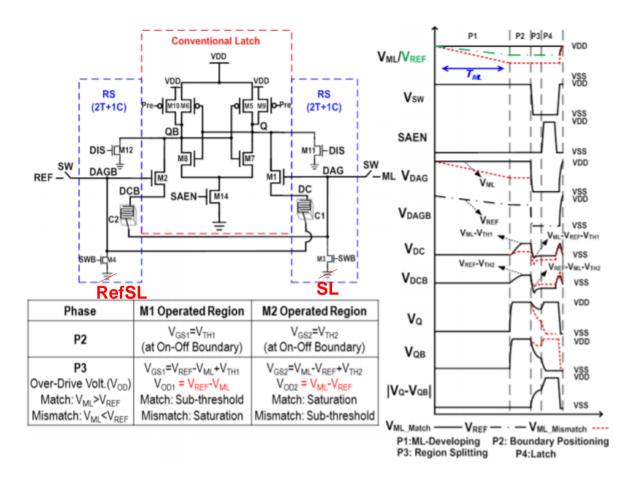

|           | The RS-SA featuring offset cancellation and on-off boundary operation                |     |

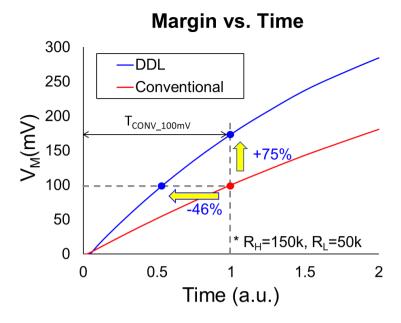

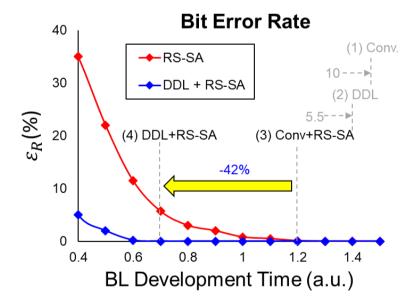

|           | Read margin as a function of BL development time                                     |     |

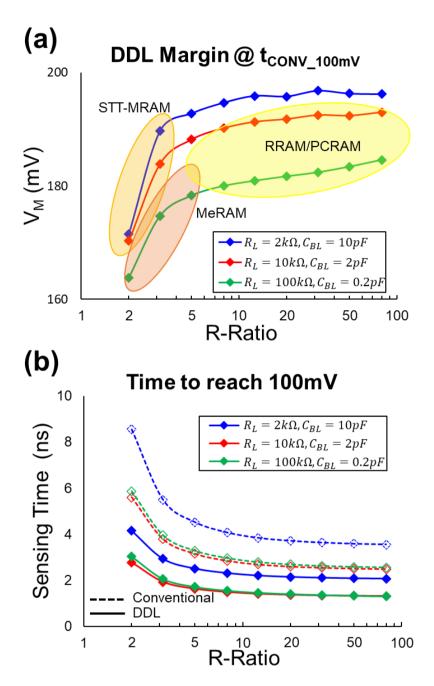

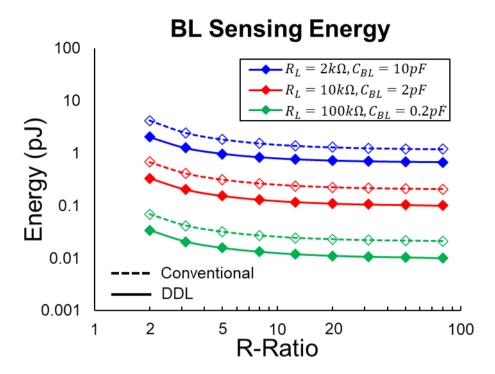

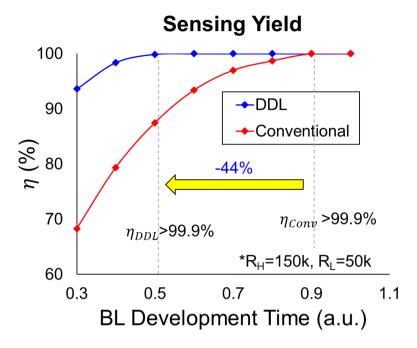

| Fig.3.4.5 | . Read margin and sensing time as a function of resistance and R-Ratio               | .80 |

| ne 81   |

|---------|

| 82      |

| emes 82 |

| 87      |

| 89      |

| 93      |

| 94      |

| E101    |

| 103     |

| 103     |

| 104     |

| 104     |

| 105     |

| 106     |

| 107     |

| 108     |

| 113     |

| 117     |

|         |

# LIST OF TABLES

| Table 2.4.1 NAS settings for each dataset.                                               | 41 |

|------------------------------------------------------------------------------------------|----|

| Table 3.3.1 Performance and overhead of different calibration schemes                    | 71 |

| Table 4.3.1 Device and material parameters of a Ta/CoFeB/MgO system                      | 97 |

| Table 4.3.2 Per-unit device performance metrics of the spintronic convolution engine.    | 99 |

| Table 4.3.3 Performance of an 1024-point convolution of the proposed approach.         1 | 00 |

| Table 4.4.1 Performance of the 1024-point MTJ-domain convolution engine                  | 11 |

#### ACKNOWLEDGEMENT

First of all, I would like to thank my advisor Dr. Kang Wang, an inspiring lecturer and scientist. He is my example of life-long learning, and I sincerely look up to how he continues to be extremely devoted to science despite his busy schedule. Academically, Prof. Wang allows his students to freely explore while putting us in touch with a large variety of ideas. I learned a lot from ideas that worked out, and perhaps even more from those that didn't. In addition, Prof. Wang's grand visions taught us how to view things from a greater perspective and consider about how technology interacts with the world. Throughout my Ph.D. degree, I have learned skills towards every aspect of my career path- critical thinking towards research, managing relationships with collaborators, interacting with the industry, funding for projects, intellectual properties for startups, and many more. Prof. Wang is truly the one who shaped me into the researcher I am today. On the same note, I'd like to thank Mrs. Wang, who I had the privilege to work with and learn from on various occasions. I'm a big fan of her turkey recipe as well.

I would also like to thank my committee members, Prof. Yang, Prof. Gupta, and Prof. Wu, for taking the time to discuss and go through my research and provide me with valuable advice. I would further like to thank Prof. Gupta and Prof. Pamarti, with whom I had the chance to work with very closely; and Mrs. Katie Christensen, who has been fully supportive of the group, working tirelessly with us on tight deadlines. Finally, I wish to thank Prof. Schwartz, a friendly and knowledgeable professor who serves as a secondary mentor to our subgroup, and Prof. Khalili, who introduced me to the group's magnetic technologies.

It has been an incredible experience working with the top minds at DRL. I would like to thank, in chronological order: Dr. Hochul Lee, a talented and devoted researcher. We've had countless inspiring discussions that lead to a major part of my publications, patents, and proposals. I also had the chance to participate in many of his life events (including his wedding),

and I consider him to be not only a role model but also a true friend. Likewise, I thoroughly enjoyed working with Mr. Farbod Ebrahimi, a brilliant engineer and a serial brainstormer who actively pursues higher expectations for himself. He is one of my best friends in LA and an amazing person to have deep conversations with regardless of your perspective. I have worked on countless occasions with Dr. Di Wu, who is a devoted scientist and an exceptional negotiator. He is continuously enthusiastic about bringing technologies to real-life applications, working around the clock available nearly 24-7. Mr. Bingqian Dai, the group mascot with great theoretical knowledge and is very supportive of new ideas. Di and Bingqian are my major collaborators towards the end of my Ph.D. degree. While it is impossible to list everyone that has inspired me during my degree, some of the others whom I had the chance to interact with include: Dr. Wenyuan Li, Dr. Xiang Li, Dr. Rick Tsai, Dr. Bald Tsai, just recently a doctor Yuching Hsiao, not-a-doctor-yet Ping-Keng Lu, Jiyue Yang, Dr. Chin-Chung Chen, etc.... I wish all a successful carrier.

Finally, I would like to thank my family and those who I consider to be. You have been by my side through tough times and hardship; when I have been stubborn, immature, selfish, and bad-tempered. Thank you for being by my side through the years, and for being generous when I refused to admit wrong. I am not perfect, but I truly care for you and wish could do/have done more. I would specifically like to thank Ximeng Fan, who has taught me to be optimistic and to bring joy to those around me. We share many interests and viewpoints, and we can be civil on the ones we disagree with. Thank you for dealing with some of my stupid life decisions, both prior and moving forward; and for supporting me throughout.

#### **VITA**

### **Education**

2013-2015 M.S. in Electrical Engineering

National Tsing-Hua University

Hsinchu, Taiwan

2009-2013 B.S. in Electrical Engineering and Computer Science

National Tsing-Hua University

Hsinchu, Taiwan

# **Employment history**

2016-2021 Circuit Design Engineer

Inston Inc.

Los Angeles, California

2015-2021 Graduate Student Researcher

Department of Electrical and Computer Engineering

University of California, Los Angeles

Los Angeles, California

2017-2017 Teaching Assistant: Logical Design of Digital Systems

Department of Electrical and Computer Engineering

University of California, Los Angeles

Los Angeles, California

2014-2015 Internship: Circuit Designer

United Semiconductor Corporation Flash Memory Circuit Design Team

Hsinchu, Taiwan

2014-2015 Teaching Assistant: An Introduction to VLSI; Embedded Memory Design

Department of Electrical Engineering

National Tsing-Hua University

Hsinchu, Taiwan

2013-2015 Graduate Student Researcher

Department of Electrical Engineering

National Tsing-Hua University

Hsinchu, Taiwan

2010-2010 Internship: Circuit Designer

Novatech

Mobile Design Team Hsinchu, Taiwan

#### **Selected Publications**

- <u>A. Lee</u>, B. Dai, D. Wu, H. Wu, R. N. Schwartz, and K. L. Wang, "A thermodynamic core using voltage-controlled spin-orbit-torque magnetic tunnel junctions", Nanotechnology, 2021.

- <u>A. Lee</u>, R. Jagannathan, D. Wu, and K. L. Wang, "A 2-D Calibration Scheme for Resistive Nonvolatile Memories", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 28(6), pp.1371-1377, 2020.

- <u>A. Lee</u>, D. Wu, and K. L. Wang, "Torque Optimization for Voltage-Controlled Magnetic Tunnel Junctions as Memory and Stochastic Signal Generators", IEEE Magnetics Letters, 10, pp.1-4, 2019.

- <u>A. Lee</u>, H. Lee, F. Ebrahimi, B. Lam, W.H. Chen, M.F. Chang, P. Khalili, and K. L. Wang, "A dual-data line read scheme for high-speed low-energy resistive nonvolatile memories", IEEE Transactions on Very Large Scale Integration Systems, 26(2), pp.272-279, 2017.

- <u>A. Lee</u>, C. P. Lo, C. C. Lin, W. H. Chen, K. H. Hsu, Z. Wang, F. Su, Z. Yuan, Q. Wei, Y. C. King, C. J. Lin, H. Lee, P. Khalili, K. L. Wang, Y. Wang, H. Yang, Y. Liu, and M. F. Chang, "A ReRAM-Based Nonvolatile Flip-Flop With Self-Write-Termination Scheme for Frequent-OFF Fast-Wake-Up Nonvolatile Processors", IEEE Journal of Solid-State Circuits, 52(8), pp.2194-2207, 2017.

- <u>A. Lee</u> and K. L. Wang, "Full Memory Encryption with Magnetoelectric In-Memory Computing", In 2019 International Symposium on VLSI Technology, Systems and Applications, pp.1-2, 2019.

- <u>A. Lee</u>, C. C. Lin, T. C. Yang, and M. F. Chang, "An embedded ReRAM using a small-offset sense amplifier for low-voltage operations", In 2015 VLSI Design, Automation and Test, pp. 1-4. 2015.

- <u>A. Lee</u>, M. F. Chang, C. C. Lin, C. F. Chen, M. S. Ho, C. C. Kuo, P. L. Tseng, S. S. Sheu, and T. K. Ku, "RRAM-based 7T1R nonvolatile SRAM with 2x reduction in store energy and 94x reduction in restore energy for frequent-off instant-on applications", In Symposium on VLSI Circuits, pp. C76-C77, 2015.

## **Accepted Patents**

[US10861527B2], [US10255976B1], [US9972400B1], [US9722584B1], [US9502114B1], [US9564209B1]

## **CHAPTER 1**

### INTRODUCTION

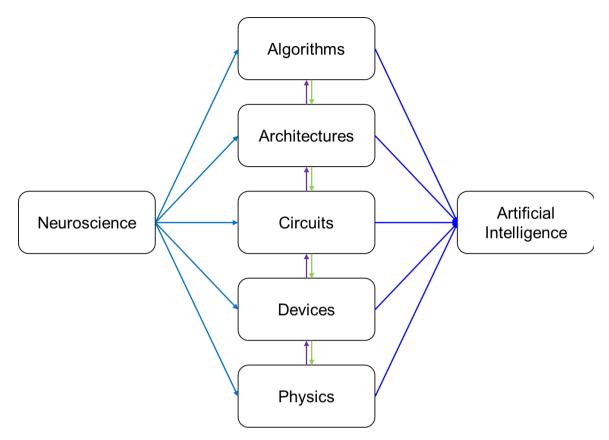

In this research, we address the advancement of next-generation AI from three vertical perspectives: At the algorithm level, the development of bio-inspired neural networks with neurons specialized for information processing; at the hardware level, improved memory design for AI accelerators; and at the single device level, spintronic devices that compose AI computation via physical mechanisms. This dissertation is organized as follows:

Chapter 1 gives an overview of the three perspectives. In Sec.1.1, We go over the historical development of AI where there were periods of booming interest and as well as times when there was lack of resources in the academia, industry, as well as the government. We review the historical reasons and events that lead to widespread AI enthusiasm, the challenges that lead to its temporary downfalls, and how prior developments affected AI as it is today. In Sec.1.2, We discuss the hardware accelerators for efficient, high-performance AI computation, from CPUs and GPUs to ASICs and memristive crossbars. In Sec.1.3, we review the history of spin-based mechanisms, recent discoveries, and their applications.

Chapter 2 presents our algorithmic approach of adopting bio-inspired signal-processing neurons in machine learning. In Section 2.1, we discuss our motivation and show examples of neuronal behavior that are critical to information processing in the human brain. In Sec.2.2, we present a modelling algorithm that is used to create models of the the signal-processing neurons. To understand the role of these neurons, we propose three bio-inspired neural architecture search (NAS) algorithms in Sec.2.3, e.g. genetic mutation, neural growth, and neural pruning. These NAS algorithms allow us to study optimized network architectures containing the signal-processing neurons as the amount of neurons in the network stays constant, increases, and decreases. Sec.2.4 describes the setup for our experiments, which include data perparation, the parameters for the NAS, and the parameters for training. Sec.2.5 presents analysis results on

the optimized network architectures, revealing general structures and the organization of the neurons. These results are used to create a new efficient and high-performance network.

Chapter 3 presents our approach for improving memory performance in AI accelerators. Section 3.1 discusses the importance of memory in AI accelerators and why they are the bottleneck in computation performance. In Section 3.2, we give an introduction on memory architecture, design, and challenges, with focus on sources of variability that limit memory performance. We then propose two approaches to overcome variation. Section 3.3 describes the 2D calibration scheme, in which an improved calibration grid compensate for variations across an array. Section 3.4 describes the dual dataline sensing scheme, in which the circuit's tolerance of variability is enhanced though a higher sensing margin. In both schemes, we show the high-level description, circuit implementation, and the simulated performance.

In chapter 4, we present our spintronic device capable of high-efficiency signal processing. Sec.4.1 outlines our motivation, which discusses the advantages of spintronics over electronics such as the flexibility in computing mechanism and nonvolatility. Sec.4.2 give a background on the problem that our device aims to solve (e.g. convolution) and the spin mechanisms that are used. In Section 4.3 and 4.4, we present two implementations of the spintronic signal processor, each based on a combination of various spin mechanisms. In both designs, we show the device structure, the theoretical performance, and the experiment or simulation results.

Finally, we wrap up this dissertation with a conclusion and a discussion of future works in the direction of the presented research in Chapter 5. We also present our perspectives towards the future of AI.

# 1.1 History of Neural Networks

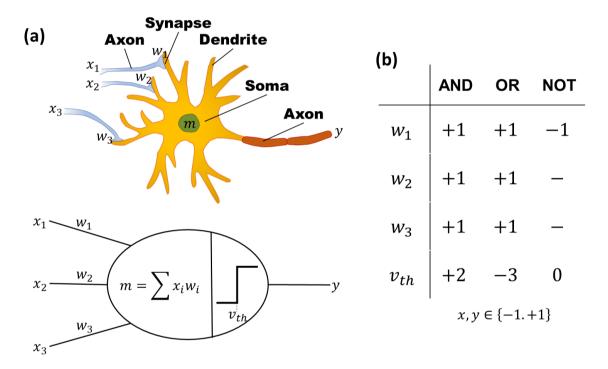

The large number of recent breakthroughs make artificial neural networks seem like a recent discovery, yet its development actually dates far back with its fair share of ups and downs. The earliest artificial neurons can be traced back to 1943 when Walter Pitts and Warren McCulloch, a neuroscientist and a logician, teamed up to create a mathematical model of a neuron in the human nervous system [1]. This model, shown in **Fig.1.1.1a**, captured the operation of the neuron in two parts: (1) The integration of input signals coming from axons, weighted by the strength of synapses as the potential of the neuron body (Soma); (2) The response of the neuron

**Fig.1.1.1** Biological neuron and the McCulloch-Pitts model. (a) In a neuron, the potential of the soma is the sum of the signals from its input axons weighted by synapses. When this potential exceeds a threshold, a pulse is sent to the output axon. This procedure is modelled in the McCulloch-Pitts neuron via integration of weighted inputs and a binary threshold function. (b) Weight and threshold design to implement the AND, OR, and NOT logical functions with a McCulloch-Pitts neuron.

potential, goingwhich goes through a rapid depolarization when it reaches a threshold. The McCulloch-Pitts neuron model can thus be described as a process with inputs  $x_i$ , each weighted by their respective weights  $w_i$ , integrated as the neuron potential  $m = \sum x_i w_i$ ; then passing the potential through a binary threshold function as the neuron's output (e.g. y = 1 if  $m > v_{th}$  else -1). The authors further showed that the model is capable of modelling universal

logic functions AND, OR, and NOT by designing the neurons weights and threshold, as shown in **Fig.1.1.1b**. For example, consider binary imputs and outputs of  $\pm 1$ . A 3-input neuron with weights of all +1 and a firing threshold of -3 would output +1 if any input is +1, and only -1 if all its inputs are -1. This neuron thus implements a 3-input OR function.

Later, Frank Rosenblatt combined the McCulloch-Pitts neuron with biological learning rules discovered to develop the perceptron [2]. By applying the learning rule discovered by neuroscientist Donald Hebb: "Neurons that fire together, wire together" [3], the perceptron promised learning capabilities of achieving binary classification on its own. Rosenblatt optimistically predicted that the perceptron "may eventually be able to learn, make decisions, and translate languages". Soon afterward, Alexey Grigoryevich Ivakhnenko and Valentin Grigor'evich Lapa proposed a hierarchical representation now considered the first multi-layer network [4].

Optimism in the bright future of AI led to a surge in funding, research interest, and, unfortunately, inflated promises on its abilities. When many of these claims failed to materialize, concerns soon arose across both funding agencies and the academia. The US government, initially interested in its ability to automatically translate Russian documents, became concerned about the lack of progress in automatic machine translation despite millions of investments. In 1964, the national research council (NRC) formed the automatic language processing advisory committee (ALPAC) to look into this issue; and concluded that machine translation was more expensive, less accurate, and slower than human translation [5]. Similarly, in the UK, Professor James Lighthill, tasked by the British Science Research Council to evaluate the state of AI research, concluded that "In no part of the field have the discoveries made so far produced the major impact that was then promised" [6]. These events led to a wide termination of funding support for AI. Academically, Marvin Minsky and Seymour Papert outlined the theoretical limitations of perceptrons in their book "Perceptrons", resulting in a

sharp drop in AI interest [7]. The lack of funding and academic interest led to a period now known as the first AI winter [8].

Research in AI revived in the mid-80s with Paul Werbos's backpropagation algorithm [9], which enabled practical, efficient training of multi-layered networks by computing error gradients through the chain rule and modifying the weights at each node accordingly. This renewed interest led to new discoveries that compose the core of many of today's AI algorithms. In 1979, Kunihiko Fukushima developed the Neocognitron based on the structure of the human primary visual cortex [10]. It demonstrated the ability to recognize visual patterns as the first convolutional neural network architecture. The Hopfield Network [11] developed by John Hopfield in 1982, made recurrent structures popular and showed promise as dynamic content-addressable memory. Q-learning presented by Christopher Watkins [12] laid the groundwork for reinforcement learning via the introduction of states, actions, and delayed rewards.

These new developments brought about the commercialization of a form of AI called the *Expert system*. The *Expert system* aims to emulate the decision-making process of a human expert to solve complex problems and make sequential decisions by reasoning through a knowledge database. In the early-mid 1980s, *Expert systems* such as XCON showed enormous commercial success and were adopted by companies around the world. Billions of dollars poured into the industry, supporting software companies like Techknoeldge, Intellicorp, and hardware companies such as Symbolics and LISP (List-Processing) machines.

However, *Expert systems* proved to be too expensive to maintain and update. They were rigid and fragile, and competition from general purpose systems soon brought down their market. Workstations from Sun Microsystems provided alternatives just as powerful but much more flexible, while personal computers from Apple and IBM provided a simpler and (through development) architecture that achieved similar results. With the market share of *Expert*

systems taken away, their demand collapsed as quickly as it rose. By the early 1990s, nearly all commercial Expert system companies had failed.

This commercial failure resulted in a second blow to the development of AI. In this second AI winter, many researchers deliberately avoided the term AI, using alternate terms like informatics, intelligent systems, and knowledge-based systems. Some believed that their works were fundamentally different from what was previously called AI, while some simply didn't want the reputation that came with the name. Nevertheless, the data-driven approach of Expert systems significantly influenced AI algorithms built today.

The recent revival of AI in the 2000s has much to do with the exponential increase in computing power from the scaling of silicon chips. Initially, brute-force approaches demonstrated superhuman performance across various tasks. Deep Blue, with the ability to compute 200 Million moves per second, became the first computer system to beat the world chess champion in 1997 [13]. Data became a driving force of AI with Yann LeCunn's release of the MNIST handwritten digits database in 1998 [14]. MNIST provided a benchmark for evaluating the performance of AI algorithms and remains widely used even today. The Imagenet database developed by Fei Fei Li [15] and its associated ImageNet Large Scale Visual Recognition Challenge (ILSVRC) is considered by many the catalyst for the AI boom. Since 2012, neural networks dominated the challenge with the Alexnet victory, significantly outperforming other competitors by over 10 percentage points [16]. Through data, AI systems began solving challenges that brute force could not: in 2016, Google's AlphaGo, a neural network trained using reinforcement learning, becomes the first program to beat an unhandicapped professional human player in Go [17]. This feat was previously thought impossible for another 30 years as a brute force approach would have to evaluate more possibilities than the number of atoms in the universe  $(10^{82})$ .

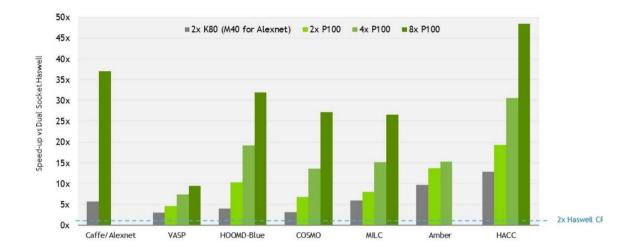

**Fig.1.2.1** Speedup of various AI platforms on a GPU. Figure adapted from Nvidia's Tesla P100 White Paper [17].

Today, our progress has far exceeded the wildest claims that brought about the 1<sup>st</sup> AI winter. Discussions surrounding the abilities of AI have shifted from questioning whether it will be useful to whether we restrict its abilities. Nevertheless, as we look towards the future, AI aims to be involved in everyday life; from tasks as small as recommending new songs to complex medical problems that trouble even top experts with decades of experience.

### 1.2 Neural Network Hardware Accelerators

The increasing demand for AI has led to the development of specialized accelerator hardware. Traditional central processing units (CPU) that were optimized for flexibility rather than parallelization did not perform well on AI tasks. On the other hand, graphic processing units (GPUs) have been able to massively parallelize AI tasks as they were built to process similar tensor (multi-dimensional vector) operations. Empirical studies show that GPUs provide over 30x speedup over state-of-the-art CPUs (Fig.1.2.1), making them the top choice for AI tasks [18]. In addition, GPU producers have also committed to developing specialized toolkits and modifying tensor cores to further accelerate AI computation [19]. These packages have been adopted by the majority of mainstream AI design platforms [20] [21].

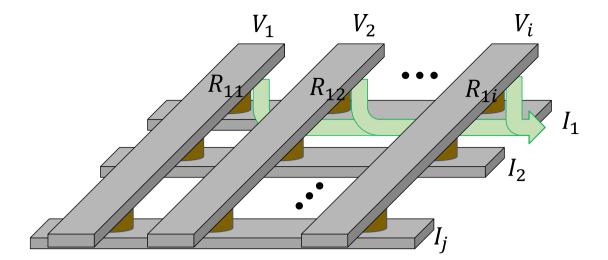

**Fig.1.2.2** Physical implementation of matrix multiplication via a crossbar of memory devices. Voltages  $V_1...V_i$  are placed on vertical wires connected to the top electrode of memristors with resistances  $R_{11}...R_{1i}$ . From the Ohm's law, each device has a current of  $V_k/R_{1k}$ . The bottom horizontal wire sums the current flowing through the memristors upon it, e.g.,  $I_1 = \sum_i V_k/R_{1k}$ . The full array entire array can be represented in matrix form as  $I = R^{-1}V = GV$ .

Compared to GPUs, application-specific integrated circuits (ASICs) can further boost the efficiency of AI computation. These accelerators discard generalized capabilities of GPUs and optimize their data flow, data format, and memory bandwidth purely for AI-related tensor processing. Many data centers today have adopted this approach with chips such as the Google TPU [22] and Baidu Kunlun processor [23] being developed; while Amazon and Facebook reportedly in the process of designing their own ASICs. Taking this approach further, designs for reduced bit counts [24]–[27], convolutional networks [28], [29], stochastic networks [30], generative adversarial networks [31], and recurrent networks [32] have also been developed.

With the recent progress in new memory technologies, researchers have also targeted the physical implementation of matrix multiplication using memory devices [33]–[37]. This approach, shown in **Fig.1.2.2**, composes a crossbar array of memory units with wires running vertically on top of the array and horizontally beneath. When voltages  $V_1 \dots V_i$  are placed on the top wires, the currents  $I_1 \dots I_j$  flowing through the bottom wires can be computed via Ohm's law and Kirchhoff's current law, as the sum of  $V_k$  times the conductance  $G_{jk} = 1/R_{jk}$  of each

memory unit, e.g.  $I_j = \sum_i V_k G_{jk}$ . Considering the entire array, the bottom wire currents can be expressed as in matrix form as I = GV. This architecture allows efficient matrix multiplication in a single cycle and significantly reduces data access across memory hierarchies.

In the advancement of AI hardware, the effect of the memory bottleneck on computing performance has become increasingly evident. As much as designs attempt to avoid the memory bottleneck (also known as the Von-Neumann Bottleneck), powerful algorithms and networks continue to demand more memory. Today's networks are often orders of magnitude larger than those used a decade ago [38]. Hundreds of megabytes are needed for weight storage alone, and an order more for computing gradients and intermediate values during training. As a result, addressing memory limitations is a critical issue in further advancing AI.

# 1.3 Spintronic Technology

Spintronics is an emerging research field that relates to the study of the electron spin and its associated magnetic moment. The theoretical foundation of spintronics was developed by Wolfgang Pauli via Pauli matrices and quantum mechanics in the 1920s [39], which also described its relation to the quantized electron spin. Subsequently, a variety of spin-related theories have been proposed, including that of the Landau–Lifshitz–Gilbert dynamics [40] in 1935 and the prediction of the spin Hall effect in 1971 [41].

Spintronic applications took a huge step forward with the discovery of magnetoresistance effects in the 80s from tunneling experiments. Meservey and Tedrow's experiments on a ferromagnet/superconductor stack [42] and Jullière's experiments on Fe/Ge/Co stack [43] discovered the conservation of spin and the tunneling magnetoresistance effect (TMR). With the development of thin-film fabrication tools, Peter Grünberg and Albert Fert showed the giant magnetoresistance (GMR) in 1988 [44]. Since then, there has been an explosion in the discovery of spintronic mechanisms, including the spin-transfer torque effect (STT) [45], [46],

Spin-Orbit Coupling (SOC) effects (voltage-controlled magnetic anisotropy effect (VCMA) [47]–[49] and spin-orbit torque (SOT) [50]–[52]); spin textures (skyrmions [53]–[55], spin fluid [56]–[58], spin glass [59]–[61], and magnetic domains[62]–[64]); spin dynamics (Dzyaloshinskii–Moriya interaction [65]–[67], spin waves [68]–[70]); spin-thermal effects (Spin Seebeck [71]–[73]); and spin-optical effects (Magneto-optical Kerr [74]–[76]).

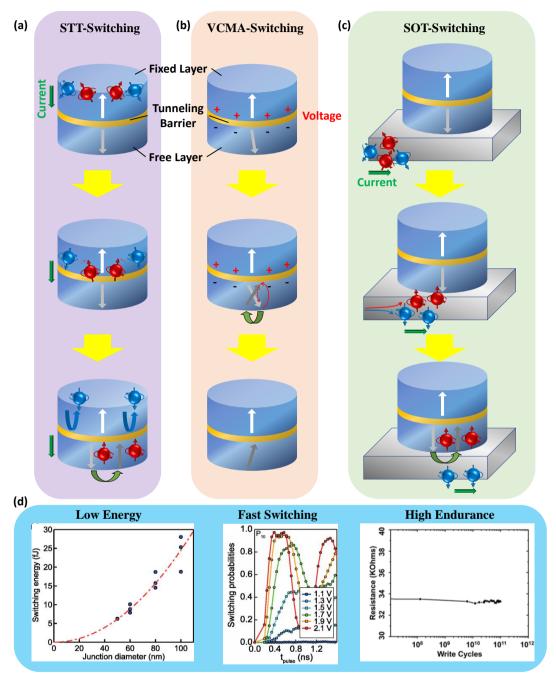

Today, spintronics is widely used in data storage and manipulation: spins provide an efficient, compact way of storing nonvolatile data in its orientation; and GMR/TMR-based sensors read out the magnetization as electrical signals. This technology brought about the development of hard drives and a drastic increase in the data storage density. In the 2000s, high tunneling magnetoresistance (TMR) magnetic tunneling junctions (MTJs) [77]–[79] have also received great interest as an integrable, nonvolatile random access memory element with high speed and endurance. Switching mechanisms have evolved from using magnetic fields to spin-based mechanisms (**Fig.1.3.1**), with STT-MRAM currently being developed by major foundries worldwide [80]–[82], and VCMA [83]–[85], SOT [86], [87] as the next-generation memory. Current research on MTJs focuses on two aspects: (1) high TMR structures with improved readability through enhanced interface characteristics and stronger polarization; and (2) energy efficient switching through enhancement of spin mechanisms.

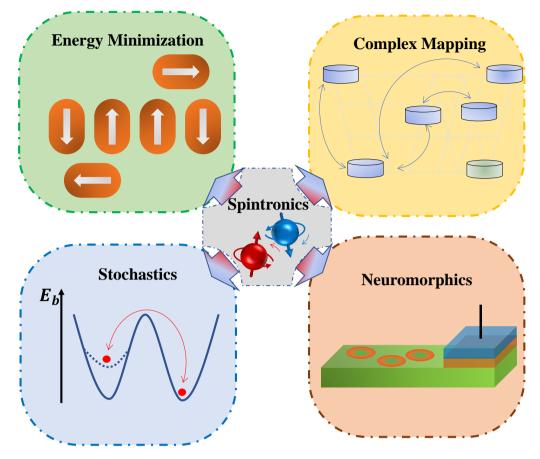

The abundance of spin mechanisms has also led to proposals for unconventional, nonbinary computing schemes (**Fig.1.3.2**). For example, coupling between magnetic elements through dipolar interaction, the Dzyaloshinskii-Moriya interaction, as well as spin waves has been proposed for optimization by utilizing the energy minimization process of the interacting bits [88]–[93]. Nonlinear interactions between spintronic elements have been used for complex mapping reservoirs built upon skyrmions, MTJs, and oscillators [94]–[98]; for composing

filter-like functions using spin-wave sources, lenses, and mirrors [99], [100]. Neuromorphic computing such as physical crossbars and nonlinear activations have been composed using

**Fig.1.3.1** MRAM operation mechanisms: (a) STT Switching. Electrons passing through the free layer transfer their spin angular momentum to the moments of the magnetic free layer, thereby switching its state. (b) VCMA switching. A voltage placed across the MTJ modifies the anisotropy of the magnetic free layer, leading to a precessional (damped oscillation) motion of the free layer magnetization. (c) SOT switching. The MTJ is placed upon a bus with high spin-orbit coupling. As current passes through the bus, electrons with different spin orientations accumulate on the sides of the material, which then transfer their spin moment to the free layer to change its state. (d) Advantages of magnetic memory: scalable, low energy, sub-ns switching, and high endurance with no degradation over 10<sup>11</sup> cycles. Subfigures adapted from [83].

**Fig.1.3.2** Illustration of spin-based nonvonventional computing methods. Energy minimization schemes compose a system of coupled spin elements so that the lowest energy state represents the solution. Complex mapping uses spin elements to map inputs to different signals, such as reserviors or high-dimensional computing. Neuromorphic devices such as synapses have been built upon spin elements, and likewise, Spin-based stochastics have utilized fluctuations in device states for computing.

domains and MTJs [101]–[105]; skyrmions have been proposed to model neurotransmitters [106]; finally, spin-stochastics have been used in probabilistic computing [107], [108], thermodynamic computing [109], and many more. However, the majority of these methods were unable to provide a definite advantage over existing CMOS implementations, and many were difficult to realize at a scaled industrial level. Our research aims to address this gap.

## **CHAPTER 2**

# SIGNAL-PROCESSING NEURAL NETWORKS

In this chapter, we present our work on utilizing special signal processing neurons to improve neural network performance. The chapter is outlined as follows: we first review different neuronal behavior and selected signal processing neurons to model. We then use neural architecture search (NAS) to optimize network architectures containing the neurons, and analyze the optimized architectures to extract characteristics of the networks. These results are then used to develop the signal-processing neural network.

Section 2.1 describes our motivation and outlines how neurons with specialized functions play a crucial role in information processing within the human brain. Chapter 2.2 reviews the functions two neurons: that of the *max* neuron in the visual cortex (Sec.2.2a) and the *coincidence* neuron in the audio cortex (Sec.2.2b), along with how they associate with neural network design today. Then, in Sec.2.2c, we detail the step-by-step process to create the approximate piecewise-linear model of these two neurons.

With the models, we then use neural architecture search (NAS) to find high-performing architectures. In Sec. 2.3, We describe the three NAS algorithms used in this study, based upon three biological pheonmena: neural growth, neural pruining, and genetic mutation. These three NAS schemes also correspond to how the network architure changes as the amount of neurons in the network stays constant, increases, or decreases. Sec.2.4 then details the setup of the experiments, e.g., the datasets we use, how they are preprocessed, and parameters of the search and training process. Analysis results of the optimized architectures is presneted in Sec.2.5, in which we illustrate how the network structure, amount of connections, and types of neurons change throughout the network. The analysis results are then used to design a compact, high-performance signal processing neural network.

### 2.1 Motivation

As described in Chapter 1, advancements in artificial neural networks have often taken inspiration from biology. For example, the McCulloch-Pitts neuron arose from modeling of the neuron's integrate and fire behavior; convolutional network structures from the visual cortex; and network compression methods from neural pruning.

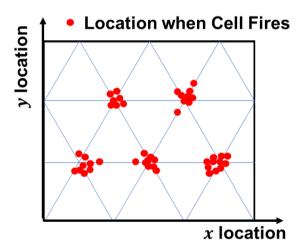

In the past decade, a large variety of neuronal behavior has been discovered. Neurons have been shown to differ in signal transmission (bipolar, unipolar, and multi-polar), functionality (sensory, motor, and interneuron), structures (connection shapes and density), as well as the type of neurotransmitter and neuromodulators involved [110]. Specialized neurons form crucial functions in information processing systems that are shared throughout organisms rather than generated through learning. For example, grid cells in the entorhinal cortex play a major role in composing the brain's cognitive spatial map [111]–[114]. They operate through the phase precession mechanism, in which the firing of a neuron is timed in relation to the phase of the neural oscillation in the surrounding cells [115]. At the behavioral level, these neurons fire when their host occupies a spatial grid in the environment (**Fig.2.2.1**). Grid cells have been

**Grid Cell Activity vs. Organism Location**

**Fig.2.1.1** Firing activity of grid cells. Grid cells fire regularly when its host organism occupies points on a spatial grid. Their firing activity contribute towards the spatial cognitive map in the brain by providing information about location and distance.

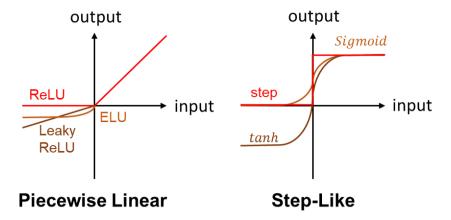

**Fig.2.1.2** Common activation functions used in today's neural networks. (Left) the family of piecewise linear units: Rectified Linear Units (ReLU) rectifying negative signals to zero, leaky ReLU has a nonzero slope in the negative region, and Exponential Linear Units (ELU) has an exponential slope in the negative region. (Right) the family of step-like activation functions take forms of the binary step, *sigmoid*, and *tanh*.

discovered across a variety of higher cognitive mammals including mice, monkeys, and humans.

Exploring and utilizing neuronal functions provide a promising path to boost machine learning performance, and could eventually lead to an improved understanding of the biological information processing flow. However, today's artificial neural networks (ANNs) have yet to take inspiration from these discoveries. Neuronal responses, often characterized by a neuron model's activation function, have settled to a few nonlinear functions after a long process of numerical and empirical exploration (Fig.2.2.2). From the binary-thresholding function used in the McCulloch-Pitts neuron, activation functions first shifted to continuous functions like sigmoid and tanh that enable backpropagation. Piecewise linear units later took the center stage due to their non-saturating gradient and low computation complexity. Rectified Linear Units (ReLU) celebrated success in image recognition [116]–[118], while those with a nonzero negative slope (Parameterized ReLU (PReLU), Exponential ReLU (ELU), LeakyReLU [119], [120]) have been used in image generation. c

### 2.2 Neuron Models

### 2.2a Max Neurons

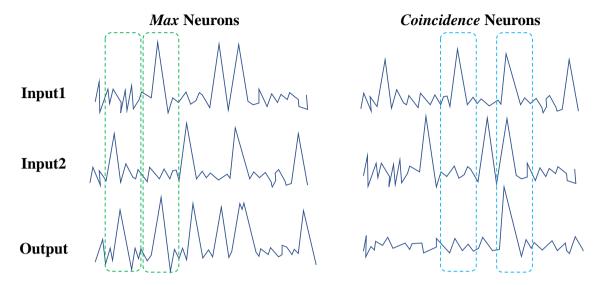

**Fig.2.2.1** The distinct features and behavior of *max* and *coincidence* neurons. A *max* neuron outputs the maximum value among its inputs, and fires whenever any of its inputs fire (green box). A *coincidence* neuron detects coincidence in its inputs, and fires only when both inputs are simultaneously active (blue box)

Signal processing in the visual cortex is mainly composed of a hierarchical buildup of receptive fields, in which larger receptive fields of latter layers can be modeled by a linear combination of the smaller receptive fields in earlier layers. However, in some of the higher regions of the visual cortex, neuronal functions that cannot be modeled by linear combinations have also been discovered. One such function is the *max* function (**Fig.2.2.1**), in which a neuron's output is determined by the input with the highest level of activity [122], [123]. The *max* function is able to identify the dominant signal in a large number of inputs, and its commutative property results in a response that is invariant to spatial shifts within its receptive field, and reduce the impact of noise in non-dominant signals [124], [125].

Since their discovery, the adaptation of the *max* function has been abundant in image processing. Its most successful adaptation is perhaps feature pooling, in which a filter scans localized patches and outputs the maximum or average value within the region. Feature pooling is often inserted after convolutions to down-sample features and extract abstract, higher-level concepts from the applied region. They have demonstrated the same benefits as the *max*

neurons, e.g., dominant signal identification, invariance to image transformations, and robustness to noise. A detailed theoretical discussion on pooling can be found in [126].

### 2.2b Coincidence Neurons

Studies of human auditory processing have shown that temporal and frequency structures are crucial to the representation of audio events [127], [128]. In the human auditory system, signals picked up by auditory nerve fibers excite cells that detect the coincidence, or simultaneous activity, in a group of fibers. *Coincidence* neurons have extremely low time constants and input resistance, giving them the ability to compare timing cues with accuracy over 100x of neural firing [129], [130]. They respond maximally when multiple input synapses are simultaneously active, and significantly less otherwise (**Fig.2.2.1**).

The success of gated networks and attention networks in audio processing is likely associated with the *coincidence* function. In a gated network, a neuron's output is blocked unless its gating signal is high. In other words, its output is high only when both the gating signal and its input are high at the same time. This behavior is characteristic of the *coincidence* function. Examples of these networks include Long Short-Term Memories (LSTMs) and gated Recurrent Neural Networks (RNNs) [131]–[133].

## 2.2c Model Algorithm

Our first step towards modeling the signal processing neurons is to represent the response of the neurons in the form of a truth table. The truth table defines the regions of linearity and boundaries where nonlinearity occurs. Here, we consider a neuron with two inputs whose activies are either *firing* or *silent*. The *max* neuron's response is the maximum value among its input synapses. In other words, its output fires whenever any of its inputs fire. On the other hand, the *coincidence* neurons only fires when all their inputs fire at the same time. The table

### (a) Truth Table Max x2 silent $x_1$ silent Silent $x_1 fires$ fires

| Coincidence  | x <sub>2</sub> silent | $x_2 fires$ |

|--------------|-----------------------|-------------|

| $x_1$ silent | Silent                | Silent      |

| $x_1$ fires  | Silent                | fires       |

#### (b) Numerical Values Max $x_2 \leq 0$ $x_1 \leq 0$ ≤ 0

| Coincidence | $x_2 \le 0$ | $x_2 > 0$ |

|-------------|-------------|-----------|

| $x_1 \le 0$ | ≤ 0         | ≤ 0       |

| $x_1 > 0$   | ≤ 0         | > 0       |

(c) Inpu

$x_1 > 0$

| ıt-Output Relationship |             |              |                   |   |

|------------------------|-------------|--------------|-------------------|---|

|                        | Max         | $x_2 \leq 0$ | $x_2 > 0$         |   |

|                        | $x_1 \le 0$ | 0            | -x <sub>i</sub> * | 4 |

|                        | $x_1 > 0$   | $x_i$        | $x_i$             | - |

|                        |             |              |                   |   |

$x_2$  fires

fires

fires

$x_2 > 0$

> 0

| Coincidence | $x_2 \leq 0$ | $x_2 > 0$ |

|-------------|--------------|-----------|

| $x_1 \le 0$ | 0            | 0         |

| $x_1 > 0$   | 0            | $x_i$     |

|             |              |           |

(d) Continuous and differentiable

$$y_{max} = ReLU(x_1) + ReLU(-x_1) * ReLU(tanh(x_2))$$

$$y_{co} = relu(x_1) * ReLU(tanh(x_2))$$

Fig.2.2.2 Modelling algorithm of the specialized neurons. The models process cosists of 4 steps: (a) creating the truth table of the neuron's response behavior, (b) assigning the numerical boundaries to regions based on the truth table, (c) assigning numerical values to each region, and (d) smoothing boundaries with the tanh function.

is shown in Fig.2.2.2a. Interestingly, the truth tables of the two neurons match that of logical functions "AND" and "OR".

After composing the truth tables, numerical ranges are assigned to define the signals that are considered as firing and silent (Fig.2.2.2b). Here, we follow the conventional definition of firing as a signal exceeding a threshold of 0 and silent otherwise.

$$x \ fires \leftrightarrow x > 0$$

;  $x \ silent \leftrightarrow x \le 0$

$$y \ fires \leftrightarrow y > 0; \ y \ silent \leftrightarrow y = 0$$

We then define the input-output relationship within each entry of the truth table. Taking inspiration from piecewise linear functions, we set the y to be linear to  $x_1$  with a unit slope when the output is *firing* and 0 otherwise:

$$y = |x_1|$$

if y is firing

$$y = 0$$

if y is silent.

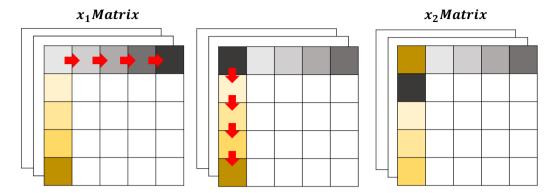

**Fig.2.2.3** Obtaining a second input  $x_2$  from a single feature map  $x_1$ . Here, we create  $x_2$  by shifting  $x_1$  by one element in each dimension of the feature map.

The corresponding gradients are:

$$|\partial y/\partial x_1| = 1$$

if y is firing

$$|\partial y/\partial x_1| = 0$$

if y is silent

Finally, as the table contains discontinuous, non-differentiable transitions, we smooth the transition between entries with tanh function on  $x_2$ . With this, we arrive at the two models of the two neurons:

$$y_{co} = R(x_1) * R(T(x_2))$$

... Eq. 2.2.1

$y_{max} = R(x_1) + R(-x_1) * R(T(x_2))$  ... Eq. 2.2.2

Where  $y_{co}$  is the *coincidence* neuron model,  $y_{max}$  is the *max* neuron model, R is the ReLU function, and T is the tanh function.

The *max* and the *coincidence* neuron models have two inputs that can come from different parts of a network architecture. Where only one input is available, we can let  $x_2$  be a manipulated or shifted version of  $x_1$ . For example, we can create  $x_2$  by shifting  $x_1$  by 1 element in each feature map dimension, as shown in **Fig.2.2.3**. In this case, we can reduce the functions to

$$y_{co\_s} = R(x_1) * R(T(x_1 \ll 1))$$

... Eq. 2.2.1a

$y_{max\_s} = R(x_1) + R(-x_1) * R(T(x_1 \ll 1))$  ... Eq. 2.2.2a

We use this reduction in our experiments in Sec.2.5.

# 2.3 Neural Architecture Search Algorithm

Specialized neurons are not located uniformly in neural networks. For example, *max* neurons are located in the higher regions of the visual cortex, operating upon the outputs of linear neurons in earlier visual regions. A network composed entirely of *max* neurons, whether biological or artificial, provides poor functionality as the entire network essentially reduces to a single wide *max*. Therefore, we must base our analysis on suitable network architectures. Toward this goal, we use network architecture search (NAS) to obtain high-performing architectures.

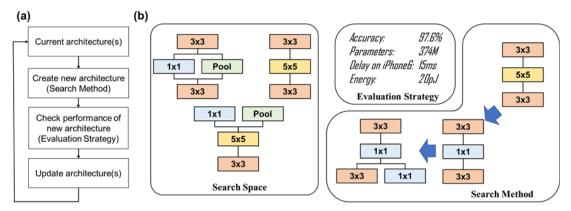

A NAS algorithm (**Fig.2.3.1**) optimizes a network by iteratively searching through an architecture space to find the best-performing architecture. It begins from a set of initial architectures; then, in each search iteration, new architectures are created and evaluated. If the new architectures perform well, they are used to update the current architectures. As a result, a high performing architecture can be obtained after multiple iterations.

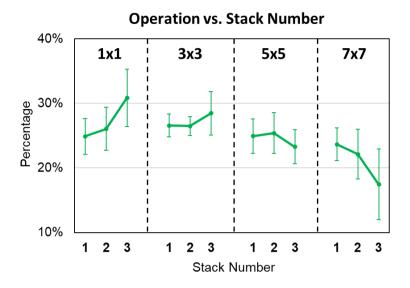

A NAS algorithm can be described in three components [134]: the search space, the search method, and the evaluation strategy. The search space defines the architecture space that the algorithm searches through, and is composed of an operation space and a structure space. The operation space defines the set of operations available to the architecture, and the structure space defines how the connections between operations are formed. The operation space can include different types of operations such as convolutions (2D, separable, depth-wise) and pooling (max, average); with various kernel dimensions (3x3, 5x5,7x7), strides (1,2,4), and dilation rates (1,2,3,4) [135]. The structure space could be sequential [136], [137], hierarchical [138], cell-based [135], [139], or memory-access-like topologies [140]. An example is shown in **Fig.2.3.1b** *Search Space*. In the example, the operation space includes "1x1 convolution (conv)", "3x3 conv", "5x5 conv", and "pool"; and the structure space is "serial" and "parallel". The search space design often involves certain amounts of human expertise and experience.

Fig.2.3.1 Illustration of a Neural Architecture Search (NAS) algorithm. (a) Flow of a NAS algorithm. The algorithm iteratively creates and evaluates new architectures to find an optimized architecture. (b) components of a NAS algorithm. The search space defines the space of all architectures. For example, the architecture could be a serial connection of a 3x3 convolution (conv), a 5x5 convolution, and another 3x3 convolution (top right in Search Space). It could branch from a 3x3conv into a 1x1 conv and a pooling in parallel, then merge back before the final 3x3 conv (top left in search space); or it could start from a parallel architecture before merging into a serial one (bottom in search space). The search method defines how the network architecture changes between each search iteration. For example, starting from the 3x3conv-5x5conv-3x3conv in the first iteration, the second layer is changed to a 1x1conv in the second iteration, and the last layer branches out another 1x1 conv in the third iteration. The evaluation strategy provides a measure of the performance of each architecture. This includes metrics such as the accuracy of the network, the memory it consumes, as well as the time and energy it takes to run.

The search algorithm defines how the network architecture changes between each search iteration. This could be re-selecting a network architecture from the search space at random or a grid-search through its parameters [141]. It could involve modification upon a previous top-performing network [138], [139]; or be determined by another neural network through a reinforcement-learning setting [136], [137]. If the architecture is differentiable, the architecture could also be trained [142]. An example of a search method is shown in **Fig.2.3.1** *Search Method*. In the example, the search method replaces the second layer in the first iteration, and branches the third layer in the second iteration.

The evaluation strategy provides a measure of the model's performance. This determines the NAS optimization target and is usually a combination of various performance metrics, such as accuracy, the number of flops, required memory, operation energy, latency, etc. Different designs of the evaluation strategy allow the NAS algorithm to optimize the architecture for a

single metric or a trade-off between metrics under a given set of constraints. An example of an evaluation strategy is shown in **Fig.2.3.1** *Evaluation Strategy*. In the example, we see that the accuracy, the network size (number of parameters), the delay on an iphone, and the energy are all components of the evaluation strategy. In most cases, the most important metric is an accuracy  $\alpha$ . The traditional way to obtain  $\alpha$  is to train and evaluate a network [143]. However, a complete train-and-evaluation procedure is costly. As a result, accuracy extraction has been accelerated through shortened training schedules on reduced-size networks [136], [139], adopting pre-trained or shared weights [144], [145], or using proxy tasks with lower complexity [135]. Accuracy could also be estimated via another neural network [140], [146].

In the remainder of this section, we present the three bio-inspired NAS algorithms used in this work. We describe the details of the search space, search algorithm, and the evaluation strategy of each algorithm. The mutation NAS algorithm is inspired by genetic mutation. During genetic mutation, the number of genes stays the same, but the genetic expressions change. Based on this observation, our mutation NAS maintains the same number of neurons, connections, and operations throughout the search process; while the architecture and the operations change. Our growth NAS is inspired by the growth of neural pathways during an organism's learning process in which new neurons and connections are formed. Taking inspiration from this, the growth NAS continuously adds neurons to the network by splitting and branching existing connections. The pruning NAS is inspired by neural pruning. During neural pruning, less important neurons are gradually removed from the network, making it more compact, efficient, and representative. Our pruning NAS follows this principle: neurons deemed less important to the task (as evaluated by an *importance* measure  $\varphi$ ) are progressively removed during the search process. These three algorithms allow us study how the network architecture as its size (e.g. amount of neurons) is kept constant, increases, or reduces.

# 2.3a Mutation NAS Algorithm

Our mutation NAS is based on the search space and search method of the evolutionary algorithm described in [139] combined with the differentiable search described in [142]. The evolutionary component primarily optimizes the network structure, while the differentiable component finds the optimal neurons of the network. We detail this below.

## Mutation NAS Search Space

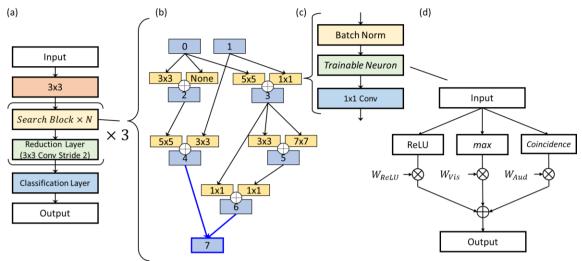

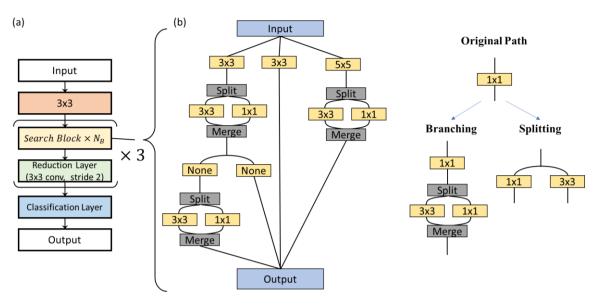

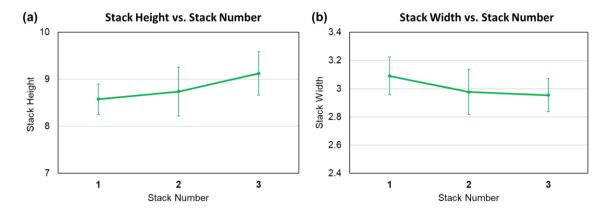

At the top level, the network of our mutation NAS has a block-based architecture (**Fig.2.3.2a**) composing an initial 3x3 convolution followed by three repetitions of (*search block*  $\times$   $N_B$  – reduction layer) stacks and a classification layer, where  $N_B$  is the number of *search blocks* in each stack. The NAS optimizes the network through manipulating the architecture of each *search block*. Connections and operations in the *search block* are modified during the NAS search process, but the number of nodes stay identical.

Each  $search\ block\ (Fig.2.3.2b)$  has an independent architecture composed of 8 nodes: node0 and node1 are replicas of the previous block outputs, node2 to node6 are pairwise combinations, and node7 concatenates unused node outputs to create the  $search\ block$  output. A pairwise combination takes the output of two previous nodes, applies an operation to each, and sums the result. For example, in Fig.2.3.2b, node4 takes the output of node1 and node2 as its inputs, applies a  $3\times 3$  operation on node1 and a  $5\times 5$  operation on node2, and sums them. The available operations for a  $search\ block\ (e.g.,\ operation\ space)$  include  $1\times 1$ ,  $3\times 3$ ,  $5\times 5$ ,  $7\times 7$  operations and a None operation.

The architecture of a  $K \times K$  operation is shown in **Fig.2.3.2c**, composing a convolution with kernel size K followed by batch normalization and a *trainable neuron layer*. On the other hand, the *None* operation passes the operation input to the operation output without applying any computation.

**Fig.2.3.2** The network architecture of our mutation NAS. (a) The top-level schematic: a block-based architecture composing a 3x3 convolution, three (search block  $\times$   $N_B$  — reduction layer) stacks, and a classification layer. (b) The schematic of a search block: composing 8 nodes with node0 and node1 as prior block inputs, node2 to node6 being pairwise combinations, and node7 concatenating all unused node outputs as the block output. Connections and operations in the search block are modified during the NAS search process, but the number of nodes stay identical. (c) The schematic of an Operation: a batch normalization, a trainable neuron layer, and a convolution with the corresponding kernel size. Note that a 1x1 Convolution is labelled as 1x1Conv while a 1x1 Operation is labelled as 1x1. The former refers to a single convolution with kernel size 1x1, while the latter also includes a batch normalization and a trainable neuron layer. (d) The trainable neuron layer contains three weighted paths, each corresponding to a neuron type: the conventional ReLU, the max, and the coincidence neurons. During training, the weights of the three paths are updated, and the path with the highest weight determines the neuron selected.

The *trainable neuron layer* (TL, **Fig.2.3.2d**) is a trainable layer that finds the optimal neuron type during training. It composes three weighted branches corresponding to the conventional ReLU neuron, the *max* neuron, and the *coincidence* neuron, respectively (e.g., the branch weights  $w_{TL} = [w_{ReLU}, w_{max}, w_{co}]$  and the branch outputs  $b_{TL}(x) = [ReLU(x), y_{max\_s}(x), y_{co\_s}(x)]$ ). A higher branch weight indicates that the corresponding neuron type has a higher probability of being the optimal neuron type. The output of the *trainable neuron layer*  $y_{TL}$  is the sum of each branch output scaled by the softmax of the branch weights, e.g.,

$$y_{TL}(x) = softmax(w_{TL}) \cdot b_{TL}(x) \dots Eq. 2.3.2$$

Where  $y_{TL}(x)$  is the output of the *trainable neuron layer*. The *softmax* of a vector is the exponential of each element in the vector divided by the sum of the exponential of all elements in the vector, e.g.,

$$softmax(z)_i = \frac{e^{z_i}}{\sum e^{z_j}} \qquad \dots Eq. 2.3.1$$

Every neuron in the *trainable neuron layer* is individually optimized. For a fully connected layer with  $N_F$  neurons, there are a total of  $3N_F$  weights (e.g. 3 weights corresponding to the three neuron types for every neuron). Likewise, for a convolution layer with  $N_F$  neurons (e.g., number of output channels or feature maps), there are  $3N_F$  weights.

The reduction layer reduces feature dimensions to create a more compact representation. Following the common practice [139], the reduction layer composes three components in series: (1) a 3x3 convolution with a stride (amount of shift during convolution) of 2 and a number of output channels equal to twice the amount of input channels, followed by (2) batch normalization and (3) a *trainable neuron layer*.

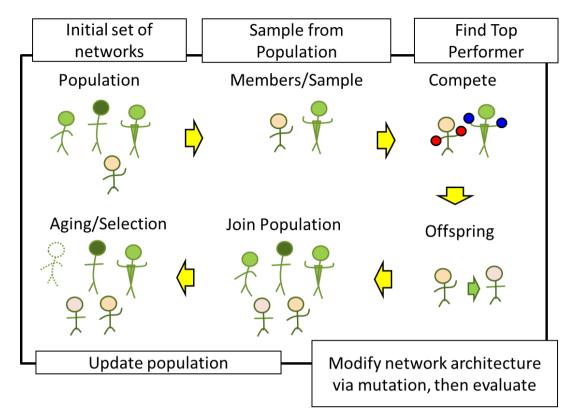

# Mutation NAS Search Method

The search method of the mutation NAS is inspired by the genetic mutation process in an evolutionary environment. Evolution can be roughly described as follows: there exists an initial population of organisms in an environment. When some organisms (e.g., a subset of the population) meet, they compete, and the best performing organisms generate offsprings that share features of their parenst. As time passes, old and poorly performing members of the population die off. As a result, many generations later, the population will be composed of members with the best suited features for the environment. An illustration of the evolution process is shown in **Fig.2.3.3**.

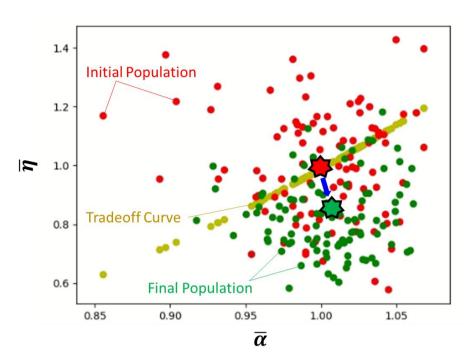

Our search algorithm mimics this process. We keep an active population P composed of n(P) architectures and their evaluation metrics  $\epsilon_i = f(\alpha_i, \eta_i); i \in [0, n(P)]$ , where  $\alpha_i$  is the

**Fig.2.3.3** Illustration of the evolutionary process and the mutation NAS search method. During the search process, a population of architectures are kept. In each search iteration, architectures are sampled from the population, and the top performing architecture is selected as the parent. The parent is used to generate a child architecture by mutating its architecture. Afterwards, the child architecture is evaluated and added to the population.

accuracy of architecture i,  $\eta_i$  is it's number of parameters, and  $\epsilon_i$  is its evaluation metric. During each search iteration, a sample S is first sampled from P. Within S, the architecture  $A^*$  with the highest evaluation metric is selected as the parent. A child A' is then generated by mutating  $A^*$ . The child is then evaluated and added to P. Finally, the oldest member (aging-evolution) or worst performing member (competition-evolution) of P is removed. The pseudocode for the search algorithm is shown in **Fig.2.3.4**.

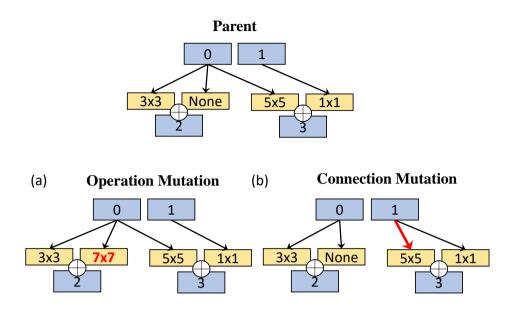

The mutation of an architecture is as follows: during each iteration,  $N_{B\_S}$  search blocks are selected to mutate. For each search block, an operation mutation is applied to  $N_{O\_S}$  nodes, and a connection mutation is applied to  $N_{C\_S}$  nodes. In an operation mutation, one of the node's operations is randomly reselected from the operation space, as illustrated in **Fig.2.3.5a**. In this example, we see that the *None* operation in *node2* is mutated to a  $7 \times 7$  operation. In a

# Algorithm1. Aging Mutation NAS

```

n<sub>iter</sub>: Number of search iterations

n(P):Population Size

n(S):Sample Size

history.arch \leftarrow []

history.perf \leftarrow []

while |history| < n(P) do

model.arch \leftarrow \mathbf{RandomModel}

model.perf \leftarrow TrainAndEval(model.arch)

append model, arch to history, arch

append model. perf to history. perf

end while

Fit tradeoff hyperparameter k on history.perf

while |history| < n_{iter} do

population \leftarrow history[-n(P):]

sample \leftarrow []

while |sample| < n(S) do

add RandomSample(population) to sample

parent \leftarrow model with highest perf in sample

child.arch \leftarrow Mutate(parents.arch)

child.perf \leftarrow TrainAndEval(child.arch)

append child. arch to history. arch

append child. perf to history. perf

end while

Return highest metric model in history

```

**Fig.2.3.4** Pseudo code of the mutation NAS algorithm. First, an initial population of architectures is generated via randomly sampling from the search space. Each architecture is evaluated, and a tradeoff parameter k is fitted on the accuracy  $\alpha$  and parameter count  $\eta$  of the initial population. Afterwards, in each search iteration, we randomly sample from the population and pick the top performing architecture as the parent. The parent architecture generates a child architecture via mutation, and the child is evaluated and added to the population. The oldest member of the population is then removed. When the maximum amount of search iterations  $n_{iter}$  is reached, the algorithm returns the architecture with the highest performance metric  $\epsilon$ .

connection mutation, one of the node's input connections is randomly reconnected to another node, as illustrated in **Fig.2.3.5b**. Here, we see that the left connection of *node3* is changed from *node0* to *node1*.

The parameters  $N_{B\_S}$ ,  $N_{C\_S}$ , and  $N_{O\_S}$  provide a tradeoff in exploration (e.g. trying out more diverse architectures in the search space with high  $N_{B\_S}$ ,  $N_{C\_S}$ , and  $N_{O\_S}$ ) vs. exploitation

**Fig.2.3.5** The mutation of an architecture. (a) The operation mutation that randomly changes one operation to another. For example, the *None operation* in *node2* is changed to a *7x7 operation*. (b) The connection mutation that randomly reconnects one input of the pairwise operation. For example, the left connection of *node3* is changed from *node0* to *node1*.

(conducting a more thorough evaluation of similar architectures in the adjacent search space with small  $N_{B,S}$ ,  $N_{C,S}$ , and  $N_{O,S}$ ).

#### Mutation NAS Evaluation Procedure

In general, the accuracy  $\alpha$  of a neural network grows with the number of parameters  $\eta$  in the network. If the evaluation metric  $\epsilon$  is based purely upon  $\alpha$ , a less efficient network with higher  $\eta$  may outperform a more efficient network with lower  $\eta$ . However, under the same resource constraints, an efficient structure will have a higher  $\alpha$ . Therefore, the network performance should be evaluated in terms of both accuracy and cost (e.g.  $\eta$ , flops, latency, energy, etc.). We adopt the evaluation metric  $\epsilon = \bar{\alpha}/\bar{\eta}^k$ , where  $\bar{\alpha} = \alpha_{model}/\alpha_{init}$  is the normalized accuracy of the model, computed as the model accuracy  $\alpha_{model}$  divided by the average accuracy of the initial population  $\alpha_{init}$ ;  $\bar{\eta} = \eta_{model}/\eta_{init}$  is the normalized number of parameters in the model, and k is a hyperparameter for controlling the tradeoff between  $\alpha$  and  $\eta$  obtained by fitting the relation  $k = -\log \bar{\alpha}/\log \bar{\eta}$  on the initial population.

### 2.3b Growth-based NAS Algorithm

**Fig.2.3.6** The network architecture of our growth-based NAS. (a) The top-level schematic: a block-based architecture composing a 3x3 convolution, three (search block  $\times$   $N_B$  — reduction layer) stacks, and a classification layer. (b) Schematic of a search block: paths are grown via branching and splitting procedures. For example, the original center path consists of only a 3  $\times$  3 operation. The right path is created by splitting the center path with a 5  $\times$  5 operation, then branching it with a 3  $\times$  3 and a a 1  $\times$  1 operation. (c) The growth procedure can be either a branch procedure or a split procedure. The branch procedure divides a path into two, applies an operation to each, and merges them back. The split procedure creates a second path with a different operation.

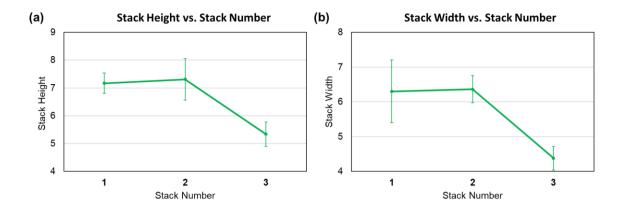

The growth NAS has a multi-branch search space [147], which is a generalized representation of modern feedforward CNN architectures [148] [149] [150]. The search method is similar to our NAS algorithm in **Sec.2.3a.** However, the procedure to generate a child architecture from a parent architecture from *mutation* process to a *growth* process.

## Growth NAS Search Space

Similar to the mutation NAS, the growth NAS also has a block-based structure (**Fig.2.3.6a**) composing an initial 3x3 convolution, followed by three repetitions of (*search block*  $\times N_B$  – reduction layer) stacks and a classification layer. Here, each *search block* (**Fig.2.3.6b**) is a multi-branch tree structure: neurons and paths in the block are formed via *branching* and *splitting* procedures. The *branch* procedure divides a path into two, applies an operation to each, and merges them back. The *split* procedure creates a duplicate path with a different operation. An example of a *search block* and an illustration of a *branch* and *split* procedures is shown in **Fig.2.3.6b**. In the example, the block begins from an initial  $3 \times 3$  operation between the input

### Algorithm2. Aging Growth NAS

```

n<sub>iter</sub> : Number of search iterations

n(P):Population Size

n(S):Sample Size

history.arch \leftarrow []

history.perf \leftarrow []

while |history| < n(P) do

model.arch \leftarrow InitialGrow(InitialModel)

model.perf \leftarrow TrainAndEval(model.arch)

append model, arch to history, arch

append model. perf to history. perf

end while

Fit tradeoff hyperparameter k on history, perf

while |history| < n_{iter} do

population \leftarrow history[-n(P):]

sample \leftarrow []

while |sample| < n(S) do

add RandomSample(population) to sample

end while

parent \leftarrow model with highest perf in sample

child.arch \leftarrow Grow(parents.arch)

child.perf \leftarrow TrainAndEval(child.arch)

append child. arch to history. arch

append child. perf to history. perf

end while

Return highest metric model in history

```

**Fig.2.3.7** Pseudocode of the growth NAS algorithm. We adopt the same evolutionary backbone as the mutation NAS, e.g., keeping a population of architectures, sampling from the population, finding the top performing parent architecture, modifying the parent architecture to create a child architecture, and updating population. The main difference of the two algorithms lies in the method to generate the child architecture. Here, the child architecture is obtained by growing the parent architecture rather than mutating it. The initial population is also generated accordingly, e.g., by randomly growing an initial network.

and output (center path). The right path is then created by (1) *spliting* the center path to create the right path with a  $5 \times 5$  operation, then (2) *branching* the right path into a  $3 \times 3$  operation and a  $1 \times 1$  operation.

Each operation has the same architecture as the mutation NAS in **Fig.2.3.2c** and **Fig.2.3.2d**, e.g., a convolution followed by batch normalization and a *trainable neuron layer*.

#### Growth NAS Search Method

The growth NAS is inspired by the growth of neural pathways: in the human brain, learning results in the creation and rearrangement of new neurons and neural connections. Upon the evolutionary backbone, we change the process to generate a child architecture from *mutation* to *growth*. From the parent architecture,  $N_{B\_S}$  search blocks are randomly selected, and  $N_{G\_S}$  random *growth* procedures, (e.g., random *branch* or *split* procedures) are applied to each block.

For the initial population, we begin with a single  $3 \times 3$  operation between the input and output of each *search block*. Each block then randomly *grows* (*branches* or *splits*) up to  $N_{G\_Init}$  times. The pseudocode of the growth NAS search algorithm is shown in **Fig.2.3.7**.

### Growth NAS Evaluation Procedure

The growth NAS optimizes for the same target as the mutation NAS, e.g., a tradeoff between the accuracy and the cost via the evaluation metric  $\epsilon = \bar{\alpha}/\bar{\eta}^k$ ,

## 2.3c Pruning NAS Algorithm

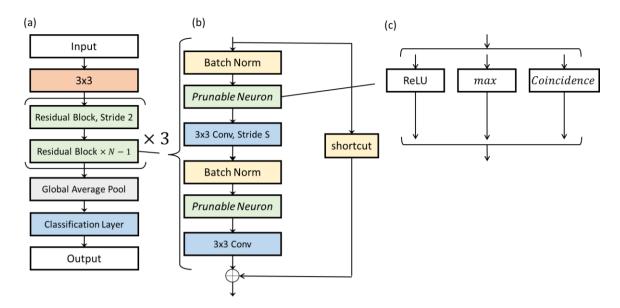

The pruning NAS begins with arguably the most widely benchmarked hand-crafted architecture: the ResNet [149]. ResNet introduced skip connections, enabling significantly deeper networks and marking a drastic improvement in deep learning performance across a large variety of tasks. We start with a ResNet that contains an equal amount of each neuron type, then consecutively remove low-importance neurons until we arrive at a high-accuracy, efficient network.

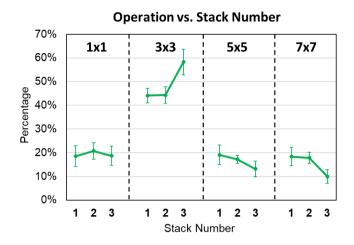

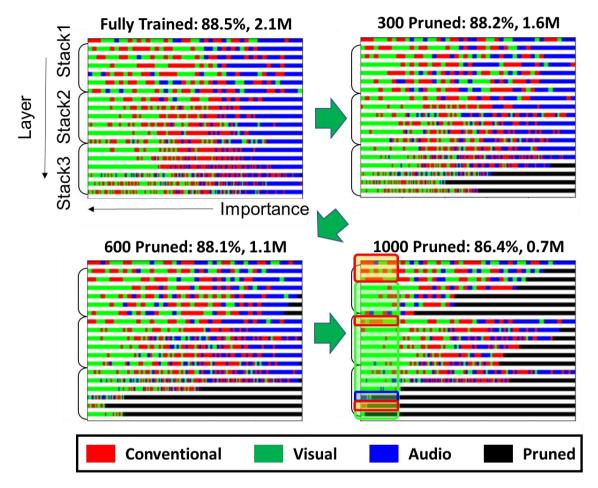

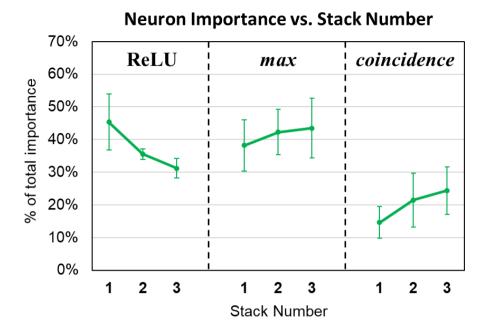

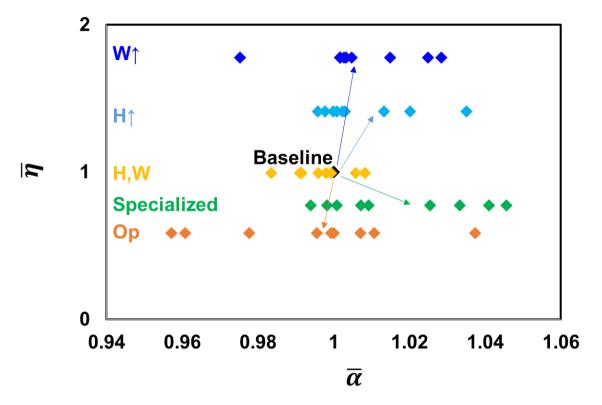

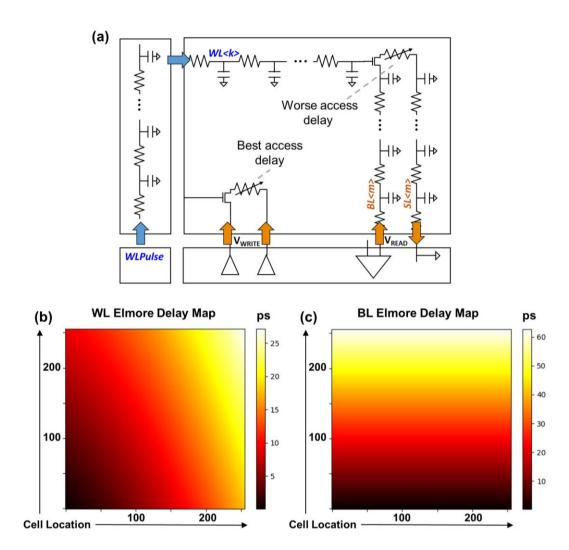

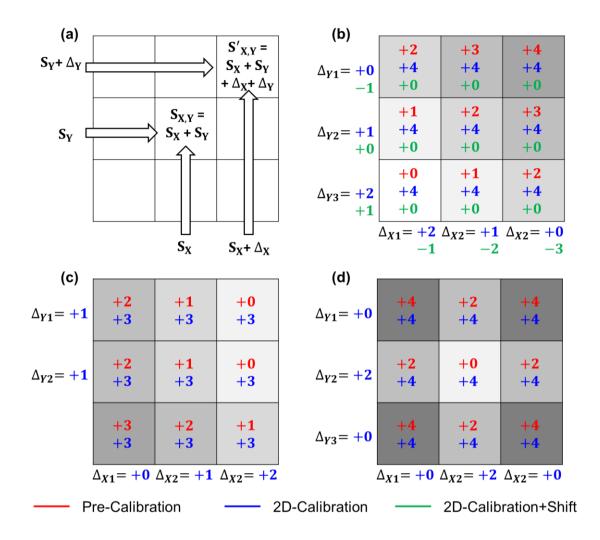

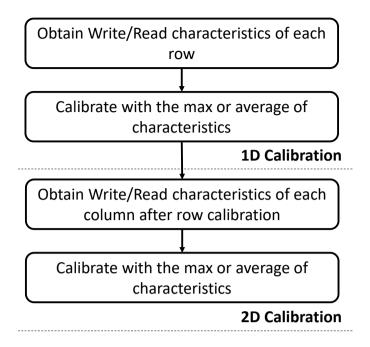

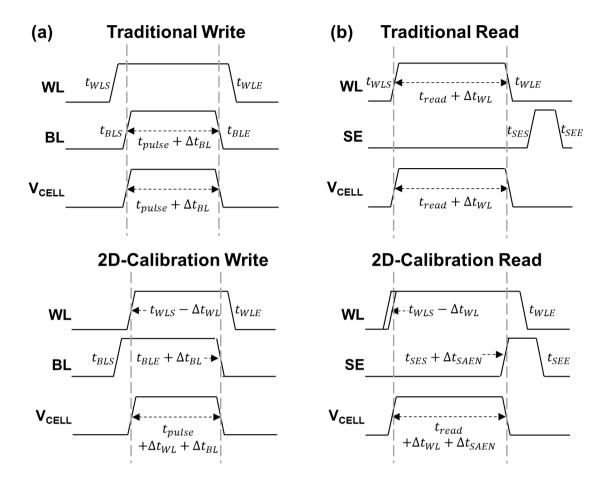

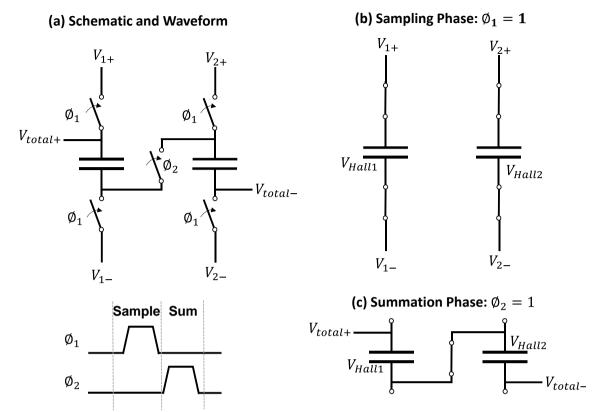

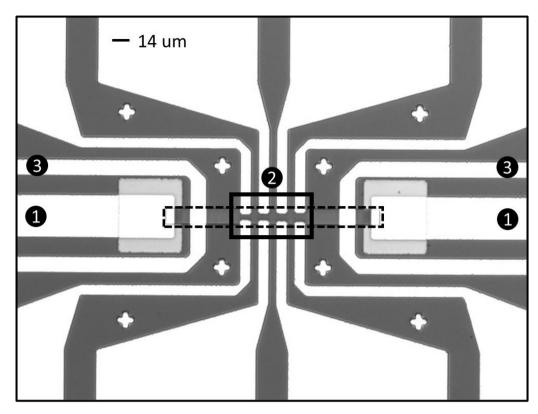

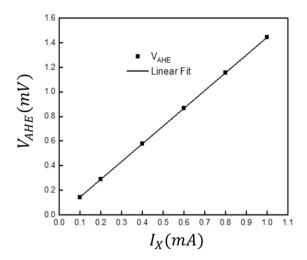

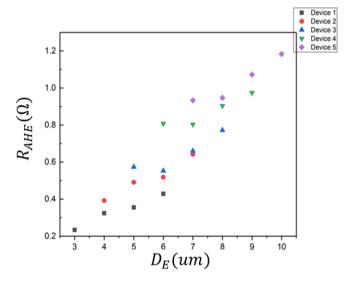

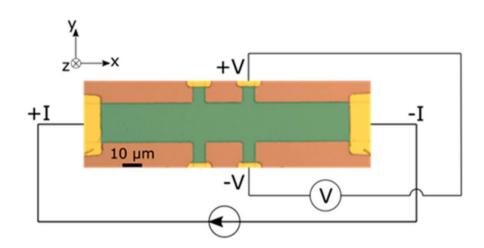

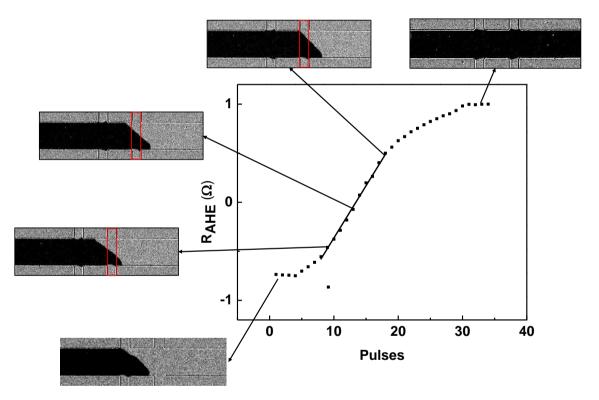

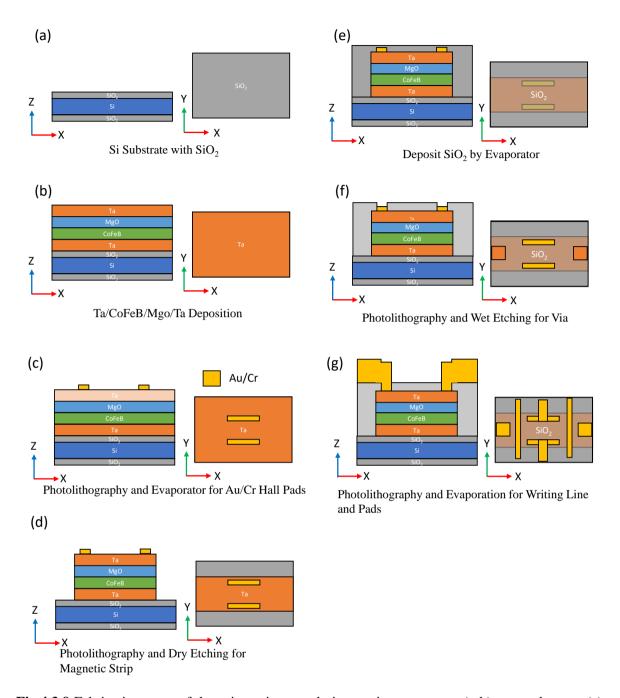

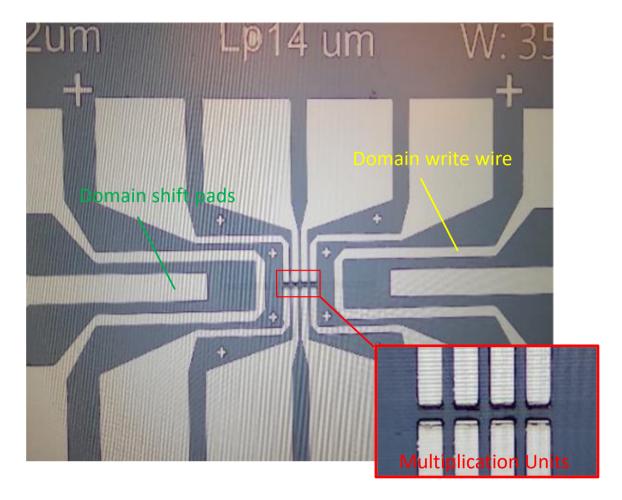

### Pruning NAS Search Space