## UC Santa Barbara

**UC Santa Barbara Previously Published Works**

### Title

Demonstration of CMOS-Compatible Multi-Level Graphene Interconnects With Metal Vias

### Permalink

https://escholarship.org/uc/item/2q1541zd

### Journal

IEEE Transactions on Electron Devices, 68(4)

### ISSN

0018-9383

### Authors

Agashiwala, Kunjesh Jiang, Junkai Parto, Kamyar <u>et al.</u>

### **Publication Date**

2021-04-01

### DOI

10.1109/ted.2021.3061637

Peer reviewed

# **Demonstration of CMOS-Compatible Multi-Level Graphene Interconnects With Metal Vias**

Kunjesh Agashiwala<sup>10</sup>, Graduate Student Member, IEEE, Junkai Jiang, Member, IEEE, Kamyar Parto<sup>®</sup>, Student Member, IEEE, Dujiao Zhang<sup>®</sup>, Student Member, IEEE, Chao-Hui Yeh<sup>®</sup>, *Member, IEEE*, and Kaustav Banerjee<sup>®</sup>, *Fellow, IEEE*

(a) 10<sup>4</sup>

Abstract—Doped-multilayer-graphene (DMLG) interconnects employing the subtractive-etching (SE) process have opened a new pathway for designing interconnects at advanced technology nodes, where conventional metal wires suffer from significant resistance increase, selfheating (SH), electromigration (EM), and various integration challenges. Even though single-level scaled graphene wires have been shown to possess better performance and reliability with respect to dual-damascene (DD) and SE-enabled metal wires, a multi-level graphene interconnect technology (with vias) has remained elusive, which is of paramount importance for its integration in future technology nodes. This work, for the first time, addresses that need by engineering a CMOS-compatible solid-phase growth technique to yield large-area multilayer graphene (MLG) on dielectric (SiO<sub>2</sub>) and metal (Cu) substrates and subsequently demonstrating multi-level MLG interconnects with metal vias. Using rigorous theoretical and experimental analyses, we demonstrate that multi-level MLG interconnects with metal vias undergo < 2% change in the via resistance under accelerated stress conditions, demonstrating its superior reliability against SH and EM, making them ideal candidates for sub-10 nm nodes.

Index Terms—CMOS-compatible, doped multilayer graphene (DMLG), dual-damascene (DD), electromigration (EM), graphene capping-layer, interconnects, multi-level, reliability, self-heating (SH), solid-phase diffusion, subtractive etching.

#### I. INTRODUCTION

♦ ONVENTIONAL metal interconnects suffer from significant size effects, as the critical wire dimension scales

Manuscript received November 18, 2020; revised January 7, 2021; accepted February 10, 2021. Date of current version March 24, 2021. This work was supported in part by the Army Research Office (ARO) under Grant W911NF1810366, in part by the Air Force Office Of Scientific Research (AFOSR) Defense University Research Instrumentation Program (DURIP) under Grant FA9550-18-1-0448, and in part by the University of California Multicampus Research Programs and Initiatives (UC MRPI) Research Program under Grant MRP-17-454999. This article is an extended version of a paper presented at IEDM 2020. The review of this article was arranged by Editor T. Grasser. (Kunjesh Agashiwala and Junkai Jiang contributed equally to this work.) (Corresponding author: Kaustav Baneriee.)

Kunjesh Agashiwala, Junkai Jiang, Kamyar Parto, Chao-Hui Yeh, and Kaustav Banerjee are with the Department of Electrical and Computer Engineering, University of California Santa Barbara, Santa Barbara, CA 93106 USA (e-mail: kunjesh@ucsb.edu; jjiang@ece.ucsb.edu; kamyar00@ucsb.edu; chyeh@ucsb.edu; kaustav@ece.ucsb.edu).

Dujiao Zhang is with the Department of Electrical and Computer Engineering, University of California Santa Barbara, Santa Barbara, CA 93106 USA, and also with the School of Electrical Engineering, Xi'an Jiaotong University, Xi'an 710049, China (e-mail: dujiao@ucsb.edu).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TED.2021.3061637.

Digital Object Identifier 10.1109/TED.2021.3061637

----- Solid Line: AR = 2 ---- Dashed Line: AR = Unit 10 Wire Resistance per Ul Length (Ω/μm) 0 ĝ a Resistance ( DMLG ٧ia Barrie — AR = 2<sup>B;</sup> -- AR = 10 Barrie 5 15 20 25 Wire Width (nm) 30 5 10 15 20 2 Via Width (nm) 30 10 25 (c) (d) Co Via (AR=2) Co Via (AR=10) (sd d DMLG Wire Delay ( Driver RC Delay 140 1  $r(C_{D1})$ +  $(0.5R_{Wire} + R_{Via})(C_{Wire} + 2C_{Load})$ - Wire Width = Via Width = 14 nm 0∔ 100 Wire Aspect Ratio = 2 @ 5 nm technology node 1000 Via Resistance (Ω) - Wire length = 10x MGP, 100x MGP

(b)

Fig. 1. (a) Resistance per unit length versus wire width for Cu, Co, and Ru wires by single damascene process, and Co and DMLG wires by SE, with AR of 1 and 2. The Cu, Co, and Ru wire resistance by damascene process is estimated from an empirical model [6]. Co wire resistance by SE is estimated from the model in [7], and DMLG wire resistance is calculated from an analytical model based on the Landauer approach [8] with consideration of DMLG bandgap opening (for sub-20 nm wire widths) and a doping level of  $|E_F| = 0.6$  eV. All the models are calibrated with measured data. (b) Via resistance versus via width for Ru and Co metals, with and without barrier layers and AR = 2 and 10, estimated from [6]. High AR (=10) contacts are used in dynamic random access memory (DRAM) cells. The side and bottom barrier thicknesses are fixed at 2 and 3 nm, respectively. For vias with barrier layers, the via resistance is the summation of the resistance of metal fill ( $R_{Metal}$ ) and barrier ( $R_{Barrier}$ ). (c) Schematic of a driver-interconnect-load circuit in HSPICE simulations, where the driver is a unit-sized inverter and load is 4× (FO4) the size of the driver (at 5 nm technology node). The interconnect is modeled by via resistors (R<sub>Via</sub>) and a distributed RC network for wires (using the RC delay equation shown). (d) FO4 delay [from (c)] versus via resistance for Co wires and DMLG wires of length  $100 \times$  and  $10 \times$  minimum gate pitch (MGP). The vertical green regions in (d) indicate the Co via resistances corresponding to AR = 2 and AR = 10, respectively. Moreover, in all these calculations, the quantum capacitance and quantum contact resistance corresponding to DMLG wires have already been incorporated in the analytical model developed in [8].

down to sub-20 nm. The nonlinear increase in resistivity, and subsequent wire and *via* resistance [Fig. 1(a) and (b)] increases self-heating (SH), degrades electromigration (EM) reliability, and thereby limits interconnect current carrying capacity and performance [Fig. 1(c) and (d)] [1]–[5]. Additionally, void formation during metal fill in highly scaled trenches and via holes during the dual-damascene (DD) process [Fig. 2(a)] exacerbates the reliability and variability problems [9]-[11].

This work is licensed under a Creative Commons Attribution 4.0 License. For more information, see https://creativecommons.org/licenses/by/4.0/

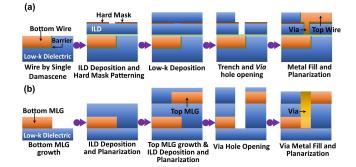

Fig. 2. Schematic of process steps of (a) DD process for conventional metal wires and (b) proposed SE *via* scheme using MLG wires and metal *vias*.

Owing to its excellent electrical [12], [13], optical [14], [15], and thermo-electric [16], [17] properties, graphene [or more specifically doped multilayer graphene (DMLG)] was first proposed by Xu et al. [18] as a promising solution to various interconnect scaling challenges, and was theoretically shown to beat the resistivity and performance of sub-20 nm Cu by appropriate level of doping (by intercalation) [8]. Thereafter, DMLG interconnects were experimentally demonstrated to overcome the fundamental current-carrying-capacity limit of nanoscale metal interconnects, improving reliability by >100fold [19], performance by > 4-fold [20], and energy-efficiency by >70% [19]. Furthermore, CMOS-compatible DMLG wires, employing low-temperature solid-phase graphene growth and SE process [20], have been demonstrated to exhibit comparable/higher electrical conductivity with respect to metal interconnects fabricated by DD process [19], negligible EM effect, and long-term doping stability.

It is worth noting that SE of metal wires (e.g., Ru [21]) leads to a marginal improvement ( $\sim 30\%$ ) in electrical conductivity as compared with those fabricated using the DD process due to larger metal grain sizes resulting from a better and more efficient metal fill process. In addition, it simplifies the backend-of-line (BEOL) fabrication by eliminating low-k dielectric etching, which can potentially increase the dielectric constant because of plasma damage, and thereby affect the circuit performance [21], [22]. Even though reliability/performance of horizontal wires by SE process for both metals [21], [7] and DMLG [19], [20] are well studied, realization and characterization of a multi-tier graphene interconnect system by SE incorporating robust and low resistance vias/contacts have remained elusive. Vias are crucial elements for signal propagation between various metallization levels, which also suffer from significant EM at advanced technology nodes [23], as also shown in detail in Section II-B. Jiang et al. [24] reported carbon nanotube (CNT) vias integrated with horizontal multi-tier multilayer graphene (MLG) wires by SE process with extremely high EM resistance in CNT vias, MLG wires, and their contacts. However, CNT vias require very high growth temperatures (>600 °C), which is not BEOL-compatible. In this work, for the first time, we demonstrate a BEOL-compatible via/contact scheme for a two-tier SE-enabled MLG wire system [Fig. 2(b)], and present a comprehensive performance and reliability study, including SH and EM analysis. The major contributions of this work include: 1) demonstration of large-area and uni-

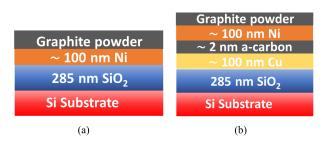

Fig. 3. (a) Schematic of the initial stack used for growing MLG at 350  $^{\circ}$ C directly onto SiO<sub>2</sub> using the CMOS-compatible solid-phase growth technique [19]. (b) Schematic of the initial stack used for growing MLG directly on Cu substrates, as demonstrated in [25].

form CMOS-compatible multi-level MLG growth on arbitrary surface topologies and substrates; 2) demonstration of an SE-enabled multi-level MLG/*via* scheme that is compatible with BEOL process and exhibits < 2% *via*-resistance change under 200 MA/cm<sup>2</sup> current stress; and 3) scalability analysis of the proposed multi-level MLG interconnect scheme to evaluate its benefits at ultimate scaled dimensions. In this article, we present a much more rigorous evaluation of our recent work [25], by providing more evidence and reasoning behind the nature of our results.

This paper is organized as follows: Section II describes the design guidelines necessary for realizing CMOS-compatible multi-level MLG interconnects. Detailed theoretical and experimental evidences are used to arrive at an optimal wirevia system for MLG-based BEOL technology. Section III discusses the fabrication process flow necessary for realizing a multi-level MLG wire-metal via system. Electrical and reliability characterization results are also shown in Section III. Section IV describes the scalability analysis of the proposed via scheme for advanced technology nodes. Finally, conclusions are drawn in Section V.

#### II. DESIGN GUIDELINES FOR CMOS-COMPATIBLE MULTITIER MLG INTERCONNECT

The use of alternative metals such as Co [7], Ru [21] (as compared with conventional Cu) at advanced technology nodes eliminates the need for the metal diffusion barriers resulting in a larger metal wire cross-section. This reduces the severity of the resistivity size effect for these metals at critical dimensions, leading to an improved electrical conductivity and circuit performance as compared with the DD process [Fig. 1(a)]. Moreover, DMLG offers much higher conductivity benefits at smaller aspect ratios (ARs) [Fig. 1(a)] as compared to these barrierless metals due to reduced surface and grain boundary scatterings, in addition to being barrier-free itself. It is instructive to note that even though the elimination of conventional TaN/TiN barrier and capping layer by using a single-layer-graphene (SLG) barrier reduces the effective resistivity of Cu [26], the fundamental reliability problem in nanoscale Cu wires arising from EM and SH remains unsolved [19].

Like other SE metals, for graphene wires to be directly integrated into the CMOS process, it is important to reliably grow large-area, uniform, and good-quality MLG at multiple levels for them to be eventually etched and connected (for multi-level schemes) into practical interconnect structures. This work first addresses this issue by engineering the solid-phase graphene growth technique [20] to yield wafer size, uniform, and high-quality MLG on dielectric (SiO<sub>2</sub>) [Fig. 3(a)] as well as metallic (Cu) substrates [Fig. 3(b)]. In this section, we describe the necessary groundwork needed for realizing the SE-enabled multilevel graphene technology.

#### A. DD Versus Proposed Subtractive Etching (SE) Based Interconnect Scheme

Our recent work on CMOS-compatible single-level DMLG wires [20] establishes its performance and reliability benefits against the state-of-the-art metal interconnects. Furthermore, for advancing this technology toward practical BEOL process integration, a multi-level interconnect scheme (supported by SE-metal via) is proposed in Fig. 2(b). In this scheme, the via is fabricated by a single damascene-like metal fill process on the via hole through top-MLG, interlayer dielectric (ILD), and bottom-MLG. This might not only reduce the overall processing time (DD versus single damascene-like process), but also result in significant current crowding and EM alleviation, as proved both theoretically (Section II-B) and experimentally (Section III-C), later. The lower resistivity of DMLG wires (as compared to metal wires) [19], [20] coupled with the use of barrierless SE metals (such as Co, Ru, W) for the vias promises much better performance (at advanced technology nodes) as compared to the conventional DD process, as also verified in Section IV. An important consequence of using a lowdimensional material like MLG as an interconnect material is the addition of a contact resistance between the MLG and metal. Among the two possible contact geometries to MLG (top contact and edge contact) [27], [28], the former one offers higher contact resistance due to the presence of a van der Waals (vdW) gap. Taking advantage of this fact, the authors uniquely design the proposed via scheme in a way that allows edge contacts to MLG, which are obviously preferred over top contacts [28] to achieve lower contact resistance [Fig. 2(b)]. As a matter of fact, this subtractive etching process was first used by the industry for fabricating Al interconnects with W plug, before transitioning to copperbased wires employing the damascene process [29]. The SE process first involves forming a multi-level stack of the wires with some overlap region separated by an ILD. Since the overlap region is used for connecting the two wires, it becomes important to modulate its dimensions to avoid any lithographyinduced opens or shorts. The via is subsequently formed in a single damascene-like metal fill process by etching through the top wire, the ILD, and the bottom wire. While forming the two-level interconnection, the following issues are the key sources of errors/risks:

1) Wire/Via Misalignment: It is obviously important to make sure that there is minimal misalignment between the wires and vias at multiple levels as it can be a significant cause of SH and current crowding, which are the major reliability degradation factors. This effect can be even more pronounced for aggressively scaled (sub-100 nm) wires and high AR vias in the proposed SE via scheme, where the anisotropic etching and lithography induced opens or shorts can significantly reduce the overall yield of the process.

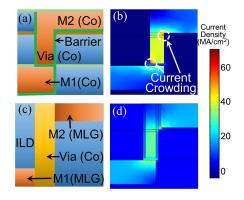

Fig. 4. Layouts and current density profiles for single side M1-*via*-M2 cross section made using: (a) and (b) DD process, and (c) and (d) proposed subtractive etching (SE) (MLG with Co *via*) process. Width of M1/M2/*via* is 12 nm and AR of M1/M2/*via* is 2. A constant current (from ITRS data set) is assumed in these simulations. These finite element electromagnetic simulations have been conducted assuming an empirical conductivity model for MLG (as developed in [8] and validated by experiments in [19]).

2) Lithography Related Challenges: As shown in Section III-A, we have used a photoresist as the mask for performing the vertical etching, which is not the best suited approach as we shrink down the wire dimensions. For sub-100 nm wire/via dimensions, a metal mask would serve as a more accurate and robust method due to high alignment accuracy and better tolerance to the etching agents used in this step. These optimizations are crucial to realize high AR vias and multi-level interconnections using the proposed via scheme.

It is also worth noting that DMLG offers higher electrical conductivity and EM resistance compared with SE Co and Ru [20], especially at smaller ARs [AR = 1, Fig. 1(a)]. Hence, even-though the addition of the edge-contact resistance between MLG and metal *via* increases the overall *via* resistance, the fan-out of four (FO4) delay remains invariant with respect to the total *via* resistance [Fig. 1(c) and (d)]. This is primarily because the FO4 delays show weak dependence on the *via* resistance in the small *via* resistance regime (AR = 2 to 10), where the *via* resistance. This highlights the negligible side effects of this technology on the eventual circuit performance.

#### B. Alleviation of SH and EM in the Proposed Via Scheme

To evaluate the SH and current crowding alleviation of the proposed SE *via* scheme, steady-state solutions were conducted for a M1-*via*-M2 system, as shown in Fig. 4. Our analyses reveal that the MLG-*via*-MLG system suffers from almost no current crowding effects as compared with conventional DD process (using Co). This is mainly due to the current redistribution at the M1/M2-*via* interface due to the edge contact resistance between MLG and metal *via*. Similar behavior is also expected for the proposed *via* scheme (with metal wires and metal *vias*) due to the presence of highly resistive barriers.

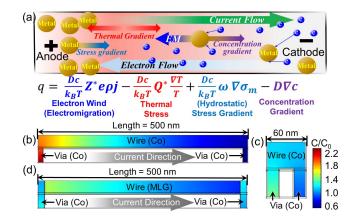

To validate the reliability of the proposed *via* scheme against SH and EM, which are major causes of wire and *via* degradation at highly scaled dimensions, a comprehensive finite element method (FEM) model capturing an interplay of the four major complex processes affecting EM and SH is

(a) Illustration of EM and an interplay of various complex Fig. 5. processes in a metal wire, where electrons under the presence of high electric stress gain enough momentum to knock out metal atoms out of their lattice sites (EM). Here, q, D,  $Z^*$ ,  $\rho$ , j,  $Q^*$ ,  $\omega$ ,  $\sigma_m$ ,  $k_B$ , and T are the total atomic flux, the effective atom diffusivity, effective charge, resistivity, current density, heat of transport, atomic volume, average hydrostatic stress, Boltzmann's constant, and temperature, respectively. (b) DD process with Co wires and Co-vias. (c) Normalized metal atomic concentration  $(C/C_0)$  in wire and vias for (b), and (d) proposed SE MLG + Co-via scheme under a constant dc current stress (same current direction for all, as shown in figure). Negligible EM is observed in the vias for the proposed scheme (d), as shown by the minor change in atomic concentration. The long wire in (d) shows some EM, primarily due to the inability of the simulator to capture the intrinsic physics of graphene under accelerated stress conditions.

developed [Fig. 5(a)]. This model solves the time-dependent continuity equation mentioned below to obtain the time evolution of the concentration gradient throughout the *via*-wire-*via* system under a constant dc stress, as shown in Fig. 5(b)–(d)

$$\nabla . \vec{q} + \frac{\partial c}{\partial t} = 0.$$

In the above equation, c is the normalized atomic concentration, given by  $c = C/C_0$ , where C is the actual atomic concentration at time  $t (= 10^6 \text{ s in these calculations}), C_0$ is the initial atomic concentration at t = 0, and  $\vec{q}$  is the total normalized atomic flux capturing the four major effects mentioned in Fig. 5(a). The constant dc stress used in these simulations is estimated from the International Technology Roadmap for Semiconductors (ITRS) corresponding to the wire/via dimensions. As seen in Fig. 5(b), the DD wire-via system suffers from significant EM, as evident by the huge change in the concentration gradient throughout the wire and the *vias*. As a sanity check to establish the validity of the simulations, Fig. 5(c) shows the normalized concentration gradient for a DD wire-via system with a wire length L less than the blech length ( $L_{\rm B}$ ) for Co (~100 nm for the chosen current density). Negligible EM is observed in the wire-via system as seen by the minor change in the atomic concentration, validating the well-known experimental claims [30]. Moreover, in the proposed via scheme [Fig. 5(d)], even though the *vias* suffer from negligible EM, some minor change in atomic concentration is observed for the MLG wires. This is slightly contradictory to the experimental demonstrations [19], [20], [31] (where MLG wires were shown to exhibit almost zero EM) and mainly arises due to the inability of the electromagnetic simulator to capture the true physics of low-dimensional materials like MLG under these elevated stress conditions. In conclusion, the absence of EM in DMLG wires [19], [20], [31] coupled with the immunity of the metal *vias* fabricated using the proposed scheme to EM [Fig. 5(d)] proves the robust nature of the proposed *via* scheme against major interconnect degradation mechanisms.

#### C. Large Area/Uniform and High-Quality Multi-Level MLG

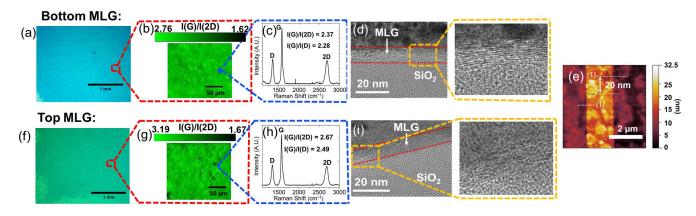

The first step toward realizing a multi-level graphene technology is its reliable growth at multiple levels in a CMOS-compatible manner. Thus, a two-tier MLG system with 200 nm SiO<sub>2</sub> as the ILD is fabricated using the initial material stack shown in Fig. 3(a) and by employing the lowtemperature (~350 °C) solid-phase MLG growth reported in [20]. Before the growth at each level, the samples are annealed at  $\sim 400$  °C for 2 h in an H<sub>2</sub>/Ar environment. Annealing improves the overall microstructure of the metal catalyst (Ni), by increasing the size of the grains from  $\sim$ 100 nm (before annealing) to  $\sim$ 5  $\mu$ m (after annealing). Since the diffusion coefficient (and hence, the carbon flux) through the bulk is about 0.5 times than that of through the grain boundaries [20], a larger grain size essentially translates to a more uniform MLG growth. However, this reduces the thickness of the MLG (for the same growth time as reported earlier [20]). To compensate for that, we have doubled the overall growth time (~60 min) and slightly increased the growth temperature ( $\sim$ 350 °C) while keeping the same pressure  $(\sim 65 \text{ psi})$  to result in similar thickness as compared with our previous work [20]. Fig. 6(a) shows the optical image after the fabrication of the bottom MLG on a 285 nm SiO<sub>2</sub>/Si substrate. A large-area Raman map in Fig. 6(b) and the sharp G and 2D peaks in the single point Raman spectrum in Fig. 6(c) confirm the uniform high-quality growth. High-angle annular darkfield scanning transmission electron microscopy (HAADF-STEM) image in Fig. 6(d) clearly shows the layered structure of graphene, once again confirming the high growth quality. Atomic force microscopy [Fig. 6(e)] confirms a thickness of  $\sim$ 20 nm for the bottom MLG. The main incentive for optimizing the growth for a thickness of  $\sim$ 15–20 nm is because it has been shown (via simulations) to minimize the FO4 delay for DMLG wires for sub-20 nm wire widths (AR  $\sim$  1) [19]. The top MLG [optical image, Fig. 6(f)] is fabricated over the ILD under the same conditions and exhibits almost comparable quality and thickness with respect to the bottom MLG, as evidenced from the single point Raman spectra [Fig. 6(g)] and the uniform large area Raman map [Fig. 6(h)]. Fig. 6(i) shows the HAADF-STEM image of the top MLG, once again validating the layered structure of graphene. The unevenness in the TEM image of the top MLG [Fig. 6(i), yellow box] is mainly due to the uneven SiO2 ILD surface grown by plasmaenhanced chemical vapor deposition (PECVD) process. This unevenness can be attributed to the relatively low substrate temperature ( $\sim 300$  °C) for the PECVD process [32], which can be eliminated by using chemical mechanical polishing (CMP) to planarize the ILD. The successful growth of highquality MLG on both levels also confirms the applicability of the growth technique on arbitrary surface morphologies.

Fig. 6. (a) Optical image of a large-area MLG (bottom level) grown using the solid-phase growth technique. (b) Raman map [corresponding to the highlighted region in (a)] of the *I*(G)/*I*(2D) ratio of the bottom MLG. (c) Shows the single point Raman spectra in (b). A large area *I*(G)/*I*(2D) ratio of  $\sim$ 2.4 indicates the uniform large area coverage of MLG using the optimized growth process. (d) HAADF-STEM of the bottom MLG in (a). The red lines indicate the approximate region of the MLG. The zoomed-in region in the yellow dashed rectangle clearly shows the layered structure of the MLG. (e) AFM profile of the bottom MLG etched into  $\sim$ 1- $\mu$ m wide wires, indicating 20 nm thickness. Similar thickness is observed for the top MLG as well. (f) Large-area optical image of the top MLG. (g) Raman map of *I*(G)/*I*(2D) ratio and (h) single point Raman spectrum of the top-level MLG in (f) indicates its large-area uniformity. The HAADF-STEM image in (i) shows a zoomed-in view of the top MLG on an uneven SiO<sub>2</sub> surface; the zoomed-in region shows the layered structure of MLG.

X-ray photoelectron spectroscopy (XPS) analyses of the grown MLG reveal that the exact peak position (1202.3 eV) and atomic composition (~83%) corresponding to the C = C sp2 bond can also be observed in the conventional CVD grown MLG [25], once again validating the high-quality growth of the solid-phase MLG.

#### D. Identification of Optimal Via Metal

The next step after forming a two-level MLG stack is to identify the optimal via metal to be used for forming a two-level interconnection. The total resistance of the via consists of two components, the resistance of the via metal due to its physical dimensions and the contact resistance between the graphene-via metal interface. Since the contact resistance forms a major component of the overall via resistance at advanced technology nodes, it becomes critical to identify the MLG edge-metal combination that offers the lowest contact resistance to minimize the overall *via* resistance and, hence, the eventual circuit performance. To this end, we employ an *ab initio* density functional theory (DFT) coupled with Non-equilibrium Green's Function (NEGF) transport framework to assess the electrical properties of MLG-metal edge following the methodology described in [33]. Fig. 7(a) shows the interface geometry of the simulated supercell. DFT calculations were performed utilizing generalized gradient approximation (GGA) functional [34] and Pseudo Dojo Pseudopotentials using 7  $\times$  5  $\times$ 200, 150 Rydberg, 0.05 eV/Å of k-point sampling, energy mesh cutoff, and maximum force for geometry optimization, respectively. To include the out-of-plane interactions, DFT-D2 corrections [35] have been incorporated. Top three SE based barrierless via metals (Co, Ru, W) [6], [36] form the prospective choice for the via metal as they minimize the resistance at sub-10 nm nodes. Contact resistance of any interface essentially translates to determining the available states with matching energy and k-vectors on both sides of the interface,

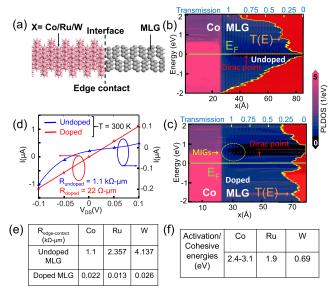

Fig. 7. (a) Atomic supercell of metal X (X = Co, Ru, W) and MLG interface. (b) Band-alignment (projected local DOS) and transmission spectrum, T(E), of undoped MLG. In undoped MLG (X = Co), Fermilevel lies at the Dirac point and transmission will be intrinsically limited by the low DOS around Dirac point. This will lead to nonlinearity in the I-V response, and result in an aggravated contact resistance. (c) Band-alignment (projected local DOS) and transmission spectrum of DMLG and Co metal. A practical doping level of -0.6 eV has been assumed in these calculations. Graphene's Fermi-level will move down and away from Dirac point to energies with higher DOS as doping increase; this will result in increase of transmission coefficient for graphene and a perfect linear I-V response and thus low contact resistance. (d) I-V response of doped graphene and undoped MLG (X = Co). (e) Table summarizing the edge-contact resistances between various SE metal candidates with doped and undoped MLG. (f) Table showing the experimentally obtained EM activation energies of the via metals [6], [36].

followed by their transmission (coupling) probability to each other. In this study, we consider the case of both undoped MLG and FeCl<sub>3</sub> doped MLG. For the case of undoped MLG, the Fermi-level lies on the Dirac point where the density of states (DOS) surrounding Fermi-level is negligible [Fig. 7(b)].

This low DOS around Fermi-level suppresses the available transmission modes, increasing the edge contact resistance between the MLG-metal interface [Fig. 7(d) and (e)]. For DMLG (p-type doping of 6.85  $\times$  10<sup>13</sup> cm<sup>-2</sup>), Fermi-level moves down and settles in a high DOS region of the Dirac cone [Fig. 7(c)]. Consequently, upon formation of the metal contact, higher DOS are available for conduction around Fermilevel which significantly reduces the edge-contact resistance, as evident in the increase of the transmission spectrum around the Fermi-level [Fig. 7(d) and (e)]. It is interesting to note that DMLG possess almost identical edge-contact resistance to the prospective metal candidates (Co, Ru, W), as shown in Fig. 7(e). The small variations in the contact resistance can be attributed to the variations in the DOS of the 3-D metal at the Fermi-level energy. While Ru performs best among the simulated metals, however, the higher activation energy and lower resistivity of Co as compared with Ru and W [6], [36] implies its higher tolerance to EM and SH [Fig. 7(f)], making it the better choice as the via metal for a multi-level MLG wire system.

#### *E.* Extension of CMOS-Compatible Graphene Growth Onto Metallic Substrates

The simplicity of the solid-phase CMOS-compatible graphene growth technique helps in easily extending it onto arbitrary substrates if the growth temperature does not result in thermal degradation of the substrate. Depending upon the relative diffusion coefficients of the substrate material and the metal catalyst (Ni) upon thermal annealing, a sacrificial separation layer might need to be inserted between them. In the previous demonstrations of the growth of MLG on SiO<sub>2</sub> substrates, no sacrificial layer is required as carbon has very little solubility in  $SiO_2$  [20]. Due to the potential use of MLG as a capping layer for conventional Cu interconnects [37], we demonstrate high-quality MLG growth directly on Cu without the need for any transfer process [25]. As both Ni and Cu have finite solubilities at  $\sim$ 350 °C, a  $\sim$ 2 nm amorphous carbon layer [25] is inserted between them [Fig. 3(b)]. The amorphous carbon prevents Cu and Ni layers from interdiffusion and aids the graphene growth process by acting as an additional source of readily available carbon at the Cu interface. Excellent optical and material characterizations of the MLG grown on Cu [25] demonstrate the outstanding reliability of the growth technique on metallic substrates.

#### III. FABRICATION AND CHARACTERIZATION OF MULTI-LEVEL MLG-INTERCONNECT

In this section, we demonstrate a two-level SE-MLG interconnect structure using Co *via* where the *via* hole is etched through the wires and ILD using a single damascene-like process. This is followed by its electrical characterization from where the edge contact resistance is extracted and compared with the numbers obtained theoretically. High current stress tests are performed to establish the reliability of the multilevel MLG wire-*via* system. Similar growth parameters as mentioned in the previous section result in 20 nm thick MLG for both levels. Although unintentional, the use of FeCl<sub>3</sub>

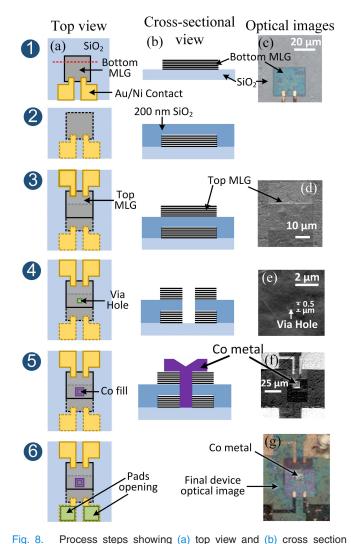

Fig. 8. Process steps showing (a) top view and (b) cross section view [along the red line in (a)]. Steps 1–6 are (1) bottom MLG synthesis by solid phase growth, patterning and contact pads fabrication, (2) SiO<sub>2</sub> ILD deposition by PECVD, (3) top MLG synthesis by solid phase growth, patterning and contact pads fabrication, (4) *via* hole opening by oxygen and CHF<sub>3</sub> ICP etching, (5) 220 nm thick Co deposition by thermal evaporation (rate < 5 Å/s), and (6) bottom pads opening by etching the SiO<sub>2</sub> ILD. (c) and (g) Optical images, and (d)–(f) SEM images are presented to confirm the key process steps.

solution for removing Ni catalyst ends up surface-doping the system, as evidenced from the presence of Fe at both the top and bottom MLG surfaces [25], which can lower the MLG resistivity. Significant performance improvement can be obtained by using intercalated DMLG wires [19], [20], as analyzed later.

#### A. Fabrication Process Flow

The major fabrication steps are summarized in the process flow described in Fig. 8. First, starting from a standard 285 nm SiO<sub>2</sub>/Si substrate, 20 nm bottom-MLG is grown and characterized, as shown in Fig. 6(a)–(e). This is followed by patterning the bottom MLG onto 25  $\mu$ m squares using a 50 nm Ni metal hard mask, followed by oxygen inductively coupled plasma (ICP) etching. The hard mask is removed by FeCl<sub>3</sub> wet etching. 15 nm Ni/150 nm Au contacts and pads are patterned

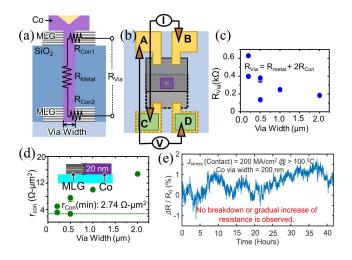

Fig. 9. (a) Cross-sectional view of a Co *via* connecting two tiers of MLG in Fig. 8, and the corresponding resistance network. The Co *via* resistance consists of edge contact resistance to top MLG ( $R_{Con1}$ ), Co metal resistance ( $R_{Metal}$ ) and edge contact resistance to bottom MLG ( $R_{Con2}$ ).  $R_{Con1}$  (or  $R_{Con2}$ ) can be estimated by subtracting  $R_{Metal}$  from the measured  $R_{via}$ , as shown in (c). (b) Schematic showing four-probe measurement scheme of the *via* resistance ( $R_{Via}$ ). (c) Measured total *via* resistance ( $R_{Via}$ ) versus *via* width. (d) Extracted specific contact resistivity ( $r_{Con}$ ) ( $\Omega$ - $\mu$ m<sup>2</sup>) versus *via* width, normalized with respect to the *via* width and thickness. (e) Measured *via* resistance change during current stress test, where 200 MA/cm<sup>2</sup> stress current is applied on edge contacts for >40 h. No breakdown or gradual resistance increase is observed, indicating no EM in Co *via* and Co-MLG contacts.

to electrically probe the bottom MLG. This is followed by depositing 200 nm thick SiO<sub>2</sub> ILD using PECVD process. Similar to the bottom MLG, the top MLG is grown and patterned using a Ni metal mask and oxygen ICP etching, while maintaining an overlapping region with the bottom MLG (step 3 in Fig. 8). This is followed by patterning of contacts and pads for the top MLG. In the overlapping region, a square *via* hole (widths ranging from 2  $\mu$ m to 200 nm) is opened by a three step oxygen-, CHF<sub>3</sub>-, and oxygen-ICP process to etch the top-MLG, ILD, and bottom-MLG, respectively, using a bilayer photoresist mask [Fig. 8(e)]. To ensure the via fill is successful at sub-1  $\mu$ m wire widths while simultaneously avoiding any alignment challenges, a 5  $\mu$ m  $\times$  5  $\mu$ m window was patterned enclosing the via hole (Step 5, Fig. 8). A  $\sim$ 240 nm thick Co is subsequently deposited by thermal evaporation (<100 °C) to fill the *via* hole [Fig. 8(f)] at slow deposition rate to ensure full metal fill. Finally, ILD on top of bottom pads is etched to access the bottom MLG pads. An important consequence of filling the *via* metal in a 5  $\mu$ m window around the via hole is the formation of both edge and top contacts to the top MLG, as shown in Fig. 9(a). This, however, does not deviate significantly from the ideal situation of pure edge contacts to both top and bottom MLG, as explained in the next section.

In these experiments, the wire/via width dimensions used are only for demonstration purposes and no way represent the state-of-the-art process technology. The primary bottlenecks in accessing smaller via/wire widths are: 1) ensuring complete vertical etch and metal fill at sub-100 nm dimensions and 2) minimizing the misalignment of the top and bottom MLG layers at sub-100 nm wire widths.

#### *B. Electrical Measurement and Contact Resistance Extraction*

Since the growth conditions and optical characterizations (Raman maps, STEM) for both the bottom and top MLG are almost identical, it can be safely assumed that they would possess similar I-V characteristics. With that said, the only unique measurable electrical component of this electrical system is the via resistance (and, hence, the edge contact resistance between MLG and Co). It is important to note that before taking any electrical measurements, the contact/pads were current annealed, which has shown to significantly enhance the current injection efficiency of the contact pads [24]. The via resistance  $(R_{Via})$  can be measured by applying current between top pad B and bottom pad C and measuring the voltage between top pad A and bottom pad D [Fig. 9(b)], like the van der Pauw method. The measured via resistance [Fig. 9(c)] consists of only the Co metal resistance ( $R_{\text{Metal}}$ ) and top and bottom Co-MLG contact resistances ( $R_{Con1}$  and  $R_{\text{Con2}}$ ). The top and bottom MLG wire resistances can be neglected because of symmetry in the measurement. Assuming a bulk resistivity for Co (the via dimensions are large enough for the resistivity to be close to its bulk value), the via metal resistance can then be easily estimated using  $R_M = \rho L/A$ , where  $\rho$  is the resistivity of the *via* metal (corresponding to a dimension of 0.2-2  $\mu$ m, which are the via widths fabricated in this experiment). An AR of 1 (corresponding to a square via hole) has been used in this analysis. A length L corresponding to  $\sim 200$  nm (ILD thickness) has been used in these calculations to estimate the metal resistance. This metal resistance is then subtracted from the measured via resistance  $(R_{via})$  to estimate the Co-MLG edge contact resistances  $(R_{con1} + R_{con2})$ . In addition, the "top-contact" resistance is much larger than the "edge-contact" resistance in metal-MLG contacts [25]. Thus, it can be assumed that the top and bottom contact resistances are dominated by the edge contacts (as both top/edge contacts act in parallel). Moreover, both the top and bottom edge contact resistances are almost identical ( $R_{\text{Con1}} \sim R_{\text{Con2}}$ ) since both top and bottom MLGs are of identical thicknesses (~20 nm). Thus, the extracted normalized Co-MLG specific contact resistivity (contact resistance normalized by the perimeter (or via width) and thickness of the top and bottom edge contact regions) is plotted in Fig. 9(d). The minimum specific contact resistivity is estimated to be 2.74  $\Omega$ - $\mu$ m<sup>2</sup>(137  $\Omega$ - $\mu$ m) for the ~0.5  $\mu$ m wide and 20 nm thick Co-MLG edge contacts. This plot is in exact correspondence to our recent results [25], where the extracted contact resistances were normalized only with the perimeter of the top and bottom contact regions. Moreover, this value also corroborates with the partial surface doping claim of MLG caused by FeCl<sub>3</sub>, as it lies between the theoretically estimated (by DFT) edge-contact resistance values of doped- and undoped-MLG with Co [Fig. 7(e), column 2] [25]. In addition, it is worthwhile to note that the extracted contact resistance reduces with a reduction in the via width. This can be attributed to the enhanced current annealing in narrow vias due to a higher local current density [24], [38].

#### C. EM Reliability Measurement

In order to demonstrate the EM resistance of the proposed Co *via* scheme with two-tier MLG, a constant current stress (current density  $J = 200 \text{ MA/cm}^2$  at > 100 °C at Co-MLG contact) is applied to the device [Fig. 8(g)] (corresponding to a *via* width of 200 nm) from top pad B to bottom pad C [Fig. 9(b)]. The *via* resistance increase is observed to be <2% over >40 h stress time, indicating negligible EM in the Co *via* and/or at the Co-MLG contacts [Fig. 9(e)]. This also validates our theoretical claims established in Fig. 5(c), regarding the robust reliability claim of the proposed *via* scheme.

#### IV. ULTIMATE SCALABILITY OF THE PROPOSED VIA SCHEME

The MLG-metal contact resistance forms an integral part of the total *via* resistance in the proposed *via* scheme. Since the scalability aspects of conventional barrierless via metals such as Co, Ru, and W have been well studied [6], [7], [21], [36], it becomes customary to look at the scaling trend of the MLG-metal contact resistance to evaluate its prospects for advanced technology nodes. As shown in Section II-D, DFT simulations have been used to estimate the theoretical lower limit of the MLG-metal (edge) contact resistance. We expect these contact resistance values to be nearly the same unless the thickness of the MLG becomes less than its vertical transfer length (<20 nm for both undoped and DMLG). However, in case of DMLG, in addition to reduction of the specific interface resistivity, the cross-plane effective mass of MLG is also predicted to decrease [39], which will lower the vertical transfer length. Further studies are required to experimentally probe the increase of the contact resistance versus the reduced thickness of the MLG to quantify the vertical transfer limit. Since our experiments have a thickness of  $\sim 20$  nm, we can safely neglect the variation of the edge contact resistance values with the thickness of the undoped/doped MLG.

The DFT simulations in Fig. 7 assume a doping level of -0.6 eV [19], which has been experimentally validated for  $\sim$ 20 nm wire width MLG. To evaluate the benefits of the proposed via scheme at sub-10 nm wire widths, these edge contact resistances were manually added to the overall via resistance while estimating the FO4 delay. Our simulations show  $\sim$  2-fold improvement in the MLG-wire resistance at  $\sim$ 5 nm wire width. It also indicates that although the edge contact resistance leads to a  $\sim$  2-fold increase in the via resistance in the DMLG/Co-via scheme [25], the smaller resistance and parasitics of DMLG wires [19] result in an overall improvement of  $\sim$  2-fold in the FO4 delay with respect to that of conventional Co-interconnects by DD process [25]. It is important to note that, in all these performance projections, a constant thickness of around 20 nm has been assumed. Due to the  $\sim 50 \times$  higher current carrying capacity of MLG interconnects as compared to that of the conventional metals, their thickness can be significantly reduced without compromising the current density requirements. This reduction in MLG thickness would significantly reduce the wire capacitance, which is the key factor determining the performance

of aggressively scaled shorter wires whose resistances are significantly smaller than the driver resistances.

#### V. CONCLUSION

In this work, the pressure-assisted solid-phase lowtemperature/transfer-free graphene growth technique has been engineered to achieve large-area and high-quality MLG films on both standard SiO<sub>2</sub> and Cu substrates. Moreover, a new SEenabled via scheme has been proposed and demonstrated for fabricating multi-level MLG wires. The low-temperature MLG growth technique has been designed to facilitate integration of graphene into the CMOS technology-either as replacement for Cu interconnects or as capping layer for certain Cu wires. The low-temperature growth process is also well-suited for monolithic-3-D integration with 2-D materials involving graphene [16]. In our current experiment, the MLG/Co-via interconnect structure offers supreme reliability against SH and EM as compared with conventional DD interconnect technologies. Rigorous scaling analyses indicate that the increase in the total via resistance in case of the DMLG/Co-via multilevel structure is more than compensated by the reduced wire resistance, resulting in  $\sim$  2-fold improvement in the overall circuit performance as compared with that of the DD process. Owing to the higher current-carrying capacity of graphene with respect to conventional metals, the performance can be further improved by using thinner MLG wires provided the driver resistance is higher than the wire resistance. The higher current-carrying capacity of DMLG wires in conjunction with their lower resistivity also make them an ideal candidate for on-chip inductor applications [40].

#### REFERENCES

- K. Banerjee and A. Mehrotra, "Global (interconnect) warming," *IEEE Circuits Devices Mag.*, vol. 17, no. 5, pp. 16–32, Sep. 2001, doi: 10.1109/101.960685.

- [2] N. Srivastava and K. Banerjee, "Interconnect challenges for nanoscale electronic circuits," *JOM*, vol. 56, no. 10, pp. 30–31, Oct. 2004, doi: 10. 1007/s11837-004-0285-1.

- [3] S. Im, N. Srivastava, K. Banerjee, and K. E. Goodson, "Scaling analysis of multilevel interconnect temperatures for high-performance ICs," *IEEE Trans. Electron Devices*, vol. 52, no. 12, pp. 2710–2719, Dec. 2005, doi: 10.1109/TED.2005.859612.

- [4] H. Li, C. Xu, N. Srivastava, and K. Banerjee, "Carbon nanomaterials for next-generation interconnects and passives: Physics, status, and prospects," *IEEE Trans. Electron Devices*, vol. 56, no. 9, pp. 1799–1821, Sep. 2009, doi: 10.1109/TED.2009.2026524.

- [5] H. Li, C. Xu, and K. Banerjee, "Carbon nanomaterials: The ideal interconnect technology for next-generation ICs," *IEEE Des. Test. Comput.*, vol. 27, no. 4, pp. 20–31, Jul. 2010, doi: 10.1109/MDT.2010.55.

- [6] C.-K. Hu et al., "Future on-chip interconnect metallization and electromigration," in Proc. IEEE Int. Rel. Phys. Symp. (IRPS), Mar. 2018, pp. 4F.1.1–4F.1.4, doi: 10.1109/IRPS.2018.8353597.

- [7] S. Dutta *et al.*, "Sub-100 nm<sup>2</sup> cobalt interconnects," *IEEE Electron Device Lett.*, vol. 39, no. 5, pp. 731–734, May 2018, doi: 10.1109/LED. 2018.2821923.

- [8] C. Xu, H. Li, and K. Banerjee, "Modeling, analysis, and design of graphene nano-ribbon interconnects," *IEEE Trans. Electron Devices*, vol. 56, no. 8, pp. 1567–1578, Aug. 2009, doi: 10.1109/TED. 2009.2024254.

- [9] S. Armini, Z. El-Mekki, J. Swerts, M. Nagar, and S. Demuynck, "Direct copper electrochemical deposition on ru-based substrates for advanced interconnects target 30 nm and 1/2 pitch lines: From coupon to full-wafer experiments," *J. Electrochem. Soc.*, vol. 160, no. 3, pp. D89–D94, 2013, doi: 10.1149/2.032303jes.

- [10] J. S. Chawla *et al.*, "Patterning challenges in the fabrication of 12 nm half-pitch dual damascene copper ultra- low-k interconnects," *Proc. SPIE*, vol. 9054, Mar. 2014, Art. no. 905404, doi: 10.1117/12.2048599.

- [11] Y. L. Hsieh *et al.*, "Effects of BEOL copper CMP process on TDDB for direct polishing ultra-low k dielectric cu interconnects at 28nm technology node and beyond," in *Proc. IEEE Int. Rel. Phys. Symp.* (*IRPS*), Apr. 2013, p. 3, doi: 10.1109/IRPS.2013.6532056.

- [12] Y.-M. Lin *et al.*, "100-GHz transistors from wafer-scale epitaxial graphene," *Science*, vol. 327, no. 5966, p. 662, Feb. 2010, doi: 10.1126/science.1184289.

- [13] F. Schwierz, "Graphene transistors," *Nature Nanotechnol.*, vol. 5, no. 7, p. 487, 2010, doi: 10.1038/nnano.2010.89.

- [14] M. Liu *et al.*, "A graphene-based broadband optical modulator," *Nature*, vol. 474, no. 7349, pp. 64–67, Jun. 2011, doi: 10.1038/nature10067.

- [15] Q. Bao and K. P. Loh, "Graphene photonics, plasmonics, and broadband optoelectronic devices," ACS Nano, vol. 6, no. 5, pp. 3677–3694, May 2012, doi: 10.1021/nn300989g.

- [16] J. Jiang, K. Parto, W. Cao, and K. Banerjee, "Ultimate monolithic-3D integration with 2D materials: Rationale, prospects, and challenges," *IEEE J. Electron Devices Soc.*, vol. 7, pp. 878–887, Jun. 2019, doi: 10. 1109/JEDS.2019.2925150.

- [17] Y. M. Zuev, W. Chang, and P. Kim, "Thermoelectric and magnetothermoelectric transport measurements of graphene," *Phys. Rev. Lett.*, vol. 102, no. 9, Mar. 2009, Art. no. 096807, doi: 10.1103/PhysRevLett.102.096807.

- [18] C. Xu, H. Li, and K. Banerjee, "Graphene nano-ribbon (GNR) interconnects: A genuine contender or a delusive dream?" in *IEDM Tech. Dig.*, Dec. 2008, pp. 201–204, doi: 10.1109/IEDM.2008.4796651.

- [19] J. Jiang *et al.*, "Intercalation doped multilayer-graphene-nanoribbons for next-generation interconnects," *Nano Lett.*, vol. 17, no. 3, pp. 1482–1488, Mar. 2017, doi: 10.1021/acs.nanolett.6b04516.

- [20] J. Jiang, J. H. Chu, and K. Banerjee, "CMOS-compatible Dopedmultilayer-graphene interconnects for next-generation VLSI," in *IEDM Tech. Dig.*, Dec. 2018, p. 34, doi: 10.1109/IEDM.2018.8614535.

- [21] S. J. Yoon, S. Lee, T. I. Lee, A. Yoon, and B. J. Cho, "Large grain ruthenium for alternative interconnects," *IEEE Electron Device Lett.*, vol. 40, no. 1, pp. 91–94, Jan. 2019, doi: 10.1109/LED.2018.2879932.

- [22] M. R. Baklanov et al., "Plasma processing of low-k dielectrics," J. Appl. Phys., vol. 113, no. 4, Jan. 2013, Art. no. 041101, doi: 10.1063/ 1.4765297.

- [23] I. Ciofi et al., "RC benefits of advanced metallization options," IEEE Trans. Electron Devices, vol. 66, no. 5, pp. 2339–2345, May 2019, doi: 10.1109/TED.2019.2902031.

- [24] J. Jiang, J. Kang, J. H. Chu, and K. Banerjee, "All-carbon interconnect scheme integrating graphene-wires and carbon-nanotube-vias," in *IEDM Tech. Dig.*, Dec. 2017, p. 14, doi: 10.1109/IEDM.2017.8268389.

- [25] K. Agashiwala, J. Jiang, C. H. Yeh, K. Parto, D. Zhang, and K. Banerjee, "Reliability and performance of CMOS-compatible multi-level graphene interconnects incorporating vias," in *IEDM Tech. Dig.*, Dec. 2020, pp. 31.1.1–31.1.4, doi: 10.1109/IEDM13553.2020.9371986.

- [26] R. Mehta, S. Chugh, and Z. Chen, "Enhanced electrical and thermal conduction in graphene-encapsulated copper nanowires," *Nano Lett.*, vol. 15, no. 3, pp. 2024–2030, Mar. 2015, doi: 10.1021/nl504889t.

- [27] A. Allain, J. Kang, K. Banerjee, and A. Kis, "Electrical contacts to two-dimensional semiconductors," *Nature Mater.*, vol. 14, no. 12, pp. 1195–1205, Dec. 2015, doi: 10.1038/nmat4452.

- [28] Y. Khatami, H. Li, C. Xu, and K. Banerjee, "Metal-to-multilayergraphene contact—Part I: Contact resistance modeling," *IEEE Trans. Electron Devices*, vol. 59, no. 9, pp. 2444–2452, Sep. 2012, doi: 10. 1109/TED.2012.2205256.

- [29] A. K. Stamper, T. L. McDevitt, and S. L. Luce, "Sub-0.25-micron interconnection scaling: Damascene copper versus subtractive aluminum," in *Proc. IEEE/SEMI IEEE/SEMI Adv. Semiconductor Manuf. Conf. Workshop*, Sep. 1998, pp. 337–346, doi: 10.1109/ASMC.1998. 731585.

- [30] I. A. Blech, "Electromigration in thin aluminum films on titanium nitride," J. Appl. Phys., vol. 47, no. 4, pp. 1203–1208, Apr. 1976, doi: 10. 1063/1.322842.

- [31] J. Jiang, J. Kang, and K. Banerjee, "Characterization of self-heating and current-carrying capacity of intercalation doped graphene-nanoribbon interconnects," in *Proc. IEEE Int. Rel. Phys. Symp. (IRPS)*, Apr. 2017, pp. 6-B.1–6-B.6, doi: 10.1109/IRPS.2017.7936339.

- [32] M. R. Amirzada, A. Tatzel, V. Viereck, and H. Hillmer, "Surface roughness analysis of SiO<sub>2</sub> for PECVD, PVD and IBD on different substrates," *Appl. Nanosci.*, vol. 6, no. 2, pp. 215–222, Feb. 2016, doi: 10. 1007/s13204-015-0432-8.

- [33] D. Stradi, U. Martinez, A. Blom, M. Brandbyge, and K. Stokbro, "General atomistic approach for modeling metal-semiconductor interfaces using density functional theory and nonequilibrium green's function," *Phys. Rev. B, Condens. Matter*, vol. 93, no. 15, pp. 28–38, Apr. 2016, doi: 10.1103/PhysRevB.93.155302.

- [34] J. P. Perdew, K. Burke, and M. Ernzerhof, "Generalized gradient approximation made simple," *Phys. Rev. Lett.*, vol. 77, no. 18, pp. 3865–3868, Oct. 1996, doi: 10.1103/PhysRevLett.77.3865.

- [35] S. Grimme, J. Antony, S. Ehrlich, and H. Krieg, "A consistent and accurate ab initio parametrization of density functional dispersion correction (DFT-D) for the 94 elements H-Pu," *J. Chem. Phys.*, vol. 132, no. 15, Apr. 2010, Art. no. 154104, doi: 10.1063/1.3382344.

- [36] S. Beyne, K. Croes, I. De Wolf, and Z. Tokei, "1/f noise measurements for faster evaluation of electromigration in advanced microelectronics interconnections," *J. Appl. Phys.*, vol. 119, no. 18, May 2016, Art. no. 184302, doi: 10.1063/1.4947582.

- [37] R. Chau, "Process and packaging innovations for Moore's law continuation and beyond," in *IEDM Tech. Dig.*, Dec. 2019, pp. 1.1.1–1.1.6, doi: 10.1109/IEDM19573.2019.8993462.

- [38] Q. Cao *et al.*, "End-bonded contacts for carbon nanotube transistors with low, size-independent resistance," *Science*, vol. 350, no. 6256, pp. 68–72, Oct. 2015, doi: 10.1126/science.aac8006.

- [39] W. Cao, M. Huang, C.-H. Yeh, K. Parto, and K. Banerjee, "Impact of transport anisotropy on the performance of van der Waals materials-based electron devices," *IEEE Trans. Electron Devices*, vol. 67, no. 3, pp. 1310–1316, Mar. 2020, doi: 10.1109/TED.2020. 2970394.

- [40] J. Kang *et al.*, "On-chip intercalated-graphene inductors for nextgeneration radio frequency electronics," *Nature Electron.*, vol. 1, no. 1, pp. 46–51, Jan. 2018, doi: 10.1038/s41928-017-0010-z.