# **Lawrence Berkeley National Laboratory**

# **Recent Work**

### **Title**

FRONT END ELECTRONICS FOR THE JET DRIFT CHAMBER

## **Permalink**

https://escholarship.org/uc/item/2rz1699b

### **Authors**

Lo, C.C. Olson, S. Bistirlich, J.

### **Publication Date**

1988-10-01

# Lawrence Berkeley Laboratory

UNIVERSITY OF CALIFORNIA

# Engineering Division

RECEIVED

LAWRENCE

BERKEI EY LABORATORY

MAY 5 1989

Presented at the IEEE Nuclear Science Symposium, Orlando, FELMENTS SECTION November 9–11, 1988, and to be published in the Proceedings

Front End Electronics for the Jet Drift Chamber

C.C. Lo, S. Olson, and J. Bistirlich

October 1988

# TWO-WEEK LOAN COPY

This is a Library Circulating Copy which may be borrowed for two weeks.

### **DISCLAIMER**

This document was prepared as an account of work sponsored by the United States Government. While this document is believed to contain correct information, neither the United States Government nor any agency thereof, nor the Regents of the University of California, nor any of their employees, makes any warranty, express or implied, or assumes any legal responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by its trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof, or the Regents of the University of California. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof or the Regents of the University of California.

# Front End Electronics for the Jet Drift Chamber

C.C. Lo, S. Olson, and J. Bistirlich

Engineering Division

Lawrence Berkeley Laboratory

1 Cyclotron Road

Berkeley, California 94720

USA

October 1988

### FRONT END ELECTRONICS FOR THE JET DRIFT CHAMBER

C.C. Lo, S. Olson and J. Bistirlich Lawrence Berkeley Laboratory 1 Cyclotron Road Berkeley, California 94720 U.S.A.

#### **ABSTRACT**

The Jet Drift Chamber employs a charge division readout scheme which requires two amplifiers per sense wire. Since there are 690 sense wires, 1380 amplifiers are needed. It follows that each end cap must accommodate 690 amplifiers which makes packaging and cooling critical problems. As a result, 30 six-layer surface mount boards each containing 24 (23 used) channels of amplifiers have been made. Each amplifier could accept up to 2 pC of charge and could provide a linear differential output of ± 300 mV which is used to drive a twisted pair transmission line up to 70' in length. The power dissipation of each board is 1.5 W.

### INTRODUCTION

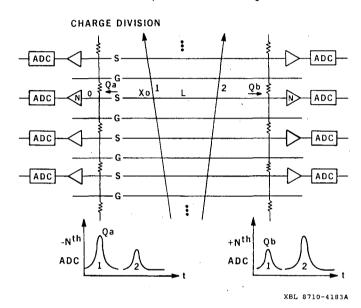

A charge division<sup>1,2</sup> readout scheme requires two amplifiers per sense wire; i.e., one amplifier at each end of the wire. There are a total of 30 sectors in the drift chamber and each sector contains 23 wires. It follows that a total of 1380 amplifiers are required with 690 amplifiers housed in each end cap. The space available in each end cap to house these amplifiers is very limited; hence, the packaging and power dissipation of the system must be carefully designed and planned. Figure 1 shows the charge division readout scheme employed by the Jet Drift Chamber. The ratio of charge collected at the two ends of the sense wire having a length L is:

Qa/Qb = (L - Xo)/XoQ = Qa + Qb

and

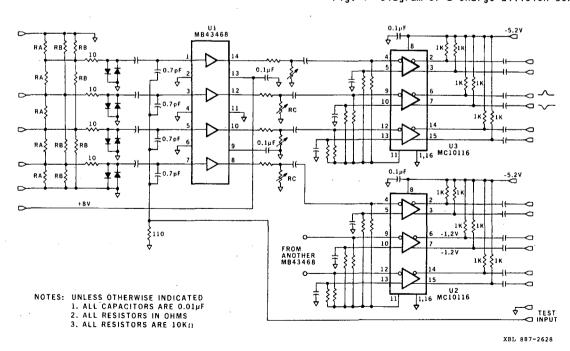

The front end electronics make use of proven and readily available components which provide 24 channels of amplifier on a single card. The card has a dimension of 11 cm in length and 5 cm in width. Figure 2 is a schematic diagram of the front end showing 4 channels of the 24 amplifiers on a single card.

Fig. 1 Diagram of a charge division scheme.

Fig. 2 Partial schematic diagram of the JDC front end.

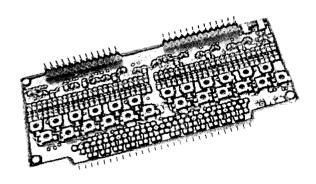

All components used are of surface mount type. The circuit board contains six layers of circuit traces, ground and power planes. Components are mounted on the two outside surfaces. The card was designed to minimize crosstalk between channels by isolating adjacent channels with either ground traces or power bus traces. Components and circuit traces placement has also been implemented carefully to reduce crosstalk to a minimum. The ground layer has been used to shield critical crosstalk paths wherever possible. The total thickness of the six-layer board is ~ 2 mm.

#### FRONT END CIRCUIT DESCRIPTIONS

The resistor network at the inputs of the amplifiers is used for chamber wire crosstalk cancellation. The values of the resistors depend on the characteristics of the drift chamber. A diode pair is connected from the input signal line to ground to provide some protection for the amplifier from voltage transients. An integrated 0.7 pF capacitor is connected to the input of each amplifier. These capacitors serve as charge injection capacitors for testing the amplifiers.

The Fujisu MB43468 amplifier chips<sup>3</sup> are used as the preamplifiers. Each chip contains 4 amplifiers. Each amplifier output is attenuated by an adjustable voltage divider to obtain the proper input signal level for the MC10116 line drivers. The 24 miniature adjustable resistors (square shapes) can be seen in Fig. 3.

Since the output signals of this front end must be transmitted to an Analog To Digital Converter (ADC) some 70' away, the MC10116 line drivers are used in the linear mode to provide differential outputs to drive twisted pair transmission lines. This substantially reduced noise pickup along this 70' run. Each MC10116 chip contains 3 differential amplifiers. It follows that, in order to make up 24 amplifier channels, six MB43468 chips and eight MC10116 chips are required on each board. The 14 chips can be seen in Fig. 4.

In order to reduce the heat load on the boards and therefore in the drift chamber, the pull down resistors for the differential amplifiers are located external of the board at the receiving ends of the twisted pair transmission lines.

CBB 886-6245

Fig. 3 Photograph of one side of the board showing 24 adjustable resistors.

CBB 886-6241

Fig. 4 Photograph of one side of the board showing 14 amplifier chips.

#### SYSTEM PERFORMANCE

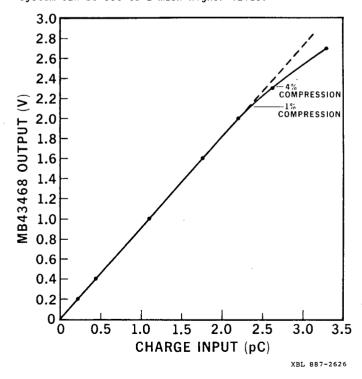

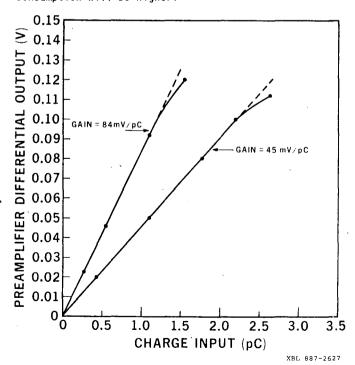

Figure 5 shows the gain of the MB43468 amplifier to be ~ 900mV/pC with the 1% compression point occuring at an input charge of 2.35 pC. Figure 6 shows two system transfer functions of the MB43468/ MC10116 amplifier. The 45 mV/pC gain was used to cover an input range of 0 - 2.3 pC. The 84 mV/pC gain was used to cover an input range of 0 - 1.2 pC. The primary limitation is caused by the ADC's ± 100 mV input signal range used in the data acquisition system. The secondary limitation is the  $\pm$  300 mV linear range of the MC10116 differential amplifier. Disregarding the ADC limitation, the best gain achieved using the MB43468/MC10116 system would be around 150 mV/pC with an input dynamic range of 0 - 2 pC. However, if the dynamic range is small, the gain of the system can be set to a much higher value.

Fig. 5 Transfer function of a typical MB43468 amplifier.

The gain compression of a typical amplifier operating in the  $\pm$  100 mV output voltage range is < 1% at the maximum output voltage level. If a  $\pm$  300 mV output voltage range is used, the pull down resistors must be changed to 270 ohms. The gain compression at the maximum output signal in this case would become 5%.

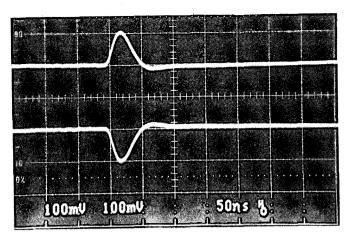

The system gain can be optimized by adjusting the attenuator between the MB43468 output and the input of the MC10116 which has a typical voltage gain of 5. Ihe attenuator also allows for correction of unequal channel gain. Figure 7 shows the outputs of a typical amplifier with a test charge injected at the signal input port. The 10-90% risetime of a typical amplifier is 12 ns. The equivalent noise at the input is 3000 electrons rms whereas the input impedence across the bandwidth of interest is  $\sim 90$  ohms.

The test charge is injected into all the amplifiers at the same time via the 0.7 pF integrated capacitors. It was noticed that the 4 channels closest to the center of the board produced output signals somewhat contaminated by the test voltage step which was producing a contamination charge via some stray capacitance in the range of 20% of the injected charge. Since this test function is not intended to be used for precise calibration, no further effort was used to improve this situation. Crosstalk between channels is less than 1.5%.

The total power consumption of each card, including the pull down resistors, amounts to 2.25 W. Locating the 46 1 K ohms pull down resistors at the receiving ends of the twisted pair transmission line will reduce the power dissipation per board to 1.5 W. Assuming a total of 30 cards per end cap, the power dissipation per end cap will be 45 W or 90 W for both end caps. The system power consumption amounts to 135 W with 45 W being dissipated by the pull down resistors. Further power reduction could be achieved by employing a pulse power scheme. A Notice that if 270 ohms are used for pull down resistors, the total power consumption will be higher.

Fig. 6 Transfer functions of a typical channel of MB43468/MC10116 amplifier.

XBB 887-7207

Fig. 7 Typical differential output waveshapes of an amplifier channel across 56 ohm loads.

#### CONCLUSIONS

Although the front end was designed for a specific drift chamber, the flexibility of the system could make it useful in many other applications. The differential outputs are very useful for driving long transmission lines to reduce noise pickup. The low cost (\$220 per board) and the compact size could also be attractive for many applications. Further reduction of the test pulse contamination could be made by shielding portions of the test pulse input trace with the ground plane and the power plane, preventing it from injecting stray charge into the nearby amplifier channels.

### ACKNOWLEDGMENTS

The authors acknowledge the diligent efforts of Judy Stirkkinen in the successful layout of this demanding front end board.

This work was supported by the Director, Office of Energy Research, Division of Nuclear Physics of the Office of High Energy and Nuclear Physics of the U.S. Department of Energy under Contract Number DE-ACO3-76SF00098. Reference to a company or product name does not imply approval or recommendation of the product by the University of California to the exclusion of others that may be suitable.

### REFERENCES

- V. Radeka and P. Rehak, Charge Dividing Mechanism On Resistive Electrode In Position-Sensitive Detectors, IEEE Trans. Nucl. Sci., NS-26, No. 1, 225-238 (1979)

- D.M. Binnie, Charge Division And Precision Timing In A Drift Chamber, Nucl. Instr. Meth., 192, No. 2-3, 231-233 (1982).

- F. Suekane, T. Kondo and S. Odaka, A New Preamplifier For Drift Chambers, IEEE Trans. Nucl. Sci., NS-33, No. 1, 73-76 (1986).

- C.C. Lo, F. Kirsten, M. Nakamura, R. Jared, F. Goulding, A. Yim, J. Moss, D. Freytag, G. Haller, R. Larsen and L. Pregernig, The Hybridized Front End Electronics Of The Central Drift Chamber In The Stanford Linear Collider Detector, IEEE Trans. Nucl. Sci., NS-35, No. 1, 142-145 (1988).

LAWRENCE BERKELEY LABORATORY

TECHNICAL INFORMATION DEPARTMENT

UNIVERSITY OF CALIFORNIA

BERKELEY, CALIFORNIA 94720