## UNIVERSITY OF CALIFORNIA

Los Angeles

Lightweight Opportunistic Memory Resilience

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical and Computer Engineering

by

Irina Alam

© Copyright by Irina Alam 2021

#### ABSTRACT OF THE DISSERTATION

Lightweight Opportunistic Memory Resilience

by

Irina Alam

Doctor of Philosophy in Electrical and Computer Engineering University of California, Los Angeles, 2021 Professor Puneet Gupta, Chair

The reliability of memory subsystems is worsening rapidly and needs to be considered as one of the primary design objectives when designing today's computer systems. From on-chip embedded memories in Internet-of-Things (IoT) devices and on-chip caches to off-chip main memories, they have become the limiting factor in the reliability of these computing systems. Today's applications demand large capacity of on-chip or off-chip memory or both. With aggressive technology scaling, coupled with the increase in the total area devoted to memory in a chip, memories are becoming particularly sensitive to manufacturing process variation, environmental operating conditions, and aging-induced wearout. However, the challenge with memory reliability is that the resiliency techniques need to be effective but with minimal overhead. Today's typical error correcting schemes do not take into consideration the data value that they are protecting and are purely based on positional errors. This increases their overheads and makes them too expensive, especially for on-chip memories. Also, the drive for denser off-chip main memories is worsening their reliability. But strengthening today's error correction techniques will result in non-negligible increase in overheads. Hence, this dissertation proposes Lightweight Opportunistic Memory Resilience. We exploit the following three aspects to make memories more reliable with low overheads: (1) Underlying memory fault models, (2) Data value behavior of commonly used applications, and (3) The architecture of the memory itself. We opportunistically exploit these three aspects to provide stronger protection against memory errors. We design novel error detecting and correcting codes and develop several other architectural fault tolerance techniques at minimal overheads compared to

the conventional reliability techniques used in today's memories.

In part 1 of this dissertation, we address the reliability concerns in lightweight on-chip caches or embedded memories like scratchpads in IoT devices. These memories are becoming larger in size, but needs to be low power. Using standard error correcting codes or traditional row/column sparing to recover from faults are too expensive for them. Here, we leverage the fact that manufacturing defects and aging-induced hard faults usually only affect only a few bits in a memory. These bits, however, inhibit how low of a voltage these chips can be operated at. Traditional software fails even when a small number of bits in a memory are faulty. For the first time, we provide two solutions, FaultLink and SAME-Infer, which help deal with these weak faulty cells in the memory by generating a custom-tailored fault-aware application binary image for each chip. Next, we designed Software-Defined Error Localization Code (SDELC) and Parity++ as lightweight runtime error recovery techniques that leverage the insight that data values have locality in them and certain ranges of data values occur more frequently than others. Conventional ECC is too expensive for these lightweight memories. SDELC uses novel ultra-lightweight error-localizing codes to localize the error to a chunk in the data. It then heuristically recovers from the localized error by exploiting side information about the application's memory contents. Parity++ is a novel unequal message protection scheme that preferentially provides stronger error protection to certain "special messages". This protection scheme provides Single Error Detection (SED) for all messages and Single Error Correction (SEC) for a subset of special messages. Both these novel codes utilize data value behavior to provide single error correction at 2.5x-4x lower overhead than a conventional hamming single error correcting code.

In part 2 of this dissertation, we focus on off-chip main memory technologies. We primarily leverage the details of the memory architecture itself and their dominant fault mechanisms to effectively design reliability schemes. The need for larger main memory capacity in today's workstation or server environments is driving the use of non-volatile memories (NVM) or techniques to enable high density DRAMs. Due to aggressive scaling, the single-bit error rate in DRAMs is steadily increasing and DRAM manufacturers are adopting on-die error correction coding (ECC) schemes, along with within memory controller ECC, to correct single-bit errors in the memory. In *COMET* we have shown that today's standard on-die ECCs can lead to silent data corruption if not

designed correctly. We propose a collaborative on-die and in-controller error correction scheme that prevents double-bit error induced silent data corruption and corrects 99.9997% of these double-bit errors at absolutely no additional storage, latency, and area overheads. Not just DRAMs, reliability is a major concern in most of the emerging NVM technologies. In *Compression with Multi-ECC (CME)*, we propose a new opportunistic compression-based ECC protection scheme for magnetic memory-based main memories. CME compresses every memory line and uses the saved bits to add stronger protection. In some of these NVMs, error rates increase as we try to improve read/write latencies. In *PCM-Duplicate*, we propose an enhanced PCM architecture that reduces PCM read latency by more than 3x and makes it comparable to that of DRAM. We then use ECC to tolerate the additional errors that arise because of the proposed optimizations.

Overall, we have developed a complementary suite of novel methods for tolerating faults and correcting errors in different levels of the memory hierarchy. We exploit the memory architecture and fault mechanisms as well as the application data behavior to tune the proposed solutions to the particular memory characteristics; lightweight solutions for low-cost embedded memories and latency-critical on-chip caches while stronger protection for off-chip main memory subsystems. With memory reliability being a major bottleneck in today's systems, these novel solutions are expected to alleviate this problem, help cope with the unique outcomes of hardware variability in memory systems and provide improved reliability at minimal cost.

The dissertation of Irina Alam is approved.

Tony Nowatzki

Chih-Kong Ken Yang

Lara Dolecek

Puneet Gupta, Committee Chair

University of California, Los Angeles

2021

To my parents who inspire me, and without whom none of this would have been possible.

## TABLE OF CONTENTS

| 1 | Intr | oductio | n                                                                     | 1  |

|---|------|---------|-----------------------------------------------------------------------|----|

|   | 1.1  | Memo    | ry Reliability is Becoming a Key Concern                              | 2  |

|   | 1.2  | Power   | /Performance Scaling and Fault Tolerance in Lightweight On-Chip SRAM- |    |

|   |      | based   | Memories                                                              | 4  |

|   | 1.3  | Scalab  | vility Concerns in DRAM-based Main Memories                           | 5  |

|   | 1.4  | Reliab  | ility and Performance Challenges of Non-Volatile Main Memory Systems  | 6  |

|   | 1.5  | Disser  | tation Outline                                                        | 7  |

| 2 | Fau  | ltLink: | Low Cost Fault Tolerance for IoT Devices                              | 11 |

|   | 2.1  | Introdu | uction                                                                | 12 |

|   | 2.2  | Backg   | round                                                                 | 13 |

|   |      | 2.2.1   | Scratchpad Memories (SPMs)                                            | 13 |

|   |      | 2.2.2   | Program Sections and Memory Segments                                  | 14 |

|   |      | 2.2.3   | Tolerating SRAM Faults                                                | 14 |

|   | 2.3  | FaultL  | ink                                                                   | 15 |

|   |      | 2.3.1   | Test Chip Experiments                                                 | 17 |

|   |      | 2.3.2   | Toolchain                                                             | 18 |

|   |      | 2.3.3   | Fault-Aware Section-Packing                                           | 18 |

|   | 2.4  | Evalua  | ation                                                                 | 21 |

|   |      | 2.4.1   | Voltage Reduction on Real Test Chips                                  | 21 |

|   |      | 2.4.2   | Yield at Min-VDD for Synthetic Test Chips                             | 23 |

|   | 2.5  | Relate  | d Work                                                                | 26 |

|   |      | 2.5.1   | Fault-Tolerant Caches                                                 | 26 |

|    |      | 2.5.2   | Fault-Tolerant Scratchpads                                                    | 26 |

|----|------|---------|-------------------------------------------------------------------------------|----|

|    | 2.6  | Discus  | sion                                                                          | 27 |

|    |      | 2.6.1   | Memory Reliability Binning                                                    | 27 |

|    |      | 2.6.2   | Coping with Aging and Wearout using FaultLink                                 | 27 |

|    |      | 2.6.3   | Directions for Future Work                                                    | 28 |

|    | 2.7  | Conclu  | sion                                                                          | 28 |

| 3  | SAM  | IE-Infe | r: <u>Software Assisted Memory Resilience for Efficient Infer</u> ence at the |    |

| Ed | lge. |         |                                                                               | 29 |

|    | 3.1  | Introdu | ction                                                                         | 30 |

|    | 3.2  | Backgr  | ound                                                                          | 32 |

|    |      | 3.2.1   | SRAM Faults                                                                   | 32 |

|    |      | 3.2.2   | Fault Resilient DL networks                                                   | 33 |

|    | 3.3  | SAME    | -Infer Methodology                                                            | 33 |

|    |      | 3.3.1   | Fault Impact Analysis                                                         | 35 |

|    |      | 3.3.2   | Packing Critical and Non-Critical Sections                                    | 35 |

|    |      | 3.3.3   | Breaking up monolithic weight sections into smaller kernels                   | 36 |

|    |      | 3.3.4   | Analytical Critical and Non-critical Section Packing Estimation               | 39 |

|    | 3.4  | Experi  | mental Setup                                                                  | 40 |

|    | 3.5  | Results |                                                                               | 42 |

|    |      | 3.5.1   | Reduction in voltage with SAME-Infer                                          | 42 |

|    |      | 3.5.2   | Splitting up Weights to Achieve Better Packing                                | 45 |

|    |      | 3.5.3   | Importance of Sensitivity Analysis of Fault Tolerant sections                 | 47 |

|    |      | 3.5.4   | Analytical Model to Estimate for Larger Sized Memories                        | 48 |

|    |      | 3.5.5   | Evaluation for Binarized Dense and Sparse Networks                            | 48 |

|   |      | 3.5.6   | Comparison with Past Works                                               | 51 |

|---|------|---------|--------------------------------------------------------------------------|----|

|   | 3.6  | Discus  | sion                                                                     | 54 |

|   |      | 3.6.1   | Fault Injection During Training to Tolerate Soft Errors                  | 54 |

|   |      | 3.6.2   | Improving Packing by Optional Reversing of Non-Critical Sections         | 54 |

|   |      | 3.6.3   | Universal Packing Solution to Allow Dynamic Voltage Scaling and Tolerate |    |

|   |      |         | Aging Induced Faults                                                     | 55 |

|   |      | 3.6.4   | Addressing the Code Memory Bottleneck                                    | 56 |

|   |      | 3.6.5   | Use of Error Correcting Codes (ECC)                                      | 56 |

|   |      | 3.6.6   | Extending SAME-Infer to Other Approximation Tolerant Applications        | 57 |

|   | 3.7  | Conclu  | usion                                                                    | 58 |

| 4 | Soft | ware-Da | efined Error-Localizing Codes (SDELC): Lightweight Recovery from Soft    |    |

|   |      |         |                                                                          |    |

|   | 4.1  | Introdu | uction                                                                   | 60 |

|   | 4.2  |         | round                                                                    |    |

|   |      | 4.2.1   | Error-Correcting Codes (ECCs)                                            |    |

|   |      | 4.2.2   | Error-Localizing Codes                                                   |    |

|   | 4.3  | Softwa  | are-Defined Error-Localizing Codes (SDELC): Recovering Soft Faults at    |    |

|   |      |         | ime                                                                      | 62 |

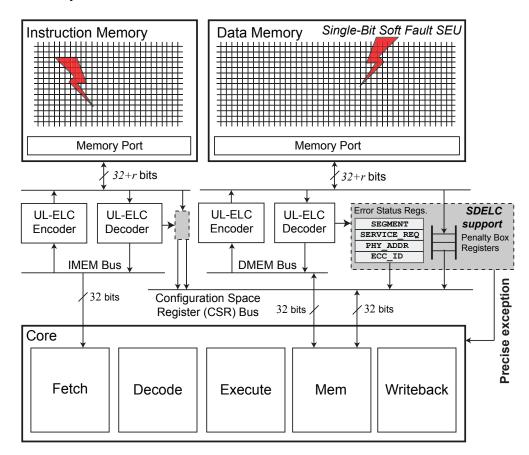

|   |      | 4.3.1   | Architecture                                                             | 63 |

|   |      | 4.3.2   | Ultra-Lightweight Error-Localizing Codes (UL-ELC)                        | 64 |

|   |      | 4.3.3   | Recovering SEUs in Instruction Memory                                    | 66 |

|   |      | 4.3.4   | Recovering SEUs in Data Memory                                           | 68 |

|   | 4.4  | Evalua  | tion - Soft Fault Recovery using SDELC                                   | 69 |

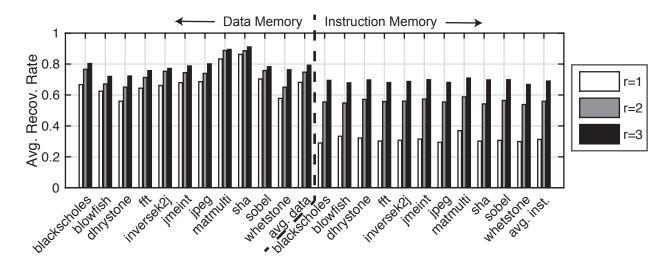

|   |      | 4.4.1   | Overall Results                                                          | 70 |

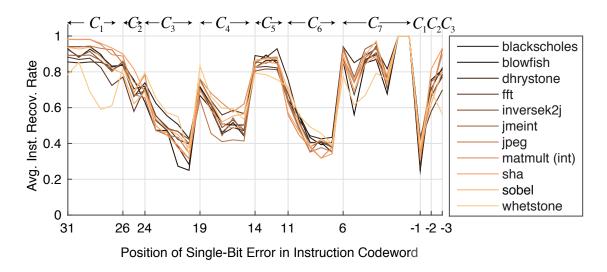

|   |      | 4.4.2   | Recovery Policy Analysis                                                 | 71 |

|   |      | 4.4.3   | Risk of SDCs from SDELC                                               | 73 |

|---|------|---------|-----------------------------------------------------------------------|----|

|   | 4.5  | Conclu  | sion                                                                  | 73 |

| 5 | Pari | ty++: L | ightweight Error Correction for Last Level Caches                     | 74 |

|   | 5.1  | Introdu | uction                                                                | 75 |

|   | 5.2  | Backgı  | round and Related Work                                                | 76 |

|   |      | 5.2.1   | Error Correcting Codes                                                | 76 |

|   |      | 5.2.2   | SRAM Reliability and Error Detection and Correction in Caches         | 77 |

|   |      | 5.2.3   | Application Characteristics                                           | 77 |

|   | 5.3  | Lightw  | reight Error Correction Code                                          | 78 |

|   |      | 5.3.1   | Theory                                                                | 78 |

|   |      | 5.3.2   | Error Detection and Correction                                        | 81 |

|   |      | 5.3.3   | Architecture                                                          | 82 |

|   |      | 5.3.4   | Coverage and Overheads                                                | 85 |

|   | 5.4  | Experi  | mental Methodology                                                    | 87 |

|   | 5.5  | Results | s and Discussion                                                      | 88 |

|   | 5.6  | Conclu  | ision                                                                 | 92 |

| 6 | CON  | ИЕТ: О  | n-die and In-controller Collaborative Memory ECC Technique for Strong | er |

| - |      |         | ection of DRAM Errors                                                 |    |

|   | 6.1  | Introdu | uction                                                                | 94 |

|   | 6.2  |         | round                                                                 |    |

|   |      | 6.2.1   | DRAM Operation                                                        |    |

|   |      | 6.2.2   | Linear Hamming Error Correcting Codes                                 |    |

|   |      | 6.2.3   | SEC vs. SECDED                                                        |    |

|   | 6.3  |         | tion                                                                  |    |

|     | 6.3.1   | Miscorrections by On-Die ECC                                             | 99  |

|-----|---------|--------------------------------------------------------------------------|-----|

|     | 6.3.2   | SDC post in-controller SECDED decoding                                   | 100 |

| 6.4 | COME    | ET ECC Design to Eliminate Silent Data Corruption                        | 102 |

|     | 6.4.1   | On-die SEC-COMET ECC                                                     | 103 |

|     | 6.4.2   | In-controller SECDED-COMET ECC                                           | 105 |

| 6.5 | COM     | ET Double-bit Error Correction                                           | 107 |

|     | 6.5.1   | Constructing on-die SEC code to enable Double-bit Error Correction (SEC- |     |

|     |         | COMET-DBC)                                                               | 107 |

|     | 6.5.2   | Collaborative DBE Correction                                             | 108 |

|     | 6.5.3   | Implementation of COMET command                                          | 115 |

| 6.6 | Result  | 8                                                                        | 116 |

|     | 6.6.1   | Reliability Evaluation                                                   | 116 |

|     | 6.6.2   | Effectiveness of COMET Double-bit Correction                             | 118 |

|     | 6.6.3   | Impact on Encoder/Decoder Area, Energy and Latency                       | 118 |

|     | 6.6.4   | Performance Impact of SEC-COMET-DBC                                      | 119 |

| 6.7 | Discus  | ssion                                                                    | 120 |

|     | 6.7.1   | Independent design of on-die and in-controller codes                     | 120 |

|     | 6.7.2   | Using Stronger On-die Codes                                              | 120 |

|     | 6.7.3   | Using Stronger In-controller ECC                                         | 121 |

|     | 6.7.4   | Comparison with Past Works                                               | 121 |

|     | 6.7.5   | Accommodating Wider Data Widths                                          | 122 |

| 6.8 | Conclu  | usion                                                                    | 123 |

| Cor | nrossia | on with Multi ECC, Enhanced Error Desilionar for Magnetic Memories       | 104 |

|     | -       | on with Multi-ECC: Enhanced Error Resiliency for Magnetic Memories       |     |

| 7.1 | Introdu | uction                                                                   | 125 |

7

| 7.2 | Backg    | round                                                                    |

|-----|----------|--------------------------------------------------------------------------|

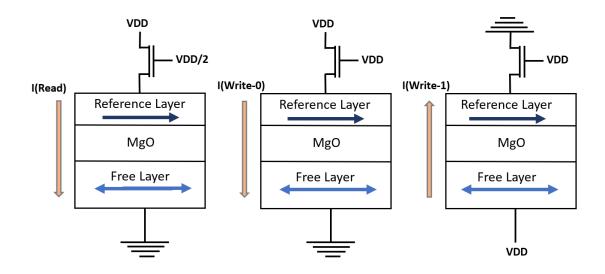

|     | 7.2.1    | STT-RAM Basics                                                           |

|     | 7.2.2    | Previous Work On STT-RAM Reliability                                     |

|     | 7.2.3    | Previous Work On Cache Compression                                       |

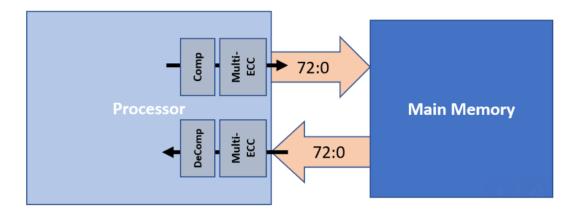

| 7.3 | Our sc   | cheme - Compression with Multi-ECC (CME)                                 |

|     | 7.3.1    | Overall Architecture                                                     |

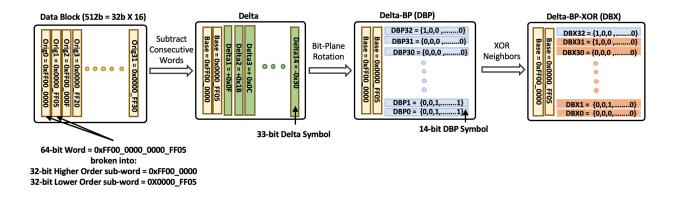

|     | 7.3.2    | Cache Line Compression using modified BPC and an optional Hamming        |

|     |          | Weight Aware Inversion Coding                                            |

|     | 7.3.3    | Multi-ECC on Compressed Cache Line                                       |

|     | 7.3.4    | Additional Tag Bits and Memory Organization                              |

| 7.4 | Evalua   | ation Methodology                                                        |

| 7.5 | Result   | s                                                                        |

|     | 7.5.1    | Reduction in Hamming Weight                                              |

|     | 7.5.2    | Reduction in block failure probability                                   |

|     | 7.5.3    | Hardware Overhead of Multi-ECC Scheme                                    |

|     | 7.5.4    | System Performance Evaluation                                            |

| 7.6 | Discus   | ssion                                                                    |

|     | 7.6.1    | Using an Alternative Compression Scheme                                  |

|     | 7.6.2    | Variable Scrubbing Interval                                              |

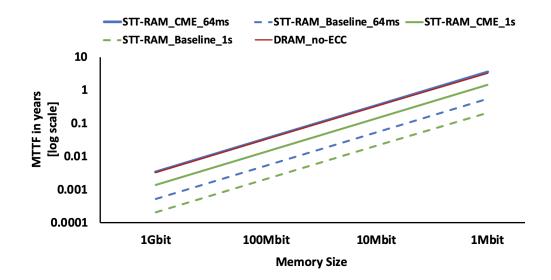

|     | 7.6.3    | Using STT-RAM as non-ECC DRAM Alternative - Reliability Point of View161 |

| 7.7 | Conclu   | usion                                                                    |

| PCN | /I-Dupli | icate: Achieving DRAM-like PCM By Trading Off Capacity For Latency 164   |

| 8.1 | Introd   | uction                                                                   |

| 8.2 | Backg    | round                                                                    |

8

|     | 8.2.1                                  | PCM Basics                                                                                                                                                                                                                         | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | 8.2.2                                  | DRAM vs. PCM                                                                                                                                                                                                                       | <i>i</i> 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 8.3 | Motiva                                 | tion and Past Work                                                                                                                                                                                                                 | 0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     | 8.3.1                                  | PCM-ECC Overview: Combination of Previously Proposed Improvements 17                                                                                                                                                               | '1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     | 8.3.2                                  | Performance Analysis: PCM-ECC vs. DRAM                                                                                                                                                                                             | '2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     | 8.3.3                                  | Motivation to achieve near-DRAM latency                                                                                                                                                                                            | '3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 8.4 | Bridgir                                | ng the Performance Gap Between PCM and DRAM                                                                                                                                                                                        | ′4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

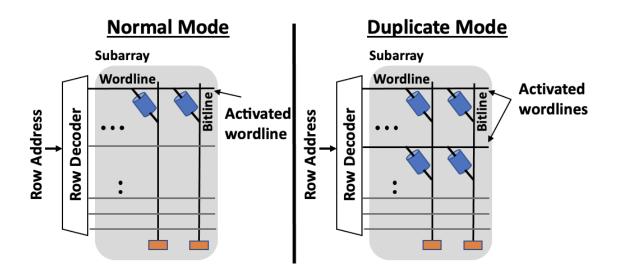

|     | 8.4.1                                  | PCM-Duplicate Overview: PCM with DRAM-like read latency 17                                                                                                                                                                         | ′4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     | 8.4.2                                  | PCM-Duplicate Implementation                                                                                                                                                                                                       | '5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     | 8.4.3                                  | Reducing Write Time and Energy using ECC and Infrequent Refresh 17                                                                                                                                                                 | '5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

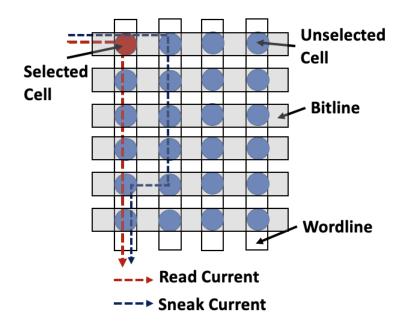

|     | 8.4.4                                  | Sneak Current in Crossbar Architecture                                                                                                                                                                                             | '6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 8.5 | Evalua                                 | tion Methodology                                                                                                                                                                                                                   | '8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 8.6 | Results                                |                                                                                                                                                                                                                                    | '9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

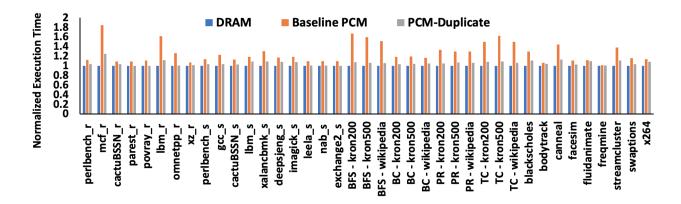

|     | 8.6.1                                  | Using PCM-Duplicate as Main Memory                                                                                                                                                                                                 | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

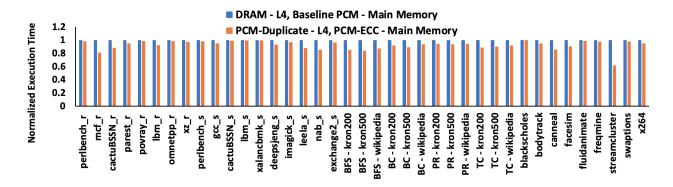

|     | 8.6.2                                  | Using PCM-Duplicate as Last Level Cache instead of DRAM 18                                                                                                                                                                         | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     | 8.6.3                                  | Enabling Lightweight Main Memory Based Persistence                                                                                                                                                                                 | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 8.7 | Conclu                                 | sion                                                                                                                                                                                                                               | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Con | clusion                                |                                                                                                                                                                                                                                    | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 9.1 | Overvi                                 | ew of Contributions                                                                                                                                                                                                                | \$4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     | 9.1.1                                  | FaultLink and SAME-Infer                                                                                                                                                                                                           | \$4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     | 9.1.2                                  | SDELC                                                                                                                                                                                                                              | \$5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     | 9.1.3                                  | Parity++                                                                                                                                                                                                                           | \$5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     | 9.1.4                                  | COMET                                                                                                                                                                                                                              | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | 9.1.5                                  | Compression with Multi-ECC                                                                                                                                                                                                         | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | 8.4<br>8.5<br>8.6<br>8.7<br><b>Con</b> | 8.2.2<br>8.3 Motiva<br>8.3.1<br>8.3.2<br>8.3.3<br>8.4 Bridgin<br>8.4.1<br>8.4.2<br>8.4.3<br>8.4.3<br>8.4.4<br>8.5 Evalua<br>8.6 Results<br>8.6.1<br>8.6.2<br>8.6.3<br>8.7 Conclu<br>9.1 Overvi<br>9.1.1<br>9.1.2<br>9.1.3<br>9.1.4 | 8.2.2       DRAM vs. PCM       16         8.3       Motivation and Past Work       17         8.3.1       PCM-ECC Overview: Combination of Previously Proposed Improvements       17         8.3.2       Performance Analysis: PCM-ECC vs. DRAM       17         8.3.3       Motivation to achieve near-DRAM latency       17         8.4       Bridging the Performance Gap Between PCM and DRAM       17         8.4.1       PCM-Duplicate Overview: PCM with DRAM-like read latency       17         8.4.2       PCM-Duplicate Implementation       17         8.4.3       Reducing Write Time and Energy using ECC and Infrequent Refresh       17         8.4.4       Sneak Current in Crossbar Architecture       17         8.5       Evaluation Methodology       17         8.6       Results       17         8.6.1       Using PCM-Duplicate as Main Memory       18         8.6.2       Using PCM-Duplicate as Last Level Cache instead of DRAM       18         8.6.3       Enabling Lightweight Main Memory Based Persistence       18         8.7       Conclusion       18         9.1       Overview of Contributions       18         9.1.1       FaultLink and SAME-Infer       18         9.1.2       SDELC       18 |

|         | 9.1.6   | PCM-Duplicate                                                         |

|---------|---------|-----------------------------------------------------------------------|

| 9.2     | Directi | ions for Future Work                                                  |

|         | 9.2.1   | Extensions Of Techniques Proposed In This Dissertation                |

|         | 9.2.2   | Asymmetric Error Correction In Non-Volatile Memories                  |

|         | 9.2.3   | Making Neuromorphic Computing Robust                                  |

|         | 9.2.4   | Improving Reliability and Endurance in Hybrid Main Memory Systems 189 |

|         | 9.2.5   | Enabling Shared-Bus Read/Write in Memories for Performance and Energy |

|         |         | Efficiency                                                            |

|         | 9.2.6   | Combining Memory Reliability with Security                            |

| Referen | ices    |                                                                       |

## LIST OF FIGURES

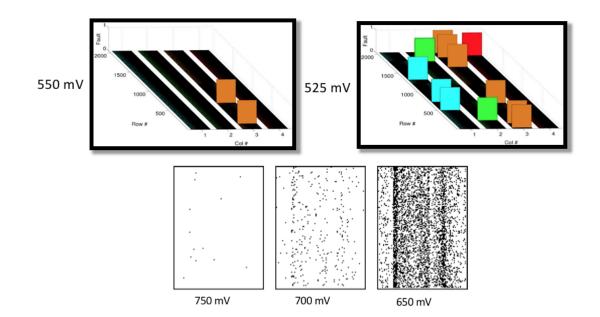

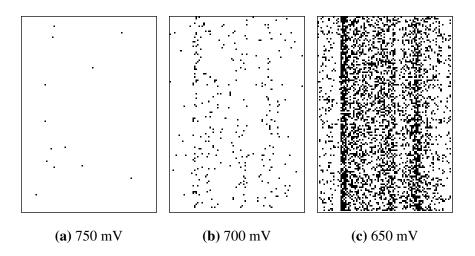

| 1.1 | Faults in two SRAM based scratchpad memories at different voltages                                                                                                                                                                                                                                                                                          | 4  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

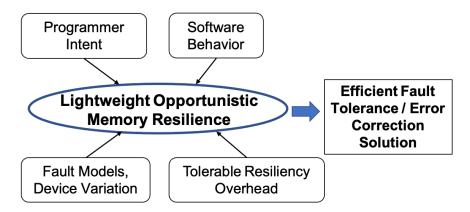

| 1.2 | High level concept of Lightweight Opportunistic Memory Resilience                                                                                                                                                                                                                                                                                           | 8  |

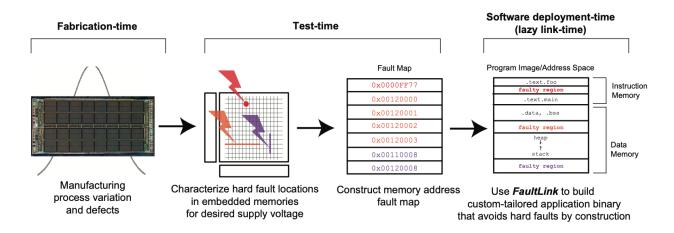

| 2.1 | Our high-level approach to tolerating hard faults in on-chip scratchpad memories                                                                                                                                                                                                                                                                            | 15 |

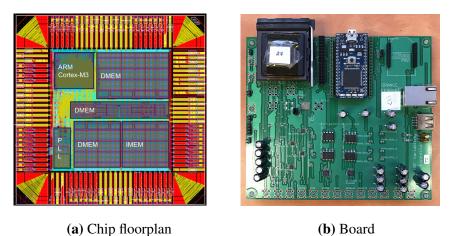

| 2.2 | Test chip and board used to collect hard fault maps for FaultLink                                                                                                                                                                                                                                                                                           | 16 |

| 2.3 | Measured voltage-induced hard fault maps of the 176 KB data memory for one test chip. Black pixels represent faulty byte locations.                                                                                                                                                                                                                         | 17 |

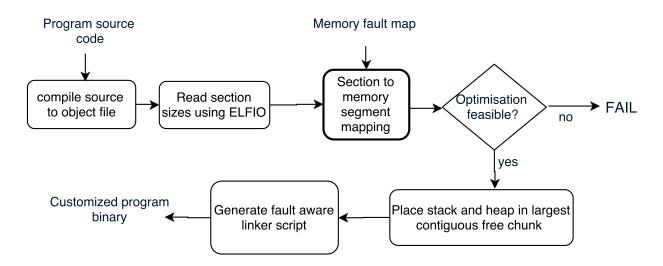

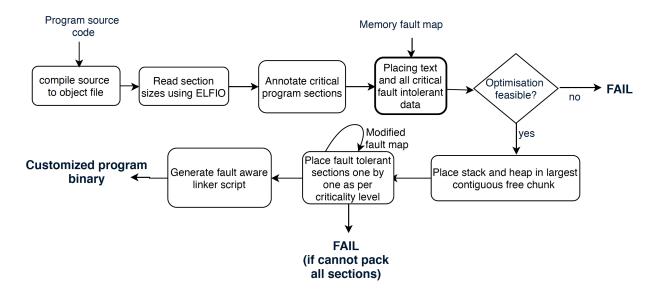

| 2.4 | FaultLink procedure: given program source code and a memory fault map, produce<br>a per-chip custom binary executable that will work in presence of known hard fault<br>locations in the SPMs.                                                                                                                                                              |    |

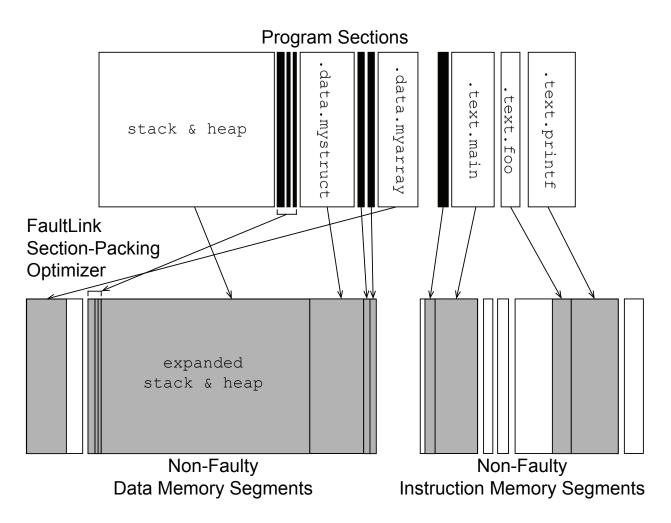

| 2.5 | FaultLink attempts to pack contiguous program sections into contiguous disjoint seg-<br>ments of non-faulty memory. Gray memory segments are occupied by mapped sections,<br>while white segment areas are free space. The depicted gaps between some of the<br>gray/white boxes indicate faulty memory regions that are not available for section-packing. | 20 |

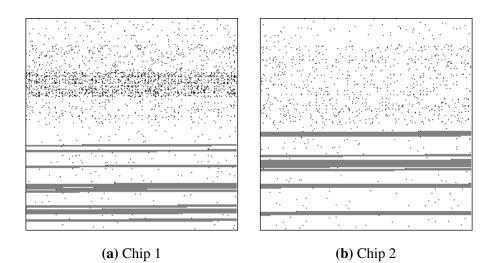

| 2.6 | Result from applying FaultLink to the sha benchmark for two real test chips' 64 KB instruction memory at 650 mV.                                                                                                                                                                                                                                            | 22 |

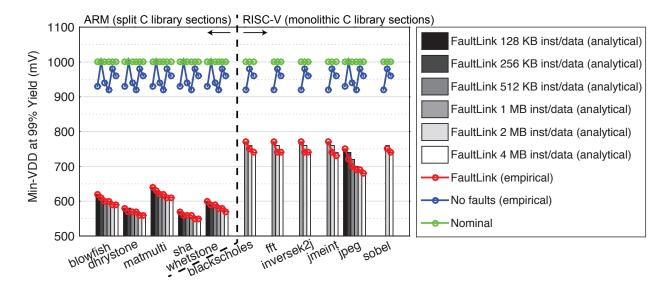

| 2.7 | Achievable min-VDD for FaultLink at 99% yield. Bars represent the analytical lower<br>bound from Equation 2.2 and circles represent our actual results using Monte Carlo<br>simulation for 100 synthetic fault maps.                                                                                                                                        | 24 |

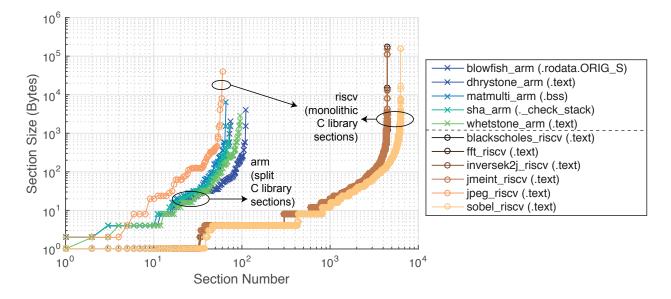

| 2.8 | Distribution of program section sizes. Packing the largest section into a non-faulty contiguous memory segment is the most difficult constraint for FaultLink to satisfy and limits min-VDD.                                                                                                                                                                | 25 |

| 3.1 | SAME-Infer procedure: given source code of a DL network and a memory fault map, produce a per-chip custom binary executable that will work in presence of known hard fault locations in the SPMs.                                                                                                                                                           | 34 |

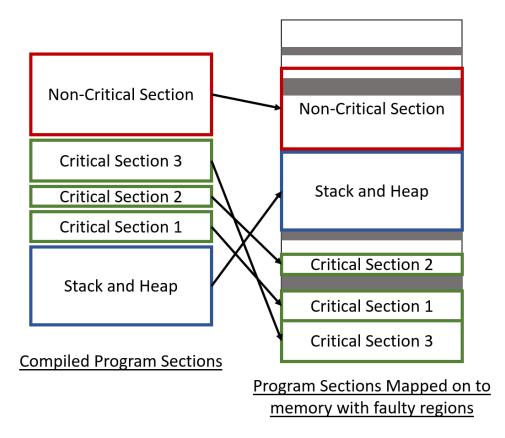

| 3.2  | A sample section packing solution provided by SAME-Infer. The critical sections are          |    |

|------|----------------------------------------------------------------------------------------------|----|

|      | placed in fault free memory segments while the non-critical sections intersect with          |    |

|      | faults (grey regions represent fault locations). The stack and heap is placed in the largest |    |

|      | non faulty contiguous memory segment remaining after placing the critical sections           | 37 |

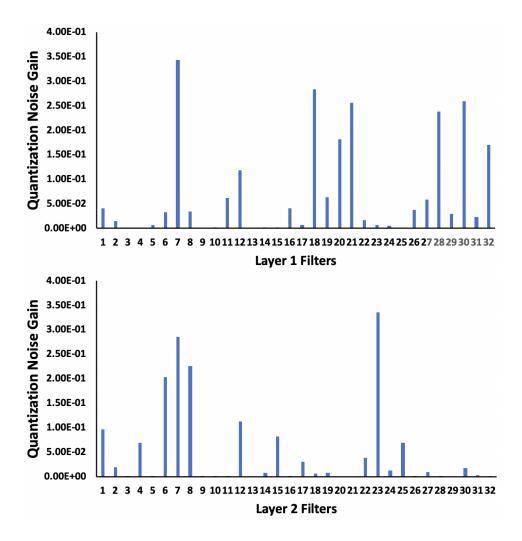

| 3.3  | Weight quantization noise gain per filter - layers 1 and 2 of a nine layer CNN               | 38 |

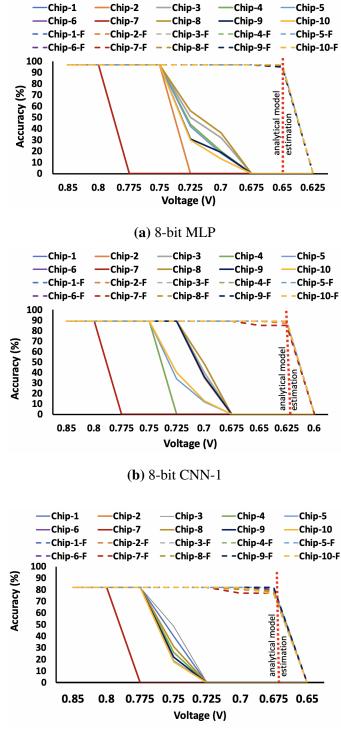

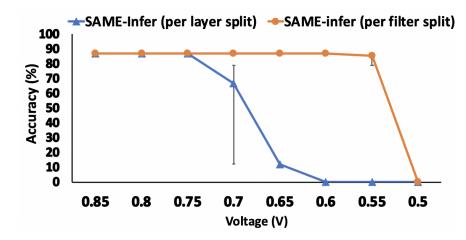

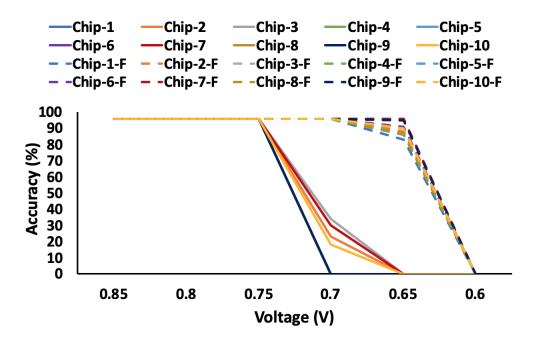

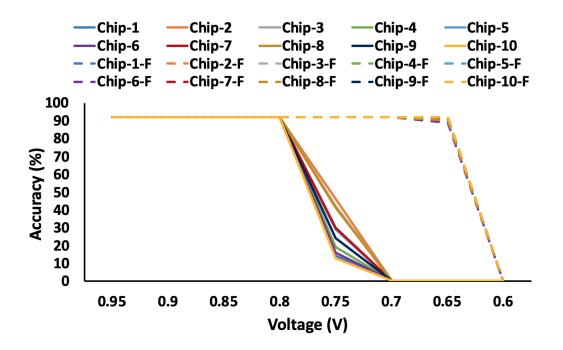

| 3.4  | Change in inference accuracy with voltage. Dotted lines are results with SAME-Infer          |    |

|      | while the solid lines are without SAME-Infer.                                                | 43 |

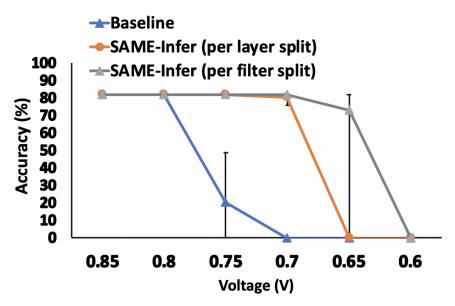

| 3.5  | Change in three layer CNN-2 inference accuracy as voltage on the test chips is scaled        |    |

|      | down. The result shown here is the average accuracy across 10 test chips for each test       |    |

|      | case. The test cases are - (1) without SAME-Infer (2) with SAME-Infer and layerwise          |    |

|      | monolithic weight sections (3) when the weight sections are split up on per filter basis     |    |

|      | in every layer.                                                                              | 45 |

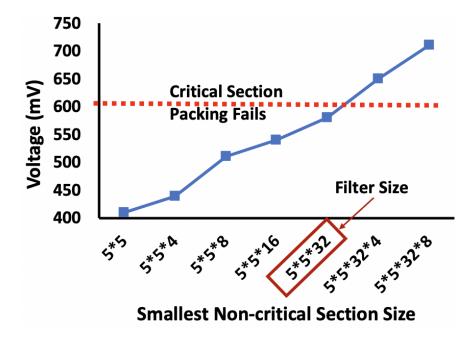

| 3.6  | Achievable min-VDD as the smallest non-critical section size is reduced for the three        |    |

|      | layer CNN. The min-VDD is obtained using Equation 2.2 while the min-VDD for                  |    |

|      | critical section is obtained from the test chip results                                      | 46 |

| 3.7  | Change in nine layer CNN inference accuracy as voltage on the synthetic chips is scaled      |    |

|      | down. The result shown here is the average accuracy across 10 synthetic chips for each       |    |

|      | test case. The test cases are - (1) with SAME-Infer and layerwise monolithic weight          |    |

|      | sections (2) when the weight sections are split up on per filter basis in every layer        | 47 |

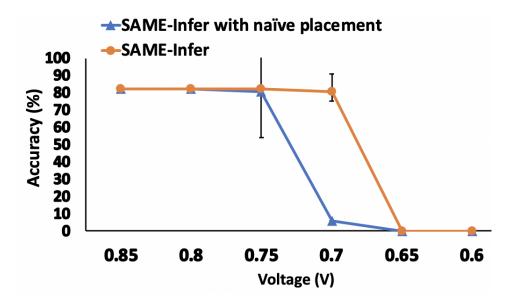

| 3.8  | Change in the three layer CNN-2 inference accuracy as voltage on the test chips is           |    |

|      | scaled down. The result shown here is the average accuracy across 5 test chips for           |    |

|      | each test case. The test cases are - (1)when the fault tolerant sections are naively         |    |

|      | placed (greedy placement) in the memory while the critical text sections are placed in       |    |

|      | non-faulty memory regions (2) SAME-Infer with criticality aware placement                    | 48 |

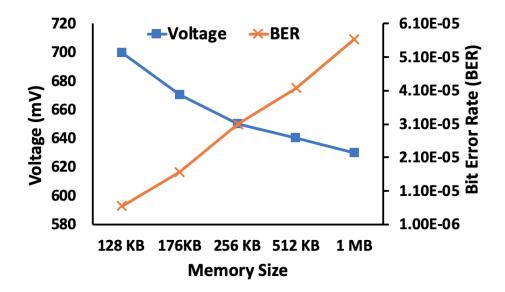

| 3.9  | Voltage reduction or BER tolerance estimation by the analytical model for the three          |    |

|      | layer CNN-2 on different memory sizes                                                        | 49 |

| 3.10 | Change in dense binarized MLP inference accuracy as voltage on the test chips is scaled      |    |

|      | down                                                                                         | 50 |

| 3.11 | Change in sparse binarized MLP inference accuracy as voltage on the test chips is        |    |

|------|------------------------------------------------------------------------------------------|----|

|      | scaled down                                                                              | 50 |

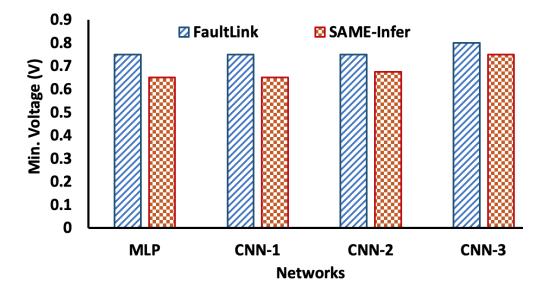

| 3.12 | SAME-Infer achieves lower min voltage as compared to FaultLink [1] with negligible       |    |

|      | impact on accuracy because SAME-Infer allows intersection with faults in the less        |    |

|      | critical LSB bits of non-critical fault tolerant data sections.                          | 51 |

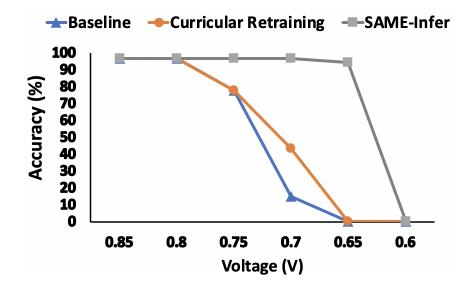

| 3.13 | MLP (2 layer) with MNIST - average accuracy measured across 10 chips for each test       |    |

|      | case - (1) Baseline (2) Curricular Retraining (3) SAME-Infer                             | 52 |

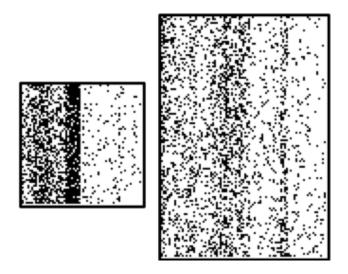

| 3.14 | Hard Fault Map of the 64KB instruction memory (left) and the 176KB data memory           |    |

|      | (right) of a test chip. The black dots represent the faulty byte locations               | 53 |

| 4.1  | Architectural support for SDELC on an microcontroller-class embedded system              | 63 |

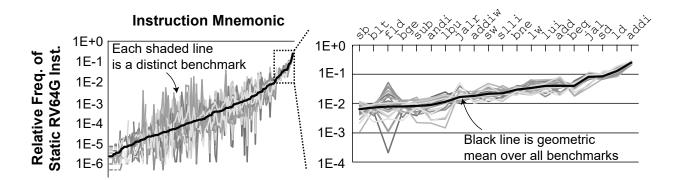

| 4.2  | The relative frequencies of static instructions roughly follow power law distributions.  |    |

|      | Results shown are for RISC-V with 20 SPEC CPU2006 benchmarks; we observed                |    |

|      | similar trends for MIPS and Alpha, as well as dynamic instructions                       | 67 |

| 4.3  | Average rate of recovery using SDELC from single-bit soft faults in instruction and      |    |

|      | data memory. <i>r</i> is the number of parity bits in the UL-ELC construction            | 70 |

| 4.4  | Sensitivity of SDELC instruction recovery to the actual position of the single-bit fault |    |

|      | with the $r = 3$ UL-ELC construction                                                     | 71 |

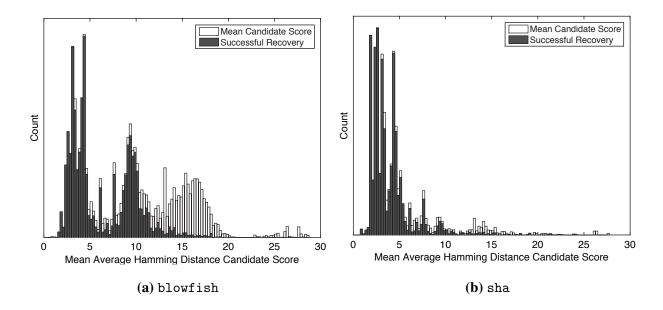

| 4.5  | Sensitivity of SDELC data recovery to the mean candidate Hamming distance score for      |    |

|      | two benchmarks and $r = 1$ parity code                                                   | 72 |

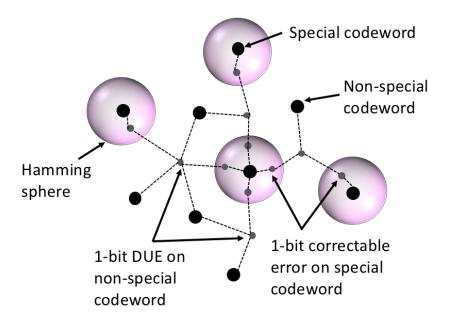

| 5.1  | Conceptual Illustration of Parity++ for 1-bit error                                      | 79 |

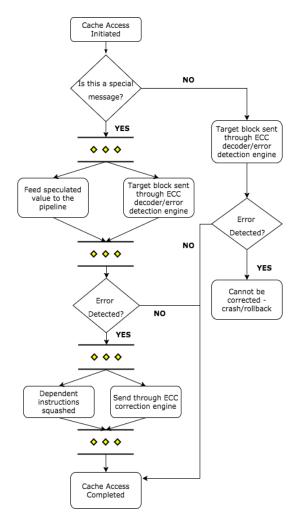

| 5.2  | Flow of read operation in cache with memory speculation and Parity++ protection          |    |

|      | schemes                                                                                  | 83 |

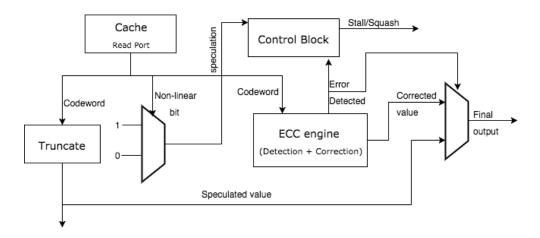

| 5.3  | Cache architecture to implement Parity++ with memory speculation                         | 84 |

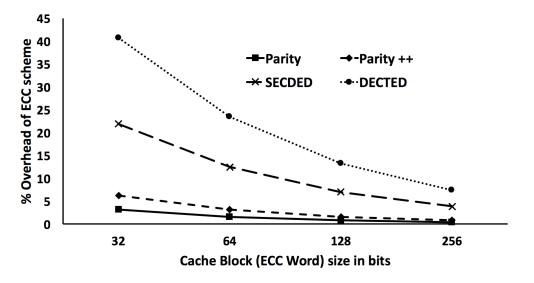

| 5.4  | Storage overhead of different commonly used ECC schemes along with our scheme            |    |

|      | Parity++                                                                                 | 86 |

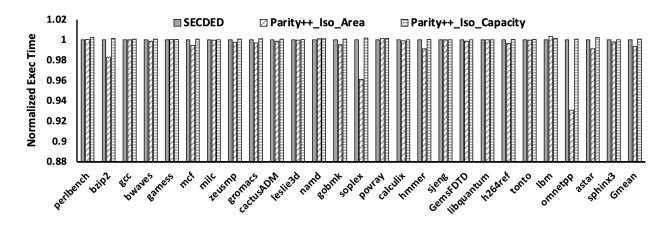

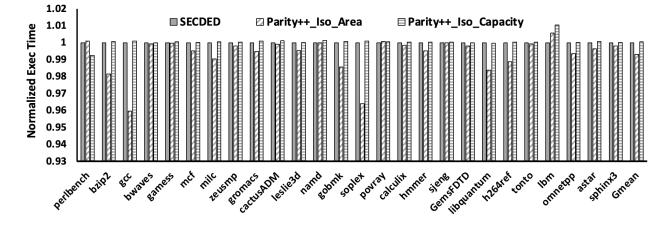

| 5.5 | Comparing Normalized Execution Time of Processor-I with SECDED and Parity++             |

|-----|-----------------------------------------------------------------------------------------|

|     | (with memory speculation)                                                               |

| 5.6 | Comparing Normalized Execution Time of Processor-II with SECDED and Parity++            |

|     | (with memory speculation)                                                               |

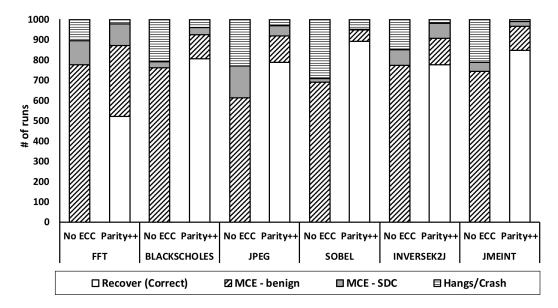

| 5.7 | Output quality of AxBench benchmarks for memory with no ECC vs with Parity++ 91         |

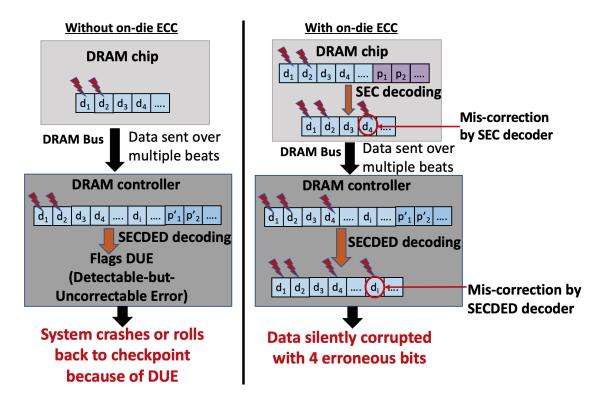

| 6.1 | Example showing the difference when a DBE occurs in DRAMs with and without              |

|     | on-die SEC. Both systems have in-controller SECDED. Assumption: data and parity         |

|     | bits that get decoded in the controller in one cycle are sent from the same DRAM chip   |

|     | across multiple beats                                                                   |

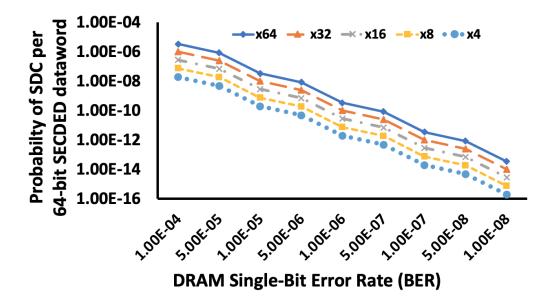

| 6.2 | Probability of SDC every 64-bits of SCEDED dataword read from memory when a             |

|     | double-bit error occurs in a system with (136,128) on-die SEC and (72,64) in-controller |

|     | SECDED coding schemes for different bit error rates and data access protocols is shown  |

|     | here                                                                                    |

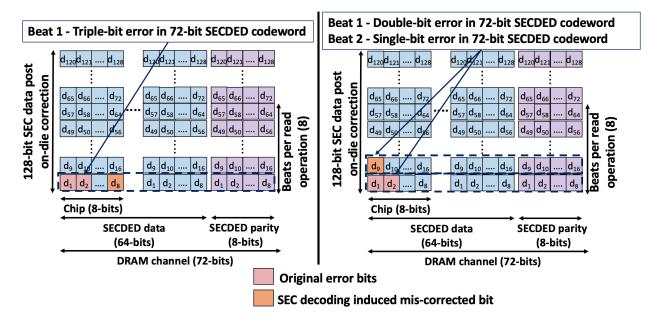

| 6.3 | Example showing how steering the miscorrected bit to a different beat transfer boundary |

|     | during SEC decoding prevents the SECDED decoder from encountering the problematic       |

|     | triple-bit error within the same 72-bit codeword                                        |

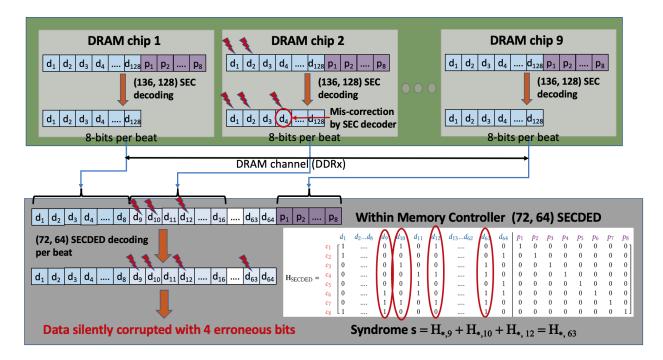

| 6.4 | Example showing SDC occurring due to miscorrection introduced by on-die ECC. We         |

|     | have considered the SEC construction provided in Section 6.3.1 where the sum of         |

|     | columns 1 and 2 in the $H_{example}$ matrix is equal to column 4                        |

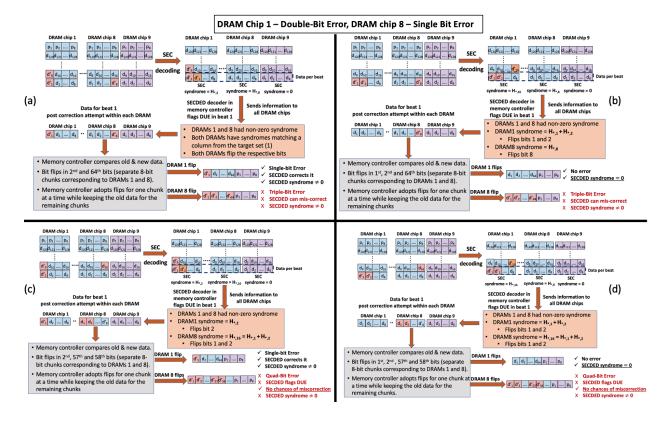

| 6.5 | The different scenarios possible when one chip has double-bit error and another chip    |

|     | has single bit error that aligns in a way leading to multiple DRAM chips modifying      |

|     | data during DBE correction                                                              |

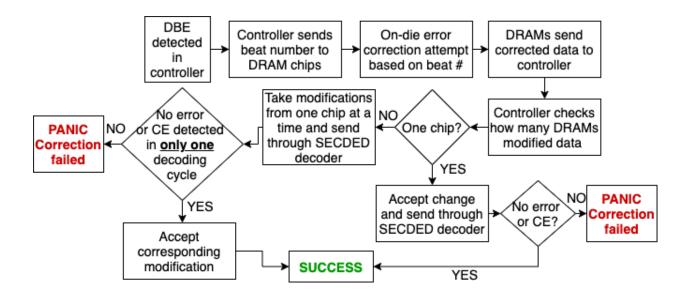

| 6.6 | Step-by-step COMET double-bit error correction mechanism                                |

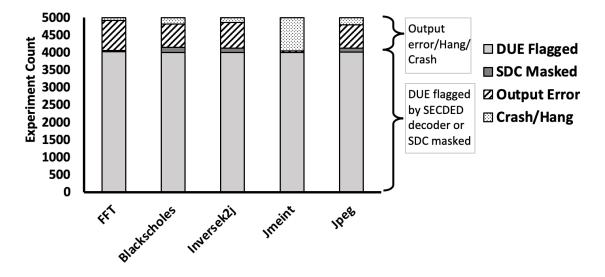

| 6.7 | The impact of on-die ECC induced SDC in the event of double-bit error on the program    |

|     | behavior when running applications from the AxBench suite                               |

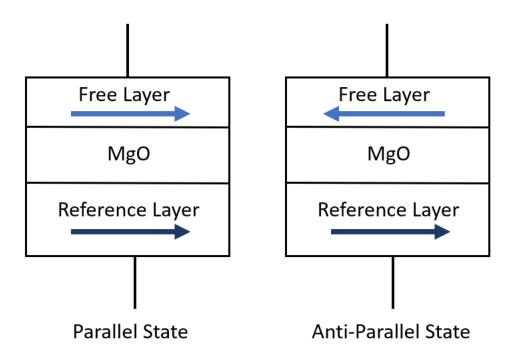

| 7.1 | Schematic of STT-RAM showing the anti-parallel and parallel states                      |

| 7.2  | Read and write mechanisms for STT-RAM is shown here                                        |

|------|--------------------------------------------------------------------------------------------|

| 7.3  | Processor Memory system architecture with CME                                              |

| 7.4  | An overview of the modified Bit-Plane Transformation scheme                                |

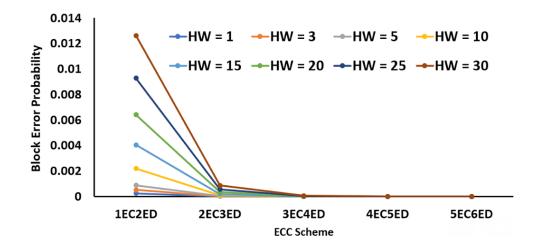

| 7.5  | Block failure probability is shown for blocks with different Hamming weight (HW) and       |

|      | ECC schemes. The probability of $1 \rightarrow 0$ bit-flip is considered to be $10^{-5}$   |

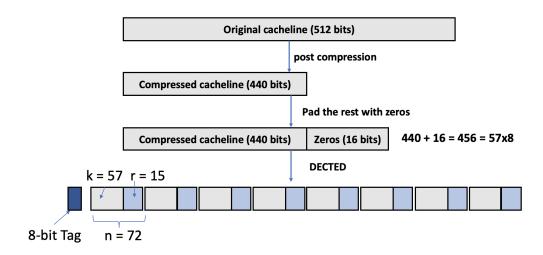

| 7.6  | An example of CME scheme where the compressed cache line size is 440 bits 139              |

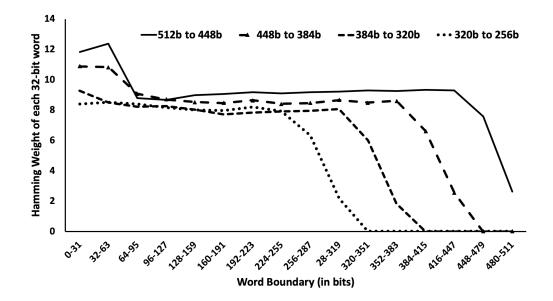

| 7.7  | Average hamming weight of each 32-bit word of all cache lines within each bucket.          |

|      | Uniform bucket size of 64 bits were used for all cache lines whose final size lies between |

|      | 512 bits and 256 bits                                                                      |

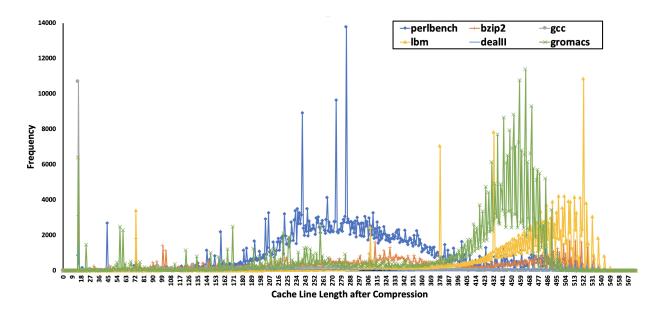

| 7.8  | Distribution of cache line length after compression of six benchmarks from the SPEC2006    |

|      | suite                                                                                      |

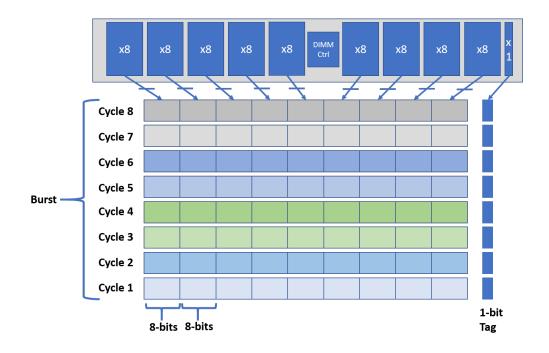

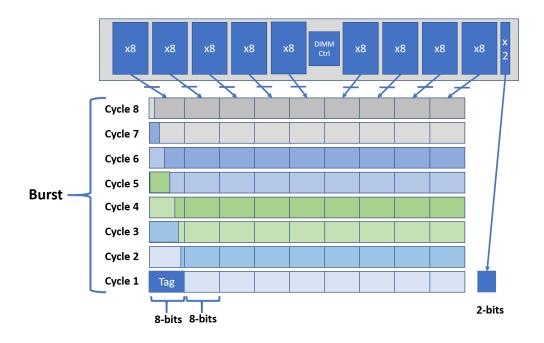

| 7.9  | CME-Scheme 1 is shown where tag bits are stored in an x1 DRAM chip. One tag bit is         |

|      | read every cycle in burst. Different colors represent different 72-bit ECC words in a      |

|      | 512-bit cache line                                                                         |

| 7.10 | CME-Scheme 2 where tag bits for ECC scheme used are stored in an x8 DRAM. The              |

|      | tag bit and it's parity representing compression are stored in an x2 DRAM chip and are     |

|      | brought in the same burst. Different colors represent different 72-bit ECC words in a      |

|      | 512-bit cache line                                                                         |

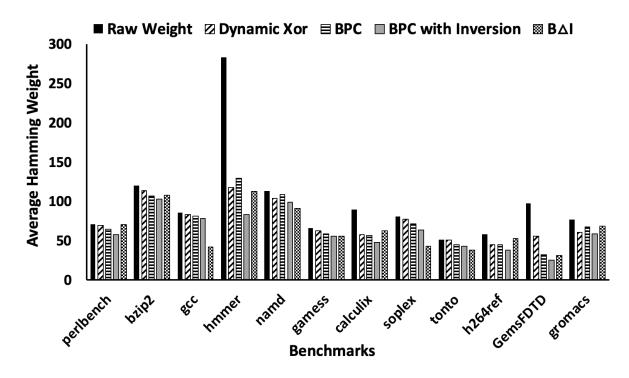

| 7.11 | Comparison of average Hamming weight of original cache line, BPC, $B\Delta I$ and $DBX$    |

|      | schemes                                                                                    |

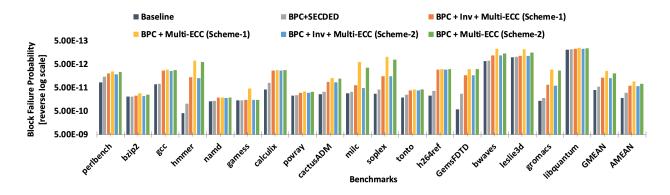

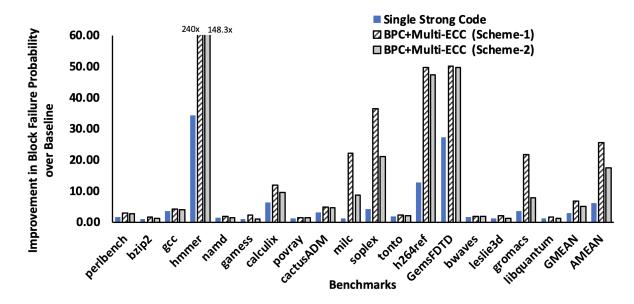

| 7.12 | Reduction in block failure probability induced due to write/read/retention errors for      |

|      | the first design point [2] is shown. The y-axis is in logarithmic scale (reverse order).   |

|      | The geometric mean and arithmetic mean of the improvement of CME Schemes over              |

|      | baseline is shown in plot                                                                  |

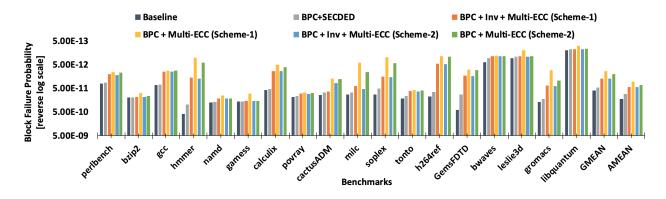

| 7.13 | Reduction in block failure probability induced due to write/read/retention errors for the  |

|------|--------------------------------------------------------------------------------------------|

|      | second design point [3] is shown. The y-axis is in logarithmic scale (reverse order).      |

|      | The geometric mean and arithmetic mean of the improvement of CME Schemes over              |

|      | baseline is shown in plot                                                                  |

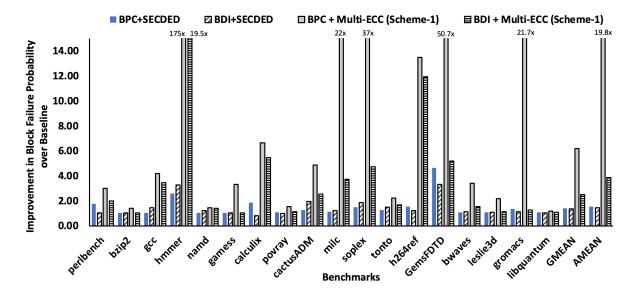

| 7.14 | Improvement of CME Schemes 1 and 2 over a scheme that provides uniform (72,57)             |

|      | DECTED for all compressible cache lines and (72,64) SECDED if in-compressible 157          |

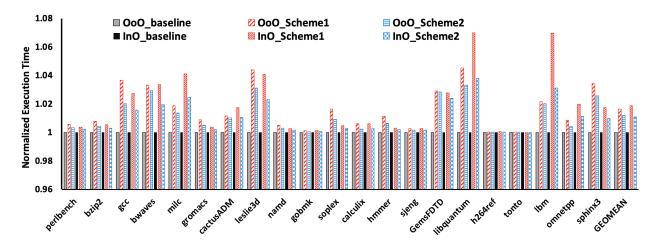

| 7.15 | Comparing Normalized Execution Time of two systems (one with 8 InO cores and               |

|      | another with a single OoO core), both having three protection schemes: baseline            |

|      | (72,64)SECDED, CME Scheme-1 and CME Scheme-2. InO and OoO results are                      |

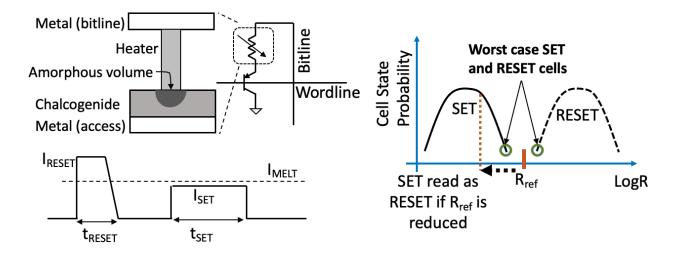

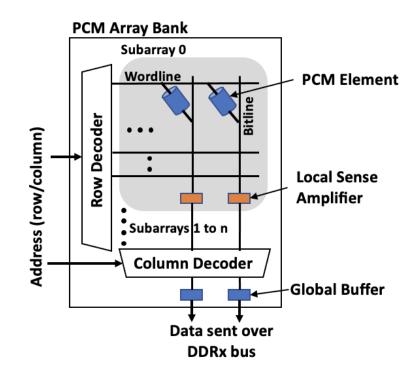

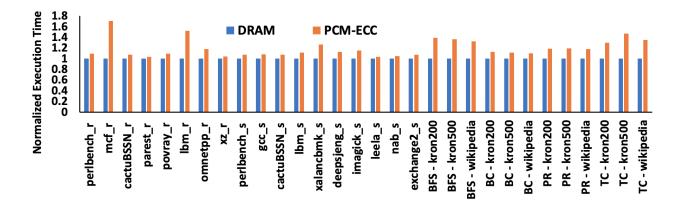

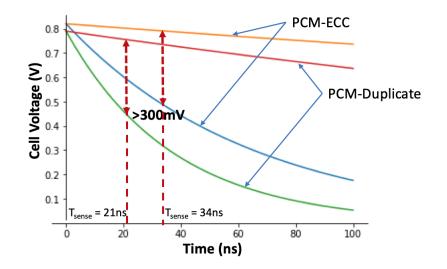

|      | normalized to their respective baselines                                                   |