# UC Irvine UC Irvine Electronic Theses and Dissertations

## Title

Preparation of Power Distribution System for High Penetration of Renewable Energy

Permalink https://escholarship.org/uc/item/2t6476kj

Author Khoshkbar-Sadigh, Arash

Publication Date 2014

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA, IRVINE

Preparation of Power Distribution System for High Penetration of Renewable Energy Part I. Dynamic Voltage Restorer for Voltage Regulation Pat II. Distribution Circuit Modeling and Validation

#### DISSERTATION

submitted in partial satisfaction of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

#### in Electrical Engineering

by

Arash Khoshkbar Sadigh

Dissertation Committee: Professor Keyue Smedley, Chair Professor Michael Green Professor Pai H. Chou

© 2014 Arash Khoshkbar Sadigh

## **DEDICATION**

То

Sima who is not just my wonderful wife, but also the greatest friend I could ever have,

Our exuberant, sweet, and kind-hearted little son, Elvin, to recharge and revitalize my mind and spirit every day after coming back home from school,

and

My always encouraging parents, Fatemeh and Jafar, for teaching me love, generosity and good manners.

# TABLE OF CONTENTS

| LIST OF FIGURESvi                                                    |     |  |

|----------------------------------------------------------------------|-----|--|

| LIST OF TABLES xii                                                   |     |  |

| ACKNOWLEDGMENTS xiii                                                 |     |  |

| CURRICULUM VITAE                                                     | xiv |  |

| ABSTRACT OF THE DISSERTATION                                         | xvi |  |

| Chapter 1: Dynamic Voltage Restorer (DVR)                            | 1   |  |

| 1.1. Introduction                                                    | 2   |  |

| 1.2. Review of Voltage Sag Compensation Methods                      | 6   |  |

| 1.2.1. In-Phase Voltage Sag Compensation Method                      | 6   |  |

| 1.2.2. Pre-Sag Voltage Compensation Method                           | 9   |  |

| 1.2.3. Energy-Minimized Voltage Compensation Method                  | 11  |  |

| 1.2.4. Hybrid Voltage Compensation Method                            | 21  |  |

| 1.3. Review of Configurations to Support Active Power at DVR DC Link | 25  |  |

| 1.3.1. Capacitor Supported DVR                                       |     |  |

| 1.3.2. Battery Supported DVR                                         |     |  |

| 1.3.3. Diode Rectifier or Shunt Converter Based DVR                  |     |  |

| 1.4. Effect of Upstream Step-Down Transformer                        |     |  |

| 1.5. DVR Reference Voltage Determination:                            |     |  |

| 1.6. Proposed DVR configuration                                      | 41  |  |

| 1.7. Conclusion                                                      | 57  |  |

| 1.8. References                                                      | 59  |  |

| Chapter 2: Voltage Sag Detection65                                   |     |  |

| 2.1. Introduction                                                    |     |  |

| 2.2. Review of Voltage Sag Detection Methods                         | 68  |  |

| 2.2.1. Peak Value Monitoring (PVM)                                   | 68  |  |

| 2.2     | 2.2. RMS Calculation                                                                                  | 69             |

|---------|-------------------------------------------------------------------------------------------------------|----------------|

| 2.2     | 2.3. D/Q Transformation (DQT)                                                                         | 70             |

| 2.2     | 2.4. Rectified Voltage (RV)                                                                           | 71             |

| 2.2     | 2.5. Wavelet Transform (WT)                                                                           | 72             |

| 2.2     | 2.6. Kalman Filtering (KF)                                                                            | 73             |

| 2.2     | 2.7. Hybrid Methods                                                                                   | 74             |

| 2.3.    | Important Criteria for Design and Evaluation of Voltage Sag Detection Method                          | 77             |

| 2.4.    | Proposed Voltage Sag Detection Methods                                                                | 79             |

| 2.4     | 4.1. Non-Harmonic Voltage Sag Detection Method                                                        | 80             |

| 2.4     | 4.2. Harmonically-Distorted Voltage Sag Detection Method                                              | 81             |

| 2.5.    | Simulation Results                                                                                    | <del>)</del> 3 |

| 2.5     | 5.1. Non-Harmonic Voltage Sag Detection Method                                                        | 93             |

| 2.5     | 5.2. Harmonically-Distorted Voltage Sag Detection Method                                              | 96             |

| 2.6.    | Experimental Results                                                                                  | )4             |

| 2.6     | 6.1. Non-Harmonic Voltage Sag Detection Method                                                        | 05             |

| 2.6     | 6.2. Harmonically-Distorted Voltage Sag Detection Method1                                             | 11             |

| 2.7.    | Comparison with Other Methods                                                                         | 27             |

| 2.8.    | Conclusion                                                                                            | 31             |

| 2.9.    | References                                                                                            | 33             |

| Chapter | r 3: A Unified Platform Enabling Power System Circuit Model Da<br>Transfer among Different Software14 |                |

| 3.1.    | Introduction                                                                                          | 41             |

| 3.2.    | Proposed Unified Platform Based on Spreadsheet14                                                      | 43             |

| 3.3.    | Transferring Power System Circuit Model Data From Unified Platform in ETAP14                          |                |

| 3.4.    | Transferring Power System Circuit Model Data from Unified Platform in<br>OpenDSS                      |                |

| 3.5.    | Transferring Power System Circuit Model Data From Unified Platform in GridLAB-D                       |                |

| 3.6.    | Transferring Power System Circuit Model Data From Unified Platform into DE                            |                |

| 3.7. Simulation Results                                                                       | 167 |

|-----------------------------------------------------------------------------------------------|-----|

| 3.8. Discussion                                                                               | 171 |

| 3.9. Conclusion                                                                               | 173 |

| 3.10. References                                                                              | 175 |

| Chapter 4: Investigation of Large-Scale Solar Energy Penetration in I<br>Distribution Circuit |     |

| 4.1. Introduction                                                                             | 180 |

| 4.2. Impact of Time-Varying Solar Energy Penetration                                          | 184 |

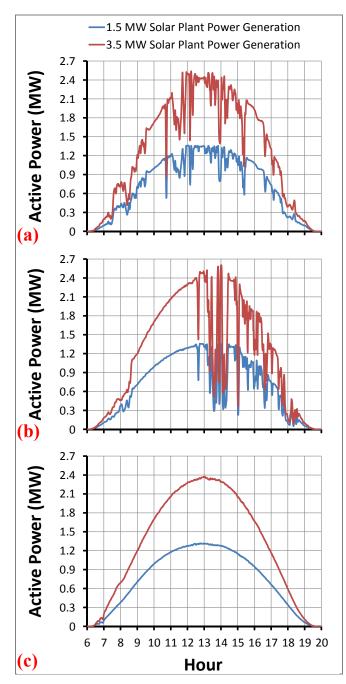

| 4.3. Modeling the Intermittency of Solar Energy                                               | 186 |

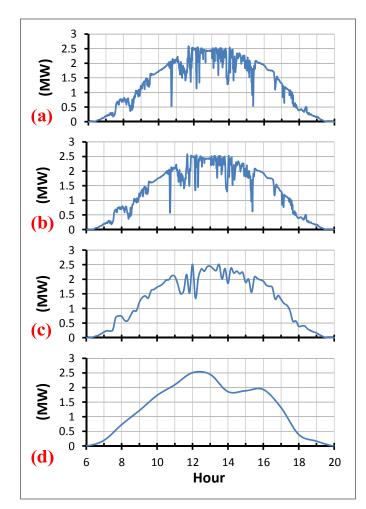

| 4.3.1. Measurement Time-Series Data Used by Model:                                            | 186 |

| 4.3.2. Time-Series Simulation                                                                 | 190 |

| 4.3.3. Circuit Model Used for Time-Series Simulation                                          | 192 |

| 4.4. Data Conversion from Random Sampling Rate to Constant Sampling Rate                      | 195 |

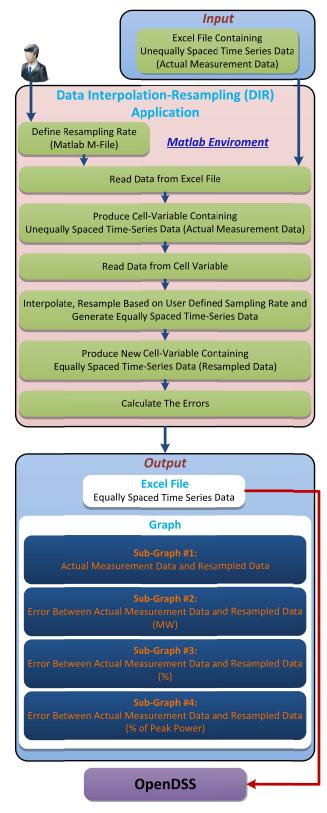

| 4.4.1. Development of Data Interpolation-Resampling (DIR) Application                         | 195 |

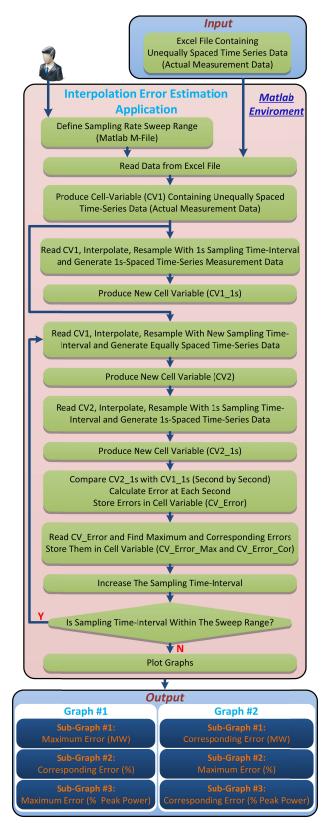

| 4.4.2. Development of Resampling Error Calculation (REC) Application                          | 199 |

| 4.5. Model Validation Considerations                                                          | 206 |

| 4.5.1. Line/Cable Modeling                                                                    | 207 |

| 4.5.2. Load Modeling                                                                          | 213 |

| 4.5.3. Solar Generation Modeling                                                              | 216 |

| 4.6. SCE Circuit Model Validation                                                             | 217 |

| 4.7. Investigation of Solar Penetration Impacts and Simulation Results                        | 224 |

| 4.8. Conclusion                                                                               | 230 |

| 4.9. References                                                                               | 233 |

## **LIST OF FIGURES**

| Page                                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

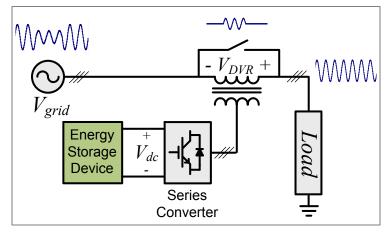

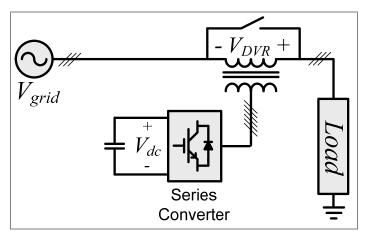

| Figure 1.1. General schematic of DVR                                                                                                                                                                  |

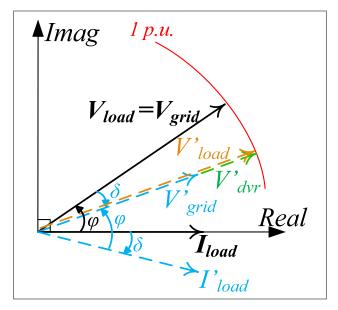

| Figure 1.2. Phasor diagram of in-phase compensation strategy                                                                                                                                          |

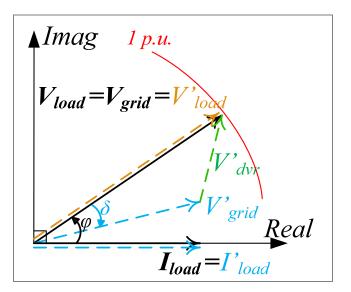

| Figure 1.3. Phasor diagram of pre-sag compensation strategy                                                                                                                                           |

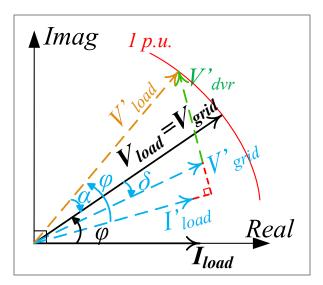

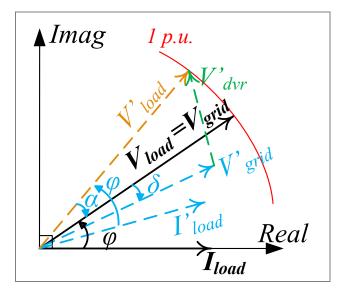

| Figure 1.4. Phasor diagram of energy minimized compensation strategy for balanced voltage sag.13                                                                                                      |

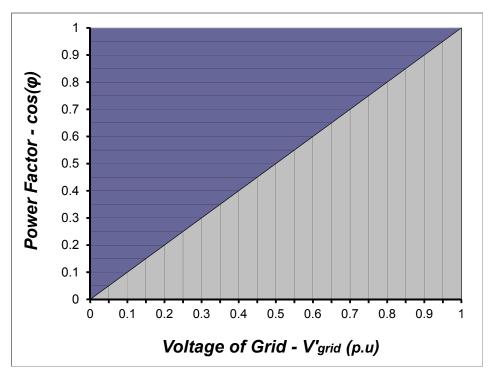

| Figure 1.5. Possibility (illustrated with gray color) and impossibility (illustrated with purple color) of avoiding active power exchanged between DVR and power grid during the balanced voltage sag |

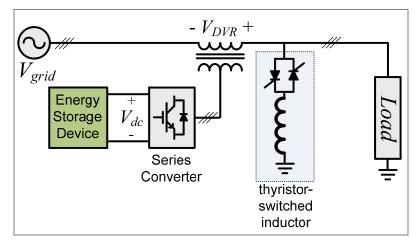

| Figure 1.6. Schematic of DVR with shunt thyristor-switched inductor to lower the power factor intentionally during the voltage sag                                                                    |

| Figure 1.7. Phasor diagram of energy minimized compensation strategy for unbalanced voltage sag                                                                                                       |

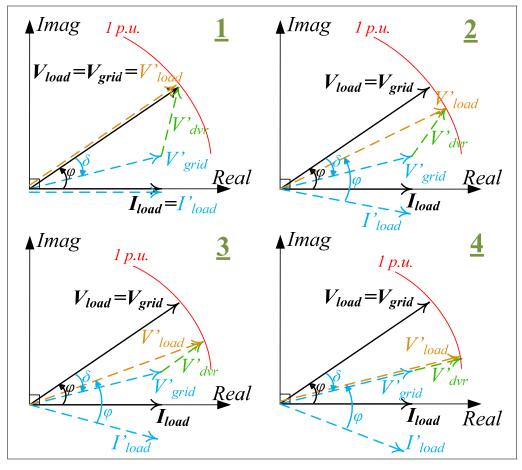

| Figure 1.8. Phasor diagram showing the procedure of hybrid voltage compensation method23                                                                                                              |

| Figure 1.9. Schematic of the capacitor supported DVR                                                                                                                                                  |

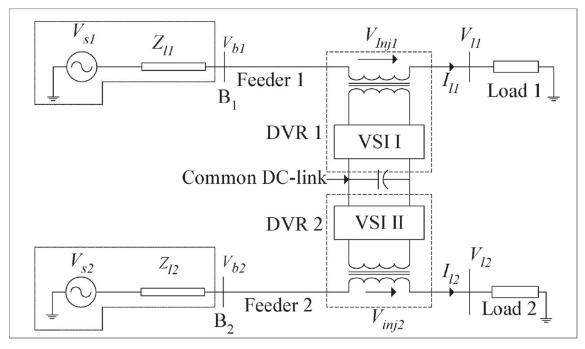

| Figure 1.10. Schematic of the interline DVR presented in [32], [48], [50]                                                                                                                             |

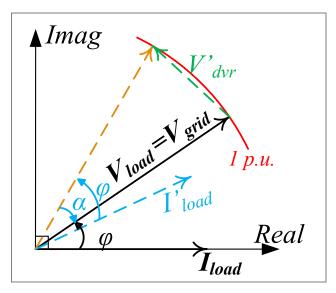

| Figure 1.11. Phasor diagram of the self-charging mode in battery supported DVR                                                                                                                        |

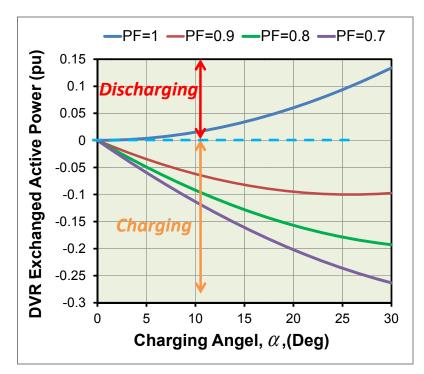

| Figure 1.12. Exchanged active power of battery supported DVR in self-charging mode                                                                                                                    |

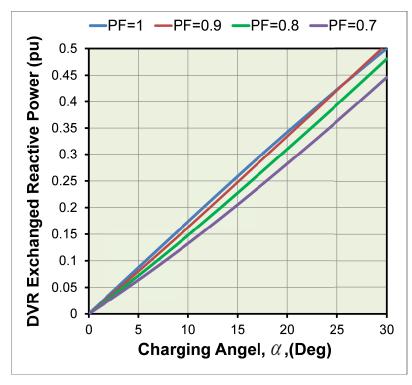

| Figure 1.13. Exchanged reactive power of battery supported DVR in self-charging mode32                                                                                                                |

| Figure 1.14. Peak voltage of battery supported DVR in self-charging mode                                                                                                                              |

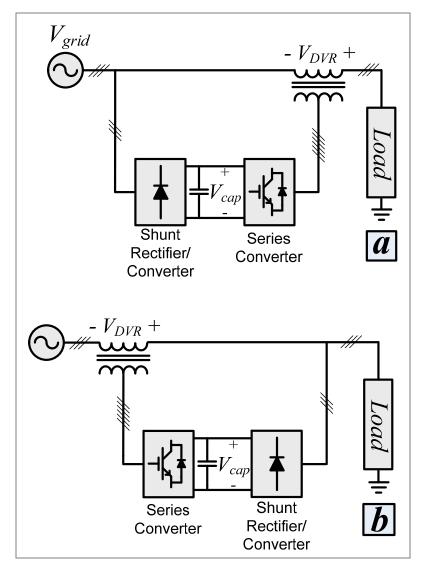

| Figure 1.15. DVR configuration with series isolation transformer and shunt rectifier/converter at the: (a) source-side; (b) load-side                                                                 |

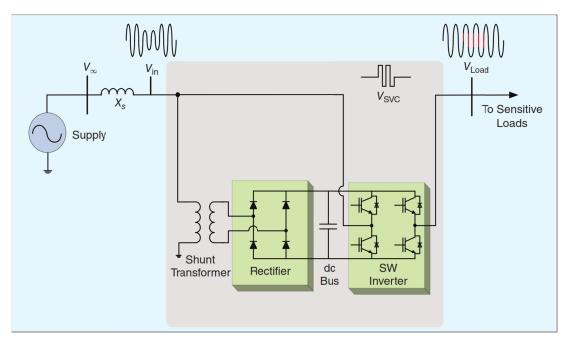

| Figure 1.16. DVR based on the square-wave injection presented in [69]–[71]                                                                                                                            |

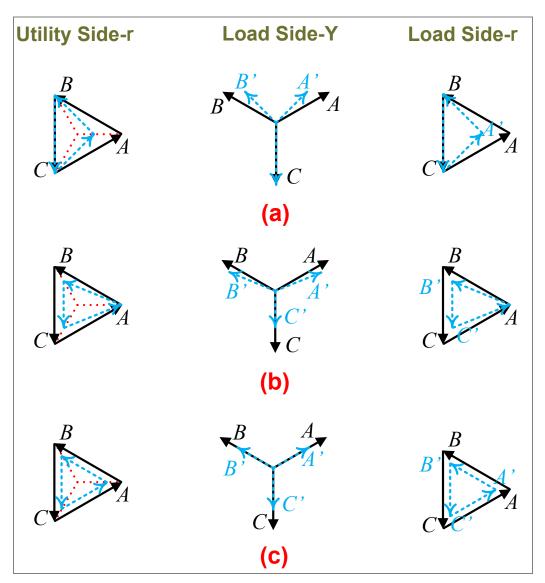

| Figure 1.17. The vector diagram of a faulted distribution system (partial voltage collapse): (a) Single line to ground fault; (b) Double line to ground fault; (c) Three lines to ground fault        |

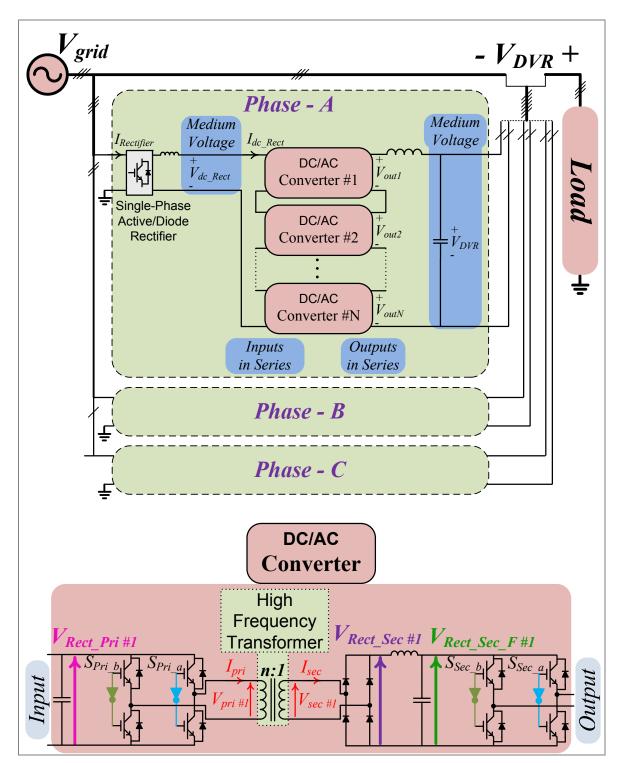

| Figure 1.18. The proposed configuration of DVR based on high-frequency transformer dc-ac converter without any bulky dc link capacitor                                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

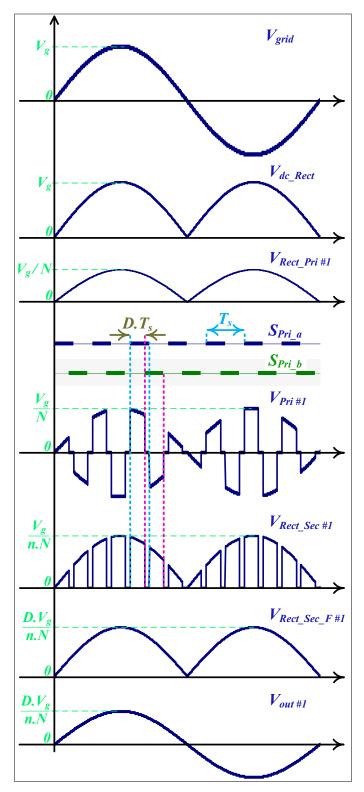

| Figure 1.19. Operation principle of high-frequency transformer based dc-ac converter in the proposed DVR configuration                                                                                                                   |

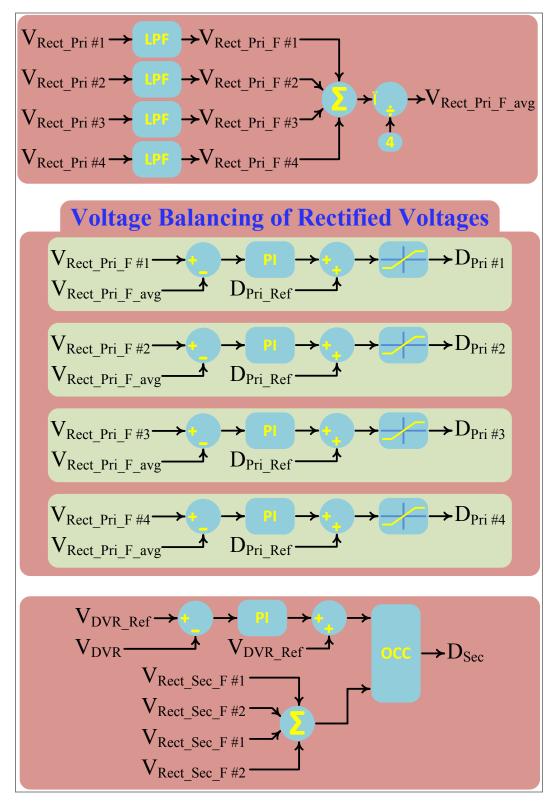

| Figure 1.20. Control scheme of the proposed DVR configuration based on high-frequency isolated dc-ac converter                                                                                                                           |

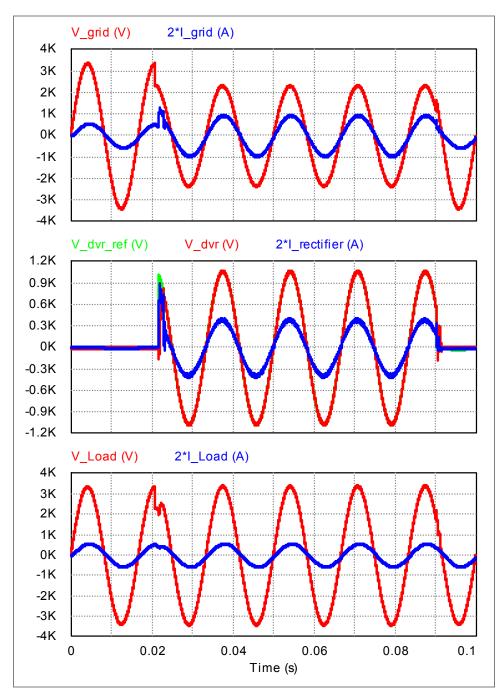

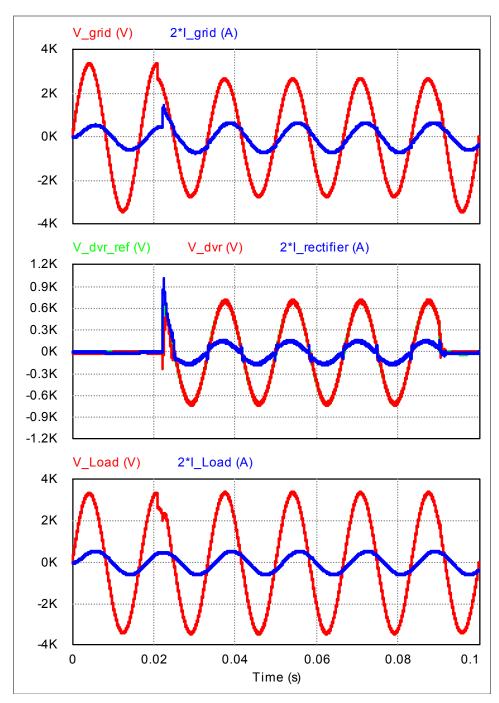

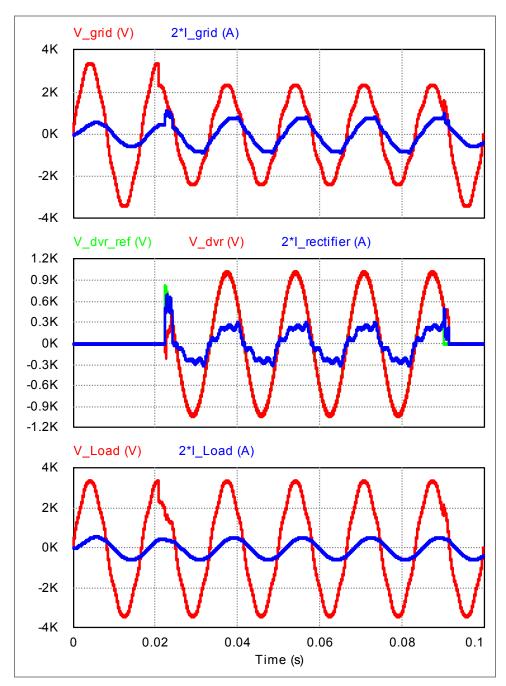

| Figure 1.21. Simulation result of the proposed DVR compensating the voltage sag with VSD of 30% and PF of 0.98                                                                                                                           |

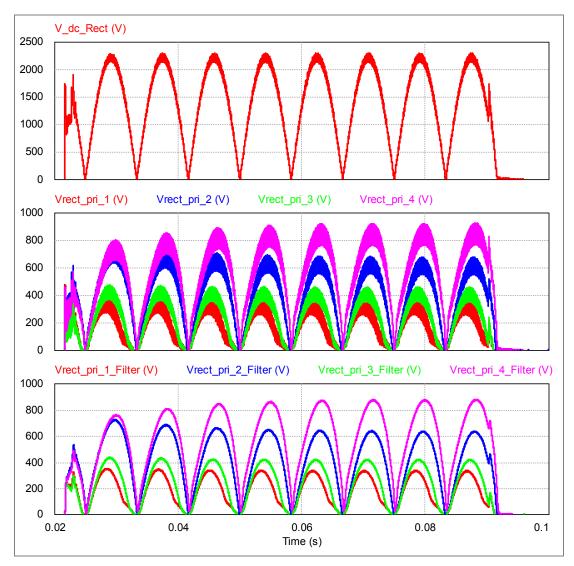

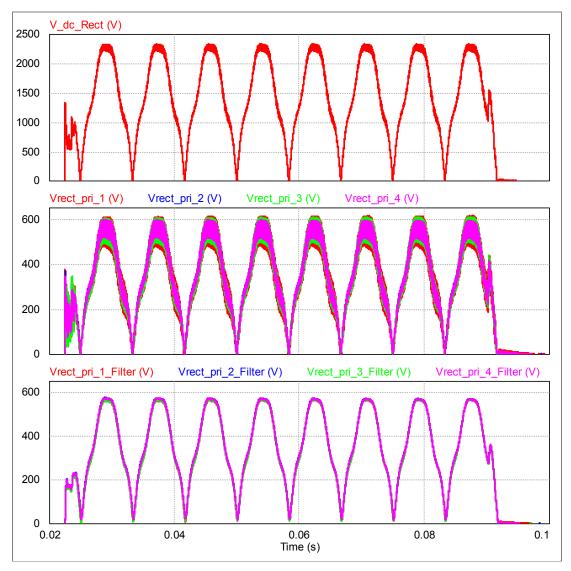

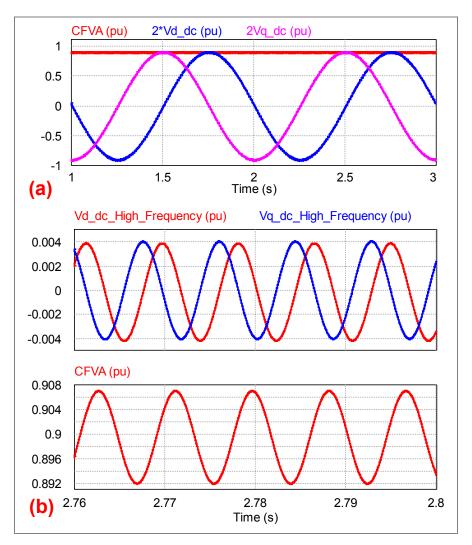

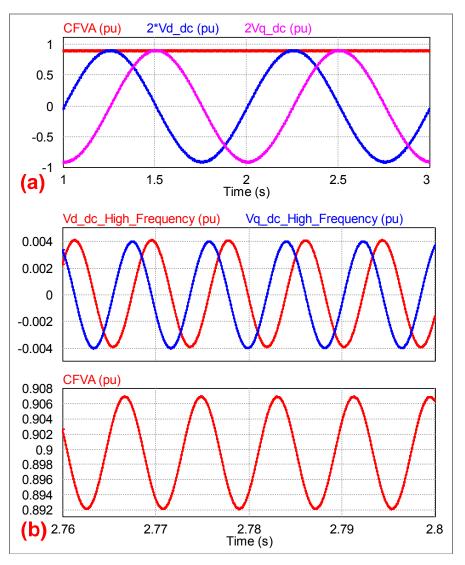

| Figure 1.22. Simulation result of the main rectified voltage ( $V_{dc\_Rect}$ ), and actual and filtered input voltage of each isolated dc-ac converter in the proposed DVR while "voltage balancing of rectified voltages" is disabled. |

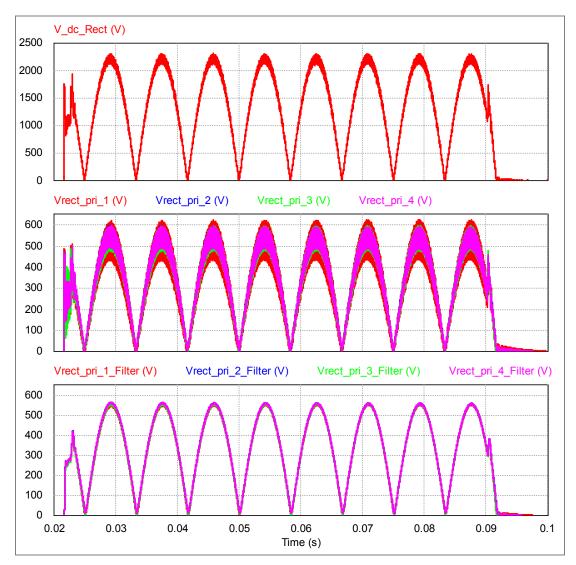

| Figure 1.23. Simulation result of the main rectified voltage ( $V_{dc\_Rect}$ ), and actual and filtered input voltage of each isolated dc-ac converter in the proposed DVR while "voltage balancing of rectified voltages" is enabled   |

| Figure 1.24. Simulation result of the proposed DVR compensating the voltage sag with VSD of 20% and PF of 0.8                                                                                                                            |

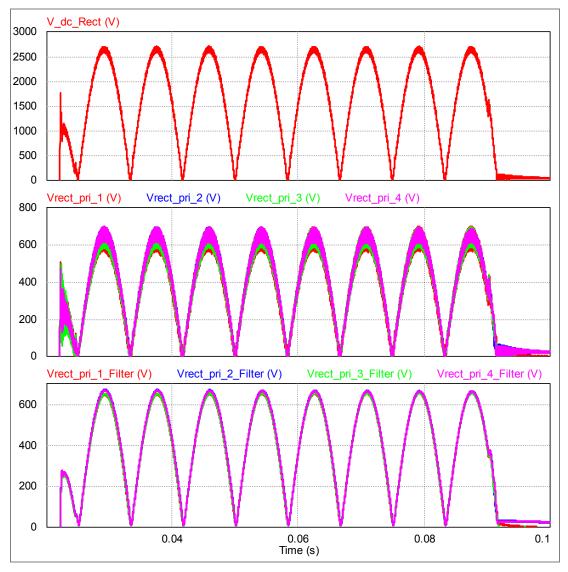

| Figure 1.25. Simulation result of the main rectified voltage ( $V_{dc\_Rect}$ ), and actual and filtered input voltage of each isolated dc-ac converter in the proposed DVR while "voltage balancing of rectified voltages" is enabled.  |

| Figure 1.26. Simulation result of the proposed DVR compensating the voltage sag with VSD of 30%, PF of 0.8 and harmonic distortion of $V_{g5} = 0.03V_{g1}$ and $V_{g7} = 0.03V_{g1}$                                                    |

| Figure 1.27. Simulation result of the main rectified voltage ( $V_{dc\_Rect}$ ), and actual and filtered input voltage of each isolated dc-ac converter in the proposed DVR while "voltage balancing of rectified voltages" is enabled   |

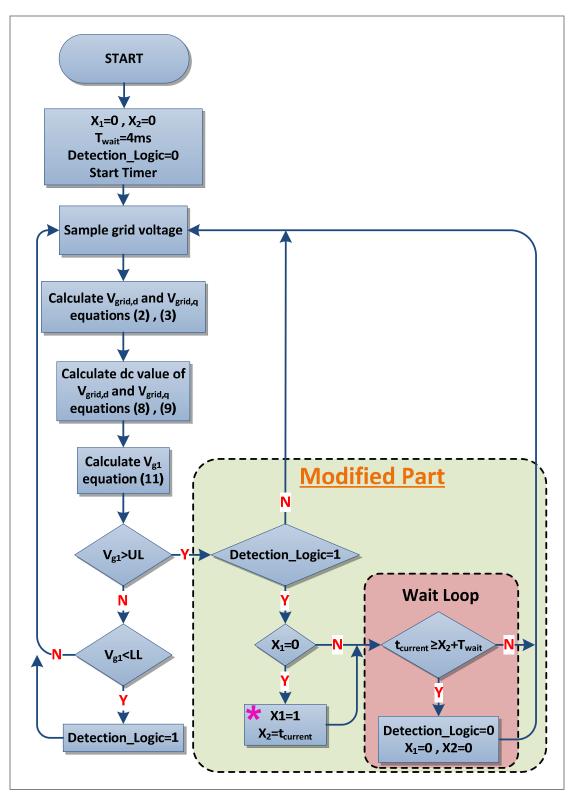

| Figure 2.1. Flow chart of proposed voltage sag detection method                                                                                                                                                                          |

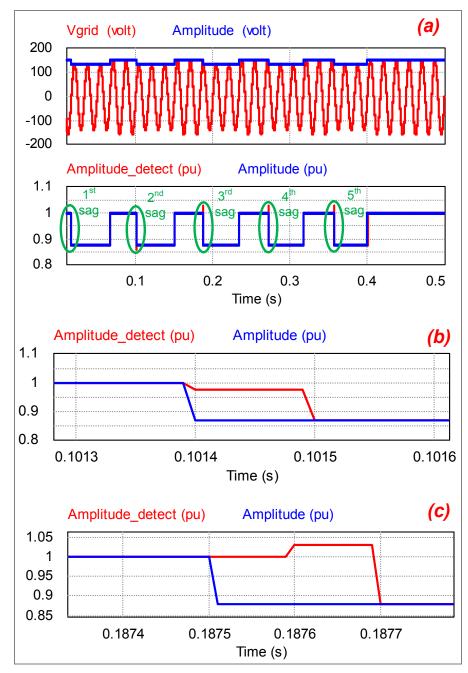

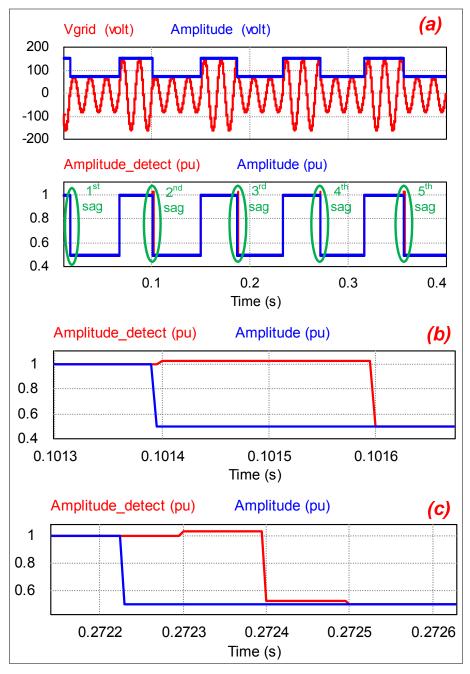

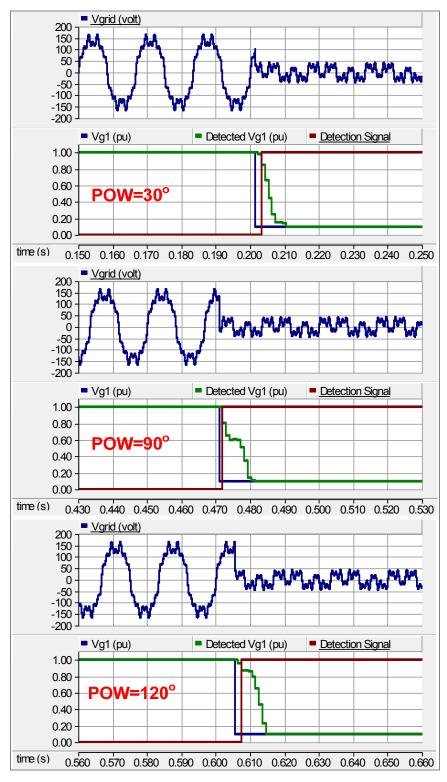

| Figure 2.2. Simulation result of VS=12% for different amount of POW with line-frequency of 60 Hz: (a) grid voltage, its amplitude and detected amplitude with proposed method; (b) & (c) more detailed view                              |

| Figure 2.3. Simulation result of VS=50% for different amount of POW with line-frequency of 60 Hz: (a) grid voltage, its amplitude and detected amplitude with proposed method; (b & c) more detailed view                                |

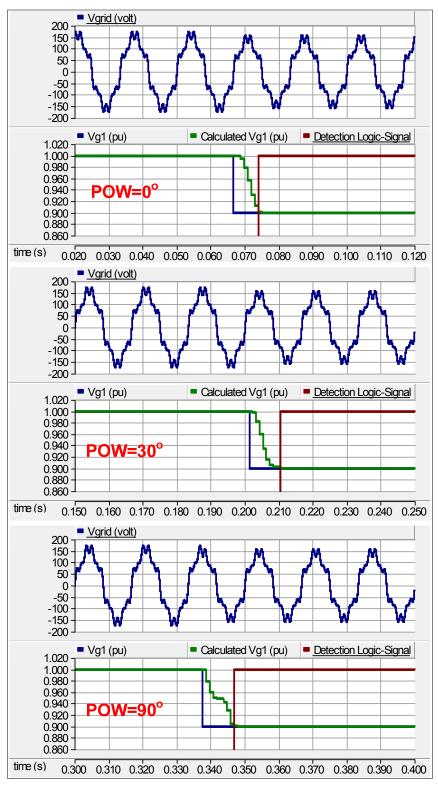

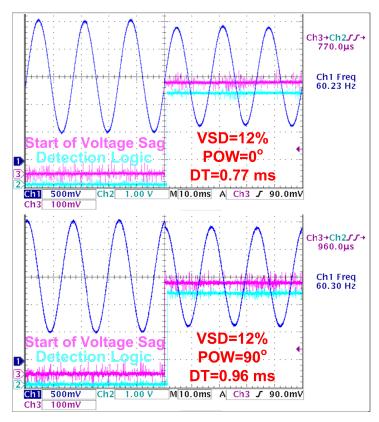

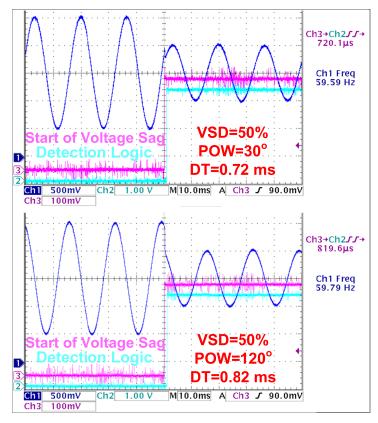

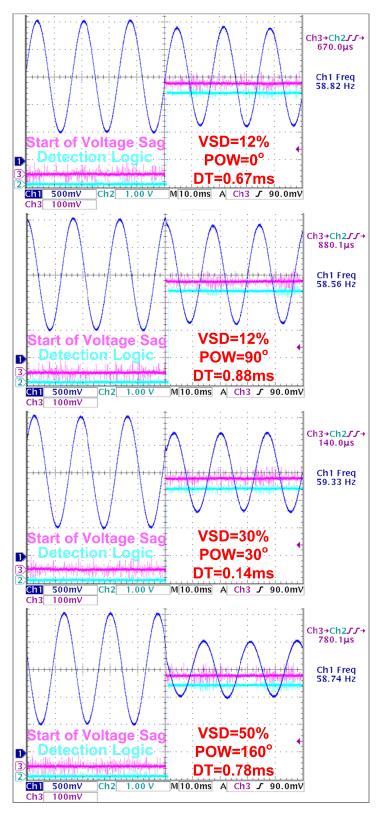

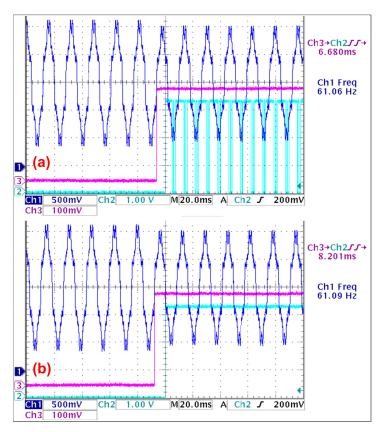

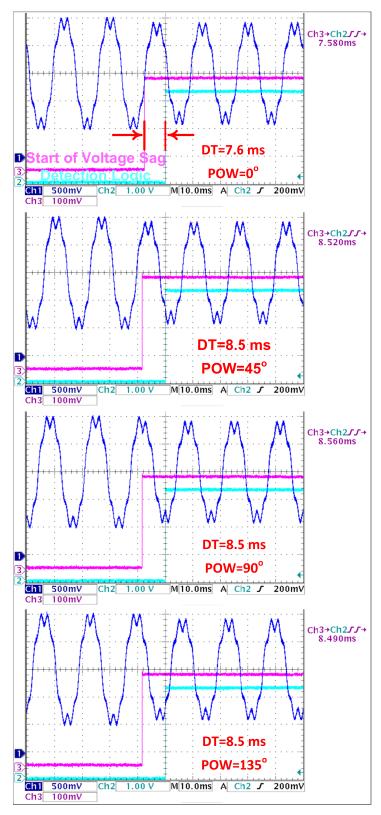

| Figure 2.10. Experimental result of 12% VSD for different amounts of POW with line-frequency of |

|-------------------------------------------------------------------------------------------------|

| 60 Hz                                                                                           |

|                                                                                                 |

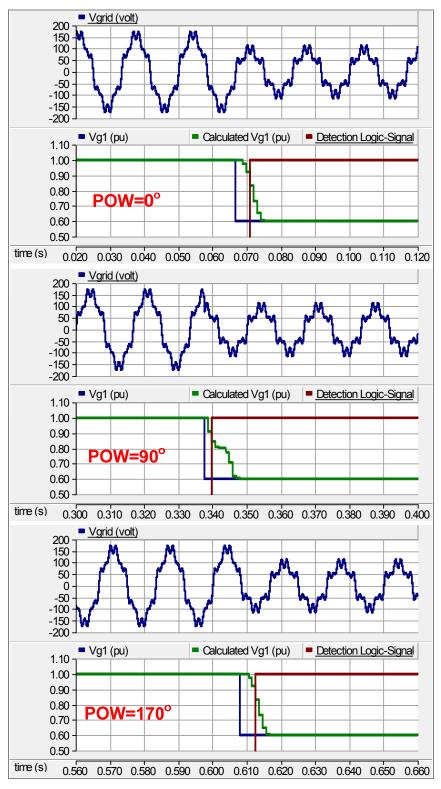

| Figure 2.11. Experimental result of 50% VSD for different amounts of POW with line-frequency of |

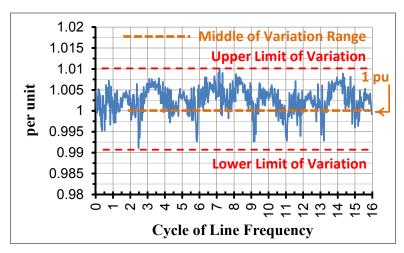

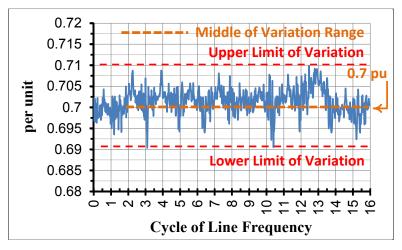

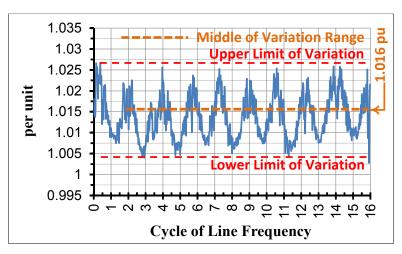

| Figure 2.16. Fundamental voltage amplitude calculated by DSP for 0% VSD with line-frequency of 61 Hz                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

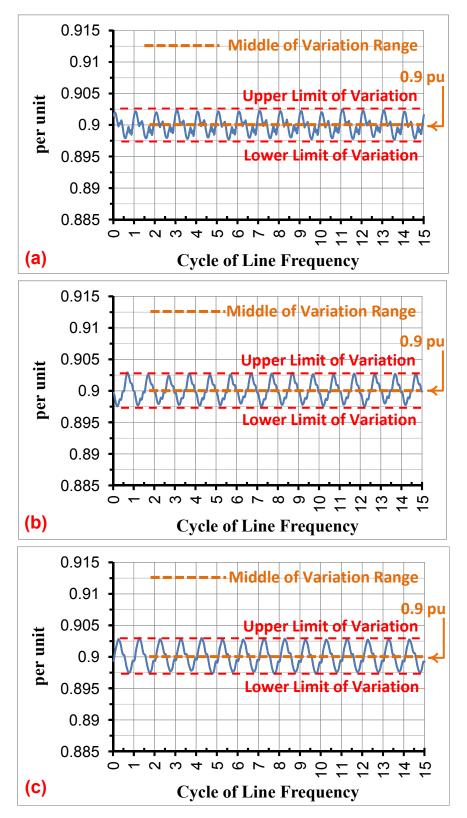

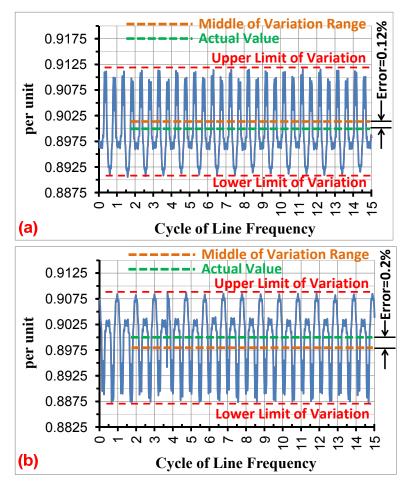

| Figure 2.17. Fundamental voltage amplitude calculated by DSP for 10% VSD with line-frequency of 60 Hz for harmonic distortion of: (a) first case; (b) second case; (c) third case                                            |

| Figure 2.18. Fundamental voltage amplitude calculated by DSP for 10% VSD with line-frequency of: (a) 61 Hz; (b) 59 Hz                                                                                                        |

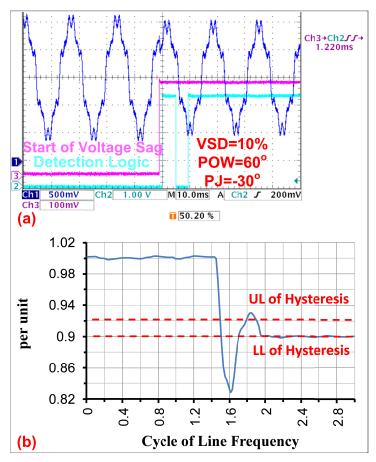

| Figure 2.19. Experimental result: VSD of 10.5% with line-frequency of 61Hz and first case of harmonic distortion using the hysteresis threshold comparator                                                                   |

| Figure 2.20. Instability of method for VSD of 10%, POW of 60° and PJ of -30° with line-frequency of 60Hz and first case of harmonic distortion: (a) experimental result; (b) fundamental voltage amplitude calculated by DSP |

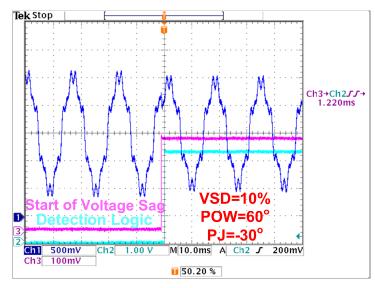

| Figure 2.21. Experimental result: stability of modified method for VSD of 10%, POW of 60° and PJ of -30° with line-frequency of 60Hz and first case of harmonic distortion                                                   |

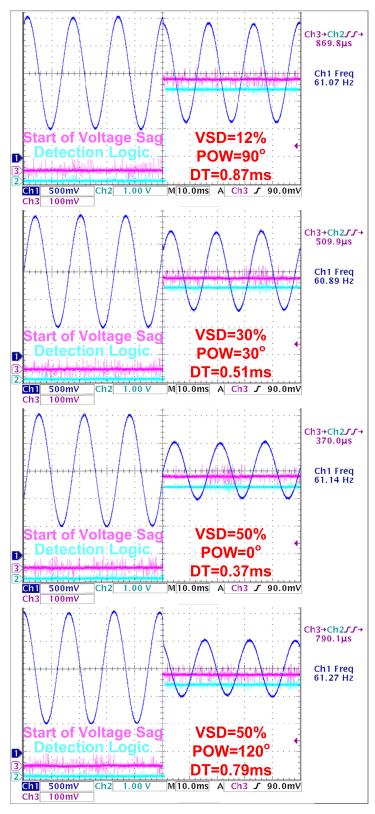

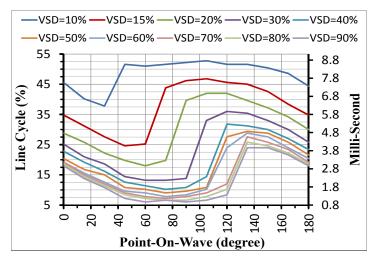

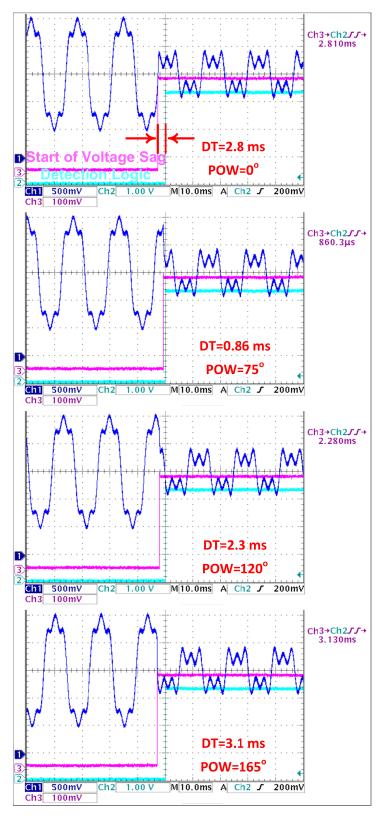

| Figure 2.22. Experimental result: DT for different amounts of VSD and POW with line-frequency of 60Hz and first case of harmonic distortion                                                                                  |

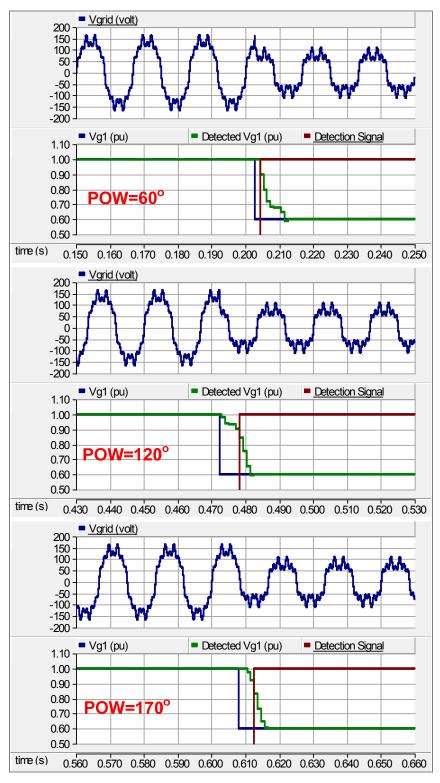

| Figure 2.23. Experimental result of 10% VSD for different amounts of POW with PJ=0°, line-frequency of 60 Hz and second case of harmonic distortion. 124                                                                     |

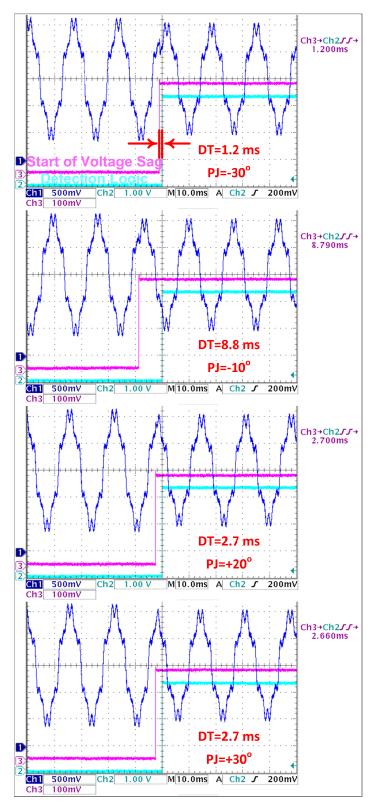

| Figure 2.24. Experimental result of 10% VSD for different amounts of PJ with POW=60°, line-frequency of 60 Hz and first case of harmonic distortion                                                                          |

| Figure 2.25. Experimental result of 70% VSD for different amounts of POW with PJ=20°, line-<br>frequency of 60 Hz and third case of harmonic distortion                                                                      |

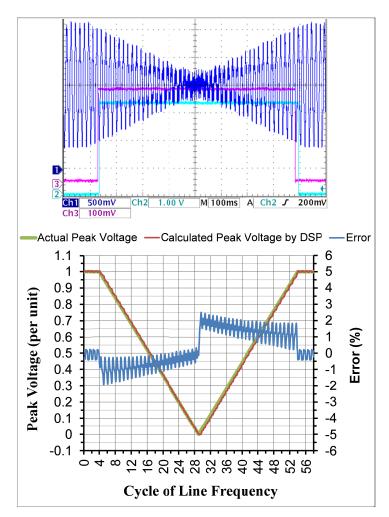

| Figure 2.26. Experimental result of continuous decrease and increase (100% within 0.417s) of fundamental voltage amplitude                                                                                                   |

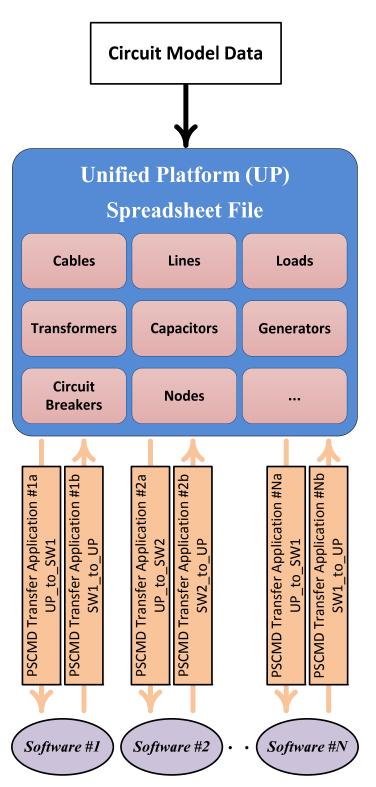

| Figure 3.1. Conceptual illustration of the proposed unified platform (UP) to transfer power system circuit model data among different software. SW stands for software                                                       |

| Figure 3.2. Snapshot of UP's spreadsheet containing required parameters of: (a) transformer; (b) cable; (c) capacitor and (d) load                                                                                           |

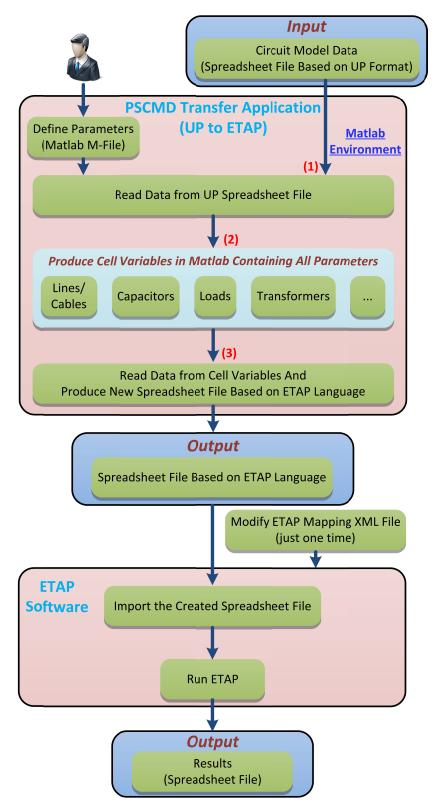

| Figure 3.3. General scheme of importing power system circuit model data from UP spreadsheet into ETAP using PSCMD transfer application                                                                                       |

| Figure 3.4. Snapshot of script to determine variable of PhaseConnection_number for ETAP 150                                                                                                                                  |

| Figure 3.5. Snapshot of script to determine variable of GroundingConnection_type for ETAP150                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.6. Snapshot of ETAP mapping XML file modification related to cable component 152                                                                                                                                 |

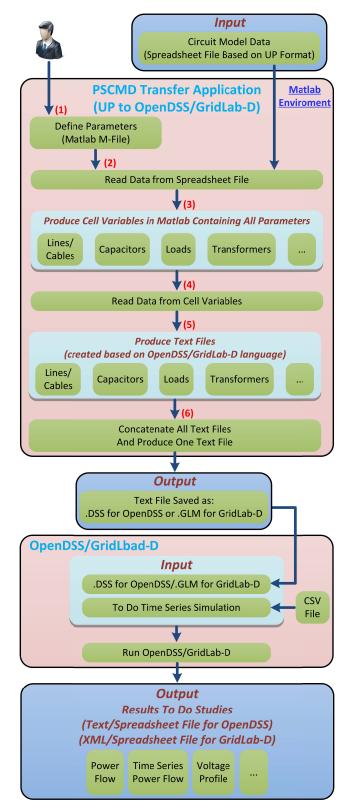

| Figure 3.7. General scheme of importing power system circuit model data from UP spreadsheet into OpenDSS using PSCMD transfer application                                                                                 |

| Figure 3.8. Snapshot of data parsing part in PSCMD transfer application to transfer power system circuit model data from UP spreadsheet into OpenDSS                                                                      |

| Figure 3.9. Snapshot of model constructing part related to overhead lines in PSCMD transfer application to transfer power system circuit model data from UP spreadsheet into OpenDSS158                                   |

| Figure 3.10. Snapshot of user initialization part in PSCMD transfer application to transfer power system circuit model data from UP spreadsheet into GridLAB-D                                                            |

| Figure 3.11. Snapshot of data parsing part in PSCMD transfer application to transfer power system circuit model data from UP spreadsheet into GridLAB-D                                                                   |

| Figure 3.12. Snapshot of model construction part in PSCMD transfer application to transfer power system circuit model data from UP spreadsheet into GridLAB-D                                                             |

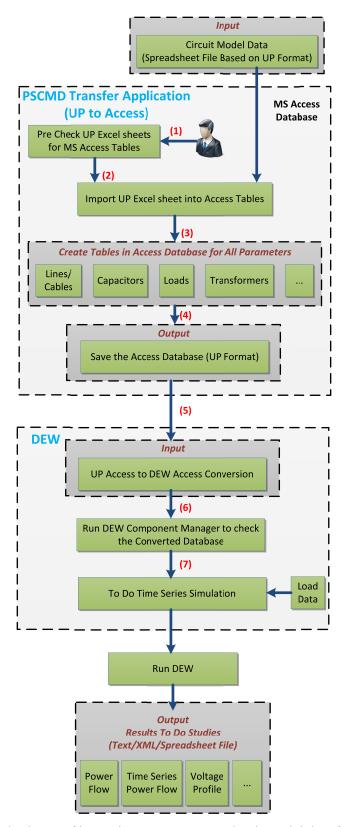

| Figure 3.13. General scheme of importing power system circuit model data from UP spreadsheet into DEW using PSCMD transfer application                                                                                    |

| Figure 3.14. Snapshot of component manager in DEW to transfer power system circuit model data from UP spreadsheet into DEW                                                                                                |

| Figure 4.1. The power generation of 3.5MW centralized solar plant: (a) raw measurement data; and interpolated data with resampling time-interval of (b) 60s; (c) 10min; (d) 60min                                         |

| Figure 4.2. The measurement power generation of 1.5MW and 3.5MW solar plants on: (a) Aug. 2, 2013; (b) Aug. 3, 2013; (c) Aug. 4, 2013                                                                                     |

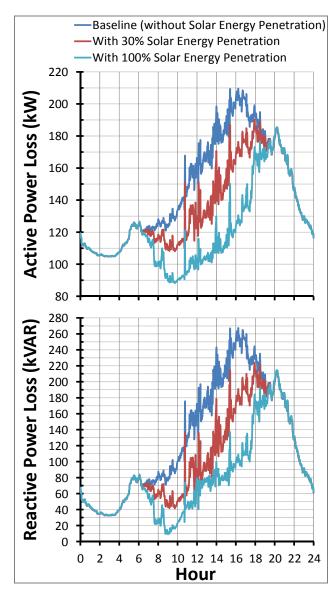

| Figure 4.3. The active and reactive power loss of lines and cables obtained from OpenDSS with baseline load demand, and at presence of 30% and 100% solar energy penetration of 3.7MW (53% of measured total load demand) |

| Figure 4.4. General scheme of the developed data interpolation-resampling (DIR) application 198                                                                                                                           |

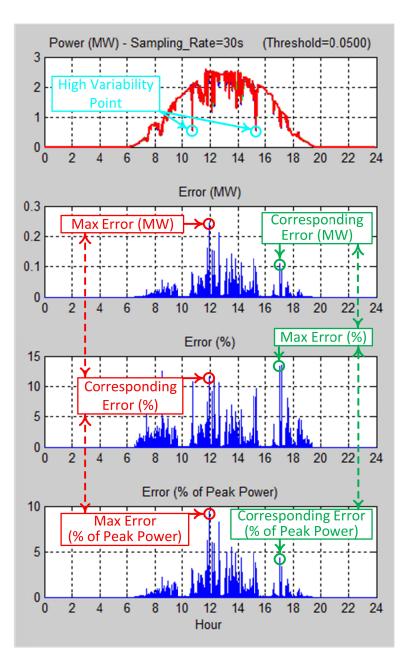

| Figure 4.5. Output graph of DIR application depicting the interpolation-resampling error of measurement output power of 3.5MW solar plant on Aug. 2, 2013 resampled at 30s                                                |

| Figure 4.6. General scheme of the developed resampling error calculation (REC) application202                                                                                                                             |

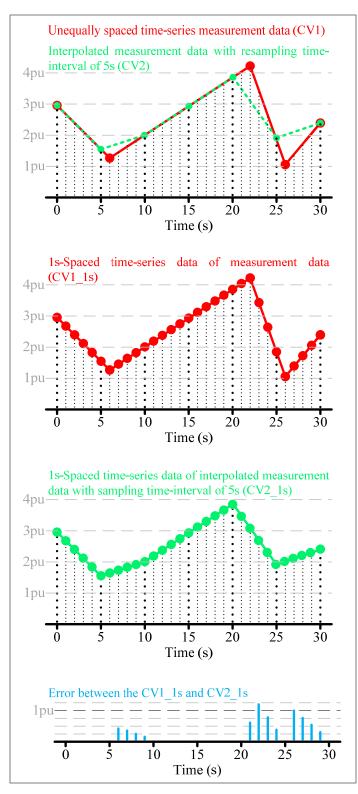

| Figure 4.7. The approach of converting both unequally spaced time-series measurement data (CV1) and interpolated measurement data (CV2) to 1s-spaced time-series data (CV1_1s and CV2_1s), comparing them and calculating the error. 205                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

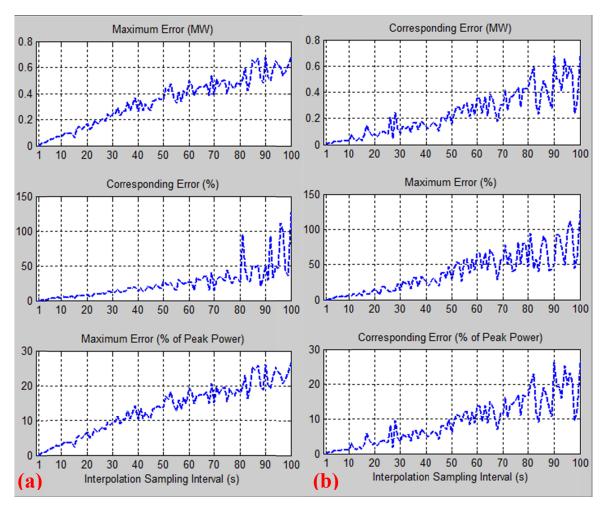

| Figure 4.8. The interpolation error of measurement output power of 2.5MW solar plant resampled<br>in the range of 1s to 100s illustrating (a) maximum Error (MW), corresponding Error (%) and<br>maximum Error (% of Peak Power); (b) corresponding Error (MW), maximum Error (%) and<br>corresponding Error (% of Peak Power) |

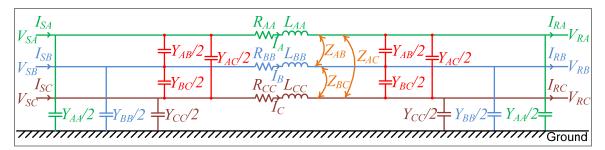

| Figure 4.9. General scheme of the unbalanced distribution line/cable                                                                                                                                                                                                                                                           |

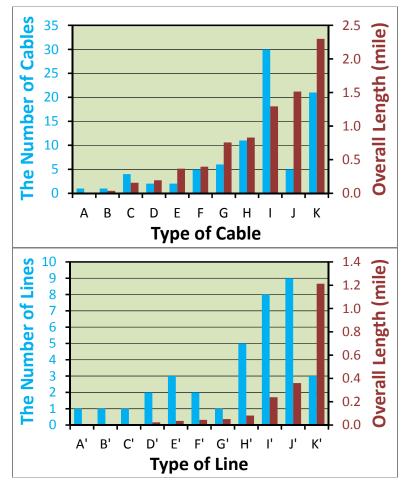

| Figure 4.10. The number of lines and cables of each type and overall length of each type of line/cable used in the SCE studied circuit                                                                                                                                                                                         |

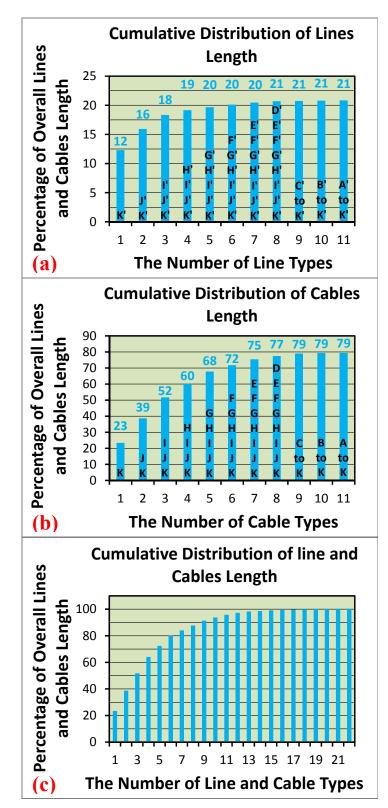

| Figure 4.11. Cumulative distribution of line/cable types in the SCE studied circuit: (a) line; (b) cable; (c) both line and cable                                                                                                                                                                                              |

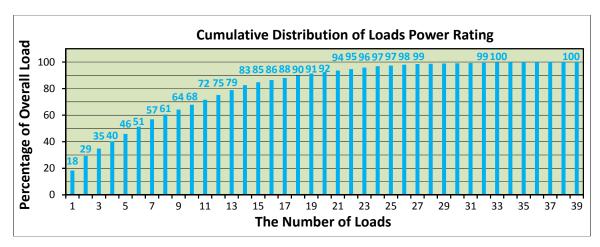

| Figure 4.12. Cumulative distribution of loads power rating in the SCE studied circuit                                                                                                                                                                                                                                          |

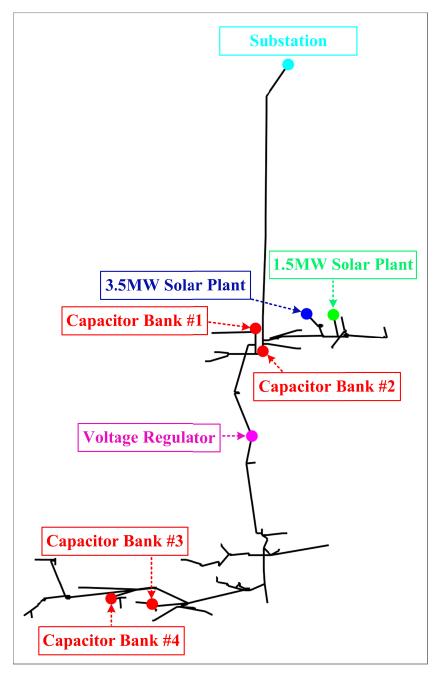

| Figure 4.13. Single-line diagram of the studied SCE power distribution circuit                                                                                                                                                                                                                                                 |

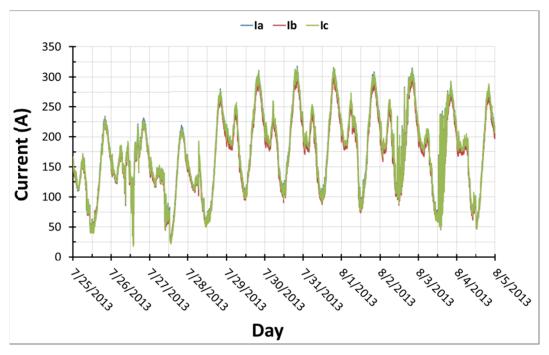

| Figure 4.14. The start-of-circuit raw measured current of all three phases                                                                                                                                                                                                                                                     |

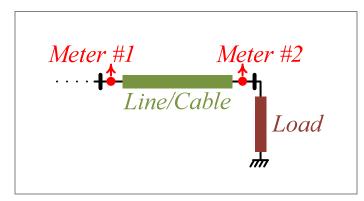

| Figure 4.15. Model validation for the combination of the load and cable/line                                                                                                                                                                                                                                                   |

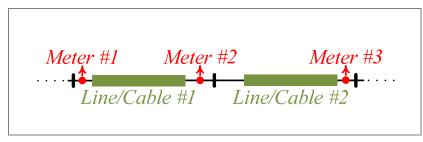

| Figure 4.16. Model validation for the case where two lines/cables are connected in series                                                                                                                                                                                                                                      |

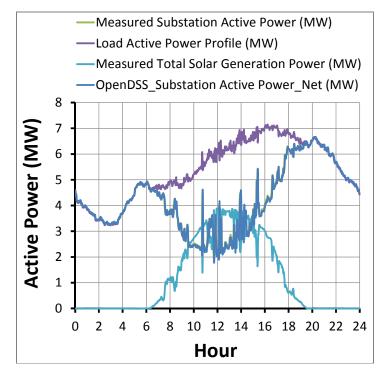

| Figure 4.15. The measurement data and obtained simulation result at start-of-circuit                                                                                                                                                                                                                                           |

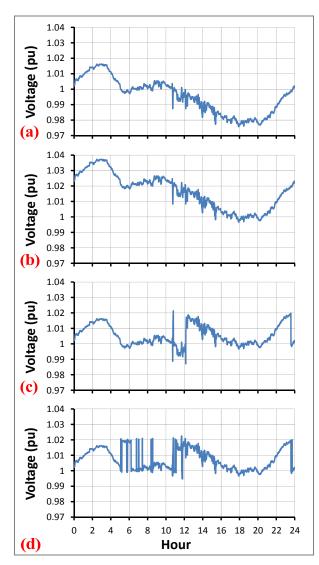

| Figure 4.16. Simulation result – voltage of phase A at the end-of-circuit while capacitor #3 is (a) disconnected; (b) connected; (c) controlled with turn-on threshold of 0.99pu; (d) controlled with turn-on threshold of 1pu                                                                                                 |

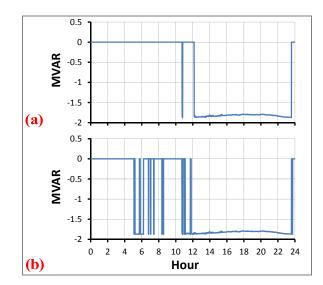

| Figure 4.17. Simulation result – capacitor #3 operation at voltage mode control while its turn-on threshold is (a) 0.99pu; (b) 1pu                                                                                                                                                                                             |

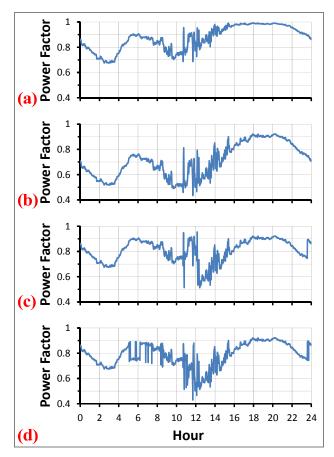

| Figure 4.18. Simulation result – power factor of phase A at the end-of-circuit while capacitor #3 is (a) disconnected; (b) connected; (c) controlled with turn-on threshold of 0.99pu; (d) controlled with turn-on threshold of 1pu                                                                                            |

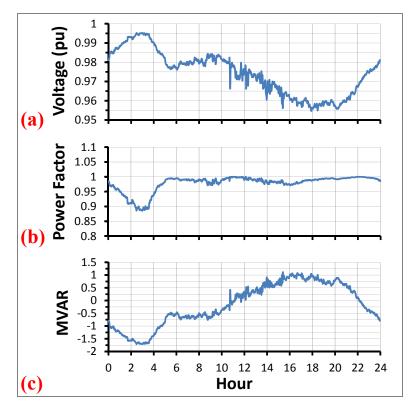

| Figure 4.19. Simulation result – (a) voltage profile at end-of-circuit; (b) power factor at start-of-circuit; (c) amount of reactive power at start-of-circuit                                                                                                                                                                 |

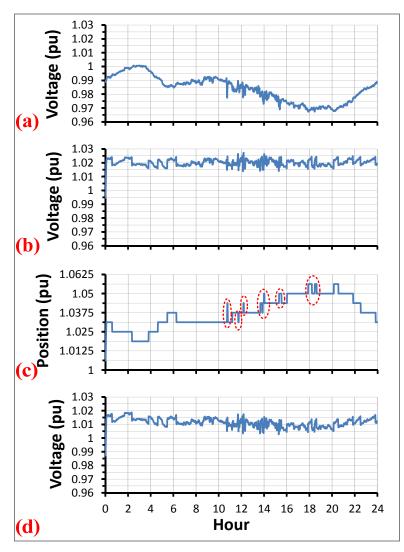

| Figure 4.20. Simulation result – (a) voltage at the primary side of regulator; (b) voltage at the secondary side of regulator; (c) regulator tap position; (d) voltage profile of end-of-circuit230                                                                                                                            |

| xi                                                                                                                                                                                                                                                                                                                             |

# LIST OF TABLES

| Table 1.1 | 24  |

|-----------|-----|

| Table 1.2 |     |

| Table 2.1 |     |

| Table 2.2 |     |

| Table 2.3 |     |

| Table 3.1 |     |

| Table 3.2 |     |

| Table 3.3 |     |

| Table 3.4 | 171 |

| Table 3.5 |     |

| Table 4.1 |     |

| Table 4.2 |     |

| Table 4.3 |     |

| Table 4.4 |     |

| Table 4.5 |     |

| Table 4.6 |     |

| Table 4.7 |     |

| Table 4.8 |     |

#### ACKNOWLEDGMENTS

The PhD program that I had been through was truly a once in a lifetime experience. I realize there are many people who deserve to be thanked for what I have been achieving and for what I have become now.

First of all, I would like to thank my Ph.D. advisor, Prof. Keyue Smedley, for all her support during my Ph.D. study and research. It has been a pleasure and honor working at UCI Power Electronics Lab while Prof. Keyue Smedley's passion towards power electronics has been an inspiration to me. Her guidance, constant moral support, and constructive advice and criticism helped me in all the time of research and writing of this thesis.

I would like to express my sincere thanks to Prof. Franco Maddaleno and Dr. Alexander Abramovitz for all their advice and teaching. My sincere thanks also go to the members of my Ph.D. dissertation committee: Prof. Michael Green and Prof. Pai H. Chou for their willingness to read and approve this thesis.

I thank all the alumni of UCI Power Electronics Lab, Dr. In-Wha Jeong, Dr. Liang Zhou, and Dr. Marco Tedde, the current Ph.D. students, Roozbeh Naderi, Bin Wu, and Shijie Yu, and the visitors, Ben Zhao, Jia Yao, and Mojtaba Heydari, for the help that I received during my Ph.D. study.

I thank the entire University of California, Irvine, for the Scholarships that I received during my Ph.D. study, especially Electrical Engineering and Computer Science department for the Teaching and Research Assistantships. Moreover, I have to thank California Energy Commission and CIEE for their support of my work on "Distribution Monitoring for Renewables Integration (DMRI)" project (Contract #500-11-019) and providing a great opportunity for me to collaborate with industries. I would like to thank Dr. Reza Arghandeh and Dr. Alexandra von Meier from CIEE for their collaboration, all the participating utilities in the DMRI project and particularly, Sunil Shah from Southern California Edison (SCE) and Steve Kirin from Sacramento Municipal Utility District (SMUD) for their time and effort to provide circuit model data. Appreciation also goes to Ken Nunes from the San Diego Super Computer Center (SDSC) to facilitate data transfer, James Sherwood from Rocky Mountain Institute for his valuable and constructive suggestions and ETAP Inc. for providing an ETAP software license.

Many special thanks to my parents, Fatemeh and Jafar, who supported me for many years, to my beloved wife, Sima, for all her support starting from the first day of our marriage, and to my son, Elvin, who has brought to me happiness and given reason to get through another day.

### **CURRICULUM VITAE**

#### Arash Khoshkbar Sadigh

| 2007        | B.Sc. in Electrical Engineering (Majoring Power)<br>University of Tabriz, Iran                                         |

|-------------|------------------------------------------------------------------------------------------------------------------------|

| 2009        | M.Sc. in Electrical Engineering (Majoring Power)<br>University of Tabriz, Iran                                         |

| 2007-2010   | Power transmission and distribution line (overhead and underground)<br>Design Engineer, ANA Co. Tabriz, Iran           |

| Summer 2012 | RTDS Research Engineer<br>Southern California Edison, Westminster, CA, US                                              |

| Summer 2013 | RTDS Research Engineer<br>Southern California Edison, Westminster, CA, US                                              |

| 2011-2013   | Teaching Assistant (Power Electronics and Control Systems)<br>EECS Department, University of California Irvine, CA, US |

| 2010-2014   | Research Assistant<br>Power Electronics Lab., University of California Irvine, CA, US                                  |

| 2014        | Ph.D., Electrical Engineering (Majoring Power)<br>University of California Irvine, CA, US                              |

#### PUBLICATIONS

- [1] A. Khoshkbar-Sadigh and K. M. Smedley, "Review of voltage compensation methods in dynamic voltage restorer (DVR)," in IEEE Power and Energy Society General Meeting, 2012, pp. 1–8.

- [2] A. Khoshkbar-Sadigh and K. M. Smedley, "Fast voltage sag detection method for single-/three-phase application," in 2013 Twenty-Eighth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), 2013, pp. 881–888.

- [3] A. Khoshkbar-Sadigh and K. Smedley, "A Fast and Precise Voltage Sag Detection Method for Dynamic Voltage Restorer (DVR) Application," IEEE Trans. Power Electron., (Revision has been submitted).

- [4] A. Khoshkbar-Sadigh and K. Smedley, "The Necessity of Time-Series Simulation for Investigation of Large-Scale Solar Energy Penetration," in 6th Innovative Smart Grid Technologies, (Accepted for publication).

- [5] A. Khoshkbar-Sadigh, M. Heydari, M. Tedde, R. Arghandeh, K. Smedley, and A. Von-Meier, "A Unified Platform Enabling Power System Circuit Model Data Transfer Among Different Software," in 6th Innovative Smart Grid Technologies, (Accepted for publication).

- [6] A. Khoshkbar-Sadigh, M. Heydari, M. Tedde, R. Arghandeh, K. Smedley, and A. Von-Meier, "A Unified Platform Enabling Power System Circuit Model Data Transfer Among Different Software," Electr. Power Syst. Res., (Under review).

- [7] A. Khoshkbar-Sadigh and K. Smedley, "Investigation of Utility-Scale PV Penetration in Power Distribution Circuit of Southern California Edison," IEEE Trans. Sustainable Energy, (Under review).

#### **ABSTRACT OF THE DISSERTATION**

Preparation of Power Distribution System for high Penetration of Renewable Energy Part I. Dynamic Voltage Restorer for Voltage Regulation Pat II. Distribution Circuit Modeling and Validation

By

Arash Khoshkbar Sadigh

Doctor of Philosophy in Electrical Engineering

University of California, Irvine, 2014

Professor Keyue Smedley, Chair

#### Part I: Dynamic Voltage Restorer

In the present power grids, voltage sag is recognized as a serious threat and a frequently occurring power-quality problem and has costly consequences such as sensitive loads tripping and production loss. Consequently, the demand for high power quality and voltage stability becomes a pressing issue. Dynamic voltage restorer (DVR), as a custom power device, is more effective and direct solutions for "restoring" the quality of voltage at its load-side terminals when the quality of voltage at its source-side terminals is disturbed.

In the first part of this thesis, a DVR configuration with no need of bulky dc link capacitor or energy storage is proposed. This fact causes to reduce the size of the DVR and increase the reliability of the circuit. In addition, the proposed DVR topology is based on high-frequency isolation transformer resulting in the size reduction of transformer. The proposed DVR circuit, which is suitable for both low- and medium-voltage applications, is based on dc-ac converters connected in series to split the main dc link between the inputs of dc-ac converters. This feature makes it possible to use modular dc-ac converters and

utilize low-voltage components in these converters whenever it is required to use DVR in medium-voltage application. The proposed configuration is tested under different conditions of load power factor and grid voltage harmonic. It has been shown that proposed DVR can compensate the voltage sag effectively and protect the sensitive loads.

Following the proposition of the DVR topology, a fundamental voltage amplitude detection method which is applicable in both single/three-phase systems for DVR applications is proposed. The advantages of proposed method include application in distorted power grid with no need of any low-pass filter, precise and reliable detection, simple computation and implementation without using a phased locked loop and lookup table. The proposed method has been verified by simulation and experimental tests under various conditions considering all possible cases such as different amounts of voltage sag depth (VSD), different amounts of point-on-wave (POW) at which voltage sag occurs, harmonic distortion, line frequency variation, and phase jump (PJ). Furthermore, the ripple amount of fundamental voltage amplitude calculated by the proposed method and its error is analyzed considering the line frequency variation together with harmonic distortion. The best and worst detection time of proposed method has been compared with other voltage sag detection methods available in literature.

#### Part 2: Power System Modeling for Renewable Energy Integration

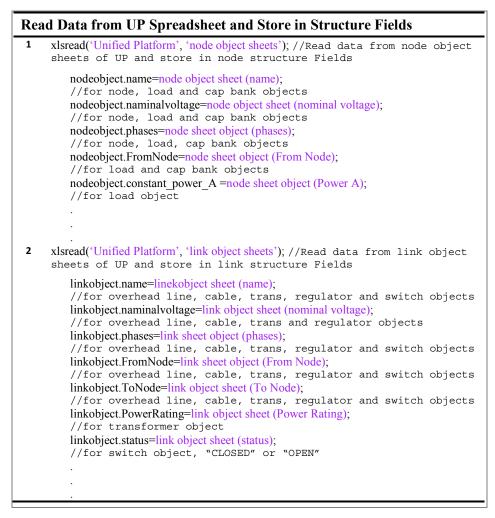

As power distribution systems are evolving into more complex networks, electrical engineers have to rely on software tools to perform circuit analysis. There are dozens of powerful software tools available in the market to perform the power system studies. Although their main functions are similar, there are differences in features and formatting structures to suit specific applications. This creates challenges for transferring power system circuit models data (PSCMD) between different software and rebuilding the same circuit in the second software environment. The objective of this part of thesis is to develop a Unified Platform (UP) to facilitate transferring PSCMD among different software packages and relieve the challenges of the circuit model conversion process. UP uses a commonly available spreadsheet file with a defined format, for any home software to write data to and for any destination software to read data from, via a script-based application called PSCMD transfer application. The main considerations in developing the UP are to minimize manual intervention and import a one-line diagram into the destination software or export it from the source software, with all details to allow load flow, short circuit and other analyses. In this study, ETAP, OpenDSS, and GridLab-D are considered, and PSCMD transfer applications written in MATLAB have been developed for each of these to read the circuit model data provided in the UP spreadsheet. In order to test the developed PSCMD transfer applications, circuit model data of a test circuit and a power distribution circuit from Southern California Edison (SCE) – a utility company – both built in CYME, were exported into the spreadsheet file according to the UP format. Thereafter, circuit model data were imported successfully from the spreadsheet files into above mentioned software using the PSCMD transfer applications developed for each software.

After the SCE studied circuit is transferred into OpenDSS software using the proposed UP scheme and developed application, it has been studied to investigate the impacts of large-scale solar energy penetration. The main challenge of solar energy integration into power grid is its intermittency (i.e., discontinuity of output power) nature

due to cloud shading of photovoltaic panels which depends on weather conditions. In order to conduct this study, OpenDSS time-series simulation feature, which is required due to intermittency of solar energy, is utilized. In this study, the impacts of intermittency of solar energy penetration, especially high-variability points, on voltage fluctuation and operation of capacitor bank and voltage regulator is provided. In addition, the necessity to interpolate and resample unequally spaced time-series measurement data and convert them to equally spaced time-series data as well as the effect of resampling time-interval on the amount of error is discussed. Two applications are developed in Matlab to do interpolation and resampling as well as to calculate the amount of error for different resampling timeintervals to figure out the suitable resampling time-interval. Furthermore, an approach based on cumulative distribution, regarding the length for lines/cables types and the power rating for loads, is presented to prioritize which loads, lines and cables the meters should be installed at to have the most effect on model validation. Chapter 1: Dynamic Voltage Restorer (DVR)

#### **1.1. Introduction**

Sensitive loads such as medical equipment, factory automations, semiconductordevice manufacturer, and paper manufacturer are vulnerable to power-supply disturbances [1], [2]. Consequently, the demand for high power quality and voltage stability becomes a pressing issue. In the present, voltage sags are recognized as a serious threat to the power grid and are a frequently occurring power-quality problem and have costly consequence such as sensitive loads tripping and production loss [3]–[6]. Both the "Canadian Power Quality Survey" conducted by the Canadian Electrical Associate (CEA) in 1991 on 550 customer sites and the "Distribution System Power Quality Survey" conducted by the Electric Power Research Institute (EPRI) on 222 utility distribution feeders between 1993 and 1995 have shown that voltage sags are the most frequent power quality events [7]. According to an EPRI report, the economic losses due to poor power quality are \$400 billion dollars a year in the U.S. alone [8], [9]. These disturbances occur due to, e.g., short circuits in upstream power transmission line or parallel power distribution line connected to the point of common coupling (PCC), inrush currents involved with the starting of large machines, sudden changes of load, energizing of transformers or switching operations in the grid [10], [11]. According to the IEEE STD 1959-1995 and IEEE STD 1564-2014 (IEEE Guide for Voltage Sag Indices), voltage sag is defined as a decrease of 0.1 to 0.9 p.u. in the rms voltage at system frequency and with the duration of half a cycle to one minute [12]–[14]. According to the definition and nature of voltage sag, it can be found that this kind of disturbance is a transient phenomenon whose causes are classified as lowor medium-frequency transient events [12].

Due to the above mentioned effects of voltage sags on sensitive loads, compensating voltage sags and minimizing their effects is necessary. Traditional methods of suppressing voltage variations include static transfer switches (STS), tap-changing transformers, and uninterruptible power supplies (UPS) [15]. However, tap-changing transformer is bulky, costly and not fast enough to eliminate the voltage sag effects at load side. On the other hand, UPS is bulky and expensive device which needs energy storage such as battery. Furthermore, UPS systems are typically designed for small loads, such as a computer mainframe or low-power safety critical systems. Since voltage sags are the most troublesome on the distribution network, where loads can range from tens of kilowatts to a few megawatts, the cost of a UPS system is prohibitive as the UPS would need to be able to withstand not only the load current, but also the full load voltage [15]. There are custom power devices such as static synchronous compensator (STATCOM), distribution-STATCOM (D-STATCOM), unified power-quality conditioner (UPQC), and dynamic voltage restorer (DVR) as power electronics based solutions to minimize costly outcomes of voltage sags [15]. The custom power devices are developed and installed at consumer point to meet the power quality standards such as IEEE-519. Among the available technologies, DVR is more effective and direct solution (it only needs to withstand part of the load voltage) for "restoring" the quality of voltage at its load-side terminals when the quality of voltage at its source-side terminals is disturbed [16]–[21].

DVRs compensate voltage sags by injecting the proper amount of voltages in series with the supply voltage, in order to maintain the load side voltage within the specification [22]–[25]. Typically, a DVR consists of an energy storage device and an inverter which is coupled via a series transformer to the grid. The purpose of inverter is injecting the series voltage with a controlled magnitude and phase angle to restore the quality of load voltage and avoid load tripping [6], [26], [27]. The basic concept of DVR is depicted in Figure 1.1.

Figure 1.1. General schematic of DVR.

The control system of DVR has two main parts: detection of the voltage sag and determination of the reference signal. The voltage sag detection part measures and analyzes the grid voltage to detect any voltage disturbance. There are different detection methods such as peak measurement, rms measurement, dq0 components measurement [1], [28], decoupled positive- and negative-sequence dq0 components measurement [27], [29]–[31] and phasor parameters estimation using Kalman filters [32], [33] or complex Fourier Transformation as reported in articles [34], [35]. The voltage sag detection methods will be investigated in detail in Chapter 2. The second part of DVR control system is determination of the DVR reference signal of series injected voltage. The method to determine reference signal of series injected voltage is based on the type of voltage sag compensation method, type of energy storage device and its ability to support active power. There are four basic methods of voltage compensation which are in-phase, pre-sag,

energy minimized and hybrid compensation methods.

This chapter is organized as follows. Section 1.2 investigates four mentioned compensation methods with the detailed discussions and analysis. Moreover, a comparison of the mentioned compensation methods is conducted to highlight their advantages and disadvantages. In Section 1.3, DVR circuit topologies are discussed regarding the possible configurations and approaches to feed active power to DVR dc link since DVR may need active power to restore the voltage quality of sensitive loads. In addition, effect of the upstream step-down transformer on causing the zero-sequence voltage sag is discussed in Section 1.4. In Section 1.5, DVR reference voltage determination is explained in detail and the required equations are obtained based on d-q synchronous reference frame. In Section 1.6, a new topology of DVR based on high-frequency isolation transformer is proposed to reduce the size of transformer and its control strategy is presented. Another advantage of the proposed DVR configuration is that it does not need any bulky dc link capacitor or energy storage to make a flat dc link voltage. This fact causes to reduce the size of the DVR and increase the reliability of the circuit. The proposed DVR circuit is based on dc-ac converters connected in series to split the main dc link between the inputs of dc-ac converters. This feature makes it possible to use modular dc-ac converters and utilize low-voltage components in these converters whenever it is required to use DVR in medium-voltage application. In Section 1.7, simulation results of the proposed DVR topology are provided to show its performance and effectiveness to compensate the voltage sag.

#### 1.2. Review of Voltage Sag Compensation Methods

As mentioned previously, there are four different compensation methods to restore the voltage quality of sensitive loads by DVR. In the following subsections, these four methods are explained in detail and compared to emphasize their pros and cons.

#### 1.2.1. In-Phase Voltage Sag Compensation Method

The in-phase compensation strategy is the straightest forward method in which the injected DVR voltage is in phase with the supply side voltage regardless of pre-fault condition [1], [5], [7], [22]. The phasor diagram of the in-phase compensation strategy is shown in Figure 1.2 in which the dashed quantities  $(V'_{grid}, V'_{load}, V'_{dvr} \text{ and } I'_{load})$  indicate variables after the sag. The phasors prior to the sag are represented by  $V_{grid}$ ,  $V_{load}$  and  $I_{load}$ . Moreover, angle of  $\phi$  is phase angle difference between the load voltage and load current phasors and angle of  $\delta$  is phase jump of grid voltage during the voltage sag. All of the load and grid voltage phasors are line-to-neutral voltages. To realize this strategy, phase-locked loop (PLL) has to be synchronized to the grid voltage all the time and therefore, PLL will not be locked during the compensation [1], [22].

Figure 1.2. Phasor diagram of in-phase compensation strategy.

It is worth mentioning that this compensation strategy leads to minimize the magnitude of series injected voltage by DVR in comparison with other compensation methods [1], [5]. Consequently, voltage rating of dc link in this method is minimal. However, in-phase compensation method just leads to correct the load voltage magnitude and can't correct the phase jump at load voltage if voltage sag occurs with phase jump. Therefore, the distortions of phase changes are not compensated and as a consequence, a phase jump will occur at the load side which may lead to transient and circulating currents depending on the load type [1]. Regarding the amount of active power exchanged between DVR and power grid, this method injects both active and reactive power. The reason for injecting active power is that injected voltage phasor is not certainly perpendicular to the load current phasor. Consequently, it needs the active power to be supplied at dc link side otherwise this method can't compensate deep voltage sags for a long time. Thus, without supporting the active power at the dc link, it will drop during the compensation and as a

result, the maximum producible voltage of DVR will decrease. Furthermore, the modulation index of series converter will increase continuously and may hit the maximum value; therefore, over-modulation may occur causing undesirable harmonics at the output voltage of power converter.

The power rating of DVR controlled by in-phase compensation method is as follows:

$$S_{DVR} = \sum_{k=a,b,c} \left[ V'_{DVR,k} \cdot I_{load} \right]$$

Eq. 1.1

where,  $V'_{DVR,k}$  is the rms of DVR injected voltage in phase k and  $I_{load}$  is rms of load current. The amount of active power exchanged between the DVR and power grid is as follows:

$$P_{DVR} = P_{load} - P_{grid} = \begin{bmatrix} 3 \cdot V_{load} \cdot I_{load} \cdot \cos(\phi) \\ -\sum_{k=a,b,c} \begin{bmatrix} V'_{grid,k} \cdot I_{load} \cdot \cos(\phi) \end{bmatrix} \end{bmatrix}$$

Eq. 1.2

where,  $V'_{grid,k}$  is the rms of line-to-neutral grid voltage in phase k and  $V_{Load}$  is rms of line-to-neutral load voltage. The magnitude of injected voltage is:

$$V'_{DVR,k} = \sqrt{2} \cdot \left| V_{load} - V'_{grid,k} \right| \text{ and } k = a, b, c$$

Eq. 1.3

and the phase angle of injected voltage phasor is the same as phase angle of grid voltage phasor.

#### 1.2.2. Pre-Sag Voltage Compensation Method

A commonly used method for compensating voltage sags is restoring the load voltage to the level and condition before the sag [6], [22]. Therefore, the amplitude and the phase of the voltage before the sag have to be exactly restored [6], [22]. The phasor diagram of the pre-sag compensation strategy is shown in Figure 1.3. In this figure, the dashed quantities  $(V'_{grid}, V'_{load}, V'_{dvr}$  and  $I'_{load}$ ) indicate variables after the sag. The phasors prior to the sag are represented by  $V_{grid}$ ,  $V'_{load}$  and  $I_{load}$ . Moreover, angle of  $\phi$  is phase angle difference between the load voltage and load current phasors and angle of  $\delta$  is phase jump of grid voltage during the voltage sag. All of the load and grid voltage phasors are line-to-neutral voltages. For this strategy, the PLL is synchronized with the load voltage. As soon as a failure occurs, the PLL will be locked and so, the phase angle can be restored [1], [22].

Figure 1.3. Phasor diagram of pre-sag compensation strategy.

The magnitude of DVR injected series voltage in this compensation method is not

minimal and it depends on both amount of voltage drop and phase jump during the voltage sag because the phase jump of the grid voltage has also to be compensated by the DVR. Consequently, DVR has to be designed for the highest possible voltage sag compensation. Furthermore, voltage rating of dc link in DVR controlled with this method needs to be larger than one controlled with in-phase compensation method. Moreover, this compensation strategy leads to the lowest distortions at the load-side because both phase angle and magnitude of the voltage at the load-side are restored during the sag. Thus, the sensitive load doesn't sense any voltage disturbance. This method is so reliable and proper to protect sensitive loads without having any possible transient and circulating currents. Moreover, even if the phase jumps of grid voltage in each phase are not the same, DVR controlled with pre-sag compensation method can eliminate the voltage disturbance completely. This strategy is able to compensate any kind of voltage sags including balanced or unbalanced voltage sags with or without any phase-variations in each phase of grid voltages.

Regarding the amount of power exchanged between DVR and power grid, pre-sag compensation method injects both active and reactive power depends on magnitude of injected voltage, grid voltage phase jump and phase angle difference between load voltage and load current phasors. The reason for injecting active power is that the injected voltage phasor is not certainly perpendicular to the load current phasor in this method as like as inphase compensation method. Consequently, it needs the active power to be supplied at dc link side otherwise this method can't compensate deep voltage sags for a long time. Thus, without supporting the active power at the dc link, dc link voltage will drop during the compensation and as a result, the maximum producible voltage of DVR will decrease and the modulation index of series converter will increase continuously and therefore, overmodulation may occur.

The power rating of DVR controlled by pre-sag compensation method is same as Eq. 1.1. The amount of active power exchanged between the DVR and power grid is as follows:

$$P_{DVR} = P_{load} - P_{grid} = \begin{bmatrix} 3 \cdot V_{load} \cdot I_{load} \cdot \cos(\phi) \\ -\sum_{k=a,b,c} \begin{bmatrix} V'_{grid,k} \cdot I_{load} \cdot \cos(\phi - \delta_k) \end{bmatrix} \end{bmatrix}$$

Eq. 1.4

where,  $\delta_k$  is the phase jump in phase k. The magnitude of injected voltage is:

$$V'_{DVR,k} = \sqrt{2} \cdot \sqrt{\left(V_{load}\right)^2 + \left(V'_{grid,k}\right)^2 - 2 \cdot V_{load} \cdot V'_{grid,k} \cdot \cos(\delta_k)}$$

Eq. 1.5

and the phase angle of injected voltage phasor is:

$$\angle V'_{DVR,k} = \arctan\left(\frac{V_{load} \cdot \sin(\varphi) - V'_{grid,k} \cdot \sin(\varphi - \delta_k)}{V_{load} \cdot \cos(\varphi) - V'_{grid,k} \cdot \cos(\varphi - \delta_k)}\right)$$

Eq. 1.6

#### 1.2.3. Energy-Minimized Voltage Compensation Method

As mentioned and discussed in subsections 1.2.1 and 1.2.2, the in-phase and presag compensation methods injects active power during compensation time. Thus, the active power should be supported at the dc link; otherwise, the dc link voltage will drop continuously. However, there is another compensation method called energy minimized compensation method to minimize any exchange of active power in compensation process. The basic principle of this method is injecting to or absorbing from power grid as much reactive power as possible to compensate the voltage sag [1], [5], [22], [36], [37]. Therefore, the DVR voltage must be controlled in such a way that the DVR does not exchange active power with power grid and as a result, the amount of active power needed from the dc-link can be minimized. Compensating voltage sags with pure reactive power is possible as long as the voltage sag is quite shallow and satisfies the required condition (will be discussed later) and therefore, the compensation time is not limited.

Besides the significant advantage of not requiring active power, this strategy has in most cases two major disadvantages. First, a phase jump occurs when this method is applied as voltage sag compensation method; thus, it is not suitable for sensitive loads in which the voltage jump is a critical issue [1]. Even if there is not any phase jump in grid voltage during the voltage sag, this method causes a phase jump at load voltage to minimize the amount of active power exchanged between DVR and power grid. Second drawback of this method is that the amplitude of DVR injected voltage may become quite high in comparison with two previous methods explained in subsections 1.2.1 and 1.2.2. Thus, the voltage rating of dc link is higher than the case in which the DVR controlled by two previously mentioned methods. This compensation strategy is explained in detail for two cases of balanced and unbalanced voltage sags as following subsections.

#### 1.2.3.1. Balanced voltage sag:

In this case, it is assumed that the phase jump and amplitude drop of grid voltage in all three phases during the voltage sag are equal. The voltage phasors for the energy minimized compensation strategy in the balanced voltage sag are depicted in Figure 1.4 in which  $\alpha$  is the phase variation of load voltage after compensation. As shown in Figure 1.4, the phasor of DVR series injected voltage is perpendicular to the load current phasor to avoid exchanging the active power between DVR and power grid. In Figure 1.4, the dashed quantities  $(V'_{grid}, V'_{load}, V'_{dvr}$  and  $I'_{load})$  indicate variables after the sag. The phasors prior to the sag are represented by  $V_{grid}$ ,  $V'_{load}$  and  $I_{load}$ . All of the load and grid voltage phasors are line-to-neutral voltages.

Figure 1.4. Phasor diagram of energy minimized compensation strategy for balanced voltage sag.

In Figure 1.4, the angle of  $\alpha$  is unknown which is calculated by making the required active power of DVR equals to zero as follows:

$$P_{DVR} = P_{load} - P_{grid} = 0$$

Eq. 1.7

$$P_{load} = 3 \cdot V_{load} \cdot I_{load} \cdot \cos(\phi)$$

Eq. 1.8

$$P_{grid} = 3 \cdot V'_{grid} \cdot I_{load} \cdot \cos(\phi - \alpha - \delta)$$

Eq. 1.9

where,  $P_{grid}$ ,  $P_{load}$  and  $P_{DVR}$  are the supplied active power by power grid, required active power of load and the exchanged active power of DVR, respectively. By substituting Eq. 1.8 and Eq. 1.9 into Eq. 1.7, it can be written as follows:

$$\alpha = \phi - \delta - \cos^{-1} \left( \frac{V_{load} \cdot \cos(\phi)}{V'_{grid}} \right)$$

Eq. 1.10

According to above equation, following condition must be satisfied:

$$V_{load} \cdot \cos(\phi) \le V'_{grid}$$

Eq. 1.11

Otherwise, the angle of  $\alpha$  should be obtained from Eq. 1.12 and in this condition, the amount of active power exchanged between DVR and power grid can't be zero.

$$\frac{d}{d\alpha}(P_{DVR}) = 0$$

Eq. 1.12

which results in:

$$\sin\left(\varphi - \delta - \alpha\right) = 0$$

Eq. 1.13

and:

$$\alpha = \varphi - \delta$$

Eq. 1.14

The magnitude of DVR series injected voltage can be calculated as follows:

$$V_{DVR} = \sqrt{2} \cdot \sqrt{\left(V_{load}\right)^2 + \left(V_{grid}'\right)^2 - 2 \cdot V_{load} \cdot V_{grid}' \cdot \cos\left(\delta + \alpha\right)}$$

Eq. 1.15

If Eq. 1.11 is satisfied, the phase angle of DVR series injected voltage phasor is:

$$\angle V'_{DVR} = \alpha + \frac{\pi}{2}$$

Eq. 1.16

otherwise:

$$\angle V'_{DVR} = \arctan\left(\frac{V_{load} \cdot \sin(\varphi + \alpha) - V'_{grid} \cdot \sin(\varphi - \delta)}{V_{load} \cdot \cos(\varphi + \alpha) - V'_{grid} \cdot \cos(\varphi - \delta)}\right)$$

Eq. 1.17

As explained, the Eq. 1.11 should be satisfied to avoid exchanging active power between DVR and power grid. It means that exchanging active power is not avoidable for all conditions. Figure 1.5 shows the conditions in which avoiding active power exchange is possible (illustrated with light gray color) or impossible (illustrated with purple color).

Figure 1.5. Possibility (illustrated with gray color) and impossibility (illustrated with purple color) of avoiding active power exchanged between DVR and power grid during the balanced voltage sag.

As shown in Figure 1.5, the power factor of load should be less than grid voltage (in p.u.) to avoid active power exchange. For example, if the grid voltage drops to 0.7 p.u., the power factor should be less than 0.7 to avoid exchanging active power between DVR and power grid. However, this is not likely in industry because industries prefer to increase power factor from financial point of view by using shunt switching capacitor bank or reactive power compensator. Thus, in most cases of deep voltage sag, energy minimized compensation method is not able to avoid active power exchange completely but it can minimize it. To suppress this drawback, a solution has been presented in [36] to decrease the power factor intentionally during the voltage sag by connecting a thyristor-switched inductor in parallel with load as shown in Figure 1.6. In this configuration, the thyristor switch turns on during the voltage sag to connect the inductor parallel with load to lower

the power factor and make it possible to compensate voltage sag without exchanging active power between DVR and power grid. However, drawback of this solution is high-power low-frequency inductor which can be a bulky and costly.

Figure 1.6. Schematic of DVR with shunt thyristor-switched inductor to lower the power factor intentionally during the voltage sag.

#### 1.2.3.2. Unbalanced voltage sag:

In this case which is more common than previous one discussed in subsection 1.2.3.1, it is assumed that the variations of voltage phase angle and amplitude in all three phases are not the same. The voltage phasors for the energy minimized strategy in the unbalanced voltage sag are shown in Figure 1.7 just for one phase. In this method, the phasor of DVR series injected voltage is not perpendicular to the load current phasor. Thus, the amount of active power exchanged between DVR and power grid in each phase is not zero. But the reference signal for series injected voltage can be determined in such a way that total exchanged active power in all three phases becomes zero. It means that, for example, the exchanged active power in one phase is positive and in other two phases is negative but the total exchanged active power is zero.

Figure 1.7. Phasor diagram of energy minimized compensation strategy for unbalanced voltage sag.

This compensation method either minimizes or avoids the requirement of supporting active power in dc link depending on load power factor and amount of voltage drop. It is worth mentioning that all three power converters in each phase should have common dc link capacitor to add the exchanged active power of each phase together and as a result, make the total exchanged active power equal to zero. Otherwise, if there is not common dc link for all three power converters of each phase, it is not possible to minimize/avoid the required active power as well as to compensate the unbalanced voltage sag and make the load voltage balanced.

As shown in Figure 1.7, the angle of  $\alpha$  is unknown and should be calculated in such a way that the total exchanged active power in all three phases becomes zero. Thus, it can be written as follows:

$$P_{DVR} = P_{load} - P_{grid} = 0$$

Eq. 1.18

$$P_{load} = 3 \cdot V_{load} \cdot I_{load} \cdot \cos(\phi)$$

Eq. 1.19

$$P_{grid} = \sum_{k=a,b,c} \left[ V'_{grid,k} \cdot I_{load} \cdot \cos(\phi - \alpha - \delta_k) \right]$$

Eq. 1.20

By substituting Eq. 1.20 and Eq. 1.19 into Eq. 1.18, it can be written as follows:

$$\alpha = \phi - \lambda - \cos^{-1} \left( \frac{3 \cdot V_{load} \cdot \cos(\phi)}{\sqrt{X^2 + Y^2}} \right)$$

Eq. 1.21

where,

$$X = \sum_{k=a,b,c} \left[ V'_{grid,k} \cdot \cos(\delta_k) \right]$$

Eq. 1.22

$$Y = \sum_{k=a,b,c} \left[ V'_{grid,k} \cdot \sin(\delta_k) \right]$$

Eq. 1.23

$$\lambda = \tan^{-1} \left( \frac{Y}{X} \right)$$

Eq. 1.24

According to Eq. 1.21, Eq. 1.25 must be satisfied; otherwise, the angle of  $\alpha$  should be obtained from Eq. 1.26 and in this condition, the required active power of DVR can be minimized rather than be zero.

$$3 \cdot V_{load} \cdot \cos(\phi) \le \sqrt{X^2 + Y^2}$$

Eq. 1.25

$$\frac{d}{d\alpha}(P_{DVR}) = 0$$

Eq. 1.26

which results as:

$$\frac{d}{d\alpha} \left( P_{grid} \right) = 0$$

Eq. 1.27

$$\sum_{k=a,b,c} \left[ V'_{grid,k} \cdot \sin\left(\phi - \alpha - \delta_k\right) \right] = 0$$

Eq. 1.28

and, it can be pointed out:

$$\alpha = \varphi - \lambda$$

Eq. 1.29

The magnitude of DVR series injected voltage in each phase can be calculated as follows:

$$V'_{DVR,k} = \sqrt{2} \times \sqrt{\left(V_{load}\right)^2 + \left(V'_{grid,k}\right)^2 - 2 \cdot V_{load} \cdot V'_{grid,k} \cdot \cos\left(\delta_k + \alpha\right)}$$

Eq. 1.30

and, the phase angle of DVR series injected voltage phasor in each phase is:

$$\angle V'_{DVR,k} = \arctan\left(\frac{V_{load} \cdot \sin(\varphi + \alpha) - V'_{grid,k} \cdot \sin(\varphi - \delta_k)}{V_{load} \cdot \cos(\varphi + \alpha) - V'_{grid,k} \cdot \cos(\varphi - \delta_k)}\right)$$

Eq. 1.31

As like as balanced voltage sag, compensation of deep unbalanced voltage sag with higher power factor without requiring the active power is impossible. Thus, using thyristor-switched inductor, as shown in Figure 1.6, during the voltage sag to lower the power factor can make it possible to compensate deep unbalanced voltage sag without any active power.

## 1.2.4. Hybrid Voltage Compensation Method

As discussed in subsections 1.2.1 to 1.2.3, each compensation method has its own advantages and disadvantages. From advantages point of view, the magnitude of injected voltage is minimal in the in-phase compensation method and the amount of active power exchanged between DVR and power grid is minimal in the energy minimized compensation method. About the pre-sag compensation method, it minimizes the amount of distortion at the load side and can compensate both voltage drop and phase jump. From disadvantages point of view, the in-phase compensation method can't compensate the unbalanced voltage sag completely if the phase variations in all three phases are not the same; it means that although the magnitude of load voltage can be restored but the phase angle of load voltages may remain unbalanced. The energy minimized compensation method can't avoid phase jump at the load voltage and the magnitude of injected voltage is quite high. About the pre-sag compensation method, it needs active power during the voltage sag which requires supporting active power at dc link or using ultra capacitor or battery at the dc link. However, it can be beneficial to combine methods with each other and use their collective advantages. It has been presented in [38], [39] to combine the inphase compensation method and pre-sag compensation method. Thus, it makes it possible to have minimum distortion at load voltage due to the pre-sag compensation method and to have minimum voltage amplitude due to in-phase compensation method. The procedure of method proposed in [38], [39] is as follows. When the voltage sag is detected, DVR controlled by pre-sag compensation method injects the series voltage to restore both magnitude and phase angle of load voltage and thus, the load doesn't sense any distortion.

This method requires the active power which requires use the stored energy of dc link capacitor, discharge it and decrease the dc link voltage continuously. This issue results in increase of the modulation index of power converter. After a while, depends on voltage sag depth and phase jump, the modulation index reaches to a pre-determined value. At this time, the PLL which was locked to pre-sag condition is unblocked and starts to be synchronized with power grid voltage. The synchronization process and changing the compensation method from pre-sag to in-phase is accomplished in several cycles to avoid any sudden phase jump at load voltage. Therefore, due to controlling DVR with in-phase compensation method, the magnitude of required injected voltage reduces and dc link capacitor can be discharged even more.

Figure 1.8. Phasor diagram showing the procedure of hybrid voltage compensation method.

Figure 1.8 shows the explained procedure in 4 steps. Although this hybrid method has advantages of pre-sag and in-phase methods simultaneously, it still has disadvantage of in-phase compensation method. It means that if the phase variations of all three phases are not the same, the hybrid method can't restore the phase jump at load voltage. The reason is that after changing the compensation method from pre-sag to in-phase, DVR can't compensate phase jumps at each phase individually. On the other hand, the procedure which should be applied when the voltage sag is cleared has not been discussed in [38], [39] and it can be a drawback for the hybrid compensation method. Moreover, it has not been discussed how the hybrid method works if the voltage sag is cleared during the

transition from pre-sag method to in-phase method. Because, in real cases, it is unknown how long the voltage sag takes and when it will be cleared after starting. Table 1.1 illustrates the comparison between four mentioned methods to summarize the advantages and disadvantages.

#### TABLE 1.1

# COMPARISON OF IN-PHASE, PRE-SAG, ENERGY-MINIMIZED AND HYBRID COMPENSATION METHODS.

| Method                          | Advantage                                                                                                                                                                                                                                                                                                                 | Disadvantage                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| In-Phase                        | <ol> <li>The magnitude of the injected voltage is<br/>minimal.</li> <li>The voltage rating of the dc link and<br/>DVR is minimal.</li> </ol>                                                                                                                                                                              | <ol> <li>It needs active power during<br/>compensation.</li> <li>It can't restore the phase jump if the<br/>variations of phase jump in three phases are<br/>asymmetric.</li> </ol>                                                                                                                                                                                                    |

| Pre-Sag                         | <ol> <li>It restores both the voltage drop and the phase jump. Thus, the sensitive load doesn't sense any distortion.</li> <li>It avoids any circulating or transient current at load side.</li> <li>It can compensate any kind of voltage sag regardless of unbalanced voltage drop or unbalanced phase jump.</li> </ol> | 1) It needs active power during compensation.                                                                                                                                                                                                                                                                                                                                          |

| Energy<br>Minimized             | <ol> <li>The amount of exchanged active power<br/>between DVR and power grid is minimal.</li> <li>It may not require active power during<br/>compensation.</li> </ol>                                                                                                                                                     | <ol> <li>The magnitude of injected voltage is<br/>almost high.</li> <li>The voltage rating of dc link and DVR is<br/>almost high.</li> <li>For a load with high power factor,<br/>compensation of deep voltage sag requires<br/>active power.</li> <li>It causes phase jump at load voltage<br/>even if there is not any phase jump in gird<br/>voltage during voltage sag.</li> </ol> |

| Hybrid<br>(in-phase<br>pre-sag) | <ol> <li>It restores both voltage drop and phase<br/>jump just at the beginning.</li> <li>It avoids any circulating or transient<br/>current at load side just at the beginning.</li> </ol>                                                                                                                               | <ol> <li>It needs active power during<br/>compensation.</li> <li>It can't restore the phase jump if the<br/>variations of phase jump in three phases are<br/>asymmetric.</li> </ol>                                                                                                                                                                                                    |

## **1.3.** Review of Configurations to Support Active Power at DVR DC Link

Several configurations have been presented in literature to support active power at DVR dc link. This section discusses about the different configurations and their pros and cons.

## **1.3.1.** Capacitor Supported DVR

Figure 1.9 shows a schematic of a capacitor-supported DVR connected via a linefrequency transformer in series with power grid and critical load [5], [17], [27], [36], [40]-[43]. In [18], the super capacitor has been used at dc link to increase the amount of stored active power to be able to compensate the long-duration voltage sag. In this configuration, the required active power needs to be provided by capacitor since there is not any energy storage which results in decreasing the capacitor terminal voltage. Decrease of dc link capacitor voltage leads to increase of the modulation index of series converter and therefore, over-modulation may occur causing undesirable harmonics at the output voltage of power converter. Consequently, there is a minimum dc voltage below which the inverter of the DVR cannot generate the required voltage. Thus, the size of the dc capacitor needed to supply active power can be expressed as Eq. 1.32 in terms of maximum allowable dclink voltage ( $V_{DC,max}$ ), minimum allowable dc-link voltage ( $V_{DC,min}$ ), sag duration ( $T_{sag}$ ), DVR injected active power  $(P_{inj})$  and power loss  $(P_{loss})$ . According to Eq. 1.32, it is clear that large capacitors in the dc-link energy storage are needed to effectively mitigate longduration and deep voltage sags.