# $\begin{array}{c} {\rm UNIVERSITY\ OF\ CALIFORNIA,} \\ {\rm IRVINE} \end{array}$

# Graph Neural Network for Integrated Circuits and Cyber-Physical Systems Security ${\bf DISSERTATION}$

submitted in partial satisfaction of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

in Electrical and Computer Engineering

by

Rozhin Yasaei

Dissertation Committee: Professor Mohammad Abdullah Al Faruque, Chair Professor Fadi Kurdahi Assistant Professor Zhou Li

# **DEDICATION**

I dedicate this to my incomparable parents, Mino and Sasan. Their endless outpouring of love, unwavering support, and constant words of encouragement have fostered in me such resilience and determination that have been invaluable during my journey. Their lessons of tenacity continue to reverberate, shaping my perspective.

In addition, my heartfelt gratitude extends to my brother, Farbod. His steadfast presence, undying support, and unwavering faith in me have fortified my resolve, instilling in me the strength and confidence needed to overcome the most daunting of obstacles.

# TABLE OF CONTENTS

|              |       |        |                                              | Page |

|--------------|-------|--------|----------------------------------------------|------|

| $\mathbf{L}$ | IST ( | OF FIC | GURES                                        | vii  |

| $\mathbf{L}$ | IST ( | OF TA  | BLES                                         | ix   |

| $\mathbf{A}$ | CKN   | OWLI   | EDGMENTS                                     | X    |

| $\mathbf{V}$ | ITA   |        |                                              | xi   |

| $\mathbf{A}$ | BST   | RACT   | OF THE DISSERTATION                          | xiv  |

| 1            | Intr  | oducti | ion                                          | 1    |

|              | 1.1   | Relate | ed Works and Research Challenges             | . 4  |

|              | 1.2   | Disser | tation Contributions                         | . 6  |

|              |       | 1.2.1  | Hardware Security                            | . 6  |

|              |       | 1.2.2  | Embedded and Cyber-Physical Systems Security | . 9  |

|              | 1.3   | Disser | tation Organization                          | . 11 |

| 2            | Har   | dware  | Trojan Detection                             | 13   |

|              | 2.1   | Introd | luction                                      | . 13 |

|              |       | 2.1.1  | Motivational Example                         | . 15 |

|              |       | 2.1.2  | Research Challenges                          | . 16 |

|              |       | 2.1.3  | Chapter Contributions                        | . 17 |

|              |       | 2.1.4  | Threat Model                                 | . 18 |

|              | 2.2   | Relate | ed Works and Background                      | . 19 |

|              |       | 2.2.1  | Hardware Trojan                              | . 19 |

|              |       | 2.2.2  | Hardware Trojan Detection Methods            |      |

|              |       | 2.2.3  | Hardware as a Graph                          |      |

|              | 2.3   | Metho  | odology                                      |      |

|              |       | 2.3.1  | Graph Convolutional Networks                 |      |

|              |       | 2.3.2  | Attention-based Pooling                      | . 29 |

|              |       | 2.3.3  | Graph Embedding Generation                   |      |

|              |       | 2.3.4  | Multi-Layer Perceptron Classifier            |      |

|              |       | 2.3.5  | GNN for HT Detection in RTL                  |      |

|              |       | 2.3.6  | RTL Graph Generation                         |      |

|              |       | 2.3.7  | HT Detection Model for RTL                   |      |

|   |                   | 2.3.8 GNN for HT Detection in Netlist    | 35         |

|---|-------------------|------------------------------------------|------------|

|   |                   | 2.3.9 HT Benchmarks Synthesis to Netlist | 35         |

|   |                   | 2.3.10 Netlist Graph Generation          | 36         |

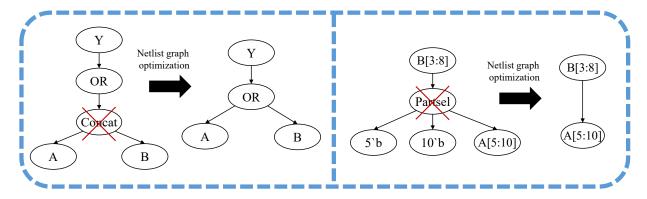

|   |                   | 2.3.11 Netlist Graph Optimization        | 36         |

|   |                   | 2.3.12 Netlist Graph Normalization       | 38         |

|   |                   | 2.3.13 HT Detection Model for Netlist    | 39         |

|   | 2.4               |                                          | 40         |

|   |                   |                                          | 40         |

|   |                   |                                          | 41         |

|   |                   |                                          | <br>43     |

|   |                   |                                          | 43         |

|   |                   | V 1 1                                    | 46         |

|   |                   |                                          | 16<br>16   |

|   |                   |                                          | 18         |

|   | 2.5               | v                                        | 49         |

|   | $\frac{2.5}{2.6}$ |                                          | 49         |

|   | 2.0               | Chapter Concluding Itematks              | ŧθ         |

| 3 | Har               | dware Trojan Localization 5              | <b>52</b>  |

| _ | 3.1               | <b>o</b>                                 | 52         |

|   | 3.2               |                                          | 55         |

|   | 3.3               | $\sim$                                   | 56         |

|   | 3.4               | <u> </u>                                 | 57         |

|   | 5.1               | 0                                        | 57         |

|   |                   | ÿ                                        | 58         |

|   | 3.5               |                                          | 59         |

|   | 0.0               | Oi                                       | 30         |

|   |                   |                                          | 31         |

|   |                   |                                          | 32         |

|   |                   |                                          | 35         |

|   |                   | * 0                                      | 35         |

|   | 3.6               | 1                                        | 59         |

|   | 0.0               |                                          | 59         |

|   |                   |                                          | 71         |

|   |                   |                                          | 72         |

|   |                   | 1                                        | 75         |

|   |                   |                                          |            |

|   | 27                | 1 0                                      | 76<br>77   |

|   | 3.7               | Chapter Concluding Remarks               | 77         |

| 4 | Har               | dware IP Piracy Detection 7              | <b>7</b> 9 |

| _ | 4.1               |                                          | 79         |

|   | 1.1               |                                          | 32         |

|   |                   | 1                                        | 32         |

|   |                   | 9                                        | 33         |

|   | 4.2               | 1                                        | 34         |

|   | 7.4               |                                          | 24<br>27   |

|       | 4.2.2 Graph Neural Networks                                          | 8  |  |  |  |  |

|-------|----------------------------------------------------------------------|----|--|--|--|--|

| 4.3   | Methodology                                                          | 8  |  |  |  |  |

|       | 4.3.1 Threat Model                                                   | 8  |  |  |  |  |

|       | 4.3.2 Hardware Data Flow Graph Extraction                            | 8  |  |  |  |  |

|       | 4.3.3 Hardware IP Piracy Detection Algorithm                         | 8  |  |  |  |  |

| 4.4   | Evaluation                                                           | 9  |  |  |  |  |

|       | 4.4.1 Dataset                                                        | 9  |  |  |  |  |

|       | 4.4.2 IP Piracy Detection Accuracy and Timing                        | 9  |  |  |  |  |

|       | 4.4.3 Embedding Visualization                                        | 9  |  |  |  |  |

|       | 4.4.4 Similarity Score Results                                       | 9  |  |  |  |  |

|       | 4.4.5 Piracy Detection in Obfuscated Netlists                        | 9  |  |  |  |  |

|       | 4.4.6 Comparison with Rival Methods                                  | 9  |  |  |  |  |

| 4.5   | Chapter Concluding Remarks                                           | 9  |  |  |  |  |

| 5 Cor | ntext-Aware Adaptive Anomaly Detection in IoT through Sensor As-     |    |  |  |  |  |

| soc   | lation                                                               | 9  |  |  |  |  |

| 5.1   | Introduction                                                         | 9  |  |  |  |  |

|       | 1                                                                    | 10 |  |  |  |  |

|       |                                                                      | 10 |  |  |  |  |

|       | 5.1.3 Research Challenges                                            | 10 |  |  |  |  |

|       | 1                                                                    | 10 |  |  |  |  |

| 5.2   | Related Works                                                        | 10 |  |  |  |  |

| 5.3   | Anomaly Detection Methodology                                        | 10 |  |  |  |  |

|       | 5.3.1 Context Generation                                             | 10 |  |  |  |  |

|       | 5.3.2 Sensor Association                                             | 10 |  |  |  |  |

|       | 5.3.3 Predictive Model                                               | 11 |  |  |  |  |

|       | 5.3.4 Anomaly Detection                                              | 11 |  |  |  |  |

|       | 5.3.5 Model Adaptation                                               | 11 |  |  |  |  |

| 5.4   | Results and Evaluation                                               | 11 |  |  |  |  |

|       | 5.4.1 Fog Computing Architecture                                     | 11 |  |  |  |  |

|       |                                                                      | 11 |  |  |  |  |

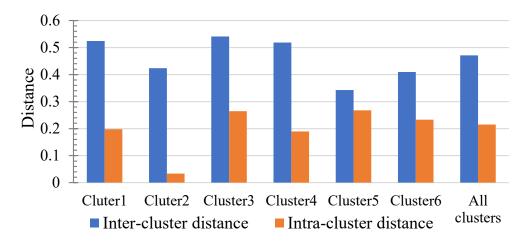

|       | 5.4.3 Sensor Association Evaluation                                  | 11 |  |  |  |  |

|       | 5.4.4 Anomaly Detection Evaluation                                   | 11 |  |  |  |  |

|       | 5.4.5 Robustness                                                     | 12 |  |  |  |  |

|       | 5.4.6 Case Study                                                     | 12 |  |  |  |  |

|       | 0 ,                                                                  | 12 |  |  |  |  |

|       | 5.4.8 Aliveness Assessment                                           | 12 |  |  |  |  |

| 5.5   | Chapter Concluding Remarks                                           | 12 |  |  |  |  |

|       | lti-Modal Data Fusion for Anomaly Detection in IoT Physical and Net- |    |  |  |  |  |

|       | work Layers                                                          |    |  |  |  |  |

| 6.1   |                                                                      | 12 |  |  |  |  |

|       | 1                                                                    | 12 |  |  |  |  |

|       | 6.1.2 Research Challenges and Opportunities                          | 12 |  |  |  |  |

|       |                                                                      | 12 |  |  |  |  |

| 6.2        | Relate | ed Works and Background                                    | 130 |

|------------|--------|------------------------------------------------------------|-----|

|            | 6.2.1  | Network Intrusion Detection                                | 130 |

|            | 6.2.2  | Data Fusion                                                | 131 |

|            | 6.2.3  | GNN for Anomaly Detection                                  | 132 |

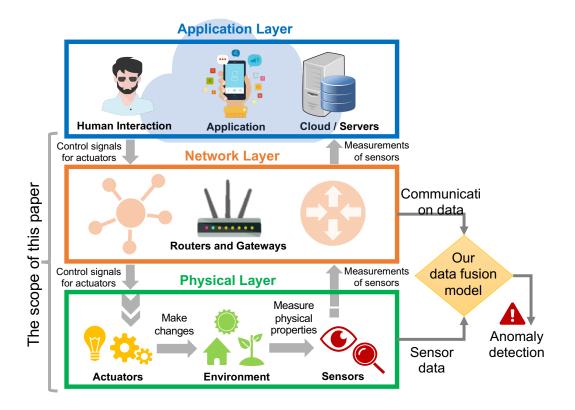

| 6.3        | IoT Se | ecurity and Data Analysis                                  | 135 |

|            | 6.3.1  | IoT Network Security Analysis                              | 135 |

|            | 6.3.2  | Anomaly Implementation                                     | 138 |

| 6.4        | Multi- | modal data fusion                                          | 139 |

|            | 6.4.1  | Data Preprocessing                                         | 140 |

|            | 6.4.2  | Context Extraction and Graph Generation                    | 141 |

|            | 6.4.3  | Forecasting Graph Neural Network                           | 143 |

|            | 6.4.4  | Anomaly Detection                                          | 145 |

| 6.5        | Evalua | ation                                                      | 148 |

|            | 6.5.1  | Experiment Setup                                           | 148 |

|            | 6.5.2  | Forecasting Model Performance                              | 149 |

|            | 6.5.3  | Anomaly Detection Performance                              | 151 |

|            | 6.5.4  | Timing Analysis                                            | 154 |

|            | 6.5.5  | Attack Analysis                                            | 155 |

| 6.6        | Chapt  | er Concluding Remarks                                      | 156 |

| Bibliog    | graphy |                                                            | 158 |

| Appendix A |        | Post-Silicon Hardware Trojan Detection                     | 173 |

| Appen      | dix B  | Stealing Neural Network Structure through Remote FPGA Side | e-  |

| chai       | nnel A | nalysis                                                    | 177 |

# LIST OF FIGURES

|            | P                                                                                                                                                                          | age             |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 1.1        | The research vision overview; integrating various sources of information about the system and extracting practical knowledge from them to understand and secure the system | 3               |

| 1.2        | The hierarchical structure of a system from the hardware design, fabricated IC, firmware/operating system, up to the software.                                             | 3<br>4          |

| 1.3        | IC security issues and countermeasure besides Hardware Trojan                                                                                                              | 5               |

| 1.4        | The overview of hardware security methodologies developed in this dissertation                                                                                             | 9               |

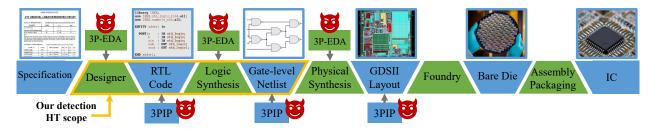

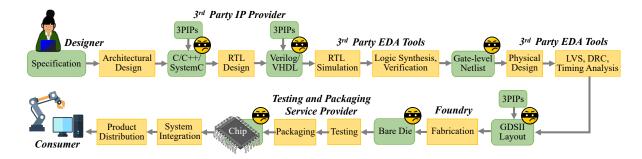

| 2.1        | Semiconductor supply chain, pre-silicon HT injection points                                                                                                                | 15              |

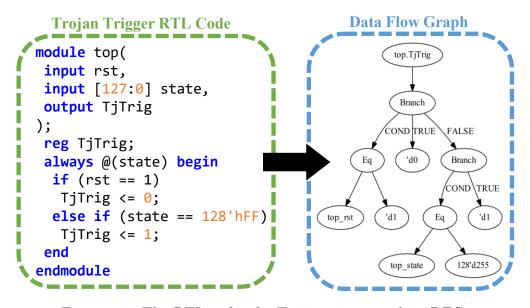

| 2.2        | The RTL code of a Trojan trigger and its DFG                                                                                                                               | 31              |

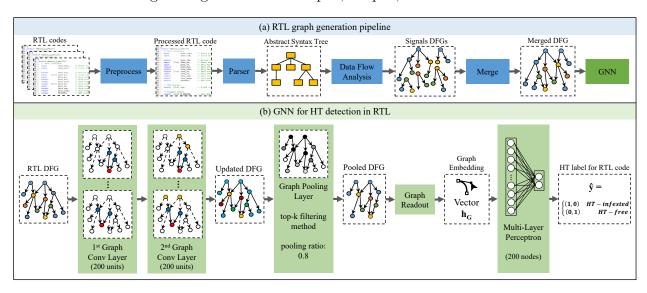

| 2.3        | The RTL DFG generation pipeline and GNN model for Trojan detection in RTL code                                                                                             | 33              |

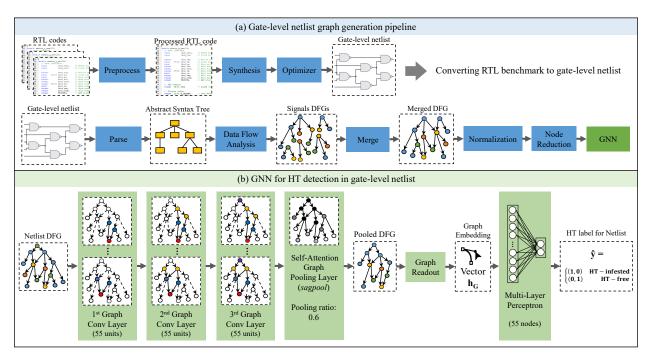

| 2.4        | The netlist DFG generation pipeline and GNN model for Trojan detection in                                                                                                  |                 |

| 0.5        | the gate-level netlist                                                                                                                                                     | 34              |

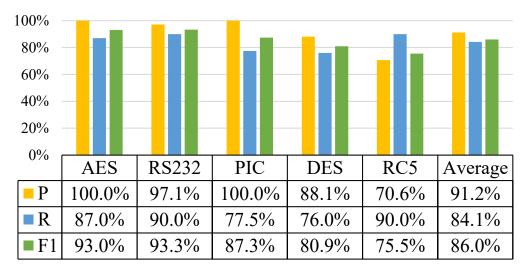

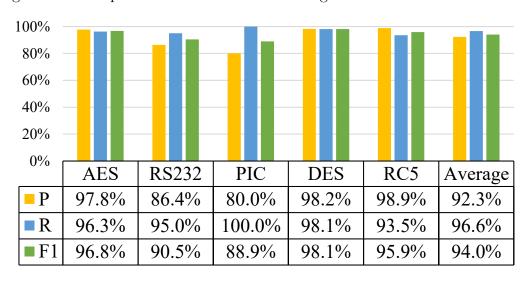

| 2.5<br>2.6 | Netlist graph optimization by removing <i>concatenation</i> and <i>part selection</i> nodes. The performance of our method in gate-level netlist HT detection              | $\frac{38}{41}$ |

| 2.7        | The performance of our method in RTL HT detection                                                                                                                          | 41              |

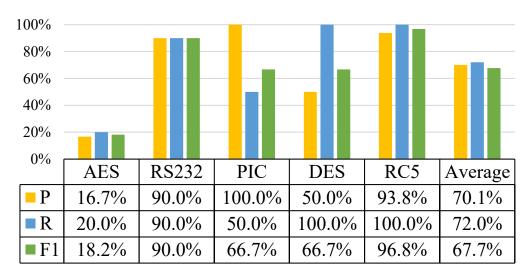

| 2.8        | The performance of our model without pooling layer.                                                                                                                        | 44              |

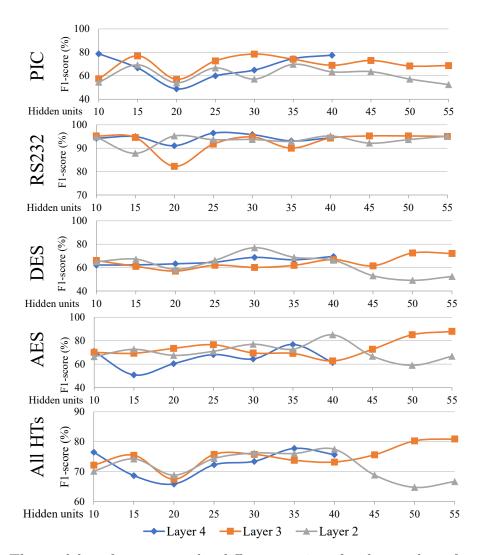

| 2.9        | The model performance under different settings for the number of convolu-                                                                                                  |                 |

|            | tional layers and hidden units in each layer                                                                                                                               | 45              |

| 3.1        | IC supply chain, vulnerable to HT insertion in different stages                                                                                                            | 53              |

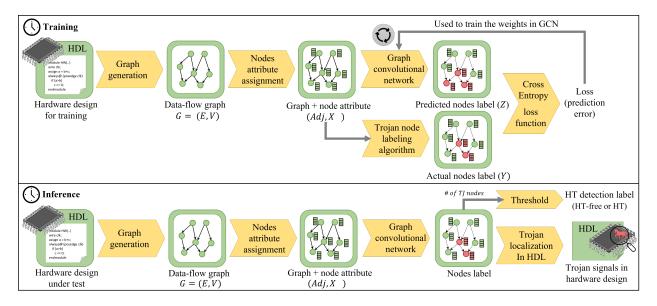

| 3.2        | Overview of our HT localization methodology in training and inference phases.                                                                                              | 59              |

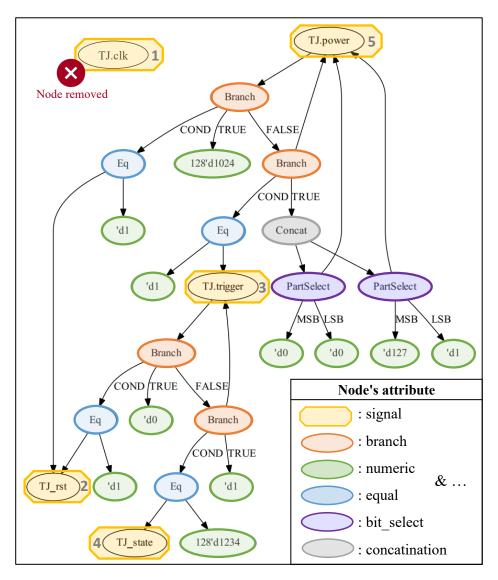

| 3.3        | The data-flow graph and node attributes of AES-T1800 Trojan benchmark, shown in Figure 3.4                                                                                 | 61              |

| 3.4        | The Verilog code of AES-T1800 Trojan benchmark                                                                                                                             | 63              |

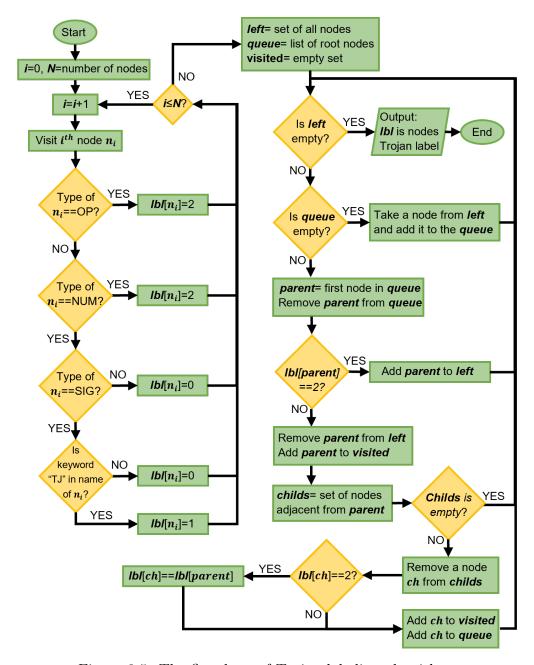

| 3.5        | The flowchart of Trojan labeling algorithm.                                                                                                                                | 64              |

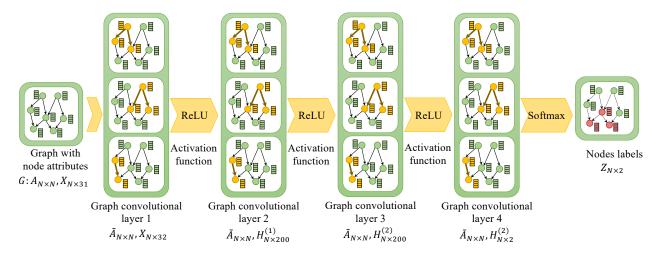

| 3.6        | The architecture of our GCN model for node classification                                                                                                                  | 69              |

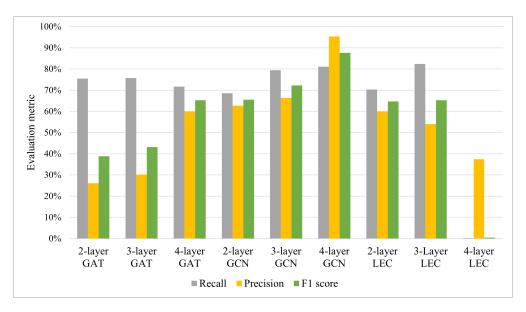

| 3.7        | Performance of various graph neural network models and architectures                                                                                                       | 75              |

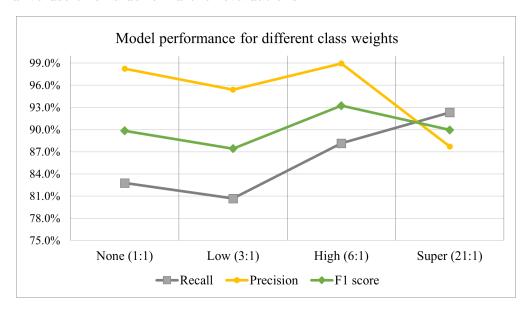

| 3.8        | Performance of GCN model with different class weights                                                                                                                      | 76              |

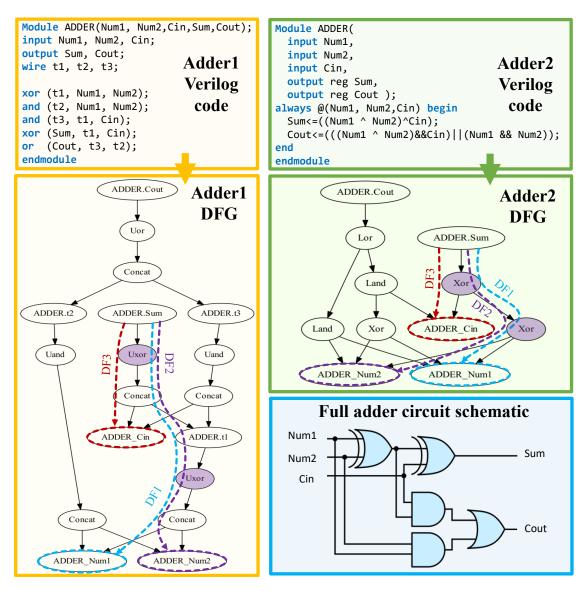

| 4.1        | The circuit schematic, Verilog codes, and DFGs of full adder circuits                                                                                                      | 81              |

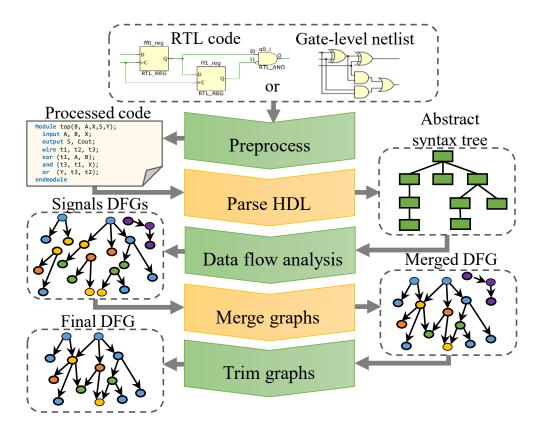

| 4.2        | Data flow graph generation pipeline for RTL code and netlist                                                                                                               | 89              |

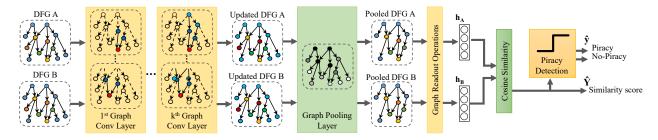

| 4.3        | The overall architecture of $GNN4IP$ for hardware IP piracy detection                                                                                                      | 90              |

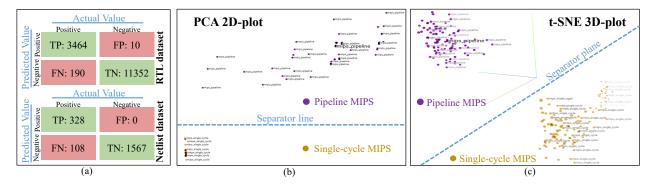

| 4.4  | (a) Confusion matrices for IP piracy detection, (b) $hw2vec$ embedding visualization using PCA, and (c) $hw2vec$ embedding visualization using t-SNE | 94   |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------|------|

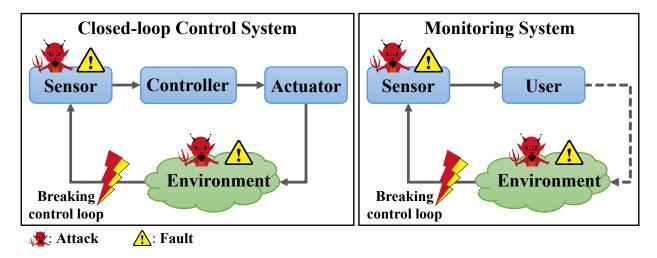

| 5.1  | Two categories of IoT systems; (a) Closed-loop control system, and (b) Monitoring system                                                             | 99   |

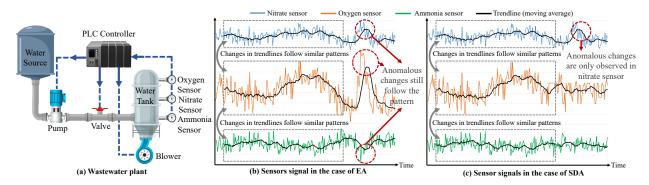

| 5.2  | (a) Schema of wastewater plant, and synthetic sensors' signals in the (b) first                                                                      |      |

|      | scenario (EA), (c) second scenario (SDA)                                                                                                             | 102  |

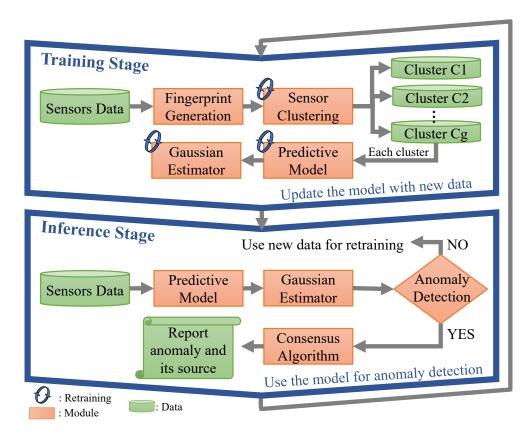

| 5.3  | The architecture of our methodology in the training and inference stage                                                                              | 106  |

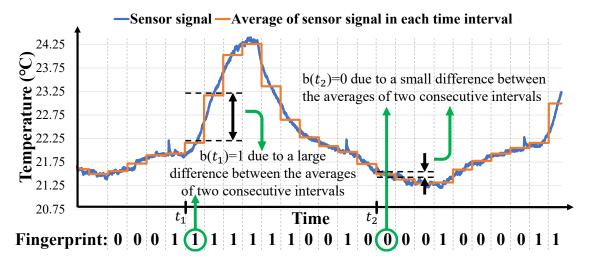

| 5.4  | Extracting the fingerprint of a temperature sensor                                                                                                   | 108  |

| 5.5  | The procedure of extracting the patterns in sensor signals and clustering them.                                                                      | .109 |

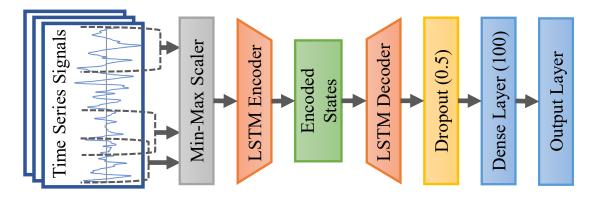

| 5.6  | The architecture of RNN used as a predictive model                                                                                                   | 113  |

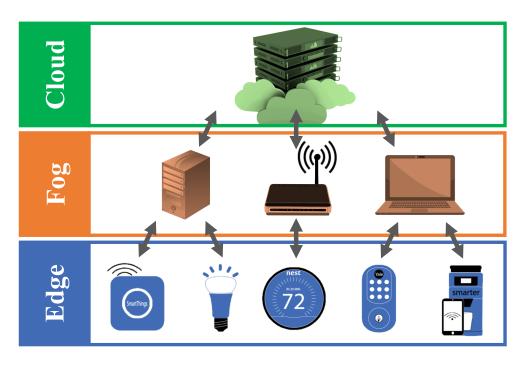

| 5.7  | Fog computing hierarchy in IoT systems                                                                                                               | 116  |

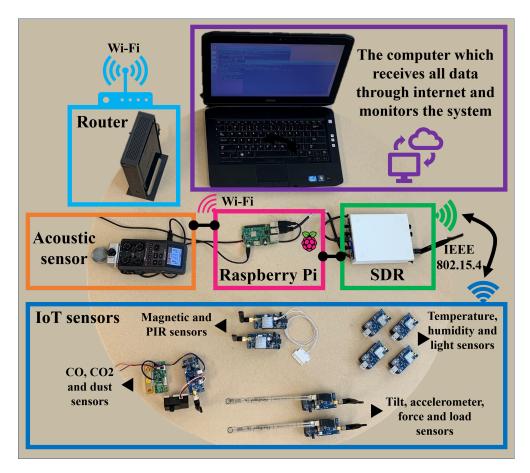

| 5.8  | The scaled-down version of the experimental setup                                                                                                    | 117  |

| 5.9  | The inter-cluster and intra-cluster distances of sensor clusters                                                                                     | 119  |

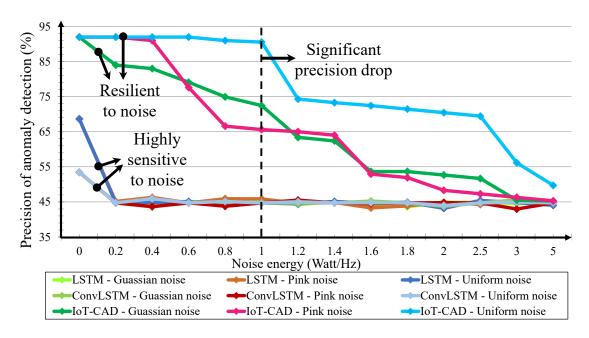

| 5.10 | Evaluating the resilience of different models to pink, Gaussian, and uniform                                                                         |      |

|      | noise signals.                                                                                                                                       | 121  |

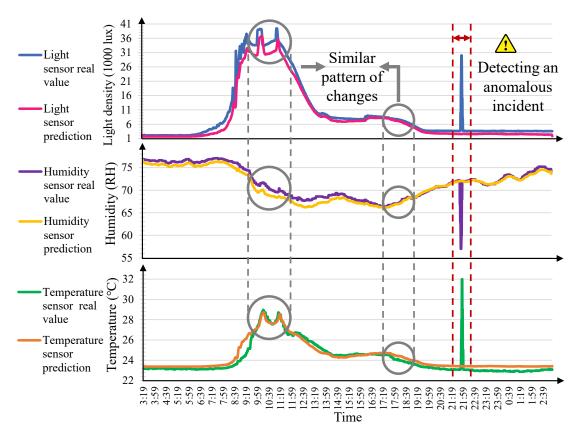

| 5.11 | The real and predicted values of three correlated sensors; light, humidity, and                                                                      |      |

|      | temperature sensors                                                                                                                                  | 122  |

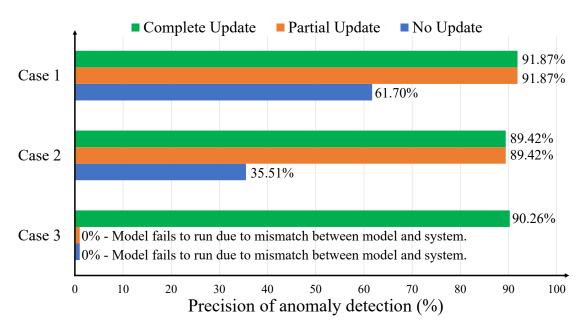

| 5.12 | Analysis of the effect of the partial and complete update on preserving the                                                                          |      |

|      | performance of the model                                                                                                                             | 124  |

| 6.1  | The IoT system architecture comprises physical, network, and application layers.                                                                     | .127 |

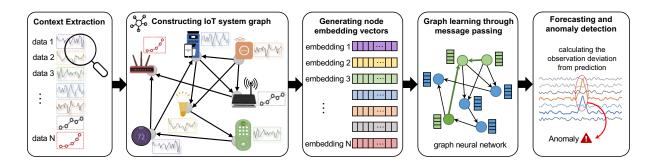

| 6.2  | Multi-modal data fusion pipeline for anomaly detection in IoT systems                                                                                | 140  |

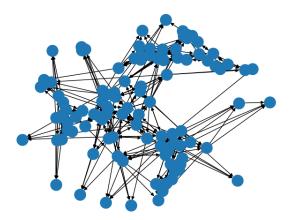

| 6.3  | The graph representation greenhouse IoT system                                                                                                       | 142  |

| 6.4  | The plot MSE and AUC loss vs. the number of epochs                                                                                                   | 150  |

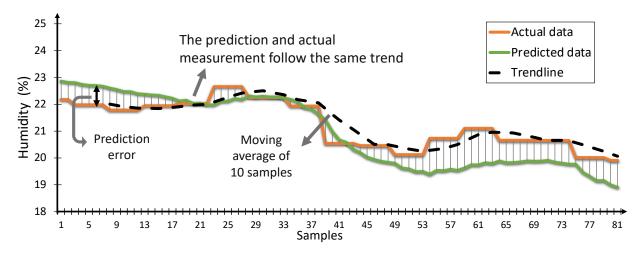

| 6.5  | The predicted values, actual recordings, and actual data trendline for a hu-                                                                         |      |

|      | midity sensor follow a similar pattern                                                                                                               | 150  |

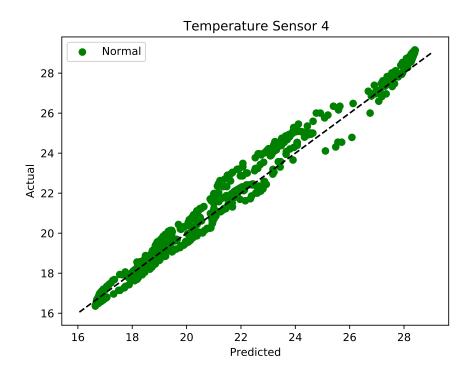

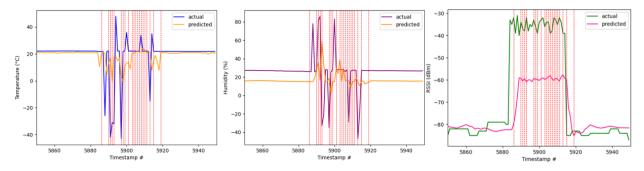

| 6.6  | The prediction vs. actual data for a temperature sensor                                                                                              | 151  |

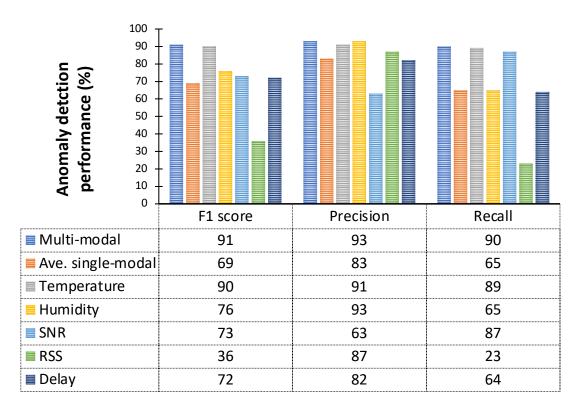

| 6.7  | The anomaly detection performance of multi-modal and single-modal models.                                                                            | 153  |

| 6.8  | The impact of a spoofing attack on temperature, humidity, and RSSI readings                                                                          |      |

|      | (left to right)                                                                                                                                      | 156  |

# LIST OF TABLES

|                          |                                                                                                                    | Page     |

|--------------------------|--------------------------------------------------------------------------------------------------------------------|----------|

| 2.1<br>2.2<br>2.3<br>2.4 | Timing of HT detection per sample and training models                                                              | 46<br>48 |

| 3.1                      | The performance of HT detection                                                                                    |          |

| 3.2                      | HT localization performance, number of Trojan nodes, and their ratio to total nodes for all AES and DES benchmarks | 73       |

| 0.0                      | nodes for all RC5 benchmarks                                                                                       |          |

| 3.4<br>3.5               | The summary of dataset and HT localization performance                                                             |          |

| 4.1<br>4.2<br>4.3        | The GNN4IP performance for IP piracy detection                                                                     | 95       |

| 5.1<br>5.2<br>5.3        | List of sensors in our experimental setup                                                                          | 120      |

| 6.1<br>6.2<br>6.3        | Statistics of the Greenhouse and SWaT dataset                                                                      |          |

| 6.4                      | efficient matrix                                                                                                   |          |

| 6.5                      | Timing of train, test, and validation for each data point                                                          | 155      |

#### ACKNOWLEDGMENTS

I would like to express my gratitude to my advisor and committee chair, Professor Mohammad Abdullah Al Faruque, for all of his help and valuable insights through my research. I would also like to express my deepest appreciation to my committee members, Professor Fadi Kurdahi and Professor Zhou Li, for dedicating their valuable time to review my work and provide insightful comments.

I would like to extend my sincere thanks to Dr. Sina Faezi for inspiring me to find my path in research. Without his irreplaceable guidance, ingenious suggestions, and profound belief in my abilities, I would not have been able to complete this dissertation today.

I would like to thank my friends, lab mates, and colleagues in the Autonomous and Intelligent Cyber-Physical Systems (AICPS) laboratory for the cherished time spent together in the lab and in social settings. I would like to extend my gratitude to my collaborators, Prof. Sitao Huang, Dr. Sina Faezi, Shih-Yuan Yu, Yasamin Moghaddas, Luke Chen, Anomadarshi Barua, Yicheng Zhang, Felix Hernandez, Qingrong Zhou, Tommy Nguyen, and Emad Kasaeyan Naeini for all the research discussions and contributions we had throughout my research endeavor.

I would like to thank UCI's Department of Electrical Engineering and Computer Science for their support that allowed me to thrive on this beautiful path. I would like to thank the Office of Naval Research (ONR) for the award N00014-17-1-2499 for supporting my research on hardware Trojan detection. Any opinions, findings, conclusions, or recommendations expressed in this Dissertation are those of the author and do not necessarily reflect the funding agencies' views. I thank IEEE and ACM for the permission to include the content of my dissertation, which portion of it was originally published in transactions and conference papers.

### VITA

#### Rozhin Yasaei

#### **EDUCATION**

Doctor of Philosophy in Electrical and Computer Engineering2023University of California Irvine (UCI)Irvine, CA, USAMaster of Science in Computer Engineering2021University of California Irvine (UCI)Irvine, CA, USABachelor of Science in Electrical Engineering2018Sharif University of TechnologyTehran, Iran

#### RESEARCH EXPERIENCE

Graduate Researcher

2018–2023

University of California Irvine (UCI)

Irvine, CA, USA

Researcher

NASA Frontier Development Lab (FDL), SETI

Mountain View, CA, USA

#### TEACHING EXPERIENCE

Pedagogical Fellow

University of California Irvine

2021-2023

Irvine, CA, USA

Teaching Assistant and Lecturer

University of California Irvine

2019-2023

Irvine, CA, USA

Teaching Assistant2015–2018Sharif University of TechnologyTehran, Iran

Teacher2015-2017Farzanegan High SchoolTehran, Iran

# REFEREED JOURNAL PUBLICATIONS 2023 MuFAD: Multi-Modal Data Fusion for Anomaly Detection in the Internet of Things through Graph Learning IEEE Internet of Things Journal Hardware Trojan Detection using Graph Neural Net-2022 works IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems Golden Reference-Free Hardware Trojan Localization 2022 using Graph Convolutional Network IEEE Transactions on Very Large Scale Integration (VLSI) Systems Brain-Inspired Golden Chip Free Hardware Trojan De-2021 tection IEEE Transactions on Information Forensics and Security Stealing Neural Network Structure through Remote 2021 FPGA Side-channel Analysis IEEE Transactions on Information Forensics and Security REFEREED CONFERENCE PUBLICATIONS HW2VEC: A Graph Learning Tool for Automating 2021 Hardware Security IEEE International Symposium on Hardware Oriented Security and Trust (HOST'21) GNN4IP: Graph Neural Network for Hardware Intel-2021 lectual Property Piracy Detection Design automation Conference (DAC'21) GNN4TJ: Graph Neural Networks for Hardware Trojan 2021 Detection at Register Transfer Level IEEE/ACM Design Automation and Test in Europe Conference (DATE'21) HTnet: Transfer Learning for Golden Chip-Free Hard-2021 ware Trojan Detection IEEE/ACM Design Automation and Test in Europe Conference (DATE'21)

IoT-CAD: Context-Aware Adaptive Anomaly Detection in IoT Systems Through Sensor Association

2020

IEEE/ACM International Conference On Computer Aided Design (ICCAD)

### ABSTRACT OF THE DISSERTATION

Graph Neural Network for Integrated Circuits and Cyber-Physical Systems Security

by

#### Rozhin Yasaei

Doctor of Philosophy in Electrical and Computer Engineering

University of California, Irvine, 2023

Professor Mohammad Abdullah Al Faruque, Chair

This Ph.D. dissertation presents a comprehensive investigation into addressing security and reliability challenges in embedded and Cyber-Physical Systems (CPS). Our research leverages advanced machine learning techniques such as Graph Neural Networks (GNN) to develop novel methodologies for cross-layer security analysis.

This dissertation addresses the growing risk posed by the globalization of the Integrated Circuit (IC) supply chain, whereby the majority of the design, fabrication, and testing processes have been outsourced to untrusted third-party entities across the globe. This development has significantly increased the threat of malicious modifications, known as Hardware Trojans (HTs), being inserted into Third-Party Intellectual Property (3PIP). HTs pose a substantial risk to IC integrity, functionality, and performance. Despite numerous HT detection methods proposed in existing literature, most limitations include reliance on a golden reference circuit, lack of generalizability, limited detection scope, low localization resolution, and manual feature extraction and property definition. Furthermore, the equally important task of HT localization has been neglected. This research proposes an innovative, golden reference-free method for HT detection and localization at the pre-silicon stage of IC development, employing models based on GNN. The circuit design is converted into a graph that is an intrinsic data structure for hardware design and captures the computational structure and

data dependencies. We develop a graph classification model to distinguish between HT-free and circuits infected with known or even unknown HTs. To push the boundaries further, we extract node attributes from the HDL code and devise a Graph Convolutional Network (GCN) that facilitates automatic feature extraction, enabling the classification of nodes as either Trojan or benign. This methodology offers an automated approach to HT detection and localization, relieving designers of the need for time-consuming manual code review. The developed method achieves exceptional performance in detecting HT-infected circuits and locating the HT. The approach outlined in this dissertation sets a new benchmark for HT detection and localization, offering a scalable, efficient, and highly accurate tool for securing the pre-silicon IC supply chain.

This dissertation expands to encompass the challenges facing IP piracy. The productivity gap, coupled with time-to-market pressure, has led to increased interest in hardware Intellectual Property (IP) core design within the semiconductor industry, dramatically reducing design and verification costs. Recognizing these challenges, this dissertation proposes a novel IP piracy detection methodology, modeling circuits and assessing similarity between IP designs. Contrary to traditional methods that embed a signature within the circuit design, our method does not introduce additional hardware overhead, nor is it vulnerable to removal, masking, or forging attacks. This approach effectively exposes IP infringements, even when the original IP is complicated by the adversary to deceive the IP owner. To represent the circuit accurately for modeling, we translate the hardware design into a data-flow graph due to similar data types and properties and subsequently model it using state-of-the-art graph learning methods. This approach effectively complements the GNN-based techniques proposed earlier in this dissertation, presenting a robust and comprehensive suite of solutions for security and reliability challenges in the semiconductor industry.

Moving to the CPS domain, the dissertation addresses security challenges in IoT systems through the development of adaptive anomaly detection methods. The first proposed ap-

proach utilizes IoT sensor data and fog computing to ensure data integrity and detect anomalous incidents. The proposed methodology incorporates our sensor association algorithm, LSTM neural networks, and Gaussian estimation for real-time anomaly detection. The dissertation further extends the research to multi-modal data fusion, where the integration of sensor and communication data using GNN enables improved anomaly detection, source identification, and recovery in IoT systems.

Overall, this dissertation showcases the application of advanced techniques such as GNN and machine learning in enhancing security and reliability in hardware design and IoT systems. The proposed methodologies for anomaly detection, hardware Trojan detection, IP piracy detection, and cross-layer security analysis contribute to advancing the state-of-the-art in ensuring the integrity and security of critical systems in the digital era.

# Chapter 1

# Introduction

The 21st century is an era of elegantly engineered components, devices, and systems that can communicate across different platforms to provide information on demand and make necessary decisions. The ability to connect real-world applications with modeling techniques is crucial to successful research and a critical need in today's world. This includes abstracting a problem or system to its essence, pinpointing pieces of collectible data that capture the system's essence, and devising effective data-driven models to learn and interpret the data. Reliability and security are currently being explored from a single-layer perspective in the literature. However, a holistic model of a system to analyze cross-layer security is still a challenging necessity, which this dissertation intends to address.

Cyber-physical systems are conventionally studied to be mathematically defined in the control systems domain. Such approaches construct definitive or state-based models that overlook the information hidden in various data generated by the system. For example, human interaction with the system is an essential factor that is hard to define mathematically. Therefore, we intend to leverage the abundance of data in the modern world to convert theoretical models to statistical models that embed our prior knowledge of the system as well

as the information derived from data analysis.

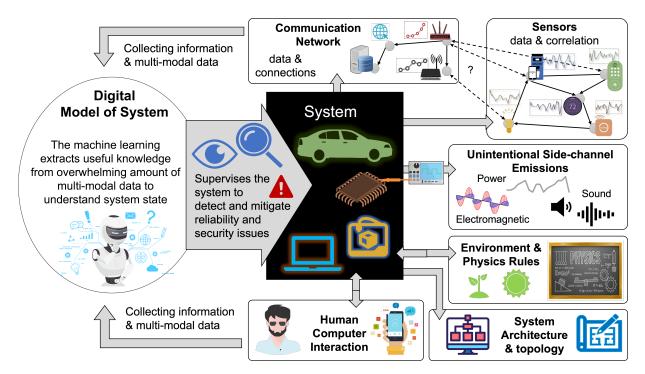

Constructing a digital model of a real-world system is challenging because modern systems are quite complex; They comprise hardware, software, and communication layers that often interact with the physical world and generate multi-modal data such as design and architecture, sensor recording, communication network data, side-channel emissions, human-computer interaction, etc. In addition to generated data, the mutual information and correlation patterns shared among various components of the system, known as context, are shown to be very valuable in advanced security and reliability analysis [174, 109, 110, 182, 118]. Integrating multi-modal data and extracting the context are keys to a holistic model, leading to new knowledge discovery levels, and can be leveraged to analyze and enhance security, reliability, and even performance. We pursue this vision in this dissertation and develop a strategy to apply machine learning to hardware and system for cross-layer security and reliability.

To follow this strategy, various challenges emerge, but advances in data fusion and learning models support the vision of developing such multi-modal models. We utilize Graph Neural Networks (GNN) to learn and interpret knowledge graphs, a data structure that can embody multi-modal Euclidean and non-Euclidean data. For example, GNN is shown superior performance when the interconnection between system components is dense. When the data generated in each component is complex, Convolutional Neural Networks (CNN) is a suitable choice for automated feature extraction and learning. Understanding textual data, especially human-computer interaction, would require different techniques known as natural language processing. Adopting mathematical knowledge of the system in the statistical model is another challenge that requires fundamental adjustment in the machine learning model.

Moreover, many apparently different problems, in fact, share some common characteristics.

Understanding these inherent characteristics enables us to tackle deeper problems and de-

velop better solutions. Building upon this idea, machine learning introduces transfer learning that studies the ability to apply a model trained for a system to a different but related target system. Transfer learning can be another influential strategy in modeling complex systems. Figure 1.1 illustrates the integration of various data sources to create a model of a system such as hardware, automotive vehicle, Internet of Things (IoT), etc.

Figure 1.1: The research vision overview; integrating various sources of information about the system and extracting practical knowledge from them to understand and secure the system.

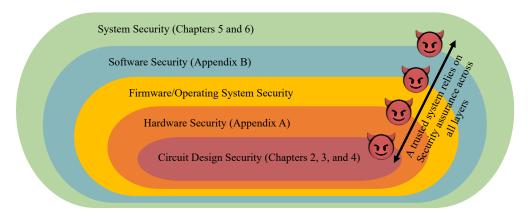

A salient attribute of digital systems is their hierarchical architecture, wherein high-level systems are constructed upon foundational layers. In the context of computing systems security, this hierarchical structure is vital as the security and reliability of the high-level design are contingent upon the trustworthiness of the underlying layers. Figure 1.2 exemplifies the fact that cybersecurity cannot be effectively achieved without ensuring security at the hardware platform upon which it operates.

Figure 1.2: The hierarchical structure of a system from the hardware design, fabricated IC, firmware/operating system, up to the software.

# 1.1 Related Works and Research Challenges

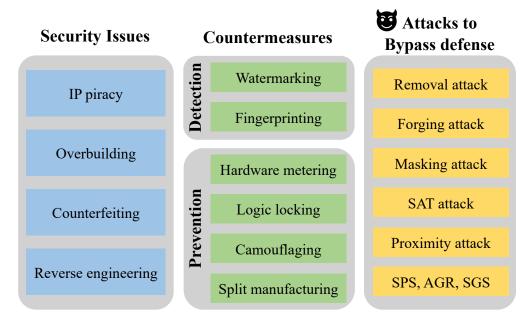

Numerous approaches have been proposed to mitigate the HT and IP piracy threats in the literature. However, they suffer from several shortcomings, as explained further. Currently, there is no universal method and design automation tool for detecting all types of HTs. Thus, a new scalable method and the associated tool are required for unknown HT detection that is expandable as new HTs are introduced. The existing pre-silicon HT detection solutions fall into five main categories [172, 173]; (i) test pattern generation, (ii) formal verification, (iii) code analysis, (iv) machine learning, and (v) graph similarity techniques. These methods propose new ideas but have several shortcomings; reliance on golden-reference, unable to identify unknown HTs, burdening the designer with a manual review of code, unable to guarantee HT detection, limited detection scope to some specific type of HTs, not being scalable, or too complex.

Conventionally, the IP protection techniques fall into preventive (i.e., logic encryption, camouflaging, metering, and split manufacturing) and detective (i.e., digital signature) methods. All these methods add excessive implementation overhead to the hardware design that limits their applications in practice. Moreover, they mostly focus on security at the IC level, while many commercial IPs comprise the soft IPs due to flexibility, independence of plat-

form technology, portability, and easy integration with other components. The high level of abstraction makes IP protection more challenging since it is easier for an adversary to slightly change the source code and redistribute it illegally at the lower levels of abstraction. Although the existing preventive countermeasures deter IP theft, they cannot guarantee IP security as the adversaries keep developing more sophisticated attacks to bypass them. Therefore, an effective IP piracy detection tool is crucial for IP providers to disclose the theft. To this end, the state-of-the-art piracy detection method embeds signatures of IP owners known as watermark and legal IP user known as a fingerprint, in the circuit design to assure authorship and trace legal/illegal IP usage. IP watermarking and fingerprinting are prone to removal, masking, or forging attacks that attempt to omit the watermark, distort its extraction process, or embed another watermark in IP.

Figure 1.3: IC security issues and countermeasure besides Hardware Trojan.

### 1.2 Dissertation Contributions

### 1.2.1 Hardware Security

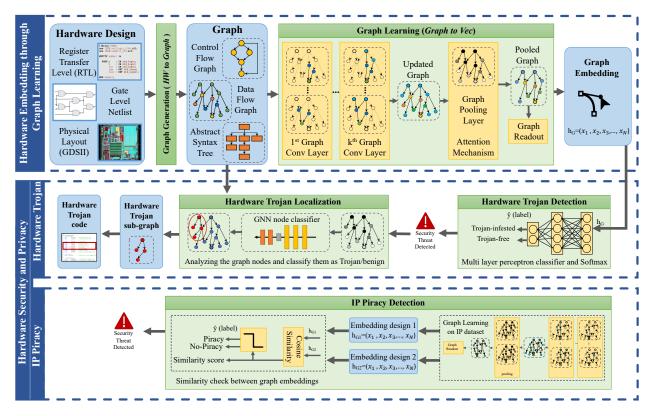

The time-to-market pressure and continuous growing complexity of hardware designs have promoted the globalization of the integrated circuit supply chain and pushed most of the design, fabrication, and testing process from a single trusted entity to various untrusted third-party entities worldwide. Outsourcing has made the semiconductor industry vulnerable to security threats such as hardware Intellectual Property (IP) piracy or hardware Trojans (HT). Hardware Trojan Detection. HT is a minimal malicious circuit inserted by an adversary in an IC to leak sensitive information, change functionality, degrade performance, or deny the service of the chip. It remains hidden and inactive to avoid detection during testing and only gets triggered under rare circumstances in run-time. HT is known to be the underlying reason for several severe system failures. Thus, HT is one of the major hardware security concerns, and we have worked on approaches to tackle this security threat in the design stage (pre-silicon) and after chip fabrication (post-silicon). To ensure the trustworthiness of IC design, it is essential to ascertain the authenticity of in-house and third-party IPs. Detection of HT in the early stages of the design flow is beneficial because removing it would be very expensive later. The existing HT detection solutions suffer from limitations; reliance on trusted golden reference (unavailable in practice), unable to identify unknown HTs, burdening the designer with a manual review of hardware, unable to guarantee HT detection, and limited detection scope to some specific types of HTs, not scalable, or too complex. To overcome these challenges, we proposed the first methodology that encodes IC design as a graph and models it with GNN [176] (Chapter 2). A circuit is non-Euclidean data that shares similar characteristics with the graph data structure. Thus, based on data flow, we generate a heterogenous graph representation of hardware design register transfer level code or netlist [172] (Chapter 2). We utilized graph data to develop a GNN model that learns circuits and Trojans' behavior and key features and distinguishes them through graph classification. This research resulted in a golden reference-free end-to-end fully automated security defense that demonstrated high performance in detecting known and unknown HTs in the pre-silicon stage. In the subsequent research [173] (Chapter 3), we pushed the limits even further to locate the Trojan in the victim circuit, which is currently a challenge, and the limited number of proposed methods have low accuracy and require an exhaustive manual search. We developed a node classification GNN model that focuses on the graph nodes and connection to perform node classification and determine the Trojan nodes. Later, an automated algorithm maps the malicious nodes to their counterpart in the circuit. The evaluation demonstrated it could locate all the Trojans with very high accuracy, fully automated. We further investigated the HT detection in a manufactured IC as a second layer of defense against overseas untrusted rouge foundries. In the post-silicon stage, the internal design of the IC is hardly accessible without the destruction of the chip. Therefore, we studied hardware side-channel power and Electromagnetic emissions as a non-invasive method to detect the presence of HTs. Common machine learning classification methods require a trusted golden chip which is not available in practice. Therefore, we collected electromagnetic and power side-channel signals for a library of known HTs and developed a convolutional neural network model on a library of Trojans to learn the best discriminative features for HT detection. Then, we devised a neural network architecture to perform transfer learning and apply the learned knowledge from the library to the circuit under test. Eventually, the learning outcome is passed to an anomaly detection mechanism that monitors the chip and reports malicious activities upon HT activation in run-time [50] (Appendix A). Later, we proposed a brain-inspired HT detection architecture using Hierarchical Temporal Memory. Similar to the human brain, this solution is resilient against natural changes that might happen in the side-channel measurements while accurately detecting the chip's abnormal behavior when the HT gets activated. We used a self-referencing method for HT detection, eliminating the golden chip's need [51] (Appendix A). IP Piracy Detection. The superiority of GNN led to leveraging the GNN-based approach for IP piracy, a serious security issue, especially in IP-intensive economies such as the US. To increase productivity under time-to-market pressure, IP core design has grabbed substantial attention from the semiconductor industry and has dramatically reduced the design and verification cost. However, the globalization of the IC supply chain poses a high risk of theft for design companies that share their most valuable assets, IPs, with other entities. We proposed a novel methodology for IP piracy detection that models the circuits and assesses the similarity between IP designs instead of the conventional techniques of inserting and extracting a signature to prove the ownership. This method does not add any hardware overhead as a signature and is not vulnerable to removal, masking, or forging attacks. It also effectively exposes the infringement between two IPs even if the adversary complicates the original IP through obfuscation techniques to deceive the IP owner. We convert each circuit to a data-flow graph with attribute vectors assigned to each node. Then, a GNN-based model is constructed on labeled pair of similar and dissimilar circuit graphs to learn the critical properties that define circuits, evaluate similarity on a scale of -1 to 1, and determines IP piracy. The results indicated that this method could detect even partial similarity with high performance [175] (Chapter 4). Another expensive IP of tech companies is the machine learning models, often developed with expensive computation and private datasets. Many companies use public server services such as AWS, which makes them vulnerable to IP piracy. We explored machine learning security on FPGA-based servers, and due to our cross-later security perspective, we leveraged software/hardware co-design to construct an attack model. It resulted in a remote side-channel attack that can steal the machine model configuration running on multi-tenant FPGA servers and revealed the vulnerability of these systems [190] (Appendix B). The experiences with the GNN model have shown its high potential for modeling hardware and system, and the methodology to leverage it led to a patent. To facilitate this multi-disciplinary research, we created an open-source library of GNN models called HW2VEC [183] and a few datasets for the public. We later employed GNN for hardware design automation as well. Figure 1.4 represents the big picture of the methodologies we developed based on GNN for understanding and securing complex hardware designs.

Figure 1.4: The overview of hardware security methodologies developed in this dissertation.

# 1.2.2 Embedded and Cyber-Physical Systems Security

In today's world, we are surrounded by interconnected networks of intelligent devices called the Internet of Things (IoT) that monitor and control our home, health [133, 135, 134], vital infrastructure [34, 157, 158, 17], factory planes [108, 181, 32, 31, 180, 47], etc. The widespread presence of IoT systems and their critical applications emphasize the importance of their security and integrity. IoT devices are vulnerable to attacks and failures due to low computational resources, cost constraints, and tight time-to-market. It is challenging to mitigate these attacks and failures because of the multi-disciplinary nature of IoT, which brings together the physical domain through sensor interaction and the cyber domain through

the communication network and the cloud.

We started investigating IoT systems security from a bottom-up perspective. Our approach is motivated by the observation that strongly correlated patterns might be found in sensor data, and the discovery of such coherent clusters of sensors is essential in revealing abnormality and attack toward the system from different points of view. We proposed an adaptive context-aware anomaly detection method [174] that captures the system's physical properties to ensure the integrity of IoT sensor data and identify anomalous incidents. In this approach, we devised a novel sensor association algorithm that generates fingerprints of sensors, clusters them, and extracts the context of the system. Based on the contextual information, a predictor model, which comprises a long short-term memory neural network and Gaussian estimator, detects anomalies. Then, a consensus algorithm identifies if the anomaly is an environmental incident or a security and reliability issue. This model wholly or partially updates itself to adapt to the variation in the environment and changes in IoT system architecture. The experiments showed that context awareness and adaptability are crucial features in modeling cyber-physical systems, which enhance the performance and robustness of the anomaly detection model (Chapter 5).

Although stand-alone approaches are proposed in the literature for network intrusion detection or sensor anomaly detection, a holistic model needs to be included to integrate the information from both domains and extract the valuable context shared among different system components. We proposed a multi-modal data fusion methodology that fuses sensor and communication data. We integrate IoT physical and cyber elements into a knowledge graph representation that signifies the correlation between elements as a connection and provides embedding for data generated by each component. We constructed a GNN model to learn the context and normal state of the system and detect abnormal activities. We further studied the signatures of networks and sensor attacks to determine the source of the anomaly to facilitate fast and informed recovery after an incident. Experiments on the

greenhouse monitoring IoT systems demonstrated that this holistic multi-modal anomaly detection model, on average, achieves a 22% F1-score improvement over the single-modal approaches (Chapter 6).

# 1.3 Dissertation Organization

This dissertation embarks on a comprehensive exploration of cross-layer security, starting from hardware security and methodically progressing toward an understanding of higher-level embedded and cyber-physical system security. In Chapters 2 and 3, we delve into one of the primary security threats plaguing the semiconductor industry: hardware Trojans (HTs).

Chapter 2 unveils a hardware Trojan detection model that leverages a Graph Neural Network (GNN) classifier, detailing the process of translating hardware design into a graph format that accurately encapsulates its intrinsic structure. This chapter culminates in the evaluation of the proposed model, demonstrating its superior performance in both precision and speed compared to existing methods.

Building on the HT detection discourse, Chapter 3 tackles the subsequent phase of HT localization and elimination from the compromised circuit. We discuss a node classifier model rooted in GNN and delineate algorithms designed to convert the circuit into a graph with attached node attributes, identify Trojan nodes within the graph, and map the nodes back to their HDL code representation.

Having demonstrated the potential of graph learning in the hardware domain, Chapter 4 confronts another IC security threat: IP piracy. Borrowing the graph generation process from Chapter 2, we propose a new approach toward IP piracy detection. Instead of relying on traditional signature-based defense mechanisms, an automated GNN-based tool is introduced

to assess the similarity between different hardware designs.

The lessons learned in Chapters 2, 3, and 4, such as the importance of context and understanding the relationships between various components for security assurance, serve as cornerstones for the following chapters. Shifting from the low-level circuit to the system level, Chapter 5 presents a context-aware model for Cyber-Physical System (CPS) security, demonstrated within an Internet of Things (IoT) system. We discuss the pressing need for IoT security and introduce a novel methodology. This methodology extracts sensor finger-prints to identify clusters of related sensors, leveraging this sensor association information for enhanced fault and attack detection.

Finally, Chapter 6 integrates the GNN development insights from Chapters 2, 3, and 4 and the context-aware anomaly detection perspective from Chapter 5. It presents a novel approach for cross-layer anomaly detection in the physical and communication layers of IoT systems. Here, we elaborate on a GNN model that performs data fusion between multimodality communication network data and sensor measurements.

The appendices A and B provide a summary of three collaborative research projects that explore post-silicon IC security and software adversary attacks, effectively bridging the gaps in the cross-layer security exploration proposed in the main body of the dissertation.

# Chapter 2

# Hardware Trojan Detection

### 2.1 Introduction

The scale and complexity of modern System-on-Chip (SoC) designs have made it increasingly challenging and expensive for chip manufacturers to design, fabricate, and test every component in-house. The time-to-market pressure and resource constraints have pushed SoC designers to outsource hardware designs and use Third-Party Electronic Design Automation (3P-EDA) tools and Intellectual Property (IP) cores from various vendors worldwide. Using Third-Party IPs (3PIP) can be cost-effective due to the re-usability of IP cores so that chip manufacturers can reallocate their resources to meet market demands. However, the security and trustworthiness of 3PIPs are not always guaranteed, and reliance on untrusted IPs and EDA tools greatly raises the risks of HT insertion by rogue entities in the Integrated Circuit (IC) supply chain.

HT refers to an intentional and malicious modification of an IC that is usually designed to leak information, change functionality, degrade performance, or deny the service of the chip. Due to the wide applications of ICs in military systems, critical infrastructures, medical devices, etc., the consequences of an undetected HT in a chip can be life-threatening. For example, an actual demonstration of the HT threat occurred in 2007, when a suspected nuclear installation in Syria was bombed by Israeli jets because Syrian radar was disabled by a remote kill switch backdoor in its commercial off-the-shelf microprocessor [6]. In 2012, an undocumented hardware backdoor was found in the Actel/Microsemi ProASIC3 chips used in military-grade FPGAs [147] that allowed the extraction of secret keys, enabling an adversary to modify the chip's configurations and gain full control of the chip. Furthermore, it is projected that the global semiconductor IP market will reach 7.3 Billion by 2025, with a compounded annual growth rate of 5.5% from 2020-2025 [1], and the security concerns about untrusted IPs can significantly damage the market.

Figure 2.1 shows the typical life cycle of an SoC design, starting from system-level specification to fabrication, in which several stages of the IC supply chain are marked as potential points of HT injection. A rogue in-house designer/team can manually modify or add malicious functions in the hardware design at any design abstraction level (system level, behavioral level, and logic level). Moreover, the 3P-EDA tools used for behavioral, logic, and physical synthesis may insert HT into the synthesized RTL and gate-level netlist code. Using untrusted 3PIP in various design stages introduces a means for adversaries to tamper and infect a design with HTs. To ensure the trustworthiness of an SoC design, it is crucial to ascertain the authenticity of 3PIPs. The 3PIPs are typically classified into three categories based on their format; Soft IP (i.e., synthesizable Verilog or VHDL in the RTL format), Firm IP (i.e., gate-level netlist), and Hard IP (i.e., GDSII files and custom physical layout format).

The flexibility of IP cores in higher levels of abstraction makes it easier for the attacker to design and implement various malicious functions. It is crucial to identify HTs early on in the design stages because it becomes increasingly expensive to remove them later. Detecting a few lines of HTs in an industrial-strength IP with thousands and hundreds of thousands of

Figure 2.1: Semiconductor supply chain, pre-silicon HT injection points.

code lines is extremely challenging. Any work requiring manual code review is error-prone, time-consuming, and not scalable. The need for a scalable pre-silicon security verification method is highlighted in many technical documents, such as a recent white paper from Cadence and Tortuga Logic [53] because existing solutions fail to safeguard the hardware design from the constantly evolving HTs designed by adversaries. We further elaborate on this necessity through a motivational example.

### 2.1.1 Motivational Example

The HT detection problem has always been a back-and-forth tug-of-war. HTs are stealthy by design and are composed of a payload and trigger. They are usually very small and inactive, with minimal effects on the chip until the trigger circuit is activated under very rare circumstances and triggers the payload to perform its malicious activities. The HT detection problem has always been a back-and-forth tug of war. Whenever new HT detection methods are proposed in the literature capable of detecting currently known HTs, new HTs are designed to bypass state-of-the-art detection methods. This behavior can be observed by looking at the trend in HT detection over the past decade. One of the earliest defense mechanisms, [69] proposed a novel Unused Circuit Identification (UCI) technique that identifies suspicious circuitry not being used or activated during design verification. However, the authors in [148] later designed a new type of HT called Stealthy Malicious Circuits (SMC), which could bypass UCI by hiding HT in nearly-unused logic. Further, FANCI [160] was

successful in detecting SMC by identifying the low control value exhibited by the nearly-unused logic, but it was later defeated by DeTrust [186], which designed a new class of HTs with stealthy implicit triggers. Mero[23] generates test vectors that are capable of activating HTs with low trigger probabilities for detection. Still, it fails to generate test vectors that can activate "hard-to-trigger" HTs with trigger probabilities less than 10<sup>-6</sup> [138].

Among the more recent works that use Trusthub benchmarks, [130] is supposed to detect HTs that leak sensitive data, such as secret keys in cryptographic cores, as in the AES-T600 benchmark. However, it fails to detect another similar HT benchmark, AES-T700. Later, [131] identifies different data leaking HTs (e.g., AES-T600 and AES-T700) by adding data leaking as an additional security property for model checking. However, it fails for HTs that execute other malicious functions, such as chip degradation (e.g., the AES-500 benchmark), rather than data leakage. A recent paper [56] showed that modeling the hardware design as a graph can be beneficial in the hardware security domain. However, the HT detection scope of [123, 56] based on graph similarity algorithms is limited to known HTs in the method's library. There have also been methods that convert the hardware design into a graph representation of the circuit and extract HT features to build a database of HT features for detection [27], but the detection scope is also limited to the HTs in its database.

Despite the various HT detection methods proposed in the literature, the HT problem remains significant as there exists no single method that can detect all different types of HTs. While most detection algorithms can only detect known HTs, new HTs are designed to circumvent existing detection methods. Thus, a new flexible technique for detecting unknown HTs is needed, one that can be expanded as new HTs emerge.

# 2.1.2 Research Challenges

The existing pre-silicon HT detection methods have several shortcomings:

- 1) Reliance on golden-reference: Most HT detection methods rely on a golden HT-free reference circuit to compare the design under test with the golden reference and flag it as HT-infected in the case of deviation. Nevertheless, a golden reference is hard to obtain in practice, especially infeasible at the IP level.

- 2) Limited detection scope: Some HT detection algorithms are constructed based on a library of known HTs. Consequently, they fall short in detecting unknown HTs. Another set of methods assumes particular properties in the Trojan design of the trigger or payload, limiting the detection scope to specific HTs.

- 3) Manual code review: Many HT countermeasures mark the parts of the design under test which are prone to HT insertion. However, this does not guarantee that an HT is present/detected, and it would burden the circuit designer with a manual review of the suspicious parts, which is tedious and error-prone for large designs.

- 4) Scalability and complexity issue: Due to the growing complexity of modern ICs, scalability is an essential feature for any hardware design tool but many current techniques and algorithms are so complicated that they face time or memory issues for large designs.

# 2.1.3 Chapter Contributions

To address these challenges, we propose a golden reference-free pre-silicon HT detection approach that takes advantage of state-of-the-art machine learning techniques to learn the circuit behavior and detect the anomalous and malicious presence of Trojan inside the design. Since hardware is a non-euclidean, structural type of data in nature, we use the graph data structure to represent the hardware design and generate the Data Flow Graph (DFG) for both RTL codes and gate-level netlists. We leverage GNN to model the behavior of the circuit. The scalability of our method stems from

the fully automated process of graph generation, feature extraction, and detection without any manual workload. Automatic feature extraction is crucial when new HTs are discovered, as our model will be readily updated without the need to define new properties or introduce additional feature engineering as in previous works. Our contributions are outlined below:

- We propose a novel approach for modeling the hardware design to ensure its security.

Our methodology models the circuit as its intrinsic representation, a graph, and we leverage GNN to extract the critical features of hardware design and learn its behavior.

- We construct two fully automated models for HT detection in the pre-silicon stage. Each model includes a DFG generation pipeline followed by a GNN-based graph learning flow, and it is developed and customized for its target hardware design, either RTL code or gate-level netlist. The models discover even unknown HTs without relying on golden HT-free references or manual code reviews from the circuit designer. Our models are faster than existing methods and scalable for large designs.

- We create a Trojan DFG dataset consisting of RTL codes and gate-level netlists. We expand the HT-infested RTL benchmarks from Trusthub and perform logic synthesis and optimization to acquire the corresponding gate-level netlist.

- We survey the pre-silicon HT detection techniques in the literature, analyze state-ofthe-art and make a comprehensive comparison with our approach.

#### 2.1.4 Threat Model

This work aims to determine whether an RTL code or gate-level netlist is infected with a malicious Trojan circuit or not. There is no assumption on the type of HT and the design of the trigger or payload. Therefore, our method can detect trigger-based or always active Trojans with a payload circuit to modify functionality, degrade performance, leak confidential

data, or deny the service. The only premise is that the HT is inserted in the design stage through the following attack scenarios: 1) A rogue in-house designer intentionally manipulates the RTL/netlist design manually. 2) The 3P-EDA tool used for design/logic synthesis and analysis inserts an HT into the synthesized RTL/netlist code automatically. 3) 3PIP vendor is not trustworthy, and a malicious circuit is hidden in the IP.

# 2.2 Related Works and Background

The majority of the pre-silicon HT detection techniques in the literature fall into four main categories, described below:

#### 2.2.1 Hardware Trojan

An HT consists of two fundamental parts: payload and trigger. The payload is the implementation of the malicious behavior of the HT. This malicious behavior could lead to information leaks, such as the secret key of a cryptographic core which would enable unrestricted access to sensitive data. It could change the functionality of the circuit to sabotage or cause harm. It can deny the service of certain functionalities of the chip or degrade the performance by increasing power consumption. The trigger is an optional circuit that monitors various signals or events in the base circuit and activates the payload when a specific signal or event is observed. HTs without triggers are usually always-on Trojans. HTs with triggers in the context of digital circuits can either be combinational or sequential. Combinational triggers activate upon a specific set of signal inputs. Sequential triggers rely on a specific sequence of signals or events. A sequential trigger could be based on a counter reaching a specific value or when a signal pattern repeats over a certain duration. A sequential trigger is more difficult to activate compared to a combinational trigger due to the vast number of states

that are required to be checked. We classify the triggers of HTs into three main categories; i) time bomb, ii) cheat code and iv) always on. The time bomb trigger is activated after numerous clock cycles, and the cheat code trigger depends on one or a sequence of specific inputs in the base circuit.

HTs are designed with malicious intent and to stay undetected. HT designers can reduce the likelihood of their HTs from being detected by using a common technique that involves placing them in rare internal nodes with exceedingly low activation probabilities. Rare internal nodes are difficult to detect because they are often outside the functional context of the intended design, and they often go undetected by traditional test methods. Therefore, many HT detection methods take into account the rare internal node characteristic of HTs as part of their detection schemes.

# 2.2.2 Hardware Trojan Detection Methods

Test Pattern Generation: Traditional test pattern generation has been widely used in both pre-silicon and post-silicon manufacturing stages. The idea is to create an extensive set of test vectors with varying input logic combinations to validate a circuit's output against the intended design output. The intended design output must come from a trusted golden reference chip of the original circuit design. These test patterns are typically generated based on the system specifications of the design, which describes the functionalities and behaviors of the circuit. However, due to their stealthy nature, HTs remain inactive and well-hidden during simulation and testing. Many HTs can bypass detection from these test vectors by simply not modifying the functionalities of the original circuit. More importantly, most HTs only activate under particular rare events. This makes it difficult for traditional test generation methods to trigger HTs that use internal node triggers with extremely low activation probability.

To tackle these issues, the authors in [23, 138] use automatic test pattern generation (ATPG) to create effective test vectors by identifying rare input logic at internal nodes to increase the probability of triggering the HT. However, even with this strategy, the scale of modern designs makes it possible for HT designers to create extremely low activation triggers that could evade detection by combining multiple rare signals and having the trigger conditions occur over multiple steps. [103] proposed a new test generation method by mapping the trigger activation problem to a clique cover problem which can detect extremely rare triggers but is shown to have unstable coverage performance. A recent study employs reinforcement learning techniques in conjunction with rare node excitation, as well as controllability and observability analysis to generate test vectors with improved trigger coverage and test generation time. Most methods above assume a full-scan chain design which simplifies ATPG by converting sequential elements into combinational elements with scan flip flops. However, not all designs have full-scan chains due to design constraints such as power, area, and additional hardware components required [18]. Therefore, a partial-scan chain design has been adopted. [39] tackles the challenges of partial-scan designs by combining ATPG with model checking for more efficient test vector generation and improved HT coverage. Still, there is no guarantee of success in the test pattern generation approach, and most test generation techniques are time-consuming due to their iterative nature. More importantly, in order to achieve full coverage, test pattern generation would need to generate and test all the possible cases, but given the scale of modern ICs, it is simply infeasible since the state space for test vectors grows exponentially to the number of rare input signals.

Formal Verification (FV): Formal verification is a mathematical proof-checking technique that relies on the security and trust policies defined in the system-level specification. It verifies the integrity of the design using common verification methods such as property checking, equivalence checking, and model checking. In order to apply formal verification, the 3PIP design must first be converted from an HDL language like Verilog to an equivalent

model in the proof-checking format using a formal language like Gallina, a tactic language developed as part of the well-known theorem prover called Coq. The 3PIP is delivered with a separate code representing the 3PIP but written in formal language and used for proof-checking; this code is known as proof-carrying code (PCC). PCC can either be provided by the 3PIP vendor directly or they can provide a Soft IP that can be converted into a proof-checking format.

Applying FV methods, [150] formulate taint-propagation properties that verify the data flow between signals in a design to identify unintentional design bugs. HTs, however, are intentional by nature, so the criteria for bug detection do not directly apply to HT detection. A similar approach is able to detect information leakage [131] and malicious modification to registers [130] by applying information leakage and register modification as criteria for the security properties. While using formal verification on 3PIP proves the predefined security properties, its detection scope is limited to the properties stated in the system-level specification. Only specific types of HTs can be detected because the properties are insufficient to cover all the various types of malicious behaviors that HTs can exhibit. [130], for example, defines "no-critical-data-corruption" which can only detect data-corrupting HTs. [131] modifies the security criteria from data corruption to data leakage. Both approaches employ model checking, which does not scale to large designs because model checking is NP complex and suffers from state explosion. [59] combines theorem proving with model checking to overcome the state explosion issues of model checking; however still suffers from the limited scope issue. Information flow tracking has been used to model security properties that can provide wider coverage of HTs [119]. FV does not depend on HT trigger conditions for detection, so it does not suffer from the issue of not being able to detect HTs due to low trigger probability. However, it is still possible for 3PIP vendors to intelligently manipulate the proofs and security properties to evade FV.

Code Analysis (CA): Code analysis or code coverage is a technique that analyzes the execution of the RTL or gate-level netlist code. To verify the 3PIP for trust, code analysis uses metrics such as line, statement, toggle, and finite state machine (FSM) coverage and compares against the design specification to ascertain the suspicious signals that imitate the HT. These coverage metrics respectively check which lines and statements are executed, what signals are being switched in the gate-level netlist, and which states are reached during execution. If anything less than 100% coverage is reported, then the 3PIP design is considered to be HT infested.

Using CA, [120] extracts state transition graphs from gate-level netlist and reports state transitions that are vulnerable to HT injection. This approach burdens the designer with manual analysis of the suspicious regions to identify the possible HT. It is also limited to the design's combinational logic. FANCI [160] proposed a control value metric that measures the degree of influence a given input has on the operation and output of a circuit. It looks for nets in the HDL code with very low control values and marks them as suspicious nets. VeriTrust [185] returns the nets that are not driven by functional inputs as potential triggers for an HT. DeTrust [186], on the other hand, proposes an attack that exploits the vulnerabilities of FANCI and VeriTrust by modifying the HTs with stealthy implicit triggers. Trigger logic for these HTs is distributed over multiple stages with a combination of sequential and combinational logic alongside logic that is part of the intended design, making them much more challenging to detect. In order to execute/cover all the lines of the code, code analysis requires an effective test bench to cover all the execution scenarios of the design. This causes the same problems as test pattern generation in that the number of test patterns needed for higher coverage scales poorly with larger designs, and verification time increases to an infeasible amount. It has also been shown that even 100% coverage does not guarantee that a 3PIP is HT-free [76].