# UNIVERSITY OF CALIFORNIA, IRVINE

An Initial Study of Two Approaches to Eliminating Out-of-Thin-Air Results

### DISSERTATION

submitted in partial satisfaction of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

in Computer Engineering

by

Peizhao Ou

Dissertation Committee: Professor Brian Demsky, Chair Professor Rainer Dömer Professor Guoqing (Harry) Xu

$\bigodot$ 2018 Peizhao Ou

## DEDICATION

To my family

## TABLE OF CONTENTS

|               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Page                                                                                                                                             |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| $\mathbf{LI}$ | ST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                       | v                                                                                                                                                |

| A             | CKNOWLEDGMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                      | ix                                                                                                                                               |

| CI            | URRICULUM VITAE                                                                                                                                                                                                                                                                                                                                                                                                                                     | x                                                                                                                                                |

| A             | BSTRACT OF THE DISSERTATION                                                                                                                                                                                                                                                                                                                                                                                                                         | xii                                                                                                                                              |

| 1             | Introduction         1.1       The Sequentially Consistent Memory Model         1.2       Hardware Memory Models         1.2.1       Relaxed Behaviors Exposed by Hardware         1.2.2       Constraining Relaxed Behavior with Memory Fences and Dependencies         1.3       Compiler Optimizations         1.4       Programming Language Memory Models         1.4.1       The Java Memory Model         1.4.2       The C/C++ Memory Model | $     \begin{array}{c}       1 \\       4 \\       6 \\       6 \\       10 \\       13 \\       14 \\       16 \\       17 \\     \end{array} $ |

| 2             | Overview of the OOTA Problem         2.1       The Problem                                                                                                                                                                                                                                                                                                                                                                                          | 24<br>25<br>27<br>30<br>30<br>32<br>33                                                                                                           |

| 3             | Memory Model Extensions that Disallow OOTA Behaviors         3.1       The Language                                                                                                                                                                                                                                                                                                                                                                 | <b>34</b><br>35<br>35<br>45<br>47                                                                                                                |

| 4             | Dependency-Preserving Compiler         4.1       Design         4.2       Implementation                                                                                                                                                                                                                                                                                                                                                            | <b>49</b><br>49<br>52                                                                                                                            |

|          |       |             | nodified Passes                                           |             | 52  |

|----------|-------|-------------|-----------------------------------------------------------|-------------|-----|

|          |       | 4.2.2 Mod   | lified Passes                                             | •••         | 53  |

| <b>5</b> | Loa   | l-Store-Or  | der-Preserving Compiler                                   |             | 60  |

|          | 5.1   | Target-Inde | ependent Optimizations                                    |             | 60  |

|          | 5.2   | Backend O   | ptimizations for AArch64                                  |             | 61  |

|          |       | 5.2.1 LLV   | M AArch64 Backend for C/C++ Atomics                       |             | 61  |

|          |       | 5.2.2 For   | bidding Reordering of Loads and Stores in AArch64         |             | 62  |

| 6        | Eval  | uation      |                                                           |             | 67  |

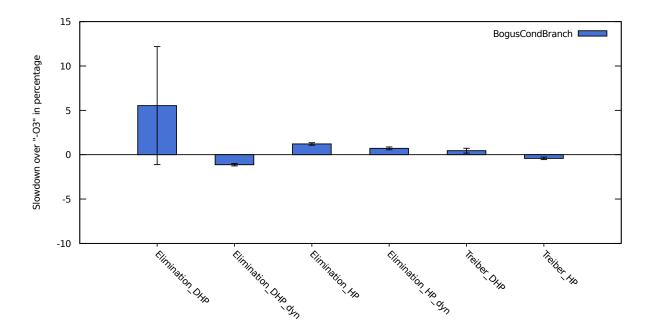

|          | 6.1   | Cost of Pre | serving Dependencies                                      |             | 68  |

|          |       |             | gle-Threaded Programs                                     |             | 68  |

|          |       |             | tiple Copies of Single-Threaded Programs                  |             | 71  |

|          | 6.2   |             | bidding Load-Store Reordering                             |             | 71  |

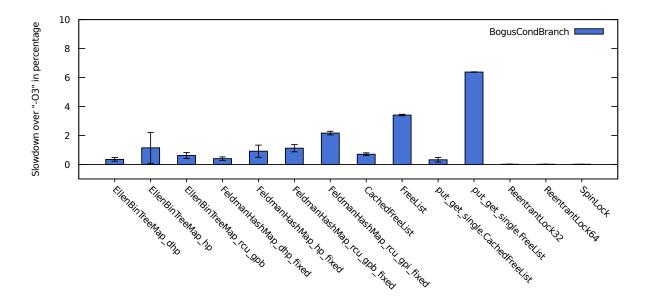

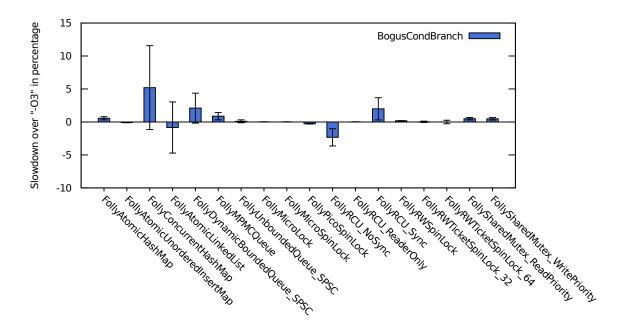

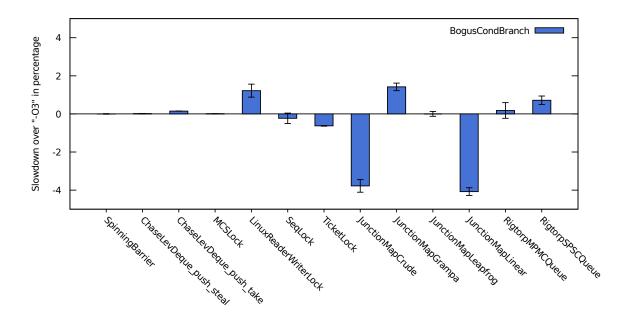

|          |       | 6.2.1 Con   | current Data Structures with Multiple Threads             |             | 73  |

|          |       | 6.2.2 Con   | current Data Structures with a Single Thread              |             | 75  |

|          |       | 6.2.3 Opt   | imizations for the Load-Store-Order-Preserving Approach   |             | 76  |

|          |       | 6.2.4 Sub   | tleties of Control Dependencies in the ARMv8 Memory Model |             | 78  |

| 7        | Rela  | ted Work    |                                                           |             | 82  |

|          | 7.1   | The Java a  | nd C/C++ Memory Models $\ldots$                           |             | 82  |

|          | 7.2   | Forbidding  | OOTA While Allowing Compiler Optimizations                |             | 84  |

|          | 7.3   | Case-Based  | Approaches                                                |             | 87  |

|          | 7.4   | Enforcing S | Stronger Memory Models                                    |             | 88  |

|          | 7.5   | Other Rela  | ted Work on Weak Memory Models                            |             | 90  |

| 8        | Con   | clusion and | d Future Work                                             |             | 93  |

| Bi       | bliog | raphy       |                                                           |             | 95  |

| Δ        | The   | Select Set  | of IR-Level Passes Enabled in Our Dependency-Preserv      | <i>z</i> in | a   |

| 11       | Inc   | Sciect Set  | Compiler                                                  | , 111       | 102 |

| в        | Deta  | ailed Resul | lts for the Load-Store-Order-Preserving Compiler          |             | 104 |

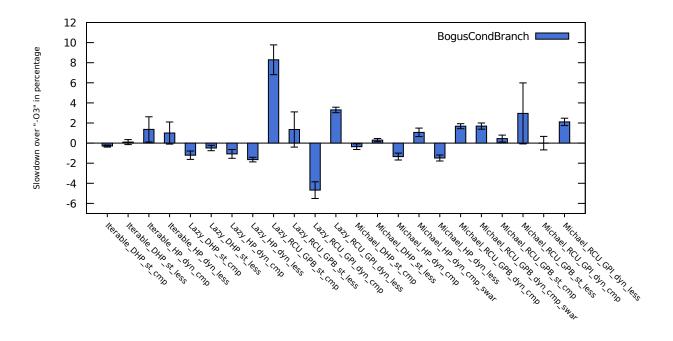

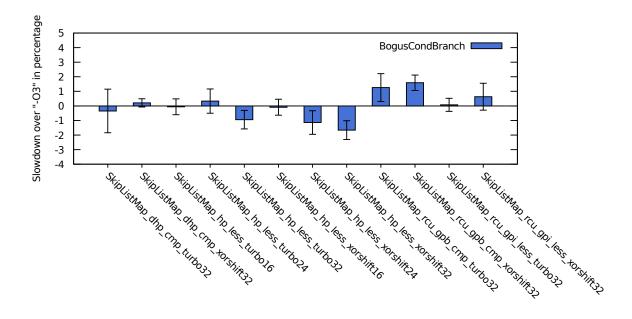

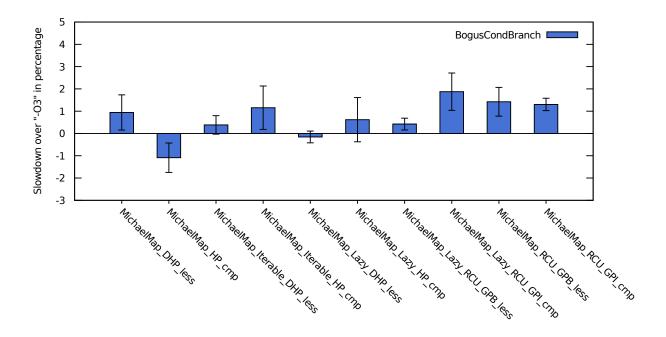

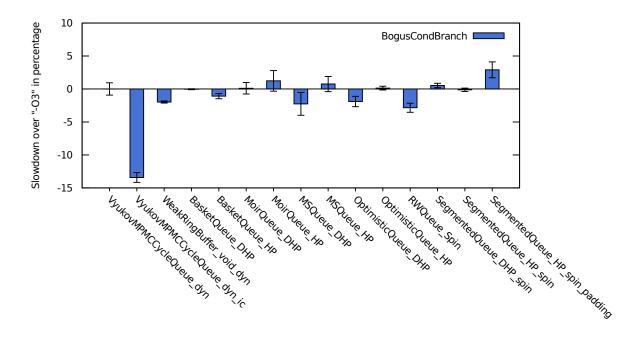

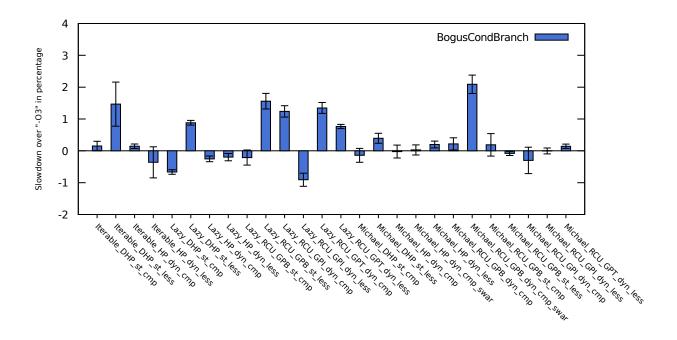

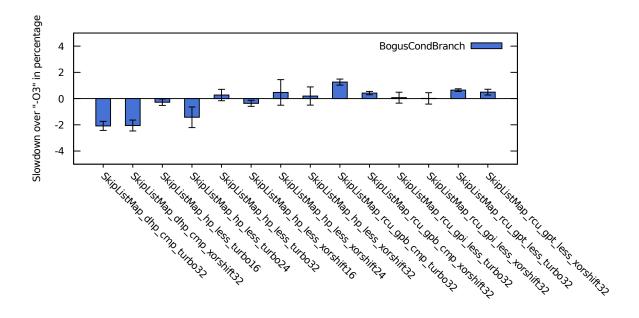

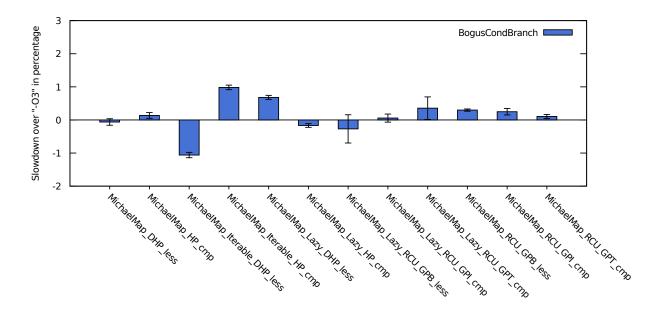

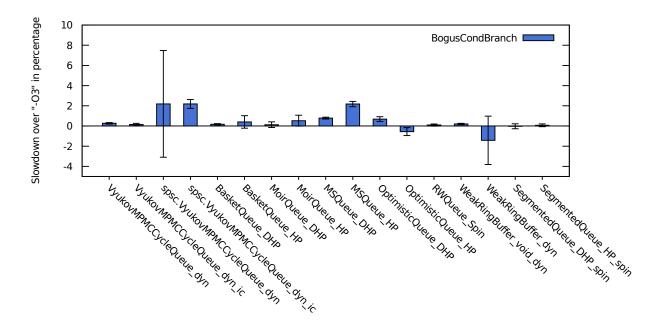

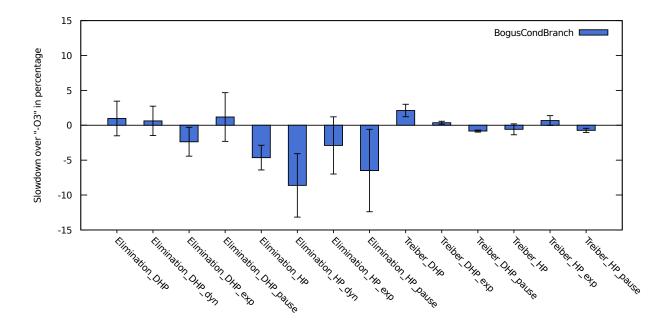

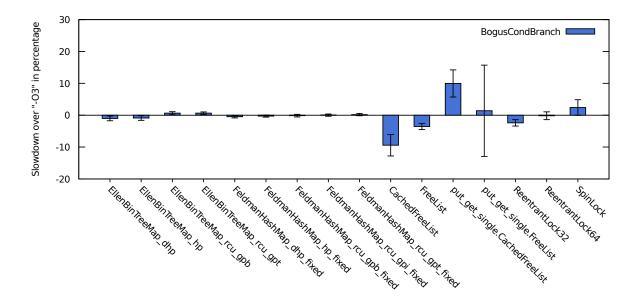

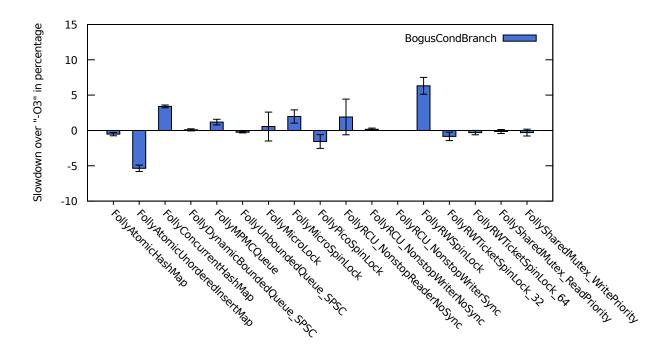

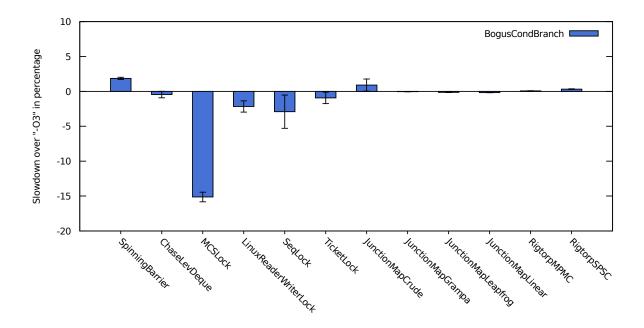

|          | B.1   |             | Adding Bogus Conditional Branches on Cortex-A72 Cores     |             | 105 |

|          |       |             | uning with a Single Thread                                |             | 105 |

|          |       |             | ming with Multiple Threads                                |             | 113 |

## LIST OF FIGURES

### Page

| 1.1  | With $x=y=r1=r2=0$ initially, $r1=r2=0$ is not allowed under the SC memory model. The Dekker's algorithm essentially relies on the non-existence of this behavior to provide mutual exclusion. | 5   |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.2  | A possible interleaving of Thread 1 and Thread 2 in Figure 1.1 which yields                                                                                                                    | 0   |

|      | the result of r1=r2=1 under the SC memory model                                                                                                                                                | 5   |

| 1.3  | The message passing example. With data=flag=r1=r2=0 initially, although the execution of r1=1 $\land$ r2=0 is not allowed by the x86-TSO memory model,                                         |     |

|      | it is allowed by the ARM and Power memory models                                                                                                                                               | 9   |

| 1.4  | The <i>load buffering</i> example. With x=y=r1=r2=0 initially, although the execution of r1=r2=1 is not allowed by the x86-TSO memory model, it is architec-                                   |     |

|      | turally allowed for ARM and Power.                                                                                                                                                             | 10  |

| 1.5  | With $x=y=r1=r2=0$ initially, $r1=r2=0$ is not allowed by the x86-TSO memory                                                                                                                   | 10  |

| 1.0  | model because we insert an <b>mfence</b> instruction between every store-load pair                                                                                                             |     |

|      | in both threads                                                                                                                                                                                | 10  |

| 1.6  | A variant of the <i>load buffering</i> example. With x=y=r1=r2=0 initially, r1=r2=1                                                                                                            | _ 0 |

|      | is not allowed by the ARM or Power memory models because in both threads                                                                                                                       |     |

|      | there exists a control dependency from the earlier load to the later store                                                                                                                     | 12  |

| 1.7  | The <i>load buffering</i> example with intentionally added control dependencies.                                                                                                               |     |

|      | Here, one should expect that this is ARM or Power assembly code with the                                                                                                                       |     |

|      | branch conditions translated exactly as in "r1==r1" and "r2==r2". With                                                                                                                         |     |

|      | x=y=r1=r2=0 initially, r1=r2=1 is not allowed by the ARM or Power memory                                                                                                                       |     |

|      | models similar to Figure 1.6                                                                                                                                                                   | 12  |

| 1.8  | Given this program written in a high-level programming language such as                                                                                                                        |     |

|      | C/C++, with x=y=r0=r1=r2=0 initially, an optimizing compiler can transform                                                                                                                     |     |

|      | the code such that the execution $r1=r2=0$ is allowed even if the transformed                                                                                                                  |     |

|      | program is run on a multiprocessor that only admits SC behaviors                                                                                                                               | 15  |

| 1.9  | With $\mathbf{x}$ and $\mathbf{y}$ declared as atomic variables and all memory accesses to them                                                                                                |     |

|      | associated with the seq_cst memory order parameter, this C++ program will                                                                                                                      |     |

|      | only admit SC executions, i.e., r1=r2=0 is not allowed                                                                                                                                         | 20  |

| 1.10 |                                                                                                                                                                                                |     |

|      | forbids the execution of both loads reading the initial stores                                                                                                                                 | 21  |

| 1.11         | With data declared as an non-atomic variable, flag declared as an atomic variable, data=flag=0 initially, the release store and acquire load together establish a <i>synchronizes-with</i> edge and thus ensure that the ordinary store data=1 <i>happens-before</i> the ordinary load r2=data, and thus this code is data- |                                        |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 1.12         | race-free and the execution of $r1=1 \land r2=0$ is not allowed                                                                                                                                                                                                                                                             | 21                                     |

|              | establishes <i>happens-before</i> relationship between the store/load on variable data.<br>With x and y declared as atomic variables and all memory accesses to them                                                                                                                                                        | 22                                     |

|              | associated with the relaxed memory order parameter, the C++ memory model allows the behavior of $r1=r2=1$ .                                                                                                                                                                                                                 | 22                                     |

| 1.14         | The execution graph for the example shown in Figure 1.13. The loads and stores with the <b>relaxed</b> ordering parameter do not establish synchronization, and the $C/C++$ memory model allows cycles in the union of the <i>sb</i> and <i>rf</i> relation.                                                                | 23                                     |

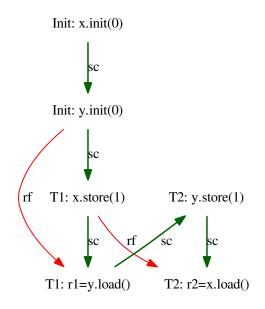

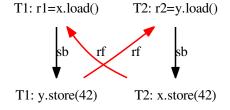

| $2.1 \\ 2.2$ | "Real Example". With $x=y=0$ initially, can $r1=r2=42$ ?                                                                                                                                                                                                                                                                    | 25<br>26                               |

| 2.3          | The execution graph for both executions in Figure 2.1 and Figure 2.2. Though the two examples are different, both executions are allowed by the $C/C++$ memory model formalism, and we cannot differentiate one from another by                                                                                             |                                        |

| 2.4          | the sequenced-before and reads-from relationship. $\dots \dots \dots$                                                                                                                                                       | 26                                     |

| 2.5          | agree whether the execution in this example is OOTA behavior                                                                                                                                                                                                                                                                | $\begin{array}{c} 27\\ 30 \end{array}$ |

| $3.1 \\ 3.2$ | The core syntax of our language                                                                                                                                                                                                                                                                                             | 36<br>36                               |

| 3.3          | Does the last store to y depend on the first load "r1 = load &x" in each of theses examples? Assume z=1 before each execution.                                                                                                                                                                                              | 37                                     |

| 3.4          | If x=y=0 and each element in array z is 0 initially, can r1=r2=1? Note that according to our dependency notion, store "y=1" has an address dependency on load "r1=x" because the address of store "z[r1]=1" depend on "r1=x".                                                                                               | 43                                     |

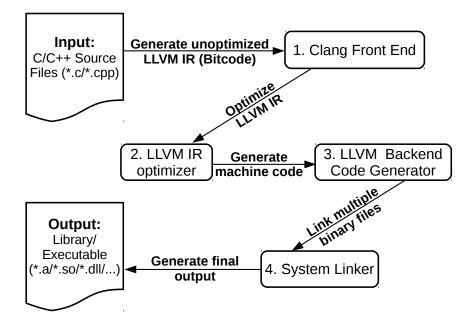

| $4.1 \\ 4.2$ | The standard LLVM compilation workflow for $C/C++$                                                                                                                                                                                                                                                                          | 50                                     |

| 1.2          | the store to y as long as function <b>bar</b> preserves its internal dependencies, as shown in the third column.                                                                                                                                                                                                            | 52                                     |

| 4.3          | LLVM optimizations (-03) can break data dependencies.                                                                                                                                                                                                                                                                       | 53                                     |

| 4.4          | LLVM optimizations (-03) can break control dependencies                                                                                                                                                                                                                                                                     | 54                                     |

| 4.5          | Examples of how the dependency-preserving <i>instcombine</i> pass transforms the code                                                                                                                                                                                                                                       | 54                                     |

| 4.6          | Examples of how the <i>simplifycfg</i> pass can potentially break dependencies                                                                                                                                                                                                                                              | 57                                     |

| 4.7          | Examples of how reordering stores can potentially break dependencies                                                                                                                                                                                                                                                        | 58                                     |

| 4.8        | Examples of loop unrolling. (a) statically computing the trip count and unrolling the loop potentially breaks control dependencies; (b) unrolling loops with explicit constant trip count does not break dependencies.                         | 59       |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 5.1        | Examples of how LLVM backend compiles C++ atomic operations to assembly code for AArch64 targets. In each example, variable <b>arr</b> is an array of <b>atomic_int</b> , and register <b>x8</b> contains the base address of array <b>arr</b> | 63       |

| 5.2        | Performance overhead incurred by different strategies of forbidding load-store                                                                                                                                                                 | 00       |

| 5.3        | reordering for micro-benchmarks                                                                                                                                                                                                                | 64<br>65 |

|            |                                                                                                                                                                                                                                                | 00       |

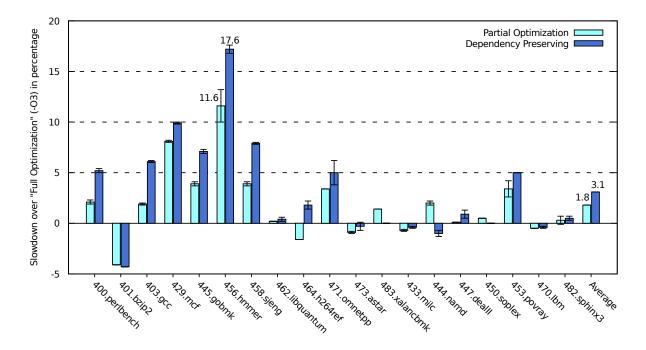

| 6.1        | Performance overhead (in percentage) introduced by different compiler con-<br>figurations compared to the full optimization configuration (-03) for C/C++<br>benchmarks in SPEC CPU2006                                                        | 69       |

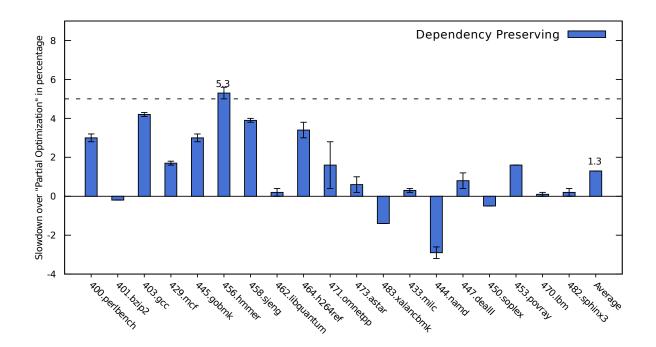

| 6.2        | Performance overhead (in percentage) introduced by our dependency-preserving compiler compared to the "Partial Optimization" configuration for C/C++                                                                                           | 70       |

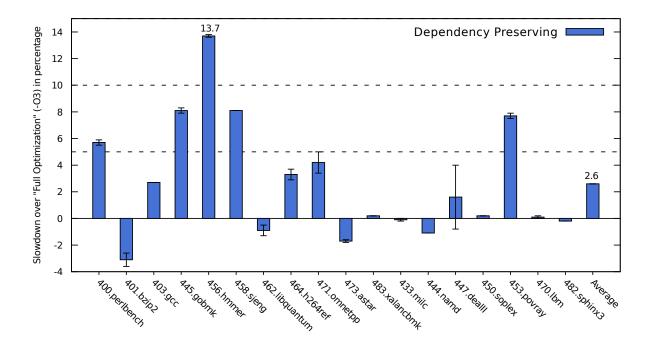

| 6.3        | benchmarks in SPEC CPU2006                                                                                                                                                                                                                     | 70       |

| 6.4        | thus causes out-of-memory error                                                                                                                                                                                                                | 72       |

| 6.5        | show results for benchmarks running with a single thread                                                                                                                                                                                       | 74       |

| 6.6        | other atomic store in between) is naturally guaranteed to be ordered before<br>subsequent stores after the read-modify-write operation                                                                                                         | 77       |

| 0.0        | cannot be reordered across the release store, we can safely delay adding a<br>bogus conditional branch till after the release store rather than before the                                                                                     |          |

| a <b>-</b> | release store                                                                                                                                                                                                                                  | 78       |

| 6.7        | According to Pulte et al. (2018)'s memory model, the store in line 5 has control dependency on the load in line 1.                                                                                                                             | 79       |

| 6.8 | In this example, the target of the conditional branch in line 3 is an infinite |    |

|-----|--------------------------------------------------------------------------------|----|

|     | loop (line 6 and 7), instead of the next instruction as shown in Figure 6.7.   |    |

|     | This does not change the semantics of the original code since the branch would |    |

|     | not be taken at runtime                                                        | 80 |

## ACKNOWLEDGMENTS

First of all, I would like to express my sincere gratitude to my advisor, Professor Brian Demsky, who has been incredibly supportive and an integral part of my doctoral research. His involvement and guidance have fueled my progress in every step of the way, and I have learned a ton about what qualities a good researcher should have while working with him. Without his persistent help and patience, this dissertation would not have been possible.

I would like to thank Professor Rainer Dömer and Professor Guoqing Xu, who have served on my candidacy exam committee and defense committee, for their invaluable time, contributions, and helpful feedback to my research. I would also like to thank many other researchers and anonymous reviewers for their very helpful discussion and feedback, which have helped improve my research.

I would also like to thank my previous and current colleagues in the *Programming Language Research Group*, Jin Zhou, Yong hun Eom, Brian Norris, Byron Hawkins, Ali Younis, Bin Xu, Rahmadi Trimananda, Hamed Gorjiara, and Zachary Snyder, for their invaluable advice, support and assistance. Specifically, I would like to thank Brian Norris for his wonderful CDSCHECKER model checking tool, upon which part of my doctoral research has been built.

I would like to thank Shuang Feng and Huan Tang, for giving me the internship opportunity at Google and their invaluable advice, guidance and patience during my internship period.

I would like to thank all of the great friends who I have made during my stay at UCI, for their help and support, and also for making the life of graduate school less boring.

Finally, I would like to thank my girlfriend, my parents, and my sister for their tremendous support, understanding and love in every aspect of my life.

My doctoral research and the work presented in this dissertation have been partly supported by a Google Research Award and the National Science Foundation under grants CCF-0846195, CCF-1217854, CNS-1228995, CCF1319786, OAC-1740210, and CNS-1703598.

## CURRICULUM VITAE

### Peizhao Ou

#### EDUCATION

**Doctor of Philosophy in Computer Engineering** University of California, Irvine

Master of Science in Computer Engineering University of California, Irvine

Bachelor of Science in Software Engineering Shanghai Jiao Tong University

#### **RESEARCH EXPERIENCE**

**Graduate Student Research** University of California, Irvine

#### TEACHING EXPERIENCE

**Teaching Assistant** University of California, Irvine **2012-2018** *Irvine, CA, USA*

**2012-2014** *Irvine*, *CA*, *USA*

2008-2012 Shanghai, China

2012 - 2018

Irvine, CA, USA

Spring 16 & Spring 17 Irvine, CA, USA

### PEER-REVIEWED CONFERENCE PUBLICATIONS

| Towards Understanding the Costs of Avoiding Out-of-<br>Thin-Air Results                   |          |

|-------------------------------------------------------------------------------------------|----------|

| International Conference on Object-Oriented Programming, Systems, Languag<br>Applications | ges, and |

| Checking Concurrent Data Structures Under the $C/C++11$ Memory Model                      | Feb 2017 |

| Symposium on Principles and Practice of Parallel Programming                              |          |

| AutoMO: Automatic Inference of Memory Order Parameters for $C/C++11$                      | Oct 2015 |

| International Conference on Object-Oriented Programming, Systems, Languag<br>Applications | ges, and |

| Automatic Parameter Recommendation for Practical<br>API Usage                             | Jun 2012 |

| International Conference on Software Engineering                                          |          |

#### SOFTWARE

OOTA-free Compiler Frameworkhttp://plrg.eecs.uci.edu/oota-html/An LLVM-based C/C++11 compiler framework that prohibits OOTA behavior by pre-serving syntactic dependencies or atomic load-store ordering.

AutoMO http://plrg.eecs.uci.edu/automo/ A tool that can infer memory order parameters for C/C++11 concurrent programs such that the programs only exhibit SC behaviors for the given test cases.

## ABSTRACT OF THE DISSERTATION

An Initial Study of Two Approaches to Eliminating Out-of-Thin-Air Results

By

Peizhao Ou

Doctor of Philosophy in Computer Engineering University of California, Irvine, 2018 Professor Brian Demsky, Chair

Eliminating so-called "out-of-thin-air" (OOTA) results is an open problem in many existing programming language memory models including Java, C, and C++. OOTA behaviors are problematic in that they break both formal and informal modular reasoning about program behavior. In spite of many years of research efforts, defining memory model semantics that are easily understood, allow existing optimizations, and forbid OOTA results remains an open problem. This dissertation explores two solutions to this problem that forbid OOTA results. The first solution is targeted towards Java-like languages in which all memory operations may create OOTA results, and the second solution is targeted towards C/C++-like memory models in which racing operations are explicitly labeled as atomic operations. Our solutions provide a per-candidate execution criterion that makes it possible to examine a single execution and determine whether the memory model permits the execution. We implemented and evaluated both solutions in the LLVM compiler framework. Our results show that on an ARMv8 processor the first solution has an average overhead of 3.1% and a maximum overhead of 17.6% on the SPEC CPU2006 C/C++ benchmarks, and that the second solution has no overhead on average and a maximum overhead of 6.3% on 43 concurrent data structures. The results indicate that these approaches to eliminating out-of-thin-air behaviors deserve further consideration.

## Chapter 1

## Introduction

With the wide scale deployment of multi-core processors, software developers must write parallel software to leverage the benefits provided by additional cores. In the meantime, mainstream hardware architectures primarily target shared-memory multiprocessors, in which multiple cores share the same main memory and communicate with one another through reading from and writing to the shared memory<sup>1</sup>. In a simplistic and ideal world, reasoning the execution of multi-threaded programs would be fairly straightforward: there exists a global view of the shared memory; each thread executes the memory operations strictly in program order, and a write to the shared memory immediately updates the shared memory and becomes visible to all the threads while a read from the shared memory retrieves the most up-to-date value. This intuitive abstraction was first introduced as *sequential consistency* by Lamport (1979).

However, in order to gain better performance, modern hardware violates sequential consistency in many ways. For example, out-of-order execution in modern processors can break the abstraction that memory accesses are executed in program order; or the memory subsystem

$<sup>^{1}</sup>$ In this dissertation, we are somewhat relaxed in our exchangeable usage of load/read to refer to the action of retrieving the value from a shared memory location, and store/write to refer to the action of updating a shared memory location with a value.

(e.g., store buffer or cache, etc.) can break the abstraction that a write is immediately visible to all the threads. Thus, we need a contract between a specific architecture and its users to specify what value a load can obtain for a multi-threaded program written at the machinecode level. Such a contract is known as a hardware memory model. A memory model in general specifies the semantics of memory reads/writes in a multi-threaded environment, and a hardware memory model does so at the hardware (or machine code) level.

In addition to the underlying hardware, standard compiler optimizations can also violate sequential consistency because they can transform the source code in such a way that read-/write operations appear to be reordered (Marino et al., 2011). In the meantime, the correctness of certain multi-threaded programs written in high-level programming languages can rely on the non-existence of certain relaxed behaviors<sup>2</sup> (e.g., reordering of memory accesses). Thus, in order to make source code portable across different compiler frameworks and hardware platforms, researchers and practitioners have designed and proposed programming language implementers to specify the semantics of loads and stores in a multi-threaded program at the programming language level. Most programming languages, such as C/C++ and Java, guarantee sequential consistency for programs without data races (Adve and Hill, 1990).

However, this guarantee is fragile — a single data race voids the sequential consistency guarantee for the entire program. Indeed, programs with data races have undefined semantics under the C/C++11 memory model (Boehm and Adve, 2008; JTC, 2011; Becker, 2011; Batty et al., 2011), mostly due to the fact that data races can violate the assumptions made by compiler optimizations. For existing compilers, assigning meaningful semantics to racy programs is extremely complicated. The language semantics must capture behaviors that arise from both compiler and processor optimizations. While the C and C++ memory models

$<sup>^{2}</sup>$ In literature, in the context of shared-memory multi-core systems, relaxed/weak (memory) behavior usually refers to the executions that are not sequentially consistent, and relaxed/weak memory models usually refer to the memory models that allow relaxed/weak behavior.

do not even attempt to assign semantics to such programs, Java is intended to support the safe execution of untrusted code. Thus, Java must ensure safety for racy programs and the Java Memory Model (Manson et al., 2005; Shipilëv, 2016a,b) attempts to assign semantics to such programs. A similar situation exists in C and C++ when it comes to the support for low-level atomic operations. The weakest atomic operations, which are specified using the memory\_order\_relaxed memory order parameter, only guarantee coherence and cannot be used to implement synchronization.

Hence, in both situations for Java and C/C++ relaxed atomics, one of the design goals is to define reasonable and preferably easy-to-understand semantics that allow standard compiler optimizations and modern hardware optimizations. This, however, has been shown to be very difficult, mostly due to an outstanding problem — eliminating out-of-thin-air (OOTA) results, i.e., results that can be justified only by some circular reasoning. For example, in a concurrent execution, we may justify the store of value 42 to memory location  $\mathbf{x}$  only because we assume the exact store would happen in the first place. Such OOTA results have been shown to be disastrous because they hinder both formal and informal modular reasoning of concurrent programs. In this dissertation, we present two approaches to tackling this problem, i.e., the dependency-preserving approach and the load-store-order-preserving approach. We implemented both approaches on top of the LLVM compiler framework and evaluated their runtime overheads on an ARMv8 multiprocessor<sup>3</sup>. The remainder of this dissertation is structured as follows:

- In the remainder of this chapter, we discuss the background of sequential consistency (Section 1.1), hardware memory models (Section 1.2), compiler optimizations (Section 1.3), and programming language memory models (Section 1.4) in order to give readers sufficient background on how the out-of-thin-air problem arises.

- In Chapter 2, we depict the out-of-thin-air problem that this dissertation focuses on, <sup>3</sup>The study presented in this dissertation is based on Ou and Demsky (2018).

show the disastrous consequences of allowing OOTA results, and outline existing proposals for solving the problem and our contributions.

- In Chapter 3, we demonstrate our memory model extensions for both of our approaches.

- In Chapter 4, we discuss our approach to extending the LLVM compiler to preserve our dependency notion.

- In Chapter 5, we discuss our approach to extending the LLVM compiler to preserve load-store ordering.

- In Chapter 6, we evaluate both approaches and show their runtime overheads.

- In Chapter 7, we discuss related work.

- In Chapter 8, we conclude and outline potential future work.

### 1.1 The Sequentially Consistent Memory Model

Sequential consistency, or the sequentially consistent  $(SC^4)$  memory model, provides an intuitive abstraction that a multi-threaded program is executed as if there exists a strict interleaving of memory accesses from each thread that respects program order. Figure 1.1 shows the execution of a simple example<sup>5</sup> under the SC memory model. Here, variables **x** and **y** are two global variables which have the initial value of **0**, and variables **r1** and **r2** are local variables (or registers) that are initialized to be **0**. Then there are two threads, Thread 1 and Thread 2: Thread 1 writes value **1** to variable **x** and then reads from variable

$<sup>^{4}</sup>$ We loosely use the term "SC" to refer to either "sequentially consistent" or "sequential consistency" in this dissertation.

<sup>&</sup>lt;sup>5</sup>We use pseudocode snippets like this throughout this dissertation. It is important to note that these examples are written in a C-like language whose purpose is to show the effect of memory accesses in a multi-threaded environment, and that they can actually represent code written in assembly, C/C++, or Java, etc., depending on the context. Also, in later examples, we use lower-case letters x, y, z, etc., to represent shared global variables, and symbols r1, r2, r3, etc., to represent local variables or registers, unless otherwise stated.

y; Thread 2 symmetrically writes value 1 to variable y and then reads from variable x. Under the SC memory model, depending on the actual interleaving of the two threads, there exist three possibilities for the values that variables r1 and r2 can hold: (1) r1=r2=1; (2) r1=1  $\land$ r2=0; or (3) r1=0  $\land$  r2=1. We show a possible interleaving of an SC execution that yields the result of r1=r2=1 in Figure 1.2, in which the two stores from both threads are executed before both loads. Notably, no execution would generate the result of r1=r2=0 under the SC memory model since both threads must respect the program order and thus write value 1 to either variable x or y before any reads from variable x or y can be executed. The Dekker's mutual exclusion algorithm (Dijkstra, 2002) essentially relies on the non-existence of this behavior (i.e., r1=r2=0) to provide mutual exclusion.

| x = y = r1 = r2 = 0; // Initially |          |

|-----------------------------------|----------|

| Thread 1                          | Thread 2 |

| x = 1;                            | y = 1;   |

| r1 = y;                           | r2 = x;  |

Figure 1.1: With x=y=r1=r2=0 initially, r1=r2=0 is not allowed under the SC memory model. The Dekker's algorithm essentially relies on the non-existence of this behavior to provide mutual exclusion.

| Steps                          | States of Shared Memory and Local Variables |

|--------------------------------|---------------------------------------------|

| Initially, no thread executes  | x=y=r1=r2=0                                 |

| Thread 1 executes line "x=1;"  | x=1 $\land$ y=r1=r2=0                       |

| Thread 2 executes line "y=1;"  | x=y=1 ∧ r1=r2=0                             |

| Thread 1 executes line "r1=y;" | x=y=r1=1 $\land$ r2=0                       |

| Thread 2 executes line "r2=x;" | x=y=r1=r2=1                                 |

Figure 1.2: A possible interleaving of Thread 1 and Thread 2 in Figure 1.1 which yields the result of r1=r2=1 under the SC memory model.

Given its simplicity, there exist many analyses, tools, concurrent data structures, and algorithms that are designed based on the SC memory model. In fact, researchers have explored approaches that just provide sequential consistency (Marino et al., 2011; Singh et al., 2012) for memory accesses for the C/C++ programming language. However, these approaches may require special hardware support to achieve competitive performance because mainstream hardware does not implement sequential consistency. We will illustrate this in Section 1.2.

## **1.2 Hardware Memory Models**

While the SC memory model is intuitive, it is not implemented by mainstream processors (e.g., x86, ARM<sup>6</sup>, Power<sup>7</sup>, and Itanium) for the sake of performance. Instead, these processors have relaxed memory models that are strictly weaker than the SC memory model and generally allow different levels of reordering of memory accesses.

#### **1.2.1** Relaxed Behaviors Exposed by Hardware

#### The x86 Multiprocessors

The x86 multiprocessors are designed to have a relatively strong hardware memory model, which is formalized as the *x86-TSO* memory model (Owens et al., 2009; Sewell et al., 2010). It disallows load-load, load-store, and store-store reordering, but allows store-load reordering, i.e., allowing a later load to be reordered up across a previous store (in program order) to a different memory location. Also, the x86-TSO memory model enforces that there exists a total order for stores (to all memory locations) that is consistent across all the threads, which is referred to as *total store ordering* (TSO).

We use Figure 1.1 as an example to show the relaxed behavior that x86 processors can expose. Here, if we write the code snippet in Figure 1.1 in x86 assembly and run it on an x86 processor, it is possible that we observe the result of r1=r2=0. In this non-SC execution,

$<sup>^6\</sup>mathrm{We}$  use the term "ARM" to refer to both the older version of ARM — ARMv7, and the more recent version of ARM — ARMv8, unless otherwise stated.

<sup>&</sup>lt;sup>7</sup>We use the term "Power" in this dissertation to refer the multiprocessor family that includes various IBM POWER and PowerPC implementations.

both threads appear to perform store-load reordering and let both loads execute before the previous stores and read the stale values. One notable hardware optimization called *store buffering* can result in this execution. This optimization would add a store buffer unit that is local to each thread<sup>8</sup>. Then a store would go to the store buffer unit rather than directly to the main memory. To ensure per-location coherence, a load would first check whether the store buffer contains a store to its location or not; if so, it can do a thread-local store-to-load forwarding or otherwise would need to fetch the value from the shared memory (or a higher-level cache). At some point of the execution, the stores in the store buffer would be propagated to other cores. Hence, in this example, if both stores to variable x and y execute and stay in each thread's store buffer, and before they are propagated to the other thread, both loads to the opposite variables may execute and only see the initial value of 0. This example is also known as the *store buffering* example.

#### The ARM and Power Multiprocessors — More Relaxed Behavior

The ARM and Power architectures have similar (but not identical) relaxed memory models (Maranget et al., 2012; Sarkar et al., 2011, 2012; Flur et al., 2016; Pulte et al., 2018), which are weaker than the x86-TSO memory model and can expose more relaxed behavior. First of all, not surprisingly, similar to the x86-TSO memory model, the ARM and Power memory models allow the store buffering behavior (i.e., the store-load reordering). In addition, in the architectural design of ARM and Power multiprocessors, there exist other aspects/optimizations that can expose other types of reordering of memory accesses, e.g., aggressive out-of-order execution such as speculative execution, more complicated store buffering optimizations such as hierarchical store buffering, and complex memory subsystem, etc. Also, as opposed to the total store ordering property in the x86-TSO memory model, the ARM and

$<sup>^{8}</sup>$ Here we picture a context where the store buffer unit is local to each thread, which is consistent with the x86-TSO abstract machine. However, for processors other than x86, depending on the actual processor design, the store buffer unit could be local to each thread, shared between threads on the same SMT core, or some more complicated design, etc.

Power memory models allow stores to different memory locations to propagate to different threads in different orders (with caveats). We will show examples to illustrate the relaxed behavior that the ARM and Power memory models allow in the following.

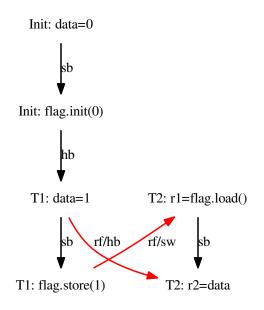

Message Passing — Store-Store & Load-Load Reordering Consider the message passing example shown in Figure 1.3. Here, variables data and flag are two shared variables, and variables r1 and r2 are registers, and they all have the initial value of 0. Thread 1 can be viewed as a producer thread which updates the value of variable data and then updates variable flag to 1 to indicate to Thread 2 that variable data is ready to be consumed. Thread 2 can be viewed as a consumer thread, which continuously reads the flag variable until it has a non-zero value; once Thread 2 observes that the value of variable flag becomes non-zero, it starts to read variable data, which presumably should observe the value of 1 by the design of this producer-consumer scheme. In real-world code, one can expect Thread 1 to be the thread that initializes the fields of a complex object (i.e., store "data=1") and then assigns the pointer to the initialized object to a variable (i.e., store "flag=1"), and Thread 2 to be the thread that continuously checks if the pointer to that object is non-null (i.e., "r1=flag") and starts to read the fields of that object (i.e., "r2=data") if the pointer is non-null. Thus, the correctness of this code scheme essentially relies on the assumption that when the load from variable flag reads non-zero values, the later load from variable data must see the effect of the store "data=1".

If we write this code directly in x86 assembly, we are guaranteed that we will only observe the result of r1=r2=1 because the x86-TSO memory model does not allow store-store or load-load reordering. However, for the same example, the ARM and Power memory models allow the non-SC result of  $r1=1 \land r2=0$  because they allow load-load reordering as well as store-store reordering for different memory locations. For example, under the ARM and Power memory models, stores in a thread may not propagate to other threads in program order. Thus in Thread 1, the store to variable flag may propagate to Thread 2 before the store to variable data, as a result of which Thread 2 may see the update to variable flag but miss the update to variable data. It appears to Thread 2 that the two stores in Thread 1 are reordered. In addition, the two loads in Thread 2 can also appear to be reordered even if both stores are propagated to Thread 2 in program order. A possible scenario is that the processor performs speculative reads. In Thread 2, before the earlier load from variable flag returns value 1, the later load from variable data can speculatively execute and return a stale value (i.e., value 0).

| data = flag = $r1 = r2 = 0$ ; // Initially |                                  |

|--------------------------------------------|----------------------------------|

| Thread 1                                   | Thread 2                         |

| data = 1;                                  | <pre>while (!(r1 = flag));</pre> |

| flag = 1;                                  | r2 = data;                       |

Figure 1.3: The *message passing* example. With data=flag=r1=r2=0 initially, although the execution of r1=1  $\land$  r2=0 is not allowed by the x86-TSO memory model, it is allowed by the ARM and Power memory models.

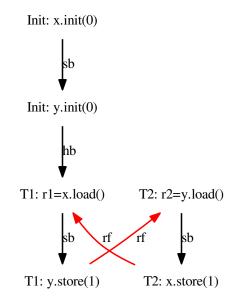

Load Buffering — Load-Store Reordering Another notable reordering that is architecturally allowed on ARM and Power is the load-store reordering. Consider the example shown in Figure 1.4, which looks similar to the store buffering example except that both threads perform a load first and a store to the opposite location second. The non-SC result of r1=r2=1 is architecturally allowed on ARM and Power<sup>9</sup>. Once again, similar to the message passing example, x86 processors would disallow this execution as they do not allow load-store reordering.

$<sup>^{9}</sup>$ According to Maranget et al. (2012), this result has been observed on ARM processors and has not been observed on Power processors in practice, but it is architecturally allowed for both.

| x = y = r1 = r2 = 0; // Initially |          |

|-----------------------------------|----------|

| Thread 1                          | Thread 2 |

| r1 = x;                           | r2 = y   |

| y = 1;                            | x = 1;   |

Figure 1.4: The *load buffering* example. With x=y=r1=r2=0 initially, although the execution of r1=r2=1 is not allowed by the x86-TSO memory model, it is architecturally allowed for ARM and Power.

## 1.2.2 Constraining Relaxed Behavior with Memory Fences and Dependencies

Although mainstream hardware can expose relaxed behaviors to users, they usually offer options to constrain relaxed behavior by enforcing stronger ordering guarantees. One important mechanism is to provide explicit machine instructions called *memory fences* (or *memory barriers*), or fences. The core idea is that given a specific fence instruction, certain types of memory operations that are before the fence (in program order) must become globally visible<sup>10</sup> before certain types of memory operations that are after the fence (in program order). For example, the **mfence** instruction in the x86 architecture requires that all memory operations before it (in program order) must be globally visible before any memory operations after it (in program order)<sup>11</sup>. Figure 1.5 shows a concrete example in which we use the **mfence** instruction to forbid the execution of **r1=r2=0** in the store buffering example, by adding an **mfence** instruction between each store-load pair in both threads.

| x = y = r1 = r2 = | = 0; // Initially |

|-------------------|-------------------|

| Thread 1          | Thread 2          |

| x = 1;            | y = 1;            |

| mfence;           | mfence;           |

| r1 = y;           | r2 = x;           |

Figure 1.5: With x=y=r1=r2=0 initially, r1=r2=0 is not allowed by the x86-TSO memory model because we insert an mfence instruction between every store-load pair in both threads.

$<sup>^{10}</sup>$ A load operation is considered to be globally visible when the value to be loaded into the destination register is determined.

<sup>&</sup>lt;sup>11</sup>In the abstract machine of the x86-TSO memory model, the **mfence** instruction will flush the store buffer of that thread and propagate the stores to other threads.

Similarly, in the ARM and Power memory models, there exist similar fence instructions. The notable difference is that since the ARM and Power processors generally allow more reordering of memory accesses than the x86 architecture does, they provide more flexible fence variants. For example, the ARM architecture provides the full fence named "dmb sy" (or "dmb" for short), which is effectively similar to mfence in the x86 architecture (Maranget et al., 2012; Pulte et al., 2018); also, it provides weaker variants, such as the "dmb ld" instruction which only waits for loads (before the fence in program order) to complete, or the "dmb st" instruction which only waits for stores (before the fence in program order) to complete (ARM, 2016). Similarly, the Power architecture also provides different variants of fence instructions such as the sync instruction (also known as the heavyweight sync) which enforces store-store, store-load, load-load, and load-store ordering, and the lwsync instruction (also known as the lightweight sync) which is cheaper to execute than the sync instruction and enforces similar ordering constraints except store-load ordering (Sarkar et al., 2011; Maranget et al., 2012). For example, if we replace the mfence instructions in Figure 1.5 with either dmb or sync instructions in ARM or Power assembly, respectively, they can prohibit the execution of r1=r2=0, similar to using mfence instructions in x86 processors; however, fences like "dmb ld", "dmb st", or lwsync are not sufficient to prohibit the relaxed behavior in this case. In addition, the ARMv8 architecture introduces fence-like load/store instructions to enforce ordering constraints, which we will discuss in more details in Chapter 5.

In addition to fences, certain dependencies between hardware instructions can also constrain the reordering of memory operations. For example, Figure 1.6 shows a variant of the load buffering example, with the key difference that there exists a *control dependency* from the earlier load to the later store in both threads. Loosely speaking, under the ARM and Power memory models, when the result of a load is used to compute the condition of a conditional branch, and a store is after the conditional branch in program order, then the load forms a control dependency towards the store, which requires the load-store ordering to be respected (Sarkar et al., 2011; Maranget et al., 2012; Pulte et al., 2018). Hence, in this case, the result of r1=r2=1 is disallowed. There also exist other types of dependencies. For example, a *data dependency* roughly captures the dependency from the storing value of a store to the store itself, and an *address dependency* captures the dependency from the address of a load/store to the load/store itself. While dependencies can exist naturally in the source code as shown in Figure 1.6, one can also intentionally add dependencies to the assembly code for stronger ordering guarantees. For example, we can write the code shown in Figure 1.7 directly in ARM or Power assembly, in which the branch conditions are translated exactly as in "r1==r1" and "r2==r2". Then these intentionally added control dependencies can effectively forbid the load-store reordering in both threads and thus the result of r1=r2=1 is disallowed.

| x = y = r1 = r2 = 0; // Initially |           |

|-----------------------------------|-----------|

| Thread 1                          | Thread 2  |

| r1 = x;                           | r2 = y    |

| if (r1) {                         | if (r2) { |

| y = 1;                            | x = 1;    |

| }                                 | }         |

Figure 1.6: A variant of the *load buffering* example. With x=y=r1=r2=0 initially, r1=r2=1 is not allowed by the ARM or Power memory models because in both threads there exists a control dependency from the earlier load to the later store.

| x = y = r1 = r2 = 0; // Initially |               |

|-----------------------------------|---------------|

| Thread 1                          | Thread 2      |

| r1 = x;                           | r2 = y        |

| if (r1==r1) {                     | if (r2==r2) { |

| y = 1;                            | x = 1;        |

| }                                 | }             |

Figure 1.7: The *load buffering* example with intentionally added control dependencies. Here, one should expect that this is ARM or Power assembly code with the branch conditions translated exactly as in "r1==r1" and "r2==r2". With x=y=r1=r2=0 initially, r1=r2=1 is not allowed by the ARM or Power memory models similar to Figure 1.6.

Note that hardware fences (depending on the actual type of fences) may incur significant runtime overhead, so developers generally use them only when a specific ordering constraint is necessary to guarantee the correctness of a multi-threaded program. For example, if we want to implement the Dekker's mutual exclusion algorithm correctly on x86 processors, we must insert the mfence instruction appropriately similar to Figure 1.5.

It is important to note that the discussion about the x86-TSO, ARM, and Power memory models in this section is far from complete, but it should be sufficient for the purpose of illustration in the scope of this dissertation. Notably, the ARM and Power memory models would allow more relaxed behaviors such as allowing a store to be propagated to other threads at different time, etc., but mainstream hardware does enforce cache coherence — a per-location total order. Indeed, researchers have invested tremendous efforts in clarifying and formalizing hardware memory models vigorously. Notably, Owens et al. (2009); Sewell et al. (2010) formalize the x86-TSO memory model; Sarkar et al. (2011) formalize the Power memory model; Maranget et al. (2012) clarify the Power and ARMv7 memory model; and Flur et al. (2016); Pulte et al. (2018) formalize the ARMv8 memory model.

## **1.3** Compiler Optimizations

There exists yet another important aspect that attributes to exposing relaxed behaviors. Given a multi-threaded program written in a high-level programming language such as C/C++ or Java, etc., and suppose we have a specialized multiprocessor that only admits SC executions, we could still be subject to relaxed behaviors, due to the existence of compiler optimizations. Modern compilers have introduced many optimizations that help increase the performance of programs written in high-level programming languages, and there is a general rule behind these optimizations, usually referred to as the "as-if" rule, which roughly means that a compiler can transform a program as long as they do not change the observable behavior of the program. This, however, can expose relaxed behaviors in a multi-threaded environment.

Consider the example shown in Figure 1.8, which is a variant of the program shown in Figure 1.1. The difference is that this program is written in a high-level programming language such as C/C++, and that Thread 1 has one more load statement "r0=y" in the beginning. An optimizing compiler can transform this code such that the transformed program would exhibit the execution in which r1=r2=0 even if it is run on an SC multiprocessor. The likely transformation done by the compiler follows: in Thread 1, the compiler realizes that the two loads from variable  $\mathbf{y}$  are separated by a store that is to a different shared variable  $\mathbf{x}$ (by points-to analysis the compiler can figure out that variable  $\mathbf{x}$  and  $\mathbf{y}$  point to different memory locations), and thus in a single-threaded environment, the second load from variable y is redundant (since the store "x=1" cannot change the value of variable y). Hence, instead of issuing two loads, the compiler can replace the second load simply with the result of the first one. Then the execution in which r1=r2=0 can be produced by the following interleaving: (1) Thread 1 loads from variable y and r0 obtains value 0; (2) Thread 2 writes value 1 to variable y; (3) Thread 2 reads from variable x and r2 obtains value 0; (4) Thread 1 writes value 1 to variable x; and (5) variable r1 reuses the result of variable r0 (instead of reloading from variable y), which also obtains value 0. This transformation also appears that the second load "r1=y" is reordered up across the store "x=1" and executes early. Note that there also exist other compiler optimizations that may appear to perform other types of reordering (Marino et al., 2011).

## 1.4 Programming Language Memory Models

Given the fact that different multiprocessors and compilers can expose different levels of relaxed behaviors, it would be exceedingly difficult to write high-performance and portable multi-threaded programs. Moreover, Boehm (2005) argues that "threads cannot be implemented as a library", with the idea that a multi-threaded program may not be compiled

| x = y = r1 = r2 = 0; // Initially                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                   |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--|

| Thread 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Thread 2          |  |

| r0 = y;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |  |

| x = 1;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | y = 1;<br>r2 = x; |  |