## UNIVERSITY OF CALIFORNIA

## SANTA CRUZ

## **OpenRAM:** An Open-Source Memory Compiler

A thesis submitted in partial satisfaction of the requirements for the degree of

## MASTER OF SCIENCE

in

## COMPUTER ENGINEERING

$\mathbf{b}\mathbf{y}$

## Jeffrey T. Butera

September 2013

The Thesis of Jeffrey T. Butera is approved:

Professor Matthew Guthaus, Chair

Professor Jose Renau

Professor Patrick E. Mantey

Tyrus Miller Vice Provost and Dean of Graduate Studies Copyright © by Jeffrey T. Butera 2013

# Table of Contents

| Li       | st of | Figure  | es                                    | v    |

|----------|-------|---------|---------------------------------------|------|

| Li       | st of | Tables  | 5                                     | vi   |

| A        | bstra | ict     |                                       | vii  |

| A        | cknov | wledgn  | nents                                 | viii |

| 1        | Intr  | oducti  | on                                    | 1    |

| <b>2</b> | Bac   | kgrour  | nd                                    | 3    |

|          | 2.1   | SRAM    | I Architecture                        | . 3  |

|          |       | 2.1.1   | The 6T Cell and Memory Array          | . 3  |

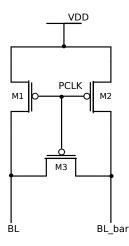

|          |       | 2.1.2   | Precharge Circuitry                   | . 6  |

|          |       | 2.1.3   | Address Decoder and Word line Drivers | . 6  |

|          |       | 2.1.4   | Column Multiplexer                    | . 8  |

|          |       | 2.1.5   | Sense Amplifier                       | . 9  |

|          |       | 2.1.6   | Write Driver                          | . 10 |

|          |       | 2.1.7   | Control Logic                         | . 10 |

|          | 2.2   | SRAM    | 1 Operation                           | . 13 |

|          |       | 2.2.1   | Signals                               | . 13 |

|          |       | 2.2.2   | Timing Considerations                 | . 14 |

|          |       | 2.2.3   | Read Operation                        | . 14 |

|          |       | 2.2.4   | Write Operation                       | . 15 |

| 3        | Soft  | tware I | Implementation                        | 17   |

|          | 3.1   | Main    | Compiler Components                   | . 17 |

|          |       | 3.1.1   | OpenRAM Design Hierarchy              | . 18 |

|          |       | 3.1.2   | GdsMill                               | . 20 |

|          |       | 3.1.3   | Technology Directory                  | . 21 |

|          | 3.2   | OpenF   | RAM Modules                           | . 21 |

|          | 3.3   | Physic  | eal Verification                      | . 31 |

|          | 3.4   | Memo    | ry Characterizer                      | . 31 |

| 4 | Con               | Contributions               |                 |  |  |  |  |

|---|-------------------|-----------------------------|-----------------|--|--|--|--|

|   | 4.1               | Snap-to-Grid                | 32              |  |  |  |  |

|   | 4.2               | Memory Characterizer        | 33              |  |  |  |  |

|   |                   | 4.2.1 Spice Stimulus        | 33              |  |  |  |  |

|   |                   | 4.2.2 Read and Write Delays | 34              |  |  |  |  |

|   |                   | 4.2.3 Power                 | 34              |  |  |  |  |

|   |                   | 4.2.4 Setup and Hold Time   | 35              |  |  |  |  |

|   | 4.3               | Characterizer Results       | 37              |  |  |  |  |

|   | 4.4               | Area                        | 42              |  |  |  |  |

| 5 | <b>Cor</b><br>5.1 |                             | <b>43</b><br>44 |  |  |  |  |

|   | 0.1               |                             | TT              |  |  |  |  |

| R | efere             | ences                       | 45              |  |  |  |  |

|   |                   |                             |                 |  |  |  |  |

47

# List of Figures

| 1  | Memory Trends                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2  |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2  | SRAM Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4  |

| 3  | Schematic: 6T Cell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4  |

| 4  | Schematic: Precharge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6  |

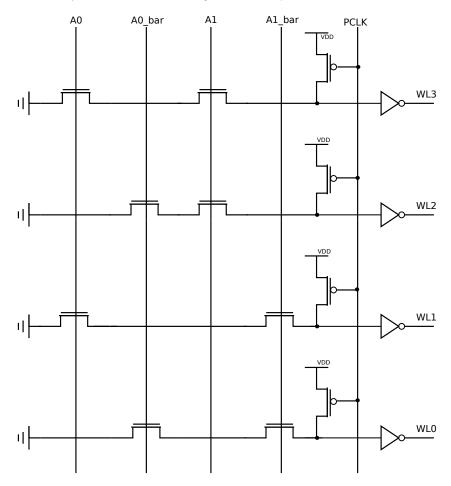

| 5  | Schematic: NAND Decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7  |

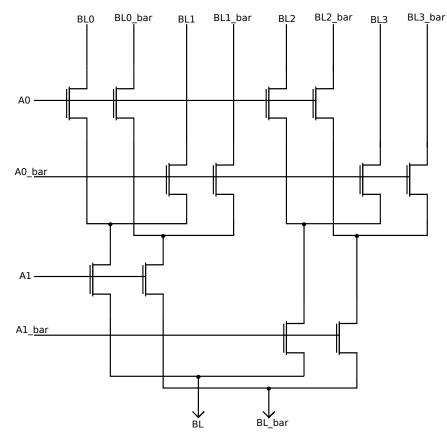

| 6  | Schematic: Column Mux                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8  |

| 7  | Schematic: Sense Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10 |

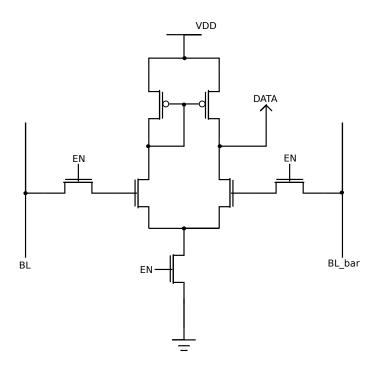

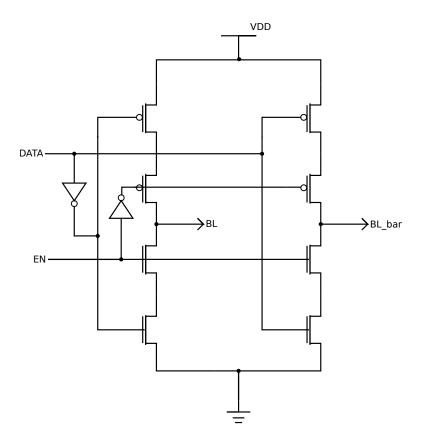

| 8  | Schematic: Write Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 11 |

| 9  | Schematic: Control Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 12 |

| 10 | Schematic: Master-Slave Flip-Flop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 13 |

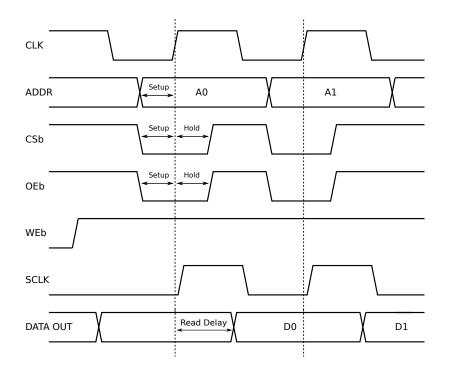

| 11 | Timing Diagram: Read Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15 |

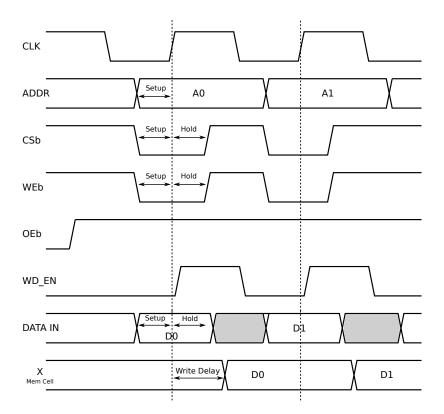

| 12 | Timing Diagram: Write Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16 |

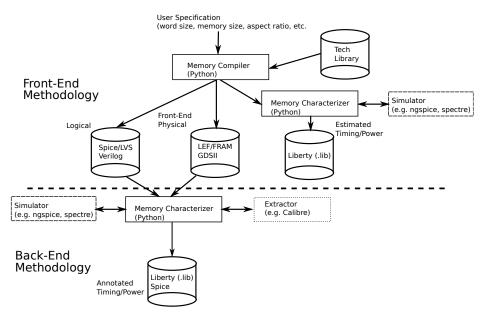

| 13 | Overall Compilation and Characterization Methodology $\hdots \hdots \hd$ | 17 |

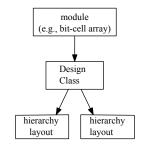

| 14 | Class Hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 18 |

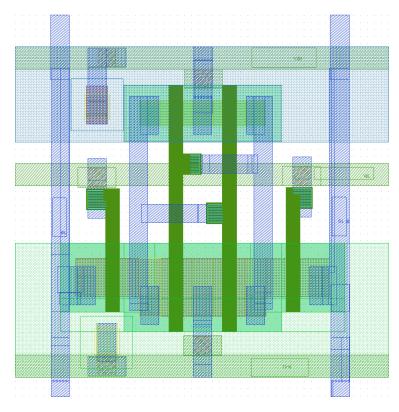

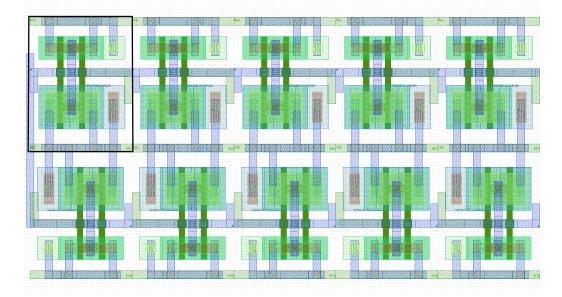

| 15 | Layout: 6T Cell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 23 |

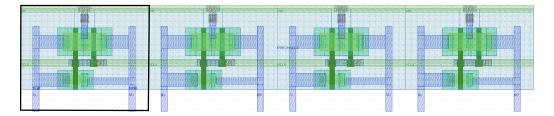

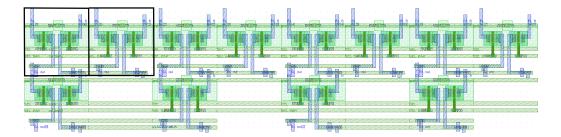

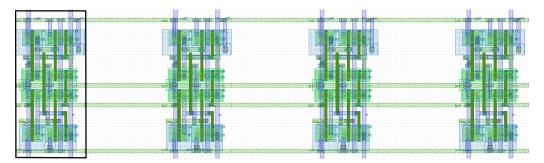

| 16 | Layout: Bitcell Array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 24 |

| 17 | Layout: Precharge Array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 24 |

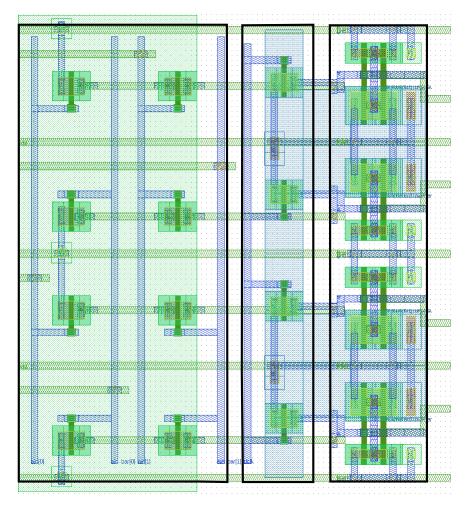

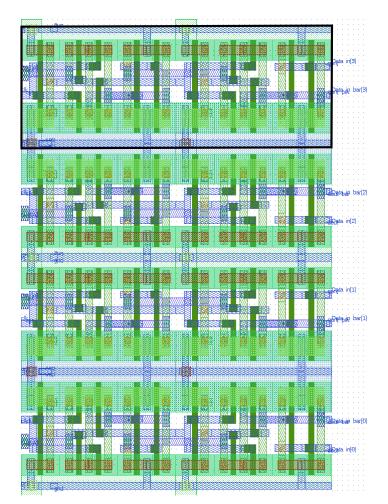

| 18 | Layout: NAND Decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 25 |

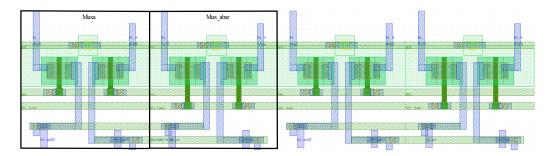

| 19 | Layout: Column Mux                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 26 |

| 20 | Layout: Column Mux, Depth=2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 26 |

| 21 | Layout: Sense Amp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 27 |

| 22 | Layout: Write Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 27 |

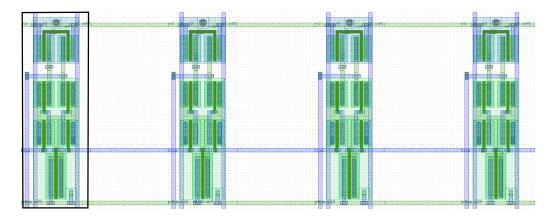

| 23 | Layout: Master-slave flip-flop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 28 |

| 24 | Layout: Control Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 29 |

| 25 | Layout: Delay Chain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 30 |

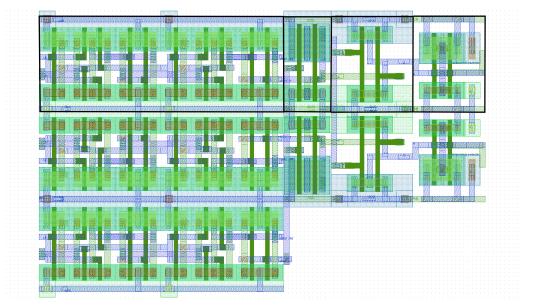

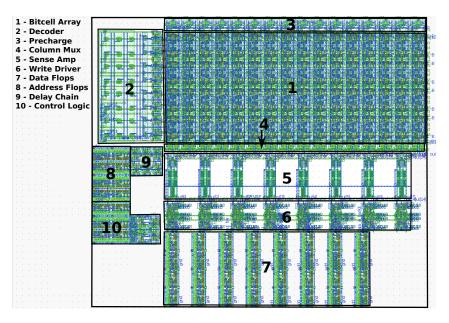

| 26 | Layout: SRAM 16x8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 31 |

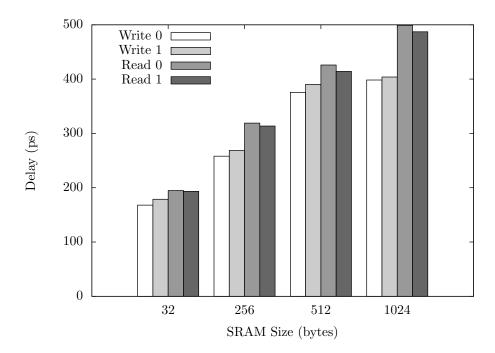

| 27 | Plot: Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 39 |

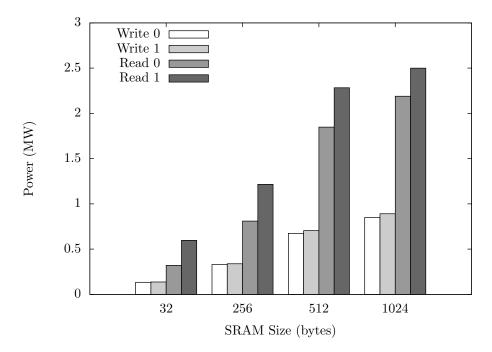

| 28 | Plot: Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 40 |

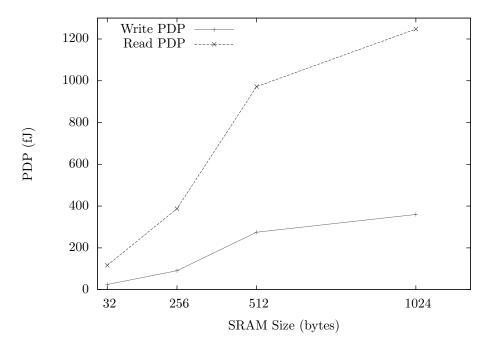

| 29 | Plot: PDP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 41 |

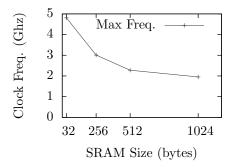

| 30 | Plot: Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 41 |

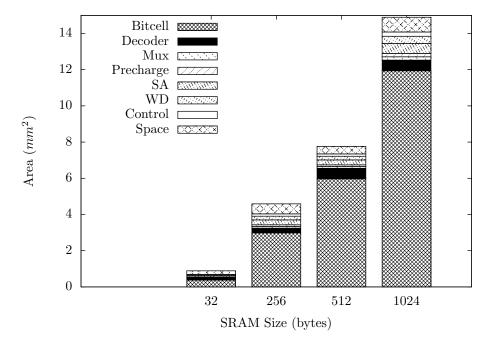

| 31 | Plot: Area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 42 |

# List of Tables

| 1 | Truth Table: NAND Decoder    | 7  |

|---|------------------------------|----|

| 2 | Truth Table: Column Mux      | 8  |

| 3 | Truth Table: Control Signals | 12 |

| 4 | Flip-flop Characterization   | 38 |

| 5 | SRAM Write Delay and Power   | 38 |

| 6 | SRAM Read Delay and Power    | 38 |

| 7 | Clock Period and Freq        | 38 |

| 8 | SRAM Area                    | 12 |

## Abstract

#### OpenRAM: An Open-Source Memory Compiler

by

#### Jeffrey T. Butera

In academia, many Application Specific Integrated Circuits and System-on-Chip design methodologies are limited by the availability of memories. As process technologies shrink, the size and number of memories on a chip are constantly increasing and memory designs become a more significant part of the overall system performance, efficiency, and cost. Random-Access Memories can be time consuming and tedious to custom design, and there are not many options for automating this process. Process design kits from foundries and vendors do not include memory compilers and commercial solutions require expensive licenses and are often un-modifiable and process specific. This thesis introduces OpenRAM, an open-source memory compiler and characterization methodology. The main objective of the OpenRAM compiler is to promote memory research in academia by providing a flexible and portable platform for generating and verifying memory designs across different technologies. Currently, the compiler generates GDSII layout and Spice netlists for single-port SRAM's using the FreePDK 45nm process design kit, and provides timing/power characterization through Spice simulation. Verification of OpenRAM designs in both 130nm (IBM 8RF) and 180nm (IBM 7SF) technologies are in progress. I would like to express my gratitude to Professor Matthew Guthaus for advising me throughout my graduate studies and driving the OpenRAM project. I would also like to thank the other members of the OpenRAM group: Bin Wu, James Stine, Brian Chen, Ping-Yao Li, and Manju Subbarayappa. OpenRAM is a group effort and my work would not have been completed without their valuable contributions.

I also extend my thanks to the members of the UC Santa Cruz VLSI Design and Automation Group (Rajsaktish Sankaranarayanan, Riadul Islam, Benjamin Lacara, and Hany Famy) for being a sounding board for ideas and insight.

Lastly, a special thanks to my parents for their support and encouragement throughout my academic endevours.

# 1 Introduction

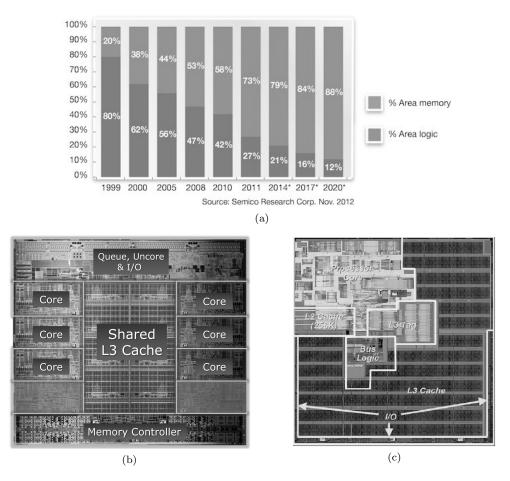

Static Random-Access Memory, or SRAM, has many applications and has become the standard for embedded memories in ASIC, SOC, and microprocessor designs. As process technologies shrink, the size and number of memories on a chip is constantly increasing and memory designs are becoming a significant part of overall system performance, efficiency, and cost. Currently, embedded memories can occupy up to 75% of the total chip area (Figures 1b and 1c). It has been reported that by 2020 the total memory area will increase closer to 90% for SOC's(Figure 1a). Consider the Itanium 2 processor with a 6MB on-die L3 cache from Intel (Figure 1c) as an example. This is a 10 year old processor, developed using a 130-nm technology, and the on-die memory dominates over 70% of the chip's area.

With current technologies pushing below the 20-nm mark, even larger and more dense memories are being placed on-chip. These newer, smaller technologies introduce very specific design challenges. The effects of variability, static power, stability, and supply noise margins are magnified as technologies shrink. Specific countermeasures must be taken to combat these effects, while still not significantly increasing the area, power, or speed of the SRAM. Consequently, SRAM's have become one of the most challenging and time consuming components to design in an integrated circuit.

One redeeming factor of the SRAM is that it can have a very regular structure consisting of cells that can be replicated many times across a single design. This promotes full custom design and encourages the use of automation techniques such as compilers to automate the design process.

Memory compilers are commonplace in industry. Two main flavors of memory compilers exist: third party compilers released with standard cell libraries by vendors, and proprietary compilers that are considered in-house intellectual property by companies. These compilers usually have the capability of generating single and dual port RAM's as well as ROM's (read only memories) and CAM's (content addressable memories). The main drawback with commercial compilers is that they require expensive licenses and may not allow customization or changes to source code. Examples of industry memory compilers are: Global Foundries' design kit[6], ARM's embedded IP memories[2], Synopsys DesignWare memory compiler[21], Dolphin Technology's memory IP[23], Faraday Technology's library and memory compiler[22].

Due to funding restrictions and customization limitations, commercial memory compilers are not a feasible solution for researchers in academia. Outside of commercial solutions,

Figure 1: a)Trend of memory and logic area for SOC's (Semico Research). b)Die photo of the Intel i7 Sandy Bridge[18]. c)Die photo of the Itanium 2 from Intel[17].

the only alternative is full-custom design. This makes it difficult and time consuming for researchers to prototype and verify new circuits and methodologies above the cell level. In order to correctly verify certain aspects of a design, such as scalability and robustness, memory designs should be considered at the system level. In attempt to combat these issues and provide a common infrastructure for memory research in academia, we introduce the OpenRAM memory compiler.

OpenRAM is an open-source memory compiler and characterization methodology. The main objectives of the compiler are: easy generation of memory arrays, being portable across many technologies and platforms, providing timing/power characterization of designs, being independent of commercial tools, and providing silicon verified designs. The OpenRAM project is funded by the National Science Foundation and is a collaboration between the VLSI Design and Automation group (run by Prof. Matthew Guthaus) at the University of California, Santa Cruz, and the VLSI Computer Architecture Research group (run by Prof. James Stine) at Oklahoma State University.

This thesis will provide an in depth discussion of the OpenRAM memory compiler, including its software implementation, features, and use. The thesis will also highlight the specific contributions of the author. These contributions include: the data structure hierarchy of the compiler, scripts to dynamically generate GDSII layouts and Spice netlists of the various blocks of the SRAM, a snap-to-grid function for the dynamic layouts, and the Spice memory characterizer.

The thesis is organized as follows. Section 2 provides a background of the SRAM architecture and operation. Section 3 discusses the implementation of the OpenRAM memory compiler and details its main features. Section 4 highlights the author's specific contributions to the project and provides preliminary results from the characterizer. Finally, Section 5 summarizes the OpenRAM memory compiler and discusses the future direction of the project.

# 2 Background

Before discussing the details of the OpenRAM memory compiler this section will give an overview of a typical SRAM architecture, its operation, and highlight several design challenges specifically associated with SRAM's.

## 2.1 SRAM Architecture

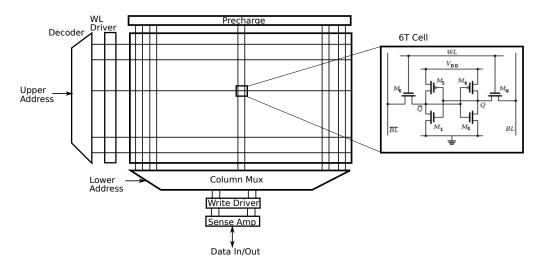

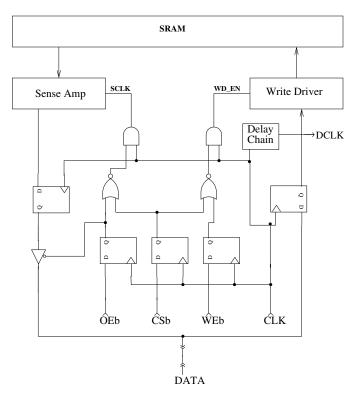

SRAM's typically consist of an array of memory cells with peripheral circuits and control logic. Figure 2 depicts the memory array (large block in the center) as well as the other main blocks: the address decoder, word line drivers, column multiplexer, precharge circuitry, write drivers, sense amplifier, and control logic. The following sub-sections explain the operation of each individual block within the SRAM, followed by a high level explanation as to how these different blocks interact to function as a memory device. It is important to note that the circuits described below are the ones that are used in the first release of the OpenRAM memory compiler. By no means is this an exhaustive list of the possible circuits that can be adapted into a SRAM architecture.

Figure 2: Single Port SRAM Architecture

#### 2.1.1 The 6T Cell and Memory Array

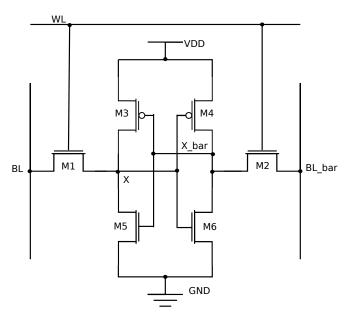

The 6T cell is the most commonly used memory cell in SRAM devices. It is named "6T cell" because it consists of six transistors: two access transistors (M1 and M2) and two cross coupled inverters as shown in Figure 3. The cross coupled inverters hold a data bit, X, and its inverted value, X\_bar. This bit can either be written into or read from the cell by the bit lines. The access transistors are used to isolate the cell from the bit lines so that data is not corrupted while a cell is idle.

Figure 3: Schematic of 6T cell.

The 6T cell can be accessed to perform the two main operations associated with memory: reading and writing. When a read is to be performed, both bit lines are precharged to Vdd.

This precharging is done during the first half of the read cycle and is handled by the precharge circuitry (see Section 2.1.2). In the second half of the read cycle the word line is asserted, which enables the access transistors. If a 1 is stored in the cell then BL\_bar is discharged to Gnd, and BL is pulled up to Vdd. Conversely, if a 0 is stored, then BL is discharged to Gnd and BL\_bar is pulled up to Vdd. While performing a write operation, both bit lines are also precharged to Vdd during the first half of the write cycle. Again, the world line is asserted, and the access transistors are enabled. The value that is to be written into the cell is applied to BL, and its complement is applied to BL\_bar. The drivers that are applying the signals to the bit lines must be appropriately sized so that the previous value in the cell can be overwritten (see Section 2.1.6).

The transistors in the cell must be carefully sized to ensure reliable operation. For a read operation, the M5 and M6 must be sized larger than access transistors M1 and M2. This is necessary because when the word line is asserted, both X and X\_bar are initially pulled up to the precharge value. Assuming that a 1 is stored at X, X\_bar must remain 0 regardless of the voltage rise experienced when the word line is asserted. In order to prevent the value in the cell from flipping, the resistance of the access transistors must be larger than that of M5 and M6. During a write operation, the value stored in the cell is being overwritten. This means that M1 and M2 must be strong enough to overpower the feedback inverter and must be sized larger than M3 and M4[5],[13].