## **UC Berkeley**

## **UC Berkeley Electronic Theses and Dissertations**

#### **Title**

Expanding the Scalability and Applications of III-V Optoelectronic Devices by Evolution of Thin-Film Vapor-Liquid-Solid Growth

#### **Permalink**

https://escholarship.org/uc/item/30q6w0wk

#### **Author**

Hettick, Mark James

#### **Publication Date**

2018

Peer reviewed|Thesis/dissertation

# Expanding the Scalability and Applications of III-V Optoelectronic Devices by Evolution of Thin-Film Vapor-Liquid-Solid Growth

$\mathbf{B}\mathbf{y}$

Mark James Hettick

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

**Graduate Division**

of the

University of California, Berkeley

Committee in charge:

Professor Ali Javey, Chair

Professor Ming C. Wu

Professor Daryl C. Chrzan

Fall 2018

# Expanding the Scalability and Applications of III-V Optoelectronic Devices by Evolution of Thin-Film Vapor-Liquid-Solid Growth

Copyright © 2018, by the authors. All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Abstract

Expanding the Scalability and Applications of III-V Optoelectronic Devices by

Evolution of Thin-Film Vapor-Liquid-Solid Growth

By

#### Mark James Hettick

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Ali Javey, Chair

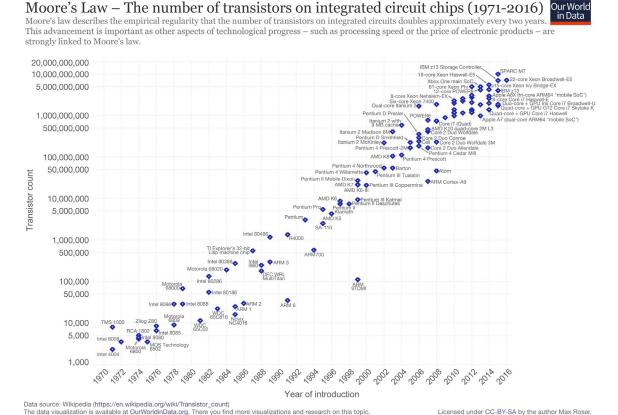

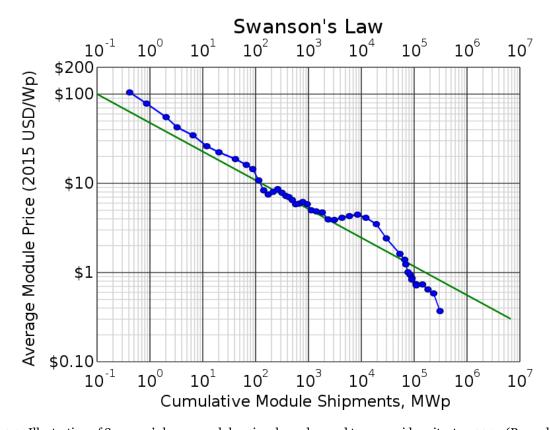

Two significant drivers to innovation in electronics and electronic materials in recent history have been electronic device scaling and the pursuit of high efficiency photovoltaic cells at low costs. The motivations of these two fields have been interestingly parallel, as "density" has been a key metric for both – areal energy density in the case of photovoltaics, and component density in the case of electronic devices. So strong is this motivation to lower device costs by packing more performance into a smaller area that "laws" have been devised to inspire innovation in each field, with Moore's law to describe the periodic doubling of transistor density and Swanson's law to outline the steady drop in solar cell module costs over time. As each law approaches a wall erected by fundamental physical limitations, science must identify roadblocks and solutions that can allow innovation to continue.

Semiconductor materials are a key limiting factor for each application, as their physical properties determine ultimate functionality of a device and the challenges involved in device design. In both electronic and optoelectronic applications, scalable manufacturing of III-V materials has been a promising avenue to improvement, as while they are traditionally expensive to produce, they use a larger portion of the solar spectrum for photovoltaic devices, and are easily utilized in the fabrication of high performance optical and electronic devices. In recent years, a more scalable method for the growth of III-V materials without costly epitaxial substrates has been developed, by utilizing the vaporliquid-solid growth (VLS) process to grow structures confined by a metal catalyst. Structures such has nanowires have been fabricated with this technique and studied extensively, but a recent expansion of the approach has also allowed for growth of highquality thin films using planar templates for nucleation control. In this dissertation, I discuss the use of this approach in a number of applications, including the development of large-area photovoltaic devices and an evolution of the technique to greatly expand its application space through lower process temperatures.

First, I will discuss an ideal preliminary application of this technique, with the development of p-body InP photoelectrochemical cells for the direct production of chemical fuel using sunlight. This application shows the utility of large-scale polycrystalline growth with larger than normal grain sizes enabled by the technique, and the fundamentals of the growth process and usable doping methods are explored in tandem. This study also demonstrates the successful application of an efficient selective electron contact to the poly-InP system, enabling promising device performance and enhancing device stability under harsh photocathode operation conditions. Hydrogen fuel production from simulated sunlight is also directly and quantifiably observed from the device as a capstone to this experiment.

Following the investigation of larger area thin-film growth, the microscale templated-liquid-phase (TLP) crystal growth method is explored and expanded to target a wider range of applications. This method, a modification to the thin-film vapor-liquid solid (TF-VLS) process initially studied, has previously enabled growth of defined patterns of single crystal domains on amorphous substrates. While this is an impressive result with great promise for integration of III-Vs into highly scaled electronics, growth temperatures previously explored would need to be lowered significantly for facile integration to be a reality. Using a simple modification to the existing TLP process, I demonstrate growth temperatures well within the silicon CMOS thermal budget, with proof-of-concept devices fabricated at temperatures as low as 270°C with the InP system. With applicability to a variety of substrates, this study has neatly expanded the application space of III-Vs, with complex methods and material requirements replaced with simple direct growth.

To Ashley

#### Acknowledgements

First, I would like to thank Prof. Ali Javey, for his mentorship, training, and support during my studies over the many years I have been part of this group. Since starting as an undergraduate in this lab, I have been able to learn so much about not only the typical experimental skills required of a researcher but also many skills in management and mentorship, which would not have been possible without his trust and guidance.

I would also like to thank my qualifying exam and dissertation committees, including Prof. Ming Wu, Prof. Daryl Chrzan, and Prof. Joel Ager. Their feedback and contributions during and after the exam were very helpful for the shaping of my project, and in particular Prof. Chrzan has provided great insight on the growth process theory and fundamentals integral to my work. Prof. Ager also played a critical role in my studies of photoelectrochemical systems, and was a great mentor as well during my initial years as an undergraduate and junior grad student. Prof. Wu also facilitated a great teaching experience while I served as his head graduate student instructor, and I really appreciate his advice, feedback, and help during the course of that class.

Lastly, I would like to also thank the many Javey lab colleagues and mentors that have helped me develop my project and skills working alongside them. In particular, Maxwell Zheng and Prof. Rehan Kapadia were amazing starting mentors and friends, and Dr. Yongjing Lin and Prof. Daisuke Kiriya were also instrumental in gaining early knowledge of chemistry that has become a critical part of my work. Kevin Chen, Prof. Kapadia, and Max also helped me a lot in understanding the VLS growth process early on, and that knowledge has been critical for the success of my projects. Dr. Corsin Battaglia, Dr. Carolin Sutter-Fella, and Prof. James Bullock were great colleagues and friends, and very helpful in their deep knowledge of PV topics and related fundamental science. In the final year of my PhD, Hao Li has been a great colleague to work with, and has helped me a lot in getting my projects where I wanted them to go.

There are many other coworkers and friends that have helped with experiments, discussions, and support, including Thomas, Sujay, Peter, Fahad, Matin, Niharika, Alison, Hansen, and many others too numerous to list – grad school is clearly a team effort for everyone, and I hope everyone I worked with continues to do well in the future.

## TABLE OF CONTENTS

| CHA | APTE | R 1: INTRODUCTION1                                                    |

|-----|------|-----------------------------------------------------------------------|

|     | 1.1  | Material limitations in near-future electronics and photovoltaics     |

|     | 1.2  | III-V materials: Optical and electronic applications 3                |

|     | 1.3  | State of the art in III-V growth for heterogeneous integration 4      |

|     | 1.4  | Thin-Film Vapor-Liquid-Solid (TF-VLS) Growth Techniques: Our approach |

|     |      | R 2: SCALABLE INP PHOTOCATHODES BY TF-VLS                             |

|     | 2.1  | III-V photovoltaics and photocathodes: Introduction                   |

|     | 2.2  | Growth, p-doping, and device structure of TF-VLS InP photocathodes11  |

|     | 2.3  | Structural and optoelectronic characterization of TF-VLS InP films15  |

|     | 2.4  | Electronic characterization of poly-InP photocathode devices . 18     |

|     | 2.5  | Poly-InP Solar Fuel Production: Conclusions and Outlook20             |

|     | 2.6  | Experimental and Theoretical Methods23                                |

|     |      | R 3: DIRECT TEMPLATED LIQUID PHASE GROWTH I QUALITY INP BELOW 300°C29 |

|     | 3.1  | Heterogeneous III-V integration: Introduction29                       |

|     | 3.2  | Low-T Templated Liquid Phase Crystal Growth of InP below 300°C30      |

|     | 3.3  | Nucleation and growth behavior of Low-T TLP InP31                     |

|     | 3.4   | Optoelectronic Characterization of Low-T TLP InP         | 32   |

|-----|-------|----------------------------------------------------------|------|

|     | 3.5   | Transient electroluminescence from InP grown below 300°C | 33   |

|     | 3.6   | Hall Mobility of Low-T TLP InP                           | 35   |

|     | 3.7   | Low-T TLP InP Transistors                                | 36   |

|     | 3.8   | Conclusion                                               | 37   |

|     | 3.9   | Experimental Methods                                     | 38   |

| CH  | APTE  | ER 4: CONCLUSIONS AND FUTURE PROSPECTS                   | . 42 |

| BIB | SLIOC | GRAPHY                                                   | . 44 |

|     |       | DIX A: SUPPLEMENTARY DATA & NOTES FOR<br>ER 3            | . 50 |

|     |       | DIX B: TF-VLS SUBSTRATE AND GROWTH LEMENTS               | . 62 |

|     |       | DIX C: PATHWAYS TO IMPROVEMENT OF TF-VLS P GROWTH        | . 65 |

## CHAPTER 1

## INTRODUCTION

## 1.1 Material limitations in near-future electronics and photovoltaics

Many of the devices we rely on today were based on the innovative driving force of a straightforward observation made more than 50 years ago. Gordon Moore's observation, that integrated circuit component density was continuously doubling every year (Figure 1-1), has encouraged the semiconductor industry to match and exceed this prediction as far as physically possible.¹ While silicon-based devices have been directly scaled to metal half pitches less than 14nm,² limitations such as direct source-drain tunneling and metal line breakdown could lead to a stall in planar scaling as early as 2021. To avoid this barrier, there are a number of different strategies for expanding transistor density and performance into the future, including 3D integration³ methods that seek to increase density by stacking and III-V on silicon processes⁴ that seek to increase performance directly by improving the channel material's carrier transport properties. In particular,

**Figure 1-1.** Transistor count on integrated circuits from 1970 to 2016. (Reproduced from plot and data in https://ourworldindata.org/technological-progress)<sup>5</sup>

III-V on silicon processes have additional advantages due to the increasing prevalence of photonic circuit applications.<sup>6</sup> However, the critical roadblock is the co-integration of silicon and III-V materials, which traditionally require complex graded heteroepitaxy or an additional transfer step to realize a III-V active layer.

With inspiration from Moore's law, other industries have targeted similar motivational trends to define a "learning curve" for their respective technological trends. One such trend which has broad impact on the world we live in is the learning curve of photovoltaic (PV) adoption, which emulated Moore's law both in form and in nomenclature. "Swanson's law," which tracks the average module price as more panels are shipped, follows a somewhat more modest 20% per year price decline. This curve (Figure 1-2) illustrates the maturation of photovoltaics, both in terms of business volume and the implicit improvement of cell efficiency, which has also been increasing steadily over time as a result of such competitive trends. However, similarly to Moore's law, cost pressures and increasing module efficiencies have pushed manufacturers to more complex designs and manufacturing methods,8 and silicon solar cells are rapidly approaching the Schockley-Quiesser limit in practical device configurations.9 Because of this, many researchers and some companies have been looking to alternative materials systems for photovoltaics, including the ideally positioned III-V materials as alternatives and tandem candidates. However, similar impediments to progress exist for broad adoption due to strict cost constraints in PV markets that have made epitaxial strategies undesirable.

**Figure 1-2.** Illustration of Swanson's law as module prices have dropped to near grid parity, to ~2015. (Reproduced from <a href="https://en.wikipedia.org/wiki/Swanson%278">https://en.wikipedia.org/wiki/Swanson%278</a> law, Data from ITRPV Edition 2017 Presentation.) $^8$

## 1.2 III-V materials: Optical and electronic applications

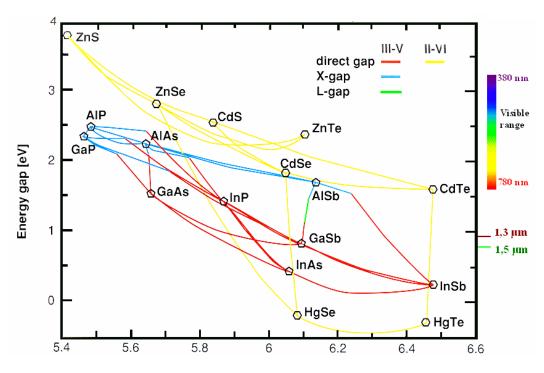

With integration issues in mind, we can look to a few additional properties and applications of III-V materials to motivate a solution and explain some of the specific physical challenges we face. Figure 1-3 displays a map of material gap vs. lattice constant for a variety of compound semiconductors, with tie lines to indicate bandgap modification with ternary compositions. This plot neatly explains both the advantages and disadvantages of III-Vs, as their ternary compounds have a wide tunable range of emission and absorption energies but require epitaxial substrates and processes to accommodate lattice differences. An example of this conundrum is the case of tandem solar cells, by which efficiencies above the single junction limit can be achieved using multiple absorbers to target the various parts of the solar spectrum. For silicon solar cells, an evolution of the limiting efficiency could be achieved with an ideally matched gap such as the 1.8 eV InGaP composition shown, but the lack of a scalable integration method between these materials has allowed only mechanical stacking methods to realize this combination.<sup>10</sup>

On-chip silicon photonics are another area of great interest in the pursuit of III-V on silicon integration. Near-IR semiconductors are prevalent in the III-V family as shown, but the silicon lattice constant of 5.43Å is difficult to match to these materials. Structures have been demonstrated with hybrid Si/III-V designs allowing wavelength tuning of on-chip lasers in the InP system,<sup>5</sup> but a multi-step process involving traditional epitaxial growth followed by wafer bonding is needed due to the lack of a direct integration method.

**Figure 1-3.** Energy gap of various III-V and II-VI semiconductors vs. lattice constant, with tie lines for bandgap of ternary compositions. (Reproduced from https://www.tf.uni-kiel.de/matwis/amat/semitech\_en/kap\_2/backbone/r2\_3\_1.html, Data from Tien 1988, Bell Laboratories.)

Finally, in the silicon complementary metal-oxide-semiconductor (CMOS) applications space, III-V materials have significant advantages in both planar and 3D cointegration. Due to their high mobilities<sup>4</sup> and the advent of photonic circuit applications<sup>11</sup> that would directly utilize on-chip optoelectronic devices, this is yet another area where simplified integration methods would be a key for future progress. One example is the integration of InAs transistors on silicon by layer transfer,<sup>12</sup> where field-effect mobilities in excess of 4000 cm<sup>2</sup>/V-s were realized. Direct growth of GaAs on Si has also been explored in the past,<sup>13</sup> but initial naïve approaches of direct metal-organic chemical-vapor-deposition (MOCVD) were limited by high pre-treatment and deposition process temperatures.

## 1.3 State of the art in III-V growth for heterogeneous integration

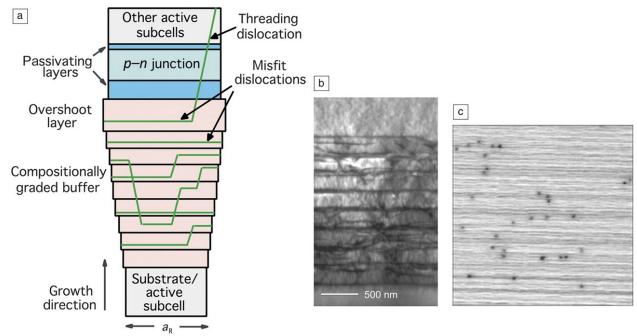

Significant effort has been placed on bonded devices for III-V on silicon photonics due to ease of stacking and component mating,<sup>11</sup> but many direct growth techniques have also been explored for accommodating the lattice mismatch between silicon and III-V materials to achieve metamorphic epitaxy. In metamorphic epitaxy, dislocations generated as lattice mismatches are accommodated and gradually graded away, and the initial dislocations are left behind well outside of the active device area.<sup>14</sup> In Figure 1-4, a graded buffer layer for a solar cell application is demonstrated, showing the possible path of dislocations in the schematic and in the transmission electron micrograph (TEM) of the real structure.

**Figure 1-4.** A graded buffer layer in schematic and TEM form displaying the accommodation of a  $Ga_{0.7}In_{0.3}As$  cell onto a nonepitaxial subcell substrate. (Reproduced from France et al. 2016, <sup>14</sup> Figure 3)

While graded buffers are an adequate strategy, they are necessarily wasteful, as many microns of growth can be necessary due to the relative ease of defect propagation.

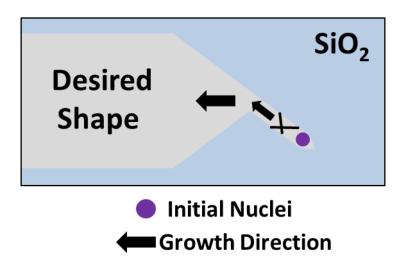

**Figure 1-5.** Schematic of aspect ratio trapping with a typical unseeded Bridgman ampoule-like design. Defect lines within the tip are cut off at the tip edges before leaving to affect the desired shape.

Aspect ratio trapping, similar to classical applications of unseeded Bridgman growth,<sup>15</sup> allows for circuitous dislocation lines to terminate at an edge within a defined pattern (Figure 1-5), greatly decreasing the distance over which a defect can propagate and cause problems in an active structure.<sup>16</sup> Through characterization of defect spacing and careful trapping structure design, traditional methods such as MOCVD can generate high quality structures within these templates, but due to high dislocation densities at typical process temperatures lateral dimensions can still be limited, and access to the base substrate is still needed. Epitaxial layer overgrowth<sup>17</sup> and rapid melt growth<sup>18,19</sup> have shown some success in high quality thin films with a similar base template idea, though neither are universally applicable, and the latter method results in some material degradation due to a decline in stoichiometry over the course of the process.

## 1.4 Thin-Film Vapor-Liquid-Solid (TF-VLS) Growth Techniques: Our approach

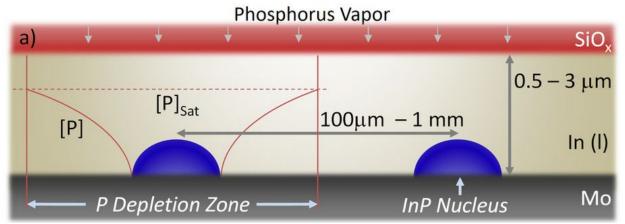

Due to the significant void in viable thin-film processes for direct III-V growth for integration into promising applications, the advent of a scalable method with reduced complexity would open up a new space for rapid innovation. In recent years, one such technique has emerged, with inspiration from the popular vapor-liquid-solid nanowire growth method. Vapor-liquid-solid nanowire growth processes utilize precipitation of precursors dissolved from the vapor phase into a liquid catalyst to grow wires in a nanoscale template defined by the catalyst area, and can be used to grow a wide variety of group IV and III-V semiconductors.<sup>20</sup> By modification to the template portion of this technique, the thin-film vapor-liquid solid method allows both large scale and locally defined thin-film growth by using liquid metals confined by oxide "capping" layers, with a patternable nucleation promoter to encourage preferential growth in specific substrate areas.<sup>21,22</sup> Importantly, the control of precursor flux through the same confinement layer also allows for fine control of nucleation density, leading to large grain sizes in thin films compared to the target film thickness (Figure 1-6).

**Figure 1-6.** Schematic representation of the TF-VLS growth mode, displaying control of nucleation density by phosphorus depletion zones that form around each nucleus. (Reproduced from Kapadia et al. 2013<sup>21</sup>)

The mechanism for nucleation control offered by this method is visualized in Figure 1-6 for the InP system. As it forms, each nucleus reduces the local phosphorus concentration as it accumulates more for growth, and in some area around the nucleus the diffusion gradient reduces the phosphorus concentration below the supersaturation concentration that is required for another nucleus to form.

This mechanism was carried even further in the development of templated liquid phase (TLP) growth, where only one nucleus is allowed to form in a feature by virtue of its defined nucleation and precursor area.<sup>23</sup> In this method, single crystal domains of III-V materials have been grown on amorphous substrates by simple nucleation layer and metal precursor patterning. In this way, the III-V process void for both large area and microscale electronic and optoelectronic applications can be filled, but further development and adaptation of the technique to specific applications is needed to pinpoint its utility in each space.

With this motivation in mind, in the rest of this report I seek to carry the reader through two unique applications and evolutions of the TF-VLS process. Chapter 2 will first show the direct application of TF-VLS growth to efficient non-epitaxial photocathode cells fabricated by scalable methods. Chapter 3 will then present a development of the technique that widely expands its application space, allowing us to conclude with a bright vision of the future of III-V applications without epitaxial substrates.

#### REFERENCES FOR CHAPTER 1

- 1. Schaller, R. R. & R., R. Moore's law: past, present and future. *IEEE Spectr.* **34,** 52–59 (1997).

- 2. Waldrop, M. M. More than Moore. *Nature* (2016). doi:10.1038/530144a

- 3. Wong, S. et al. Monolithic 3D integrated circuits. in *International Symposium on VLSI Technology, Systems, and Applications, Proceedings* 1–4 (IEEE, 2007). doi:10.1109/VTSA.2007.378923

- 4. del Alamo, J. A. Nanometre-scale electronics with III–V compound semiconductors. *Nature* **479**, 317–323 (2011).

- 5. Max Roser and Hannah Ritchie. Technological Progress. *OurWorldInData.org* (2018). Available at: https://ourworldindata.org/technological-progress. (Accessed: 18th November 2018)

- 6. Guang-Hua Duan *et al.* Hybrid III--V on Silicon Lasers for Photonic Integrated Circuits on Silicon. *IEEE J. Sel. Top. Quantum Electron.* **20**, 158–170 (2014).

- 7. Swanson, R. M. A vision for crystalline silicon photovoltaics. *Prog. Photovoltaics Res. Appl.* **14**, 443–453 (2006).

- 8. International Technology Roadmap for Photovoltaic (ITRPV) Results 2017, Ninth Edition, September 2018.

- 9. Green, M. A. & Bremner, S. P. Energy conversion approaches and materials for high-efficiency photovoltaics. *Nat. Mater.* **16**, 23–34 (2017).

- 10. Essig, S. *et al.* Progress Towards a 30% Efficient GaInP/Si Tandem Solar Cell. *Energy Procedia* 77, 464–469 (2015).

- 11. Roelkens, G. *et al.* III-V/silicon photonics for on-chip and intra-chip optical interconnects. *Laser Photon. Rev.* **4,** 751–779 (2010).

- 12. Ko, H. *et al.* Ultrathin compound semiconductor on insulator layers for high-performance nanoscale transistors. *Nature* **468**, 286–289 (2010).

- 13. Akiyama, M., Kawarada, Y. & Kaminishi, K. Growth of Single Domain GaAs Layer on (100)-Oriented Si Substrate by MOCVD. *Jpn. J. Appl. Phys.* **23**, L843–L845 (1984).

- 14. France, R. M., Dimroth, F., Grassman, T. J. & King, R. R. Metamorphic epitaxy for multijunction solar cells. *MRS Bull.* **41**, 202–209 (2016)., J. G. *et al*.

- 15. Sundaram, S. K. *et al.* Electron backscatter diffraction analysis of a CZT growth tip from a vertical gradient freeze furnace. *J. Cryst. Growth* **329**, 12–19 (2011).

- 16. Fiorenza, J. G. *et al.* (Invited) Aspect Ratio Trapping: A Unique Technology for Integrating Ge and III-Vs with Silicon CMOS. in *ECS Transactions* **33**, 963–976 (The Electrochemical Society, 2010).

- 17. Nam, O.-H., Bremser, M. D., Zheleva, T. S. & Davis, R. F. Lateral epitaxy of low defect density GaN layers via organometallic vapor phase epitaxy. *Appl. Phys. Lett.* **71**, 2638 (1998).

- 18. Feng, J. et al. P-channel germanium FinFET based on rapid melt growth. *IEEE Electron Device Lett.* **28**, 637–639 (2007).

- 19. Shu-Lu Chen, Griffin, P. B. & Plummer, J. D. Single-Crystal GaAs and GaSb on Insulator on Bulk Si Substrates Based on Rapid Melt Growth. *IEEE Electron Device Lett.* **31**, 597–599 (2010).

- 20. Duan, X. & Lieber, C. M. General Synthesis of Compound Semiconductor Nanowires. *Adv. Mater.* **12**, 298–302 (2000).

- 21. Kapadia, R. *et al.* A direct thin-film path towards low-cost large-area III-V photovoltaics. *Sci. Rep.* **3**, 2275 (2013).

- 22. Kapadia, R. *et al.* Deterministic nucleation of InP on metal foils with the thin-film vapor-liquid-solid growth mode. *Chem. Mater.* **26**, 1340–1344 (2014).

- 23. Chen, K. *et al.* Direct growth of single-crystalline III-V semiconductors on amorphous substrates. *Nat. Commun.* **7**, 10502 (2016).

### CHAPTER 2

## SCALABLE INP PHOTOCATHODES BY TF-VLS GROWTH

## 2.1 III-V photovoltaics and photocathodes: Introduction

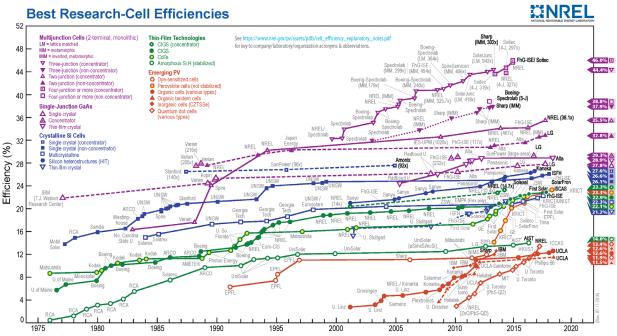

In the realm of clean energy, photovoltaic devices are king, due to the large amount of mostly unharnessed energy density¹ in sunlight that could easily provide abundant free energy reserves to the world. In particular among photovoltaic devices, though silicon dominates the filed due to continuously dropping cell and module costs, III-V compound semiconductors are among the most promising candidates for future solar cells because of their primarily direct band gaps with a wide range of tunable energies. The high quality and tunability of this materials system has allowed III-V cells to consistently hold both the single- and multi-junction efficiency records (Figure 2i), in both thin-film and bulk crystal forms. However, the aforementioned difficulties with III-V process and material integration have inhibited widespread adoption of these technologies, as the highest efficiency devices displayed all rely on complex multijunction growth and strategies to lower costs of epitaxial substrates. As a result, the TF-VLS process is uniquely suited to address this problem, as in the large area format any suitable material from the chart could be chosen to design a more scalable thin-film III-V PV structure, enabling higher limiting efficiencies in future cells and a continued downward trend in PV energy costs.

**Figure 2i.** Research cell efficiency chart from the National Renewable Energy Laboratory (NREL), additional explanatory notes at https://www.nrel.gov/pv/assets/pdfs/cell\_efficiency\_explanatory\_notes.pdf.

This chapter has been published in a similar form, and is reprinted and adapted with permission from Hettick et al. Journal of Physical Chemistry Letters, 6, 2177-2182, 2015. Copyright 2015 American Chemical Society.

Among PV applications, the generation of storable fuel from sunlight in the manner of photosynthesis is a particularly promising solution to the clean energy problem, and the prospect of highly efficient photoelectrochemical (PEC) cells is an attractive route to generation of solar fuels<sup>1,2,3</sup>. Due to the 1.23 eV free energy required for the water splitting process, in addition to the overpotentials generated at each electrode under operation, work on the tandem cell architecture with a particular focus on producing high voltage half cells is desirable to meet this requirement while maintaining adequate absorption across the solar spectrum.<sup>4</sup> For the H<sub>2</sub> producing photocathode half-cell, a variety of semiconductors have been explored, including planar,<sup>5,6,7</sup> micro-<sup>8</sup>, and nano-structured<sup>9</sup> crystalline Si, amorphous Si,<sup>10</sup> InP,<sup>11-17</sup> WSe<sub>2</sub><sup>18</sup>, TiO<sub>2</sub> coated Cu<sub>2</sub>O,<sup>19,20</sup> and CdS-modified *p*-CuGaSe<sub>2</sub>.<sup>21</sup>

In particular, p-type InP stands out for its direct bandgap of ~1.35 eV, suitable conduction band position in relation to the proton reduction potential, and associated high efficiency for the hydrogen evolution reaction. 12-16 In fact, nanostructured crystalline InP wafers have achieved a half-cell solar-to-hydrogen (STH) efficiency of approximately 14%, 12 which is the highest reported to date. In addition, other work on TiO<sub>2</sub> passivated crystalline InP wafers resulted in half-cells with an onset potential greater than 800 mV, providing some of the high voltage necessary for unassisted water splitting in the ideal tandem cell configuration.<sup>13</sup> Still, despite its high efficiency, prior work on InP as a PEC photocathode material has primarily focused on single crystal wafers, which limits largescale application due to the high cost of the bulk substrates. In this work we explore a more practical approach, utilizing a new high quality thin-film InP growth method<sup>22</sup> on low-cost Mo substrates along with previously explored protection schemes<sup>7,10,12,13</sup> to establish a low-cost and high efficiency PEC system. The system, the first solar device structure implemented using the TF-VLS growth method, exhibits decreased overall material usage, high performance, and potential expansion to device structures requiring fine nucleation and growth control.<sup>22,23</sup> Material and device quality is evaluated using imaging, photoluminescence and Mott-Schottky capacitance-voltage (PL), measurements, and performance of our photocathodes is evaluated through current voltage (J-V) measurements, to be compared with previous photocathode reports.

## 2.2 Growth, p-doping, and device structure of TF-VLS InP photocathodes

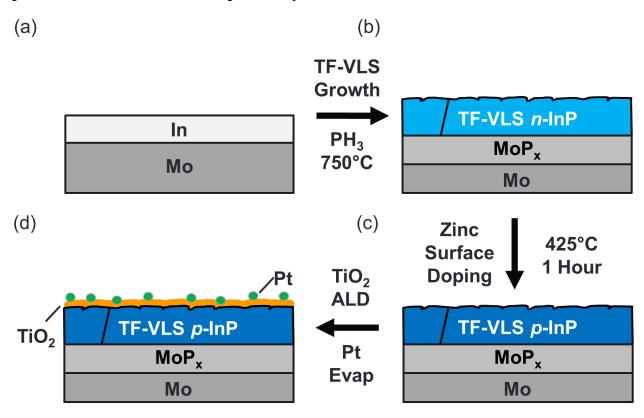

A full process scheme for our photocathodes is visualized in Figure 2-1. The TF-VLS growth method is chosen as it produces films with high optical and crystal quality with theoretical performance approaching that of the bulk crystal in terms of the luminescence efficiency and optically implied open-circuit voltage. Priefly, the TF-VLS growth method begins with an indium film approximately 2 micron in thickness deposited on a molybdenum substrate, capped by a thin silicon oxide (SiO<sub>x</sub>) layer (details in Methods). This stack is heated in hydrogen past the film's melting point, followed by the introduction of PH<sub>3</sub> gas for phosphorization of the liquid indium by a vapor-liquid-solid growth mode. Importantly, the SiO<sub>x</sub> layer confines the indium during growth to a planar thin-film geometry, allowing growth to proceed only in the lateral direction and reducing loss of the metal source to evaporation. The resulting InP is poly-crystalline with a thickness of 2 to 3  $\mu$ m (determined by the evaporated indium thin film thickness) and a lateral grain size of up to 1 mm.<sup>22,23</sup> This ultra-large grain size produces high optoelectronic performance as demonstrated previously.<sup>22</sup>

**Figure 2-1.** The fabrication process for TF-VLS InP PEC devices. (a) Indium metal is evaporated on the substrate using an electron beam evaporator. (b) An n-type (unintentionally doped) polycrystalline InP film is grown on the Mo substrate through a TF-VLS process. (c) The n-type film is p-doped by surface diffusion using a  $Zn_3P_2$  solid source. (d) A TiO $_2$  protection layer is grown by ALD on the top surface of the InP and a Pt co-catalyst is evaporated onto the surface of the TiO $_2$  to finish the device fabrication.

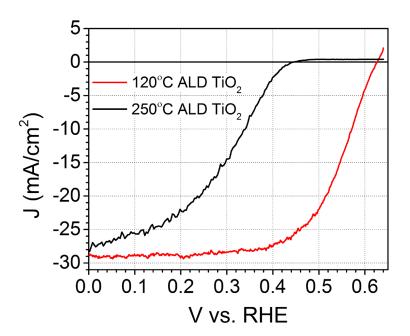

To produce *p*-type InP for use as a photocathode, an *ex-situ* surface diffusion doping process was carried out at a sample temperature of 425°C using zinc phosphide (Zn<sub>3</sub>P<sub>2</sub>) as the precursor (see Methods for details). Zn was chosen as the dopant since it is a commonly used acceptor in InP with a low activation energy.<sup>24</sup> Notably, the Zn<sub>3</sub>P<sub>2</sub> source was chosen to prevent InP decomposition by providing a phosphorus ambient present during the doping period. A 30 nm thick *n*-TiO<sub>2</sub> protection layer was then deposited by ALD at 120 °C to protect the surface from corrosion during PEC measurements.<sup>12</sup> Our previous studies<sup>13,25</sup> have shown that this *n*-TiO<sub>2</sub> layer on InP also provides a favorable surface energy band bending, allowing for transport of electrons while reflecting the holes due to the large barrier height at the InP/TiO<sub>2</sub> interface. Thus, higher V<sub>OC</sub> was observed previously for TiO<sub>2</sub> coated InP PV and PEC devices.<sup>13,25</sup> The temperature of TiO<sub>2</sub> deposition was optimized for device performance, as pictured in the J-V comparison shown in Figure 2-S1. Finally, Pt was used as an efficient catalyst material for water reduction. Throughout, growth and processing choices were influenced not only by the goal of cost reduction but also by stability and efficiency.

**Figure 2-S1.** J-V performance of TF-VLS InP PEC devices, comparing the performance for TiO<sub>2</sub> ALD deposition temperatures of 120°C and 250°C under AM1.5 illumination. J-V test performed in 1M HClO<sub>4</sub>.

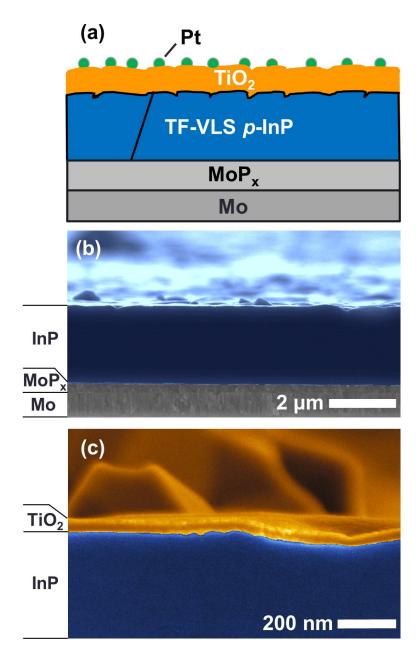

**Figure 2-2.** (a) Schematic of the typical device stack. (b) False-colored cross-section SEM image of the as-grown InP film. (c) High magnification SEM image (false-colored) of the TiO<sub>2</sub>-InP interface after TiO<sub>2</sub> deposition by ALD.

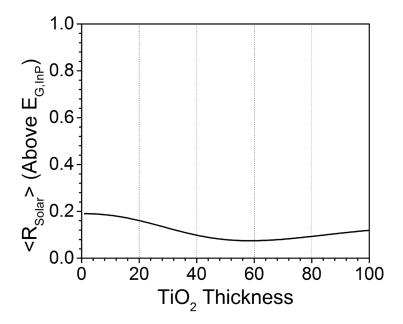

Morphological characterization of completed photocathodes is given by SEM images of a representative cross section in Figures 2-2b-c. Note that as reported in our previous studies, each grain extends vertically from the Mo substrate to the top-surface with a surface roughness defined primarily by the confinement of indium metal under the SiO<sub>2</sub> cap, as demonstrated by the limited protrusions extending above large, high quality grains shown in Figure 2-2b.<sup>22</sup> The 30 nm thick, highly uniform and conformal TiO<sub>2</sub> layer depicted is designed to not only improve the protective qualities over the TF-VLS InP, but also to act as an anti-reflective coating, improving the solar-weighted reflectance of the stack as compared to thinner coatings (Figure 2-S2). This structural and electrically

functional anti-reflection coating is particularly important in a PEC cell since conventional multilayer anti-reflective coatings may not be possible due to the intimate semiconductor-solution contact necessary for charge transfer. It has also been shown previously that TiO<sub>2</sub> thickness does not significantly impact charge transfer through the film, so this design choice does not impact the electrical performance of our devices.<sup>10,25</sup> Further optimization of the reflectance properties is possible with thicker TiO<sub>2</sub> films, and sputtering of TiO<sub>2</sub> as a protection layer and electron contact has been explored and implemented at much greater thicknesses in other photocathode systems.<sup>10</sup> In the future, the electronic benefits and chemical stability shown in ALD TiO<sub>2</sub> films could be combined with the increased throughput and lower cost of sputtering processes to yield optimal electronic, chemical passivation, and optical properties for photocathode cells.

**Figure 2-S2.** Calculated average solar reflectance above the InP bandgap as a function of  $TiO_2$  thickness, defined as the weighted average of reflectance with the normalized AM1.5 solar spectrum as a weighting parameter.

## 2.3 Structural and optoelectronic characterization of TF-VLS InP films

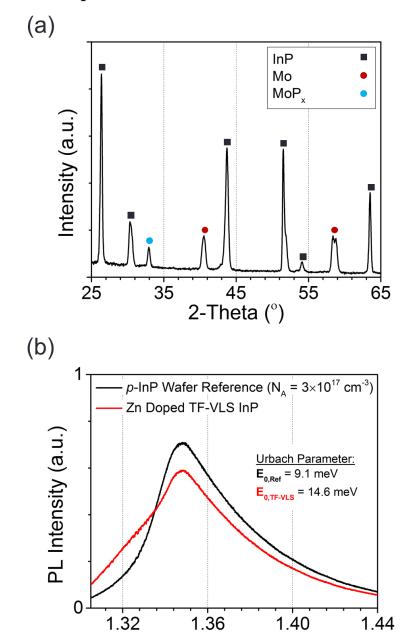

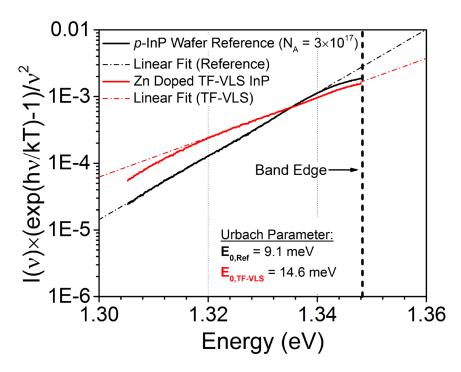

**Figure 2-3.** Physical and optical characterization of as-grown TF-VLS InP material and processed devices. (a) X-ray diffraction data of as-grown material, indicating high crystallinity with narrow peaks closely matching a zinc blende powder reference. Peaks attributed to the growth substrate are also visible, here denoted as Mo and Mo<sub>1-x</sub>P<sub>x</sub> (0.5 < x < 0.8) according to a powder reference. (b) Steady-state micro-PL measurements, indicating similarity of intensity and shape to a p-type crystalline reference. Extracted Urbach tail parameter E<sub>0</sub> fitted from extracted absorbance (Experimental and T, Figure 2-S3) is also reported for both the single crystalline wafer reference and our p-type TF-VLS film.

Energy (eV)

The intrinsic optoelectronic and structural qualities of the material used in these PEC cells are also quite important, and these parameters were explored by steady state microphotoluminescence (PL) and X-ray diffraction (XRD) measurements (Figure 2-3). XRD measurements (Figure 2-3a) indicate a high level of crystallinity of as-grown films, with peak positions closely matching a zincblende powder reference, <sup>29</sup> and with other peaks attributed to the MoP<sub>x</sub>/Mo substrate. <sup>30,31</sup> As in our previous reports, a preferred (111) texture is observed for growth on Mo. In addition, while Mo is the most prominent feature of the substrate, MoP<sub>x</sub> peaks are also visible in XRD (with 0.5 < x < 0.8), demonstrating that there is some phosphorization of the Mo substrate during the growth process as shown in previous explorations of InP growth. <sup>22,26,27</sup> While not directly explored in this work, this modification of the Mo contact layer could have some impact on the device performance.

Steady state, room temperature PL data for Zn-doped TF-VLS InP show peak positions, intensity, and full-width half maxima close to those of a crystalline *p*-InP reference with similar doping concentration (Figure 2-3b), with only a low energy shoulder distinguishing the TF-VLS InP in this PL comparison. Particularly notable is the similarity in PL intensity and integrated counts, as this indicates our material approaches a similar luminescence yield and optically implied open circuit voltage (Voc) to the crystalline reference.<sup>22</sup> The difference in peak shape can be attributed to the non-epitaxial growth and effects from the zinc doping process, a feature previously observed in impurity studies for InP and attributed to both the Zn impurity level and LO phonon coupling with the Zn impurity.<sup>28</sup>

To further characterize our material, we perform a fit of the Urbach tail using the Roosbroeck-Shockley<sup>32</sup> equation to extract a relative absorption parameter from our steady-state PL data. From a logarithm fit to the Urbach formula for band tail absorption (1) we can extract the Urbach parameter E<sub>0</sub>, which is a measure of band edge sharpness that can be correlated to disorder in a semiconductor. Details of this extraction can be found in the Experimental and Theoretical Methods and in Figure 2-S3. Comparing the single-crystal *p*-type wafer reference and our *p*-type TF-VLS film with a similar doping concentration, we see similar E<sub>0</sub> values of 9.1 meV and 14.6 meV respectively, indicating band edge sharpness in our TF-VLS material in line with the single crystal wafer. In summary, the PL data show that our TF-VLS material is of high optical quality for implementation in a device, and that the growth and doping methods used here represent a promising route to poly-crystalline thin-film material approaching equal performance to previously explored bulk single-crystals.

$$(\alpha(E) = \alpha_0 e^{\left(\frac{E - E_{ref}}{E_0}\right)}) \tag{1}$$

**Figure 2-S3.** Extracted absorption tails near the InP band edge, extracted using the Roosbroeck-Schockley equation for the Zn doped *p*-type TF-VLS InP and a *p*-type wafer reference of similar doping concentration. Urbach parameter, representing the sharpness of the band edge according to the exponential decay constant of the band tail, is extracted from the linear fits to the log plot.

## 2.4 Electronic characterization of poly-InP photocathode devices

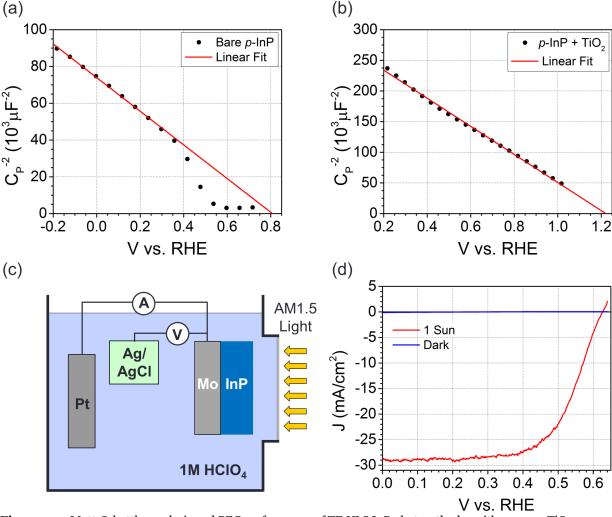

Given the high optical and crystalline quality of our thin-film InP on Mo, we then sought characterization of the electronic properties and photoelectrochemical performance of the complete photocathode cell. Before measuring our device in the final configuration, we first aimed to understand the doping and solution-semiconductor electronic interface properties by performing Mott-Schottky capacitance-voltage measurements both without and with the protective  $TiO_2$  window layer (Figure 2-4a,b). Without the  $TiO_2$  layer, we can first measure the bare InP surface in order to extract doping concentration and flatband potential ( $V_{FB}$ ) of the InP-solution interface. The measured doping concentration of our material following the aforementioned doping process is  $1.9 \times 10^{17} cm^{-3}$ , a concentration in line with single crystal wafers used in record photocathode cells. The  $V_{FB}$  extracted in this measurement is 0.81 V vs. RHE, a value  $\sim$ 0.55 eV less than the InP band gap. As the

**Figure 2-4.** Mott-Schottky analysis and PEC performance of TF-VLS InP photocathodes with a 30 nm  $TiO_2$  protection layer and Pt co-catalyst. (a,b) Mott-Schottky plot for p-doped TF-VLS, before (a) and after (b)  $TiO_2$  deposition in a pH 7 buffer. Linear fits are included for extraction of flatband potential and doping concentration. (d) J-V performance of a TF-VLS InP PEC device under AM1.5 illumination. J-V test performed in 1M  $HClO_4$  with the cell depicted in (c).

InP conduction band is close to the H<sub>2</sub>O/H<sub>2</sub> redox potential at pH o according to previous reports,  $^{12,13}$ , we would expect n-type surface inversion of the p-InP material at the liquid junction, a condition that would require a value of V<sub>FB</sub> near the band gap to flatten the InP bands. The value of V<sub>FB</sub> is thus a reflection of the surface band position prior to applying a potential, as the built-in potential is applied to return the surface to the bulk band position. The lower value of  $V_{FB}$  despite an effective metal work function  $(\Phi_m)$ position near the InP conduction band edge suggests reduced sensitivity of the built-in potential to  $\Phi_{\rm m}$ , a condition reflective of Fermi level pinning at the direct solution-InP interface. A similar result has been observed in previous explorations of the p-InP liquid junction (Figure 2-4a).33,34 Ideally, while the deposition of a TiO<sub>2</sub> protective layer should primarily serve to allow electrode operation in strong acid solutions, the semiconductor heterojunction quality should also be maintained or improved following this process if it is a practical solution for high efficiency cells, since any degradation of the interface would lead to a direct reduction of obtainable Voc.34 Measuring the flatband potential by the same method (Figure 2-4b), a measurement enabled due to rapid depletion of the thin TiO<sub>2</sub> layer under reverse bias, we see that the V<sub>FB</sub> of the InP/TiO<sub>2</sub>-solution interface shifts positively to 1.22 V. This positive shift implies that indeed the TiO<sub>2</sub> deposition improves the InP junction, as the proximity of V<sub>FB</sub>, and thus built-in potential, to the band gap energy places the redox potential far from the valence band, a condition that maximizes possible photovoltage in a solar device.<sup>34</sup> As discussed in prior work on InP-TiO<sub>2</sub> p-n heterojunctions, we have created a thin-film cell with a high built-in potential, as well as a large barrier to minority holes that prevents interface recombination and supports charge separation. 13,25 Therefore, the application of our TiO<sub>2</sub> heterojunction contact provides both a chemically inert surface and an ideal structure for a high efficiency cathode cell.

Finally, TF-VLS InP photocathode device performance was evaluated directly on the basis of J-V measurements in 1M HClO<sub>4</sub> (Figure 2-4d). Light and dark J-V sweeps were measured with a three-electrode configuration depicted in Figure 2-4c, under a simulated AM1.5 spectrum at 100 mW/cm<sup>2</sup>, showing a short-circuit current density (J<sub>SC</sub>) of 29.4 mA/cm<sup>2</sup> and a photocurrent onset of approximately 630 mV vs. RHE, with no significant features in the dark J-V curve that would suggest unwanted electrochemical sidereactions. Moreover, this performance level is consistent across multiple devices fabricated under these conditions, with a mean Voc of 609 mV and mean Jsc of 27.4 mA/cm<sup>2</sup>. More detailed device statistics are available in Figure 2-S4. Comparing device performance, single crystalline bulk wafers have a Jsc of 25.5 mA/cm<sup>2</sup> and a photocurrent onset potential of approximately 810 mV vs. RHE.<sup>12</sup> The lower V<sub>OC</sub> for the TF-VLS InP compared to single crystal wafers, despite the comparable high photoluminescence yields both as-grown<sup>22</sup> and after doping (Figure 2-3) is attributed to a non-ideal back contact and remaining observable crystal defects such as twin boundaries and grain boundaries. For the back contact, the effects of the MoP<sub>x</sub> present below the InP are not known, and previous reports suggest that a Zn-based metal alloy is necessary for ohmic contact to ptype InP. Therefore, further optimization in the doping process or growth substrate may improve photocathode performance.35,36 To this end, contact improvement strategies such as film transfer and alternate nucleation and contact layers for film growth are being pursued,<sup>22,23</sup> so significant improvement in overall photocathode performance using TF-VLS InP is certainly possible.

| Number of Devices:<br>12 | Voc (V) | J <sub>SC</sub> (mA/cm <sup>2</sup> ) | FF (%) | η (%)  |

|--------------------------|---------|---------------------------------------|--------|--------|

| Mean                     | 0.609   | 27.4                                  | 49.3   | 8.330  |

| Standard Deviation       | 0.0237  | 2.510                                 | 9.07   | 2.001  |

| Max                      | 0.639   | 30.0                                  | 63.0   | 11.595 |

| Champion                 | 0.626   | 29.4                                  | 63.0   | 11.595 |

**Figure 2-S4.** Device statistics for the final set of conditions presented in the text, including mean, max, and standard deviation for each major performance parameter. 12 devices were successfully fabricated and tested in this set.

### 2.5 Poly-InP Solar Fuel Production: Conclusions and Outlook

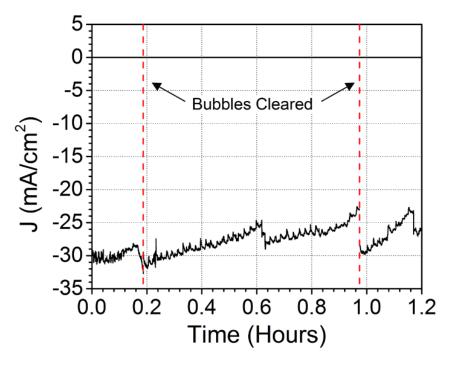

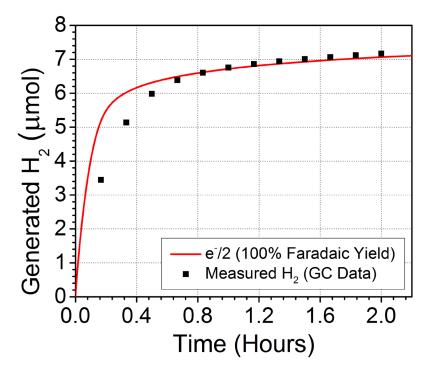

Nevertheless, the performance obtained here is still quite remarkable, with comparable voltage and improved efficiency compared to most non-III-V cathode technologies (Table 2-1). As the water-splitting PEC system requires large overpotentials beyond a minimum of 1.23 V for normal operation, the ultimate achievable voltage of a material is of utmost importance to its viability. When compared to single crystal systems, the TF-VLS InP photocathode is favorable over silicon and WSe<sub>2</sub> in voltage, and possesses one of the highest short-circuit current densities of all reported photocathodes with a competitive fill factor of 63%. In addition, we have measured sustained photocurrent and 100% Faradaic efficiency for H<sub>2</sub> over more than two hours, suggesting that our device structure is stable against corrosion during testing (Figure 2-S5, S6). Along with efficiency closely approaching that of crystalline InP wafer devices, the TF-VLS InP photocathode is poised as a promising future choice in high efficiency PEC systems.

In this work, we have demonstrated a stable, efficient photocathode device utilizing a low-cost, scalable fabrication technique that avoids expensive epitaxial growth processes and maintains high voltages and efficiencies necessary for viable operation of the water splitting PEC system. The devices presented in this work are the first demonstrated using this growth method, a technique that decreases usage of precious feedstock materials in high efficiency III-V systems. While the existing performance is promising, the implied potential from this growth method, on the basis of measurements of the material's intrinsic quality, suggests that much more can be done to bring the system and structures explored in this work up to and beyond the crystalline wafers. To this end, the TF-VLS growth method will be a valuable tool for production of higher efficiency photocathodes, with precisely controlled nucleation and mm-scale grain sizes as the ultimate limit in highly scalable thin-film PEC technology.

| System:<br>absorber/catalyst                | E <sub>G</sub> (eV) | Voc (V vs. RHE) | Jsc <br>(mA/cm²) | η (%) |

|---------------------------------------------|---------------------|-----------------|------------------|-------|

| Si Microwire <sup>a</sup>                   | 1.1                 | 0.54            | 15               | 5.8   |

| Planar Si <sup>a</sup>                      | 1.1                 | 0.56            | 28               | 9.6   |

| Microtextured Si <sup>c</sup>               | 1.1                 | 574             | 31.8             | 10.6  |

| Amorphous Si <sup>b</sup>                   | 1.7                 | 0.93            | 11.6             | 6     |

| WSe <sub>2</sub> Crystal <sup>d</sup>       | 1.2                 | 0.63            | 24.5             | 7.2   |

| Cu <sub>2</sub> O/MoS <sub>2+x</sub> e      | 2.2                 | 0.45            | 5.7              | 0.85  |

| CuGaSe/CdS <sup>f</sup>                     | 1.68                | 0.65            | 8.7              | 0.83  |

| InP Wafer<br>Nanopillars <sup>g</sup>       | 1.35                | 0.73            | 37               | 14    |

| InP Wafer/(Rh, H sat.) <sup>h</sup>         | 1.35                | 0.64            | 28.6             | 13.3  |

| InP Wafer/TiO <sub>2</sub> i                | 1.35                | 0.81            | 25.5             | 12.2  |

| This Work<br>(TF-VLS InP/TiO <sub>2</sub> ) | 1.35                | 0.63            | 29.4             | 11.6  |

$\textbf{Table 2-1.} \ \ \text{Tabulated half-cell STH efficiencies, } \ V_{OC}, \ \text{and } \ J_{SC} \ \text{of reported photocathode devices.}$

$<sup>{}^{</sup>a}Ref.\ 8;\ {}^{b}Ref\ 10;\ {}^{c}Ref\ 38;\ {}^{d}Ref\ 18;\ {}^{e}Ref\ 37;\ {}^{f}Ref\ 21;\ {}^{g}Ref\ 12;\ {}^{h}Ref\ 39,\ 81.7\ mW/cm^{2}\ illumination;\ {}^{i}Ref\ 13$

**Figure 2-S5.** Stability demonstration of TF-VLS InP photocathodes in 1M HClO4. Bubble clearing events, where measurements are paused to remove bubbles from electrode, are marked by dotted lines.

**Figure 2-S6.** Stability demonstration of TF-VLS InP photocathode in 0.1M H2SO4, with H<sub>2</sub> gas production measured by a gas chromatograph. H<sub>2</sub> generation calculated by 1-to-1 conversion of passed current is shown as a solid line. Data for this measurement is collected following the measurement in Figure 2-S<sub>5</sub>, but from the same device.

#### 2.6 Experimental and Theoretical Methods

#### A. Fabrication Process.

InP materials used in this work were grown using a recently developed Thin-Film Vapor-Liquid-Solid (TF-VLS) growth method.<sup>22</sup> Molybdenum foil substrates were degreased in acetone and isopropanol, followed by a hydrochloric acid etch and a deionized (DI) water rinse and nitrogen blow dry. The cleaned substrates were then loaded immediately into an electron beam evaporator, and 2 µm of 99.9999% pure indium metal was deposited on the foils, followed by a 40 nm SiO<sub>2</sub> capping layer. After this, the coated substrates were placed in a tube furnace, where they were phosphorized according to a previously described method utilizing 10% PH<sub>3</sub> in H<sub>2</sub> as the phosphorus source.<sup>22</sup> The typical growth process involves heating the substrates to 750 °C in H<sub>2</sub> ambient, followed by a 20 minute phosphorization step in 10 sccm of 10% PH<sub>3</sub>. This process yields an n-type InP layer approximately 3 µm in thickness, after etching of the SiO<sub>2</sub> capping layer in 49% HF. As we wish to extract minority electrons for the reduction of protons in solution, this *n*-type as-grown material must then be doped p-type. For this process, a closed-space sublimation system was used, with the TF-VLS InP placed on a 2 mm quartz spacer above Zn<sub>3</sub>P<sub>2</sub> (99.999%) powder used as the Zn acceptor source. The powder and substrate, held in thermal contact to graphite blocks, are heated separately by quartz lamps at 520 °C and 425 °C respectively, for a total doping time of one hour. The acceptor doping concentration in the InP layer using this method is approximately 10<sup>17</sup> cm<sup>-3</sup> as extracted by Mott-Schottky analysis. The doped samples were cleaned in five cycles of an acid treatment, utilizing 1% HCl, 1% HNO<sub>3</sub>, and DI water in succession to remove surface layers that may have been damaged during the doping step. The InP films were then coated with a 30 nm thick layer of titanium oxide (TiO2) by an atomic layer deposition (ALD) process using titanium tetraisopropoxide and water, and a deposition temperature of 120 °C. Finally, to enhance catalytic activity at the solution interface, a thin layer of platinum (thickness of approximately 1 nm) co-catalyst was deposited by electron beam evaporation.

#### **B. Physical Characterization.**

Scanning electron microscope (SEM) images were taken using a Zeiss Gemini Ultra-55. X-ray diffraction (XRD) data were taken using a Bruker AXS D8 Discover GADDS XRD Diffractometer system. Steady state micro photoluminescence (PL) data were taken using a 633 nm HeNe laser and the detector was a silicon CCD.

#### C. Photoelectrochemical (PEC) Characterization.

PEC devices were characterized using a BioLogic SP-300 bipotentiostat in a three-electrode, quartz-windowed cell with a BASi RE5B Ag/AgCl Reference electrode, platinum wire counter electrode, and TF-VLS InP as the working electrode. 1M HClO<sub>4</sub> was used as the electrolyte for J-V experiments, and a pH 7 buffer solution was used for Mott-Schottky measurements. The illumination source for J-V characterization, stability, and H<sub>2</sub> generation measurements was a Solar Light 16S-300-005 solar simulator with

AM1.5 filter. The light intensity of 100 mW/cm<sup>2</sup> was adjusted and calibrated using a Solar Light PMA-2100 radiometer and a PMA-2144 pyranometer, verified using a crystalline InP electrode IPCE calibrated against a NIST traceable photodiode (71648) from Newport.  $H_2$  generation data were measured using an Agilent 490 Micro Gas Chromatograph (GC), with  $N_2$  carrier gas and a 0.1M  $H_2SO_4$  electrolyte to avoid corrosion of internal GC components.

#### D. Average Solar Reflectance Calculation.

Average solar reflectance above  $E_{G,InP}$  is defined by a weighted average of the spectral reflectance  $R_S(\lambda)$  weighted by the AM1.5G solar spectrum  $E(\lambda)$ .

$$< R_{Solar} \ge = \frac{\sum_{\lambda} R_{S}(\lambda) \times E(\lambda) \times \Delta \lambda}{\sum_{\lambda} E(\lambda) \times \Delta \lambda}$$

The spectral reflectance  $R_S$  in this calculation was determined by the following equations for a one layer anti-reflection coating of varying thickness  $t_{AR}$ , with the three interface refractive indices for water,  $TiO_2$ , and InP taken at the InP band edge of 1.35 eV. These values are 1.3280, 2.496, and 3.395 respectively.

$$r1 = \frac{n_0 - n_1}{n_0 + n_1}$$

$$r2 = \frac{n_1 - n_2}{n_1 + n_2}$$

$$\theta = \frac{2\pi n_1 t_{AR}}{\lambda}$$

$$R = |r^2| \frac{r_1^2 + r_2^2 + 2r_1 r_2 cos 2\theta}{1 + r_1^2 r_2^2 + 2r_1 r_2 cos 2\theta}$$

## E. Extraction of absorption and Urbach Tail Parameter by the Roosbroeck - Shockley Relation

By the Roosbroeck-Schockley equation, emission rate can be directly related to absorption by an exponential relationship. The inverse of this relationship has been used<sup>32</sup> to extract the absorption coefficient from the photoluminescence emission of III-V materials. Here we utilize the same method to extract a relative absorption parameter:

$$\alpha(h\nu) \sim I(h\nu) \times (e^{\frac{h\nu}{kT}} - 1)/(h\nu^2)$$

As the Urbach energy parameter, defined as the exponential decay factor  $E_0$  in the Urbach tail equation below can be extracted as the inverse *slope* of the log of this absorption parameter, the absolute emission intensity is not required in this process. Therefore, in this case we extract the Urbach parameter directly from the slope of our relative PL intensity near the band edge as in figure 2-S3, converting the  $log_{10}$  slope to the exponential factor.

$$\alpha(h\nu) = \alpha_0 e^{(\frac{E-E_{ref}}{E_0})}$$

#### REFERENCES FOR CHAPTER 2

- 1. Grätzel, M. Photoelectrochemical Cells. *Nature* **2001**, *414*, 338–344.

- 2. Walter, M. G.; Warren, E. L.; McKone, J. R.; Boettcher, S. W.; Mi, Q.; Santori, E. A.; Lewis, N. S. Solar Water Splitting Cells. *Chem. Rev.* **2010**, *110*, 6446–6473.

- 3. Turner, J. A. Sustainable Hydrogen Production. Science 2004, 305, 972-974.

- 4. Seger, B.; Castelli, I. E.; Vesborg, P. C. K.; Jacobsen, K. W.; Hansen, O.; Chorkendorff, I. *Energy Environ. Sci.*, **2014**, *7*, 2397.

- 5. Maier, C. U.; Specht, M.; Bilger, G. Hydrogen evolution on platinum-coated *p*-silicon photocathodes. *Int. J. Hydrogen Energy* **1996**, *21*, 859–864.

- 6. Hou, Y.; Abrams, B. L.; Vesborg, P. C. K.; Björketun, M. E.; Herbst, K.; Bech, L.; Setti, A. M.; Damsgaard, C. D.; Pedersen, T.; Hansen, O.; Rossmeisl, J.; Dahl, S.; Nørskov, J. K.; Chorkendorff, I. Bioinspired molecular co-catalysts bonded to a silicon photocathode for solar hydrogen evolution. *Nat. Mater.* **2011**, *10*, 434–438.

- 7. Seger, B.; Pedersen, T.; Laursen, A. B.; Vesborg, P. C. K.; Hansen, O.; Chorkendorff, I. Using TiO<sub>2</sub> as a Conductive Protective Layer for H<sub>2</sub> Evolution. *J. Am. Chem. Soc.* **2013**, *135*, 1057–1064.

- 8. Boettcher, S. W.; Warren, E. L.; Putnam, M. C.; Santori, E. A.; Turner-Evans, D.; Kelzenberg, M. D.; Walter, M. G.; McKone, J. R.; Brunschwig, B. S.; Atwater, H. A.; Lewis, N. S. Photoelectrochemical Hydrogen Evolution Using Si Microwire Arrays. *J. Am. Chem. Soc.* **2011**, *133*, 1216–1219.

- 9. Oh, I.; Kye, J.; Hwang, S. Enhanced Photoelectrochemical Hydrogen Production from Silicon Nanowire Array Photocathode. *Nano Lett.* **2012**, *12*, 298–302.

- 10. Lin, Y.; Battaglia, C.; Boccard, M.; Hettick, M.; Yu, Z.; Ballif, C.; Ager, J.W.; Javey, A.; *Nano Lett.* **2013**, *13* (11), 5615-5618.

- 11. Szklarczyk, M.; Bockris, J. O. Photoelectrochemical Evolution of Hydrogen on *p*-Indium Phosphide. *J. Phys. Chem.* **1984**, *88*, 5241–5245.

- 12. Lee, M. H.; Takei, K.; Zhang, J.; Kapadia, R.; Zheng, M.; Chen, Y.-Z.; Nah, J.; Matthews, T. S.; Chueh, Y.-L.; Ager, J. W.; Javey, A. *p*-Type InP Nanopillar Photocathodes for Efficient Solar-Driven Hydrogen Production. *Angew. Chem., Int. Ed.* **2012**, *51*, 10760–10764.

- 13. Lin, Y.; Kapadia, R.; Yang, J.; Zheng, M.; Chen, K.; Hettick, M.; Yin, X.; Battaglia, C.; Sharp, I. D.; Ager, J. W.; Javey, A. The role of TiO2 surface passivation on improving the performance of *p*-InP Photocathodes. *J. Phys. Chem. C.* **2015**, DOI: 10.1021/jp5107313.

- 14. Heller, A.; Miller, B.; Lewerenz, H. J.; Bachmann, K. J. An Efficient Photocathode for Semiconductor Liquid Junction Cells: 9.4% Solar Conversion Efficiency with *p*-InP/VCl<sub>3</sub>-VCl<sub>2</sub>-HCl/C. *J. Am. Chem. Soc.* **1980**, *102*, 6555–6556.

- 15. Heller, A. Hydrogen Evolving Solar Cells. *Catal. Rev.: Sci. Eng.* **2013**, *26*, 655–681.

- 16. Schulte, K.; Lewerenz, H. Combined Photoelectrochemical Conditioning and Photoelectron Spectroscopy Analysis of InP Photocathodes. I. The Modification Procedure. *Electrochim. Acta* **2002**, *47*, 2633–2638.

- 17. Arai, T.; Sato, S.; Uemura, K.; Morikawa, T.; Kajino, T.; Motohiro, T. Photoelectrochemical reduction of CO<sub>2</sub> in water under visible-light irradiation by a *p*-type InP photocathode modified with an electropolymerized ruthenium complex. *Chem. Commun.* **2010**, *46*, 6944–6946

- 18. McKone, J. R.; Pieterick, A. P.; Gray, H. B.; Lewis, N. S. Hydrogen Evolution from Pt/Ru-Coated p-Type WSe<sub>2</sub> Photocathodes. *J. Am. Chem. Soc.* **2013**, *135*, 223–231.

- 19. Siripala, W.; Ivanovskaya, A.; Jaramillo, T. F.; Baeck, S.-H.; McFarland, E. W. A Cu<sub>2</sub>O/TiO<sub>2</sub> heterojunction thin film cathode for photoelectrocatalysis. *Sol. Energy Mater. Sol. Cells* **2003**, *77*, 229–237.

- 20. Paracchino, A.; Laporte, V.; Sivula, K.; Grätzel, M.; Thimsen, E. Highly Active Oxide Photocathode for Photoelectrochemical Water Reduction. *Nat. Mater.* **2011**, *10*, 456–461.

- 21. Moriya, M.; Minegishi, T.; Kumagai, H.; Katayama, M.; Kubota, J.; Domen, K. Stable Hydrogen Evolution from CdS-Modified CuGaSe<sub>2</sub> Photoelectrode under Visible-Light Irradiation. *J. Am. Chem. Soc.* **2013**, *135*, 3733–3735.

- 22. Kapadia, R.; Yu, Z.; Wang, H.-H. H.; Zheng, M.; Battaglia, C.; Hettick, M.; Kiriya, D.; Takei, K.; Lobaccaro, P.; Beeman, J. W.; Ager, J. W.; Maboudian, R.; Chrzan, D. C.; Javey, A. A direct thin-film path towards low-cost large-area III-V photovoltaics. *Scientific Reports*, **2013**, *3*, 2275.

- 23. Kapadia, R.; Yu, Z.; Hettick, M.; Xu, J.; Zheng, M. S.; Chen, C.-Y.; Balan, A. D.; Chrzan, D. C.; Javey, A. Deterministic nucleation of InP on metal foils with the thin-film vapor-liquid-solid growth mode. *Chem. Mater.* **2014**, *26* (3), 1340–1344.

- 24. Yang, J. J.; Ruth, R. P.; Manasevit, H. M. Electrical properties of epitaxial indium phosphide films grown by metalorganic chemical vapor deposition. *J. Appl. Phys.* **1981**, *52*, 6729.

- 25. Yin, X.; Battaglia, C.; Lin, Y.; Chen, K.; Hettick, M.; Zheng, M.; Chen, C.-Y.; Kiriya, D.; Javey, A. 19.2% efficient InP heterojunction solar cell with electron selective TiO2 contact. *ACS Photonics*, **2014**, *1* (12), 1245–1250.

- 26. Zheng, M.; Yu, Z.; Joon Seok, T.; Chen, Y.-Z.; Kapadia, R.; Takei, K.; Aloni, S.; Ager, J. W.; Wu, M.; Chueh, Y.-L.; Javey, A. High Optical Quality Polycrystalline Indium Phosphide Grown on Metal Substrates by Metalorganic Chemical Vapor Deposition. *J. Appl. Phys.* **2012**, *111*, 123112.

- 27. Kiriya, D.; Zheng, M.; Kapadia, R.; Zhang, J.; Hettick, M.; Yu, Z.; Takei, K.; Hank Wang, H.-H.; Lobaccaro, P.; Javey, A. Morphological and Spatial Control of InP Growth Using Closed-Space Sublimation. *J. Appl. Phys.* **2012**, *112*, 123102.

- 28. Williams, E. W.; Elder, W.; Astles, M. G.; Webb, M.; Mullin, J. B.; Straughan, B.; Tufton, P. J. Indium Phosphide I. A Photoluminescence Materials Study. *J. Electrochem. Soc.* **1973**, *120* (12), 1741-1749.

- 29. ICDD PDF-2, Entry 00-032-0452, 2003.

- 30.ICDD PDF-2, Entry 00-065-6024, **2003.**

- 31. ICDD PDF-2, Entry 00-089-5156, 2003.

- 32. Kost, A.; Lee, H. C.; Zou, Y.; Dapkus, P. D.; Garmire, E. Band-edge absorption coefficients from photoluminescence in semiconductor multiple quantum wells. *Appl. Phys. Lett.* **1989**, *54*, 1356-1358.

- 33. Heller, A. Conversion of sunlight into electrical power and photoassisted electrolysis of water in photoelectrochemical cells. *Acc. Chem. Res.*, **1981**, *14* (5), pp 154–162.

- 34. Bard, A.J.; Bocarsly, A.B.; Fan, F.R.F.; Walton, E.G.; Wrighton, M.S. The concept of Fermi level pinning at semiconductor/liquid junctions. Consequences for energy conversion efficiency and selection of useful solution redox couples in solar devices. *J. Am. Chem. Soc.*, **1980**, *102* (11), pp 3671–3677.

- 35. Piotrowska, A.; Guivarc'h, A.; Pelous, G. Ohmic contacts to III–V compound semiconductors: A review of fabrication techniques. *Solid-State Electron.* **1983**, *26*, 179–197.

- 36. Park, M.-H.; Wang, L. C.; Cheng, J. Y.; Palmstrom, C. J. Low resistance Ohmic contact scheme ( $\sim \mu\Omega$  cm<sup>2</sup>) to *p*-InP. *Appl. Phys. Lett.* **1997**, *70*, 99–101.

- 37. Morales-Guio, C.G.; Tilley, S.D.; Vrubel, H.; Grätzel, M.; Hu, X. Hydrogen evolution from a copper(I) oxide photocathode coated with an amorphous molybdenum sulphide catalyst. *Nat. Commun.* **2014**, *5*, 3059.

- 38. Matthew G. Kast , Lisa J. Enman , Nicholas J. Gurnon , Athavan Nadarajah , and Shannon W. Boettcher

- 39. Heller, A. Hydrogen-Evolving Solar Cells. Science 1984, 223 (4641), 1141-1148.

## CHAPTER 3

## DIRECT TEMPLATED LIQUID PHASE GROWTH OF HIGH QUALITY INP BELOW 300°C

### 3.1 Heterogeneous III-V integration: Introduction

While photovoltaic devices have broad applicability to environmentally motivated applications, another thrust of scientific innovation with significant impact to our lives has been the continuous increase in the power and efficiency of electronic and optoelectronic devices. Computers work every day to make our lives simpler and solve important problems for the world, and their power has been continuously rising over the years thanks to constant innovation in silicon device structures and processing. However, to sustain the meteoric rise in computing power that has been the result of continuous size scaling of silicon-based circuit elements over the past five decades, 3D integration must be pursued as nanometer-scale devices approach both electronic and atomic limits. In addition, significant advances in optoelectronics have not only expanded the scope of electronic circuit paradigms but also the power and efficiency of light emitting devices (LEDs) such as the III-V based white LEDs used in a variety of industries today. All of this has the additional benefit of enabling new low-power devices with high energy efficiency while maintaining high device performance.

Still, while certain applications have been able to leverage III-V materials such as GaN (LEDs) and InP (on-chip lasers)¹ to great benefit, most techniques still require clever but complex process modifications such as advanced bonding techniques for silicon and III-Vs to coexist. In this chapter, we take the TF-VLS process explored thus far and use the templated liquid phase (TLP) process modification to target microscale device structures with the goal of expanding process integration opportunities on a variety of substrates. With this, we hope to again demonstrate the scalability of this approach, indicating the possibility of future growth in III-V optoelectronics utilizing the TF-VLS method.

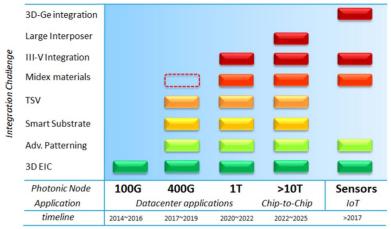

Figure 3i. Process integration roadmap for silicon photonic systems on a chip. (Fig. 11 top panel, Thomson et al. 2016)1

#### 3.2 Low-T Templated Liquid Phase Crystal Growth of InP below 300°C

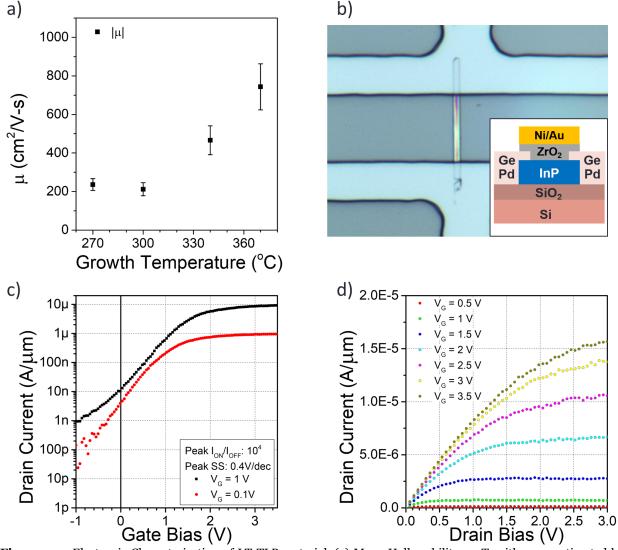

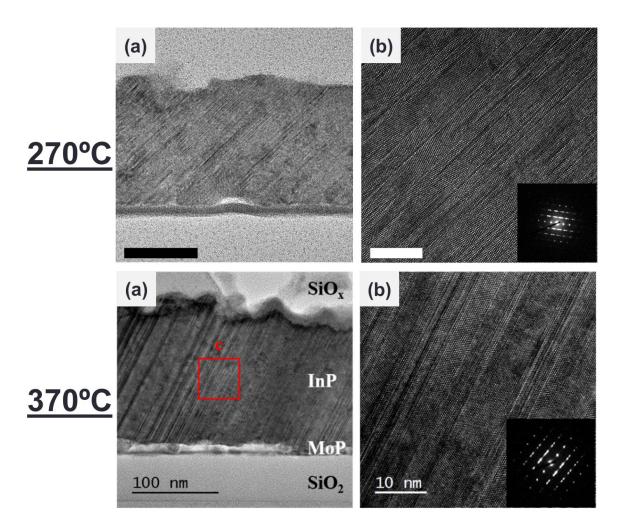

Three-dimensional integration of microelectronic circuits, where additional devices are placed above prior layers in the overall structure, is a promising method for increasing device density in electronics as size scaling approaches physical limits.<sup>2</sup> Particularly, Monolithic 3D integration, by which subsequent layers and interconnects are directly fabricated on the same chip, offers the best path to improvement due to reduction in complexity and similarity to existing "bottom up" fabrication schemes.<sup>3,4,5,6</sup> However, while III-V nanowire and 2D material transfer processes<sup>3,5</sup> have been demonstrated in monolithic structures, direct growth of high-performance electronic materials such as III-Vs has been limited primarily by high typical process temperatures<sup>7,8</sup> given the low temperature tolerance of materials such as interlayer metals and metal nitrides.9 Recently, a new method has been developed that allows for direct growth of III-V thin films on amorphous substrates, using the vapor-liquid-solid (VLS) process with thin-film templates (TF-VLS) to grow single crystal domains in defined patterns. 10, 11, 12 In this work, we extend this templated liquid phase (TLP) crystal growth method by utilizing a thermal gradient to lower sample process temperatures, enabling InP growth at temperatures below 300 °C while maintaining material quality at the micron scale due to single crystal domain size thresholds identified for each temperature range. Importantly, with process temperatures below the silicon complementary metal-oxide-semiconductor (CMOS) integration threshold of 400 °C, promising electronic performance is demonstrated, with measured Hall mobilities  $\mu_H > 800 \text{ cm}^2/\text{V-s}$  and with transistor effective mobility  $\mu_{Eff}$  over 600 cm<sup>2</sup>/V-s. With light emitting devices also demonstrated at temperatures below 300 °C and proof-of-concept growths on plastic and indium-tin-oxide (ITO) glass substrates, this evolution of the TLP process has greatly expanded the application space of III-V materials.

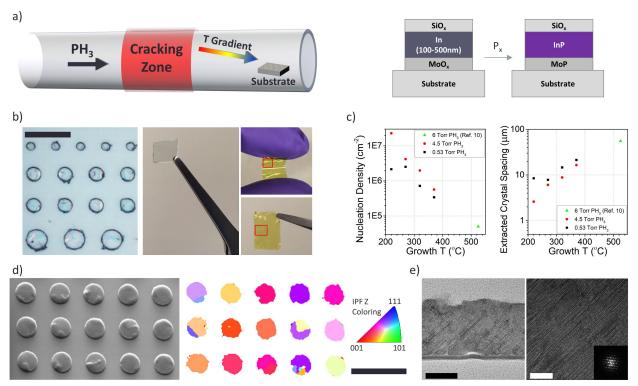

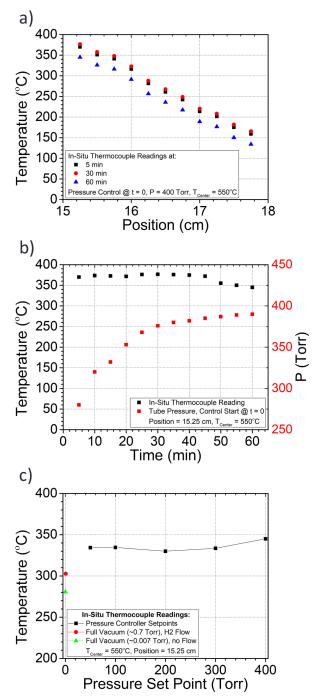

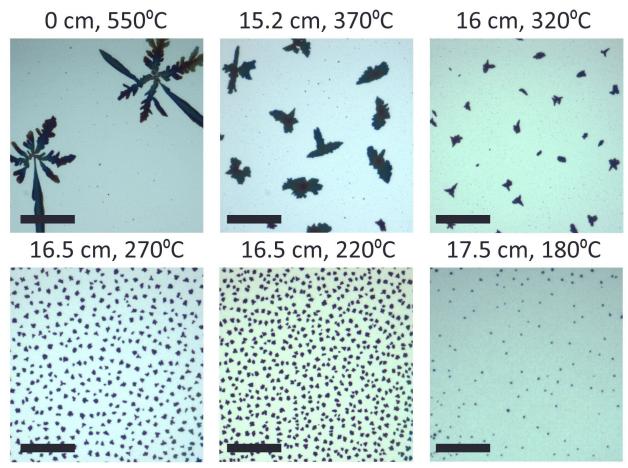

The first benefit of this method is its simplicity, as indicated in the growth process schematic in Figure 3-1a. A standard tube furnace is used for the reaction, with PH<sub>3</sub> diluted by H<sub>2</sub> at a controlled pressure. In this case, as with some MBE systems, a key step is the separation of source cracking from substrate heating, so the gaseous PH<sub>3</sub> source can be converted into useful P<sub>2</sub> and P<sub>4</sub> reactants.<sup>13</sup> As phosphine cracking is inefficient below 500 °C,14 and as phosphorus condensation can also be a concern, both a cracking zone and a temperature gradient to the substrate are needed to enable low temperature TLP (LT-TLP) growth. In this case, a calibrated gradient in a typical tube furnace was used with a center temperature of 550 °C to ensure adequate PH<sub>3</sub> cracking and accurate substrate temperature (Details in Experimental Methods, Supplementary Data Figure S1). Otherwise, the process is similar to previous descriptions of TF-VLS and TLP growth, where patterned nucleation layers and confining SiO<sub>x</sub> caps lead to localized VLS growth of crystalline thin films. Optical images of sample patterns in Figure 3-1b demonstrate Si/SiO<sub>2</sub>, ITO glass, and polyimide substrates in sequential panels, grown at temperatures of 370 °C, 270 °C, and 270 °C respectively. Critically, at these growth temperatures there is no strong impact to the properties of each substrate, such as the ITO resistivity and transparency and polyimide flexibility. While 270 °C is the lowest temperature explored for devices in this paper, nucleation and growth also occurs at temperatures as low as 180 <sup>o</sup>C (Figure S2), demonstrating the enabling power of this method for many applications.

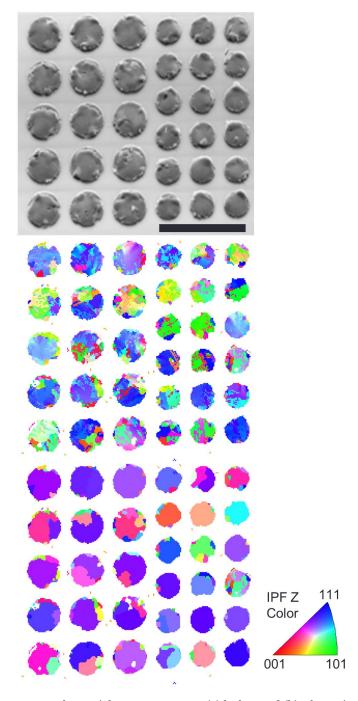

**Figure 3-1.** (a) General low temperature TLP process, with thermal gradient for T reduction, and typical substrate schematic. (b) Images of grown patterns on  $Si/SiO_2$ , ITO, and peeled polyimide from left to right, with contacts defined on the polyimide. Scale bar 15  $\mu$ m for optical microscope image of  $Si/SiO_2$  substrate. (c) Nucleation density vs. growth temperature for varied PH<sub>3</sub> concentration. (d) SEM image with EBSD map for 3  $\mu$ m circles grown at 270°C, scale bar 8  $\mu$ m. (e) TEM/HRTEM characterization at 270°C growth temperature, with SAED inset in the HRTEM image. TEM and HRTEM scale bars 50 nm and 10nm respectively.

## 3.3 Nucleation and growth behavior of Low-T TLP InP

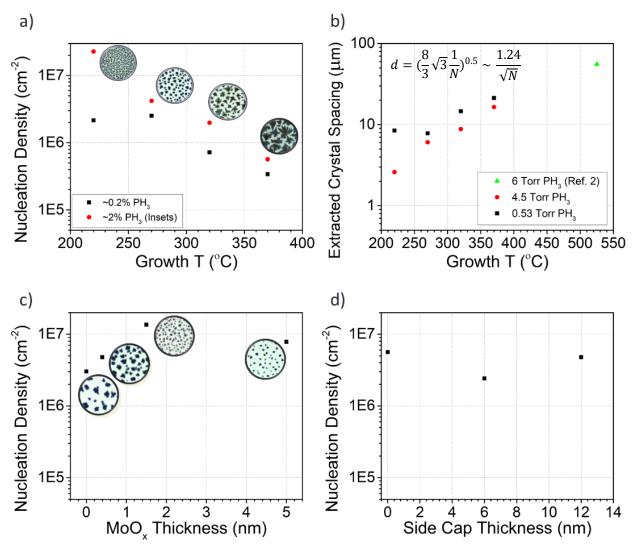

As growth temperatures are lowered, it is critical to identify the nucleation behavior at these lower substrate temperatures to define a useful target condition for a given process or application. To this end, partial growths on indium strips with full area  $MoO_x$  layers are completed at a range of temperatures from 180 to 370 °C, and a plot of extracted nucleation density as a function of growth temperature for different  $PH_3$  partial pressures is shown in Figure 3-1c. Assuming a hexagonal packing geometry, an estimate of domain spacing can also be extracted from the nucleation density data, with a range of approximately 8 to 21  $\mu$ m spacing for 220 to 370 °C at the lowest  $PH_3$  partial pressure presented. This projected feature spacing compares favorably to the reference point of 55  $\mu$ m at a 550 °C, and the clear exponential relationship between projected feature size and growth temperature over the entire range can be easily explained by the previously developed model of nucleation density for TF-VLS growth (Details in Ref. 11, Supplementary Note 1):

$$N_{Total} = \frac{A}{h^2} \left(\frac{Fh^4}{D}\right)^{\alpha} \tag{1}$$

In this case, the parameters of interest are the flux of phosphorus (F) and the diffusivity of phosphorus in indium (D). The exponential increase in nucleation density with decreasing T, as well as the weak dependence of nucleation density on cap thickness (Figure S3), suggests that the decreasing diffusivity of phosphorus due to an Arrhenius relationship is the dominant factor in nucleation behavior.

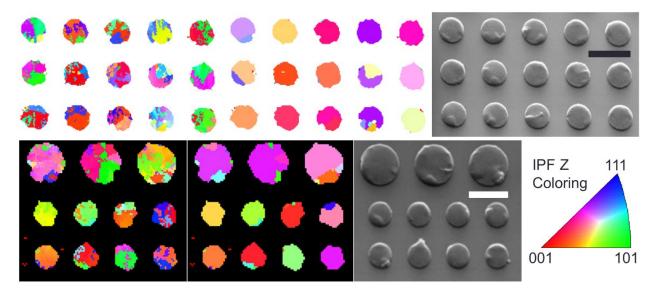

The projected domain spacing data in Figure 3-1c also show that despite increasing nucleation density, process conditions can be controlled to enable variation in the singledomain threshold temperature. Assuming nucleation behavior extends from MoO<sub>x</sub> films to MoO<sub>x</sub> patterns, nucleation density data predicts an approximately 8 µm threshold size for single crystal domains at 270 °C. In Figure 3-1d, a set of crystals is shown in a representative scanning electron microscope (SEM) image for a 270 °C growth condition, with a corresponding twin-corrected electron back scatter diffraction (EBSD) map (Details and additional images in Supplementary Data Figure S4). The majority of the 3 um features in this image contain a single crystal domain, and while single domain features quickly become less common for ≥5 µm features at this growth temperature, the EBSD data largely agrees with the nucleation density extraction when accounting for the geometrical estimation. Transmission electron microscope characterization further confirms the crystalline nature of films grown using this condition, with HRTEM and selected area electron diffraction (SAED) images displaying uniform twin orientation across the exposed crystal face (Figure 3-1e). Similar twin behavior is also observed as expected for higher growth temperatures, with similar manifestation of stacking faults and only minor rotational differences likely from sample variation. (Supplementary Data Figure S<sub>5</sub>, S<sub>6</sub>)

### 3.4 Optoelectronic Characterization of Low-T TLP InP

**Figure 3-2.** Photoluminescence characterization of LT-TLP material at various temperatures. (a) Normalized steady state PL spectra at different growth temperatures, compared to an n-type wafer reference. (b) Extracted Urbach tail parameter vs. extracted carrier concentration at different growth temperatures. (c) A comparison of internal quantum efficiency between 550 and 370°C growth temperatures.

Given the apparent extendibility of crystal domain control to lower temperatures, the material's overall optical and electronic quality should also be assessed to prove viability for real applications. In Figure 3-2, the basic optoelectronic quality of locally defined crystals grown at various temperatures below 400 °C is first explored.

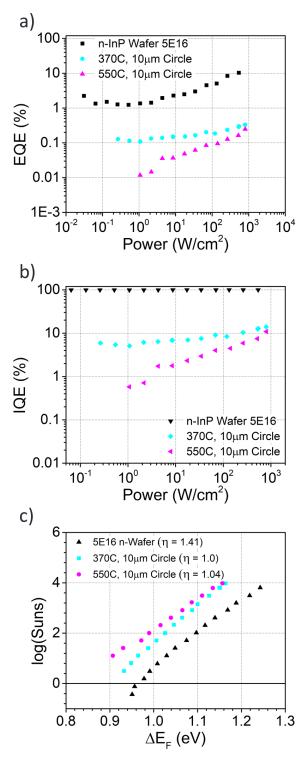

In Figure 3-2a, normalized photoluminescence (PL) spectra from TLP crystals are plotted for growth temperatures from 270 °C to 370 °C. Though all are broader than the bulk wafer reference, the shape and peak positions of the PL spectra are largely unchanged until below 300 °C. At the 270 °C growth temperature, the full-width half-max (FWHM) of the spectrum increases from ~58 meV to ~74 meV and the peak position shifts from ~1.35 eV to ~1.359 eV, indicating some defect influence when compared to growths above 300 °C. The Urbach tail parameter, a common optical measure of band-edge sharpness and disorder in crystalline materials, 15,16 can also be extracted from absorbance converted from the steady state PL spectra (Figure 3-2b, Details in Methods). It should be noted that the carrier concentration for each measurement in this plot is estimated from the Burstein-Moss peak shift above a reference gap energy, in this case taken from the moderately doped wafer plotted in Figure 3-2a. For all lower growth temperatures, despite any changes in spectrum broadness or intensity, the Urbach tail parameter remains very similar to values extracted from 550 °C and bulk references. 10,17 A comparison of PL internal quantum efficiency (IQE) extracted from measured external quantum efficiency (Figure 3-2c, Supplementary Data Figure S8) shows similar emission performance between 550 °C and 370 °C growth temperatures, indicating limited impact to radiative efficiency. As in previous work, 11 extracted quasi-Fermi level splitting is still above 900 meV for the 370 °C growth temperature at approximately 1 sun illumination, including a slight decrease in ideality factor from the "optical I-V" measurement (Supplementary Data Figure S7). Overall, optoelectronic measurements show that material grown across all temperatures 270 °C and upwards should be appropriate for light emitting devices and other optoelectronic applications.

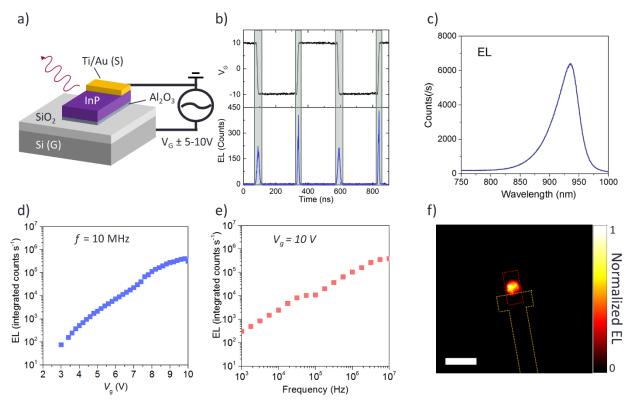

## 3.5 Transient electroluminescence from InP grown below 300°C