# UNIVERSITY OF CALIFORNIA SAN DIEGO

### **Cross-Layer Pathfinding for Off-Chip Interconnects**

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

# Electrical Engineering (Computer Engineering)

by

Vaishnav Srinivas

Committee in charge:

Andrew B. Kahng, Chair Jonathan Klamkin Farinaz Koushanfar Bill Lin Naveen Muralimanohar Dean Tullsen

2019

Copyright Vaishnav Srinivas, 2019 All rights reserved. The dissertation of Vaishnav Srinivas is approved, and it is acceptable in quality and form for publication on microfilm and electronically:

Chair

University of California San Diego

2019

# DEDICATION

To first principles.

# TABLE OF CONTENTS

| Signature Page  | ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dedication      | iv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Table of Conte  | nts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| List of Figures | ix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| List of Tables  | xiii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Acknowledgm     | entsxiv                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Vita            | xvii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Abstract of the | Dissertation                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Chapter 1       | Need for Cross-Layer Off-Chip Interconnect Optimization and Exploration 1                                                                                                                                                                                                                                                                                                                                                                                                            |

| Chapter 2       | Tools that Enable Interconnect Search and Power-Area-Timing Optimization82.1Introduction82.2IO, PHY, and Interconnect Models122.2.1Power Models132.2.2Voltage and Timing Margins212.2.3Area Models252.3Technology Portability252.4Validation272.5CACTI-IO312.5.1Simulation Methodology332.5.2High-capacity DDR3 Configurations332.5.33D Stacking Using Wide-IO352.5.4BOOM: LPDDRx for Servers372.5.5Optimizing Fanout for the Data Bus402.5.7PCRAM432.6Summary462.7Acknowledgments47 |

| Chapter 3       | Early Exploration of Mobile Memory Interconnect483.1Mobile System Considerations for SDRAM Interface Trends493.2SDRAM Capability Trends533.3Mobile Requirements Trends543.4Interface Considerations553.4.1Capacity563.4.2Throughput573.4.3Power60                                                                                                                                                                                                                                    |

|           |       | 3.4.4 Latency                                                 |

|-----------|-------|---------------------------------------------------------------|

|           |       | 3.4.5 Examples                                                |

|           | 3.5   | Summary                                                       |

|           | 3.6   | Acknowledgments                                               |

|           |       |                                                               |

| Chapter 4 | Next  | -Generation Server Memory Interconnect                        |

|           | 4.1   | Introduction                                                  |

|           | 4.2   | Tool Creation         71                                      |

|           |       | 4.2.1 Motivation                                              |

|           |       | 4.2.2 Tool Inputs and Outputs                                 |

|           |       | 4.2.3 Tool Modeling                                           |

|           |       | 4.2.4 Power Modeling                                          |

|           |       | 4.2.5 An API to Define New Interconnects                      |

|           |       | 4.2.6 Validation                                              |

|           |       | 4.2.7 Contributions                                           |

|           | 4.3   | Tool Analysis    81                                           |

|           |       | 4.3.1 Contribution of Memory I/O Power                        |

|           |       | 4.3.2 Motivation for Cascaded Channels and Narrow Channels    |

|           | 4.4   | The Cascaded Channel Architecture                             |

|           |       | 4.4.1 Proposed Design                                         |

|           |       | 4.4.2 Cascaded Channel Evaluation Methodology                 |

|           |       | 4.4.3 Cascaded Channel Results                                |

|           | 4.5   | The Narrow Channel Architecture                               |

|           |       | 4.5.1 Proposal                                                |

|           |       | 4.5.2 Evaluation                                              |

|           | 4.6   | Related Work   98                                             |

|           | 4.7   | Summary                                                       |

|           | 4.8   | Acknowledgments                                               |

|           | 1.0   |                                                               |

| Chapter 5 | Inter | connect for Silicon-Photonic NoCs                             |

|           | 5.1   | Introduction and Motivation                                   |

|           | 5.2   | Previous Work                                                 |

|           | 5.3   | MILP-Based Floorplan Optimization                             |

|           |       | 5.3.1 Notation Used in the MILP                               |

|           |       | 5.3.2 Formal MILP Statement                                   |

|           |       | 5.3.3 MILP Instance Complexity and Scalability                |

|           |       | 5.3.4 Optimization Flow Details and HotSpot Approximation 113 |

|           | 5.4   | Experimental Results and Discussion                           |

|           |       | 5.4.1 Simulation Infrastructure                               |

|           |       | 5.4.2 Design of Experiments                                   |

|           |       | 5.4.3 Results and Discussion                                  |

|           | 5.5   | Summary                                                       |

|           | 5.6   | Acknowledgments   121                                         |

|           |       |                                                               |

| Chapter 6 | Interconnect for 2.5D NoCs                                                                                                                  |            | 122 |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------|------------|-----|

|           | 6.1 Introduction                                                                                                                            |            | 122 |

|           | 6.2 Background                                                                                                                              |            | 125 |

|           | 6.3 Related Work                                                                                                                            |            | 127 |

|           | 6.4 Cross-layer Co-Optimization of Network Design and Chiplet Pl                                                                            | acement in |     |

|           | 2.5D Systems                                                                                                                                |            | 128 |

|           | 6.4.1 Optimization Problem Formulation and Methodology                                                                                      |            | 129 |

|           | 6.4.2 Cross-layer Optimization Knobs                                                                                                        |            | 133 |

|           | 6.4.3 Evaluation Framework                                                                                                                  |            | 138 |

|           | 6.4.4 Thermally-Aware Placement Algorithm                                                                                                   |            | 147 |

|           | 6.5 Evaluation Results                                                                                                                      |            | 150 |

|           | 6.5.1 Optimal Chiplet Placement Analyses                                                                                                    |            | 150 |

|           | 6.5.2 Iso-cost and Iso-performance Analyses                                                                                                 |            | 152 |

|           | 6.5.3 Analyses of Different Types of Applications                                                                                           |            | 154 |

|           | 6.5.4 Analyses of Cross-layer Co-optimization Benefits                                                                                      |            | 156 |

|           | 6.5.5 Sensitivity Analysis                                                                                                                  |            | 158 |

|           | 6.6 Summary                                                                                                                                 |            | 159 |

|           | 6.7 Acknowledgments                                                                                                                         |            | 160 |

| Chapter 7 | IO and Clock Tree Optimizations for 3D Integration                                                                                          |            | 161 |

|           | 7.1 Introduction                                                                                                                            |            | 161 |

|           | 7.2 3DIO Clustering and Clocking                                                                                                            |            | 163 |

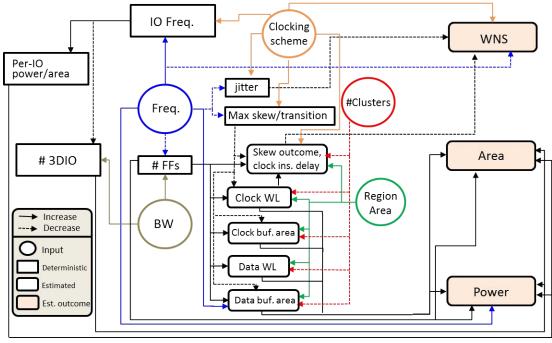

|           | 7.3 Power, Area and Timing Model                                                                                                            |            | 167 |

|           | 7.3.1 Clock and Data Wirelength                                                                                                             |            | 168 |

|           | 7.3.2 Clock and Data Whetength                                                                                                              |            | 169 |

|           | 7.3.2 Clock and Data Builer Alea                                                                                                            |            | 172 |

|           | 7.3.5         SDIO Alea and Fower                                                                                                           |            | 172 |

|           | 7.3.5 WNS and $F_{max}$ for On-die and 3DIO                                                                                                 |            | 173 |

|           | 7.4 P&R and Timing Flow $\dots \dots \dots$ |            | 174 |

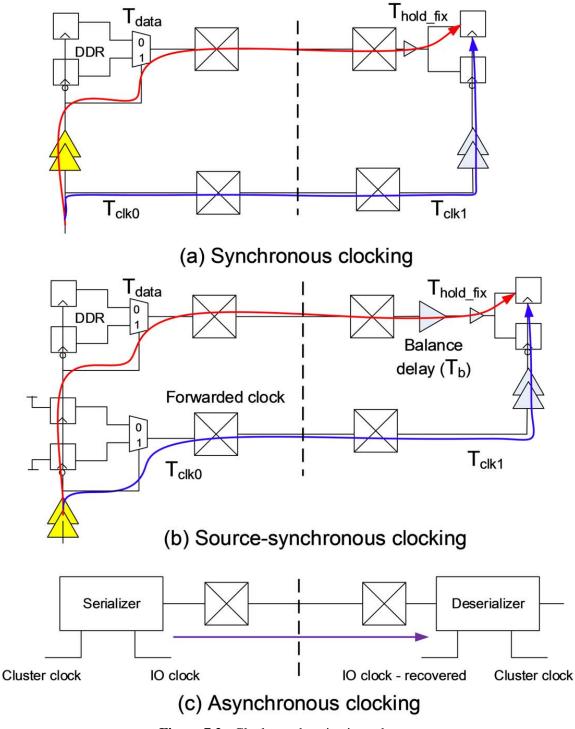

|           | -                                                                                                                                           |            | 175 |

|           |                                                                                                                                             |            |     |

|           | 5                                                                                                                                           |            | 177 |

|           | 7.4.3 Asynchronous                                                                                                                          |            | 178 |

|           | 7.5 Results                                                                                                                                 |            | 179 |

|           | 7.5.1 DOE                                                                                                                                   |            | 179 |

|           | 7.5.2 Model Fitting                                                                                                                         |            | 179 |

|           | 7.5.3 Design Space                                                                                                                          |            | 181 |

|           | 7.6 Summary                                                                                                                                 |            | 183 |

|           | 7.7 Acknowledgments                                                                                                                         |            | 185 |

| Chapter 8 | PDN Co-Optimization                                                                                                                         |            | 186 |

|           | 8.1 Introduction                                                                                                                            |            | 186 |

|           | 8.2 Approaches to Bump Inductance Modeling                                                                                                  |            | 190 |

|           | 8.3 Our Methodology                                                                                                                         |            | 191 |

|           | 8.3.1 Selection of Model Parameters                                                                                                         |            | 191 |

|           | 8.3.2 Modeling Techniques                                                                                                                   |            | 193 |

|           | 8.3.3 Reporting Metrics                                                                                                                     |            | 194 |

|              | 8.4  | Experie | ments   |         |       |      |     | <br> | <br>    | •   | <br> |       | <br>    | •          |       | 194 |

|--------------|------|---------|---------|---------|-------|------|-----|------|---------|-----|------|-------|---------|------------|-------|-----|

|              |      | 8.4.1   | Design  | of Ex   | kperi | men  | ts. | <br> | <br>    | •   | <br> |       | <br>    | •          |       | 195 |

|              |      | 8.4.2   | Results | s for E | Expe  | rime | nts | <br> | <br>• • | •   | <br> |       | <br>    | •          |       | 196 |

|              | 8.5  | Summa   | ary     |         |       | •••  |     | <br> | <br>•   | •   | <br> |       | <br>    |            | <br>• | 202 |

|              | 8.6  | Acknow  | wledgm  | ents    |       | •••  | • • | <br> | <br>••• | •   | <br> | <br>• | <br>• • | •          |       | 203 |

| Chapter 9    | Conc | clusion |         |         |       | •••  |     | <br> | <br>••• | ••• | <br> | <br>• | <br>    | . <b>.</b> |       | 204 |

| Bibliography |      |         |         |         |       | •••  |     | <br> | <br>••  | •   | <br> |       | <br>    | •          |       | 207 |

# LIST OF FIGURES

| Figure 1.1:  | Organization of this thesis.                                                                 | 4        |

|--------------|----------------------------------------------------------------------------------------------|----------|

| Figure 1.2:  | Die/PKG/PCB co-design and pathfinding.                                                       | 4        |

| Figure 2.1:  | CACTI-IO: Off-chip modeling and exploration within CACTI.                                    | 9        |

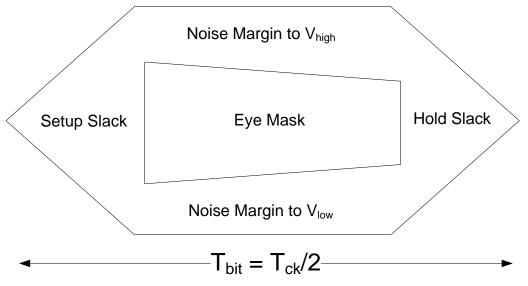

| Figure 2.2:  | Memory interface eye diagram for voltage and noise budgets.                                  | 10       |

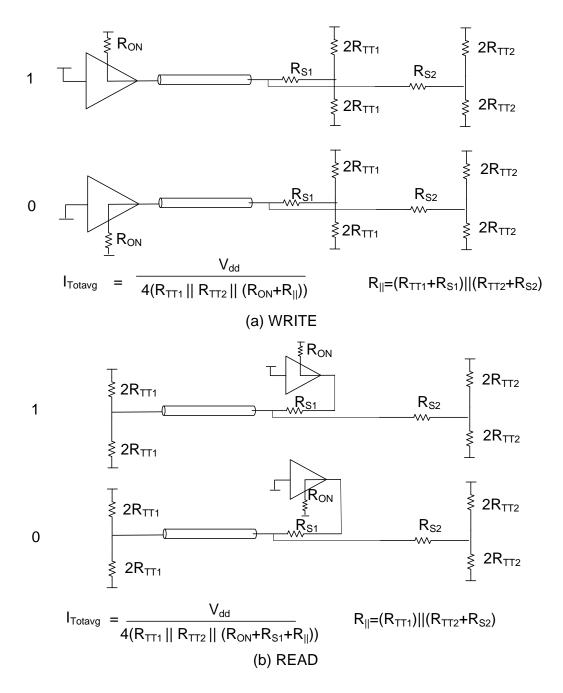

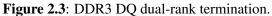

| Figure 2.3:  | DDR3 DQ dual-rank termination.                                                               | 15       |

| -            |                                                                                              | 15       |

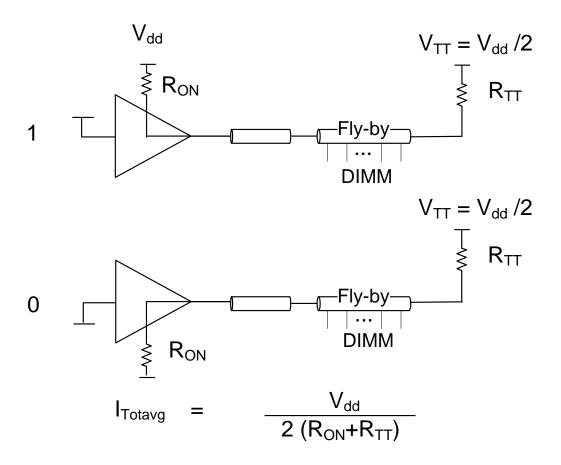

| Figure 2.4:  | DDR3 CA termination.                                                                         |          |

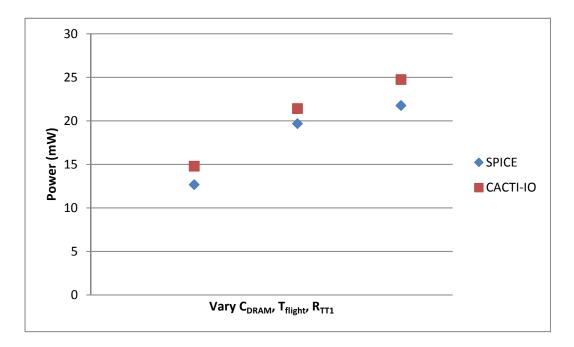

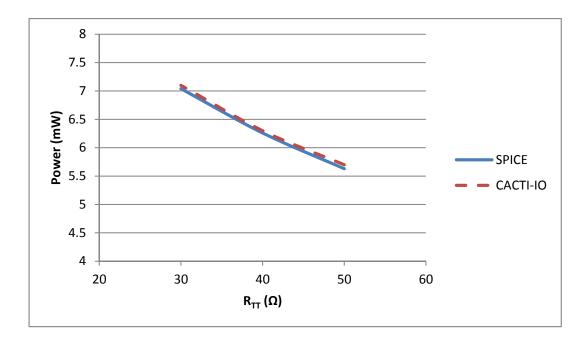

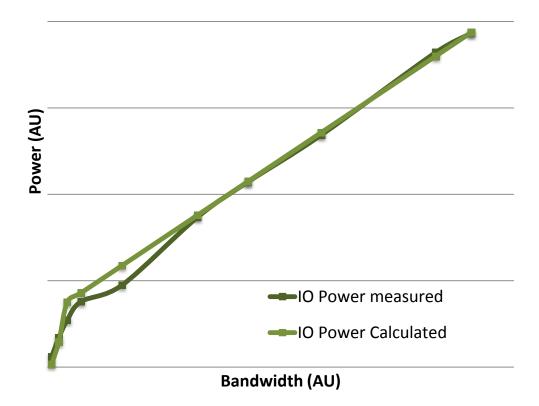

| Figure 2.5:  | DQ single-lane DDR3 termination power                                                        | 28       |

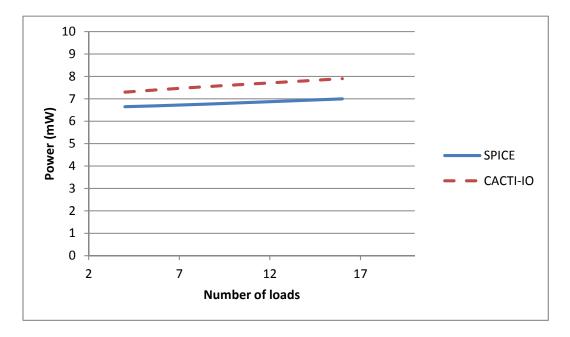

| Figure 2.6:  | DQ single-lane DDR3 total IO power.                                                          | 28       |

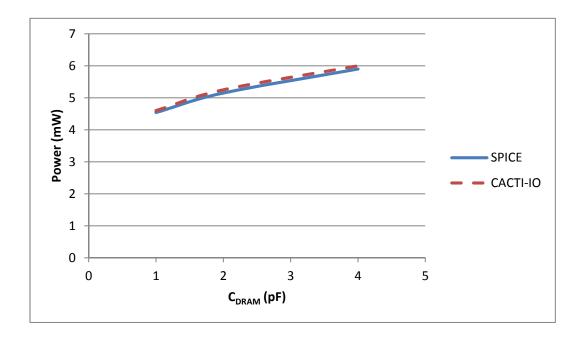

| Figure 2.7:  | CA single-lane DDR3 termination power.                                                       | 29       |

| Figure 2.8:  | CA single-lane DDR3 total IO power.                                                          | 29       |

| Figure 2.9:  | DQ single-lane LPDDR2 total IO power.                                                        | 30       |

| Figure 2.10: | LPDDR2 WRITE measurement vs. model                                                           | 30       |

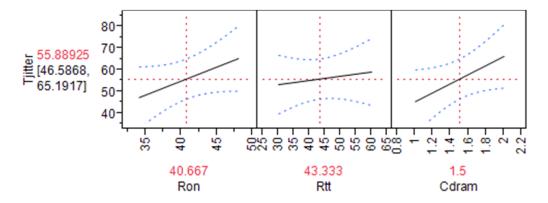

| Figure 2.11: | DOE analysis on a DDR3 channel.                                                              | 31       |

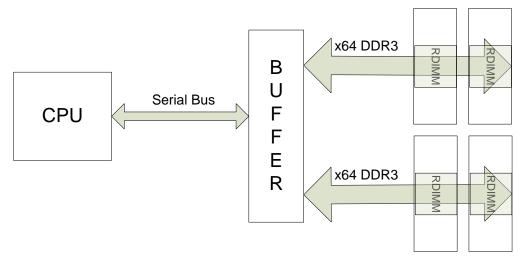

| Figure 2.12: | BoB (Buffer-on-Board) [169]                                                                  | 34       |

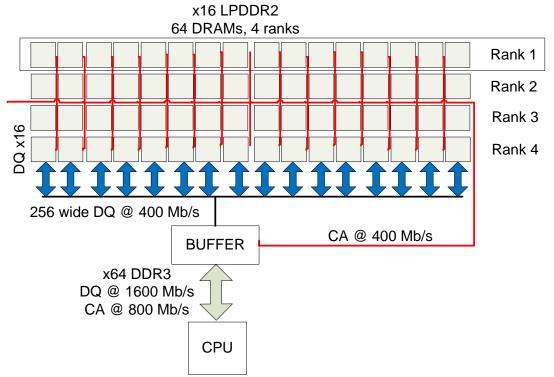

| Figure 2.13: | BOOM-N4-L-400 configuration with x16 devices [157].                                          | 37       |

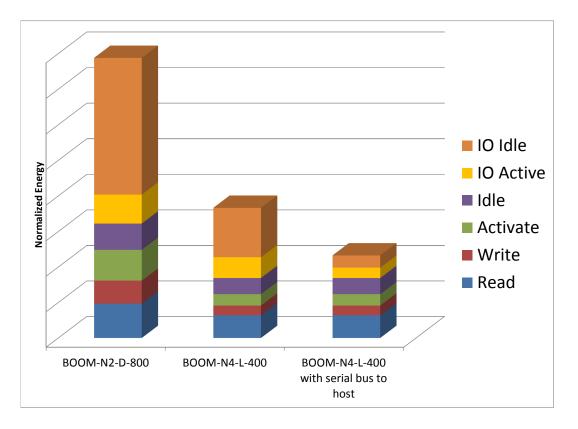

|              | Normalized system (DRAM+IO) energy for BOOM configurations                                   | 39       |

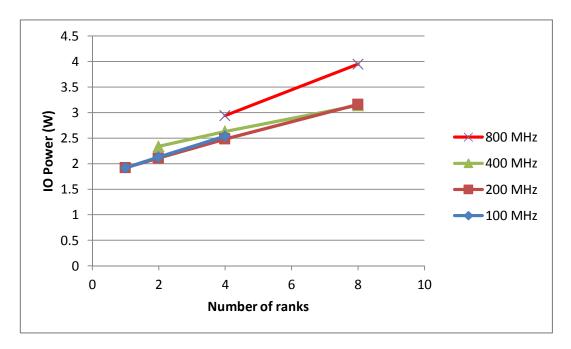

| Figure 2.15: | IO power vs. number of ranks for BOOM-LPDDR2                                                 | 41       |

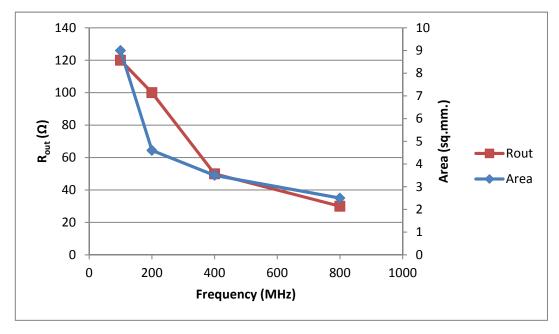

| Figure 2.16: | Area vs. frequency for a constant-bandwidth BOOM-LPDDR2                                      | 41       |

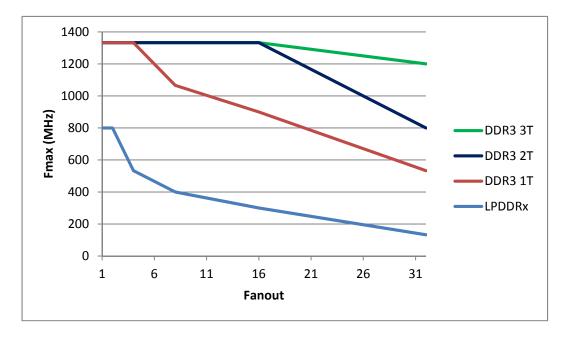

| Figure 2.17: | Fanout vs. $F_{max}$ for a typical DDR3 CA bus.                                              | 42       |

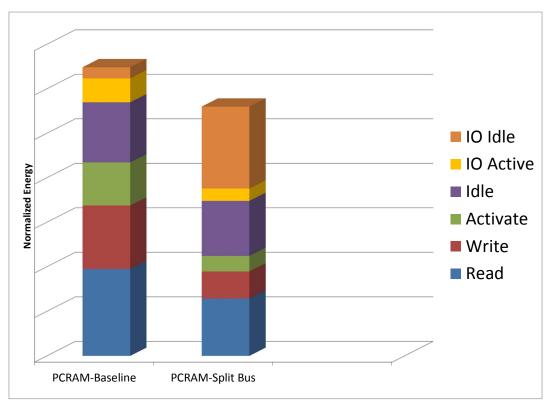

| Figure 2.18: | Normalized system (DRAM+IO) energy for PCRAM configurations.                                 | 44       |

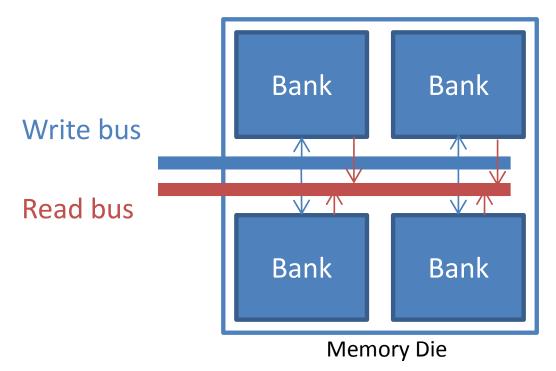

| Figure 2.19: | Split-bus PCRAM configuration.                                                               | 45       |

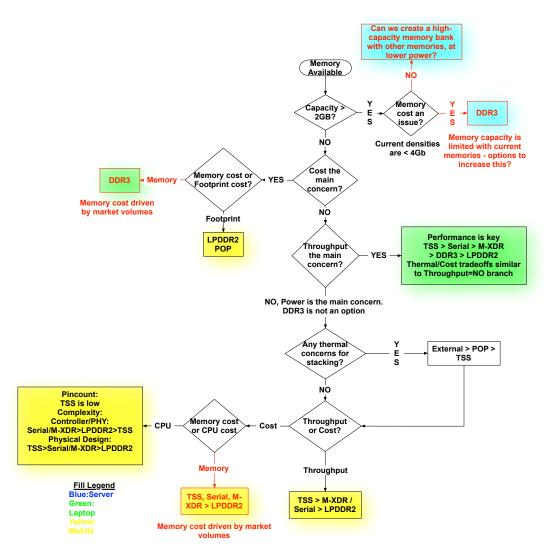

| Figure 3.1:  | The decision tree with forks based on SDRAM capabilities and regions based on                |          |

| 1 iguie 5.1. | system requirements.                                                                         | 50       |

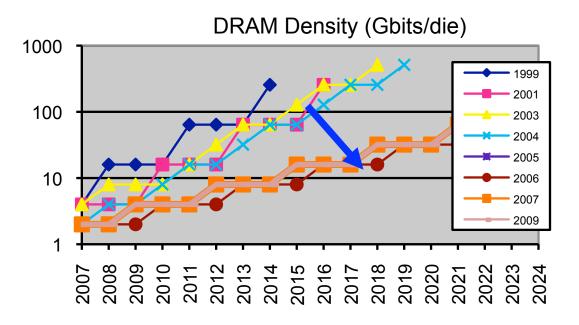

| Figure 3.2:  | DRAM density projections [168].                                                              | 53       |

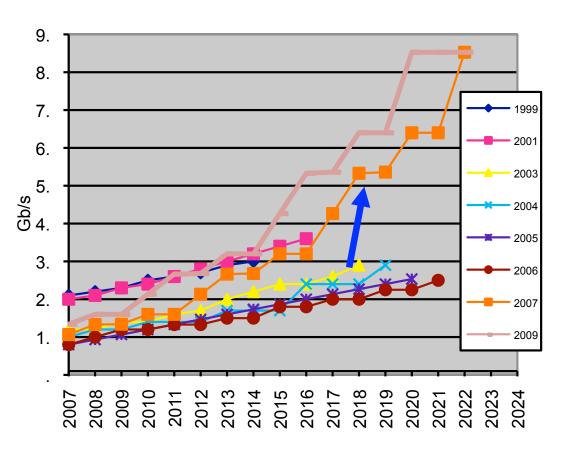

| Figure 3.3:  |                                                                                              | 55<br>54 |

| -            | DRAM data rate projections [168].                                                            | 54<br>55 |

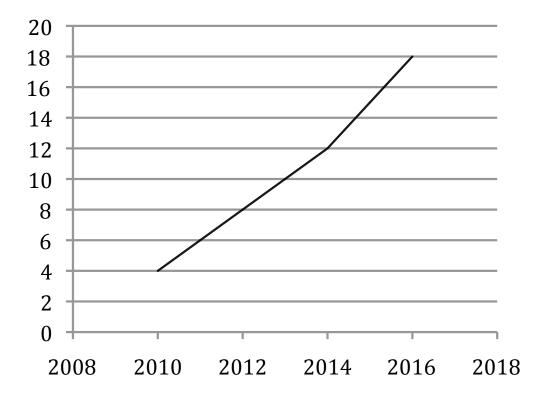

| Figure 3.4:  | Peak throughput projections for mobile platforms (in GB/s) [232]                             |          |

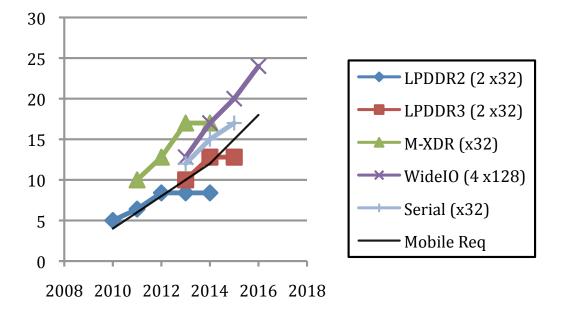

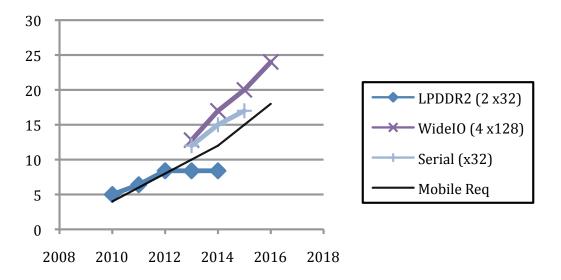

| Figure 3.5:  | Throughput (GB/s) projections based on the memory interface calculator. $\ldots$             | 60       |

| Figure 3.6:  | Gap in throughput (GB/s) before LPDDR3                                                       | 67       |

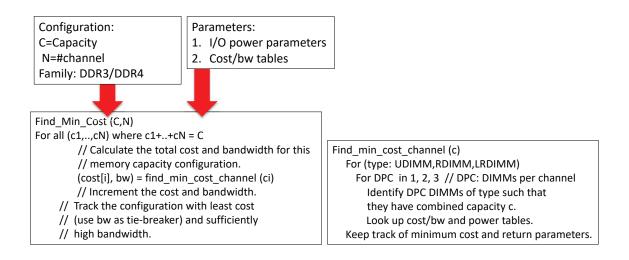

| Figure 4.1:  | Basic flowchart for the tool's design space exploration for traditional DDR topologies.      | 74       |

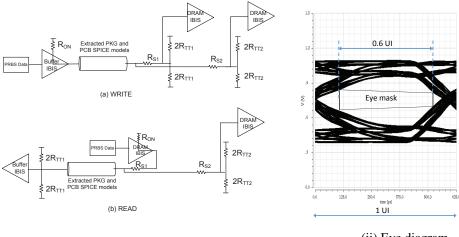

| Figure 4.2:  | (i) DDR3 SPICE testbench. The testbench includes IBIS models for the buffer                  |          |

|              | and DRAM, extracted SPICE models for the package and PCB, and a PRBS input                   |          |

|              | stimulus pattern. We sweep the termination resistances $R_{TT1}$ and $R_{TT2}$ to identify a |          |

|              | configuration with high signal integrity. (ii) DDR3 eye diagram.                             | 77       |

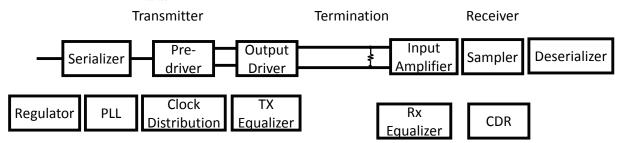

| Figure 4.3:  | Typical components in a SERDES link.                                                         | 78       |

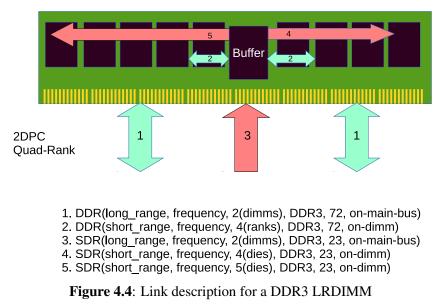

| Figure 4.4:  | Link description for a DDR3 LRDIMM                                                           | 80       |

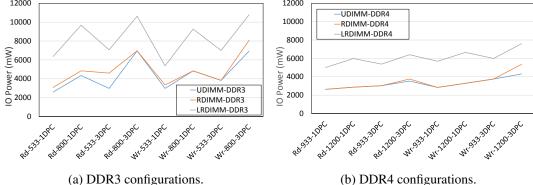

| Figure 4.5:  | Memory I/O power (mW) for a number of DDR3/DDR4 design points that vary                      |          |

|              | DIMM type, read/write intensity, frequency, and DIMMs per channel (DPC)                      | 82       |

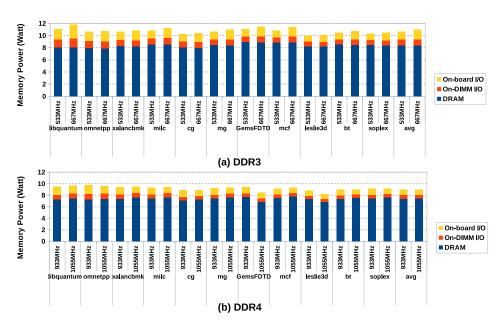

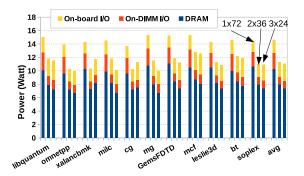

| Figure 4.6:  | Breakdown of memory power (mW) for DDR3/DDR4 design points for each bench-                   | 52       |

| 19410 1.0.   | mark. We assume 3 LRDIMMs per channel.                                                       | 83       |

|              | maria ite accune o Literittito per enamela i a a a a a a a a a a a a a a a a a a             | 00       |

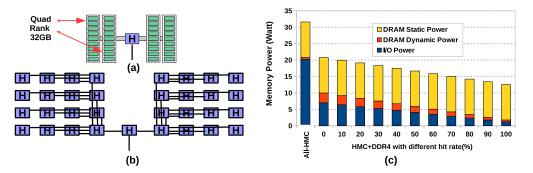

| Figure 4.7:           | (a) A memory organization with one HMC "cache" that is backed by two DDR4 channels and four quad-rank LRDIMMs. (b) An HMC-only organization with one |          |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                       | HMC "cache" backed by 32 other 4GB HMCs. (c) Memory power for the two                                                                                |          |

|                       | organizations, as a function of the hit rate in the HMC "cache".                                                                                     | 83       |

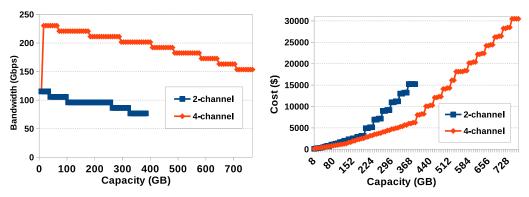

| Figure 4.8:           | Identifying the best bandwidth (left) and cost (right) design points for each memory                                                                 | ~ .      |

|                       | capacity requirement.                                                                                                                                | 84       |

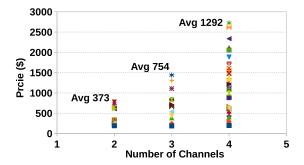

| Figure 4.9:           | Prices for Intel Xeon (E3 and E5) processors as a function of channel count [201].                                                                   | 85       |

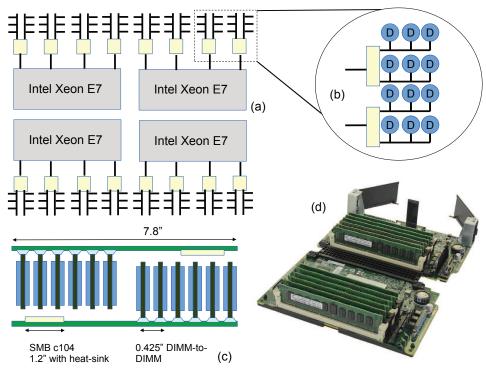

| Figure 4.10:          | Organization of the HP ProLiant DL580 Gen8 server (a). The memory cartridge is                                                                       |          |

|                       | represented in (b), (c), and (d).                                                                                                                    | 86       |

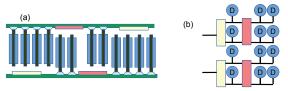

| Figure 4.11:          | The Cascaded Channel Architecture. RoB chips are used to partition each channel.                                                                     | 86       |

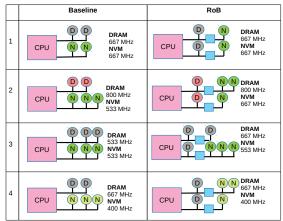

| Figure 4.12:          | Four different cases that use DRAM and NVM. The Baseline organizations use sepa-                                                                     |          |

|                       | rate channels for DRAM and NVM. The corresponding RoB architecture implements                                                                        |          |

|                       | NVM on a distant cascaded channel. The 800 MHz and 400 MHz channels work at                                                                          | 00       |

| <b>F</b> : 4.12       | 1.5V and 1.2V, respectively, while other channels operate at 1.35V.                                                                                  | 89       |

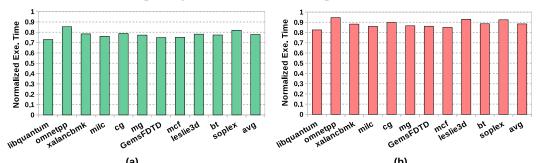

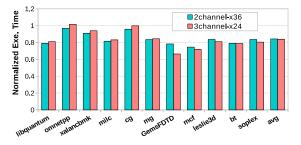

| Figure 4.13:          | Execution times for the cascaded channel architecture, normalized against the baseline                                                               | 0.1      |

| E                     | cartridge (DDR3 (a) and DDR4 (b)).                                                                                                                   | 91       |

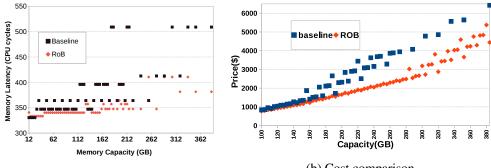

| Figure 4.14:          | Memory latency and cost comparison with baseline and RoB approaches, as the                                                                          | 02       |

| E                     | memory capacity requirement is varied.                                                                                                               | 92       |

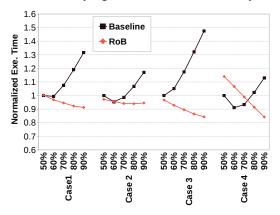

| Figure 4.15:          | Normalized execution time (averaged across all benchmarks) for baseline and RoB                                                                      | 02       |

| E                     | cases, as the fraction of DRAM accesses is varied from 50% to 90%                                                                                    | 93<br>04 |

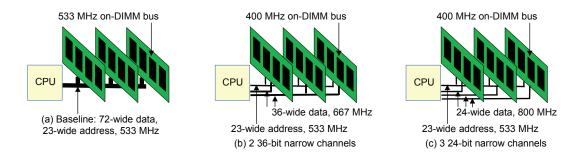

| -                     | The baseline (a) and two narrow channel organizations (b and c).                                                                                     | 94       |

| Figure 4.17:          | Execution time for the two narrow channel designs in Figure 4.16, normalized against the baseline.                                                   | 97       |

| Figure 4.18:          | Memory power for the two narrow channel designs in Figure 4.16, normalized against                                                                   | 97       |

| Figure 4.18.          | the baseline (left).                                                                                                                                 | 98       |

|                       |                                                                                                                                                      | 70       |

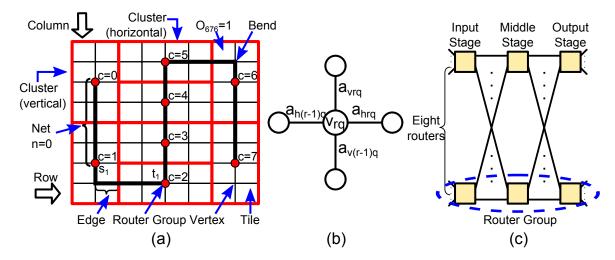

| Figure 5.1:           | (a) Example of chip floorplan to illustrate our terminology. (b) A vertex and its                                                                    |          |

|                       | surrounding edges in the routing graph. (c) 3-stage Clos topology with 8 router groups                                                               |          |

|                       | per stage                                                                                                                                            | 106      |

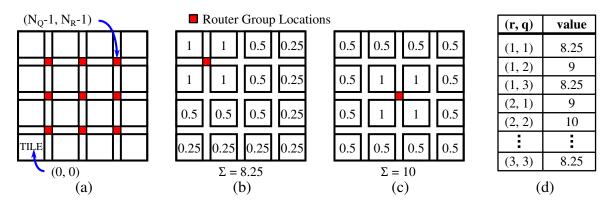

| Figure 5.2:           | Core impact matrix generation: (a) illustrative floorplan with 16 tiles (64 cores) and                                                               |          |

|                       | nine potential router group positions; (b) sample core impact calculation for router                                                                 |          |

|                       | group (1,3); (c) sample core impact calculation for router group (2,2); (d) a 1x9 core                                                               |          |

|                       | impact array generated for the floorplan.                                                                                                            | 114      |

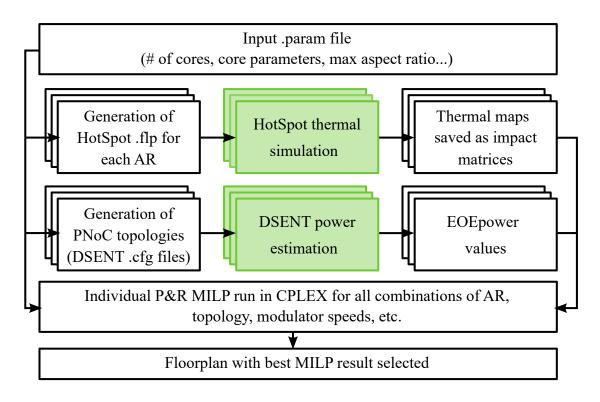

| Figure 5.3:           | The floorplan optimization flow.                                                                                                                     | 115      |

| Figure 5.4:           | Six power profiles studied. Darker tiles indicate higher-power cores                                                                                 | 116      |

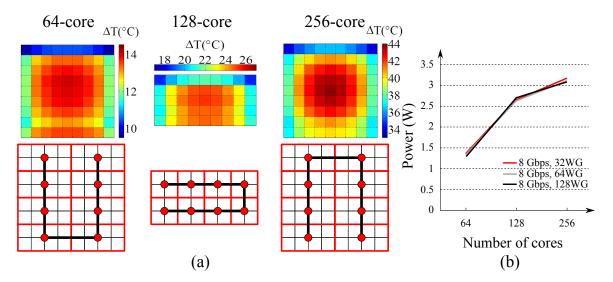

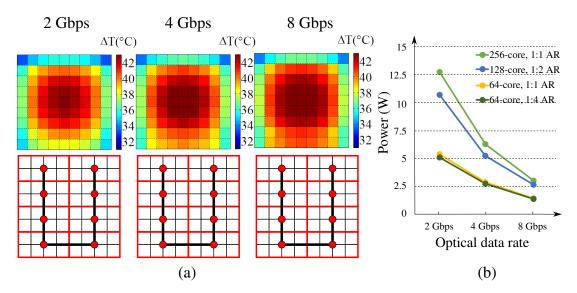

| Figure 5.5:           | Accumulated thermal weight profile and optimal floorplan vs. $N_{cores}$                                                                             | 117      |

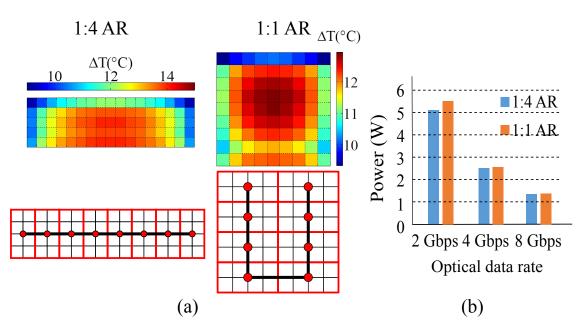

| Figure 5.6:           | Accumulated thermal weight profile and optimal floorplan vs. AR                                                                                      | 118      |

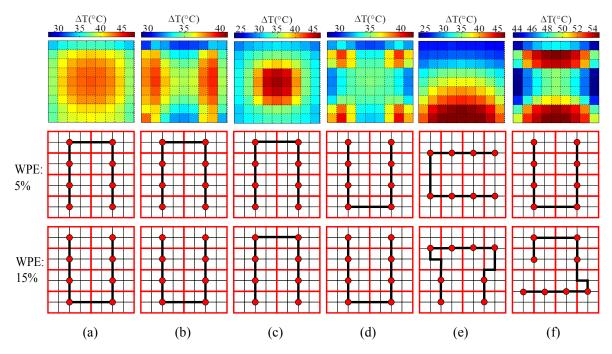

| Figure 5.7:           | Accumulated thermal weight profile on the first row, and optimal floorplan with WPE                                                                  |          |

|                       | of 5% and 15% on the second and third row respectively for power profiles (a) - (f) in                                                               |          |

| <b>F</b> : <b>F</b> 0 | Figure 5.4.                                                                                                                                          | 119      |

| Figure 5.8:           | Accumulated thermal weight profile and optimal floorplan vs. optical data rate                                                                       | 119      |

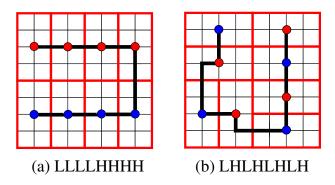

| Figure 5.9:           | Optimal floorplan for different cluster power weights; blue (red) router group indicates                                                             | 120      |

|                       | a low- (high-) power cluster respectively.                                                                                                           | 120      |

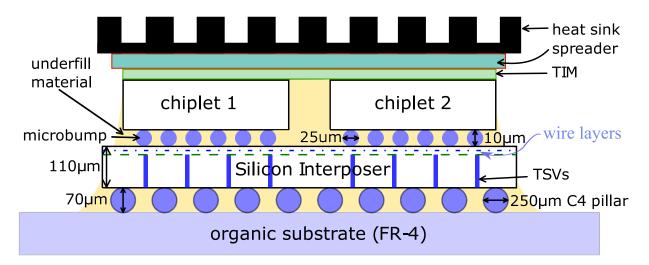

| Figure 6.1:           | Cross-section view of a 2.5D system.                                                                                                                 | 125      |

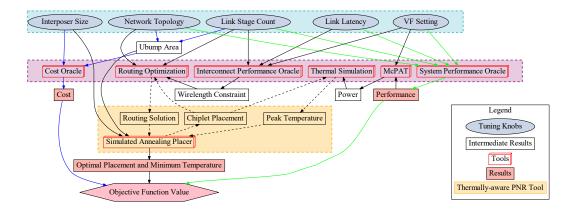

| Figure 6.2:           | Cross-layer co-optimization methodology.                                                                                                             | 129      |

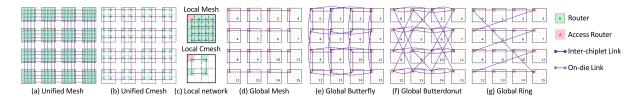

| Figure 6.3:                | Logical view of network topologies. (a)-(b) are unified networks, while (c)-(g) are used to form hierarchical networks.                                                        | 133        |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

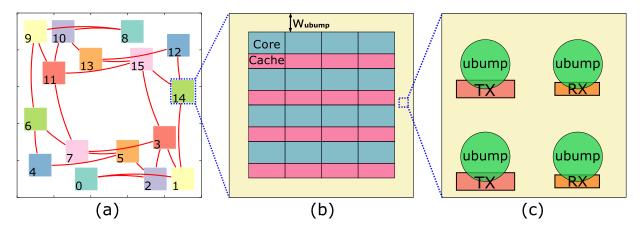

| Figure 6.4:                | Illustration of (a) chiplet placement on an interposer with logical connections, (b) a chiplet with $\mu$ bump overhead, and (c) $\mu$ bumps with TX/RX regions (not to scale) | 136        |

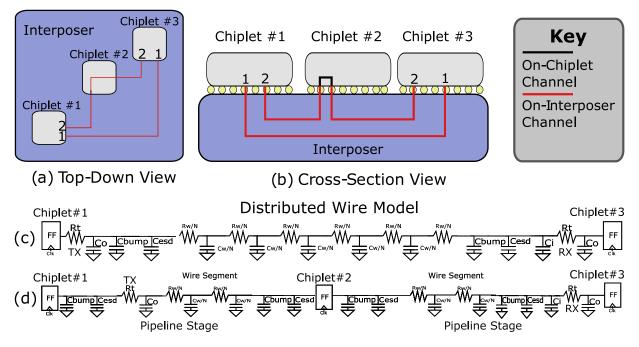

| Figure 6.5:                | Illustration of (a) top-down view and (b) cross-section view of inter-chiplet link                                                                                             | 150        |

| Figure 0.5.                | implementation, and distributed wire models for (c) repeaterless link (Path 1 in (a)-(b))                                                                                      |            |

|                            | and (d) gas-station link (Path 2 in (a)-(b)). $\dots \dots \dots$              | 137        |

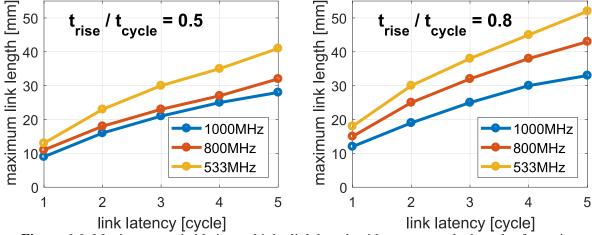

| Figure 6.6:                | Maximum reachable inter-chiplet link length with respect to clock cycles for various                                                                                           | 157        |

| i iguie oloi               | frequencies and rise-time constraints.                                                                                                                                         | 138        |

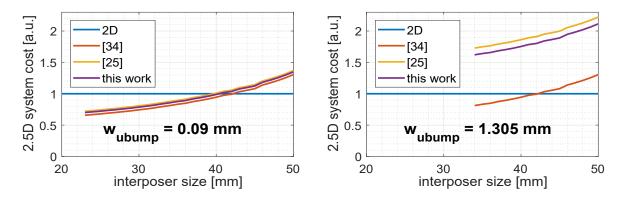

| Figure 6.7:                | Comparison between the cost of a 2D system, and the cost of a 2.5D system estimated                                                                                            |            |

| 0                          | using prior cost models [34, 25] and our enhanced cost model for interposer sizes                                                                                              |            |

|                            | from 20mm to 50mm and $\mu$ bump stretch-out widths ( $w_{\mu b \mu m p}$ ) of 0.09mm and 1.305mm,                                                                             |            |

|                            | which correspond to the lower and upper limits of $w_{ubump}$ in our analysis, respectively.                                                                                   | 141        |

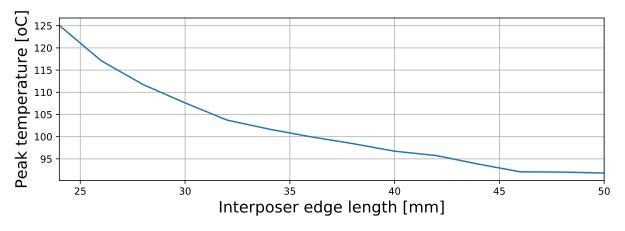

| Figure 6.8:                | Temperature of best chiplet placement for each interposer size, running Cholesky with                                                                                          |            |

|                            | Mesh network using single-cycle link without gas stations                                                                                                                      | 143        |

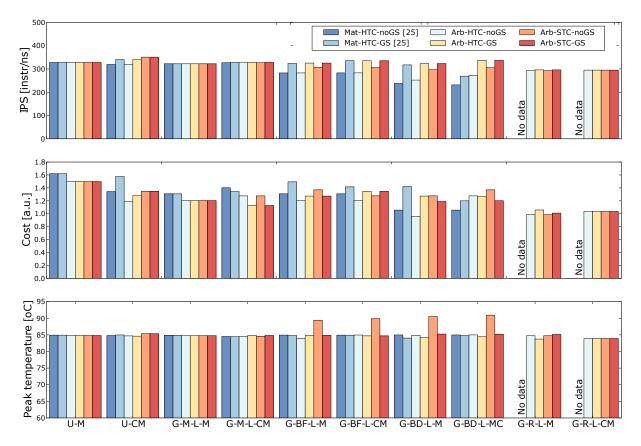

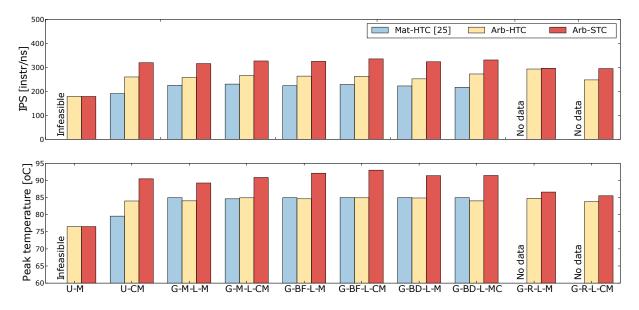

| Figure 6.9:                | Maximum performance, the corresponding cost and the corresponding peak tempera-                                                                                                |            |

|                            | ture for various networks with and without gas-station links when running Cholesky                                                                                             |            |

|                            | benchmark. Here the optimization goal is to maximize performance; the cost values                                                                                              |            |

|                            | are normalized to the cost of a 2D system                                                                                                                                      | 151        |

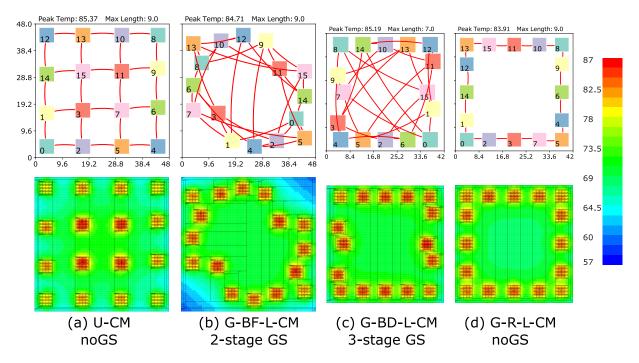

| Figure 6.10:               | Optimal chiplet placement for maximum performance and corresponding thermal                                                                                                    |            |

|                            | maps when running the <i>Cholesky</i> benchmark in 2.5D systems with different network                                                                                         |            |

| <b>D</b> ' (11)            | topologies. The figures are scaled to the interposer sizes.                                                                                                                    | 153        |

| Figure 6.11:               | Iso-cost performance and the corresponding peak temperature when running <i>Cholesky</i>                                                                                       | 154        |

| Eisen (12)                 | benchmark for various networks, while not exceeding the cost budget of a 2D system.                                                                                            | 154        |

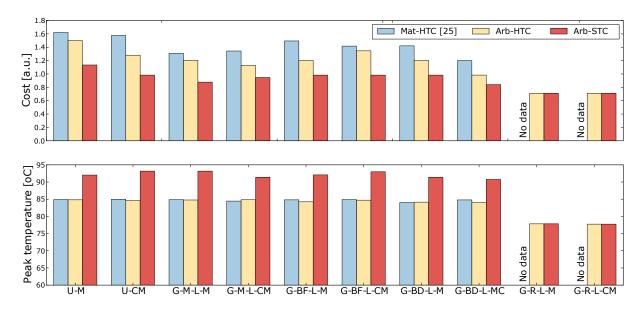

| Figure 6.12:               | Iso-performance cost and the corresponding peak temperature for each network. Here the performance is equal to the maximum performance schiaved using Mat HC CS                |            |

|                            | the performance is equal to the maximum performance achieved using <i>Mat-HC-GS</i> [25] when running <i>Cholesky</i> benchmark. The cost values are normalized to the cost of |            |

|                            | a 2D system.                                                                                                                                                                   | 155        |

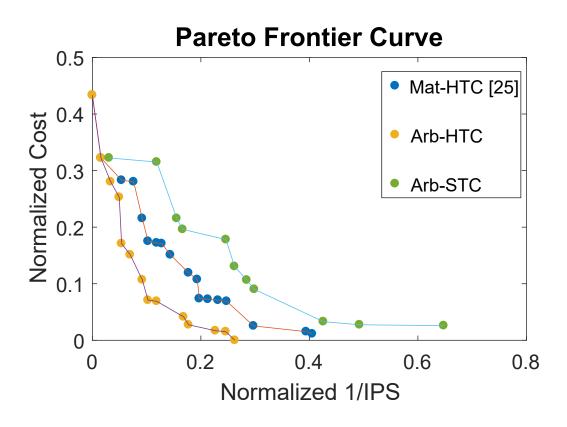

| Figure 6 13.               | Pareto Frontier Curve of normalized performance $(1/IPS)$ and normalized cost using                                                                                            | 155        |

| 1 iguie 0.15.              | <i>Mat-HTC</i> approach [25], <i>Arb-HTC</i> approach, and <i>Arb-STC</i> approach                                                                                             | 156        |

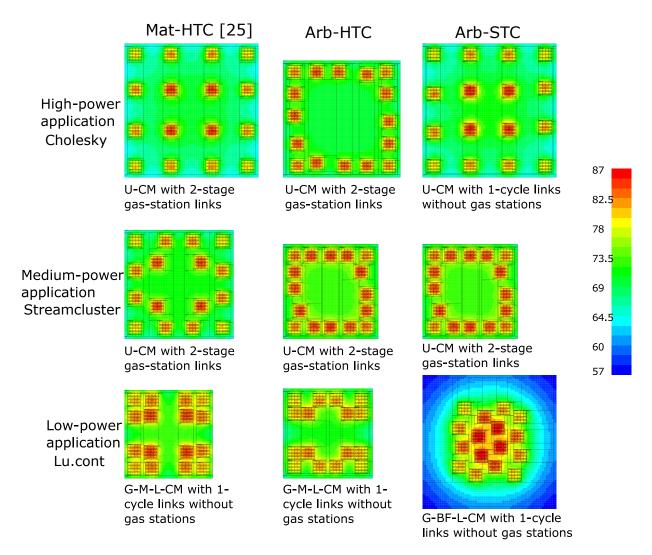

| Figure 6.14:               | Thermal maps of 2.5D systems designed for high-power, medium-power, and low-                                                                                                   | 100        |

| 0                          | power applications using <i>Mat-HTC</i> [25], <i>Arb-HTC</i> , <i>Arb-STC</i> approaches. The figures                                                                          |            |

|                            | are scaled to the interposer sizes.                                                                                                                                            | 157        |

| Figure 6.15:               | Sensitivity analysis comparing hard temperature constraint, soft temperature con-                                                                                              |            |

|                            | straints with linear function and square function, and no temperature constraint for                                                                                           |            |

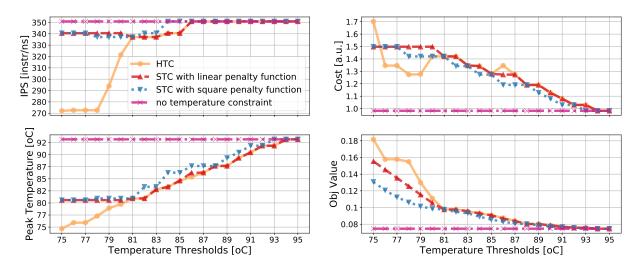

|                            | various temperature thresholds from $75-95^{\circ}C$                                                                                                                           | 160        |

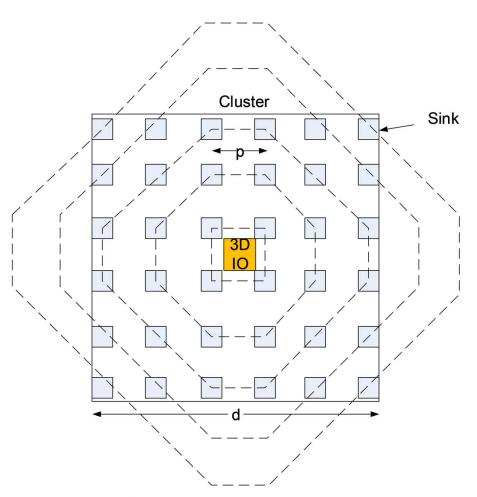

| Figure 7.1:                | Clustering the cleak domains                                                                                                                                                   | 164        |

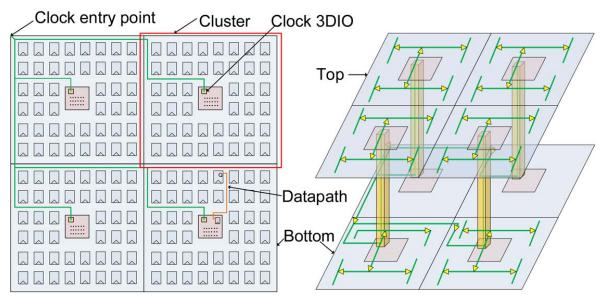

| Figure 7.1:<br>Figure 7.2: | Clustering the clock domains.                                                                                                                                                  | 164<br>166 |

| Figure 7.2:                | 3DIO/CTS directed graph.                                                                                                                                                       | 171        |

| Figure 7.4:                | Data wirelength distribution.                                                                                                                                                  | 172        |

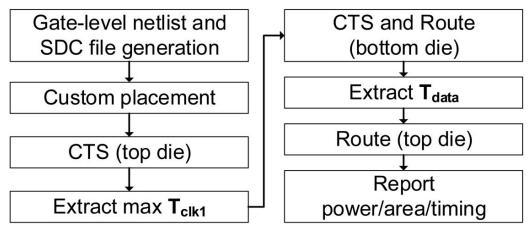

| Figure 7.5:                | Flow for synchronous clocking scheme.                                                                                                                                          | 172        |

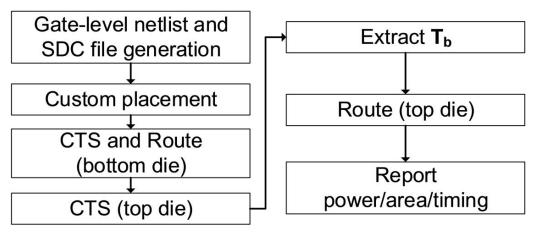

| Figure 7.6:                | Flow for source-synchronous clocking scheme.                                                                                                                                   | 178        |

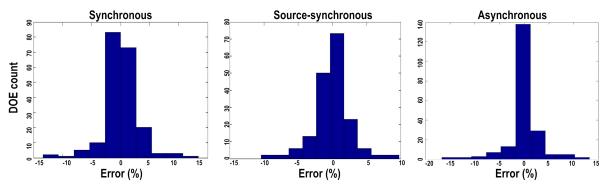

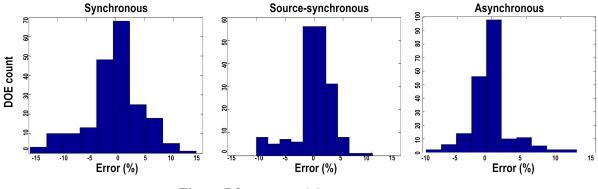

| Figure 7.7:                | Area model percentage error.                                                                                                                                                   | 180        |

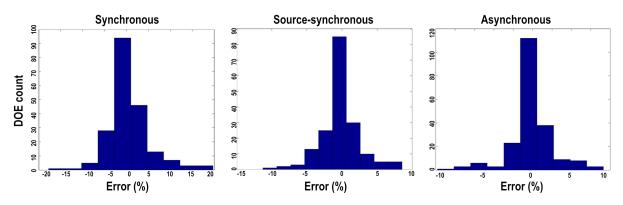

| Figure 7.8:                | Power model percentage error.                                                                                                                                                  | 180        |

| Figure 7.9:                | $F_{max}$ model percentage error                                                                                                                                               | 181        |

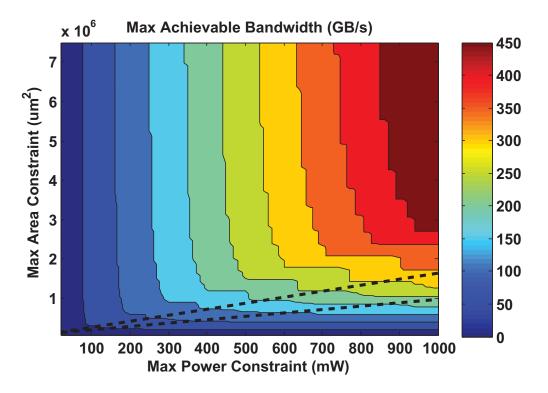

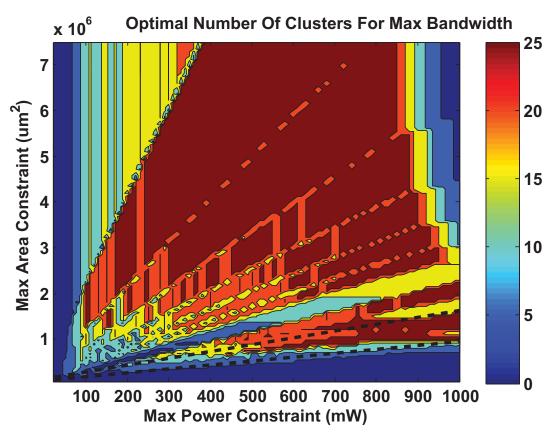

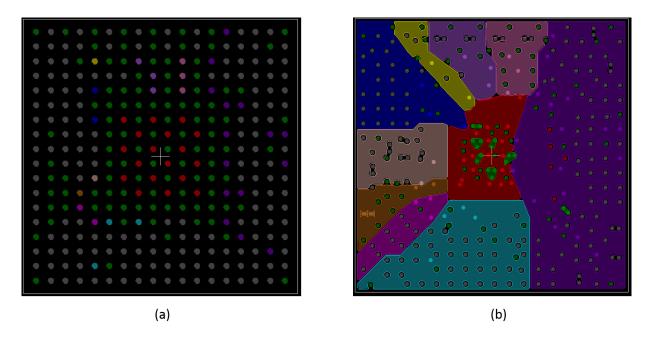

| Figure 7.10: | Maximum achievable bandwidth for given power and area constraints.                                                                                            | 182 |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

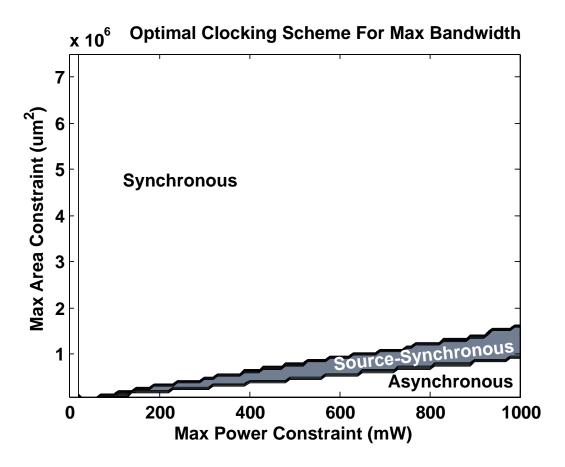

| Figure 7.11: | Guidance for synchronization scheme for given power and area constraints                                                                                      | 183 |

| Figure 7.12: | Optimal number of clusters for given power and area constraints.                                                                                              | 184 |

|              | Cluster clock frequency based on power and area constraints                                                                                                   | 185 |

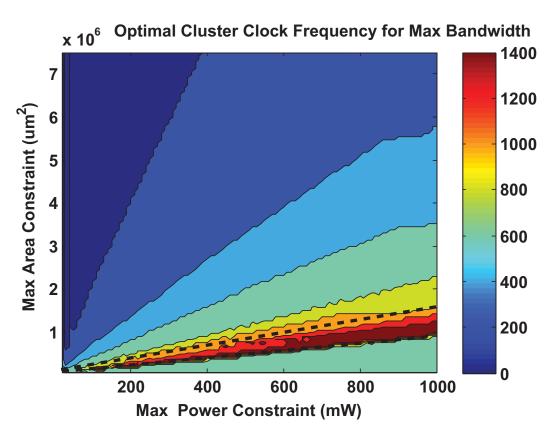

| Figure 8.1:  | (a) Original layout fragment and map of bump inductance (a.u.). (b) Perturbed (degraded) layout with several balls, metal traces and vias removed, and map of | 100 |

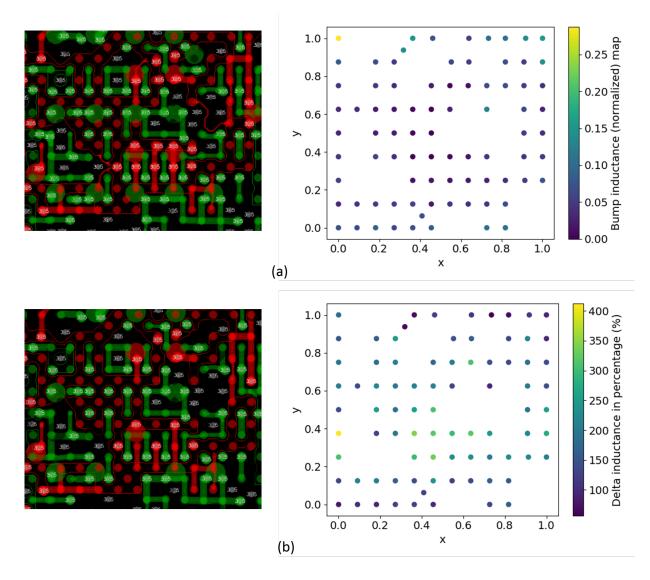

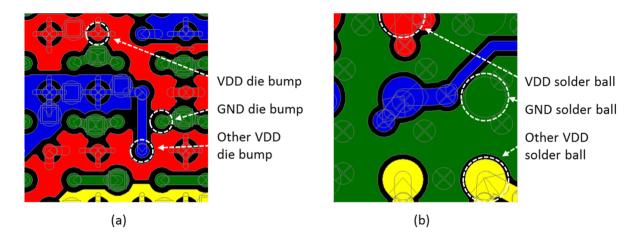

| Figure 8.2:  | percentage change in per-bump inductance relative to original layout An example of package PDN design: (a) pre-layout, and (b) post-layout. Colors            | 188 |

| Figure 6.2.  | indicate distinct rails. Figure courtesy of ASE Group.                                                                                                        | 189 |

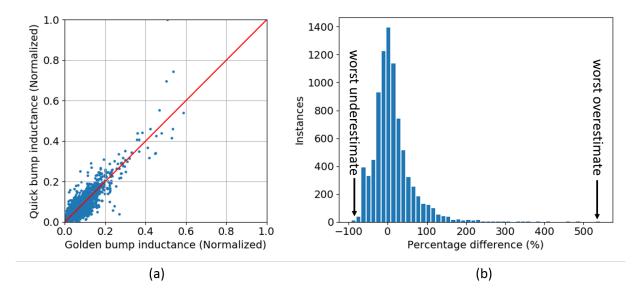

| Figure 8.3:  | Comparison between Quick tool and Golden tool. (a) Golden versus Quick bump                                                                                   |     |

|              | inductance (a.u.). (b) Histogram of percentage difference between Quick tool and                                                                              |     |

|              | Golden tool.                                                                                                                                                  | 191 |

| Figure 8.4:  | Illustration of notations in the model parameters.                                                                                                            | 192 |

| Figure 8.5:  | Illustration of piecewise-linear hybrid surrogate modeling based on ANN prediction.                                                                           | 194 |

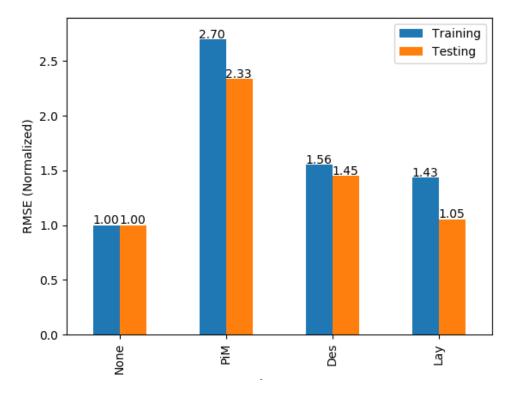

| Figure 8.6:  | Sensitivity of RMSE (a.u.) to parameter set removal                                                                                                           | 197 |

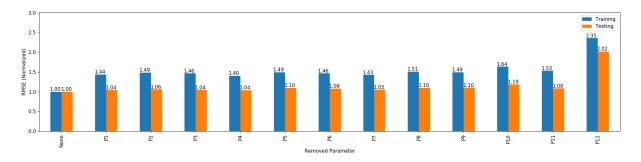

| Figure 8.7:  | Sensitivity of RMSE to individual parameter removal.                                                                                                          | 198 |

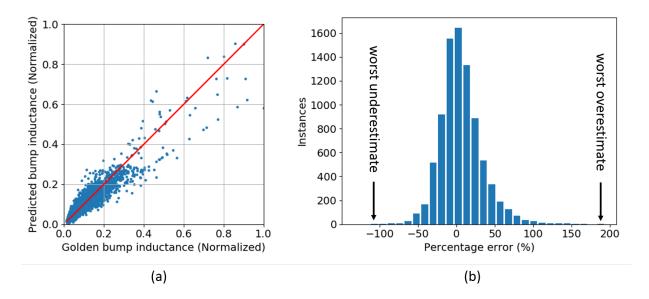

| Figure 8.8:  | Results for <i>achievable</i> bump inductance model. (a) Golden versus predicted <i>achievable</i>                                                            |     |

|              | bump inductance. (b) Percentage error histogram.                                                                                                              | 199 |

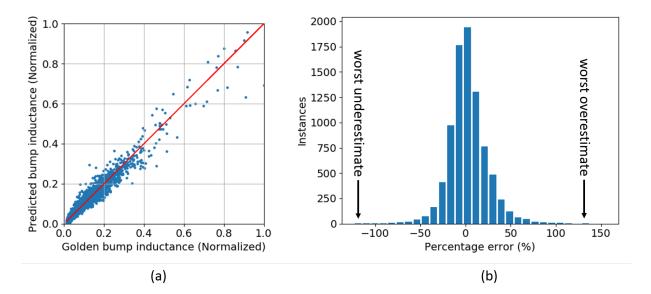

| Figure 8.9:  | Results for <i>actual</i> bump inductance model. (a) Golden versus predicted <i>actual</i> bump                                                               |     |

| C            | inductance and (b) Percentage error histogram.                                                                                                                | 199 |

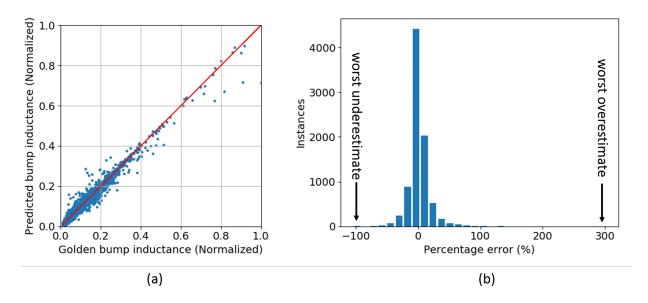

| Figure 8.10: | Results for Quick tool and Golden tool correlation model. (a) Golden versus predicted                                                                         |     |

| 0            | bump inductance. (b) Percentage error histogram.                                                                                                              | 201 |

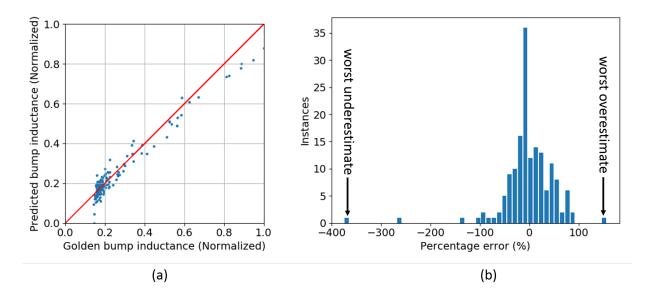

| Figure 8.11. | Results for model generality study. (a) Golden versus predicted bump inductance of                                                                            | -01 |

|              | variant design. (b) Percentage error histogram.                                                                                                               | 202 |

|              |                                                                                                                                                               |     |

# LIST OF TABLES

| Table 2.1: | PHY active dynamic power per bit for 3D configurations.                                                       | 20  |

|------------|---------------------------------------------------------------------------------------------------------------|-----|

| Table 2.2: | PHY static power for a x128 3D configuration.                                                                 | 20  |

| Table 2.3: | PHY dynamic power per bit and static power for a x64 DDR3-1600.                                               | 20  |

| Table 2.4: | PHY wakeup times from sleep and idle modes.                                                                   | 20  |

| Table 2.5: | Technology scaling for DDR3.                                                                                  | 26  |

| Table 2.6: | Case Study 1: Summary of power for server configurations using x4 4Gbit DRAMs.                                | 32  |

| Table 2.7: | Case Study 2: Summary of power for 3D configurations.                                                         | 32  |

| Table 2.8: | Case Study 3: Summary of power for BOOM configurations.                                                       | 33  |

| Table 2.9: | PCRAM IO Area.                                                                                                | 45  |

|            |                                                                                                               |     |

| Table 3.1: | Capacity projections for mobile and PC markets (source: IDC Market Survey)                                    | 55  |

| Table 3.2: | Summary of parameters of existing memory interfaces from the calculator                                       | 63  |

| Table 3.3: | Inputs and outputs of the calculator for two design examples                                                  | 66  |

| Table 4.1: | Cost of DDR3 and DDR4 DIMMs.                                                                                  | 75  |

| Table 4.2: | Typical frequencies of available DIMMs                                                                        | 75  |

| Table 4.3: | Configuration parameters of different link types.                                                             | 79  |

| Table 4.4: | Validation of termination power.                                                                              | 81  |

| Table 4.5: | Simics and USIMM parameters.                                                                                  | 90  |

| Table 4.6: | Power breakdown of baseline and cascaded channels.                                                            | 91  |

| Table 5.1: | Classification of previous work and our work. OR-Optical Routing; OP-Optical                                  |     |

|            | Placement; ER–Electrical Routing; EP–Electrical Placement; TA–Thermally-Aware;                                |     |

|            | 3D–3D-Related; NoC: NoC Topology.                                                                             | 104 |

| Table 5.2: | Notations used in the MILP.                                                                                   | 107 |

| Table 5.3: | Experimental configurations studied.                                                                          | 116 |

| Table 5.4: | Losses in PNoCs [57]                                                                                          | 117 |

| Table 6.1: | Notations used in the cross-layer co-optimization methodology.                                                | 130 |

| Table 6.2: | $\mu$ bump count, stretch-out width of $\mu$ bump region ( $w_{ubump}$ ), and $\mu$ bump area ( $A_{ubump}$ ) | 100 |

| 14010 0.2. | overhead per chiplet for different network topologies designed using repeaterless links,                      |     |

|            | 2-stage and 3-stage <i>gas-station</i> links.                                                                 | 134 |

| Table 6.3: | Technology node parameters.                                                                                   | 137 |

| Table 6.4: | Notations used in the cost oracle.                                                                            | 140 |

| Table 6.5: | Notations used in routing optimization.                                                                       | 144 |

| Table 6.6: | Inputs to routing optimization.                                                                               | 146 |

| Table 6.7: | Cross-layer vs. single-layer optimization.                                                                    | 140 |

| 1dblc 0.7. |                                                                                                               | 150 |

| Table 8.1: | Parameters used in our modeling.                                                                              | 193 |

| Table 8.2: | Description of reporting metrics.                                                                             | 195 |

| Table 8.3: | Accuracy metrics for <i>achievable</i> bump inductance model                                                  | 198 |

| Table 8.4: | Accuracy metrics for <i>actual</i> bump inductance model                                                      | 200 |

| Table 8.5: | Accuracy metrics comparison between Quick tool and our model.                                                 | 200 |

| Table 8.6: | Accuracy metrics for correlation between Quick tool and Golden tool.                                          | 201 |

#### ACKNOWLEDGMENTS

These acknowledgments may seem like the letter C. S. Lewis wrote to Lucy in his dedication of *The Lion, the Witch and the Wardrobe*. Having decided to pursue a Ph. D. while still working full-time, I have come to realize the amount of time it has taken for me to complete it, and this in turn has put into sharp relief how truly grateful I am to many people for their patience, guidance and collaboration. And I hope that this thesis is still relevant and useful for the approaches and methodologies used, and the cross-layer fundamentals of the design space explored, despite its somewhat lengthy journey to completion.

I'd first and foremost like to thank my advisor, Professor Andrew B. Kahng, whom I have been very fortunate to have guide me through my Ph. D. I have learnt many things from him about research and life in general, not the least of which has been the persistence to complete this thesis. I am grateful beyond these words for the opportunity he has provided along this road shared.

I'd like to thank my family and friends for their patience and encouragement - my wife Vanoli, my parents, Hema and Srinivas, my brother and sister-in-law, Vinay and Sunitha, and my many friends who have stood by me in various portions of this journey.

I would like to thank my present and former labmates in the UCSD VLSI CAD Laboratory, including Hyein Lee, Kwangsoo Han, Seokhyeong Kang, Kwangok Jeong, Wei-Ting Chan, Minsoo Kim, Mingyu Woo, Lutong Wang, Bangqi Xu, Siddhartha Nath, Jiajia Li and Tuck-Boon Chan. It has been amazing collaborating with them and I am grateful for their assistance, friendship and guidance.

I would like to thank my Thesis Committee (Professors Dean Tullsen, Bill Lin, Farinaz Koushanfar and Jonathan Klamkin, and Dr. Naveen Muralimanohar) for their time, support and insightful suggestions.

I would like to thank all my coauthors and collaborators, without whose help and support this thesis would not have been possible. All my coauthors have kindly approved inclusion of these publications in my thesis.

Chapter 2 contains a reprint of N. P. Jouppi, A. B. Kahng, N. Muralimanohar and V. Srinivas, "CACTI-IO: CACTI With Off-Chip Power-Area-Timing Models", *IEEE Transactions on Very Large Scale Integration Systems* 23(7) (2015). The dissertation author is a main contributor to, and a primary author of this paper. I would like to thank my coauthors Norm P. Jouppi, Andrew B. Kahng and Naveen Muralimanohar.

Chapter 3 contains a reprint of A. B. Kahng and V. Srinivas, "Mobile System Considerations for SDRAM Interface Trends", *Proc. ACM International Workshop on System-Level Interconnect Prediction*, 2011. The dissertation author is a main contributor to, and a primary author of this paper. I would like to thank my coauthor Andrew B. Kahng.

Chapter 4 contains a reprint of R. Balasubramonian, A. B. Kahng, N. Muralimanohar, A. Shafiee and V. Srinivas, "CACTI 7: New Tools for Interconnect Exploration in Innovative Off-Chip Memories", *ACM Transactions on Architecture and Code Optimization* 14(2) (2017). The dissertation author is a main contributor to this paper. I would like to thank my coauthors Rajeev Balasubramonian, Andrew B. Kahng, Naveen Muralimanohar and Ali Shafiee.

Chapter 5 contains a reprint of A. Coskun, A. Gu, W. Jin, A. J. Joshi, A. B. Kahng, J. Klamkin, Y. Ma, J. Recchio, V. Srinivas and T. Zhang, "Cross-Layer Floorplan Optimization For Silicon Photonic NoCs In Many-Core Systems", *Proc. Design, Automation and Test in Europe*, 2016, pp. 1309-1314. The dissertation author is a main contributor to this paper. I would like to thank my coauthors Ayse Coskun, Anjun Gu, Warren Jin, Ajay J. Joshi, Andrew B. Kahng, Jonathan Klamkin, Yenai Ma, John Recchio and Tiansheng Zhang.

Chapter 6 contains a reprint of A. Coskun, F. Eris, A. Joshi, A. B. Kahng, Y. Ma, A. Narayan and V. Srinivas, "Cross-Layer Co-Optimization of Network Design and Chiplet Placement in 2.5D Systems", *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, in revision. The dissertation author is a main contributor to this paper. I would like to thank my coauthors Ayse Coskun, Furkan Eris, Ajay Joshi, Andrew B. Kahng, Yenai Ma and Aditya Narayan.

Chapter 7 contains a reprint of S. Bang, K. Han, A. B. Kahng and V. Srinivas, "Clock Clustering and IO Optimization for 3D Integration", *Proc. ACM International Workshop on System-Level Interconnect Prediction*, 2015. The dissertation author is a main contributor to this paper. I would like to thank my coauthors Samyoung Bang, Kwangsoo Han and Andrew B. Kahng.

Chapter 8 contains a reprint of Y. Cao, J. Li, A. B. Kahng, A. Roy, V. Srinivas and B. Xu, "Learning-Based Prediction of Package Power Delivery Network Quality", *Proc. Asia and South Pacific Design Automation Conference*, 2019. The dissertation author is a main contributor to this paper. I would like to thank my coauthors Yi Cao, Joseph Li, Andrew B. Kahng, Abinash Roy and Bangqi Xu.

Last but definitely not least, I would like to thank Qualcomm Inc., for its invaluable support through my Ph. D., including funding it, providing me with an environment of innovation, and collaboration and support from my colleagues and my managers.

#### VITA

| 2000 | B. Tech., Electrical Engineering,<br>Indian Institute of Technology, Madras                  |

|------|----------------------------------------------------------------------------------------------|

| 2002 | M. S., Electrical Engineering,<br>University of California, Los Angeles                      |

| 2019 | Ph. D., Electrical Engineering (Computer Engineering),<br>University of California San Diego |

#### PUBLICATIONS

A. Coskun, F. Eris, A. Joshi, A. B. Kahng, Y. Ma, A. Narayan and V. Srinivas, "Cross-Layer Co-Optimization of Network Design and Chiplet Placement in 2.5D Systems," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, in revision.

Y. Cao, J. Li, A. B. Kahng, A. Roy, **V. Srinivas** and B. Xu, "Learning-Based Prediction of Package Power Delivery Network Quality," *Proc. Asia and South Pacific Design Automation Conference*, 2019, pp. 160-166.

T. Ajayi, D. Blaauw, T.-B. Chan, C.-K. Cheng, V. A. Chhabria, D. K. Choo, M. Coltella, S. Dobre, R. Dreslinski, M. Fogaa, S. Hashemi, A. Hosny, A. B. Kahng, M. Kim, J. Li, Z. Liang, U. Mallappa, P. Penzes, G. Pradipta, S. Reda, A. Rovinski, K. Samadi, S. S. Sapatnekar, L. Saul, C. Sechen, **V. Srinivas**, W. Swartz, D. Sylvester, D. Urquhart, L. Wang, M. Woo and B. Xu, "OpenROAD: Toward a Self-Driving, Open-Source Digital Layout Implementation Tool Chain," *Proc. Government Microcircuit Applications and Critical Technology Conference*, 2019, pp. 1105-1110.

R. Bairamkulov, K. Xu, E. G. Friedman, M. Popovich, J. Ochoa and V. Srinivas, "Versatile Framework for Power Delivery Exploration," R. Bairamkulov, K. Xu, E. G. Friedman, M. Popovich, J. Ochoa and V. Srinivas, *Proc. ISCAS*, 2018, pp. 1-5.

A. Coskun, F. Eris, A. Joshi, A. B. Kahng, Y. Ma and V. Srinivas, "A Cross-Layer Methodology for Design and Optimization of Networks in 2.5D Systems," *Proc. IEEE/ACM International Conference on Computer-Aided Design*, 2018, pp. 101:1-101:8.

R. Balasubramonian, A. B. Kahng, N. Muralimanohar, A. Shafiee and **V. Srinivas**, "CACTI 7: New Tools for Interconnect Exploration in Innovative Off-Chip Memories," *ACM Transactions on Architecture and Code Optimization* 14(2) (2017), pp. 14:1-14:25.

J. L. Abellan, A. K. Coskun, A. Gu, W. Jin, A. Joshi, A. B. Kahng, J. Klamkin, C. Morales, J. Recchio, **V. Srinivas** and T. Zhang, "Adaptive Tuning of Photonic Devices in a Photonic NoC Through Dynamic Workload Allocation," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems* 36(5) (2017), pp. 801-814.

A. Coskun, A. Gu, W. Jin, A. J. Joshi, A. B. Kahng, J. Klamkin, Y. Ma, J. Recchio, V. Srinivas and T. Zhang, "Cross-Layer Floorplan Optimization For Silicon Photonic NoCs In Many-Core Systems," *Proc. Design, Automation and Test in Europe*, 2016, pp. 1309-1314.

N. P. Jouppi, A. B. Kahng, N. Muralimanohar and V. Srinivas, "CACTI-IO: CACTI With Off-Chip Power-Area-Timing Models," *IEEE Transactions on Very Large Scale Integration Systems* 23(7) (2015), pp. 1254-1267.

S. Bang, K. Han, A. B. Kahng and V. Srinivas, "Clock Clustering and IO Optimization for 3D Integration," *Proc. ACM International Workshop on System-Level Interconnect Prediction*, 2015, pp. 1-8.

N. Jouppi, A. B. Kahng, N. Muralimanohar and V. Srinivas, "CACTI-IO: CACTI with Off-chip Power-Area-Timing Models," *Proc. IEEE/ACM International Conference on Computer-Aided Design*, 2012, pp. 294-301.

A. B. Kahng and V. Srinivas, "Mobile System Considerations for SDRAM Interface Trends," *Proc. ACM International Workshop on System-Level Interconnect Prediction*, 2011, pp. 1-8.

V. J. Vijayakrishna, V. Srinivas, N. DasGupta and A. DasGupta, "Unified Analytical Model of HEMTs for Analogue and Digital Applications," *IEE Proceedings on Circuits, Devices and Systems* 152(5) (2005), pp. 425-432.

**V. Srinivas**, K. J. Bois, D. Knee, D. Quint, M. F. Chang and I. Verbauwhede, "Gigabit Simultaneous Bi-directional Signaling Using DS-CDMA," *Proc. EPEP*, 2002, pp. 15-18.

A. DasGupta, V. Srinivas, V. P. Reddy and N. DasGupta, "A New Unified Analytical Model for I-V characteristics of HEMTs," *10th International Conference on the Physics of Semiconductor Devices*, 1999, pp. 467-474.

#### ABSTRACT OF THE DISSERTATION

#### **Cross-Layer Pathfinding for Off-Chip Interconnects**

by

Vaishnav Srinivas

#### Doctor of Philosophy in Electrical Engineering (Computer Engineering)

University of California San Diego, 2019

Andrew B. Kahng, Chair

Off-chip interconnects for integrated circuits (ICs) today induce a diverse design space, spanning many different applications that require transmission of data at various bandwidths, latencies and link lengths. Off-chip interconnect design solutions are also variously sensitive to system performance, power and cost metrics, while also having a strong impact on these metrics. The costs associated with off-chip interconnects include die area, package (PKG) and printed circuit board (PCB) area, technology and bill of materials (BOM). Choices made regarding off-chip interconnects are fundamental to product definition, architecture, design implementation and technology enablement. Given their *cross-layer* impact, it is imperative that a cross-layer approach be employed to architect and analyze off-chip interconnects up front, so that a top-down design flow can comprehend the cross-layer impacts and correctly assess the system

performance, power and cost tradeoffs for off-chip interconnects. Chip architects are not exposed to all the tradeoffs at the physical and circuit implementation or technology layers, and often lack the tools to accurately assess off-chip interconnects. Furthermore, the collaterals needed for a detailed analysis are often lacking when the chip is architected; these include circuit design and layout, PKG and PCB layout, and physical floorplan and implementation.

To address the need for a framework that enables architects to assess the system-level impact of off-chip interconnects, this thesis presents power-area-timing (PAT) models for off-chip interconnects, optimization and planning tools with the appropriate abstraction using these PAT models, and die/PKG/PCB co-design methods that help expose the off-chip interconnect cross-layer metrics to the die/PKG/PCB design flows. Together, these models, tools and methods enable cross-layer optimization that allows for a top-down definition and exploration of the design space and helps converge on the correct off-chip interconnect implementation and technology choice. The tools presented cover off-chip memory interfaces for mobile and server products, silicon photonic interfaces, 2.5D silicon interposers and 3D through-silicon vias (TSVs). The goal of the cross-layer framework is to assess the key metrics of the interconnect (such as timing, latency, active/idle/sleep power, and area/cost) at an appropriate level of abstraction by being able to do this across layers of the design flow. In additional to signal interconnect, this thesis also explores the need for such cross-layer pathfinding for power distribution networks (PDN), where the system-on-chip (SoC) floorplan and pinmap must be optimized before the collateral layouts for PDN analysis are ready.

Altogether, the developed cross-layer pathfinding methodology for off-chip interconnects enables more rapid and thorough exploration of a vast design space of off-chip parallel and serial links, inter-die and inter-chiplet links and silicon photonics. Such exploration will pave the way for off-chip interconnect technology enablement that is optimized for system needs. The basis of the framework can be extended to cover other interconnect technology as well, since it fundamentally relates to system-level metrics that are common to all off-chip interconnects.

# Chapter 1

# Need for Cross-Layer Off-Chip Interconnect Optimization and Exploration

Ever-increasing compute requirements have led to a consequent increase in off-chip interconnect bandwidth. Power and cost considerations have led to various advancements in interconnect technology to address this need for higher bandwidths. These include advanced signaling schemes on traditional interconnect on a printed circuit board (PCB), 2.5D and 3D interconnect technology, and silicon photonic interconnects. The tradeoffs for performance, power and cost of off-chip interconnects are often complex and subtle, involving various layers of abstraction in the design flow to help assess them. At the same time, the tradeoffs are so fundamental for system metrics and architecture that they must be considered up front in the design cycle of a chip. This requires new enablement of *system-level pathfinding* for off-chip interconnects, to allow reasonably accurate assessment of system-level metrics early in the design cycle. System-level pathfinding requires a framework wherein the key cross-layer aspects of the off-chip interconnect are modeled and exposed at a suitable level of abstraction. Such a framework would allow architects to model and optimize the off-chip interconnect based on the system needs of performance, power and cost. The key metrics for the off-chip interconnect include (i) timing, latency and bandwidth to evaluate system performance; (ii) active, idle and sleep currents and supply voltage to evaluate system power; and (iii) die area, die technology, bump and ball cost, package (PKG) and PCB area, stackup and bill of materials (BOM) cost to evaluate system cost. In addition, thermal and power distribution network (PDN) considerations are additional metrics that are important. Evaluating these metrics requires a cross-layer model and assessment, as they are dependent on the architecture, design, implementation and technology of the off-chip interconnects.

This thesis presents the models, tools and methods to address the need for cross-layer off-chip interconnect optimization and exploration. The models include Power-Area-Timing (PAT) and PDN impedance models. The tools and methods presented use such models for the key metrics for the off-chip interconnect enumerated above at a suitable level of abstraction such that the model captures the key tradeoffs within the physical design, circuit design and technology layers, while still being able to assess the metrics without the detailed collaterals of design and layout of the die, PKG and PCB. The modeling methods presented here employ various techniques to achieve the suitable level of abstraction, including directed graphs, analytical models, lookup tables, metamodeling and machine learning techniques. The tools include optimization tools and planning tools, including stand-alone excel frameworks, scripts to assist existing flows, including place-and-route (P&R) and floorplanning, global optimizers, and application program interfaces (APIs) that allow for easy integration into higher-level simulators. These tools integrate into die, PKG and PCB design flows for floorplanning, package bump and ball planning and assignment, interface and PDN definition, and interconnect technology exploration. As described below, the chapters of this thesis cover different types of interconnects, the cross-layer challenges that each present, as well as the tools and methods built to address these challenges and enable off-chip interconnect optimization and exploration.

Shown in Figure 1.1 is the organization and scope of the chapters of this thesis. The columns show the various interconnect types studied, including memory interconnect, 2.5D, 3D, photonic interconnect, as well as PDN which forms a key piece of the connections off-chip. The rows show the system-level metrics and considerations covered, including PPA+Cost (power, performance, area and cost), thermal, HW/SW (hardware/software) co-design for off-chip interconnects, and die/PKG/PCB co-design. These are the key system-level metrics and considerations impacted by off-chip interconnect, including the need

for co-design of the system-on-chip (SoC) with the PKG/PCB and runtime considerations for off-chip interconnects. Runtime considerations for off-chip interconnect include off-chip bandwidth and latency management at runtime, workload allocation, and thermal and PDN mitigation techniques. Die/PKG/PCB co-design is strongly connected with off-chip interconnect as the interactions between the three respective design flows largely involve off-chip interconnect definition and design.

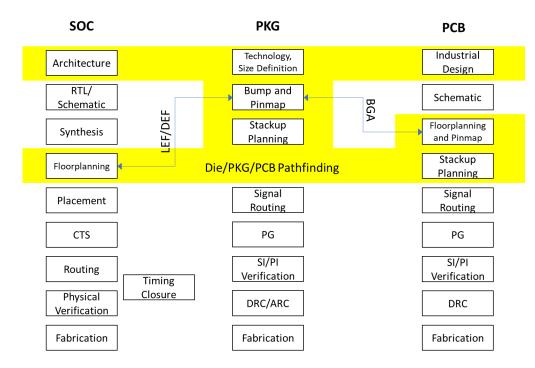

Various aspects of the cross-layer pathfinding framework for off-chip interconnect tie in with die/PKG/PCB co-design. Floorplanning and pin planning, including bumps and balls, are key aspects that define the top-down configuration, including the bandwidth, capacity/loading, latency, bus width, signaling and clocking. The interconnect technology is also a key die/PKG/PCB co-design aspect, as the technology roadmap for the PKG and PCB drive the interface definition. In addition to the signal interconnect, PDN exploration is crucial, as a large part of the PKG and PCB are dedicated for PDN. Figure 1.2 shows the design flows for SoC, PKG and PCB. The portion highlighted in yellow is where the methods and tools presented in this thesis fit and enable die/PKG/PCB co-design. The SoC flow covers an RTL (register-transfer level) to GDS (graphic data system) type flow, with the architecture definition having been made before the RTL definition. The PKG and PCB flows start from the technology and size definition and industrial design. The tools and methods in this thesis aid in connecting the dots between the three flows, especially from architecture to pinmap, floorplanning and PKG/PCB definition. They consider the key system metrics that affect die/PKG/PCB co-design, including the thermal, signal and power integrity impact, in addition to performance, power, area and cost.

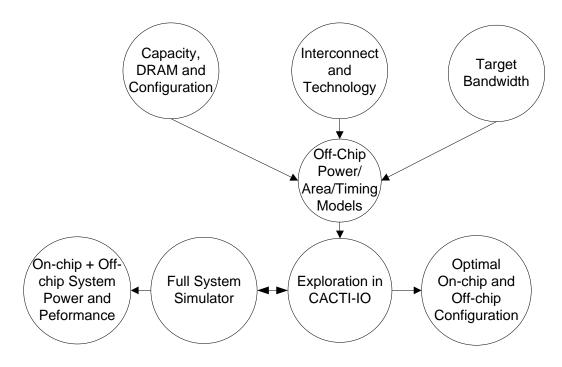

Chapter 2 describes a tool that enables memory interface exploration. Specifically, the chapter presents CACTI-IO, an extension to CACTI [171] that includes power, area, and timing models for the IO and PHY of the off-chip memory interface for various server and mobile configurations. CACTI-IO enables design space exploration of the off-chip IO along with the DRAM and cache parameters. We describe the models added and four case studies that use CACTI-IO to study the tradeoffs between memory capacity, bandwidth, and power. The case studies show that CACTI-IO helps (i) provide IO power numbers that can be fed into a system simulator for accurate power calculations; (ii) optimize off-chip configurations including the bus width, number of ranks, memory data width, and off-chip bus frequency, especially for novel buffer-based topologies; and (iii) enable architects to quickly explore new interconnect technologies,

|                          |         | Interconnect Types |    |          |     |  |  |  |  |  |

|--------------------------|---------|--------------------|----|----------|-----|--|--|--|--|--|

| System Metric            | Memory  | 2.5D               | 3D | Photonic | PDN |  |  |  |  |  |

| Die/PKG/PCB<br>Co-Design | 4       | 6                  |    |          | 8   |  |  |  |  |  |

| PPA+Cost                 | 2, 3, 4 | 6                  | 7  | 5        | 8   |  |  |  |  |  |

| Thermal                  |         | 6                  |    | 5        |     |  |  |  |  |  |

| HW/SW<br>Co-Design       | 2, 4    | 6                  |    | 5        |     |  |  |  |  |  |

# Mapping of Thesis Chapters to System Metrics and Interconnect Types

Figure 1.1: Organization of this thesis.

Figure 1.2: Die/PKG/PCB co-design and pathfinding.

including 3D interconnect. We find that buffers on board and 3D technologies offer an attractive design space involving power, bandwidth, and capacity when appropriate interconnect parameters are deployed.

Chapter 3 includes an early work focused on mobile memory interfaces that connect the SoC to the SDRAM (Synchronous Dynamic Random Access Memory). A variety of interconnect technologies and standards (dual inline memory modules (DIMMs), multi-chip package (MCP), package on package (POP), stacked-die and 3D-stack) enable a controller integrated circuit (IC) to communicate with an external SDRAM, or with multiple SDRAMs over a shared interconnect. Low-power requirements have driven mobile controllers to mobile-SDRAM low-power double data rate (LPDDR) memory solutions. However, LPDDR configurations do not scale to match the throughput and capacity requirements of mobile processors, or of emerging tablet products that bring new and divergent tradeoffs among memory subsystem metrics. As a result, identifying the memory configuration best suited to a given mobile application becomes quite challenging. This chapter considers some of the basic methods and approaches to enable a cross-layer framework for mobile memory interfaces. We highlight considerations that apply when choosing a particular memory configuration for a mobile processor based on capacity, throughput, latency, power, cost and thermal concerns. Further, we distinguish various choices according to interconnect implementation and performance, including power and timing in the IO and interconnect. To do this, we develop a three-part framework: (i) driving questions in the form of a *decision tree*; (ii) a *calculator* that projects power and timing for mobile IO implementations; and (iii) propagated top-down requirements and bottom-up capabilities that distinguish interconnect implementations.

Historically, server designers have opted for simple memory systems by picking one of a few commoditized DDR memory products. We are already witnessing a major upheaval in the off-chip memory hierarchy, with the introduction of many new memory products – buffer-on-board (BoB), latency-reduced DIMM (LRDIMM), hybrid memory cube (HMC), high bandwidth memory (HBM), and non-volatile memories (NVMs) to name a few. Chapter 4 extends CACTI-IO to custom memory solutions for server designs. We use the resulting capability to explore and define two new memory solutions: (i) we introduce a new relay-on-board chip that partitions a DDR channel into multiple cascaded channels; and (ii) we design a custom DIMM to reduce energy and improve performance, where the data channel is split into three narrow parallel channels and the on-DIMM interconnects are operated at a lower frequency. In

addition, this allows us to design a two-tier error protection strategy that reduces data transfers on the interconnect. The cascaded channel and narrow channel architectures serve as case studies for the new tool, and show the potential for benefit from re-organizing basic memory interconnects.