# **UC San Diego**

# **UC San Diego Electronic Theses and Dissertations**

#### **Title**

Manufacturing-aware physical design techniques

### **Permalink**

https://escholarship.org/uc/item/33458506

#### **Author**

Sharma, Puneet

### **Publication Date**

2007

Peer reviewed|Thesis/dissertation

## UNIVERSITY OF CALIFORNIA, SAN DIEGO

Manufacturing-Aware Physical Design Techniques

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical Engineering (Computer Engineering)

by

Puneet Sharma

### Committee in charge:

Professor Andrew B. Kahng, Chair Professor Chung-Kuan Cheng Professor Rajesh Gupta Professor Tajana Simunic Rosing Professor Yuan Taur

Copyright ©

Puneet Sharma, 2007

All rights reserved.

| The dissertation of Puneet Sharma is approved, and it is |

|----------------------------------------------------------|

| acceptable in quality and form for publication on micro- |

| film:                                                    |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

| Chair                                                    |

University of California, San Diego

2007

To my loving parents, without whose support, encouragement, and sacrifices, this thesis would not have been possible.

## TABLE OF CONTENTS

|    | Signature Page                                                  | iii                                                     |

|----|-----------------------------------------------------------------|---------------------------------------------------------|

|    | Dedication                                                      | iv                                                      |

|    | Table of Contents                                               | v                                                       |

|    | List of Figures                                                 | iii                                                     |

|    | List of Tables                                                  | iv                                                      |

|    | Acknowledgments                                                 | ⁄ii                                                     |

|    | Vita and Selected Publications                                  | ťΧ                                                      |

|    | Abstract                                                        | κiii                                                    |

| I  | Introduction                                                    | 1<br>2<br>3<br>4<br>8                                   |

|    | B. Yield and Sources of Variability C. Design for Manufacturing | 8<br>11<br>12<br>14<br>15<br>15<br>22<br>24<br>28<br>31 |

| II | A. Introduction                                                 | 36<br>36<br>38<br>41<br>47<br>50<br>55<br>50            |

|    | Pitch Variation                                                 | 53                                                      |

|     | 1. Detailed Placement                                       |

|-----|-------------------------------------------------------------|

|     | 2. Assessing Leakage Impact of Detailed Placement 6         |

|     | 3. Leakage Optimization                                     |

|     | 4. Experimental Study                                       |

|     | D. Aberration-Aware Timing Analysis                         |

|     | 1. Methodology                                              |

|     | 2. Experimental Study                                       |

|     | E. Conclusions                                              |

|     | F. Acknowledgments                                          |

| III | STI Stress-Aware Analysis and Optimization                  |

|     | A. Introduction                                             |

|     | B. Modeling of STI Width-Dependent Stress                   |

|     | C. Stress-Aware Timing Analysis                             |

|     | 1. Traditional SPICE-Based Timing Analysis                  |

|     | 2. STI Stress-Aware Timing Analysis                         |

|     | 3. Alternative Flow                                         |

|     | D. Timing Optimization                                      |

|     | 1. Active Layer (RX) Fill Insertion                         |

|     | 2. Intra-Row Placement Optimization                         |

|     | E. Experimental Study                                       |

|     | 1. Experimental Setup                                       |

|     | 2. Experimental Results                                     |

|     | F. Conclusions                                              |

|     | G. Acknowledgments                                          |

| IV  | Enhancing Design Robustness to Gate Length Variations       |

|     | A. Introduction                                             |

|     | B. Cell-Level Gate Length Biasing                           |

|     | 1. Library Generation                                       |

|     | 2. Optimization for Leakage                                 |

|     | C. Transistor-Level Gate Length Biasing                     |

|     | 1. Library Generation                                       |

|     | 2. Optimization for Leakage                                 |

|     | D. Experiments and Results                                  |

|     | 1. Leakage Reduction                                        |

|     | 2. Manufacturability and Process Effects                    |

|     | 3. Process Variability                                      |

|     | 4. Leakage Reduction from Transistor-Level Biasing          |

|     | E. Impact of Biasing on Threshold Voltage Selection         |

|     | 1. Simultaneous Threshold Voltage Assignment and Biasing 14 |

|     | 2. Threshold Voltage Customization                          |

|    | 3. Experiments and Results                                     | 148 |

|----|----------------------------------------------------------------|-----|

|    | F. Gate Length Biasing Using Lagrangian Relaxation             | 155 |

|    | 1. Nomenclature and Models                                     | 156 |

|    | 2. Lagrangian Relaxation-Based Solution                        | 158 |

|    | 3. Computational Experience                                    |     |

|    | G. On Synthetic Benchmarks with Known Upper Bounds             | 162 |

|    | 1. Chain Eye Chart                                             |     |

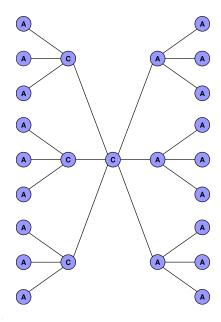

|    | 2. Star Eye Chart                                              |     |

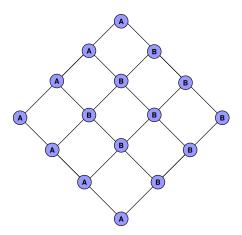

|    | 3. Mesh Eye Chart                                              | 166 |

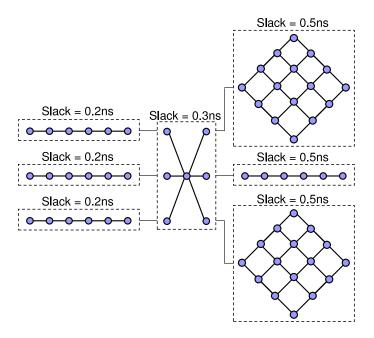

|    | 4. Hybrid Testcases                                            |     |

|    | H. Conclusions                                                 |     |

|    | I. Acknowledgments                                             | 170 |

| V  | Reducing CMP Variability Through Fill Insertion                | 171 |

|    | A. Introduction                                                |     |

|    | B. FEOL Fill for Improved Planarity                            | 173 |

|    | 1. Background                                                  |     |

|    | 2. Motivations and Objectives of Fill Insertion                |     |

|    | 3. Bi-criteria Formulation and Optimization for Fill Insertion | 179 |

|    | 4. Nitride Maximization Formulation and Optimization           | 181 |

|    | 5. Experimental Study                                          | 190 |

|    | C. On Capacitive Impact of Floating Fill                       | 195 |

|    | 1. Background                                                  |     |

|    | 2. Terminology and Assumptions                                 | 202 |

|    | 3. Foundations                                                 | 203 |

|    | 4. Study of Capacitance Impact of Fill                         | 205 |

|    | 5. Validation                                                  |     |

|    | D. Conclusions                                                 | 216 |

|    | E. Acknowledgments                                             |     |

| VI | Conclusions                                                    | 221 |

|    | Ribliography                                                   | 22/ |

## LIST OF FIGURES

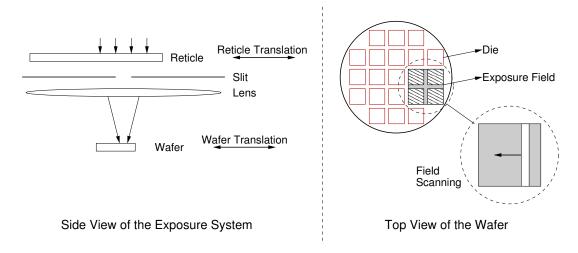

| Figure I.1:          | Schematic of a step-and-scan wafer stepper                                                                                                                                                     | ţ  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

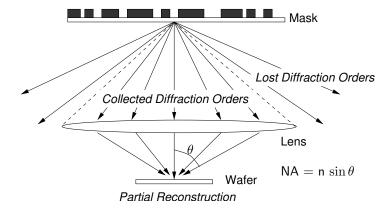

| _                    | Features on the mask cannot be completely reconstructed liffraction                                                                                                                            | (  |

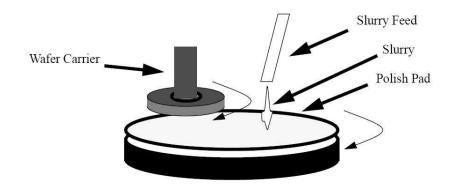

| Figure I.3:          | Equipment used for CMP [108]                                                                                                                                                                   | 16 |

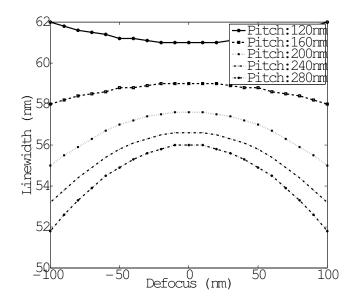

| different<br>defocus | Variation of simulated on-silicon linewidth with defocus for pitches for a 65nm technology. Linewidth increases with for dense (small pitch) patterns, and decreases for sparse itch) patterns | 39 |

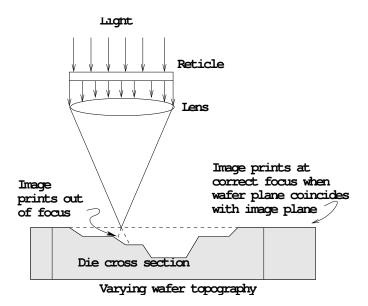

| uniform              | A vertical cross section of a wafer showing topography non-<br>ity. Focus variation due to non-planar wafer topography is<br>ed                                                                | 40 |

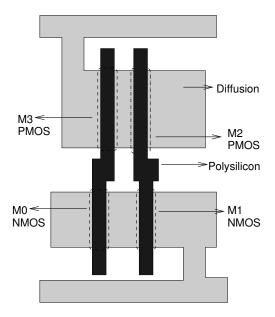

| polysilic            | Layout of a 2-input NOR gate in 90nm technology with on and diffusion layers only. Devices M0, M1, M2 and M3 led on the layout                                                                 | 4. |

| _                    | Linewidth variations induced by lens aberration for differs in a lens field                                                                                                                    | 43 |

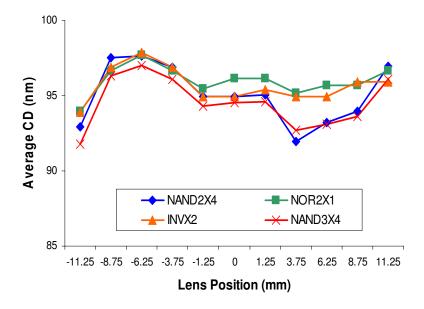

| ~                    | Average linewidth varies across the lens field; the range of ation for the NAND2X4 cell is 8nm                                                                                                 | 44 |

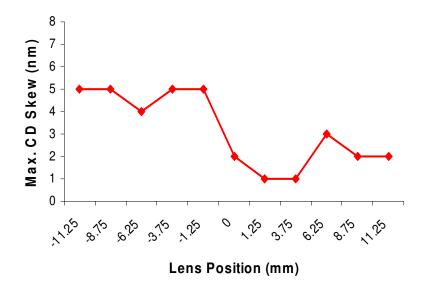

| Figure II.6:         | Maximum linewidth skew among all gates in NAND2X4 cell.                                                                                                                                        | 45 |

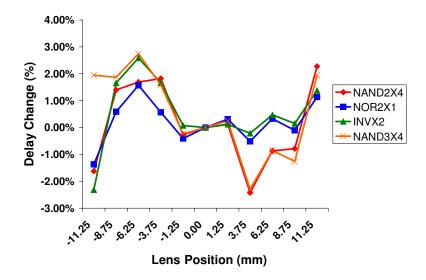

| ~                    | Change in average arc delay with lens position with respect r of the lens                                                                                                                      | 46 |

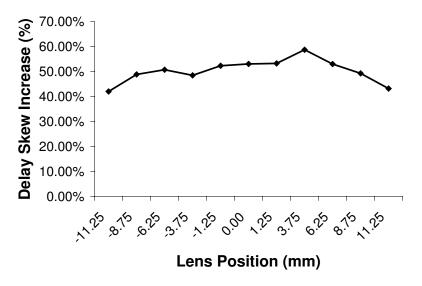

| delays o             | Percentage increase in delay skew (maximum difference in f all timing arcs) of the NAND2X4 cell as lens position is , relative to the maximum delay skew of nominal (or drawn)                 | 40 |

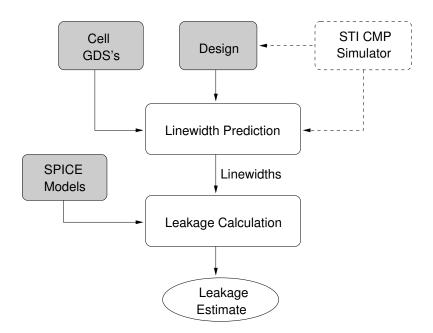

| Figure II.9:         | Our defocus-aware leakage estimation methodology                                                                                                                                               | 51 |

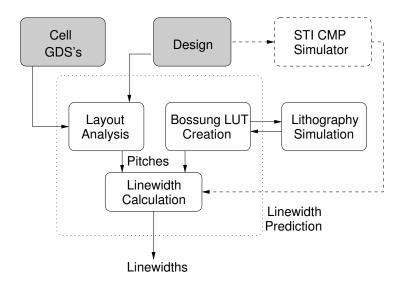

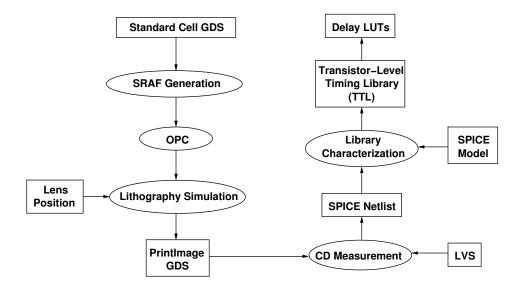

| Figure II.10:        | The proposed linewidth prediction flow                                                                                                                                                         | 52 |

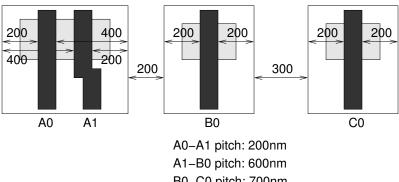

| Figure II.11: Pitch computation from a design layout. Nominal linewidth of features is $100nm$                                                                                                                                                        | ,4         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

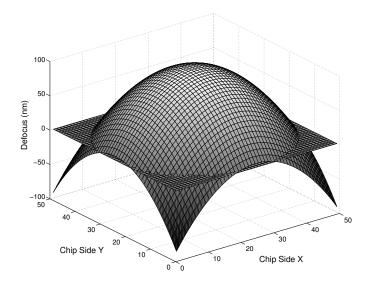

| Figure II.12: Die topography used in our experiments. Maximum height is $100nm$ higher than nominal at the center and decreases quadratically with distance from the center to become $100nm$ below nominal at the die corners                        | 57         |

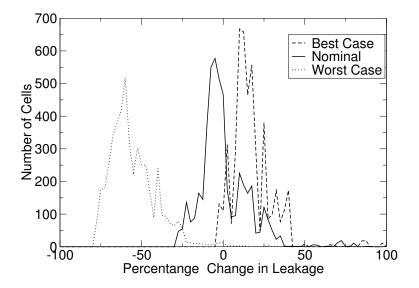

| Figure II.13: Distribution of percentage change in leakage estimated with the defocus-aware topography-aware flow with respect to the traditional flow for testcase $c6288$ for the three corners 6                                                   | 50         |

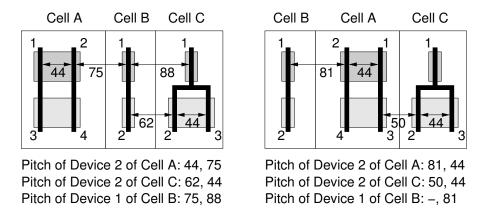

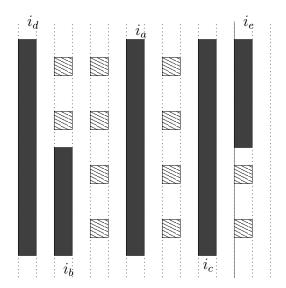

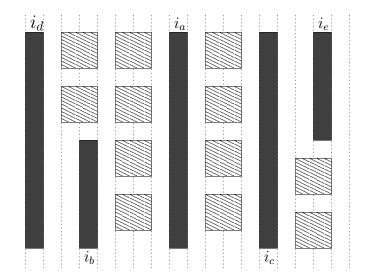

| Figure II.14: Detailed placement affects device pitches. Two placements of three cells in a row, and the device pitches, are shown 6                                                                                                                  | ;7         |

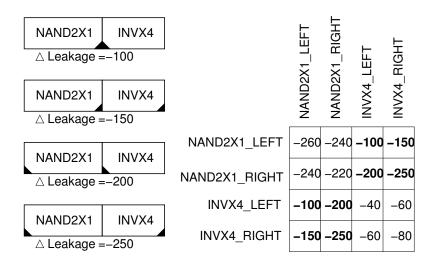

| Figure II.15: Creation of $\Delta$ leakage matrix $L$ . The bold entries are found by placing NAND2X1 and INVX4 next to each other. Non-bold entries are found by placing NAND2X1 next to another NAND2X1, and by placing INVX4 next to another INVX4 | <b>'</b> ( |

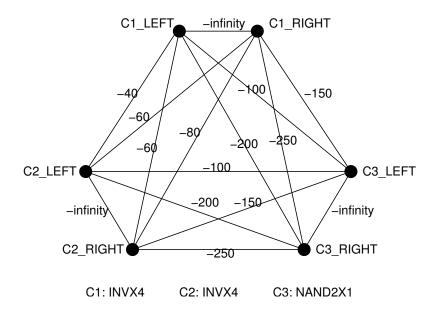

| Figure II.16: Creation of the graph for three cells C1, C2, and C3 7                                                                                                                                                                                  | '1         |

| Figure II.17: Detailed placement pseudo-code for leakage optimization 7                                                                                                                                                                               | 6          |

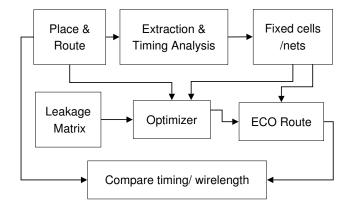

| Figure II.18: Our experimental flow                                                                                                                                                                                                                   | 7          |

| Figure II.19: Aberration-aware timing analysis and its flow 8                                                                                                                                                                                         | ;4         |

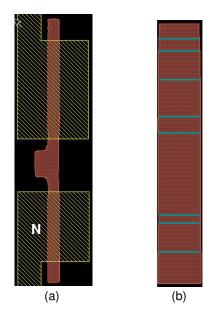

| Figure II.20: Polygon generation for CD measurement: (a) result of Print-Image simulation of an inverter, and (b) rectilinearized polygon representation of a gate device in the region N of (a) 8                                                    | :6         |

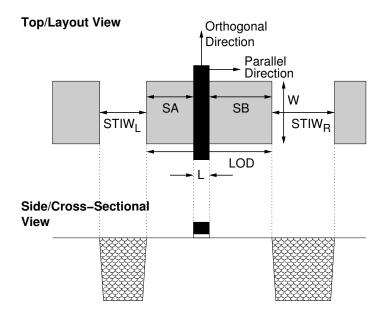

| Figure III.1: Various stress-related layout parameters. Parallel and orthogonal distances with respect to a transistor are also indicated 9                                                                                                           | 5          |

| Figure III.2: Instantiation of device-level models in a standard-cell SPICE netlist. The parameters added in BSIM 4.3.0 to partially model stress are shown in <b>bold</b>                                                                            | Ĵξ         |

| Figure III.3: Critical paths instantiate cell-level netlists which instantiate device-level models. Our modifications to the traditional flow to model STI width-dependent stress are shown in <b>bold</b> 10                                         | )(         |

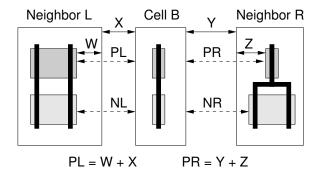

| Figure III.4: Calculation of parameters PL, PR, NL, and NR from intercell spacings and active to cell boundary spacings                                                                                                                | 101 |

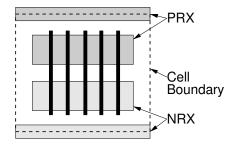

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure III.5: A generic standard cell with polysilicon, positive active regions, negative active regions, and cell boundary shown                                                                                                      | 103 |

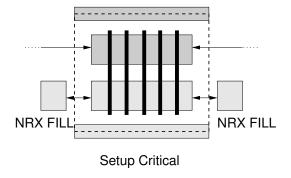

| Figure III.6: The generic cell of Figure III.5 optimized with fill insertion for setup criticality                                                                                                                                     | 104 |

| Figure III.7: A row of standard cells after active-layer fill insertion for setup time improvement. Cells patterned with diagonal lines are the setup-critical cells and solidly-filled rectangles are the inserted active-layer fills | 104 |

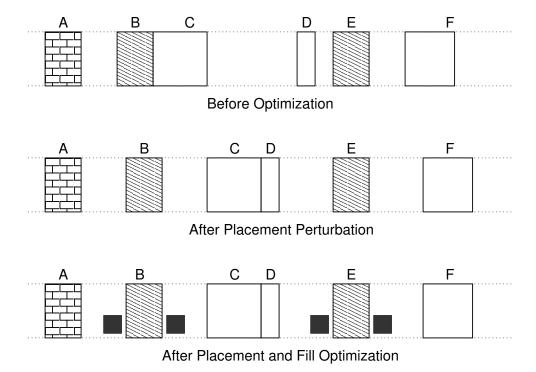

| Figure III.8: Pseudo-code for intra-row placement optimization                                                                                                                                                                         | 107 |

| Figure III.9: Placement change and fill insertion for setup time optimization. A standard-cell row is shown before optimization, after placement perturbation, and after fill insertion                                                | 108 |

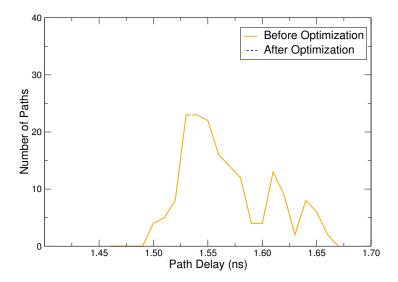

| Figure III.10: Path delay histograms for the top 200 critical paths of test-case AES before and after optimization                                                                                                                     | 113 |

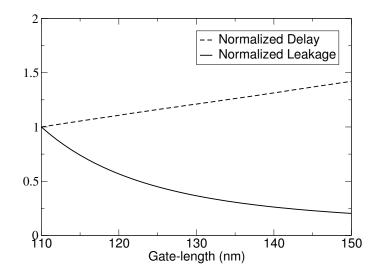

| Figure IV.1: Variation of leakage and delay (each normalized to 1.00) for an NMOS device in an industrial 130nm technology                                                                                                             | 117 |

| Figure IV.2: Pseudocode for cell-level gate length biasing for leakage optimization. Procedure <i>ComputeSensitivity</i> is defined in Figure IV.3.                                                                                    | 124 |

| Figure IV.3: Pseudocode for the <i>ComputeSensitivity</i> procedure                                                                                                                                                                    | 125 |

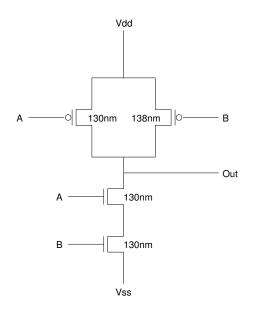

| Figure IV.4: Gate length biasing of the transistors in NAND2X1 when only the rise and fall timing arcs from input A to the output are critical                                                                                         | 127 |

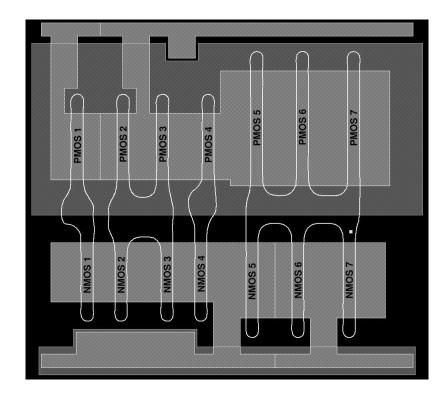

| Figure IV.5: Layout of a generic AND2X6 cell with simulated printed gate lengths                                                                                                                                                       | 138 |

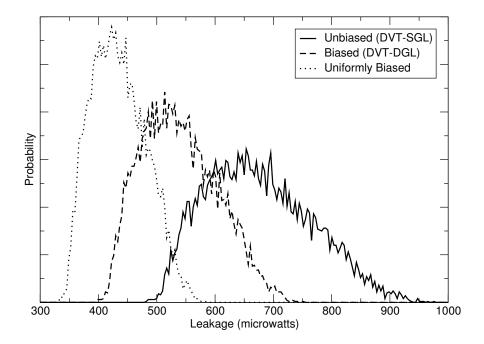

| Figure IV.6: Leakage distributions for unbiased, uniformly biased, and cell-level selectively-biased alu128. Note the "left-shift" of the distribution with the introduction of biased devices in the design                           | 142 |

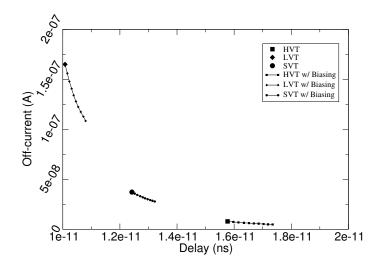

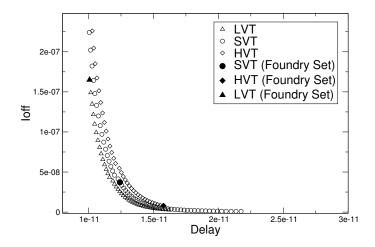

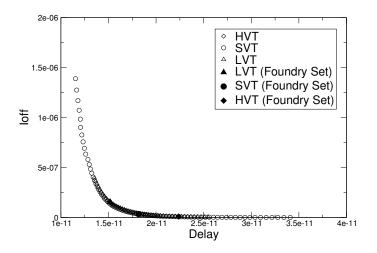

| Figure IV.7: Off-current and delay of an NMOS device as its <i>VTH0</i> is modified for HVT, SVT, and LVT                                                                                                                              | 146 |

| Figure IV.8: Off-current and delay of the NMOS device in INVX4 as <i>VTH0</i> is modified for HVT, SVT, and LVT                                                                                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure IV.9: Off-current and delay of the PMOS device in INVX4 as $VTH0$ is modified for HVT, SVT, and LVT                                                                                                                                                                                   |

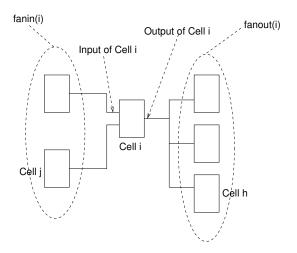

| Figure IV.10: Cell $i$ and its fanin and fanout cells                                                                                                                                                                                                                                        |

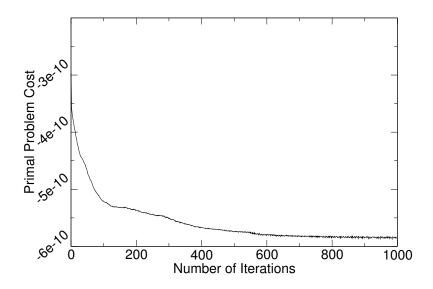

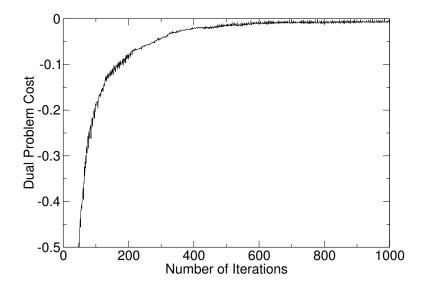

| Figure IV.11: Cost of the primal problem with iterations 161                                                                                                                                                                                                                                 |

| Figure IV.12: Cost of the Lagrangian relaxation subproblem 161                                                                                                                                                                                                                               |

| Figure IV.13: Chain eye chart                                                                                                                                                                                                                                                                |

| Figure IV.14: Star eye chart                                                                                                                                                                                                                                                                 |

| Figure IV.15: Mesh eye chart                                                                                                                                                                                                                                                                 |

| Figure IV.16: Hybrid testcase                                                                                                                                                                                                                                                                |

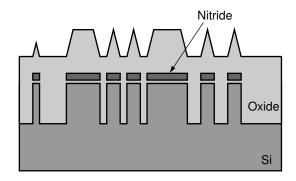

| Figure V.1: Profile before CMP. Oxide is deposited with slanted sidewalls over nitride features                                                                                                                                                                                              |

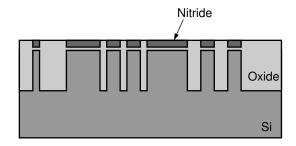

| Figure V.2: Desired profile after CMP. Oxide over nitride should be completely cleared, no nitride should erode, and no oxide dishing should occur in the trenches                                                                                                                           |

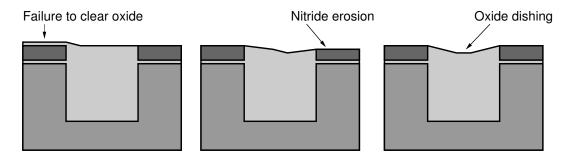

| Figure V.3: Three key failure mechanisms caused by imperfect CMP 176                                                                                                                                                                                                                         |

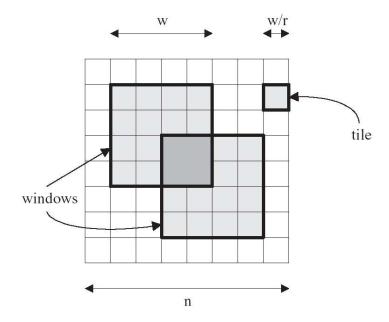

| Figure V.4: Layout is partitioned into windows of fixed size $w \times w$ and density is computed over them. Density variation is the maximum difference between densities computed over any two windows 181                                                                                 |

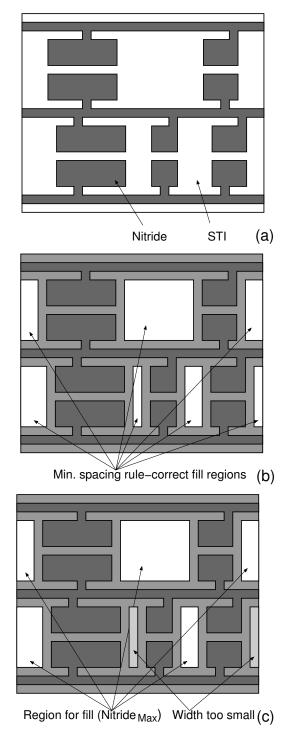

| Figure V.5: Computation of maximum fill region (Nitride <sub>max</sub> ). (a) Unfilled layout. (b) Design features bloated by minimum spacing design rule. (c) Spaces of small width and area (illustrated in the lightest shade of gray) are not available for fill                         |

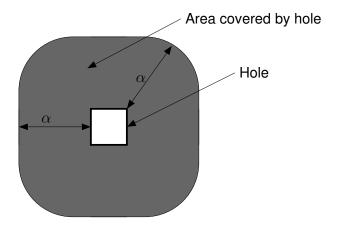

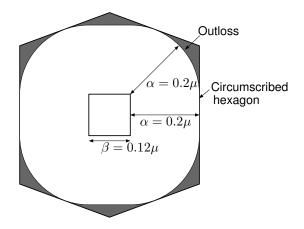

| Figure V.6: Gray area is the <i>area covered</i> by the white hole, i.e., fill features added in the gray area do not contribute to the oxide density due to the hole. $\alpha$ is the shrinkage; oxide features can be computed from nitride features by shrinking by $\alpha$ on all sides |

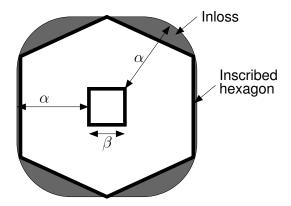

| inloss (s           | Hexagon inscribed in a rounded square and the associated shown in gray). $\beta$ is the minimum hole size permitted by the rules                                                   | 186 |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

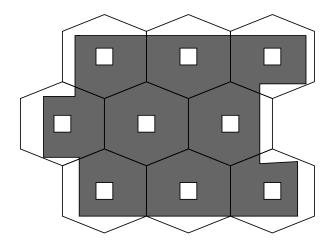

| ent hexa            | Gray rectilinear polygon represents $Nitride_{max}$ . Transparagons are tessellated in a honeycomb to cover the polygon minimum number of hexagons                                 | 187 |

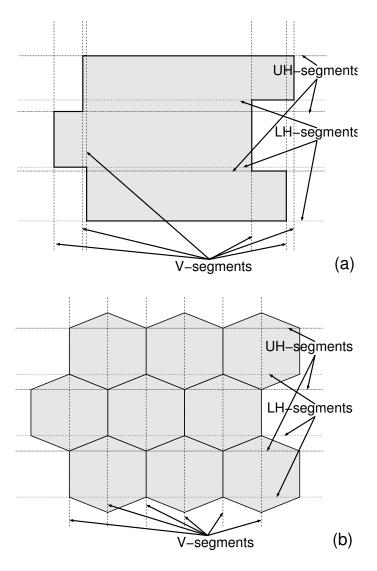

| UH- (up             | Illustration of V- (vertical), LH- (lower horizontal), and oper horizontal) segments for a (a) rectilinear polygon, and eycomb                                                     | 188 |

| _                   | Smallest hexagon circumscribed around the rounded square.  by area represents the outloss                                                                                          | 191 |

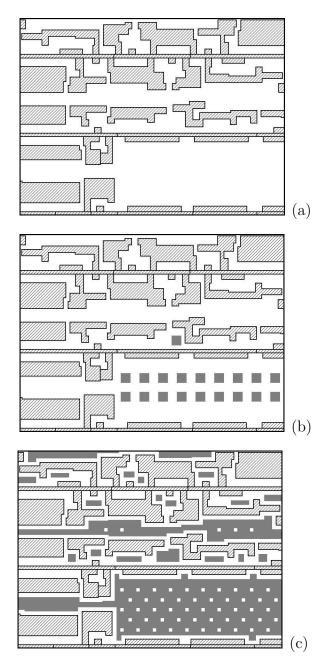

| with the fill inser | Layout with fill inserted using tiling-based method and e proposed method. Unfilled layout, layout with tile-based eted, and layout with fill inserted with the proposed method wn | 193 |

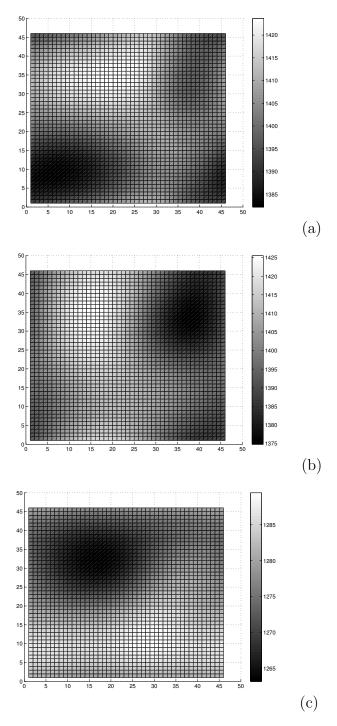

| out (a),            | Final step height (in angstroms) maps for the unfilled lay-<br>layout with tiling-based fill insertion (b), and layout with<br>posed insertion method (c)                          | 196 |

| Figure V.13:        | Assumed Layer ${\cal M}$ for first set of motivation experiments                                                                                                                   | 199 |

| Figure V.14:        | Assumed Layer $M$ for third set of motivation experiments.                                                                                                                         | 200 |

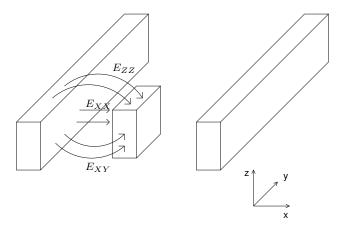

| Figure V.15:        | Different electric field components                                                                                                                                                | 202 |

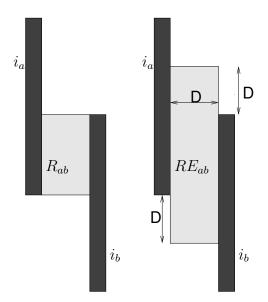

| Figure V.16:        | Rectangle enclosed by interconnects $i_a$ and $i_b$                                                                                                                                | 203 |

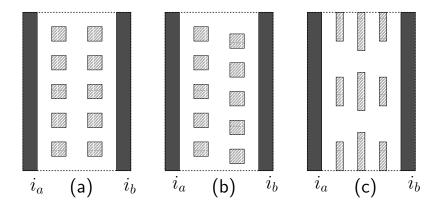

| Figure V.17:        | Five configurations used for Foundation 1 experiments. $$                                                                                                                          | 205 |

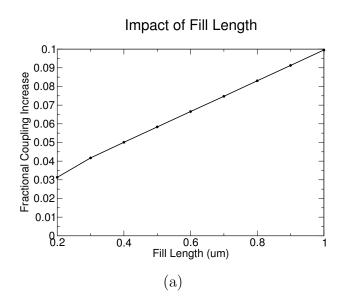

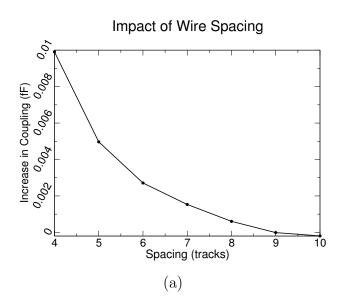

| Figure V.18:        | Impact of fill size on $\Delta C_{ab}$                                                                                                                                             | 207 |

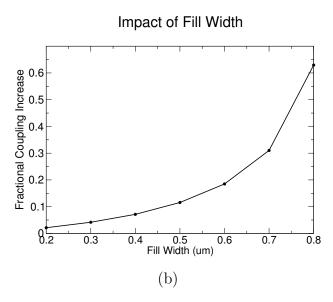

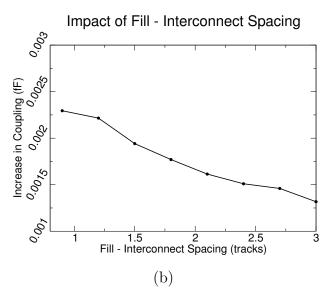

| Figure V.19:        | Impact of wire spacing and wire-fill spacing on $\Delta C_{ab}$                                                                                                                    | 208 |

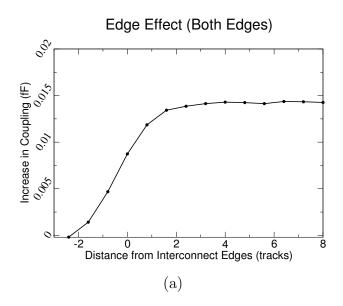

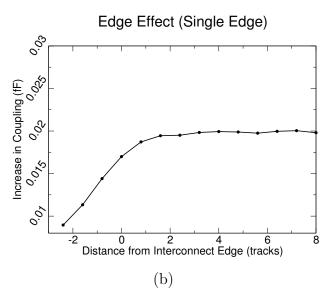

| Figure V.20:        | Edge effects in computation of $\Delta C_{ab}$                                                                                                                                     | 210 |

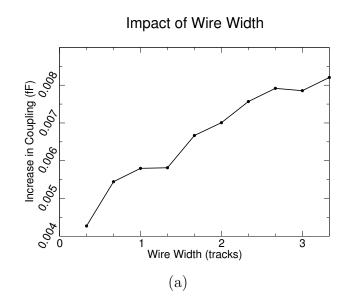

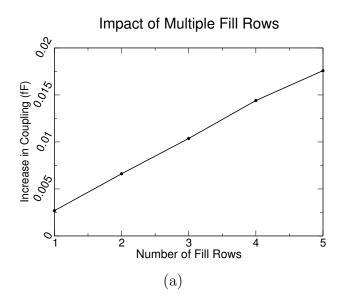

| Figure V.21:        | Impact of wire width and multiple columns on $\Delta C_{ab}$                                                                                                                       | 211 |

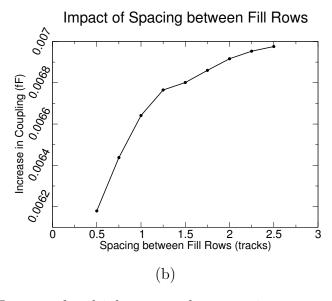

|                     | Impact of multiple rows and consecutive-row spacing on                                                                                                                             | 213 |

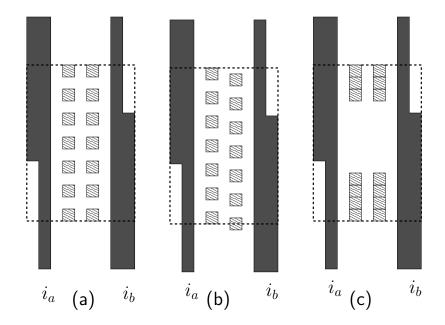

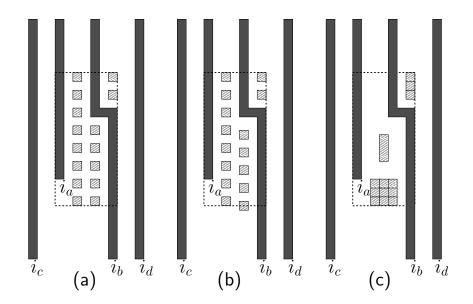

| Figure V.23: Configuration 1. (a) regular fill pattern, (b) staggered fill pattern, (c) fill insertion with guidelines.                                                                                                       | 215 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure V.24: Configuration 2. (a) regular fill pattern, (b) staggered fill pattern, (c) fill insertion with guidelines.                                                                                                       | 216 |

| Figure V.25: Configuration 3. (a) regular fill pattern, (b) staggered fill pattern, (c) fill insertion with guidelines.                                                                                                       | 217 |

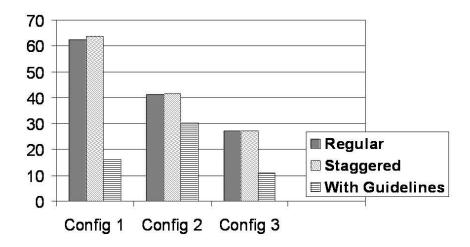

| Figure V.26: Percentage increase in coupling capacitance for the three configurations when fill insertion is performed in a regular pattern, in a staggered pattern, or with our guidelines to achieve the same metal density | 217 |

## LIST OF TABLES

| Table II.1: The effect of defocus and pitch on the linewidth of devices in a cell, NOR2X2                                                                                                                                                                | 42  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table II.2: Subthreshold and gate leakage of TSMC $90nm$ general purpose nominal $V_{th}$ PMOS and NMOS devices of $1\mu m$ width at two temperatures. Subthreshold leakage is greater than gate leakage                                                 | 48  |

| Table II.3: Estimated leakage power at worst, nominal and best process corners using (1) traditional, (2) topography-oblivious, defocusaware, and (3) topography-aware (assuming the topography of Figure II.12), defocus-aware leakage estimation flows | 59  |

| Table II.4: Leakage power after traditional and defocus-aware linewidth biasing. Leakage optimization is performed for nominal process corner and the topography of Figure II.12                                                                         | 63  |

| Table II.5: Leakage comparison of TSP-based placement versus optimal placement found by enumerating all placements. Leakage is normalized against maximum leakage                                                                                        | 74  |

| Table II.6: Testcases used in experimental validation                                                                                                                                                                                                    | 78  |

| Table II.7: Assessment of the impact on leakage, wirelength, and delay of the proposed technique                                                                                                                                                         | 80  |

| Table II.8: Design characteristics of two benchmark circuits                                                                                                                                                                                             | 86  |

| Table II.9: Circuit delay reported by traditional STA and aberrationaware STA                                                                                                                                                                            | 88  |

| Table III.1: Impact of STI width on performance of several standard cells.                                                                                                                                                                               | 94  |

| Table III.2: Model parameter table                                                                                                                                                                                                                       | 97  |

| Table III.3: Testcases used in experimental validation. $MCT$ is the minimum cycle time                                                                                                                                                                  | 110 |

| Table III.4: Traditional vs. stress-aware timing analysis                                                                                                                                                                                                | 11  |

| Table III.5: Timing optimization results with fill insertion. $MCT$ is the minimum cycle time. $WL$ is the wirelength. $TPD$ stands for top paths delay and is the sum of the delays of the top 100 critical paths. 111                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table III.6: Timing optimization results with placement and fill insertion. $MCT$ is the minimum cycle time. $WL$ is the wirelength. $TPD$ stands for top paths delay and is the sum of the delays of the top 100 critical paths                                                  |

| Table IV.1: Comparison of leakage and runtime when EISTA and CISTA are used for sensitivity computation                                                                                                                                                                           |

| Table IV.2: Asymmetry in delays and slews (transition delays) of various timing arcs within a NAND2X2 standard cell                                                                                                                                                               |

| Table IV.3: Testcases used in our experiments and their details. All cells in each circuit are low- $V_{th}$ cells and dynamic power is calculated assuming an activity factor of 0.02. We use typical corner (typical process, $1.2V$ , $25^{o}C$ ) for delay and power analysis |

| Table IV.4: Leakage reduction and delay penalty due to gate length biasing for all 25 cells in our library                                                                                                                                                                        |

| Table IV.5: Impact of gate length biasing on leakage for single threshold-voltage designs                                                                                                                                                                                         |

| Table IV.6: Impact of gate length biasing on dynamic and total power for single threshold-voltage designs                                                                                                                                                                         |

| Table IV.7: Impact of gate length biasing on leakage for dual threshold-voltage designs                                                                                                                                                                                           |

| Table IV.8: Impact of gate length biasing on dynamic and total power for dual threshold-voltage designs                                                                                                                                                                           |

| Table IV.9: Impact of gate length biasing on subthreshold leakage and gate tunneling leakage of $90nm$ PMOS and NMOS devices of $1\mu m$ width at different temperatures. Total leakage reductions are high even when gate leakage is considered                                  |

| Table IV.10: Comparison of printed dimensions of unbiased and biased versions of AND2X6                                                                                                                                                                                           |

| Table IV.11: Process window improvement with gate length biasing. The CD tolerance is kept at $13nm$ . ELAT = Exposure latitude 139                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table IV.12: Reduction in performance and leakage power uncertainty with biased gate length in presence of inter-die variations 141                                                                                                                                            |

| Table IV.13: Leakage power from transistor-level gate length biasing 143                                                                                                                                                                                                       |

| Table IV.14: Leakage reduction with: (a) two foundry-set $V_{th}$ 's, LVT and SVT; (b) two foundry-set $V_{th}$ 's, LVT and HVT; (c) three foundry-set $V_{th}$ 's, LVT, SVT and HVT; (d) $V_{th}$ 's, LVT and SVT with biasing; and (e) $V_{th}$ 's, LVT and HVT with biasing |

| Table IV.15: The seven threshold voltages used in our experiments 149                                                                                                                                                                                                          |

| Table IV.16: Testcases used in our experiments and their details. All testcases were sourced from opencores.org                                                                                                                                                                |

| Table IV.17: Post-optimization leakage (in $mW$ ) for two low $V_{th}$ 's and different high $V_{th}$ 's                                                                                                                                                                       |

| Table IV.18: Leakage reduction for different high- $V_{th}$ with different maximum gate length biases for AES. Best leakage reductions are shown in <b>bold</b>                                                                                                                |

| Table IV.19: Best high $V_{th}$ for three low $V_{th}$ 's and maximum bias of $4nm$ , $6nm$ , $8nm$ , and $10nm$ . Corresponding leakage savings are also shown                                                                                                                |

| Table IV.20: Leakage reductions for Lagrangian relaxation vs. sensitivity-based downsizing                                                                                                                                                                                     |

| Table V.1: Density improvements from the proposed fill insertion method. 194                                                                                                                                                                                                   |

| Table V.2: CMP simulation results for unfilled layout, layout with tiling-based fill insertion, and layout with the proposed fill insertion method. 195                                                                                                                        |

| Table V.3: Increase in total capacitance and in same-layer coupling capacitance of interconnect $i_a$ for Figure V.14 on fill insertion 201                                                                                                                                    |

| Table V.4: Increase in $C_{ab}$ as a single fill square is moved to the five locations shown in Figure V.17                                                                                                                                                                    |

#### **ACKNOWLEDGEMENTS**

I would like to thank my parents (my mother Kamlesh Sharma and my father Vijay Vinod Sharma) for their unconditional love and sacrifices. For their guidance and wisdom, without which I would not have been what I am. For their encouragement and support, without which I could not have gotten where I am today. I would like to especially thank my younger brother Hemant Sharma for his love and encouragement. For being my best friend, and for looking up to me for advice and inspiration.

My inexpressible gratitude goes to my advisor Prof. Andrew B. Kahng for his mentorship that has gone far and beyond my research area. For being not just the best advisor I could have desired, but also the expert, visionary, innovator, and enthusiastic researcher that has impacted me in several ways. I would also like to thank him for the research freedom, conducive environment, and financial support that have made my Ph.D. an enjoyable and smooth experience. Without him, I probably would not have pursued my Ph.D. and graduated with a Master's.

I would like to thank my mentor at Freescale Semiconductor, Dr. Kamal Khouri, for providing me my most enjoyable work environment, the encouragement, and the guidance. I am also indebted to him for his instrumental role in the excellent full-time opportunity that has been offered to me by Freescale. My experience at Blaze DFM was one of the most rewarding I have had, and I would like to especially thank Dr. Cho Moon, Venki Venkatesh, and Dr. Sam Nakagawa for providing me with their knowledge and perspectives.

I feel privileged to have a great group of friends and collaborators. I would like to thank Swamy Muddu, Prof. Sherief Reda, Prof. Puneet Gupta, Dr. Saumil Shah, Kambiz Samadi, Chul-Hong Park, Rasit Topaloglu, and Kwangok Jeong for their nicety, cooperation, and excellent research ideas. I am grateful to Prof. Dennis Sylvester, Prof. Alex Zelikovsky, and Prof. Ion Măndoiu for the insightful discussions and their guidance. I would like to thank Prof. Rakesh Kumar, Dr. Satya Mallick, Dr. Angshuman Parashar, Aseem Gupta, and Hrishikesh Gupta for all the great time we spent together.

I am thankful to my thesis committee members, Prof. Chung-Kuan Cheng, Prof. Rajesh K. Gupta, Prof. Tajana S. Rosing, and Prof. Yuan Taur, for taking time out of their schedules to review my research and provide useful feedback.

I would like to thank our lab's administrator Virginia McIlwain, graduate program coordinator Karol Previte, and payroll manager M'Lissa Michelson, for their support and cooperation which, at times, have gone beyond their job responsibility.

Last, but not least, I would like to express my hearty gratitude to Samik-sha Sorte for her constant love and encouragement. For her sacrifices, cooperation, and levelheaded attitude which facilitated my smooth and relaxed Ph.D. For being my inspiration and the reason to succeed.

The material in this thesis is based on the following publications.

- Chapter II is based on the following publications:

- A. B. Kahng, S. Muddu and P. Sharma, "Defocus-Aware Leakage Estimation and Control," to appear in *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*.

- A. B. Kahng, S. Muddu and P. Sharma, "Defocus-Aware Leakage Estimation and Control," Proc. International Symposium on Low Power Electronics and Design, 2005, pp. 263 268.

- A. B. Kahng, C.-H. Park, P. Sharma and Q. Wang, "Lens Aberration Aware Timing-Driven Placement," Proc. Design Automation and Testing in Europe, 2006, pp. 890 – 895.

- A. B. Kahng, S. Muddu and P. Sharma, "Detailed Placement for Leakage Reduction using Systematic Through-Pitch Variation," Proc. International Symposium on Low Power Electronics and Design, 2007, pp. 110 115.

- Chapter III is based on the following publication: A. B. Kahng, P. Sharma

- and R. O. Topaloglu, "Exploiting STI Stress for Performance," *Proc. International Conference on Computer-Aided Design*, 2007, to appear.

- Chapter IV is based on the following publications:

- P. Gupta, A. B. Kahng, P. Sharma and D. Sylvester, "Gate-Length Biasing for Runtime Leakage Control," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, Vol. 25(8), 2006, pp. 1475 1485.

- P. Gupta, A. B. Kahng, P. Sharma and D. Sylvester, "Selective Gate-Length Biasing for Cost-Effective Runtime Leakage Control," Proc. Design Automation Conference, 2004, pp. 327 – 330.

- A. B. Kahng, S. Muddu and P. Sharma, "Impact of Gate-Length Biasing on Threshold-Voltage Selection," Proc. International Symposium on Quality Electronic Design, 2006, pp. 747 – 754.

- Chapter V is based on the following publications:

- A. B. Kahng, P. Sharma and A. Zelikovsky, "Fill for Shallow Trench Isolation CMP," Proc. International Conference on Computer-Aided Design, 2006, pp. 661 – 668.

- A. B. Kahng, K. Samadi and P. Sharma, "Study of Floating Fill Impact on Interconnect Capacitance," Proc. International Symposium on Quality Electronic Design, 2006, pp. 691 696.

My coauthors (Prof. Puneet Gupta, Prof. Andrew B. Kahng, Prof. Ion Mandoiu, Swamy Muddu, Chul-Hong Park, Kambiz Samadi, Prof. Dennis Sylvester, Rasit O. Topaloglu, Dr. Qinke (Eric) Wang, and Prof. Alex Zelikovsky) have all kindly approved the inclusion of the aforementioned publications in my thesis.

#### VITA

| 1980 | Born, Delhi, India                                                                             |

|------|------------------------------------------------------------------------------------------------|

| 2002 | B.Tech., Computer Science and Engineering,<br>Indian Institute of Technology, Delhi, India     |

| 2005 | M.S., Electrical Engineering (Computer Engineering),<br>University of California, San Diego    |

| 2006 | C.Phil., Electrical Engineering (Computer Engineering),<br>University of California, San Diego |

| 2007 | Ph.D., Electrical Engineering (Computer Engineering),<br>University of California, San Diego   |

#### SELECTED PUBLICATIONS

All papers coauthored with my advisor Prof. Andrew B. Kahng have authors listed in alphabetical order.

- A. B. Kahng, S. Muddu and P. Sharma, "Defocus-Aware Leakage Estimation and Control," to appear in *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*.

- P. Gupta, A. B. Kahng, P. Sharma and D. Sylvester, "Gate-Length Biasing for Runtime-Leakage Control," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, Vol. 25(8), 2006, pp. 1475 1485.

- P. Gupta, A. B. Kahng, I. I. Mandoiu and P. Sharma, "Layout-Aware Scan Chain Synthesis for Improved Path Delay Fault Coverage," *IEEE Trans*actions on Computer-Aided Design of Integrated Circuits and Systems, Vol 24(7), 2005, pp. 1104 – 1114.

- A. B. Kahng, P. Sharma and R. O. Topaloglu, "Exploiting STI Stress for Performance," *Proc. International Conference on Computer-Aided Design*, 2007, to appear.

- A. B. Kahng, S. Muddu and P. Sharma, "Detailed Placement for Leakage Reduction using Systematic Through-Pitch Variation," Proc. International Symposium on Low Power Electronics and Design, 2007, pp. 110 – 115.

- A. B. Kahng, S. Reda and P. Sharma, "On-Line Adjustable Buffering for Runtime Power Reduction," Proc. International Symposium on Quality Electronic Design, 2007, pp. 550 – 555.

- A. B. Kahng, P. Sharma and A. Zelikovsky, "Fill for Shallow Trench Isolation CMP," Proc. International Conference on Computer-Aided Design, 2006, pp. 661 – 668.

- A. B. Kahng, S. Muddu and P. Sharma, "Impact of Gate-Length Biasing on Threshold-Voltage Selection," Proc. International Symposium on Quality Electronic Design, 2006, pp. 747 – 754.

- A. B. Kahng, K. Samadi and P. Sharma, "Study of Floating Fill Impact on Interconnect Capacitance," Proc. International Symposium on Quality Electronic Design, 2006, pp. 691 – 696.

- A. B. Kahng, C.-H. Park, P. Sharma and Q. Wang, "Lens Aberration-Aware Timing-Driven Placement," Proc. Design Automation and Testing in Europe, 2006, pp. 890 – 895.

- P. Gupta, A. B. Kahng, S. Nakagawa, S. Shah and P. Sharma, "Lithography Simulation-Based Full-Chip Design Analyses," Proc. SPIE Conference on Design and Process Integration for Microelectronic Manufacturing, 2006, pp. 61560T-1 – 61560T-8.

- A. B. Kahng, S. Muddu and P. Sharma, "Defocus-Aware Leakage Estimation and Control," Proc. International Symposium on Low Power Electronics and Design, 2005, pp. 263 – 268.

- P. Gupta, A. B. Kahng, P. Sharma, "A Practical Transistor-Level Dual

- Threshold Voltage Assignment Methodology," *Proc. International Symposium on Quality Electronic Design*, 2005, pp. 421 426.

- P. Gupta, A. B. Kahng, C.-H. Park, P. Sharma, D. Sylvester and J. Yang, "Joining the Design and Mask Flows for Better and Cheaper Masks," Proc. 24th BACUS Symposium on Photomask Technology and Management, 2004, pp. 318 – 329.

- P. Gupta, A. B. Kahng, P. Sharma and D. Sylvester, "Selective Gate-Length Biasing for Cost-Effective Runtime Leakage Control," *Proc. Design Automation Conference*, 2004, pp. 327 – 330.

- P. Gupta, A. B. Kahng, I. Mandoiu and P. Sharma, "Layout-Aware Scan Chain Synthesis for Improved Path Delay Fault Coverage," Proc. International Conference on Computer Aided Design, 2003, pp. 754 – 759.

#### ABSTRACT OF THE DISSERTATION

Manufacturing-Aware Physical Design Techniques

by

#### Puneet Sharma

Doctor of Philosophy in Electrical Engineering (Computer Engineering)

University of California, San Diego, 2007

Professor Andrew B. Kahng, Chair

CMOS scaling has outpaced manufacturing technology advancements, and consequently process variability continues to increase. Manufacturing non-idealities induce variations in lateral dimensions and topography, stress variations, and material variations. These are manifested as circuit delay and power variations, and consequently low parametric yield, which is the percentage of chips that, though functional, fail to meet delay and power specifications.

Design for manufacturing (DFM) refers to measures taken during design to enhance yield. Traditional DFM techniques are essentially geometric operations with limited electrical interactions or awareness. These include resolution enhancement techniques to improve fidelity of optical lithography, design rule checks to restrict the use of layout patterns not amenable to manufacturing, and guardbanding to keep margins for process variability in design. As the extent and complexity of process variations increases, and suboptimality due to conservative design threatens to offset the benefits of scaling, these traditional DFM techniques, while still crucial, are no longer adequate.

DFM techniques to improve parametric yield can be classified according to their approach. A considerable fraction of variability is systematic in nature and can be predicted using layout and process knowledge. Examples of such variations are pitch-dependent lithography variations and layout-dependent stress effects. These variations can be predicted and compensated for in physical design to improve yield. A second class of DFM techniques enhances design robustness to

process variations. Examples include gate length biasing and redundant link insertion in clock trees, which respectively reduce leakage and clock skew variations even when the gate length variability remains the same. A third class of parametric yield-directed DFM techniques reduces process variations themselves, and includes dummy fill insertion and the increased use of layout pattern regularity.

In this thesis we propose novel DFM techniques that explicitly target parametric yield. We present three techniques for analysis and optimization of circuit leakage and delay that are knowledgeable of systematic lithography variations due to pitch, defocus, and lens aberration. Stress variations, due to width of shallow trench isolation (STI) wells, can lead to considerable delay variations. We propose timing analysis and optimization methodologies to account for STI width-dependent stress, which is highly systematic in nature. Variations in gate length arising from a variety of process variations are a major cause of leakage variability, an important problem being faced by the designers today. We propose gate length biasing, which leverages the threshold voltage roll-off to significantly reduce leakage and its variability. The technique is non-obtrusive to existing flows, easy to adopt, and inexpensive to manufacture. We also present our contributions to front-end of the line (FEOL) and back-end of the line (BEOL) fill. Our FEOL insertion methodology considerably improves topography after chemical mechanical polishing for STI and may avoid the need for reverse-etchback process steps. In BEOL fill insertion, a primary concern is the capacitive impact of inserted fill and the corresponding increase of delay and crosstalk. We describe a systematic study of the capacitive impact of inserted fill, and develop guidelines that reduce capacitive impact without sacrificing metal density.

# Ι

# Introduction

CMOS device scaling has outpaced advancements in manufacturing technology. Thus, process variability, as a fraction of feature size, continues to increase. The impact of process variations on circuit power and performance is exacerbated by the superlinear dependence of several electrical metrics on feature size (e.g., subthreshold leakage on gate length, and gate tunneling leakage on gate oxide thickness). Power, and especially leakage power, is another major challenge faced by designers today. Lowering of supply voltage to reduce dynamic power necessitates lowering of threshold voltage to sustain high-performance and adequate noise margins. Unfortunately, lowering threshold voltage causes a near-exponential increase in leakage power, and a larger ratio of static ("wasted") power to total power. Leakage variability, which is increasingly a determinant of parametric yield, is another important problem that must be addressed for continued CMOS scaling.

Traditionally, design and manufacturing have been conveniently kept separated, with only minimal information exchange. From the manufacturing side, SPICE models, technology file, and design rules are supplied for performance and power estimation, and to convey manufacturing limitations. However, in today's era of large process variability, traditional corner-based analyses can be overly pessimistic, causing valuable performance to be left on the table. Design rules also become extremely complex, substantially reducing productivity. From the design side, the layout is transferred to manufacturing as a set of shapes to be printed

on silicon. To achieve high fidelity of silicon shapes to "drawn" shapes, the manufacturing side applies several resolution enhancement techniques (RETs) to the entire design. Unfortunately, RETs significantly increase the mask writing cost and multi-million dollar mask sets are now common. To reduce mask cost, it is important to additionally convey the design intent to manufacturing so that high fidelity is attempted only for selected features in the design that require accurate manufacturing. Design for manufacturing (DFM) techniques essentially address the questions related to the exchange of information across design and manufacturing, and the use of this information for yield enhancement.

The focus of this thesis is on manufacturing-aware physical design techniques. Physical design optimizations can potentially increase yield by:

- 1. making the design account for process variations (e.g., systematic variationaware design optimization techniques discussed in Chapter II and stressaware timing optimization discussed in Chapter III);

- 2. increasing the robustness to process variations (e.g., gate length biasing discussed in Chapter IV reduces leakage variability even when the process variations are unchanged); and

- 3. reducing the process variations themselves (e.g., fill insertion discussed in Chapter V reduces topography variation).

To better understand DFM, we next present a brief overview of optical lithography.

## I.A Optical Lithography

Optical lithography, or simply lithography, is the mainstream technique to create patterns on silicon wafers. While conceptually simple, lithography has evolved into a highly sophisticated process due to precision requirements that are unmatched anywhere in modern manufacturing. Lithography involves several steps which can be simplistically grouped into photoresist deposition, exposure, and etching.

The process begins with deposition of a thin layer that is intended to be patterned on the wafer. The thin layer is sacrificial and is used to selectively etch, dope, oxidize or deposit the underlying material.<sup>1</sup> The pattern on the mask is first transferred to the photoresist that is deposited over the thin layer. An etchant is then used to remove the thin layer from where it is not protected by the photoresist. We now briefly describe the major lithography steps, further details of which can be found in [116].

### I.A.1 Photoresist and its Deposition

Photoresists are materials that when exposed to light undergo a photochemical reaction that changes their solubility properties to a *developer* chemical. Positive photoresists become soluble in the regions that are exposed to light while negative photoresists become soluble in the regions occluded from light. Prior to deposition of the photoresist, the wafer may optionally be treated with a chemical that promotes adhesion between the thin layer and the photoresist.

The standard method of depositing the photoresist onto the wafer is resist spinning. In this method, a small amount of the photoresist in liquid form is dispensed onto the center of the wafer, and the wafer is then rotated about its center at a high rate. As the wafer spins, the resist spreads radially and solidifies into a uniform solid layer over the wafer. A baking step, known as soft bake, in which the wafer is heated to relatively low temperature for a short period of time, is then optionally performed to further densify the photoresist. Another optional step of coating the wafer with an anti-reflective coating (ARC) is then performed to suppress the light reflections in the succeeding exposure steps.

<sup>&</sup>lt;sup>1</sup>Certain underlying materials can be directly etched without the use of the thin layer.

### I.A.2 Exposure

By selectively exposing the photoresist to light, a pattern can be transferred to the photoresist. This process is accomplished in lithography by imaging of the mask to transfer patterns on it to the photoresist. The mask is a thin piece of a high-quality transparent material, typically quartz, partially covered with an opaque material, typically chromium, that has been removed according to the circuit pattern using an electron-beam mask writer.

Over the years, mask writing technology has improved but has failed to keep pace with the shrinkage of feature sizes. Thus, projection printing, in which projection optics (sometimes simply known as the lens) are used to reduce the mask image by a reduction factor (N), is now mainstream. The projection optics are typically an array of high-quality lenses cascaded to realize the reduction factor with minimal image distortion. The reduction factor in modern optics is most commonly equal to four or five. Larger reduction factors relax the precision requirements on the mask and reduce the linewidth variations due to mask errors. However, larger reduction factors increase the size of the mask and decrease the throughput in terms of the wafer area exposed under the mask. We note that the mask is also referred to as the reticle in the exposure context.

The equipment used to expose the photoresist-coated wafer is known as a wafer stepper. In a wafer stepper, a small portion of the wafer, known as the exposure field or simply the field, is exposed under the reticle through the projection optics. The illumination is then turned off and the wafer is displaced so that a different portion of the wafer is exposed in the next step. Modern wafer steppers are extremely sophisticated, with very high stepping precision. Additionally, steppers also align the wafer to the proper position so that the projected image will precisely overlay the patterns already on the wafer from previous lithography steps.

Modern wafer steppers are of the *step-and-scan* type in which the field is partially exposed through a slit [189, 116]. The lens and the wafer are translated synchronously such that the illumination through the slit scans the field from side to side. Due to the image reduction by the projection optics, the lens must be

Figure I.1: Schematic of a step-and-scan wafer stepper.

translated N (i.e., the reduction factor) times faster than the wafer. Illumination through a small slit restricts the area of the projection optics that is utilized, which simplifies the projection optics and reduces their distortions. A schematic of the step-and-scan system is shown in Figure I.1.

After the patterning process completes, the photoresist undergoes post-exposure bake, which entails heating at a higher temperature than soft bake. The purpose of post-exposure bake is to further drive off low molecular-weight materials that may contaminate the post-lithographic equipment. Post-exposure bake also smoothes out the resist line profiles. Then, a developer solution washes away the soluble parts of the resist and the pattern has been transferred from the mask to the photoresist.

While the patterning process is highly sophisticated, the image on the mask undergoes significant distortion as it is transferred to the photoresist. Due to the extremely small sizes of the mask features, diffraction effects, inherent to the wave nature of light, become considerable. Unfortunately, a finite-sized lens is not capable of collecting all the diffraction orders as shown in Figure I.2, and the mask image cannot be completely reconstructed. This fundamentally limits the resolving capability of lithography, which is given by the following well-known Raleigh's equation:

Figure I.2: Features on the mask cannot be completely reconstructed due to diffraction.

$$w_{min} = k_1 \frac{\lambda}{NA} \tag{I.1}$$

- $w_{min}$  is the minimum feature size that can be resolved.

- $\lambda$  is the wavelength of the illumination source. An ArF plasma source with a wavelength of 193nm is used in modern lithography, and is projected to remain in use at least through the 45nm node.

- NA is the numerical aperture of the lens and is the the sine of the maximum half-angle of light that can make it through a lens to the wafer, multiplied by the index of refraction of the medium (1.0 for air). The NA of a lens is a measure of its ability to capture the diffraction orders of light across a wide range of incidence angles.

- $k_1$  is known as the *k-factor* and captures the capability of the lithography process; it has a fundamental lower limit of 0.25. For modern processes,  $k_1$  is around 0.3.

In addition to the the minimum resolvable size, the *depth of focus (DOF)* is an important parameter of a patterning system. Ideally, the wafer should be placed at the focal plane of the lens. This, in practice, is infeasible and the wafer, or certain parts of it, may be positioned at a small distance, known as the *defocus*,

from the focal plane. DOF captures the tolerance of a exposure system to defocus. DOF is given by

$$DOF = k_2 \frac{\lambda}{(NA)^2} \tag{I.2}$$

where  $k_2$  is a constant. Similar to DOF, exposure latitude (ELAT) quantifies the tolerance to exposure dose variations. Together with DOF, exposure latitude gives the lithography process window.

Improvements in lithography equipment and resist technology, along with resolution enhancement techniques (RETs), reduce the k-factor and consequently the minimum resolvable size. RETs are methods used in lithography to enhance the printability of mask features. RETs are typically applied after signoff and before or during the mask data preparation stage. Commonly used RETs are as follows.

- Optical proximity correction (OPC) selectively alters the shapes of the mask patterns to compensate for patterning imperfections. OPC can be rule-based, which uses rules defined for different layout configurations, or model-based, which uses a lithography simulator. While OPC is very effective at reducing patterning variation, it requires a large runtime and significantly increases the mask complexity.

- Off-axis illumination (OAI) refers to illumination which has no on-axis component, i.e., which has no light that is normally incident on the mask. Examples of off-axis illumination include annular and quadrupole illumination. OAI improves the DOF for certain pitches while worsening it for others that are known as forbidden pitches. Fortunately, sub-resolution assist features can be inserted to eliminate or reduce the impact of the forbidden pitches.

- Sub-resolution assist features (SRAFs) or scattering bars (SB) are layout features that are inserted between layout features to improve their printability. SRAFs have very narrow widths and do not print on the wafer.

• Phase shift mask (PSM) adds transparent layers to the mask in certain locations to induce destructive interference at feature edges, which enhances pattern contrast and improves the k-factor.

### I.A.3 Etching

Etching is used to transfer the pattern from the photoresist to the underlying thin layer. The chemical used in etching is known as the *etchant*; it selectively reacts with the underlying thin layer only in the areas that are not protected by the photoresist, while leaving the photoresist intact. The most common etching technique is reactive ion etching in which chemically reactive plasma is used to remove the thin layer in regions not protected by photoresist. After etching, the photoresist is completely removed by a variety of methods (e.g., dry etching [156]).

# I.B Yield and Sources of Variability

Yield is defined as the number of chips that function and meet delay and power specifications, expressed as a percentage of the total number of chips manufactured. For a mature process, yield of over 90% is typical. However, during process development and ramp-up, the yield can be much less. Yield is commonly classified into the following two categories.

- Functional yield or catastrophic yield is the percentage of chips that are functional. Examples of functional failures that limit functional yield are shorts and opens in wires, open vias, line-end shortening, etc.

- Parametric yield is the number of chips that meet delay and power specifications, as a percentage of the functionally-correct chips. Parametric yield loss is due to chips that are functional but cannot be sold because they fail to meet the delay and power specifications.

A variety of process variations and defects cause yield loss. Functional yield loss is usually caused by misprocessing and random contaminant-related de-

fects. Parametric yield loss is typically due to process variations. However, process variations can also cause functional failures (e.g., line-end shortening leading to an always-on device) and defects can cause parametric yield loss (e.g., particle contamination that causes interconnect thinning but not a complete open).

While yield loss due to functional failures is significant, parametric failures have gained significance and now dominate functional failures. Arguably, measures to improve parametric yield are more challenging to develop and adopt. While most functional yield-enhancing methods are geometric and applied after signoff, parametric yield-enhancing methods often require understanding of the nature of process variations and modeling of their electrical effects. In this thesis, we focus on techniques that address parametric yield loss. Process variations, which are the primary cause of parametric yield loss, can be classified as follows.

- By nature systematic vs. random. Systematic variations are predictable and can be modeled during circuit design. Random variations, on the other hand, are either unpredictable or difficult to model. Examples of systematic variations are topography variations, linewidth variation due to defocus and exposure, and stress due to shallow trench isolation (STI). Doping concentration variation, variations due to exposure system vibration, and lot-to-lot material variations are examples of random variations.

- By spatial scale intra-die vs. inter-die. Intra-die (or within-die) variations affect the circuit components within a die differently. Examples of intra-die variations are gate length variations due to proximity effects and up to some extent topography. Intra-die variations are more difficult to account for in traditional analysis tools, and their effects are generally guardbanded. Inter-die variations include die-to-die, wafer-to-wafer, and lot-to-lot variations. They affect circuit components in a die equally and are therefore modeled as a shift in the mean.

Process variations manifest themselves as circuit metric (power and delay) variations in the following ways.

• Lateral dimension variations. The smallest dimension on a layer is referred to as the *critical dimension (CD)* because it is the most challenging to manufacture. On the polysilicon layer, CD refers to the *linewidth* of the gate poly, which is equivalent to the gate length or channel length; on metal layers, CD is the wire width. Process variations affect the CD the most, and are manifested as delay and power variations of the circuit. For example, decrease in the gate length will decrease the device delay and capacitance, but dramatically increase subthreshold leakage. Decrease in the wire width will increase resistance but decrease capacitance.

Significant sources of CD variation are exposure and etching variations in lithography. During exposure, CD variation is due to mask errors [188], resist thickness variation [116], exposure dose variations [116], defocus [116], lens aberration [34], flare [30], etc. Microloading effects during etching also cause CD variation [83]. A substantial fraction of CD variation arising due to the these exposure and etching variations is considered systematic.

- Profile/topography variation. Chemical mechanical polishing (CMP) is performed between lithography steps to attain the designed layer height and to planarize the layer for successive process steps. Unfortunately, CMP is imperfect and cannot eliminate topography variation. Topography variation changes the metal height in back-end of the line (BEOL) which affects the wire resistance and capacitance. CMP for front-end of the line (FEOL) is used to planarize the oxide that is deposited for STI. Imperfect FEOL CMP leads to defocus during polysilicon patterning and poor inter-device isolation. Topography variation is understood to be partly systematic for both FEOL [108] and BEOL [178]. Another example is gate oxide thickness variation which affects gate-tunneling leakage and device subthreshold slope. Gate oxide is manufactured by light oxidation and its thickness variation, though small, is considered random.

- Stress effects. Mechanical stress on active regions of devices arising due to

the proximity and width of STI wells are significant in existing technologies. Stress due to STI is compressive and typically enhances the mobility of PMOS while degrading the mobility of NMOS. Consequently, delay and leakage increase for PMOS while decreasing for NMOS. Several techniques have been proposed to reduce STI stress-induced variation (e.g., [113]). STI stress is highly systematic and is partly modeled in today's design flows. Recent works have proposed modeling the residual STI stress effects [127].

Material variations. Lot-to-lot material variations cause variations in carrier mobility, polysilicon resistance, etc. Dopant concentration in the device channels affects the threshold voltage and consequently subthreshold leakage and device delay. Due to the small number of dopant atoms in the channel in modern devices, dopant density varies significantly and randomly as a percentage and induces substantial random variation in threshold voltage.

As a consequence of these manifestations, a significant variation is seen in circuit delay and leakage. With technology scaling, process variations are increasing as a percentage, and consequently the delay and leakage variability is increasing. There is considerable parametric yield loss today especially during yield ramp-up phase causing substantial value loss.

# I.C Design for Manufacturing

Design for Manufacturing (DFM) refers to measures taken during the design process to enhance yield. Parametric yield enhancement facilitated by DFM can contribute to improvement of design performance and/or power, and/or designer productivity. DFM techniques can compensate for, reduce, or make the design more robust to various types of manufacturing non-idealities.

#### I.C.1 Traditional Methods

While DFM has attracted great deal of attention recently from industry and academia, several techniques that can be arguably be considered DFM techniques have been in use for several years.

- RETs. As explained earlier, the purpose of these techniques is to minimize the lateral distortion between the drawn and the on-silicon shapes.

- Design rule checking (DRC). Design rules have been the primary method for the foundry to convey manufacturing limitations to design. Design rule checking, verifies adherence to these rules, and a design that is design rule-correct is expected to have a high functional and parametric yield. Simple examples of DRCs are minimum spacing, minimum and maximum dimension or area, and minimum and maximum metal density.

- Guardbanding. Considerable margin is allocated during design to account for process variations. Today's timing and power analysis flows are cornerbased, i.e., a set of conservative process, voltage, and temperature (PVT) settings are assumed in analysis. With respect to process variations, hold and setup time checks are performed at fast and slow process corners respectively. Leakage is typically highest at the fast process corner, but the use of typical process corner to reduce pessimism in analysis is common. The premise behind corner-based flows is that if the design meets its specifications at conservative PVT settings, it will meet them at all other conditions. Unfortunately, this premise is not true and is now breaking down due to complex dependence of electrical metrics on variations. For example, shorter gate lengths do not necessarily have higher leakage (due to reverse short channel effect), and wider wires are not necessarily faster.

The above techniques were relatively easy to adopt and served well until the 130nm node. Since then, as the complexity and extent of process variations has increased, these techniques, while remaining necessary, are no longer sufficient.

Several problems stem from the inadequacy of these techniques and call for novel DFM techniques that explicitly target yield enhancement.

- With scaling, as process variations have become complex and large, design rules are no longer able to capture the variations completely and precisely. In modern technologies, layout regions that do not meet design rules may yield well, while those that meet them may not. Thus, design rules have become extremely complex in an attempt to capture process variations that arise due to complex layout configurations. Recommended design rules, which are preferably but not necessarily required to be met, have also been introduced. A large set of design rules poses maintainability problems, and limits the freedom of optimization algorithms and tools in physical design.

- The use of restricted design rules (RDRs) [118], for example those that enforce regularity by allowing only one or two pitches, increases the chip area.

- Corner-based analysis assumes conservative process conditions; this is overly pessimistic since all parameters have an extremely small likelihood of being at their conservatively assumed values at the same time. Moreover, the design metric under analysis may have a non-monotonic dependence on process parameters, in which case worst-casing the process parameter will not result in worst-casing of the design metric. An example is clock skew as a function of M3 and M4 (say) process variations. To reduce pessimism and improve worst-casing of design metrics, analysis is performed at a large number of corners. Unfortunately, the number of corners can grow rapidly with process parameters and the analysis can be both pessimistic and risky at the same time [180]. Furthermore, corner-based methods cannot account adequately for inter-die variations since all components are assumed to be at the same process corner. A notable exception is on-chip variation analysis which allows clock and data path components to be at opposite corners.

- As guardbanding increases and compromises the advantages from scaling, designers are under tremendous pressure as they seek to meet market ex-

pectations. To improve delay, power, and area of the design, considerably more time must be spent on iterations and fixing violations. This reduces productivity.

Design rules and guardbanding can no longer be sufficiently pessimistic to ensure high parametric yield. Unexpectedly large variations and failures can cause intolerable yield loss, and require costly design re-spins.

#### I.C.2 Taxonomy

DFM techniques can be broadly classified into the following two categories depending on the yield loss component that they address.