## **UC Berkeley**

#### **UC Berkeley Electronic Theses and Dissertations**

#### **Title**

Nanoscale Bulk MOSFET Design and Process Technology for Reduced Variability

#### **Permalink**

https://escholarship.org/uc/item/33r606s2

#### **Author**

Sun, Xin

#### **Publication Date**

2010

Peer reviewed|Thesis/dissertation

#### Nanoscale Bulk MOSFET Design and Process Technology for Reduced Variability

By

Xin Sun

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

**Graduate Division**

of the

University of California, Berkeley

Committee in charge:

Professor Tsu-Jae King Liu, Chair Professor Chenming Hu Professor David Brillinger

Spring 2010

#### Abstract

Nanoscale Bulk MOSFET Design and Process Technology for Reduced Variability

by

Xin Sun

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Tsu-Jae King Liu, Chair

Historically, the steady miniaturization of the conventional (planar bulk) MOSFET by simply scaling the device dimensions with minimal changes to the conventional transistor design and CMOS process flow has been effective to provide for continual improvements in integrated circuit performance and cost per function with every technology node. However, transistor scaling has become increasingly difficult in the sub-100 nm regime. Increased leakage current and variability in transistor performance are the major challenges for continued scaling of bulk-Si CMOS technology.

The benefit of using a spacer gate lithography process to mitigate the effect of gate line edge roughness (LER) is assessed using statistical 3-D device simulations. The simulation results indicate that spacer gate lithography is a scalable technology which can dramatically reduce LER-induced variation in transistor performance.

A tri-gate bulk MOSFET design combining retrograde channel doping with a multi-gate structure is proposed to provide an evolutionary pathway for bulk CMOS scaling. The scalability, design optimization, and the effect of systematic and random variations on transistor performance are investigated. As compared with the classic planar MOSFET design, the tri-gate bulk MOSFET provides for superior electrostatic integrity and reduced variability. As compared with SOI FinFET design, the tri-gate bulk MOSFET design parameters. As compared with the bulk FinFET design, the tri-gate bulk MOSFET offers comparable performance and variability. Its low-aspect-ratio channel structure is favorable for ease of manufacturing. Thus, the tri-gate bulk MOSFET is a promising structure for CMOS scaling to the end of the technology roadmap.

The fabrication process flow and the most critical processes for tri-gate bulk MOSFET fabrication are discussed. Initial device results show that tri-gate bulk MOSFET design is beneficial for reduced variability.

To my family, for their unbounded love and support

# **Table of Contents**

| Chapter 1 Introduction                                     |          |

|------------------------------------------------------------|----------|

| 1.1 The Need for CMOS Scaling                              | 1        |

| 1.2 MOSFET Scaling Challenges                              | 3        |

| 1.3 Sources of Variability                                 | 4        |

| 1.4 Advanced MOSFET Structures                             | 5        |

| 1.5 This Work                                              | 6        |

| 1.6 References                                             | 7        |

| Chapter 2 Spacer Gate Lithography for Reducing Variability | , 10     |

| 2.1 Introduction                                           |          |

| 2.2 Spacer Lithography Process                             |          |

| 2.3 Gate Line Edge Roughness (LER) Study                   | 11       |

| 2.3.1 Simulation Approach                                  |          |

| 2.3.2 Results and Discussion                               |          |

| 2.4 Summary                                                |          |

| 2.5 References                                             |          |

|                                                            |          |

| Chapter 3 Tri-Gate Bulk MOSFET Design                      | 20       |

| 3.1 Introduction                                           | 20       |

| 3.2 Tri-Gate Bulk MOSFET Structure                         | 20       |

| 3.2.1 Device Structure                                     |          |

| 3.2.2 Simulation Results and Discussion                    | 21       |

| 3.3 Scale Length Assessment                                | 24       |

| 3.3.1 Introduction                                         | 24       |

| 3.3.2 Scale Length Derivation                              | 25       |

| 3.3.3 Scale Length Comparison                              |          |

| 3.4 Design Optimization of Tri-Gate Bulk MOSFET            | 29       |

| 3.4.1 Tri-Gate vs. FinFET Design Optimization              | 29       |

| 3.4.2 Variability Study                                    | 34       |

| 3.5 Summary                                                | 35       |

| 3.6 References                                             | 36       |

| Chapter 4 Variation Study of Tri-Gate Bulk MOSFET          | 30       |

| 4.1 Introduction                                           |          |

| 4.2 Nominal MOSFET Designs                                 |          |

| 4.3 Impact of Systematic Variations                        |          |

| 4.4 Impact of Random Variations                            |          |

| 4.5 Summary                                                |          |

| 4.6 References                                             | 40<br>46 |

|                                                            |          |

| Chap       | ter 5 Segmented Bulk MOSFET Technology                       | 48 |

|------------|--------------------------------------------------------------|----|

| _          | Introduction                                                 |    |

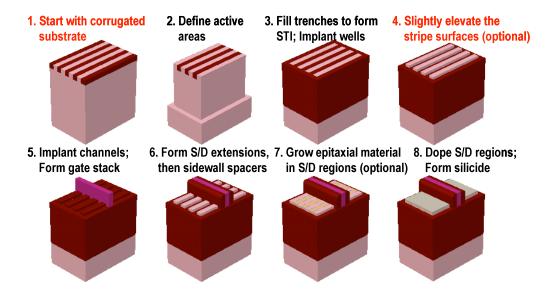

|            | Device Process Flow                                          |    |

|            | Corrugated Substrate Process                                 |    |

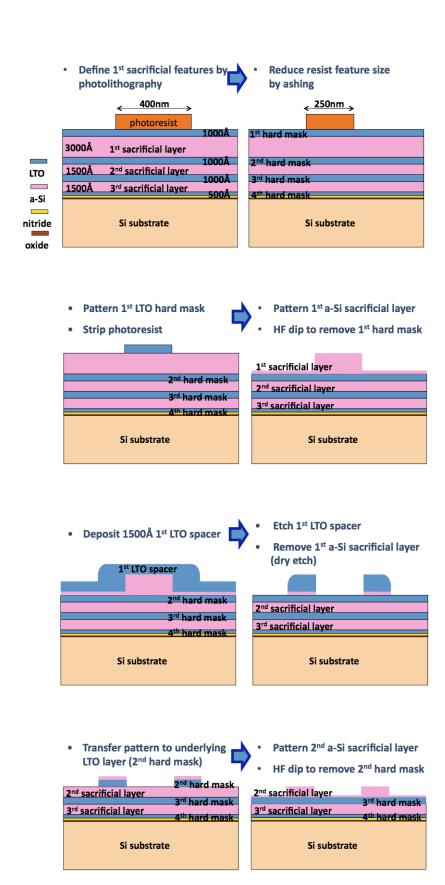

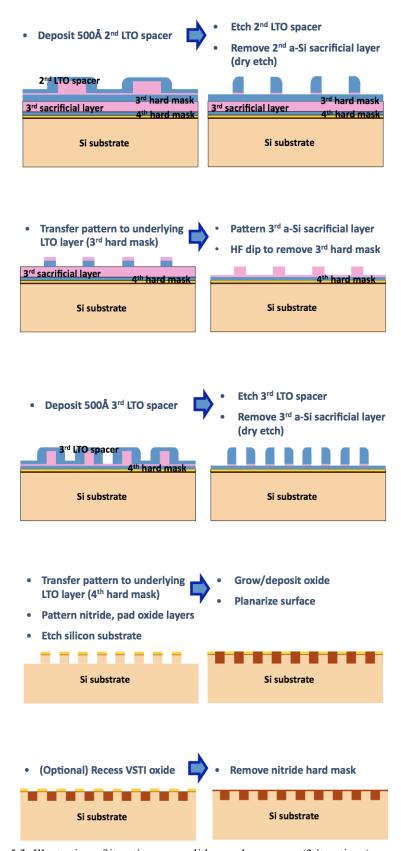

| 5.         | 3.1 Iterative Spacer Lithography Process                     | 50 |

| 5.         | 3.2 Negative Spacer Lithography Process                      | 53 |

| 5.4        | Control of Very Shallow Trench Isolation (VSTI) Oxide Recess | 55 |

| 5.         | 4.1 Introduction                                             | 55 |

| 5.         | .4.2 Experimental Results                                    | 56 |

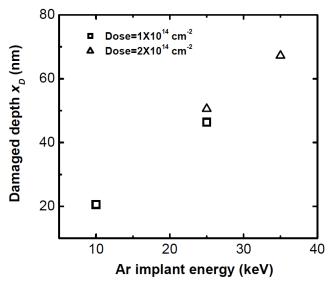

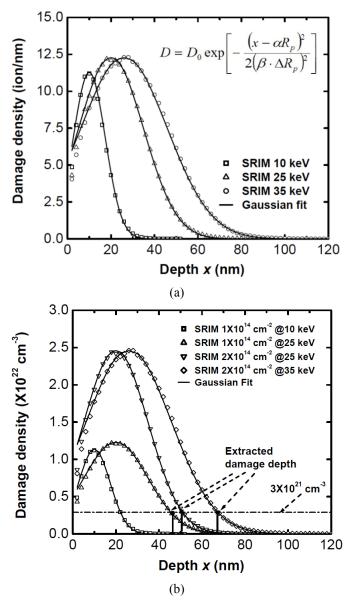

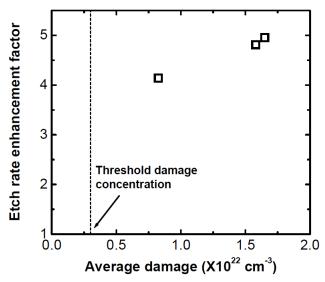

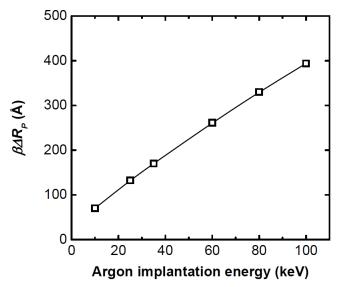

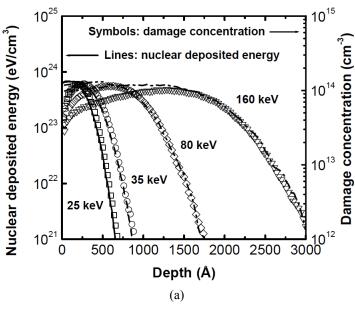

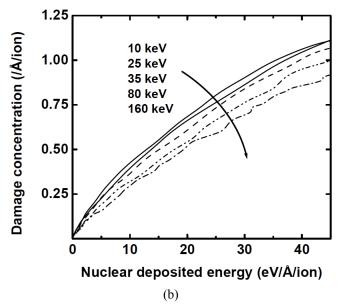

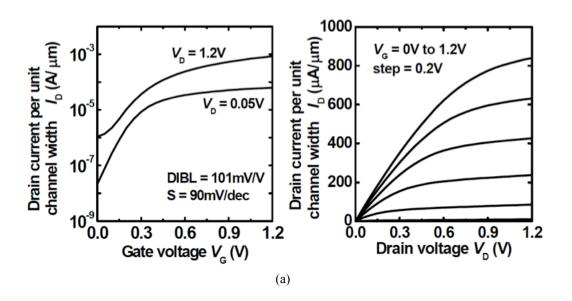

| 5.         | .4.3 Implant Damage Simulation and Model                     | 57 |

| 5.         | 4.4 Discussion                                               | 60 |

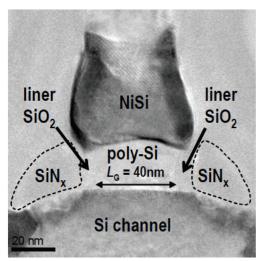

| 5.5        | Device Results                                               | 61 |

| 5.6        | Summary                                                      | 64 |

| <b>5.7</b> | References                                                   |    |

| Chap       | ter 6 Conclusion                                             | 66 |

|            | Contributions of This Work                                   |    |

| 6.2        | Future Directions                                            | 67 |

| 6.3        | References                                                   | 67 |

# Acknowledgements

Pursuing a Ph.D. is a long-term journey, with both the joys and frustrations. It is fun, it may get hard, and then it gets fun again. I am grateful for all the encouragement and help I get during my time at Berkeley.

First and foremost, I would like to express my sincere gratitude to my advisor, Professor Tsu-Jae King Liu, for her extraordinary support since the first day I came to Berkeley and for her encouragement and guidance throughout the research.

I would also like to thank Professor Chenming Hu for his enthusiasm and help, and for chairing my qualifying examination committee. I also wish to thank Professor David Brillinger and Professor Ming Wu for their valuable feedback as members of my qualifying examination.

I am grateful to Dr. Qiang Lu for his help and advice during my internship at Synopsys. I would also like to thank Dr. Ken Rim and Dr. Noah Zamdmer for their mentoring during my summer internship at IBM.

There are several people whom I would like to thank with regards to this work specifically. Dr. Andrew Carlson helped me develop the processes for the corrugated substrate. Dr. Harry Levinson and Tom Wallow at AMD provided the photoresist data for the study of gate line edge roughness. Dr. Qiang Lu and Victor Moroz helped answer my questions about TCAD simulations. Mr. Hideki Takeuchi at ATDF helped device fabrication. The UC Berkeley Microfabrication lab staff helped me debug different processes.

I am deeply grateful to the former and current members of Berkeley device research group for their encouragement and help, for being my colleague and years of friends. Thanks everyone.

This work has been sponsored by Tokyo Electron Limited and the Semiconductor Research Corporation, FLCC, IMPACT and the UC Discovery Grant program.

# Chapter 1

### Introduction

#### 1.1 The Need for CMOS Scaling

Since the integrated circuit (IC) was invented [1, 2], the evolution of IC technology has enabled the rapid growth of the electronics industry for more than forty years. Technological advancements have yielded dramatic improvements in product performance as well as cost per function, making electronics products more capable and affordable for consumers. Take the personal computer (PC), for example: the first IBM PC equipped with a 4.77 MHz Intel 8088 microprocessor and 16 kilobytes of memory was sold for around \$1,600 in 1981 (which would be around \$4,000 today); nowadays a typical laptop PC with a 2.66 GHz Intel Core 2 Duo microprocessor and 4 gigabytes of memory costs only about one-third of \$4,000. These phenomenal improvements are ascribed to the sustained scaling of the metal-oxide-semiconductor field-effect transistor (MOSFET) [3] – the most important and fundamental building block for constructing integrated circuits.

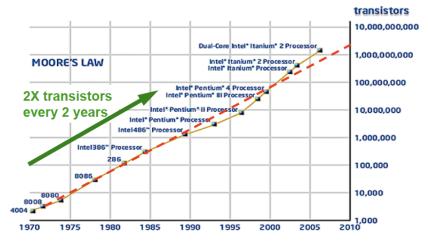

The simplicity of the MOSFET structure and the complementary symmetry of n-type and p-type MOSFETs have contributed to the success of complementary-MOSFET (CMOS) technology [4, 5]. Over the past few decades, CMOS scaling generally followed Moore's Law [6] (Fig. 1.1 [7]). Scaling theory [8, 9] provided simple rules for transistor design to increase circuit speed and density (Table 1.1). The improved circuit performance and density enable more complicated functionality, since more transistors and functionalities can be integrated on one single chip. The circuit density improvement also provides for reduction in manufacturing cost per function: with transistor scaling, the silicon die area is smaller for a given functionality, thus more dies can be fabricated from a single silicon wafer at very little marginal cost. Smaller die size is also beneficial for

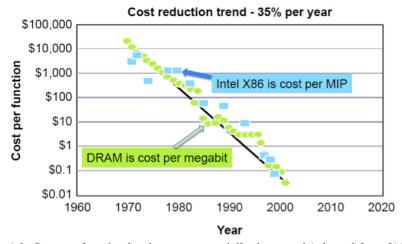

yield improvement [10]. As shown in Fig. 1.2 [11], cost per function has been exponentially decreased with every technology node.

Figure 1.1. Moore's Law: from few to billions of transistors (adapted from [7]).

| Device and circuit parameters                 | Constant-field scaling | Generalized scaling |

|-----------------------------------------------|------------------------|---------------------|

| Device dimensions $(L_G, T_{OX}, X_J, W)$     | $1/\kappa$             | $1/\kappa$          |

| Body doping concentration $(N_{\rm B})$       | κ                      | $lpha\kappa$        |

| Supply voltage $(V_{\rm DD})$                 | $1/\kappa$             | $\alpha/\kappa$     |

| Electric field ( <i>E</i> )                   | 1                      | $\alpha$            |

| Transistor current (I)                        | $1/\kappa$             | $\alpha/\kappa$     |

| Area (A)                                      | $1/\kappa^2$           | $1/\kappa^2$        |

| Capacitance (C = $\varepsilon_{OX}A/T_{OX}$ ) | $1/\kappa$             | $1/\kappa$          |

| Intrinsic delay $(\tau \sim CV_{DD}/I)$       | $1/\kappa$             | $1/\kappa$          |

| Power dissipation $(P \sim IV_{DD})$          | $1/\kappa^2$           | $\alpha^2/\kappa^2$ |

| Power density $(P/A)$                         | 1                      | $\alpha^2$          |

Table 1.1. Guidelines for MOSFET scaling (adapted from [8, 9, 12]).  $\kappa$  is the scaling factor for dimensions (> 1), and  $\alpha$  is a different scaling constant,  $\sim$  1.15 [13].

Figure 1.2. Cost per function has been exponentially decreased (adapted from [11]).

#### 1.2 MOSFET Scaling Challenges

Historically, the steady miniaturization of the conventional (planar bulk) MOSFET by simply scaling the device dimensions with minimal change to the conventional CMOS process flow has been effective to provide for continual improvements in integrated circuit performance and cost per function with every technology node. However, transistor scaling has become increasingly difficult in the sub-100 nm regime.

Material limits impose a natural barrier to continued scaling. Carrier mobilities are degraded due to higher vertical electric fields in the MOSFET channel [14, 15]. Mobility enhancement techniques such as strained-Si [16, 17, 18] and high-mobility channel materials [19, 20] have been actively pursued. Another fundamental material limit is faced by the gate oxide. Gate tunneling leakage becomes significant below 1 nm gate oxide thickness [21]. Further scaling can be realized by replacing the oxide/oxynitride gate dielectric with a high-permittivity (high-κ) gate dielectric [22].

As transistor dimensions are reduced, parasitic resistances and capacitances both scale unfavorably with reduced pitch. These parasitic elements will diminish the performance gain by transistor scaling [23].

Furthermore, power dissipation must be carefully considered in MOSFET scaling. Nowadays, passive power (due to transistor off-state leakage) constitutes a significant portion of the total power dissipation in high-performance CMOS products. The source-to-drain OFF-state leakage current ( $I_{\rm OFF}$ ) needs to be suppressed to mitigate passive power dissipation.  $I_{\rm OFF}$  increases exponentially with decreasing  $V_{\rm T}/S$ , where  $V_{\rm T}$  is the threshold voltage and S is the sub-threshold swing. Since S is fundamentally limited to be no less than 60mV/decade at room temperature due to the thermal distribution of carriers within energy bands,  $V_{\rm T}$  scaling has slowed down to avoid dramatic increases in  $I_{\rm OFF}$ . To achieve large drive current, the gate overdrive ( $V_{\rm DD}$  -  $V_{\rm T}$ ) needs to be significant and therefore  $V_{\rm DD}$  scaling also has to slow down, which results in increased active power density.

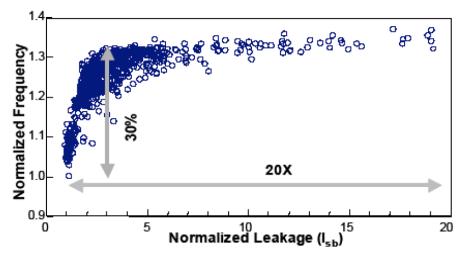

Finally, increased variability in transistor performance with each technology node poses critical challenges to future technology development, manufacturing, and design [24]. Improvements in transistor architecture and process control are needed to reduce variability. In addition, variability is detrimental to manufacturing yield, which will ultimately increase the cost per function, reducing the benefits of scaling. Fig. 1.3 [25] shows the distributions of chip frequency and leakage current of a large number of microprocessors. The variability in transistor performance causes about 20X variation in chip leakage and 30% variation in chip frequency, which substantially affects the yield [25]. Variability also affects power dissipation, since the nominal value of  $V_T$  needs to be kept high to avoid unacceptably large  $I_{OFF}$  and hence the pace of  $V_{DD}$  scaling needs to be

reduced to guarantee high performance. The impact of variability on design includes mismatch in analog/RF circuits and timing issues in digital circuits. To cope with the increased variability of scaled transistors, analog/RF circuit designers must increase the size of the critical transistors to reduce the impact of mismatch, and digital circuit designers must increase design margins [24]. These methods limit die area scaling and thus the economical benefit of scaling.

Figure 1.3. Leakage and frequency variations (adapted from [25]).

#### 1.3 Sources of Variability

Variation in transistor characteristics can be characterized by different root causes of these types of variation. There are two main categories of variation: systematic and random variations.

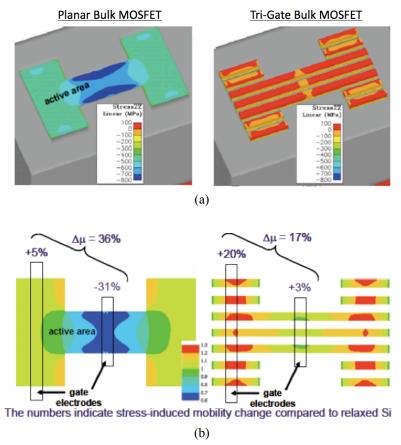

Systematic variation can further be divided into inter-die systematic variation and intra-die systematic variation [26]. Inter-die systematic variation is due to normal manufacturing tolerances. One example is gate length variation due to the length of lithographic exposure. Intra-die systematic variation comes from differences in either the device layout or the device neighborhood. For example, optical proximity effects cause the gate length to vary as a function of local layout. Resolution enhancement techniques such as optical proximity correction (OPC) and phase-shift masking (PSM) have been used in manufacturing to reduce systematic intra-die variation. However, these techniques are costly and increase process sensitivity. The use of stress to boost transistor performance is another source of systematic intra-die variation, since process-induced stress is dependent on layout.

Examples of random variation are photoresist line edge roughness (LER) (Fig. 1.4) and random dopant fluctuations. These variations are caused by fundamental phenomena associated with today's CMOS manufacturing processes. LER- and RDF-induced variations increase significantly with continued device scaling.

# EUV Resist Data 42 43 40 32 0 200 400 600 800 1000 Line Position (nm) Courtesy of Tom Wallow, Harry Levinson (AMD)

Figure 1.4. Plan-view scanning electron micrograph (SEM) of photoresist resist lines.

#### 1.4 Advanced MOSFET Structures

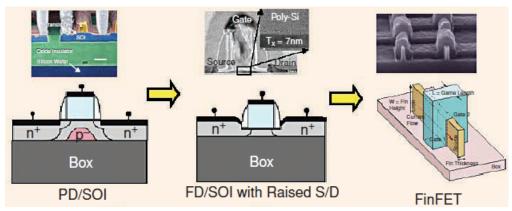

To address the scaling challenges of planar bulk CMOS technology, alternative MOSFET structures based on silicon-on-insulator (SOI) technology have been developed. Fig. 1.5 [27] illustrates three SOI MOSFET structures.

Figure 1.5. Advanced MOSFET structures: from PD SOI [28] to FD SOI with raised source/drain [29] to FinFET [30] (adapted from [27]).

Partially depleted (PD) SOI was the first SOI technology introduced for high-performance microprocessor applications [28, 31, 32]. The buried oxide (BOX) layer serves to provide for reduced source/drain junction capacitance. PD/SOI MOSFETs offer a good trade-off between power and performance.

Fully depleted (FD) SOI MOSFETs achieve superior control of short channel effects (SCE) and therefore are beneficial for low-power technologies which have stringent

leakage specifications. FD/SOI MOSFETs rely on a thin body to suppress leakage, which presents news challenge for transistor fabrication, mainly the tight control of the physical body thickness and doping profiles. Series resistance in the source and drain extension regions is another issue. An elevated source/drain structure is needed to mitigate this parasitic resistance, but this structure results in increased gate-to-drain capacitance (the Miller capacitance) and thus degrades circuit performance.

A thin-body structure with front- and back-gate electrodes allows the body thinness requirement of the FD/SOI MOSFET to be relaxed. This makes the back-gated thin-body MOSFET (e.g. an FD/SOI MOSFET with ultra-thin BOX) a good candidate for CMOS scaling.

The double-gate FinFET structure [30] can provide for improved electrostatic integrity over planar thin-body MOSFET structures. However, it requires the formation of high-aspect-ratio "fin" structures (of narrow width to suppress SCE and tall height to achieve high current per unit area) which pose a significant challenge for process control and design flexibility. By making the fin wider and much shorter, a tri-gate SOI MOSFET structure is formed, which is advantageous for manufacturability but which has poorer layout area efficiency (*i.e.* less current per unit area).

In summary, advanced MOFET structures have been developed to enable continued transistor scaling beyond the limit of the planar bulk MOSFET, but they also pose new challenges for integrated circuit manufacturing.

#### 1.5 This Work

This dissertation discusses MOSFET design and process technology for reduced variability. A quasi-planar tri-gate bulk MOSFET structure is proposed to provide an evolutionary pathway for CMOS scaling to the end of the roadmap. Through detailed modeling and simulation, scaling issues, device performance and variability of nanoscale MOSFETs are evaluated. The fabrication process for tri-gate bulk MOSFETs is also discussed.

In Chapter 2, the effect of gate line edge roughness (LER) on bulk-Si MOSFET performance is studied using statistical 3-D device simulations. The benefit of using a spacer gate lithography process to mitigate the effect of LER is assessed, with consideration of source/drain placement and spacer width variation.

In Chapter 3, a quasi-planar tri-gate bulk MOSFET design utilizing a low-aspect-ratio channel region is proposed to provide an evolutionary pathway for continued bulk CMOS scaling. The scalability and design optimization of tri-gate bulk MOSFET are investigated.

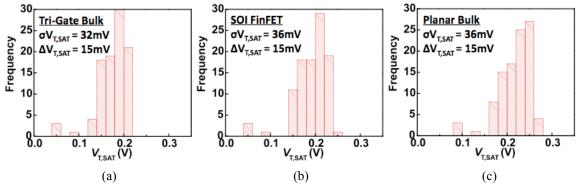

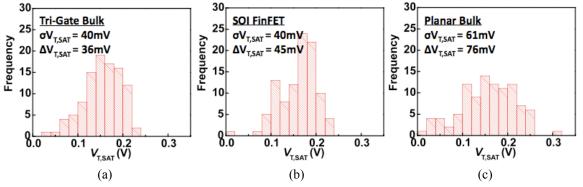

In Chapter 4, a variability study of the tri-gate bulk MOSFET is performed. The simulation results show that an optimized tri-gate bulk MOFET design offers less systematic variation as compared to planar bulk MOSFET and SOI FinFET designs, and comparable random variation as the SOI FinFET.

In Chapter 5, the fabrication process flow and the most critical processes for tri-gate bulk MOSFET fabrication are discussed. Initial device results show that tri-gate bulk MOSFET design is beneficial for reduced variability.

Chapter 6 summarizes the contributions of this work and offers directions for further research.

#### 1.6 References

- [1] R. N. Noyce, "Semiconductor device and lead structure," U.S. Patent #2,981,877, issued in April 1961.

- [2] J. S. Kilby, "Miniaturized electronic circuits," U.S. Patent #3,138,743, issued in June 1964.

- [3] D. Kahng, "Electric field controlled semiconductor device," U.S. Patent #3,102,230, issued in August 1963.

- [4] F. M. Wanlass and C. T. Sah, "Nanowatt logic using field-effect metal-oxide semiconductor triodes," *International Solid State Circuits Conference*, *Digest of Technical Papers*, pp. 32-33, 1963.

- [5] F. M. Wanlass, "Low stand-by power complementary field effect circuitry," U.S. Patent #3,356,858, issued in December 1967.

- [6] G. E. Moore, "Progress in digital integrated electronics," *IEDM Tech. Dig.*, pp. 11-13, 1975.

- [7] T. Ghani, "Challenges and innovations in nano-CMOS transistor scaling," *Nikkei Presentation*, October 2009.

- [8] R. H. Dennard, F. H. Gaensslen, H.-N. Yu, V. L. Rideout, E. Bassous, and A. LeBlanc, "Design of ion-implanted MOSFETs with very small physical dimensions," *IEEE J. Solid-State Circuits*, vol. 9, pp. 256-268, October 1974.

- [9] G. Baccarani, M. R. Wordeman, and R. H. Dennard, "Generalized scaling theory and its application to a 1/4 micrometer MOSFET design," *IEEE Trans. Electron Devices*, vol. 31, pp. 452-462, April 1984.

- [10] C. N. Berglund, "A unified yield model incorporating both defect and parametric effects," *IEEE Trans. Semiconductor Manufacturing*, vol. 9, No. 3, pp. 447-454, August 1996.

- [11] S. W. Jones, "Exponential trends in the integrated circuits industry", *ICKnowledge*, 2004.

- [12] T.-J. King Liu, and L. Chang, "Transistor scaling to the limit," *Moore's Law: Beyond Planar Silicon CMOS and into the Nano Era*, Springer-Verlag, 2008.

- [13] E. J. Nowak, "Maintaining the benefits of CMOS scaling when scaling bogs down," *IBM J. Research and Development*, vol. 46, pp. 169-180, 2002.

- [14] A. Lochtefeld and D. A. Antoniadis, "On experimental determination of carrier velocity in deeply scaled NMOS: How close to the thermal limit?," *IEEE Electron Device Lett.*, vol. 22, pp. 95-97, February 2001.

- [15] M. V. Fischetti and S. E. Laux, "Long-range Coulomb interactions in small Si devices. Part I: Performance and reliability," *J. Appl. Phys.*, vol. 89, pp. 1205-1231, January 2001.

- [16] J. Welser, J. L. Hoyt, and J. F. Gibbons, "Electron mobility enhancement in strained-Si n-type metal-oxide-semiconductor field-effect transistors," *IEEE Electron Device Lett.*, vol. 15, pp. 100-102, March 1994.

- [17] T. Mizuno, S. Takagi, N. Sugiyama, H. Satake, A. Kurobe, and A. Toriumi, "Electron and hole mobility enhancement in strained-Si MOSFET's on SiGe-on-insulator substrates fabricated by SIMOX technology," *IEEE Electron Device Lett.*, vol. 21, pp, 230-232, May 2000.

- [18] M. Saitoh, N. Yasutake, Y. Nakabayashi, K. Uchida, and T. Numata, "Understanding of strain effects on high-field carrier velocity in (100) and (110) CMOSFETs under quasi-ballistic transport", *IEDM Tech. Dig.*, pp. 469-472, 2009.

- [19] D. Kuzum, T. Krishnamohan, A. Nainani, Y. Sun, P. A. Pianetta, H. S-. P. Wong, and K. C. Saraswat, "Experimental demonstration of high mobility Ge NMOS," *IEDM Tech. Dig.*, pp. 453-456, 2009.

- [20] T. Ashley, M. T. Emeny, D. G. Hayes, K. P. Hilton, R. Jefferies, J. O. Maclean, S. J. Smith, A. W-H. Tang, D. J. Wallis, and P. J. Webber, "High-performance InSb based quantum well field effect transistors for low-power dissipation applications," *IEDM Tech. Dig.*, pp. 849-852, 2009.

- [21] T. Ghani, K. Mistry, P. Packan, S. Thompson, M. Stettler, S. Tyagi, and M. Bohr, "Scaling challenges and device design requirements for high performance sub-50nm gate length planar CMOS transistors," *Symp. VLSI Tech. Dig.*, pp. 174-175, 2000.

- [22] G. D. Wilk, R. M. Wallace, and J. M. Anthony, "High-κ gate dielectrics: Current status and materials properties considerations," *J. Appl. Phys.*, vol. 89, pp. 5243-5275, May 2001.

- [23] J.W. Sleight, I. Lauer, O. Dokumaci, D. M. Fried, D. Guo, B. Haran, S. Narasimha, C. Sheraw, D. Singh, M. Steigerwalt, X. Wang, P. Oldiges, D. Sadana, C.Y. Sung, W. Haensch, and M. Khare, "Challenges and opportunities for high performance 32 nm CMOS technology," *IEDM Tech. Dig.*, pp. 1-4, 2006.

- [24] S. Saxena, C. Hess, H. Karbasi, A. Rossoni, S. Tonello, P. McNamara, S. Lucherini, S. Minehane, C. Dolainsky, and M. Quarantelli, "Variation in transistor performance and leakage in nanometer-scale technologies," *IEEE Trans. Electron Devices*, vol. 55, pp. 131-144, January 2008.

- [25] S. Borkar, T. Karnik, S. Narendra, J. Tschanz, A. Keshavarzi, and V. De, "Parameter variations and impact on circuits and microarchitecture", *Proc. Conference on Design Automation*, pp. 338-342, 2003.

- [26] P. S. Zuchowski, P. A. Habitz, J. D. Hayes, and J. H. Oppold, "Process and environmental variation impacts on ASIC Timing," *Proc. International Conference on Computer-Aided Design*, pp. 336-342, 2004.

- [27] C.T. Chuang, K. Bernstein, R. V. Joshi, R. Puri, K. Kim, E. J. Nowak, T. Ludwig, and I. Aller, "Scaling planar silicon devices," *IEEE Circuits & Devices Magazine*, pp. 6-19, February 2004.

- [28] C.T. Chuang, P.F. Lu, and C.J. Anderson, "SOI for digital CMOS VLSI: Design considerations and advances," *Proc. IEEE*, vol. 86, pp. 689-720, April 1998.

- [29] B. Doris, M. Ieong, T. Kanarsky, Y. Zhang, R.A. Roy, O. Dokumaci, Z. Ren, F.F. Jamin, L. Shi, W. Natzle, H.J. Huang, J. Mezzapelle, A. Mocuta, S. Womack, M. Gribelyuk, E.C. Jones, R.J. Miller, H-S.P. Wong, and W. Haensch, "Extreme scaling with ultra-thin Si channel MOSFETs," *IEDM Tech. Dig.*, pp. 267-270, 2002.

- [30] J. Kedzierski, D. M. Fried, E. J. Nowak, T. Kanarsky, J. Rankin, H. Hanafi, W. Natzle, D. Boyd, Y. Zhang, R. Roy, J. Newbury, C. Yu, Q. Yang, P. Saunders, C. Willets, A. Johnson, S. Cole, H. Young, N. Carpenter, D. Rakowski, B. A. Rainey, P. Cottrell, M. leong, and P. Wong, "High-performance symmetric-gate and CMOScompatible V<sub>T</sub> asymmetric-gate FinFET devices," *IEDM Tech. Dig.*, pp. 437-440, 2001.

- [31] M. Canada, C. Akrout, D. Cawthron, J. Corr, S. Geissler, R. Houle, P. Kartschoke, D. Kramer, P. McCormick, N. Rohrer, G. Salem, and L. Warriner, "A 580 MHz RISC microprocessor in SOI," *ISSCC Tech. Dig.*, pp. 430-431, 1999.

- [32] D.H. Allen, A.G. Aipperspach, D.T. Cox, N.V. Phan, and S.N. Storino, "A 0.2 μm 1.8 V SOI 550 MHz 64 b PowerPC microprocessor with copper interconnects," *ISSCC Tech. Dig.*, pp. 438-439, 1999.

# Chapter 2

# Spacer Gate Lithography for Reducing Variability

#### 2.1 Introduction

Variability in transistor performance is one of the major challenges for continued scaling of CMOS technology. As transistor gate lengths are scaled down, gate line edge roughness (LER) is not reduced commensurately [1]. At the same time, thermal process budgets are reduced to achieve shallower and more abrupt source/drain junctions, so that the effects of gate LER become increasingly significant (Fig. 2.1). Thus, gate LER will be the dominant source of variability for channel lengths below 25nm [1]. The use of spacer lithography (also known as sidewall transfer lithography) to define fins has been experimentally demonstrated to be effective in reducing FinFET variability [2,3]. In this chapter, the effect of gate LER on bulk-Si MOSFET performance is studied using three-dimensional (3D) device simulations [4]. The use of spacer lithography to define the gate electrode is shown to be effective for reducing gate-LER-induced variability in MOSFET performance.

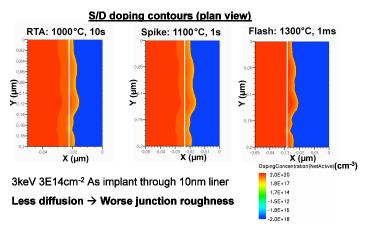

Figure 2.1. Plan view of source/drain (S/D) doping contours generated by the Sentaurus process simulator [4]. As the thermal budget for the dopant activation anneal is reduced, the effect of gate LER becomes increasingly significant.

#### 2.2 Spacer Lithography Process

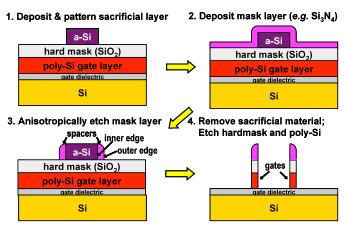

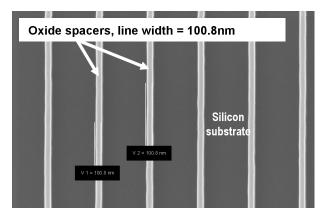

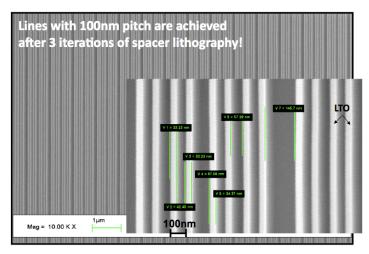

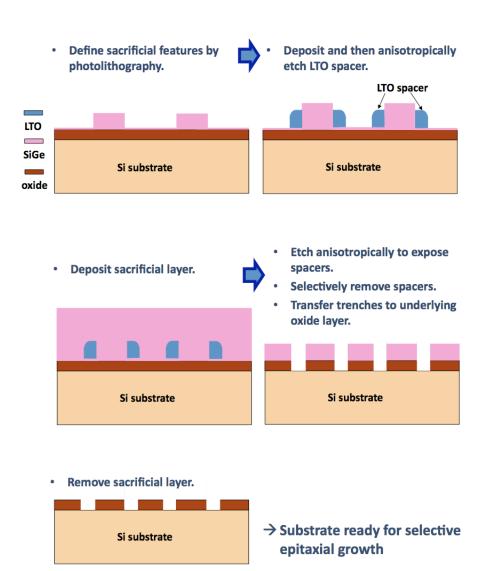

Spacer lithography is advantageous for defining fine-line features (lines and spaces) with tight line-width distribution [5]. An exemplary spacer lithography process flow is shown in Fig. 2.2. First, a sacrificial layer is deposited and patterned (into a geometrically regular array of lines and spaces) by conventional lithography. Then, a hard-mask layer is conformally deposited and anisotropically etched, so that hard-mask spacers remain along the sidewalls of the sacrificial material. The spacer width is determined by the thickness of the deposited hard-mask layer, which can be much smaller than the minimum feature size defined by conventional lithography, and very uniform (Fig. 2.3). Note that LER in the patterned sacrificial layer will result in LER for the "inner edges" of the spacers; the LER for the "outer edges" of the spacers will be correlated with that of the "inner edges," except that it will be smoothened due to the conformal nature of the hard-mask deposition process. As a result, the spacer width will always be equal to or greater than the thickness of the deposited hard-mask layer.

Figure 2.2. Illustrative spacer lithography process flow.

Figure 2.3. Plan-view scanning electron micrograph of oxide spacers formed using 248nm lithography to pattern the sacrificial layer. Very uniform line widths of sub-lithographic dimension (100.8 nm) are achieved.

After selective removal of the sacrificial material, the remaining hard-mask spacers can then be patterned (using conventional lithography and etch) to remove the spacers where gate lines are not desired. Larger feature sizes (if desired) can then be defined in another resist layer using conventional lithography. The resulting composite spacer + resist mask pattern can then be transferred to the underlying gate layer by a selective etch. Note that the minimum feature size and alignment tolerance for the lithography processes used to pattern the spacers and to define the larger feature sizes are much larger than those for a lithography process utilizing a single mask to pattern the gate layer, hence their associated costs should be much lower. Also, the geometrically regular mask used to pattern the sacrificial layer can be used for multiple chip designs, to save cost.

#### 2.3 Gate Line Edge Roughness (LER) Study

#### 2.3.1 Simulation Approach

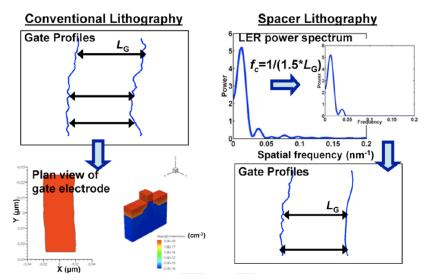

Gate line edge profiles were generated by MATLAB [6] based on measured LER data, and then input to Sentaurus [4] to generate 3D device structures for 3D device simulation (Fig. 2.4). This procedure was iterated to simulate many devices; then the simulated device I-V curves were used to assess variability in device performance. The LER and the line width roughness (LWR) values used for a conventional gate lithography process are 4nm and 6.4nm, respectively. The LWR for the electrical channel length ( $L_{\rm eff}$ ) was assumed to be the same as that for the gate, because this is the worst case (relevant for future ultra-shallow junction technology). To simulate gate line edge profiles for a spacer lithography process, the profile for one edge (the "inner edge") was duplicated, shifted by the nominal gate length  $L_{\rm G}$ , and then smoothened by filtering out the LER components with spatial frequency higher than  $1/(1.5*L_{\rm G})$  -- approximating the planarizing effect of a conformal deposition process -- to generate the profile for the other edge (the "outer edge"), as shown in Fig. 2.5. Note that, as a result of the smoothening, the width of the gate electrode at each location along the width of the transistor channel is

equal to or greater than  $L_G$ , for a spacer gate lithography process. This is in contrast to a conventional gate lithography process, for which the width of the gate electrode can also be less than  $L_G$ .

Figure 2.4. Procedure used to study the impact of LER on MOSFET performance.

Figure. 2.5. Gate electrode structure generation for conventional lithography vs. spacer gate lithography.

Simulations were performed for the following bulk-Si n-channel MOSFET designs, in order to assess the benefit of spacer gate lithography with gate-length scaling: 1)  $L_G$  = 32nm, channel width  $W_G$  = 64nm, equivalent oxide thickness EOT = 1.2nm, source/drain extension junction depth  $X_J$  = 11nm, supply voltage  $V_{DD}$  = 1.1V; 2)  $L_G$  = 14nm,  $W_G$  = 28nm, EOT = 0.5nm,  $X_J$  = 5nm,  $V_{DD}$  = 0.9V. The channel region is uniformly doped (p-type) in each case, to a concentration of  $3 \times 10^{18}$  cm<sup>-3</sup> and  $6 \times 10^{18}$  cm<sup>-3</sup> for  $L_G$  = 32nm and  $L_G$  = 14nm, respectively, to achieve drain induced barrier lowering less than 100mV/V. These design parameters are based on the International Technology Roadmap for Semiconductors (ITRS) [7]. It is assumed that gate LER is not reduced with  $L_G$  scaling.

#### 2.3.2 Results and Discussion

#### A. Spacer gate lithography vs. conventional gate lithography

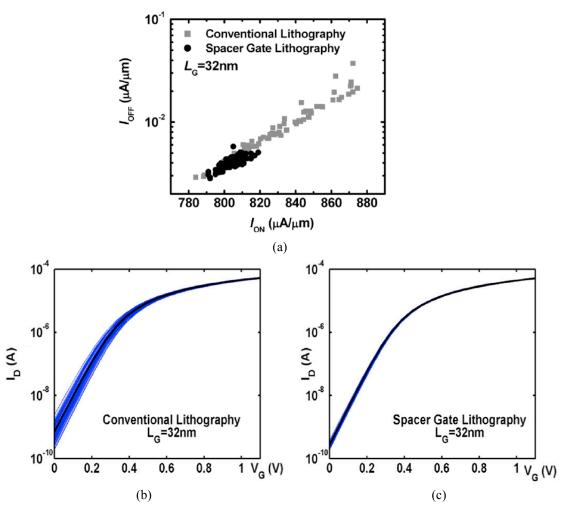

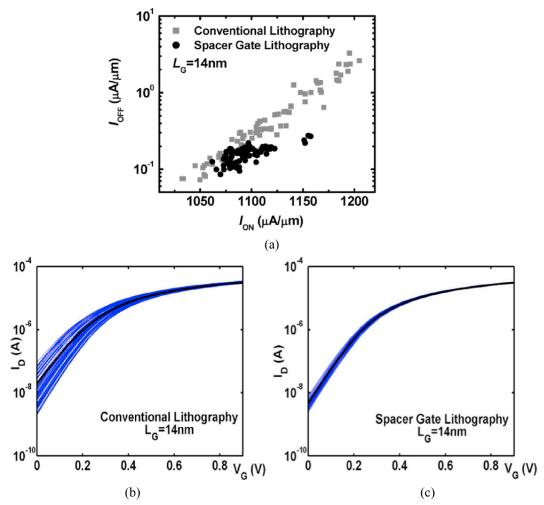

The simulated drain current vs. gate voltage characteristics ( $I_D$ - $V_G$ ) and  $I_{ON}$ - $I_{OFF}$  scatter plots (where  $I_{ON}$  is the on-state drive current for  $V_{GS} = V_{DS} = V_{DD}$ , and  $I_{OFF}$  is the off-state leakage current for  $V_{DS} = V_{DD}$  and  $V_{GS} = 0$ ) for conventional gate lithography and spacer gate lithography for  $L_G = 32$ nm and  $L_G = 14$ nm are shown in Fig. 2.6 and Fig.

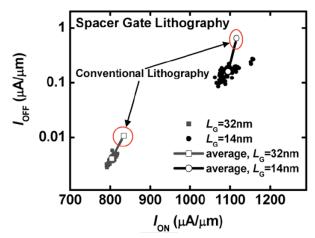

2.7, respectively. Spacer gate lithography dramatically reduces LER-induced variation. Fig. 2.8 shows that variability is well suppressed with gate-length scaling, even if LER does not scale. The average  $I_{\rm ON}$  and  $I_{\rm OFF}$  values for conventional gate lithography and spacer gate lithography are also indicated in Fig. 2.8. The average value and variance of  $I_{\rm OFF}$  are significantly reduced for spacer lithography; the variance of  $I_{\rm ON}$  is also reduced, while the average value of  $I_{\rm ON}$  is slightly degraded. This is because the average gate length along the width of the channel is larger for spacer lithography than for conventional gate lithography, as explained above. Thus, spacer gate lithography is preferable for smaller  $I_{\rm G}$ : variability is well suppressed, and  $I_{\rm OFF}$  is significantly reduced without significantly reducing  $I_{\rm ON}$ . (Note: as the thickness of the deposited hard-mask layer is reduced to scale down  $I_{\rm G}$ , the amount of LER smoothening for the "outer edge" is reduced and hence the increase in average gate length will be reduced.).

Figure 2.6. (a) Comparison of  $I_{\rm ON}$ - $I_{\rm OFF}$  for spacer vs. conventional gate lithography.  $L_{\rm G}$ =32nm. (b)  $I_{\rm D}$ - $V_{\rm G}$  curves for conventional gate lithography -- the heavy black line indicates the average  $I_{\rm D}$ - $V_{\rm G}$  curve. (c)  $I_{\rm D}$ - $V_{\rm G}$  curves for spacer gate lithography -- the heavy black line indicates the average  $I_{\rm D}$ - $V_{\rm G}$  curve.

Figure. 2.7. (a) Comparison of  $I_{\rm ON}$ - $I_{\rm OFF}$  for spacer vs. conventional gate lithography.  $L_{\rm G}$ =14nm. (b)  $I_{\rm D}$ - $V_{\rm G}$  curves for conventional gate lithography -- the heavy black line indicates the average  $I_{\rm D}$ - $V_{\rm G}$  curve. (c)  $I_{\rm D}$ - $V_{\rm G}$  curves for spacer gate lithography -- the heavy black line indicates the average  $I_{\rm D}$ - $V_{\rm G}$  curve.

Figure 2.8. Comparison of  $I_{\rm ON}$ - $I_{\rm OFF}$  for  $L_{\rm G}$ =14nm vs.  $L_{\rm G}$ =32nm, for spacer gate lithography. The average values for conventional gate lithography are also shown for reference.

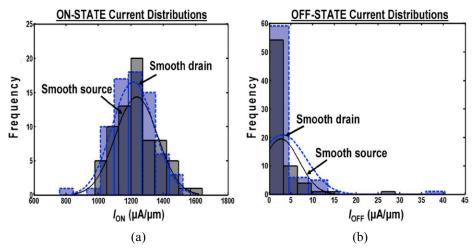

Since the "outer edge" of a spacer-defined gate is smoothened, the source and drain edge profiles are not perfectly correlated. The effect of source/drain placement is shown in Fig. 2.9. Since current is limited by thermionic emission over the source-to-channel potential barrier in the off state, variations in barrier height caused by electric-field crowding due to source-side gate edge roughness have more impact on  $I_{OFF}$ ; therefore, more reduction in  $I_{OFF}$  spread is obtained when the source edge profile is smoothened. The devices with smooth source profile have higher average  $I_{\rm ON}$  and lower average  $I_{\rm OFF}$ , because the electric-field crowding due to the drain-side gate edge roughness effectively reduces channel length, while the source-to-channel potential barrier lowering due to the electric-field crowding is eliminated. Since random dopant fluctuations (RDF) also have significant impact on deeply scaled MOSFETs [1,8], the effect of LER together with RDF in the source/drain and channel regions was studied using Kinetic Monte Carlo simulations, for the 14nm device design ( $L_{G, nominal} = 14nm$ ,  $W_{G} = 28nm$ , EOT = 0.5nm,  $X_{\rm J} = 5$ nm,  $V_{\rm DD} = 0.9$ V, channel doping concentration =  $6 \times 10^{18}$  cm<sup>-3</sup>). Fig. 2.10 shows that the performance advantages of devices with smooth source profile are retained in the presence of RDF.

Figure 2.9. Comparison of  $I_{\text{ON}}$ - $I_{\text{OFF}}$  for smooth source vs. smooth drain.  $L_{\text{G}}$ =14nm. (a)  $I_{\text{OFF}}$ - $I_{\text{ON}}$ . (b)  $I_{\text{ON}}$  distributions. (c)  $I_{\text{OFF}}$  distributions.

Figure. 2.10. Comparison of  $I_{\text{ON}}$ - $I_{\text{OFF}}$  for smooth source vs. smooth drain, including the effects of RDF.  $L_{\text{G}}$ =14nm. (a)  $I_{\text{ON}}$  distributions. (b)  $I_{\text{OFF}}$  distributions.

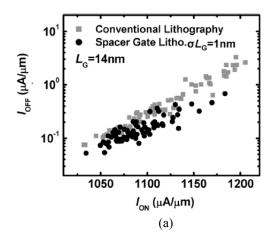

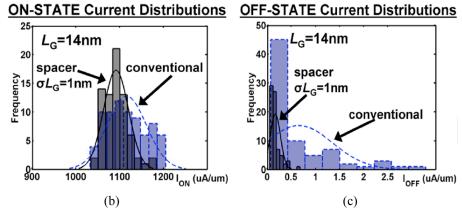

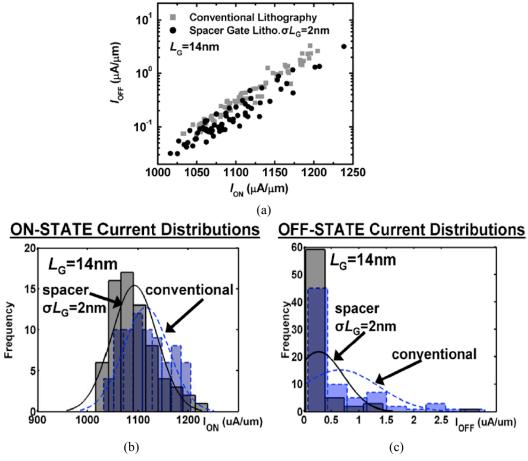

#### C. Effects of spacer width variation

Spacer gate lithography reduces LER-induced variation because the gate-edge profiles are correlated, resulting in lower LWR. However, other sources of variation are introduced in the spacer lithography process, such as film thickness non-uniformity, etch non-uniformity, etc. Device performance distributions for conventional gate lithography vs. spacer gate lithography are compared in Fig. 2.11 and Fig. 2.12 for spacer-width standard deviation values of 1nm and 2nm, respectively. The results show that spacer gate lithography reduces variability if the standard deviation in spacer width is less than 2nm. This is consistent with the LWR specified in the simulation inputs. (LWR is 6.4nm, which is very close to the  $3\sigma$  value.) For a 14nm spacer process,  $\leq$ 2nm standard deviation in spacer width is reasonable. Therefore, despite the additional sources of variation (other than LER), spacer gate lithography can significantly reduce variability in MOSFET performance.

Figure 2.11. Comparison of  $I_{\rm ON}$  and  $I_{\rm OFF}$  for spacer gate lithography ( $\sigma L_{\rm G}$ =1nm) vs. conventional gate lithography.  $L_{\rm G}$ =14nm, smooth source. (a)  $I_{\rm OFF}$  vs.  $I_{\rm ON}$ . (b)  $I_{\rm ON}$  distributions. (c)  $I_{\rm OFF}$  distributions.

Figure. 2.12. Comparison of  $I_{\rm ON}$  and  $I_{\rm OFF}$  for spacer gate lithography ( $\sigma L_{\rm G}$ =2nm) vs. conventional gate lithography.  $L_{\rm G}$ =14nm, smooth source. (a)  $I_{\rm OFF}$  vs.  $I_{\rm ON}$ . (b)  $I_{\rm ON}$  distributions. (c)  $I_{\rm OFF}$  distributions.

#### 2.4 Summary

As gate lengths and thermal process budgets are reduced, the effect of gate line edge roughness becomes increasingly significant. Statistical 3D device simulations show that spacer gate lithography is a scalable technology which can significantly reduce LER-induced variability in MOSFET performance.

#### 2.5 References

- [1] A. Asenov, "Simulation of statistical variability in nano MOSFETs," *Symp. VLSI Tech. Dig.*, pp. 86-87, 2007.

- [2] A. Kaneko, A. Yagishita, K. Yahashi, T. Kubota, M. Omura, K. Matsuo, I. Mizushima, K. Okano, H. Kawasaki, S. Inaba, T. Izumida, T. Kanemura, N. Aoki, K. Ishimaru, H. Ishiuchi, K. Suguro, K. Eguchi, and Y. Tsunashima, "Sidewall transfer process and selective gate sidewall spacer formation technology for sub-15nm FinFET with elevated source/drain extension," *IEDM Tech. Dig.*, pp. 863-866, 2005.

- [3] R. Rooyackers, E. Augendre, B. Degroote, N. Collaert, A. Nackaerts, A. Dixit, T. Vandeweyer, B. Pawlak, M. Ercken, E. Kunnen, G. Dilliway, F. Leys, R. Loo, M. Jurczak, and S. Biesemans, "Doubling or quadrupling MuGFET fin integration scheme with higher pattern fidelity, lower CD variation and higher layout efficiency," *IEDM Tech. Dig.*, pp. 993-996, 2006.

- [4] Sentaurus User's Manual, v. 2006.06 (Synopsys, Inc.)

- [5] Y.-K. Choi, T.-J. King, and C. Hu, "A spacer patterning technology for nanoscale CMOS," *IEEE Trans. Electron Devices*, Vol. 49, pp. 436-441, March 2002.

- [6] MATLAB User's Manual (The MathWorks, Inc.)

- [7] Int'l Technology Roadmap for Semiconductors, 2006 Update.

- [8] M. Miyamura, T. Fukai, T. Ikezawa, R. Ueno, K. Takeuchi, and M. Hane, "SRAM critical yield evaluation based on comprehensive physical / statistical modeling, considering anomalous non-Gaussian intrinsic transistor fluctuations," *Symp. VLSI Tech. Dig.*, pp. 22-23, 2007.

# Chapter 3

# **Tri-Gate Bulk MOSFET Design**

#### 3.1 Introduction

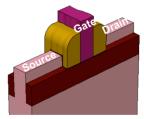

Challenges for continued scaling of bulk-Si CMOS technology include increased leakage current ( $I_{\rm OFF}$ ) [1] and variability in transistor performance [2]. Non-classical transistor structures such as thin-body MOSFETs [3] provide better control of short-channel effects (SCE) without the need for heavy channel surface doping and thus can reduce variability in threshold voltage ( $V_{\rm T}$ ) due to random dopant fluctuations (RDF). Although it is generally agreed that such structures (e.g. the FinFET [4] or the tri-gate silicon-on-insulator (SOI) FET [5]) will be necessary in the sub-20 nm gate length ( $L_{\rm G}$ ) regime, they require either expensive SOI substrates or more complex fabrication processes (e.g. [6]) and advanced compact models for circuit design, which present barriers to their adoption. For example, to circumvent the need for an SOI substrate, body-tied FinFETs have been investigated recently [7, 8, 9]. These devices have large channel aspect ratio, because they rely on a narrow and tall (fin-like) channel to suppress SCE and achieve good layout area efficiency, respectively. In this chapter we propose a tri-gate bulk MOSFET design which utilizes a low-aspect-ratio channel, for improved manufacturability.

#### 3.2 Tri-Gate Bulk MOSFET Structure

#### 3.2.1 Device Structure

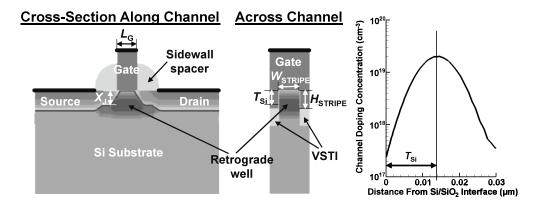

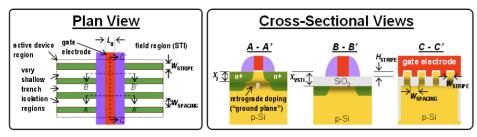

The channel region of a tri-gate bulk MOSFET consists of one or more parallel segments ("stripes") of equal width,  $W_{\rm STRIPE}$ , which can be substantially larger (by as much as  $\sim 4\times$ ) than  $L_{\rm G}$ . Within each stripe, the channel- and source/drain-doping profiles

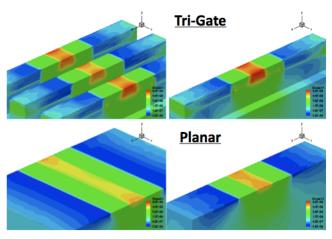

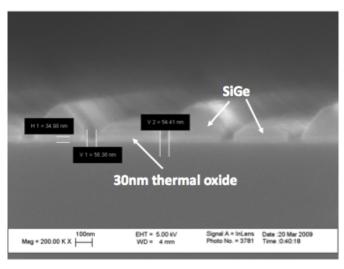

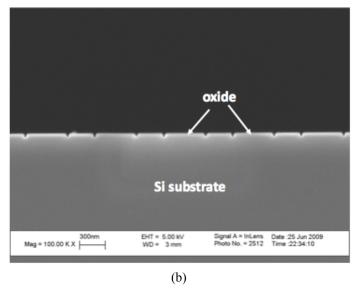

are similar to those in a planar bulk MOSFET, as illustrated in Fig. 3.1. The thickness of the lightly doped channel,  $T_{\rm Si}$ , corresponds to the depth of the retrograde channel doping, which can be controlled precisely by ion implantation. Note that the stripes within a single multi-stripe transistor are isolated by very shallow trench isolation (VSTI) oxide, which extends to a depth below the source/drain extension regions, but which can be much shallower than the STI oxide that is used to isolate individual transistors, so that there is no need to form high-aspect-ratio fins. The deep source/drain regions within a single multi-stripe transistor may be contiguous underneath the VSTI oxide. Such a segmented MOSFET structure may seem to be very complicated to manufacture. However, it can be fabricated in a relatively straightforward manner using a conventional process flow, starting with a substrate having a corrugated semiconductor surface planarized by VSTI oxide [10].

Figure 3.1. Cross-sectional views of the simulated 3-D tri-gate bulk MOSFET structure.

To provide for improved electrostatic integrity and layout area efficiency (effective channel width per unit layout width), the VSTI/STI oxide surrounding the active-area stripe(s) can be recessed by a small amount,  $H_{\rm STRIPE}$ , just prior to gate stack formation, so that the gate electrode wraps around the top portion of each stripe, resulting in a tri-gate structure. It should be noted that narrow-width MOSFETs (such as those used in SRAM cells) can be readily made into (single-stripe) tri-gate MOSFETs in this manner, *i.e.* simply by recessing the STI oxide prior to gate stack formation in a standard CMOS fabrication process. The combination of retrograde channel doping [11] with a multi-gate structure provides for superior electrostatic integrity as well as significantly reduced  $V_{\rm T}$  variation due to RDF [12, 13].

#### 3.2.2 Simulation Results and Discussion

Sentaurus 3-dimensional process and device simulations were performed using advanced physical models [14] to study the performance of tri-gate bulk MOSFETs *vs.* planar bulk MOSFETs. The retrograde well doping profiles were identical for these two device designs. Device parameters were selected based on ITRS specifications [15]. The well doping profile steepness is 4 nm/decade, which is less abrupt than required for the

source/drain extensions [15]. No mobility enhancement was assumed, although well-established techniques for inducing strain in the channel region can be readily applied.

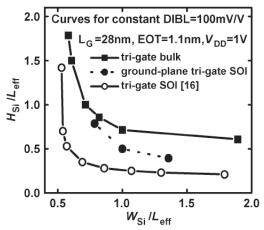

#### A. Tri-Gate Bulk MOSFET Benefit for Improved Scalability

The use of retrograde well doping (or halo doping) allows the tri-gate bulk MOSFET to achieve electrostatic integrity superior to that of the tri-gate SOI MOSFET design [5] because drain electric field penetration through the buried oxide (BOX) is eliminated. Therefore  $W_{\rm STRIPE}$  and/or  $T_{\rm Si}$  ( $\sim H_{\rm STRIPE}$ ) can be larger for the same degree of SCE control, as shown in Fig. 3.2. Note that the use of heavy doping beneath the BOX is less effective for the tri-gate SOI MOSFET, even if an ultra-thin (10nm-thick) BOX is used. For example,  $W_{\rm STRIPE}$  can be comparable to  $L_{\rm G}$  without requiring a channel thickness less than  $2/3L_{\rm G}$ , which is advantageous for improving manufacturability (since  $W_{\rm STRIPE}$  does not need to be less than  $L_{\rm G}$ ) and achieving good layout area efficiency (because the gated stripe sidewalls contribute to current conduction). The retrograde well doping profile also provides for light doping at the upper channel surfaces to mitigate corner conduction effects [16].

Figure 3.2. Stripe dimensions required to adequately suppress short-channel effects, from 3-D device simulations. For a specified amount of drain-induced barrier lowering (100 mV/V), the tri-gate bulk MOSFET offers higher layout efficiency than the tri-gate SOI transistor because taller stripes can be used (providing for more sidewall current conduction). This is the case even if the SOI device has a "ground plane" (doped to a concentration of 10<sup>20</sup> cm<sup>-3</sup>) beneath an ultra-thin (10nm-thick) BOX.

#### B. Tri-Gate Bulk MOSFET Benefit for Reduced Variability

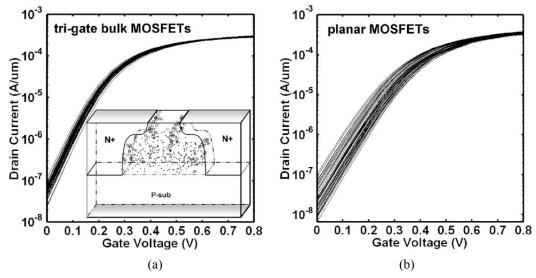

Fig. 3.3 shows drain current vs. gate voltage ( $I_{DS}$ - $V_{GS}$ ) characteristics (for 100 simulated cases) of tri-gate bulk MOSFETs and planar bulk MOSFETs with atomistic doping effects included, following the methodology described in [17, 18]. (Dopant atoms within the channel and the source/drain gradient regions were randomly placed (e.g. Fig.

3.3a inset) using a Monte Carlo algorithm [19].) Because the nominal (continuum) body and source/drain doping profiles are identical for the tri-gate and planar MOSFETs, the reduction in  $V_{\rm T}$  variation is due solely to their structural difference. The depletion charge density per unit channel width is smaller for the tri-gate structure, so that RDF effects are mitigated.

Figure 3.3. Simulated  $I_{\rm DS}$ - $V_{\rm GS}$  curves for transistors ( $L_{\rm G}=20$  nm) with discretely placed dopant atoms. Each curve corresponds to a different random placement of the source/drain-gradient and retrograde-channel dopant atoms, *e.g.* as shown in the inset in (a) where each square corresponds to an n-type dopant atom and each dot corresponds to a p-type dopant atom. Currents are normalized to effective channel width. (a) tri-gate bulk MOSFETs with  $W_{\rm STRIPE}=20$  nm,  $H_{\rm STRIPE}=14$  nm,  $W_{\rm SPACING}=20$  nm; (b) planar MOSFETs. Device layout width is 40 nm. EOT = 0.9 nm,  $X_{\rm J}=14$ nm, depth of retrograde channel doping  $T_{\rm Si}=14$ nm, gate work function = 4.1eV.

#### C. V<sub>T</sub> Adjustment via Doping and Body Biasing

The dependences of  $I_{\rm ON}$  and  $I_{\rm OFF}$  (normalized to layout width) on  $T_{\rm Si}$  ( $\sim H_{\rm STRIPE}$ ) and  $W_{\rm STRIPE}$  are shown in Fig. 3.4. (No strain-induced mobility enhancement is assumed.) The depth of the retrograde doping can be used to tune  $I_{\rm ON}$  vs.  $I_{\rm OFF}$ , so that  $V_{\rm T}$  can be adjusted without heavy channel surface doping or gate work function tuning. If  $T_{\rm Si}$  is less than one-half of  $W_{\rm STRIPE}$ , body biasing is effective for dynamic  $V_{\rm T}$  control to optimize the power vs. delay tradeoff, or for compensation of process-induced  $V_{\rm T}$  variations for improved parametric yield [1].

Figure 3.4. Simulated  $I_{\rm ON}$  &  $I_{\rm OFF}$  (normalized to layout width) for n+ poly-Si-gated tri-gate bulk MOSFETs with steep retrograde channel doping (peak concentration =  $2 \times 10^{19}$  cm<sup>-3</sup>, steepness = 4 nm/dec).  $L_{\rm G} = 20 \text{nm}$ ,  $W_{\rm STRIPE} = 20 \text{nm}$ , EOT = 0.9nm,  $V_{\rm DD} = 1 \text{V}$ . Values of the depth of retrograde channel doping  $T_{\rm SI}$  ( $\sim H_{\rm STRIPE}$ ) are indicated.  $X_{\rm J}$  and  $H_{\rm STRIPE}$  each increase with  $T_{\rm SI}$ . No mobility enhancement is assumed for the trigate bulk MOSFETs, in contrast to the ITRS specifications.

The tri-gate bulk MOSFET design provides an evolutionary pathway for bulk CMOS scaling to the end of the roadmap. The combination of retrograde channel doping with a multi-gate structure provides for superior electrostatic integrity, so that an ultra-thin/ultra-narrow channel is not required in order to suppress short-channel effects. As compared with the classic planar MOSFET design, the tri-gate bulk MOSFET also provides for reduced variability due to random dopant fluctuations. It also allows for  $V_T$  tuning via channel doping depth (vs. dose), as well as the possibility of dynamic  $V_T$  adjustment via body biasing for further yield improvement and/or versatility in circuit design.

#### 3.3 Scale Length Assessment

#### 3.3.1 Introduction

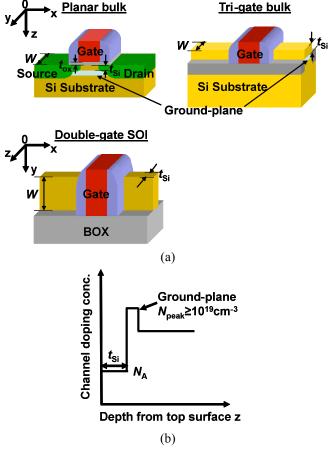

The planar ground-plane bulk MOSFET and double-gate SOI MOSFET structures have been studied as candidates to extend transistor scaling to its ultimate limit [11][20][21]. In section 3.2, the tri-gate bulk MOSFET design was proposed to provide the advantages of a multi-gate SOI MOSFET together with the advantages of a planar bulk MOSFET [22]. To assess its scaling limit, 3-dimensional (3-D) effects need to be considered. This section analytically derives the scale length for tri-gate and planar ground-plane bulk MOSFETs, and compares the scaling limit of different MOSFET designs (Fig. 3.5).

Figure 3.5. (a) 3-D view of MOSFET designs studied in this work. x = 0, y = 0, and z = 0 correspond to the location of the source-side gate edge, the center of the channel along its width, and the gate oxide-channel interface, respectively. (b) Channel doping profile for tri-gate and planar ground-plane bulk MOSFETs.

#### 3.3.2 Scale Length Derivation

The scale length of the tri-gate bulk MOSFET is derived herein, for the coordinate system shown in Fig. 3.5. The potential distribution  $\Phi(x,y,z)$  in the channel region is determined by Poisson's equation

$$\frac{d^2\Phi}{dx^2} + \frac{d^2\Phi}{dy^2} + \frac{d^2\Phi}{dz^2} = \frac{qN_A}{\varepsilon_{Si}}$$

(1)

for  $0 \le x \le L_{eff}$ ,  $-\frac{W}{2} \le y \le \frac{W}{2}$ , and  $0 \le z \le t_{Si}$ .  $N_A$  is the channel dopant concentration.

Parabolic potential variation between the two lateral gates (in the *y*-direction) is assumed [23] to describe the potential distribution:

$$\Phi(x, y, z) \approx a_0(x, z) + a_1(x, z)y + a_2(x, z)y^2$$

(2).

At y = 0, we assume a simple parabolic function in the z-direction [24]:

$$\Phi(x,0,z) = a_0(x,z) \approx c_0(x) + c_1(x)z + c_2(x)z^2$$

(3).

The boundary conditions are:  $\Phi(x,0,0) = \Phi_f(x) = a_0(x,0) = c_0(x)$  (4)

$$\frac{d\Phi}{dz}\bigg|_{y=0,z=0} = \frac{\varepsilon_{ox}}{\varepsilon_{Si}} \frac{\Phi_f(x) - \Phi_{gs}}{t_{ox}} = c_1(x)$$

(5)

$$\Phi(x,0,t_{Si}) = \Phi_{sb} = a_0(x,t_{Si}) = c_0(x) + t_{Si}c_1(x) + t_{Si}^2c_2(x)$$

(6)

$$\Phi(x, -\frac{W}{2}, z) = \Phi(x, \frac{W}{2}, z) \tag{7}$$

$$\Phi(x, \pm \frac{W}{2}, z) = \Phi_f(x) = a_0(x, z) + a_2(x, z) \frac{W^2}{4}$$

(8)

where  $\Phi_f(x)$  and  $\Phi_{sb}$  are the potentials at z=0 and  $z=t_{Si}$ .  $a_0(x,z)$  can be determined by the boundary conditions in Eqns. (4-6). From Eqn. (7), we obtain  $a_1(x,z)=0$ .  $a_2(x,z)=\frac{4}{W^2}[\Phi_f(x)-a_0(x,z)]$  is obtained by solving Eqn. (8). Using these boundary conditions, we obtain the following expression for the potential distribution within the channel:

$$\Phi(x,y,z) = \Phi_f(x) + \frac{\varepsilon_{ox}}{\varepsilon_{Si}} \frac{\Phi_f(x) - \Phi_{gs}}{t_{ox}} z - \left[ \frac{\Phi_f(x) - \Phi_{sb}}{t_{Si}^2} + \frac{\varepsilon_{ox}}{\varepsilon_{Si}} \frac{\Phi_f(x) - \Phi_{gs}}{t_{ox}t_{Si}} \right] z^2 - \left[ \frac{\Phi_f(x) - \Phi_{sb}}{t_{Si}^2} + \frac{\varepsilon_{ox}}{\varepsilon_{Si}} \frac{\Phi_f(x) - \Phi_{gs}}{t_{ox}t_{Si}} \right] z^2 \right\} y^2$$

(9).

The following equation is obtained by substituting (9) into (1) and setting y to 0:

$$\left(1 + \frac{\varepsilon_{ox}}{\varepsilon_{Si}} \frac{z}{t_{ox}} - \frac{z^{2}}{t_{Si}^{2}} - \frac{\varepsilon_{ox}}{\varepsilon_{Si}} \frac{z^{2}}{t_{ox}t_{Si}}\right) \frac{d^{2}\Phi_{f}(x)}{dx^{2}} - \left(\frac{8}{W^{2}} \frac{\varepsilon_{ox}}{\varepsilon_{Si}} \frac{z}{t_{ox}} - \frac{8}{W^{2}} \frac{\varepsilon_{ox}}{\varepsilon_{Si}} \frac{z^{2}}{t_{ox}t_{Si}} + \frac{\varepsilon_{ox}}{\varepsilon_{Si}} \frac{2}{t_{ox}t_{Si}}\right) \cdot \left[\Phi_{f}(x) - \Phi_{gs}\right] - \left(\frac{2}{t_{Si}^{2}} - \frac{8}{W^{2}} \frac{z^{2}}{t_{Si}^{2}}\right) \left[\Phi_{f}(x) - \Phi_{sb}\right] = \frac{qN_{A}}{\varepsilon_{Si}}$$

(10).

By making the following transformations

$$\lambda = \sqrt{\frac{1 + \frac{\varepsilon_{ox}}{\varepsilon_{Si}} \frac{z}{t_{ox}} - \frac{z^2}{t_{Si}^2} - \frac{\varepsilon_{ox}}{\varepsilon_{Si}} \frac{z^2}{t_{ox}t_{Si}}}{\frac{8}{W^2} \left(\frac{\varepsilon_{ox}}{\varepsilon_{Si}} \frac{z}{t_{ox}} - \frac{z^2}{t_{Si}^2} - \frac{\varepsilon_{ox}}{\varepsilon_{Si}} \frac{z^2}{t_{ox}t_{Si}}\right) + \frac{\varepsilon_{ox}}{\varepsilon_{Si}} \frac{2}{t_{ox}t_{Si}} + \frac{2}{t_{Si}^2}}}$$

(11)

$\phi(x) = \left(1 + \frac{\varepsilon_{ox}}{\varepsilon_{Si}} \frac{z}{t_{ox}} - \frac{z^{2}}{t_{Si}^{2}} - \frac{\varepsilon_{ox}}{\varepsilon_{Si}} \frac{z^{2}}{t_{ox}t_{Si}}\right) \Phi_{f}(x) + \frac{qN_{A}}{\varepsilon_{Si}} \lambda^{2}$   $-\left(\frac{8}{W^{2}} \frac{\varepsilon_{ox}}{\varepsilon_{Si}} \frac{z}{t_{ox}} - \frac{8}{W^{2}} \frac{\varepsilon_{ox}}{\varepsilon_{Si}} \frac{z^{2}}{t_{ox}t_{Si}} + \frac{\varepsilon_{ox}}{\varepsilon_{Si}} \frac{2}{t_{ox}t_{Si}}\right) \Phi_{gs} \lambda^{2} - \left(\frac{2}{t_{Si}^{2}} - \frac{8}{W^{2}} \frac{z^{2}}{t_{Si}^{2}}\right) \Phi_{sb} \lambda^{2}$  (12),

Eqn. (10) can be simplified to

and

$$\frac{d^2\phi(x)}{dx^2} - \frac{\phi(x)}{\lambda^2} = 0 \quad (13),$$

where  $\lambda$  is the scale length. In calculating  $\lambda$ , the value of z corresponding to the effective location of the conduction path of off-state leakage, *i.e.* the "weak spot" in the channel, should be used. Given the symmetry of the structure, y = 0 at the "weak spot":

$$\Phi(x,y,z) = \Phi_f(x) + \frac{\varepsilon_{ox}}{\varepsilon_{Si}} \frac{\Phi_f(x) - \Phi_{gs}}{t_{ox}} z - \left[ \frac{\Phi_f(x) - \Phi_{sb}}{t_{Si}^2} + \frac{\varepsilon_{ox}}{\varepsilon_{Si}} \frac{\Phi_f(x) - \Phi_{gs}}{t_{ox} t_{Si}} \right] z^2 \quad (14).$$

Eqn. (14) is a quadratic function of z, which reaches a maximum at

$$z_{peak} = \frac{\frac{\varepsilon_{ox}}{\varepsilon_{Si}} \frac{\Phi_f(x) - \Phi_{gs}}{t_{ox}}}{2 \cdot \left[ \frac{\Phi_f(x) - \Phi_{sb}}{t_{Si}^2} + \frac{\varepsilon_{ox}}{\varepsilon_{Si}} \frac{\Phi_f(x) - \Phi_{gs}}{t_{ox}t_{Si}} \right]} = \frac{1}{2\varepsilon_{Si}} \frac{t_{ox}}{\varepsilon_{ox}} \frac{\Phi_f(x) - \Phi_{sb}}{t_{Si}^2} + \frac{2}{t_{Si}}$$

(15).

In the off-state,  $\Phi_{sb} = \Phi_{gs} = 0$ , and Eqn. (15) is simplified to  $z_{peak} = \frac{1}{\frac{2\varepsilon_{Si}}{\varepsilon_{ox}} \frac{t_{ox}}{t_{Si}^2} + \frac{2}{t_{Si}}}$ , which

corresponds to the location of the highest leakage current density.

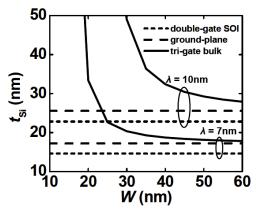

#### 3.3.3 Scale Length Comparison

Fig. 3.6 shows scale length contour lines for different values of channel width (W) and lightly doped channel thickness  $(t_{Si})$ . For reference, the scale length for the double-gate SOI MOSFET [20] design is also shown. As W increases, the scale length for the tri-gate bulk MOSFET approaches the value of the scale length for the planar ground-

plane bulk MOSFET (W>>t<sub>Si</sub>):

$$\lambda = \sqrt{\frac{1 + \frac{\varepsilon_{ox}}{\varepsilon_{Si}} \frac{z_{peak}}{t_{ox}} - \frac{z_{peak}^2}{t_{Si}^2} - \frac{\varepsilon_{ox}}{\varepsilon_{Si}} \frac{z_{peak}^2}{t_{ox}t_{Si}}}}{\frac{\varepsilon_{ox}}{\varepsilon_{Si}} \frac{2}{t_{ox}t_{Si}} + \frac{2}{t_{Si}^2}}}$$

. It should be noted

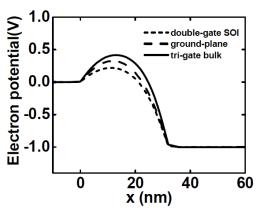

that this formula yields a larger scale length for the planar ground-plane MOSFET than the formula given in [11], because the scale length formula derived in [11] assumed that the off-state leakage path is at the gate oxide-channel interface so that it is overly optimistic. For given values of W and  $t_{\rm Si}$ , the scale length is smallest for the tri-gate bulk MOSFET design because it *combines* the benefit of a multi-gate structure (improved gate control) with the benefit of a ground-plane structure (leakage suppression). Fig. 3.7 shows the off-state electron potential distribution along the leakage path, for each of the transistor structures with identical channel dimensions (W and  $t_{\rm Si}$ ). The tri-gate bulk MOSFET has the least amount of drain-induced barrier lowering and therefore is most scalable.

Figure 3.6. Channel dimensions required to achieve 7nm and 10nm scale length.  $t_{ox} = 1$ nm

Figure 3.7. Off-state electron potential distribution along the leakage path.  $L_{\text{eff}} = 32 \text{nm}$ , W = 20 nm,  $t_{\text{Si}} = 20 \text{nm}$ ,  $t_{\text{ox}} = 1 \text{nm}$ ,  $V_{\text{dd}} = 1 \text{V}$ .

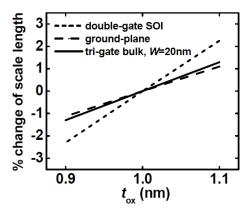

Fig. 3.8 shows the scale length sensitivity to  $t_{\rm ox}$  for different designs. Tri-gate and planar ground-plane bulk MOSFETs are less sensitive to  $t_{\rm ox}$  variation as compared with the double-gate SOI MOSFET, because they each employ a ground-plane to help suppress short channel effects (SCE), whereas the double-gate SOI structure relies on good gate control (*i.e.* a combination of ultra-thin  $t_{\rm ox}$  and thin  $t_{\rm Si}$ ) to suppress SCE.

Figure 3.8. Scale length sensitivity to  $t_{ox}$ . The  $t_{si}$  values are selected to obtain  $\lambda = 7$ nm at  $t_{ox} = 1$ nm.

# 3.4 Design Optimization of Tri-Gate Bulk MOSFET

As CMOS technology scaling continues, short-channel effects (SCE) and variability in transistor performance become increasingly difficult problems for the planar bulk MOSFET design [1, 2], so that alternative MOSFET designs eventually will be needed to extend transistor scaling into the sub-20nm gate length regime [15]. The FinFET [25] is a leading candidate: it utilizes the combination of a thin channel (which eliminates subsurface leakage paths) with a double-gate structure (which increases capacitive coupling between the gate and the channel) to suppress SCE and variability. However, the FinFET presents significant challenges for manufacturing because it requires the formation of narrow (sub-gate-length) fins [4] with uniform width [26] and large (>1) aspect ratio [27] particularly if a bulk silicon wafer is to be used [28].

The tri-gate bulk MOSFET design was proposed in section 3.2 to provide a more evolutionary pathway for continued transistor scaling [22]. It utilizes a combination of retrograde channel doping (which suppresses drain-induced barrier lowering, DIBL) with a triple-gate structure (which increases capacitive coupling between the gate and the channel) to suppress SCE and variability. Thus, it offers superior electrostatic integrity (hence scalability) as compared to the double-gate MOSFET (*i.e.* the FinFET) (as discussed in section 3.3, [29]), without requiring the formation of sub-gate-length or high-aspect-ratio features. In this section, design optimization and performance of trigate bulk MOSFETs [22] vs. bulk FinFETs [28] are compared.

Sentaurus 3-dimensional (3-D) device simulations were performed using advanced physical models [14] to study transistor performance as a function of the retrograde channel doping profile and the effective channel length ( $L_{\rm eff}$ ), physical channel width (W) and height ( $H_{\rm STRIPE}$ ). 3-D quantization effects were included using the density gradient quantization model. Hydrodynamic model (physical parameters tuned according to Monte Carlo simulation results) was used to model the transport of the carriers [14]. The values used for the supply voltage  $V_{\rm DD}$  and other device design parameters were based on ITRS low-operating-power (LOP) specifications at gate length ( $L_{\rm G}$ ) values of 18nm and 13nm [15]. For simplicity, no mobility enhancement was assumed.

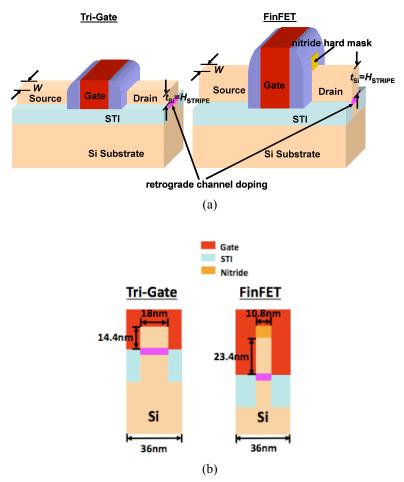

#### 3.4.1 Tri-Gate vs. FinFET Design Optimization

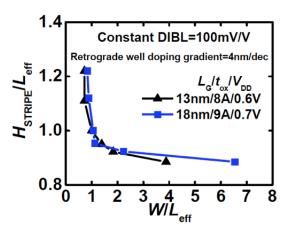

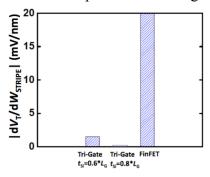

In principle, the height  $(H_{\rm STRIPE})$  of a FinFET can be made to be very tall to achieve high layout efficiency, *i.e.* large effective channel width  $(W_{\rm eff})$  per unit layout area. In practice, however, shorter fins are preferred for ease of manufacture and for design flexibility (*i.e.* to allow for finer increments in designed  $W_{\rm eff}$ ). Therefore, optimized bulk tri-gate and FinFET designs of the same  $W_{\rm eff}$  are compared (for each  $H_{\rm STRIPE}$  of the tri-gate design). Fig. 3.9 shows 3-D and cross-sectional views (across the channel) of the tri-gate and FinFET structures, for  $L_{\rm G}=18$ nm. Note that they are assumed to have the same channel stripe pitch  $(2*L_{\rm G})$ , which is an aggressive estimation), as this is set by

lithography limitations. For the tri-gate design,  $H_{\rm STRIPE}$  values are set to  $0.6*L_{\rm G}$  (lower bound for high  $I_{\rm ON}$  and good manufacturability) and  $0.8*L_{\rm G}$  (upper bound for less than  $100 \, {\rm mV/V}$  DIBL when the silicon stripe width W and effective channel length  $L_{\rm eff}$  are each equal to  $L_{\rm G}$ , from Fig. 3.10).  $t_{\rm Si}$  (the peak depth of the retrograde channel doping profile) is set to be equal to  $H_{\rm STRIPE}$ .  $L_{\rm eff}$  is then optimized (in practice by adjusting the width of the gate-sidewall spacers) to maximize the on-state drive current ( $I_{\rm ON}$ ) for a fixed  $7 \, {\rm nA/\mu m}$  off-state leakage current ( $I_{\rm OFF}$ ) as specified for double-gate FETs [15], while maintaining DIBL to be less than  $100 \, {\rm mV/V}$ . The optimal design is then obtained to minimize intrinsic delay  $C_{\rm total}*V_{\rm DD}/I_{\rm eff}$ , where  $C_{\rm total}$  is the total gate capacitance, and  $I_{\rm eff}$  is the average of the drain current  $I_{\rm D}$  for  $V_{\rm GS}=V_{\rm DD}$  and  $V_{\rm DS}=V_{\rm DD}/2$  and  $I_{\rm D}$  for  $V_{\rm GS}=V_{\rm DD}/2$  and  $V_{\rm DS}=V_{\rm DD}/2$

Figure 3.9. (a) 3-D and (b) cross-sectional views (across the channel) of the simulated tri-gate and FinFET bulk MOSFET structures, for  $L_G = 18$ nm.

Figure 3.10. Stripe dimensions required to adequately suppress short-channel effects, from 3-D device simulations.

For the FinFET design, the value of  $H_{\rm STRIPE} = t_{\rm Si}$  is selected to provide the same  $W_{\rm eff}$  as the tri-gate design, i.e.  $H_{\rm STRIPE,FinFET} = 0.5*[W_{\rm Tri-Gate} + 2*H_{\rm STRIPE,Tri-Gate}]$ , and the maximum value of W that meets the  $100 \, {\rm mV/V}$  DIBL specification is selected ( $W = 0.6*L_{\rm G}$ ).  $L_{\rm eff}$  is then adjusted to maximize  $I_{\rm ON}$  and to minimize delay. The thickness of the nitride hard-mask layer is assumed to be equal to  $L_{\rm G}$ .

A lower-aspect-ratio tri-gate bulk MOSFET design, with  $W = 2*L_G$  and channel stripe pitch =  $4*L_G$  (which is the worst case for layout area efficiency and fringing capacitance), is also investigated to find the optimal physical channel width for tri-gate design.

For all designs, source/drain contacts are assumed to be made along the top and sidewall surfaces of the source/drain regions. The gate work function is assumed to be around 4.2 to 4.5eV, which is experimentally achievable [30].

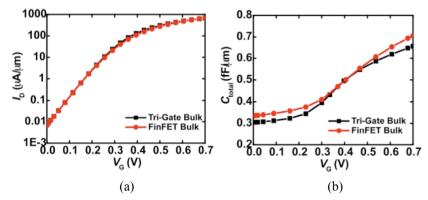

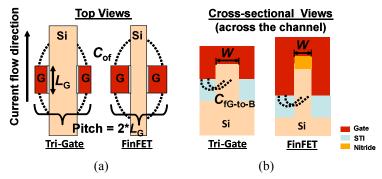

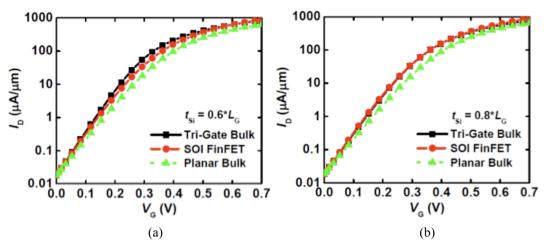

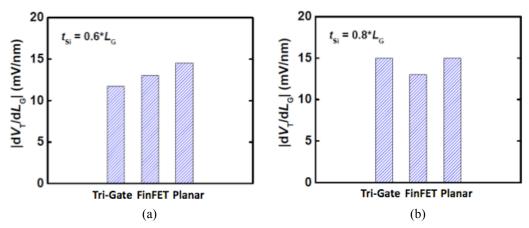

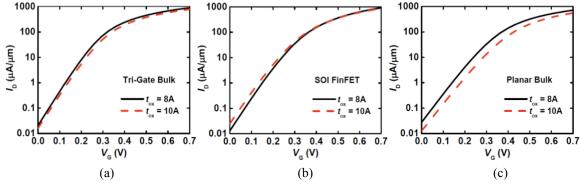

The DC and AC characteristics of the tri-gate and FinFET bulk MOSFETs with same  $W_{\rm eff}$  are shown in Fig. 3.11.  $I_{\rm ON}$  normalized to  $W_{\rm eff}$  is larger for the FinFET design, due to lower average channel doping. Note that the source/drain lateral doping gradient (2 nm/dec) [15] and retrograde well doping gradient (4 nm/dec) are assumed to be the same for the tri-gate and FinFET designs. Since the doping profiles in a FinFET likely would be less abrupt in practice (because it is more difficult to form a steep retrograde profile and abrupt source/drain profiles at the base of a tall stripe),  $I_{\rm ON}$  is overestimated for the FinFET. 3-D simulated total gate capacitance is also larger for the FinFET design, due to larger fringing capacitances, as illustrated in Fig. 3.12. Since the FinFET has a narrower and taller stripe, the thickness and height of the gate electrode along the channel-stripe sidewalls are larger for the FinFET design, resulting in larger outer fringing capacitance ( $C_{\rm of}$ ). Similarly, the gate-to-substrate coupling capacitance is also larger for the FinFET design.

Figure 3.11. Comparison of simulated characteristics for bulk MOSFETs: (a) DC characteristics, (b) AC characteristics.  $L_G = 18$ nm,  $t_{ox} = 9$ A,  $V_{DD} = 0.7$ V,  $L_{eff} = 22$ nm.

Figure 3.12. Illustration of parasitic capacitances in multi-gate MOSFET structures. (a) Outer fringing capacitance  $C_{\rm of}$ , (b) Gate-to-substrate capacitance  $C_{\rm fG-to-B}$ .

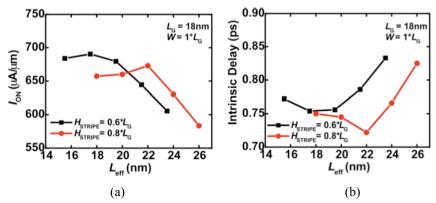

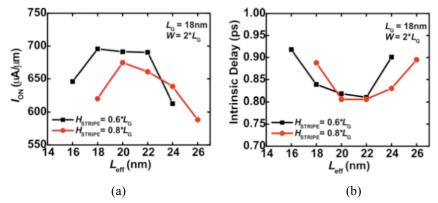

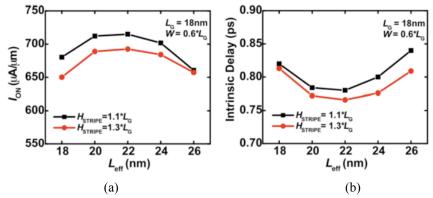

Figs. 3.13a and 3.13b show the  $L_{\text{eff}}$  dependence of  $I_{\text{ON}}$  and intrinsic delay, respectively, for different values of  $H_{\text{STRIPE}}$ , with  $W = 1*L_{\text{G}}$ , channel stripe pitch =  $2*L_{\text{G}}$ . It can be seen from Fig. 3.13b that the optimal design with larger  $H_{\text{STRIPE}}$  has larger  $L_{\text{eff}}$ (wider gate-sidewall spacers, smaller  $C_{\rm of}$ ) and smaller minimum intrinsic delay. The trigate bulk MOSFET design with  $W = 2*L_G$  and channel stripe pitch =  $4*L_G$  shows poorer intrinsic delay (Fig. 3.14b) due to degraded  $I_{ON}$ , consistent with a larger scale length [29]. For the FinFET design ( $W = 0.6*L_G$ , channel stripe pitch =  $2*L_G$ ), a larger value of  $H_{\text{STRIPE}}$  is advantageous to achieve smaller delay, since the ratio of  $C_{\text{of}}$  over total gate capacitance is smaller (Fig. 3.15b). Based on the results in Figs. 3.13, 3.14, and 3.15, the tri-gate bulk MOSFET design with  $W = 1*L_G$  is optimal to minimize intrinsic delay. Fig. 3.16 show the effect of retrograde channel doping gradient on MOSFET performance. Note that the retrograde doping gradients that are used in the simulations range from 5 nm/dec and aggressively down to 1 nm/dec, for the purpose of finding the optimal doping gradient value. In practice, steep retrograde doping profiles (3 nm/dec ~ 4 nm/dec) can be achieved by utilizing diffusion-barrier layers [31]. For the tri-gate design, there exists an optimal value of retrograde doping gradient that optimizes the trade-off between mobility and SCE suppression; for the FinFET design, which does not rely on retrograde channel doping to suppress SCE, the retrograde doping gradient generally should be as steep as possible in order to minimize mobility degradation. Therefore, the optimal

retrograde channel doping gradient for the tri-gate design is less steep than that for the FinFET design, and is easier to attain in practice.

Figure 3.13. Tri-gate bulk MOSFET design optimization for channel stripe width  $W = L_G$ . (a)  $I_{ON}$  vs.  $L_{eff}$ , for  $I_{OFF} = 7$  nA/ $\mu$ m, (b) Delay vs.  $L_{eff}$ .  $L_G = 18$ nm,  $t_{ox} = 9$ A,  $X_{J,SD} = 1.2*H_{STRIPE}$ ,  $t_{Si} = H_{STRIPE}$ ,  $V_{DD} = 0.7$ V.

Figure 3.14. Tri-gate bulk MOSFET design optimization for channel stripe width  $W = 2*L_{\rm G}$ . (a)  $I_{\rm ON}$  vs.  $L_{\rm eff}$ , for  $I_{\rm OFF} = 7$  nA/ $\mu$ m, (b) Delay vs.  $L_{\rm eff}$ .  $L_{\rm G} = 18$ nm,  $t_{\rm ox} = 9$ A,  $X_{\rm J,SD} = 1.2*H_{\rm STRIPE}$ ,  $t_{\rm Si} = H_{\rm STRIPE}$ ,  $V_{\rm DD} = 0.7$ V.

Figure 3.15. FinFET bulk MOSFET design optimization. (a)  $I_{ON}$  vs.  $L_{eff}$ , for  $I_{OFF} = 7$  nA/ $\mu$ m, (b) Delay vs.  $L_{eff}$ .  $L_{G} = 18$ nm,  $W = 0.6*L_{G}$ ,  $t_{ox} = 9$ A,  $X_{J,SD} = 1.2*H_{STRIPE}$ ,  $t_{Si} = H_{STRIPE}$ ,  $V_{DD} = 0.7$ V.

Figure 3.16. Impact of retrograde channel doping gradient on the performance of tri-gate bulk and FinFET bulk MOSFETs. For the tri-gate design,  $W = 1*L_{\rm G}$ ,  $H_{\rm STRIPE} = 0.8*L_{\rm G}$ ; for the FinFET design,  $W = 0.6*L_{\rm G}$ ,  $H_{\rm STRIPE} = 1.3*L_{\rm G}$ . (a)  $L_{\rm G} = 18$ nm,  $t_{\rm ox} = 9$ A,  $t_{\rm Si} = H_{\rm STRIPE}$ ,  $V_{\rm DD} = 0.7$ V, (b)  $L_{\rm G} = 13$ nm,  $t_{\rm ox} = 8$ A,  $t_{\rm Si} = H_{\rm STRIPE}$ ,  $V_{\rm DD} = 0.6$ V.

#### 3.4.2 Variability Study

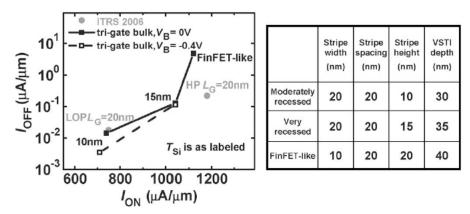

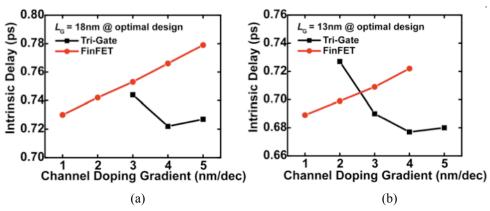

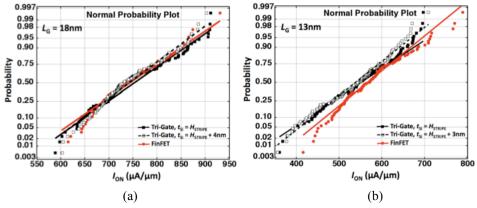

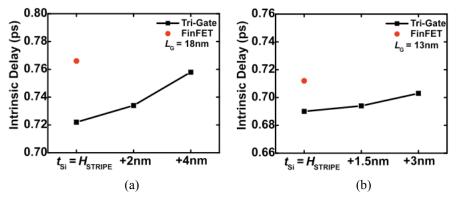

The impact of gate line edge roughness (LER) together with random dopant fluctuations (RDF) on bulk tri-gate and FinFET designs is studied using Kinetic Monte Carlos simulations [14]. The LER value used in the simulations is 4nm. For a fair comparison, the nominal structures for tri-gate and FinFET designs are the optimal structures (with minimum intrinsic delay) with the same source/drain lateral doping gradient (2nm for  $L_G$  = 18nm, 1.5nm for  $L_G$  = 13nm) and retrograde well doping gradient (4nm for  $L_G$  = 18nm, 3nm for  $L_G$  = 13nm). Figs. 3.17a and 3.17b show  $I_{ON}$  distributions for  $I_G$  = 18nm and  $I_G$  = 13nm, respectively. As compared to FinFET designs, the  $I_{ON}$  variations are larger for tri-gate designs with  $I_{Si}$  =  $I_{STRIPE}$  due to higher average channel doping. Comparable  $I_{ON}$  variations can be achieved by making  $I_{Si}$  larger than  $I_{STRIPE}$  in tri-gate designs while still maintaining smaller intrinsic delay than FinFET designs (Fig. 3.18).

Figure 3.17.  $I_{ON}$  distributions due to LER and RDF. (a)  $L_G = 18$ nm,  $t_{ox} = 9$ A,  $V_{DD} = 0.7$ V, (b)  $L_G = 13$ nm,  $t_{ox} = 8$ A,  $V_{DD} = 0.6$ V.

Figure 3.18. Tri-gate design intrinsic delay dependence on  $t_{\rm Si}$ . (a)  $L_{\rm G}=18$ nm,  $t_{\rm ox}=9$ A,  $V_{\rm DD}=0.7$ V, (b)  $L_{\rm G}=13$ nm,  $t_{\rm ox}=8$ A,  $V_{\rm DD}=0.6$ V.

Table 3.1 summarizes the parameters for the optimized tri-gate and FinFET bulk MOSFET designs. The tri-gate bulk MOSFET design offers comparable (or even less) delay, with less aggressive features (stripe width, stripe aspect ratio, retrograde doping gradient) for improved manufacturability.

|                                                             | Parameter                                   | Finl | FET  | Tri- | Gate |

|-------------------------------------------------------------|---------------------------------------------|------|------|------|------|

| Design $L_{\rm G}  ({\rm nm})$                              |                                             | 18   | 13   | 18   | 13   |

|                                                             | $T_{\rm ox}$ (nm)                           | 0.9  | 0.8  | 0.9  | 0.8  |

|                                                             | Gate work function (eV)                     | 4.51 | 4.45 | 4.35 | 4.34 |

|                                                             | $L_{\mathrm{eff}}\left(\mathrm{nm}\right)$  | 22   | 17   | 22   | 17   |

|                                                             | $W/L_{ m G}$                                | 0.6  | 0.6  | 1    | 1    |

|                                                             | $H_{ m STRIPE}/L_{ m G}$                    | 1.3  | 1.3  | 0.8  | 0.8  |

|                                                             | Retrograde gradient (nm/dec)                | 1    | 1    | 4    | 4    |

| Performance                                                 | $I_{\rm ON}  (\mu {\rm A}/\mu {\rm m})$     | 754  | 592  | 673  | 531  |

| $(V_{\rm DD} = 0.7 \text{V for } L_{\rm G} = 18 \text{nm},$ | (for $I_{OFF} = 7 \text{ nA/}\mu\text{m}$ ) |      |      |      |      |

| $V_{\rm DD} = 0.6 \text{V for } L_{\rm G} = 13 \text{nm}$   | CV/I <sub>eff</sub> (ps)                    | 0.73 | 0.69 | 0.72 | 0.68 |

Table 3.1. Optimal designs for the tri-gate and FinFET bulk MOSFETs.

# 3.5 Summary

The tri-gate bulk MOSFET structure is proposed to provide an evolutionary pathway for continued CMOS scaling. An analytical equation for the scale length of a tri-gate bulk MOSFET is derived. As compared with the double-gate SOI MOSFET, the tri-gate bulk MOSFET design is more scalable and less sensitive to device design parameters. As

compared with the bulk FinFET design, the tri-gate bulk MOSFET design offers comparable performance and variability. Its low-aspect-ratio channel structure is favorable for ease of manufacturing. Thus, the tri-gate bulk MOSFET is a promising structure for CMOS transistor scaling to the end of the technology roadmap.

#### 3.6 References

- [1] S. Borkar, "Circuit techniques for subthreshold leakage avoidance, control, and tolerance," *IEDM Tech. Dig.*, pp. 421-424, 2004.

- [2] H. Masuda, S. Ohkawa, A. Kurokawa, and M. Aoki, "Challenge: variability characterization and modeling for 65- to 90-nm process," *Custom Integrated Circuits Conf.*, pp. 593-599, 2005.

- [3] Y.-K. Choi, K. Asano, N. Lindert, V. Subramanian, T.-J. King, J. Bokor, and C. Hu, "Ultra-thin-body SOI MOSFET for deep-sub-tenth micron era," *IEEE Electron Device Lett.*, vol. 21, pp. 254–255, May 2000.

- [4] N. Lindert, L. Chang, Y.-K. Choi, E.H. Anderson, W.-C. Lee, T.-J. King, J. Bokor, and C. Hu, "Sub-60-nm quasi-planar FinFETs fabricated using a simplified process," *IEEE Electron Device Lett.*, vol. 22, pp. 487–489, October 2001.

- [5] B.S. Doyle, S. Datta, M. Doczy, S. Hareland, B. Jin, J. Kavalieros, T. Linton, A. Murthy, R. Rios, and R. Chau, "High performance fully-depleted tri-gate CMOS transistors," *IEEE Electron Device Lett.*, Vol. 24, pp. 263-265, April 2003.

- [6] M. Jurczak, T. Skotnicki, M. Paoli, B. Tormen, J. Martins, J. L. Regolini, D. Dutartre, P. Ribot, D. Lenoble, R. Pantel, and S. Monfray, "Silicon-on-Nothing (SON)-an innovative process for advanced CMOS," *IEEE Trans. Electron Devices*, Vol. 47, pp. 2179-2187, November 2000.

- [7] T. Park, S. Choi, D.H. Lee, J.R. Yoo, B.C. Lee, J.Y. Kim, C.G. Lee, K.K. Chi, S.H. Hong, S.J. Hynn, Y.G. Shin, J.N. Han, I.S. Park, U.I. Chung, J.T. Moon, E. Yoon, and J.H. Lee, "Fabrication of body-tied FinFETs (Omega MOSFETs) using bulk Si wafers," *Symp. VLSI Tech. Dig.*, pp. 135-136, 2003.

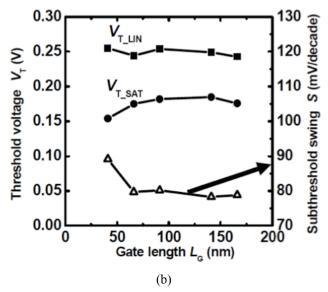

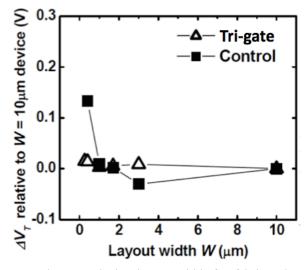

- [8] T.-S. Park, H. J. Cho, J. D. Choe, I. H. Cho, D. Park, E. Yoon, and J.H. Lee, "Characteristics of body-tied triple-gate pMOSFETs," *IEEE Electron Device Lett.*, vol. 25, pp. 798-800, December 2004.