## UC San Diego Technical Reports

**Title** Event-Driven Multithreaded Dyanmic Optimization

Permalink https://escholarship.org/uc/item/35m7m747

Author Zhang, Weifeng

Publication Date 2006-12-09

Peer reviewed

### UNIVERSITY OF CALIFORNIA, SAN DIEGO

Event-Driven Multithreaded Dynamic Optimization

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

$\mathrm{in}$

Computer Science

by

Weifeng Zhang

Committee in charge:

Professor Bradley Calder, Chair Professor Dean Tullsen, Co-Chair Professor Paul Chau Professor Ranjit Jhala Professor Chandra Krintz

2006

Copyright Weifeng Zhang, 2006 All rights reserved. The dissertation of Weifeng Zhang is approved, and it is acceptable in quality and form for publication on microfilm:

Chair

Co-Chair

University of California, San Diego

2006

#### DEDICATIONS

I dedicate this work to my family, the most important people in my life. To my wife, Xuejun, for her love, patience, and support throughout my study at UCSD. To my son, Brandon, and my daughter, Sophia, for bringing love and joy to my life. To my parents, my brother, and my sisters for their support and encouragement.

I owe sincere thanks to my advisors, Dr. Bradley Calder and Dr. Dean Tullsen, for their excellent guidance, inspiration, and support. I would also like to thank the other committee members, Dr. Paul Chau, Dr. Ranjit Jhala, and Dr. Chandra Krintz for their suggestions and final approval to my thesis.

I also owe significant thanks to all members in the Processor Architecture and Compilation Lab, Gilles, Erez, Jeremy, Satish, Rakesh, Jeff, Weihaw, Michael, Subhra, Jack, Ganesh, Matt, Allen, Anthony, Steve, Leo, and Cristiano, for fruitful discussions and making my time at UCSD enjoyable. Needless to say, this is the best time of my life.

## 高者抑之,下者举之; 有余者损之,不足者补之.

It is lowered if too high; It is raised if too low. It is shortened if too long; It is lengthened if too short.

– Lao Tsu (500 BC), ancient Chinese philosopher

## TABLE OF CONTENTS

|    | Signature Page        | •                                     | iii                                                                                                                    |

|----|-----------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------|

|    | Dedication Page       |                                       | iv                                                                                                                     |

|    | Epigraph              |                                       | v                                                                                                                      |

|    | Table of Contents     |                                       | vi                                                                                                                     |

|    | List of Figures       |                                       | х                                                                                                                      |

|    | List of Tables        |                                       | xvi                                                                                                                    |

|    | Acknowledgments       |                                       | xviii                                                                                                                  |

|    | Vita and Publications |                                       | xix                                                                                                                    |

|    | Abstract              |                                       | xx                                                                                                                     |

| Ι  | Introduction          |                                       | $     \begin{array}{c}       1 \\       3 \\       5 \\       6 \\       7 \\       9 \\       11 \\     \end{array} $ |

| II | Background            | · · · · · · · · · · · · · · · · · · · | $ \begin{array}{c} 12\\ 12\\ 13\\ 13\\ 18\\ 19\\ 20\\ 22\\ 26\\ 26\\ 26\\ 26\\ 26\\ 28\\ \end{array} $                 |

| III | Event-Driven Multithreaded Architecture                 | 30 |

|-----|---------------------------------------------------------|----|

|     | A. Overview of Trident Architecture                     | 32 |

|     | 1. Definitions                                          | 32 |

|     | 2. Runtime Support                                      | 34 |

|     | 3. The Dynamic Optimizer                                | 35 |

|     | 4. Hardware Monitors and Events                         | 36 |

|     | B. Trident Optimization Flow                            | 40 |

|     |                                                         |    |

| IV  | Trace Formation Based Optimization                      | 44 |

|     | A. Trace Formation                                      | 45 |

|     | B. Methodology                                          | 46 |

|     | 1. The Configuration of Hardware Monitors               | 46 |

|     | 2. Benchmarks                                           | 48 |

|     | 3. Simulation Assumptions                               | 49 |

|     | C. Evaluation of Trace Formation                        | 49 |

|     | 1. Candidate Hot Path Starting Points and Trace Linking | 49 |

|     | 2. Hot Trace Invalidation                               | 52 |

|     | 3. Trace Optimization Overhead                          | 53 |

|     | D. Color-based Code Placement                           | 55 |

|     | E. Architecture-Specific Optimizations                  | 57 |

|     | F. Summary                                              | 59 |

|     | 1. Summary                                              | 05 |

| V   | Speculative Dynamic Value Specialization                | 60 |

|     | A. Related Work                                         | 61 |

|     | 1. Code Specialization                                  | 61 |

|     | 2. Value Profiling                                      | 63 |

|     | B. An Example of Dynamic Value Specialization           | 63 |

|     | C. Dynamic Value Specialization Architecture            | 65 |

|     | 1. Hot Value Profiler                                   | 66 |

|     | 2. Hot Value Events                                     | 68 |

|     | D. Implementation of Dynamic Value Specialization       | 68 |

|     | 1. Verifying the Specialized Load Value                 | 69 |

|     | 2. Exploring Stride Values                              | 70 |

|     | E. Methodology                                          | 72 |

|     | F. The Performance of Value Specialization              | 72 |

|     | 1. Comparison with Value Prediction                     | 72 |

|     | 2. Comparison with Load Prefetching                     | 75 |

|     | G. Summary                                              | 76 |

|     |                                                         | 10 |

| VI  | Adaptive Dynamic Software Prefetching                                                    | 8 |

|-----|------------------------------------------------------------------------------------------|---|

|     | A. Related Work                                                                          | 9 |

|     | 1. Hardware Based Prefetching                                                            | 0 |

|     | 2. Software Inlined Prefetching                                                          | 1 |

|     | 3. Prefetching via Dynamic Optimization Systems                                          | 2 |

|     | B. Dynamic Software Prefetching Architecture                                             | 3 |

|     | C. Delinquent Load Table                                                                 | 5 |

|     | D. Dynamic Prefetch Optimizer                                                            | 7 |

|     | 1. Delinquent load identification                                                        | 7 |

|     | 2. Stride-Based Prefetching of Same-Object Loads                                         | 0 |

|     | 3. Prefetching for Pointer Loads                                                         | 1 |

|     | E. Adaptive, Self-Repairing Prefetching                                                  | 2 |

|     | 1. Prefetch Distance for Stride Address Predictable Loads 9                              | 2 |

|     | 2. Adaptive discovery of prefetching distance                                            | 3 |

|     | 3. Prefetch Maturing                                                                     | 4 |

|     | F. Methodology                                                                           | 7 |

|     | 1. Baseline Processor Architecture                                                       | 7 |

|     | 2. Benchmarks                                                                            | 9 |

|     | 3. Prefetching via Trident Architecture                                                  | 0 |

|     | G. Performance                                                                           | 2 |

|     | 1. Overhead of the Dynamic Prefetch Optimizer                                            | 2 |

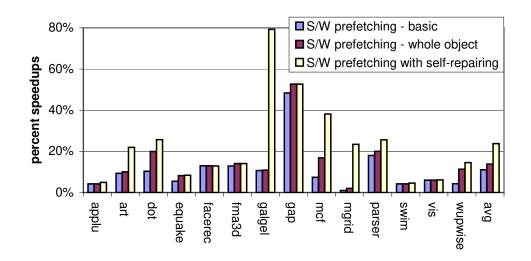

|     | 2. Load Coverage by Software Prefetching                                                 | 4 |

|     | 3. Performance of Software Prefetching                                                   | 5 |

|     | 4. Software Prefetching Sensitivity                                                      | 9 |

|     | 5. Comparison with Hardware Prefetching                                                  | 2 |

|     | H. Summary                                                                               | 2 |

|     |                                                                                          |   |

| VII | Accelerating Precomputation Based Prefetching                                            |   |

|     | A. Related Work                                                                          |   |

|     | 1. Prefetching via Precomputation                                                        |   |

|     | 2. Static Precomputation Construction                                                    | 9 |

|     | B. Dynamic Precomputation Prefetching Architecture                                       | 1 |

|     | 1. Overview $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $12$ | 1 |

|     | 2. Precomputation Code Construction                                                      | 2 |

|     | 3. Precomputation Thread Triggering and Termination 12                                   | 5 |

|     | 4. Precomputation Thread Priority                                                        | 7 |

|     | 5. Precomputation Thread Synchronization                                                 | 7 |

|     | C. Accelerating Precomputation Threads                                                   | 8 |

|     | 1. Precomputation With Speculative Strides                                               | 9 |

|     | 2. Precomputation Jump Starting                                                          | 9 |

|     | 3. Precomputation Code and Hot Trace Co-Location                                         | 3 |

| D. Precomputation Prefetching Address Coherence                                                                                                                               | 34 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| E. Methodology $\ldots \ldots \ldots$                         | 35 |

| 1. Trident's Monitoring Hardware                                                                                                                                              | 35 |

| 2. The Dynamic Optimizer $\ldots \ldots \ldots$               | 36 |

| F. Performance Evaluation                                                                                                                                                     | 36 |

| 1. Overhead of the Dynamic Prefetch Optimizer                                                                                                                                 | 36 |

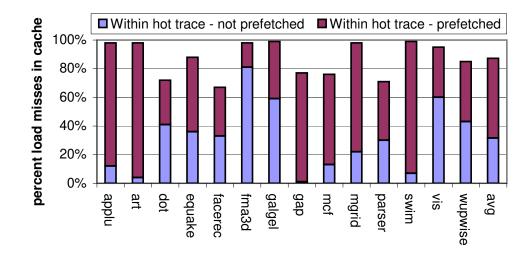

| 2. Load Coverage by Software Prefetching                                                                                                                                      | 38 |

| 3. Performance of Precomputation Based Prefetching 13                                                                                                                         | 38 |

| 4. Prefetching Address Coherence                                                                                                                                              | 41 |

| 5. Jump Start and Runahead Distances $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots $                                                                        | 42 |

| 6. Comparison with Inlined Prefetching $\ldots \ldots \ldots$ | 43 |

| 7. Comparison with Larger Data Cache Sizes $\ldots \ldots \ldots \ldots 14$                                                                                                   | 44 |

| VIIISummary and Future Work                                                                                                                                                   | 46 |

| A. Trident Optimizations                                                                                                                                                      | 47 |

| B. Future Work                                                                                                                                                                |    |

| 1. In This Thesis $\ldots \ldots 1$                                  | 53 |

| 2. Advanced Optimizations with Trident                                                                                                                                        | 55 |

| Bibliography                                                                                                                                                                  | 59 |

## LIST OF FIGURES

| II.1  | Dynamo interpretation and optimization flow. Dynamo starts<br>with interpretation of the program's binary. The program is pro-<br>filed while being interpreted. When Dynamo detects a hot path,<br>it switches to the collecting phase where the trace is formed. The<br>trace is then being optimized and inserted into the code cache.<br>So Dynamo interleaves interpretation/profiling, trace optimiza-<br>tion, and notive execution of optimized traces. | 15       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| II.2  | tion, and native execution of optimized traces                                                                                                                                                                                                                                                                                                                                                                                                                  | 15       |

| II.3  | trace, which has been formed early                                                                                                                                                                                                                                                                                                                                                                                                                              | 17       |

| III.1 | instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 24       |

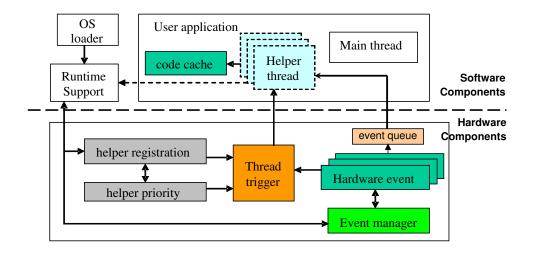

| III.2 | dler) is triggered to run, in parallel with other threads<br>An implementation of Trident architecture. Trident is a soft-<br>ware/hardware hybrid. The software component is responsible<br>for registering an optimization event, performing optimization,<br>and managing optimized hot traces. The hardware component<br>is responsible for monitoring the program's behavior and trig-                                                                     | 31       |

| III.3 | gering optimization threads                                                                                                                                                                                                                                                                                                                                                                                                                                     | 33<br>34 |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |

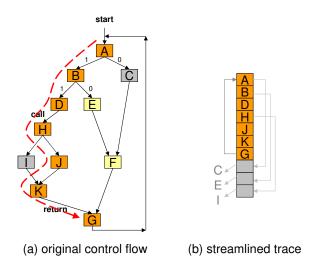

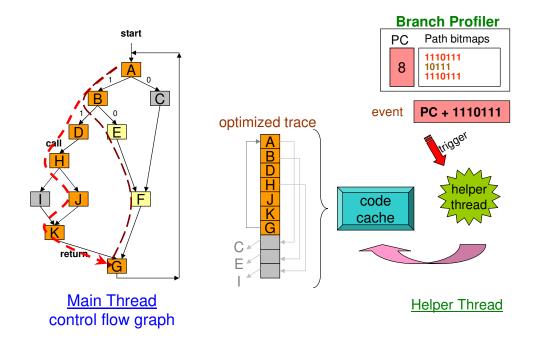

- III.4 Trident dynamic optimization flow. The path A-B-D-H-J-K-G is the frequently executed path (*hot*). The path A-B-E-F-G is a less frequent path (*warm*). Both paths end at the block G since it has a loop-back branch, which terminates a path during branch profiling. The path history bitmaps for these two paths are 1110111 and 10111, respectively. The voting scheme picks the winner path 1110111 inside the branch profiler. This generates the hot branch event: <PC, 1110111>. Then the Trace Construction thread is triggered to run. The hot trace is created, optimized, and inserted into the code cache.

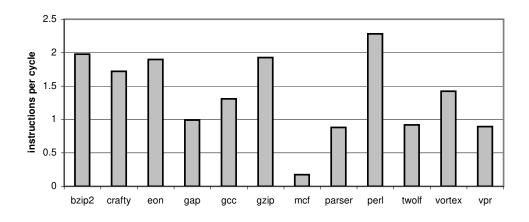

- IV.1 Performance of SPEC 2000int on the baseline SMT processor. Each benchmark runs alone in one hardware thread while other hardware threads are idle. The simulation is warmed up for 5 millions instructions, and then a total of 100 million instructions are simulated.

43

48

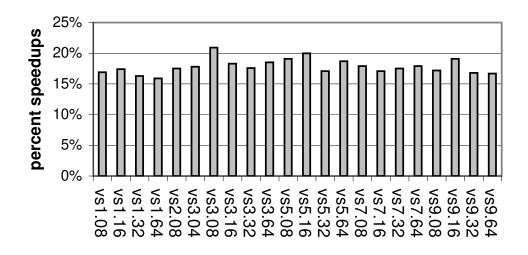

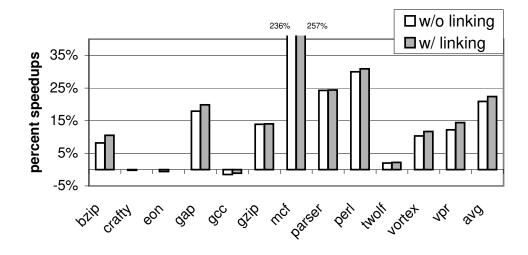

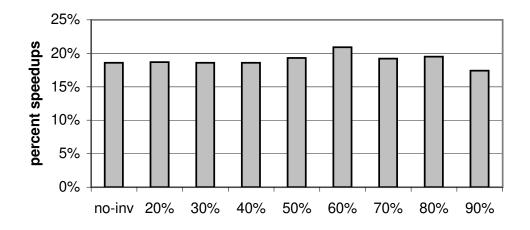

- IV.3 Performance with and without linking. Trace linking chains optimized traces together inside the code cache. If one trace has an exit branch whose target is the beginning address of another optimized trace, then the branch can directly jump to its target trace without jumping back to the original binary. 51

xi

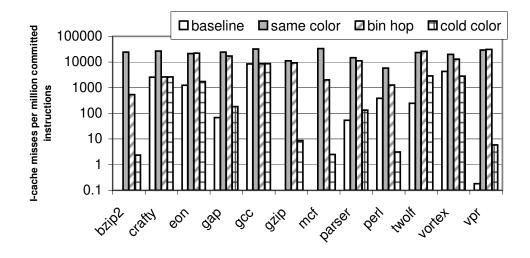

| IV.6 | I-Cache misses on various placement policies. The first bar<br>"baseline" indicates the I-cache misses when running the origi-<br>nal binary on the baseline SMT processor alone.                                                                                                                                                                                                                                                                               | 56       |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

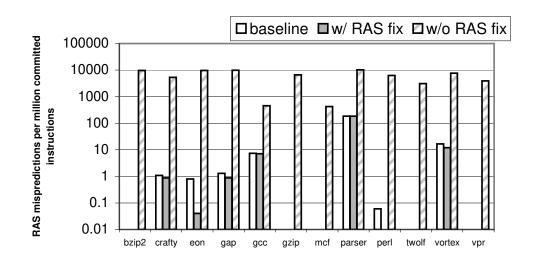

| IV.7 | RAS mispredictions due to dynamic optimization. The first bar<br>"baseline" represents the number of RAS mispredictions when<br>running the original binary on the baseline SMT processor alone.<br>The second bar indicates the RAS mispredictions with Trident's<br>fix. The last bar is the RAS mispredictions, which would be<br>expected when running current software dynamic optimization<br>systems on the processor with the RAS prediction mechanism. | 58       |

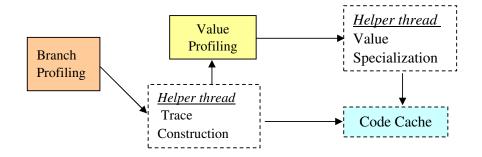

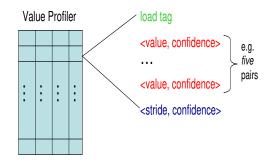

| V.1  | Trident speculative value specialization architecture. The value<br>profiler monitors load instructions inside hot traces. When the<br>profiler detects a semi-invariant value, it triggers the hot value<br>event to perform value specialization on this hot trace with this                                                                                                                                                                                  |          |

| V.2  | value                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 66       |

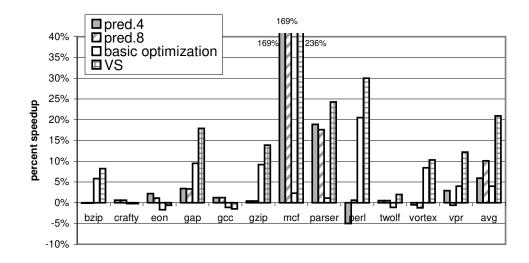

| V.3  | confident, the stride value may be used if it is confident<br>Comparison of value specialization with value prediction [136].<br>The first two bars show traditional value prediction with 4 and 8<br>predictions per cycle, respectively. The last bar shows speedups<br>from speculative value specialization                                                                                                                                                 | 67<br>74 |

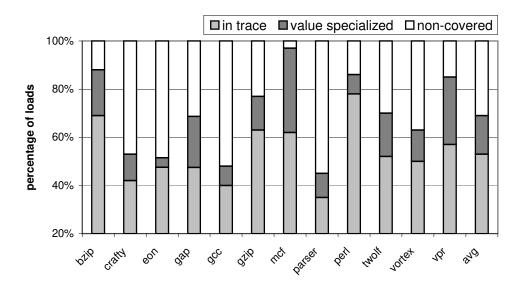

| V.4  | Breakdown of dynamic load instructions. 100% represents total<br>dynamic instances of all load instructions. The "in trace" repre-<br>sents all loads inside hot traces, which have potential to be opti-<br>mized during base optimization. The "value specialized" stands<br>for loads being value specialized. The "non-covered" shows all                                                                                                                   |          |

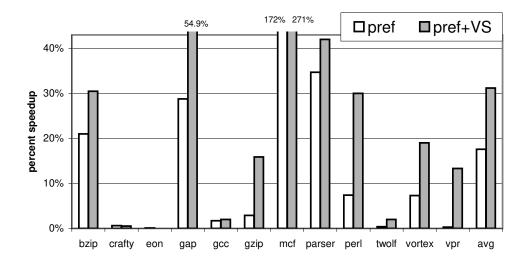

| V.5  | loads falling outside hot traces                                                                                                                                                                                                                                                                                                                                                                                                                                | 74       |

|      | ization.                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 76       |

xii

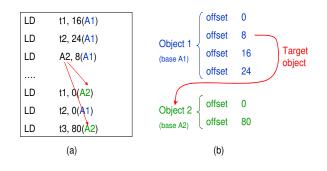

- VI.1 An example of object groups. In this example, there are four loads with the same base register (A1), and other two loads with the base register A2. Two objects are formed in (b). The second object is the target object of the pointer load in the first object. Object 1 can be prefetched using a single prefetch instruction. Object 2 needs two prefetch instructions.

- 89

95

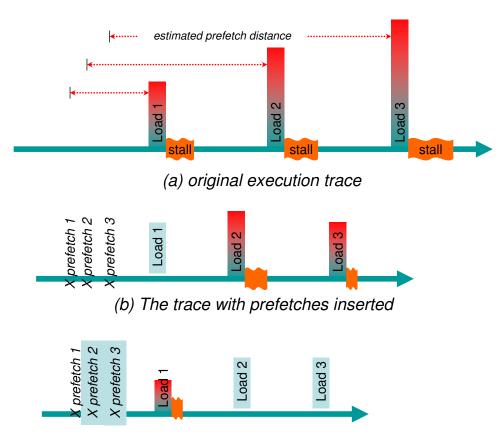

- VI.2Trident's adaptive discovery of optimal prefetch distances. In this example, we assume there are three delinquent loads, which stall the program's execution, in the original trace, as shown in (a). Software prefetches are inserted with estimated prefetch distances. These prefetches make the total execution time of the trace shorter than before. However, since each prefetch distance is estimated independently, these distances are not far enough to hide all load latencies. In this example, load 2 and load 3 are still delinquent, as shown in (b). Trident then adjusts these prefetches (2 and 3) to hide latencies from loads 2 and 3. The adjustment further reduces the total execution time. Because of this, load 1 becomes delinquent again. This triggers Trident to adjust the prefetch instruction for load 1. However, other loads may become delinquent after this adjustment. This adjustment process continues until all loads are stabilized or matured.

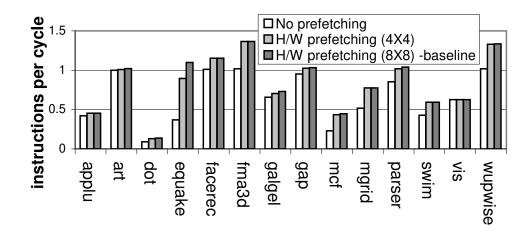

- VI.3 Performance on the baseline SMT processor with hardware stream prefetching enabled. The default stream prefetching mechanism has 8 stream buffers. Each buffer can hold up to 8 fetch blocks. 100

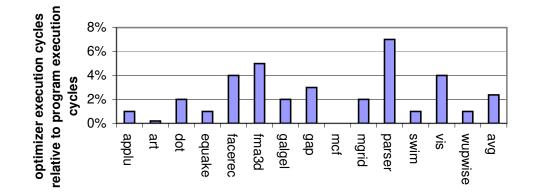

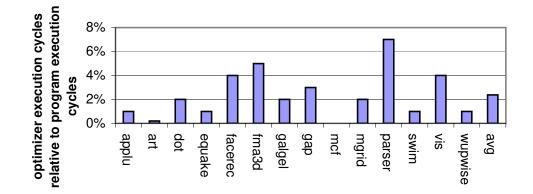

- VI.4 The execution time of optimization threads relative to the main program's execution time. The execution time does not include the time of repetitious discovery of prefetch distances. . . . . 103

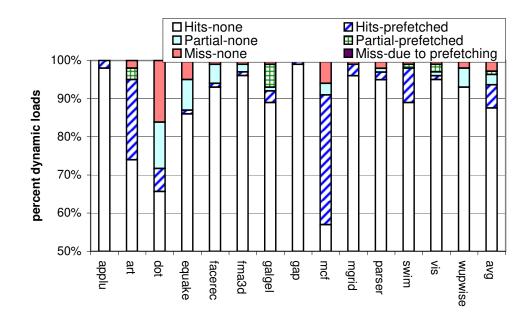

| VI.7  | Percentage breakdown of all dynamic loads. The "hits-none" represents the normal cache hits. The "hits-prefetched" repre-               |     |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|

|       | sents the cache hit due to software prefetching. A prefetch hit<br>is only counted once. Any subsequent access to the prefetched        |     |

|       | cache block is classified as "hits-none". The "miss-none" indi-                                                                         |     |

|       | cates the normal cache misses. The "miss-due to prefetching"                                                                            |     |

|       | represents the side effect of software prefetching, which are cache<br>misses caused by a prefetched block replacing a block that would |     |

|       | have gotten a hit in the future.                                                                                                        | 108 |

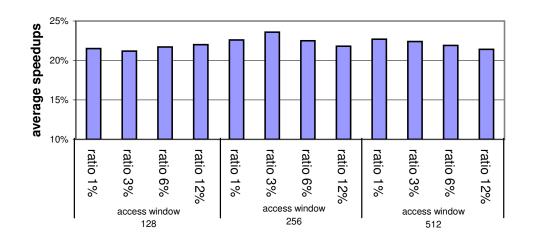

| VI.8  | Average performance improvement of software prefetching with                                                                            | 100 |

|       | different load monitoring window sizes and cache miss rate thresh-                                                                      |     |

|       | olds. The miss rate is calculated as the miss count divided by                                                                          |     |

|       | the access count during a given monitoring window.                                                                                      | 109 |

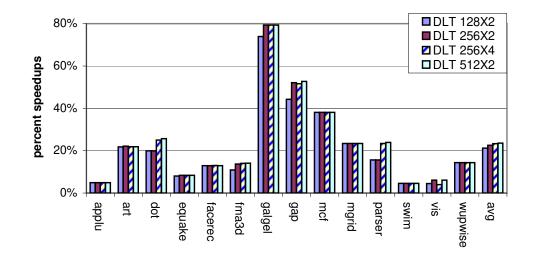

| VI.9  | Average performance improvement of software prefetching with                                                                            |     |

|       | different DLT sizes. The DLT is organized as a set-associative                                                                          |     |

|       | cache. Each configuration represents the number of sets and the cache associativity.                                                    | 110 |

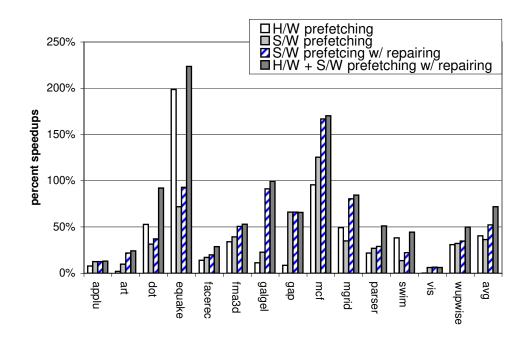

| VI.10 | Performance comparison with hardware prefetching. The sec-                                                                              | 110 |

|       | ond bar represents the performance when applying the existing                                                                           |     |

|       | dynamic prefetching system alone. The third bar stands for the                                                                          |     |

|       | speedup when using our adaptive dynamic prefetching alone.                                                                              |     |

|       | The last bar is for hardware stream prefetching combined with<br>our adaptive dynamic software prefetching.                             | 111 |

|       | our adaptive dynamic software prefetching                                                                                               | 111 |

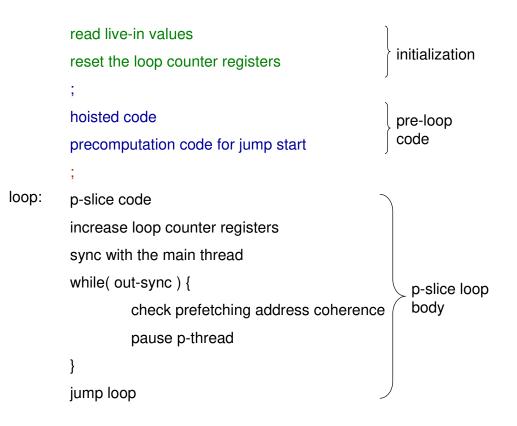

| VII.1 | The layout of precomputation slices. The p-slice code can be di-                                                                        |     |

|       | vided into three portions. The first portion contains the p-slice                                                                       |     |

|       | initialization code. It reads live-in values from the main thread                                                                       |     |

|       | to start up the p-thread, and initializes the p-slice loop counter<br>to keep in sync with the main thread. The second portion in-      |     |

|       | cludes any loop-invariant computation code. We also insert code                                                                         |     |

|       | here to jump start the p-thread as needed. The last portion is                                                                          |     |

|       | the p-slice loop body. We augment the code here to enforce                                                                              |     |

|       | prefetching address coherency with the main thread                                                                                      | 124 |

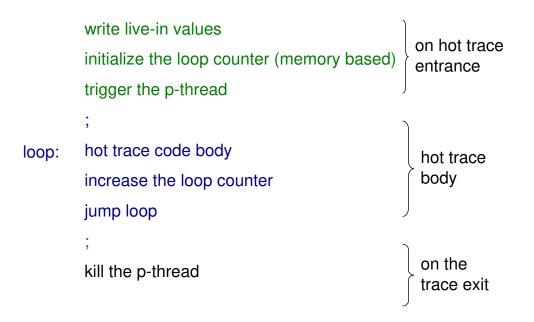

| VII.2 | The hot trace layout to start up and terminate the p-thread.                                                                            |     |

|       | The original hot trace is wrapped with the p-thread startup and<br>termination code. We introduce a memory based loop counter in        |     |

|       | the hot trace. The p-thread reads this counter from memory to                                                                           |     |

|       | synchronize itself with the main thread. Since the main thread                                                                          |     |

|       | does not have any data dependence on this counter, increment-                                                                           |     |

|       | ing the counter every loop iteration should have minimal impact                                                                         |     |

|       | on the main thread.                                                                                                                     | 126 |

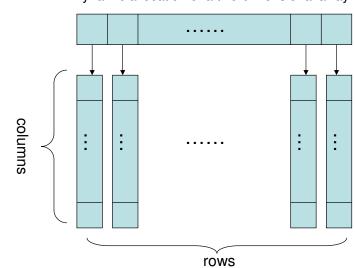

| VII.3         | An example of dynamic memory allocation for a two-dimensional          |

|---------------|------------------------------------------------------------------------|

|               | array. The pointer array (row) is allocated first, and each col-       |

|               | umn is allocated separately. Then the pointers in the row ar-          |

|               | ray are assigned to point to individual column. Depending on           |

|               | the runtime memory allocation policy, the starting addresses of        |

|               | columns may or may not be strided                                      |

| VII.4         | Runaway prefetching detection for a strided load                       |

| VII.5         | Concurrent execution cycles between the main and optimization          |

|               | threads. Prefetching threads do not run since hot traces are not       |

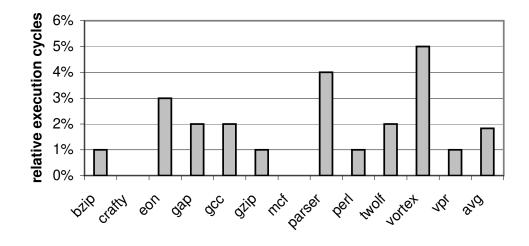

|               | activated during this measurement                                      |

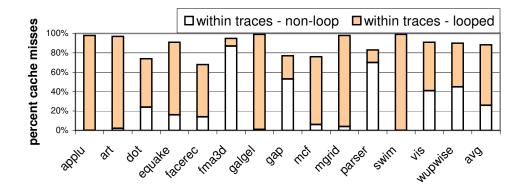

| VII.6         | Dynamic load misses within hot traces. Since p-slices are con-         |

|               | structed on hot traces with self-loops, our precomputation based       |

|               | prefetching only targets delinquent loads within looped hot traces.138 |

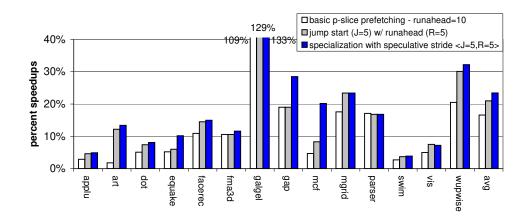

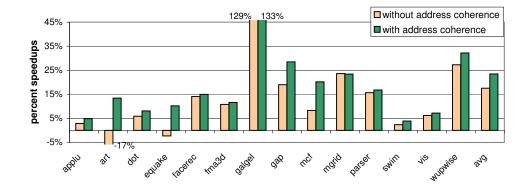

| VII.7         | Performance of precomputation based prefetching. The per-              |

|               | formance gains are relative to the baseline architecture with          |

|               | a hardware stream buffer prefetcher. The first bar ("basic p-          |

|               | slice prefetching") is intended to represent the performance from      |

|               | prior research. The second bar is the Trident based scheme with        |

|               | the jump start distance 5 and the runahead distance 5, which           |

|               | makes the total prefetch distance 10. The last bar shows the per-      |

|               | formance when combining p-slice code specialization with jump          |

|               | start. P-threads are constructed only for the looped traces 139        |

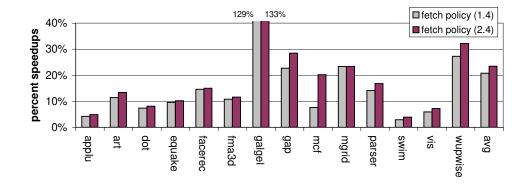

| VII.8         | Comparison of instruction fetch policies. The policy ICOUNT            |

|               | 1.4 indicates that only one thread is fetched, with up to 4 in-        |

|               | structions, at any given cycle. The policy of ICOUNT2.4 allows         |

|               | two threads, with total 4 instructions, to be fetched in one cycle.    |

|               | This is the policy used in this study                                  |

| VII.9         | Performance of the prefetching address coherence scheme. P-            |

|               | threads have the jump start distance of 5 and the runahead             |

|               | distance of 5                                                          |

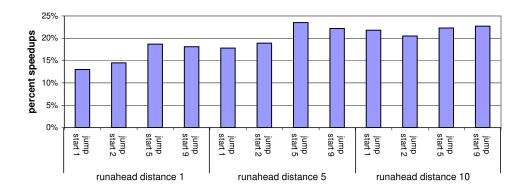

| <b>VII.10</b> | Performance of jump start distances with different runahead            |

|               | distances                                                              |

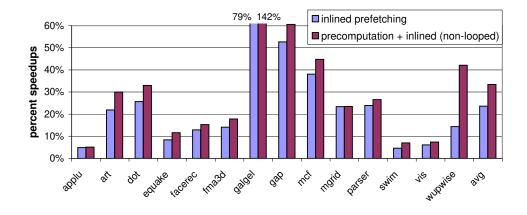

| VII.11        | Performance of combining precomputation based prefetching              |

|               | (for looped traces) with inlined prefetching (for non-looped traces).  |

|               | P-threads have the jump start distance of 5 and the runahead           |

|               | distance of 5. $\ldots$ 144                                            |

## LIST OF TABLES

| III.1 | Trident hardware monitors and events. The first two structures<br>will trigger optimization events. I-cache counters are used to<br>place hot traces into the code cache. These counters are already<br>available in modern processors.                                                                                                                                                                                                                                                                           | 36       |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| III.2 | Trident hot trace voting scheme. The profiler collects multiple<br>history path bitmaps after a hot branch. Voting starts off from<br>the first bit in all bitmaps to choose the majority as the win-<br>ner, which represents the <i>hot</i> outcome/direction of that branch.<br>Then it moves to the second bit for the next round of voting,<br>and so on. The losing bitmap will be dropped from next round<br>of voting. The final result represents the longest common sub-<br>sequence among all bitmaps. | 30       |

| IV.1  | The baseline SMT processor configuration. The SMT processor has two hardware contexts to run programs simultaneously                                                                                                                                                                                                                                                                                                                                                                                              | 47       |

| IV.2  | Trident baseline monitor configurations. These hardware struc-<br>tures are needed to form basic hot traces                                                                                                                                                                                                                                                                                                                                                                                                       | 47       |

| V.1   | An example of code specialization from <i>parser</i> . The load in line 2 produces the value of zero with high frequency. Thus, the prediction on this load can further trigger instruction removal in lines 3, 4, and 5. After value specialization, the load in line 6 no longer depends on the load in line 2. These two loads can                                                                                                                                                                             |          |

| V.2   | be issued and executed in parallel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 64<br>72 |

| VI.1  | Trident delinquent load table. The watch table is augmented<br>with an optimization flag. This flag works together with the<br>delinquent load's maturing flag to avoid over-optimization                                                                                                                                                                                                                                                                                                                         | 84       |

| VI.2  | The configuration of the baseline SMT processor with hardware<br>stream prefetching. There are total 8 stream buffers, and each<br>buffer can hold up to 8 fetch blocks. The prefetching is guided<br>by a two-delta stride predictor.                                                                                                                                                                                                                                                                            | 98       |

| VI.3  | Trident hardware monitoring structures. The DLT table detects address stride values for the delinquent loads. A load is delinquent if its miss rate is higher than 3% and its average miss                                                                                                                                                                                                                                                                                                                        |          |

|       | latency is higher than 1.5 times the L1 miss penalty. $\ldots$ $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                           | 101      |

#### ACKNOWLEDGMENTS

Portions of Chapters IV and V reproduce the material from the paper, Weifeng Zhang, Brad Calder, and D.M. Tullsen, "An Event-Driven Multithreaded Dynamic Optimization Framework", in the proceedings of the 14th International Conference on Parallel Architectures and Compilation Techniques (PACT 2005), September 2005, Saint Louis, MO. The dissertation author was the primary researcher and author and the co-authors involved in the publication [142] directed, supervised, and assisted in the research which forms the basis for that material.

The text of Chapter VI is in part a reprint of the material from the paper, Weifeng Zhang, Brad Calder, and D.M. Tullsen, "A Self-Repairing Prefetcher in an Event-Driven Dynamic Optimization Framework", in the proceedings of the 4th International Symposium on Code Generation and Optimization (CGO 2006), March 2006, New York, NY. The dissertation author was the primary researcher and author and the co-authors involved in the publication [143] directed, supervised, and assisted in the research which forms the basis for that material.

#### VITA

| 1968      | Born, Henan, China                                                                                          |

|-----------|-------------------------------------------------------------------------------------------------------------|

| 1987      | B.S. in Electronics and Information Science<br>Wuhan University, China                                      |

| 1990      | M.S. in Computer Science and Application<br>Chinese Academy of Science, Beijing, China                      |

| 1996      | M.S. in Physics<br>University of California, Irvine                                                         |

| 1996-1997 | Software Engineer<br>Phoenix Technologies, Ltd<br>San Jose, California                                      |

| 1997-1999 | Senior Software Engineer<br>Phoenix Technologies, Ltd<br>San Jose, California                               |

| 1999-2002 | Principal Software Engineer<br>Phoenix Technologies, Ltd<br>San Jose, California                            |

| 2002-2006 | Research Assistant<br>Department of Computer Science and Engineering<br>University of California, San Diego |

| 2006      | Ph.D. in Computer Science<br>University of California, San Diego                                            |

#### PUBLICATIONS

Weifeng Zhang, Brad Calder, and D.M. Tullsen, "An Event-Driven Multithreaded Dynamic Optimization Framework", in the 14th International Conference on Parallel Architectures and Compilation Techniques, (PACT 2005), September 2005, Saint Louis, MO

Weifeng Zhang, Brad Calder, and D.M. Tullsen, "A Self-Repairing Prefetcher in an Event-Driven Dynamic Optimization Framework", *in the 4th International Symposium on Code Generation and Optimization*, (CGO 2006), March 2006, New York, NY

### ABSTRACT OF THE DISSERTATION

Event-Driven Multithreaded Dynamic Optimization

by

Weifeng Zhang Doctor of Philosophy in Computer Science University of California, San Diego, 2006 Professor Bradley Calder, Chair Professor Dean M. Tullsen, Co-Chair

Dynamic optimization has been proposed to overcome many limitations of static optimization, such as inaccurate assumptions about the underlying processor architecture and lack of adaption to the program's runtime behavior. However, existing dynamic optimization systems often impose high runtime overhead (software systems) or great hardware complexity (hardware systems), and only have limited runtime adaptability.

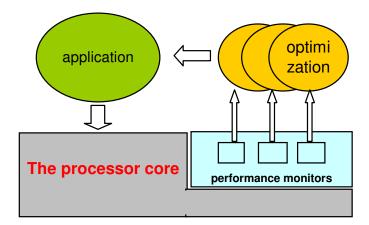

This thesis proposes a new model of optimization, where optimization is triggered by hardware optimization events and is performed concurrently on an application while it is running. We introduce an event-driven multithreaded dynamic optimization architecture, called *Trident*. Trident is a software/hardware solution which strives to reduce software runtime overhead as well as reduce hardware complexity and inflexibility. Trident takes advantage of two key features in modern processors, abundant chip-level parallelism (through Simultaneous Multithreading, Chip Multithreading, or a combination) and increasing hardware support for runtime performance monitoring. Trident proposes generic, lightweight extensions of the hardware monitoring mechanisms to profile the program's execution behavior. Hardware triggers an event for optimization upon detection of any interesting behavior. Lightweight helper threads are spawned to process these events, in parallel with the main thread. The combination of event-driven and concurrent optimization makes Trident extremely low overhead in both profiling and optimization. This enables Trident to perform more expensive optimizations than existing dynamic systems, and perform continuous recurrent optimizations without fear of performance loss.

The power and flexibility of Trident enable many types of optimizations. In this thesis, we demonstrate it with an aggressive optimization, called speculative dynamic value specialization. We also demonstrate Trident's power of continuous, gradual optimization by improving traditional software prefetching to better attack the classical memory wall problem. These approaches include adaptive dynamic software prefetching via self-repairing and accelerating precomputation based prefetching.

## Ι

# Introduction

This dissertation explores Event-Driven Multithreaded Dynamic Optimization, a new optimization model, to enable continuous recurrent optimizations which are difficult to perform in traditional dynamic optimization systems. Static compilation and optimization techniques have been well studied in the past few decades [75, 2, 137, 1, 47, 96]. Static optimization and code generation often rely on assumed knowledge of the underlying processor architecture, such as the number of physical registers [22, 38], the number of functional units, cache hierarchy [80, 52, 17], and processing element (*PE*) organizations [51, 79, 69]. Static compilation has the advantage of doing sophisticated and global optimization without suffering runtime overhead. However, it is increasingly difficult for static compilers to make accurate assumptions about the underlying processor architecture. Inaccurate assumptions produce sub-optimal performance. Furthermore, the uniform assumptions made during static compilation do not always work well. This is because a program not only has different execution behavior with different input, but also exhibits phased behavior even with the same input [124]. A particular optimization performed by the static compiler may be optimal in one phase, but suboptimal in another phase of execution.

Dynamic optimization [7, 29, 39, 85, 10, 32, 104, 112, 13, 92, 121] has

emerged as an alternative solution to the above problems. Since a program is dynamically optimized while it runs, optimizations can be specifically customized to the underlying machine architecture, and they can automatically adapt to the program's changing behavior at runtime. While dynamic optimization has many advantages over static optimization, it also imposes several new challenges.

- Runtime Overhead: Dynamic optimization suffers three types of overhead, which are absent in static optimization. First, dynamic optimization requires runtime profiling to identify the program's execution behavior and runtime analysis to detect any behavior patterns. The accuracy of runtime profiling often determines the ultimate performance of dynamic optimization. Second, the runtime optimizer competes for execution resources with the main thread of the program. Thus, optimizing the program on the fly may unnecessarily impact the performance of the main program. To minimize this overhead, dynamic optimization is often judiciously performed on the common cases. It is often known that a program spends 90% (or more) of its execution time in 10% (or less) of its code. A common technique for reducing overhead is to classify the dynamic instruction streams into frequently-executed (hot) streams and infrequently-executed (cold) streams. When dynamic optimization is applied on the hot traces, the highest benefits are achieved and the cost is amortized if the hot traces are executed many times. Thus, a companion challenge for dynamic optimization is how to select hot traces with high dynamic coverage. Finally, because only a part of the program is dynamically re-optimized, overhead also occurs when switching between the optimized and un-optimized code during execution.

- **Program control:** It is also important to efficiently maintain control over the running program, in order to dynamically alter its code, and switch between the optimized code and un-optimized code. In the purely software-

controlled dynamic optimization systems, this is usually difficult to achieve without severely penalizing the performance.

• Optimization Adaptation: The optimized code in a program may need to be re-optimized as the program's behavior changes over time. Optimizing the program dynamically, but staying unchanged afterwards, has the same pitfall as static optimization. Adapting the optimization to the program's varying behavior requires continuous profiling and recurrent optimization, which can be very expensive.

The optimized code is either stored in a memory buffer (in software systems) or in a hardware cache (in hardware systems). Managing the optimized code imposes new software overhead or hardware complexity. The management policy may also reflect how fast the dynamic optimization adapts to the program's behavior.

However, existing dynamic optimization systems essentially have the same limitation as the static systems. In these dynamic systems, profiling, optimization, and execution are interleaved, but still done one at a time. Thus, execution stalls when profiling or optimization occurs. Especially context switches are incurred when switching from one to another.

## I.A Event-Driven Multithreaded Dynamic Optimization

This thesis proposes a new model of optimization, where optimization is triggered by hardware optimization events and is performed concurrently with the program's execution. By allowing profiling, optimization, and execution to occur in parallel, this model eliminates the above overhead, and enables continuous and adaptive optimization.

We implement this concurrent model as an event-driven multithreaded

dynamic optimization framework, called *Trident*. Trident is a software/hardware solution to enable low overhead and fast optimization with efficient hardware support. Trident exploits two features present in many modern processor architectures: increasing hardware support for runtime monitoring of execution and the ability to execute multiple threads, either through chip multiprocess-ing [56], hardware multithreading [133], or a combination [68]. Trident exploits a hardware multithreading processor, using an otherwise idle hardware thread to concurrently optimize a thread that is running.

This thesis also proposes conservative extensions to the existing hardware support to identify performance-critical events to trigger dynamic optimization. It provides efficient support to enable Trident's optimization without introducing much complexity to the processor's performance monitoring mechanism (e.g. Itanium). Thus, optimization that runs concurrently with execution and monitoring provides an extremely low-overhead dynamic optimization system. It significantly reduces overhead inherent to most prior systems, and can enable very aggressive optimizations.

The two key features of our optimization system are:

- Performance and event monitoring can be done with no software overhead. This allows more frequent monitoring and higher coverage of the executable. It also allows monitoring to continue with no overhead during and after optimization, allowing more opportunities to repair or back out of bad optimizations.

- Event-driven low-overhead optimization. Because optimization happens in response to hardware optimization events, optimizations are easily handled by spawning a lightweight helper thread, which does not interrupt the main thread's execution. Trident avoids the profile polling and associated software overhead (as in ADORE [84]). Thus, concurrent execution

and optimization allow the framework to explore much more aggressive optimizations without significant fear of performance loss, even if the code being optimized is short lived. Low overhead profiling and low overhead optimization also make it possible to enable continuous and gradual optimization, which is difficult to do in the existing systems.

## I.B Optimizations with the Trident Framework

Our framework focuses on efficient dynamic optimization for a multithreaded processor – in this thesis, the hardware platform we examine is the Simultaneous Multithreaded (SMT) processor [133].

Low overhead profiling and optimization provide Trident more freedom to re-consider some design tradeoffs in traditional dynamic optimization systems. In this thesis, we examine the benefit of using Trident to perform basic compiler optimizations, to guide code layout for the instruction cache conflict reduction, and to enable an architectural specific optimization (reduction of the Return Address Stack misprediction).

Trident is flexible enough to enable a variety of optimizations at once, and we demonstrate it in this thesis with dynamic value specialization combined with these basic dynamic optimizations. In addition, we demonstrate Trident's ability to enable continuous and gradual optimizations by re-examining the classical *Memory Wall* problem [139, 89]. The memory wall problem has been studied via pure hardware approaches [125]. Conventional dynamic systems (e.g. ADORE [84]) also try to solve this problem by dynamically inserting software prefetches according to its runtime memory behavior. In this thesis we show that Trident's gradual re-optimization can further improve these systems to achieve significantly better performance.

#### I.B.1 Dynamic Value Specialization

Value specialization is a compiler technique which makes a special version of code if a procedure (or an execution trace, in general) frequently takes the same parameter values during each invocation. Depending on the actual value used for specialization, the specialized code could be dramatically reduced from its original version. However, the compiler has to insert extra code to recover when the parameters does not take the predicted value. This is called *misspecialization*.

In this thesis, we study a form of speculative dynamic code specialization. The program's execution traces are speculatively specialized with semiinvariant runtime values, which are identified via runtime profiling. Values are dynamically verified to ensure the correctness of the program. Recovery is automatically performed using the existing mis-speculation hardware. The advantage of this technique over compiler-based value specialization is the ability to specialize on values identified dynamically during execution, to adapt value specialization as the application changes behavior, and to recover from mis-speculation quickly in hardware.

Speculative value specialization benefits from two factors - value prediction and value specialization. Traditional hardware value prediction takes advantage of value locality, and breaks true data dependence chains by directly predicting load values [83, 136, 145, 18]. With load value prediction, instructions that depend on load values are executed speculatively. The benefit of value prediction comes from reducing the program's critical dependence path of execution, which is of critical importance when loads that miss in the cache are part of the dependence chain. However, a significant missed opportunity for dynamic value prediction techniques is that unnecessary, or unnecessarily complex, instructions are executed after the value is "known" (speculatively). These are instructions the compiler could have eliminated or reduced if the value had been a static constant.

Thus, by doing speculative value specialization in software, we end up expanding benefits beyond the very conservative use of value locality. Dynamic value specialization allows compiler-like optimizations to be applied to semiinvariant runtime values. Anytime value locality is able to make value prediction useful, value specialization significantly enhances its effectiveness.

#### I.B.2 Adaptive Dynamic Software Prefetching via Self-Repairing

The performance of modern processors is increasingly dominated by the widening latency gap between processors and memory subsystems. This is called the *Memory Wall* problem. As the microarchitecture pipeline is getting deeper and the clock frequency is getting higher, it puts even more pressure on the memory system [129]. Prior research also shows that growing cache size does not always improve the program performance[118]. This is especially true for the data cache due to diversified program memory behaviors.

One way to bridge the latency gap is to prefetch load values into the cache, which attempts to overlap the memory latency with the execution of other useful instructions in the same program. This essentially decreases the observed latency, increases memory level parallelism, and allows cache-hit dominated performance even when the working set is larger than the cache. Software based prefetching [20, 95, 87, 138, 85, 31, 62, 109] has been shown to be a promising technique to address the memory wall problem, and all modern high-performance instruction set architectures provide support for software prefetching.

Software prefetching should meet these criteria in order to be effective:

• Prefetches should be accurate. That is, prefetching should target the loads that are actually missing in the cache. Unnecessary prefetches may reduce

the effective memory bandwidth.

- Prefetching should be timely and far enough ahead of time to fully cover the miss latency. Prefetching a load too late will prevent the prefetch from hiding the entire memory latency. However, prefetching too far in advance may unnecessarily displace useful data, increases the likelihood that prefetched data will be replaced, and also increases the likelihood of prefetching unneeded data due to unexpected intervening control flow. Therefore, we want to prefetch a load just in time, so its value appears in the cache right before it is needed. This is the goal behind our study to enable adaptive (self-repairing) prefetching.

- Prefetching address computation should have low overhead. Determining where to prefetch should be fast and easy.

Static compilation does not always provide efficient prefetching, even with offline profiling. For the first criterion, which loads are critical and whether they will miss in the cache cannot be determined accurately offline, since what misses in the cache largely depends on the underlying cache size and organization. For the second criterion, the average latencies of cache-missing loads will vary across different data inputs. Additionally if the code runs on different machines, how far ahead to prefetch a load for one machine will be inappropriate for the other.

Existing dynamic optimization systems (e.g. ADORE [84]) overcome the above limitations by dynamically inserting software prefetches to target true cache misses. Prefetching distances (i.e. *how far to prefetch ahead*) are estimated using average memory latency. However, due to their high runtime overhead, these prefetch instructions stay unchanged during a very long stable phase after being inserted. There are two main limitations with this approach: (1) Due to heavy interaction between prefetches and neighboring load instructions, prefetching distances are not necessarily correct through one profile estimation. Incorrect prefetching distances may only lead to *partial prefetching*. That is, the load latency is only partially hidden by prefetches. (2) Prefetching does not adapt to the runtime behavior as quickly as the program execution changes phases.

The adaptive prefetching proposed in this thesis overcomes these limitations of both static and dynamic approaches, by re-evaluating the effectiveness of the inserted prefetches through continuous hardware monitoring. Prefetches may be re-adjusted, or may be removed altogether, according to the program's runtime behavior. Like hardware prefetching, our technique operates on dynamic information rather than static information to initiate prefetching, and it works on legacy code without sacrificing software compatibility with past and future processors.

#### I.B.3 Accelerating Precomputation Based Prefetching

Software-based prefetching can be enabled either by inlining prefetches inserted into the dynamically-generated code as described in Section I.B.2, or by running prefetch instructions in a separate thread (e.g., precomputation thread, or *p-thread*). While inlined prefetching is typically effective for simple addressing patterns (e.g., strided addresses), p-thread based prefetching has the potential to handle more complex address patterns (e.g., pointer chasing).

Precomputation is a technique to speculatively execute small code traces to compute load addresses and then prefetch these loads [36, 86] or determine branch directions [116] before the main thread reaches those instructions. Precomputation code traces, called *p-slices* [36], can be constructed statically [37, 87, 71, 109], or dynamically [36, 116, 86]. The p-slice is a distilled version of the main thread code. When a p-slice is instantiated to run on the processor, it is referred as a *p*-thread.

P-threads usually run in a separate hardware thread, in parallel with the main thread. In this research, we focus on precomputation based prefetching to hide memory latency.

A common problem in existing precomputation based prefetching schemes is that a p-thread often cannot run sufficiently ahead of the main thread. Though the p-slice is extracted from the main thread's code, it may be no simpler than the main thread when the load behavior is complex. Thus, the p-thread may run no faster than the main thread. At the same time, cache misses occurring inside the p-thread also impede the p-thread from running further ahead. This is especially true when there is pointer chasing behavior inside the p-thread. Another problem associated with precomputation based prefetching is that decoupling of the prefetching thread from the main thread allows the prefetching thread's address stream to possibly diverge from the main thread, if the prefetcher is based on control flow or address speculation. Runaway prefetching may unnecessarily displace useful data, resulting in more data cache misses in the main thread. Both problems above can dramatically reduce the effectiveness of precomputation based prefetching.

In this research, we dynamically construct p-slices from the main thread's hot execution traces. By embedding our p-slice generation in an event-driven dynamic optimization framework, we can overcome several key challenges of threadbased prefetching. We can adapt the same program differently depending on the input and the underlying hardware architecture, we can adapt to changing behaviors at runtime (different loads become problematic, control flow behavior changes).

Additionally, our low overhead, multithreaded optimization enables a few sophisticated techniques to accelerate the p-thread ahead of the main thread. For example, we exploit dynamic hardware load stride prediction to speculatively specialize p-slices, allowing for simpler p-slices with lower overhead. Furthermore, we can dynamically perform code analysis on a p-slice to extract precomputation code from the p-slice, allowing us to jump start the p-slice execution a few iterations ahead of the main thread. Finally, during dynamic p-slice construction, we can insert code to enable a low overhead mechanism for tracking prefetching addresses to determine when they become out of sync with the main thread. This prevents a p-slice from running away from the main thread.

### I.C Thesis Organization

The reminder of this thesis is organized as follows. Chapter II discusses prior research related to dynamic optimization. Chapter III describes details of our even-driven multithreaded dynamic optimization architecture. Chapter IV presents the base optimizations with our optimization architecture. These include hot trace formation, classical compiler optimizations, code relayout, and branch misprediction reduction due to the return address stack misalignment. Chapter V shows the ability of our framework for more aggressive optimizations by speculatively specializing hot traces using semi-invariant runtime values. Chapter VI demonstrates its ability of continuous and recurrent optimization via adaptive, self-repairing prefetching to target the memory wall problem. Chapter VII extends its ability to accelerate the precomputation based prefetching. We summarize this thesis in Chapter VIII and present a few research directions with our dynamic optimization architecture.

## II

# Background

This thesis proposes an event-driven multithreaded dynamic optimization framework, called *Trident*. It enables low overhead, continuous, and recurrent optimizations on applications. Our framework is based in part on a large body of prior research in dynamic optimization. In this chapter, we focus on summarizing prior research on dynamic optimization in both software and hardware based systems, and comparing it against our proposed framework. The related work in the areas where we apply the Trident framework is discussed in individual chapters to demonstrate how Trident improves these techniques. Related work in these applications includes value specialization, hardware and software inlined prefetching, and precomputation based prefetching.

## II.A A Brief History of Dynamic Optimization

Dynamic optimization, as often embedded in binary translation [4], can be traced back to the middle 60's when the IBM/360 series was first introduced. Binary translators often optimize the code for new underlying architectures using the program's dynamic behavior during translation. Early forms of dynamic optimization include ISA remapping, basic block reordering, limited memory coloring, and code specialization (specialized with the procedure's parameter values). As processor technologies evolve, more sophisticated binary translation and dynamic optimization techniques are developed. Examples of these systems include Digital FX!32 [30], HP Aries [141], IBM DAISY [42], Transmeta Code Morphing System (CMS) [41], and the Intel IA-32 execution layer [10]. In 1996, Sun released the Java JDK. Java just-in-time (JIT) compilation [39, 131, 15], which delays all compilations until runtime, gradually gained popularity. On a different path, selective dynamic compilation, such as DyC [93], was proposed to restrict dynamic compilation to only selected portions of code. The code, identified by the user annotation or source language extension, is optimized by a static compiler as much as possible to generate templates that are invoked at runtime by a specialized dynamic compiler. A truly dynamic optimization system, called *Dynamo*, was developed at HP labs in 2000. This is one of the first such systems which demonstrated that a statically optimized native program could still benefit from runtime optimization.

### **II.B** Software Based Dynamic Optimization

We will first summarize prior research on the software dynamic optimization systems. We divide these systems into two groups – those that optimize native binaries and those that perform optimization while doing ISA translation.

#### **II.B.1** Native Binary Optimization Systems

There have been several software dynamic optimization systems proposed in prior research, such as Dynamo [7], DynamoRIO [13], and Mojo [29]. Dynamo intends to offer a client-side performance delivery mechanism, and mainly targets single-threaded applications on the HP PA-RISC architecture. Mojo, developed at Microsoft, targets the x86 architecture and desktop computing environment, which has rich multithreaded applications.

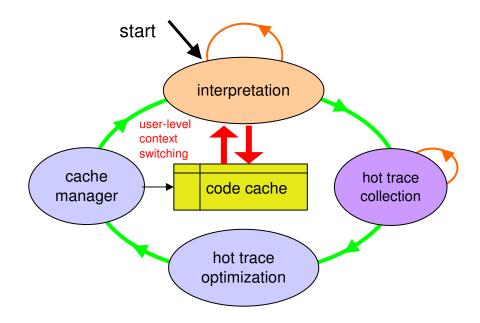

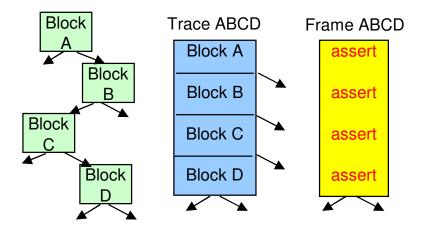

Dynamo provides transparent dynamic optimization on binaries without any support from user annotation, operating system, or underlying hardware architecture. Dynamo detects a program's frequent instruction execution streams (called *hot traces*) by directly interpreting the statically compiled binary. Here, a hot trace is a single-entry-multiple-exit instruction sequence. Dynamo exploits optimistic detection strategies to quickly identify hot traces in order to reduce the costly overhead of interpretation. After a hot trace is identified, Dynamo stops interpreting the current application and starts optimizing the hot trace. Interpretation resumes after the optimization is done. When Dynamo encounters the same instructions during future interpretation as the optimized trace, it does a user-level context switch so that the optimized code can be executed natively (instead of interpreted). Dynamo interleaves code interpretation and native execution, as shown in Figure II.1.

Mojo [29] has a similar optimization flow as Dynamo, but it targets multithreaded Windows applications. Mojo makes two design improvements over Dynamo. (1) Mojo uses the Just-in-Time direct translation approach to simulate a basic block, instead of code interpretation in Dynamo. Direct translation involves copying a basic block into a buffer, augmenting the buffer with control instructions at the end, and executing the instruction buffer. The control instructions will ensure the control returns to the Mojo dispatcher after the buffer is executed. (2) Mojo partitions the *Code Cache*, where optimized traces are stored, into several sections. It fills the sections one at a time. Optimized traces are invalidated gradually by flushing out the oldest section. This policy incurs lower trace re-optimization overhead and has quicker adaptation to the program's behavior than the global flushing in Dynamo.

A common attribute of these systems is that optimization is typically

Figure II.1: Dynamo interpretation and optimization flow. Dynamo starts with interpretation of the program's binary. The program is profiled while being interpreted. When Dynamo detects a hot path, it switches to the collecting phase where the trace is formed. The trace is then being optimized and inserted into the code cache. So Dynamo interleaves interpretation/profiling, trace optimization, and native execution of optimized traces.

performed in the same thread as the main execution within a single hardware context. Sharing the same hardware context requires the system to pause the current program's execution in order to perform optimization. This also introduces additional runtime overhead due to heavyweight user-level context switching between execution, profiling, and optimization. So, these systems often adopt simple and optimistic strategies to reduce profiling and hot trace detection cycles. But these strategies can result in poor quality of hot traces. Similarly, these systems also perform less sophisticated optimizations to reduce optimization overhead.

The binary optimization framework proposed by Ootsu, et al. [101], focuses on detecting parallelizable loops in a single-threaded binary to speed up loop execution on multithreaded processors. The framework uses two phases of translation and optimization. Static translation and optimization (*STO*) analyzes the binary to identify control and data flow information, and instruments the binary to collect profiles at runtime. Dynamic translation and optimization (*DTO*) performs further optimizations partially done by STO. Trident, as described in this thesis, differs in that it performs all of its analysis on a code fragment in a parallel helper thread, so it requires no static analysis and instrumentation. In addition, rather than relying on statically identified events for optimization, Trident triggers optimization from dynamically identified hardware events.

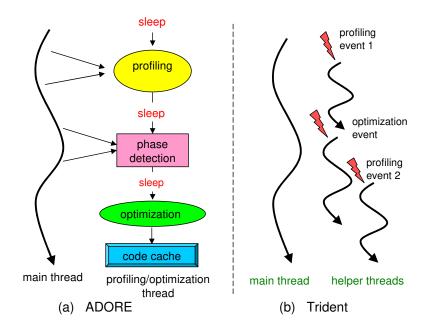

The *ADORE* framework [85, 26] is the closest runtime optimization system to the Trident framework. ADORE is a two-thread model, as shown in Figure II.2 (a). It lets the application run in one thread, and uses a separate OS level thread to perform profiling and optimization (i.e., prefetching). ADORE takes advantage of Intel Itanium hardware counters [63] to collect a sequence of raw profile segments. The profiling thread periodically wakes up to mine through the raw profiles to detect any meaningful behavior patterns. These patterns identify the instruction PC's inside the program's hot traces. After

Figure II.2: ADORE and Trident threading models. ADORE interleaves profiling/analysis, phase detection, and optimization in a dedicated stand-alone thread. Trident allows multiple lightweight helper threads to be active concurrently. One helper thread is triggered to form a hot trace upon the profiling event, while the other thread can perform further optimizations on an optimized trace, which has been formed early.

being identified, hot traces are stored in a buffer and stay unused. The profiling thread begins to collect more profiles to detect the program's phase behavior. Only after a stable phase is detected, will the profiling thread begin to optimize hot traces. Otherwise, the thread will start over for both hot trace and phase detection. ADORE performs multitasking of profile collection, profile analysis, phase detection, and optimization inside a single thread. It is different from Dynamo in that ADORE performs these tasks in a separate thread and does not pause the main thread's execution.

Our Trident is built on the above ideas (from Dynamo and ADORE), but it dramatically reduces the profiling and optimization overhead. With the removal of the overhead constraint, Trident is flexible enough to reconsider the optimization strategies, and has more freedom to re-optimize the code to take advantage of efficient hardware mechanisms available in new architectures. Trident makes these clear distinctions from previous work.

- The Trident framework focuses on reducing the overhead of profiling and optimization by proposing lightweight hardware support to perform all of the profiling needed to guide dynamic optimization. This avoids software profiling/analysis overhead and associated context switching overhead.

- The hardware interacts with the optimization framework by generating optimization events. These events are quickly handled by helper threads to make optimization decisions as well as to perform optimizations with very low overhead. Thus, Trident can react immediately to the program's behavior changes and adapt to shorter phases.

- Trident's event-driven nature makes it possible to process multiple optimization events via multiple helper threads simultaneously, as shown in Figure II.2 (b). All helper threads run concurrently with the main thread. Therefore, it allows continuous monitoring of more complex program behavior and allows continuous and recurrent optimizations. Trident naturally enables aggressive optimization by applying simple optimizations gradually, and provides the ability to recover from previous bad optimizations.

### **II.B.2** Translation Optimization Systems

Dynamic optimization is commonly seen in dynamic translation systems [41, 42, 10] through just-in-time compilation. Translation occurs from one ISA to another existing or proprietary ISA. These systems usually focus on compatibility or power efficiency issues. Optimization is often limited to the level of the basic block. Binary translation is discussed more thoroughly by Altman, et al. [4].

In the Java Virtual Machine (JVM) [103, 15, 34], the JIT compiler interprets/compiles abstract Java byte-code and optimizes it to run on native machines. Optimization is usually tightly coupled with the virtual machine semantics. Runtime compilation overhead may be reduced with *Lazy Compilation* [77], where individual Java methods are compiled on demand upon their first invocation. The overhead may be further reduced using the *Background Compilation* technique, which uses an extra dedicated thread to perform just-in-time compilation on the background. The Java methods to be background compiled are prioritized according to static profiling.

The Jrpm system [27], with a similar motivation as [101], speculatively parallelizes a single-threaded Java program to run on a CMP processor with thread-level speculation (TLS) support [56]. Because CMPs have relative low sharing and communication cost, programs can be optimistically (via TLS) parallelized without violating correct sequential program order. Implemented as a Java virtual machine with dynamic compilation support, Jrpm is coupled with a hardware profiler to identify candidate loops to parallelize at runtime.

Our approach builds on all the research above, but uses helper threads to provide low overhead dynamic optimization of any binary running on the processor.

#### **II.B.3** Selective Compilation