### UC Berkeley UC Berkeley Electronic Theses and Dissertations

### Title

Unlocking Design Reuse with Hardware Compiler Frameworks

### Permalink

https://escholarship.org/uc/item/37f2j2qq

### Author Izraelevitz, Adam Moshe

# Publication Date 2019

Peer reviewed|Thesis/dissertation

Unlocking Design Reuse with Hardware Compiler Frameworks

by

Adam Izraelevitz

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

$\mathrm{in}$

Engineering – Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Adjunct Professor Jonathan Richard Bachrach, Co-chair Professor Krste Asanović, Co-chair Professor Simon Schleicher Professor Jonathan Ragan-Kelley

Fall 2019

### Unlocking Design Reuse with Hardware Compiler Frameworks

Copyright 2019 by Adam Izraelevitz

#### Abstract

#### Unlocking Design Reuse with Hardware Compiler Frameworks

by

Adam Izraelevitz

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences University of California, Berkeley

Adjunct Professor Jonathan Richard Bachrach, Co-chair

Professor Krste Asanović, Co-chair

Emerging applications from the edge to the cloud are constantly increasing demand for energy efficient and performant computation. While specialized hardware can meet these power and performance goals, the high non-reoccurring engineering (NRE) costs of designing, testing, and verifying custom hardware severely hinders its supply. Hardware construction languages such as Chisel enable hardware designers to write parameterized hardware libraries which increase design reuse by turning NRE effort into reusable solutions for future specialized chips. This thesis introduces FIRRTL, Chisel's hardware compiler framework, which enables automatic and custom RTL-transformations including logic optimization and design instrumentation. In addition, this thesis proposes an aspect-oriented-inspired paradigm, Colla-Gen, as a mechanism to improve design collateral reuse (e.g. physical design floorplanning or verification instrumentation), which forms another large portion of chip NRE costs. To my parents David and Terry, who taught me to look forward.

To my brothers Joe and Jacob, who taught me to appreciate the moment.

To my partner Christine, who taught me that things outside my thesis matter most of all.

## Contents

| Co | Contents                                                                                                                                                                                                                                                        |                                                                   |  |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--|

| Li | t of Figures                                                                                                                                                                                                                                                    | iv                                                                |  |

| Li | t of Tables                                                                                                                                                                                                                                                     | v                                                                 |  |

| 1  | Introduction1.1The Trend of Hardware Specialization1.2Reducing Per-Chip NRE Costs1.3Summary of Research Contributions1.4Previous Publication, Collaboration, and Funding                                                                                        | <b>1</b><br>1<br>3<br>4<br>5                                      |  |

| 2  | An Analysis and Proposal for Hardware Design Methodologies2.1Incorrect Hypotheses2.2Hypothesis 1—Existing HDLs lack expressivity2.3Hypothesis 2—Underlying complexity requires RTL customization2.4Hypothesis 3—Design collateral is necessary but not reusable | 7<br>7<br>8<br>9<br>10                                            |  |

| 3  | Hardware Construction Languages3.1Limitations of Hardware Description Languages3.2Hardware Construction Languages for Hardware Libraries3.3Evaluating Chisel's Support for Hardware Libraries3.4Summary                                                         | <b>14</b><br>14<br>16<br>17<br>19                                 |  |

| 4  | FIRRTL: A Hardware Intermediate Representation and Compiler Frame-<br>work                                                                                                                                                                                      | 21                                                                |  |

|    | 4.1Background4.2FIRRTL's Intermediate Representation4.3Width, Bound, and Precision Inference4.4Specificity and Metadata4.5Circuit Traversals4.6Transformation Evaluation4.7Summary                                                                              | $ \begin{array}{c} 22\\ 24\\ 29\\ 34\\ 40\\ 49\\ 64 \end{array} $ |  |

|    | ·                                                                                                                                                                                                                                                               |                                                                   |  |

iii

| 5  | Colla-G      | en: A Chisel Interface for Hardware Collateral                                                                     | Generation | 65  |  |  |  |  |  |  |

|----|--------------|--------------------------------------------------------------------------------------------------------------------|------------|-----|--|--|--|--|--|--|

|    | 5.1 Asp      | pect-Oriented Programming                                                                                          |            | 66  |  |  |  |  |  |  |

|    | 5.2 The      | e Colla-Gen Interface                                                                                              |            | 69  |  |  |  |  |  |  |

|    | 5.3 Col      | la-Gen Library Examples                                                                                            |            | 75  |  |  |  |  |  |  |

|    | 5.4 Sur      | nmary                                                                                                              |            | 80  |  |  |  |  |  |  |

| 6  | Researc      | h Contributions and Future Outlook                                                                                 |            | 83  |  |  |  |  |  |  |

|    | 6.1 Sta      | tus and Future Work                                                                                                |            | 84  |  |  |  |  |  |  |

| Α  | The FI       | RRTL Specification                                                                                                 |            | 87  |  |  |  |  |  |  |

|    | A.1 Pro      | ject History                                                                                                       |            | 87  |  |  |  |  |  |  |

|    |              | ails about Syntax                                                                                                  |            | 88  |  |  |  |  |  |  |

|    |              | $\tilde{\rm cuits}$ and $\tilde{\rm Modules}$                                                                      |            | 89  |  |  |  |  |  |  |

|    |              | Des                                                                                                                |            | 90  |  |  |  |  |  |  |

|    |              | $tements \ldots \ldots$ |            | 95  |  |  |  |  |  |  |

|    |              | pressions                                                                                                          |            | 113 |  |  |  |  |  |  |

|    |              | mitive Operations                                                                                                  |            | 120 |  |  |  |  |  |  |

|    |              | WS                                                                                                                 |            | 131 |  |  |  |  |  |  |

|    |              | nespaces                                                                                                           |            | 132 |  |  |  |  |  |  |

| Bi | Bibliography |                                                                                                                    |            |     |  |  |  |  |  |  |

# List of Figures

| $2.1 \\ 2.2 \\ 2.3$ | Underlying constraints require programmatic transformations of RTL9CAD-tool command APIs lack concern abstractions.1Hammer software architecture overview.1 |   |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 3.1                 | Parameterizing a hardware module's condition to filter incoming packets 1                                                                                   |   |

| 3.2                 | OpenPiton versus BOOM source code comparison                                                                                                                | - |

| 3.3                 | Rocket versus BOOM area and performance comparison                                                                                                          | 9 |

| 3.4                 | Reusability of Rocket, BOOM and DecVec source code                                                                                                          | 0 |

| 4.1                 | LLVM and HCF software architecture                                                                                                                          | 2 |

| 4.2                 | Forward-backward substitution for solving constraints                                                                                                       | 3 |

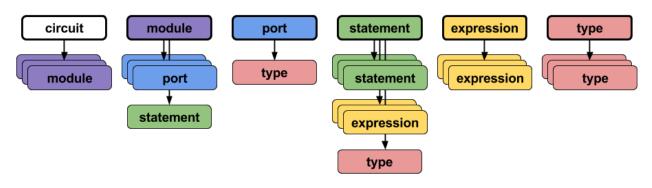

| 4.3                 | FIRRTL AST and children node types                                                                                                                          | 2 |

| 4.4                 | Example FIRRTL circuit and AST                                                                                                                              | 2 |

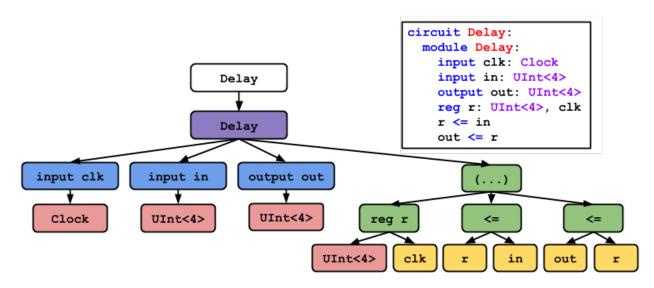

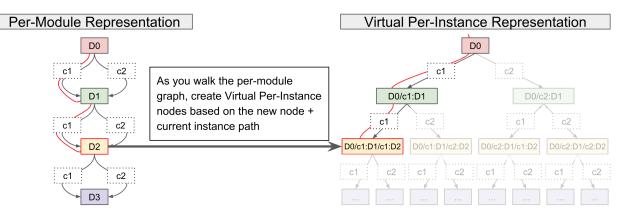

| 4.5                 | In-memory representations: per-module versus per-instance                                                                                                   | 5 |

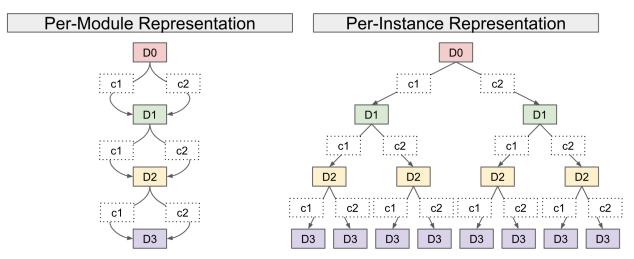

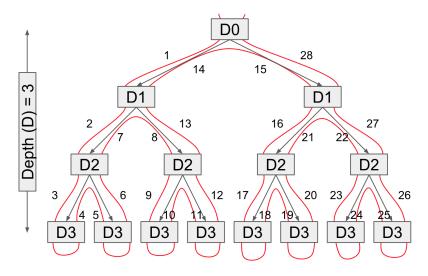

| 4.6                 | Example of FIRRTL connectivity path length                                                                                                                  | 6 |

| 4.7                 | Topological search example                                                                                                                                  | 7 |

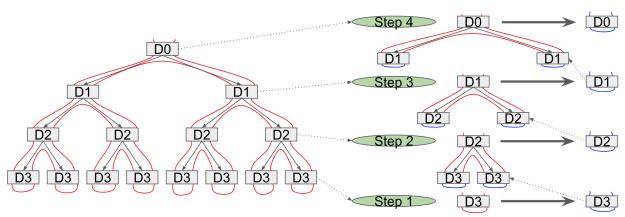

| 4.8                 | Virtual occurrence graph example                                                                                                                            | 8 |

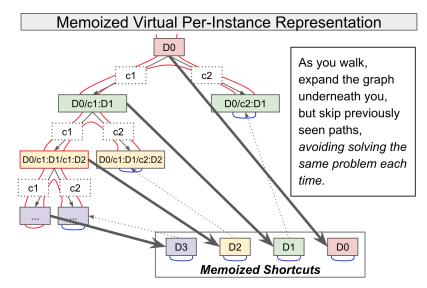

| 4.9                 | Memoizing search on a virtual occurrence graph                                                                                                              | 0 |

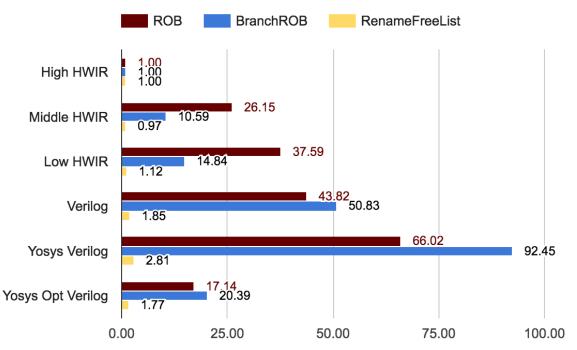

| 4.10                | FIRRTL code size expansion during lowering                                                                                                                  | 3 |

| 4.11                | FIRRTL versus Yosys logic optimization evaluation                                                                                                           | 5 |

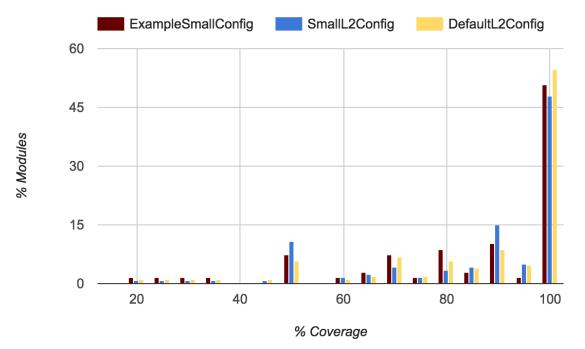

| 4.12                | Demonstration of line coverage for Chisel modules                                                                                                           | 1 |

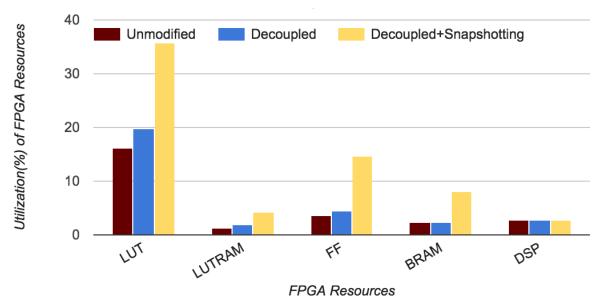

| 4.13                | FPGA decoupling and snapshotting transforms evaluation                                                                                                      | 2 |

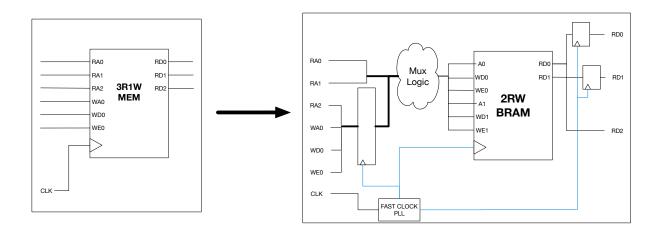

| 4.14                | FPGA double-pumping memory transformation evaluation                                                                                                        | 2 |

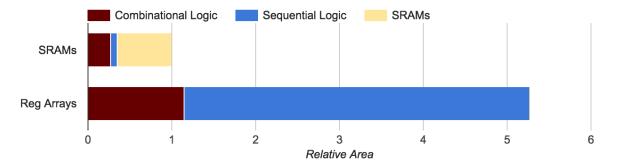

| 4.15                | FIRRTL SRAM transformation evaluation on a Chisel FFT design 6                                                                                              | 3 |

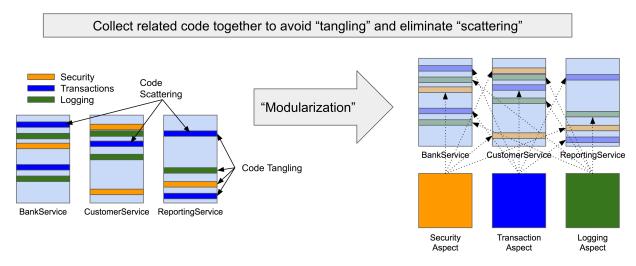

| 5.1                 | Code scattering and modularization with aspect-oriented programming 6                                                                                       | 6 |

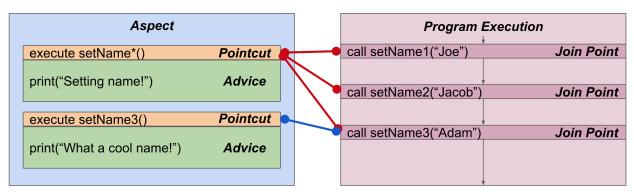

| 5.2                 | Aspect-oriented programming example                                                                                                                         | 7 |

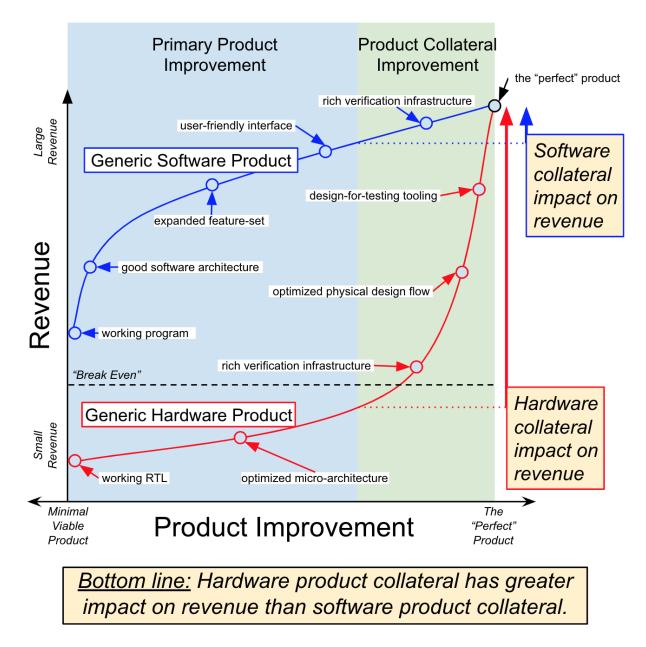

| 5.3                 | Illustration of important of product collateral to hardware design                                                                                          | 8 |

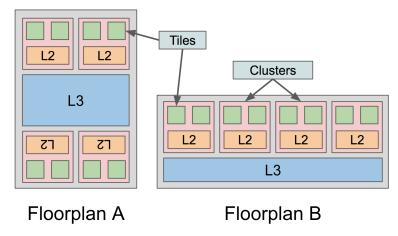

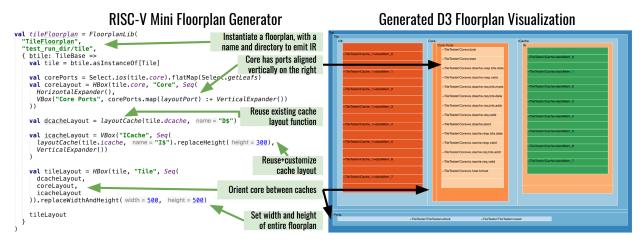

| 5.4                 | Floorplanning example                                                                                                                                       | 0 |

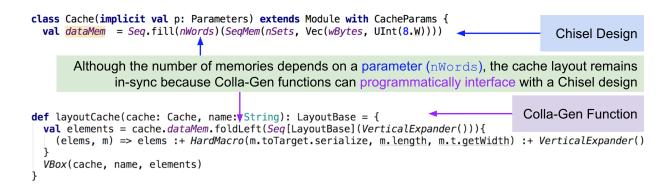

| 5.5                 | Example of floorplanning Colla-Gen library                                                                                                                  | 3 |

| 5.6                 | Synchronization of floorplan with Chisel generator.                                                                                                         | 3 |

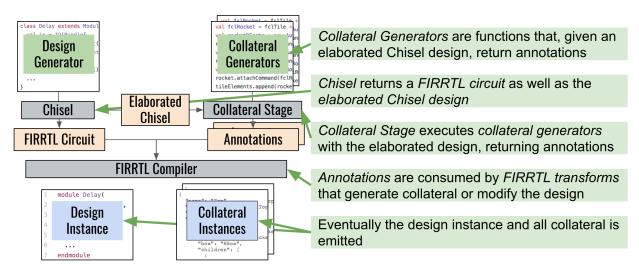

| 5.7                 | Colla-Gen software architecture                                                                                                                             | 4 |

## List of Tables

| 4.1 | Constraint extraction for bound and precision inference. | 32 |

|-----|----------------------------------------------------------|----|

| 4.2 | Target concrete syntax                                   | 38 |

| 4.3 | Examples of renaming targets                             | 41 |

### Acknowledgments

This dissertation could not have been conceived, achieved, nor written without the help of many of the faculty and students in the ASPIRE/ADEPT lab, and the University of California, Berkeley, as well as many of my own personal friends and family whose support was immense.

I would like to thank the following individuals in particular for their contributions to the Chisel and FIRRTL ecosystem, upon which this entire thesis is built:

- Patrick Li: for designing and implementing the first prototype of the FIRRTL language, writing the initial specification for the language, and jointly writing the current specification for the language. Thank you for your constant mentorship and belief in me; I am immensely grateful for our collaboration and friendship. I divide my PhD into three parts: before, during, and after Patrick. You are a landmark in my life.

- Jack Koenig: for numerous and substantial contributions to the FIRRTL and Chisel projects including asynchronous reset, parameterized black boxes, ANTLR parser, Protobul parser, dontTouch annotation, refactoring annotations, Travis+Yosys continuous integration, improving optimization passes, improving compiler speed and memory usage, improving the ExpandWhens pass, reworking name uniquification, mappers implementation, clock/reset scoping, the record type, printable, along with many bug-fixes and community/governance/outreach contributions. Thank you for being such an amazing collaborator full of new ideas, endless motivation, and uplifting spirit. Keeping your contributions open source is a difficult yet often thankless job: thank you. Finally, thank you for teaching me that projects could be shared and are better for it, as well as making me a better programmer (given you review most of my code, I'm not sure that was purely selfless...).

- Edward Wang: for collaborating with me on your Hammer project and the floorplan DSL, as well as the MixedVec implementation and significant contributions to the bootcamp and other documentation. Our conversations about collaboration challenged, clarified and improved my own views about the subject. Thank you for teaching me so much about how to be a good mentor, friend, and listener; thank you also for listening to my good advice and discarding my bad advice.

- Schuyler Eldridge: for numerous and substantial contributions to the FIRRTL and Chisel projects including stage refactoring, dependency API, improving wiring transform, and library registration; for running Chisel outreach and massive improvements to the website. You are a selfless collaborator both in the time you contribute and the ideas you share. Once you grab on you never let go, and your ability to identify and embrace what you enjoy serves as an inspiration to me when I'm discouraged.

- Chick Markley: for numerous and substantial contributions including the FIRRTL interpreter, Treadle, Chisel intervals and fixed-point implementations, the logger, the

load memory feature, creating the new testing harness, porting the Chisel tutorial, overseeing the GUI and visualizer along with many bug-fixes and community/governance/outreach contributions. Thank you for your consistent work ethic yet easy-going attitude; it often kept me focused while still seeing life's big picture.

- Albert Magyar: for numerous and substantial contributions to the FIRRTL and Chisel projects including the FPGA memory transform and data collection, combinational loop detection, specification clarifications, improving constant propagation, digraph library, FIRRTL memory utilities, and clone module. It was wonderful being your lab partner in class and life. Your unique perspective on complex problems always helped clarify my research direction. Thank you for the unwavering support in both the technical and emotional sides of my PhD.

- Richard Lin: for numerous and substantial contributions to Chisel including improving the Chisel 3.0 code base for release quality, improving testing infrastructure, significant bootcamp contributions, bundle literals, naming annotations, autoclonetype, bindings refactor, module hierarchy refactor, Chisel ranges, along with many bug-fixes and community/governance/outreach contributions. Thank you for your unwavering belief in, love of, and sacrifices for this project, and for teaching me that a user's experience is paramount.

- Jim Lawson: for numerous and substantial contributions to Chisel and FIRRTL including improving the Chisel 3.0 code base for release quality, continuous integration features, compatibility mode, code releases, Verilog front-end, along with many bug-fixes and community/governance/outreach contributions. Thank you for your willingness to do the unglamorous tasks with consistent enthusiasm and completeness; I will always appreciate your humor, which is rarely shown but treasured when found.

- Andrew Waterman: for contributions to the design of FIRRTL's constructs and Chisel 3.0, porting architecture research infrastructure, and FIRRTL optimization passes. Thank you for your eager and excellent advice, but more personally for your willingness to place your trust into me as a new and inexperienced graduate student.

- Henry Cook: for porting and cleaning up many aspects of Chisel 3.0, including the testing infrastructure and the parameterization library. Thank you for your early mentorship and for providing me with an amazing graduate student role model.

- Angie Wang: for your contributions to FIRRTL including the ReplSeqMem transforms and memory utilities, as well as your original insights into interval analysis. Your encouragement of my values regarding team social dynamics allowed me to trust my own voice and be a better advocate for my colleagues.

- Paul Rigge: for your contribution and leadership in the Chisel bootcamp project, as well as your significant contributions to our collaboration in DSP tools and interval

analysis. Your willingness to collaborate and discuss any topic with a deep and measured perspective made our conversations uniquely valuable and inspirational.

- Donggyu Kim: for your contributions to the FIRRTL project including the latency pipe memory transformation, the inference of readwrite memory ports, and memory utility library contributions. Thank you also for our early Strober collaboration and the passion, drive, and hard-working spirit you bring to your work and collaborations; you take the "make it work" mantra to a new level.

- Stephen Twigg: for insights into the design of FIRRTL, and for many foundational improvements to the Chisel language. Thank you for challenging my conceptions about hardware intermediate representations, educating me in proper software development practices and the Scala language. Most importantly, thank you for teaching me to listen, stay humble, and reconsider my actions.

- Stevo Bailey: for contributions to the bootcamp, the CRAFT project, and for your advocacy of an agile design methodology. Thank you for bringing such a positive spirit and focused work ethic to our collaborations.

- Albert Chen: for contributions to the FIRRTL project including the clarification and implementation of the renaming algorithm, as well as implementing Verilog comments. I appreciate your reserved approach of active listening and precision of words, which kept our collaboration on topic, productive, and efficient.

- John Buchan: for the original contribution of the context dependent environment parameterization implementation. Our collaboration was one of my first attempts at research, and your willingness to mentor me and share your ideas set an excellent example for an impressionable young PhD student.

- Chris Celio: for converting BOOM to Chisel 3.0 and collecting data for motivating the project through code reuse. You were always by my side (figuratively and literally) and your mix of passion and perspective that life exists outside of a PhD served as an excellent role model that I have tried to emulate.

The road taken throughout a PhD takes many turns, and I've often relied on the support of my colleagues for both their technical expertise as well as their compassion. I'd like to additionally thank Orianna Demasi, Michael Driscoll, Yunsup Lee, Lisa Wu, Sarah Bird, Scott Beamer, Palmer Dabbelt, Eric Love, Martin Maas, David Biancolin, Ben Keller, Jenny Huang, Arya Reais-Parsi, Nathan Pemberton, John Wright, Kevin Laeufer, Howard Mao, Ameer Haj Ali, Alon Amid, David Bruns-Smith, Hasan Genc, Abraham Gonzalez, Sagar Karandikar, Ben Korpan, Dayeol Lee, Albert Ou, Jerry Zhao, Brendan Sweeney, Kyle Kovacs, and Danny Tang. You all made my work a second home through your willingness to commiserate in our failures and celebrate in our successes. I would not be here without such consistent and excellent mentorship to help me navigate the confusing, non-linear, and difficult trek through academia. Mike Hamada and Christine Anderson-Cook took me under their wings at Los Alamos National Laboratory and surprised an intimidated high school student with their unwavering encouragement of my creativity - I learned from you that creative projects spark passion, and rules (while not made to be broken) are certainly made to be questioned. David Albonesi and Paula Petrica gave me the opportunity to work in their lab at Cornell, and with them I found a collaboration which valued my contributions, a mentorship which gave me the perfect mix of freedom and guidance, and opened my eyes to the beautiful world of computer architecture and hardware design methodologies.

My path through Berkeley was helped through by many staff and faculty. Ria Briggs, Tamille Chouteau, Kostadin Ilov, Roxana Infante, and Shirley Salanio are amazing administrators who constantly tackled logistical, bureaucratic, and technical obstacles to create a distraction-free and productive environment for graduate student research; I have zero doubts that my PhD would have been significantly longer and more painful without their constant and timely interventions. Borivoje Nikolić was an unofficial advisor to me and fully embraced both the Chisel ecosystem and my contributions to it. Jonathan Ragan-Kelley and Simon Schleicher provided me with novel and useful perspectives on the impact of my research and the choices I made when designing the FIRRTL compiler. To my secondary advisor, Krste Asanović: you are a man of few words but each is packed with meaning. Thank you for the advice - the technical but more importantly, the personal.

This thesis would not have been possible without the continuous feedback and encouragement of my primary advisor Jonathan Bachrach. His leadership in vision and implementation of Chisel's ecosystem has been constant from the start. Thank you for believing in me, investing in me, and giving me the room to grow (and for encouraging me to take a programming languages class).

While on paper a PhD is a solitary achievement, in reality it is the culmination of decades of personal investment into me as a person by those individuals who care and sacrifice the most. To my friends outside of Soda Hall, thank you for the closeness when I needed it, the space when I didn't, and the support always. To my friend and lab partner Colin Schmidt: you are an extraordinary individual with equal parts passion and compassion. Your single focus towards impact coupled with your love of humanity continues to be an inspiration. Keep on trucking; your friends and family are here for you.

To my parents David and Terry, brothers Jacob and Joe, sisters-in-law Leah and Lauren (and nephew Nathan): what a family. Your support for me on the sidelines has kept me going when the tank was empty. I am eagerly looking forward to our family's journey together through more of life's joys and challenges.

To my partner Christine: you are witness to my darkest and brightest moments, and have stood proud anyways. I love you dearly; thank you for always helping us build a joyous life - a life I am so privileged to share with you.

# Chapter 1 Introduction

The end of Dennard scaling and the slowing of technology advances are eliminating the associated "free" power, performance, and area improvements for digital circuits. Since specialized hardware implementations have enormous energy and performance improvements over software on a general-purpose processor, specialization is hardware design's path forward for the foreseeable future. This trend manifests in an increasing demand for diverse products containing different specialized digital logic descriptions, also known as RTL (register-transferlevel). Meeting this demand with existing methodologies is difficult.

In contrast, the software industry has faster design cycles than the hardware industry; a small team can go from idea to profitable software in under two weeks. What can the hardware industry learn from the software community?

A key contributor to software industry's productivity is reusable libraries, which amortize development and verification costs of new applications. These libraries are built upon expressive languages with retargetable compilers that perform platform-specific optimizations on general-purpose code.

In comparison, hardware reuse is relatively rare; no widely-used reusable hardware library exists. However, if hardware projects reused more code, engineers might spend less time designing and, more importantly, less time verifying the new design. Since the benefits of reusing code are clear, *why don't hardware engineers write reusable libraries?*

This thesis attempts to answer this question, as well as describe the infrastructure necessary to develop reusable hardware libraries.

### 1.1 The Trend of Hardware Specialization

Novel applications are discovered daily which demand faster computation and lower power requirements. To meet this need, the hardware community proposes specializing hardware to the demands of the application; instead of accelerating general-purpose computation, companies design processors which quickly and efficiently execute a single, specific application (specialization). For example in autonomous driving, a car must quickly recognize obstacles such as pedestrians in their path - this low latency, high complexity calculation requires significant computation embedded within the car. Enhancing a car with a specialized image-processing chip running image-processing code meets these requirements; the chip's lack of general-purpose usability is immaterial given the restricted application domain. However, the market's relatively low volume demand of per-application chips restricts hardware manufacturers because they cannot offset their custom chip designing and engineering costs through selling high volumes of that chip.

### From Idea to Product

Prior to specialization, a company addressed an application by selling customized products containing commodity general-purpose chips. This previous era enabled large chip companies such as Intel to design a single generic chip that was manufactured in bulk and sold to a wide variety of per-application companies who integrated the chip within their product. Today in the post-Moore's Law age of computing, this business model breaks down because one general-purpose chip is neither fast enough nor efficient enough to address the full spectrum of modern application demands.

Without this market for general-purpose chips, application companies must accommodate the custom chip design effort within their process of transitioning from idea to product. Now, a company undergoes the following steps where the time, effort and cost of designing a new specialized chip directly delays the time-to-market:

- 1. Identify new application

- 2. Design new algorithm

- 3. Write software for new algorithm

- 4. Design hardware that runs that software quickly<sup>1</sup>

- 5. Produce chip, deploy design, sell product

Using current methods to design, verify, and produce a chip, there are staggering amounts of non-reusable-engineering (NRE) costs (e.g. the engineers' salaries). While previously chip companies amortized the large NRE cost bottleneck by selling millions of identical chips and reducing the per-chip NRE cost, the current market lacks sufficient demand to sufficiently amortize this cost. In the age of specialization, the per-chip NRE cost becomes the dominating cost of producing a specialized chip.

$<sup>^1 \</sup>mathrm{Ideally\ hardware}/\mathrm{software\ are\ designed\ in\ tandem}$

### 1.2 Reducing Per-Chip NRE Costs

Writing reusable designs, rather than one-off designs, allows greater amortization of NRE costs into recurring engineering costs. This approach requires a shift in thinking from traditional hardware engineers; in addition to designing their product, engineers consider how their design is reused in a future design. When a higher percentage of their work is directly usable in future designs, NRE cost of the next chip is reduced. Over time, the cost of developing and verifying a design is amortized over each future usage. In summary, the goal of designing a chip is to finish a design as well as contribute to a reusable chip-design ecosystem.

Suppose an existing design almost solves a new need; rather than starting afresh or copypaste-modifying (both of which create new designs and restart the NRE-amortization), an engineer "grows" the existing design to address their new use case and preserve existing use cases; all existing designs are then updated to the new version. This approach reduces the growth of code whose maintenance, design, and verification costs contribute to the total NRE cost, while constant design sharing continuously amortizes the original NRE effort. Ideally, bringing up a new chip uses existing designs, existing verification infrastructure, and existing physical designs. Any new code an engineer writes is refactored and contributed back to the ecosystem to be used by others.

Recently, the hardware industry has increased its reuse of large complex custom IP blocks at the system-on-chip (SoC) level, which has had many benefits including faster time to market and reduced verification effort. However, custom IP blocks are usually very specialized, as opposed to being basic building blocks of hardware like queues, arithmetic units, multipliers, caches, and so on, and pose more integration challenges than a typical reusable library.

Take an analogy to software - if an open source library almost addresses a new use case, upstreaming a new API (application programming interface) or feature increases the power of the library, while rewriting the library or modifying it without contributing back increases the total amount of code to design and verify. Analogous to hardware IP (intellectual property) blocks, hand-optimized assembly routines are reusable but limited in scope, which distinguishes them from these wide-ranging and fully featured libraries. In short, reduce NRE costs by designing hardware and software for reuse and growing their codebases with new features.

A large majority of the NRE costs of designing a chip are in the verification and physical design of the chip, not just the digital logic of the hardware. Here is where the previous analogy to software breaks down. First, most software requires significantly less verification than hardware, as software bugfixes are relatively cheap to deploy. Secondly, compilers successfully increase code reusability by isolating code from computational platforms. Thirdly, slow but correct code can be iteratively improved upon via updates, making software's initial performance a lesser concern.

Hardware is different. Bugs are extremely costly to fix, if downright impossible. Most

hardware is very coupled to the underlying technology, exacerbating the lack of reusability. Finally, the production of chips is so expensive that slow chips are effectively useless and companies must invest significantly into early optimization of their design.

Verification infrastructure and physical design tools require additional design collateral which must also be reused. A hardware design is not simply the digital logic description of a chip; rather the design includes the digital logic + verification tests/in-frastructure + simulation mapping collateral + physical design scripts + input/output cell placements + SRAM macro compiler calls + etc.

As demonstrated in Chapter 2, the existing flaws of verification technologies, design languages, and physical design tools limit the degree of design reusability; an engineer cannot write reusable designs given these tools. For example, the parameters supported by a design language directly influence a design's reusability; if a desired parameterization is not supported, then the code must be duplicated and modified. Another example is how the mixing of concerns within a codebase reduces its reuse potential. If a verification flow implicitly depends on a transistor technology, then every future design that uses a different transistor technology cannot use this flow, regardless of other design similarities.

Take another analogy to software - if a library is written only using x86 assembly, it cannot run on an ARM machine. Similarly, a design that directly instantiates 14nm SRAMs can never be reused in a 7nm process.

The existing software paradigm of aspect-oriented programming is well-suited as inspiration to solve the problem of reusing hardware design collateral.

Software aspect-oriented programming (AOP) is not widely adopted because the benefits of reusing software code collateral do not offset the downsides of aspect-oriented programming. In contrast, the degree of necessary hardware design collateral significantly improves the overall outcome of applying an AOP-inspired approach; the benefits from reusing design collateral outweigh the added downsides. In fact, the hardware design collateral problem is so severe that many predominant physical design and verification flows are aspect-oriented in spirit; if rewritten with a consideration of aspect-oriented programming, these flows would enable clearer semantics, more reuse, and more powerful features. In all, introducing an aspectoriented approach brings reusability to hardware design collateral and enables a healthy chip design ecosystem.

### **1.3** Summary of Research Contributions

This thesis contributes the following:

- Chapter 1: An introduction to hardware specialization, non-reusable engineering costs and its impact on hardware design reusability

- Chapter 2: Four hypotheses accounting for the stagnation of hardware library development, as well as an overview of the Hammer framework which enables the abstraction of physical design concerns

- Chapter 3: An introduction and evaluation of Chisel, a hardware construction language which enables the ability to express reusable hardware designs. This chapter includes the following: (1) an analysis of existing hardware description languages and their flaws, (2) an analysis of Chisel as a primary tool for hardware libraries, and (3) an evaluation of Chisel's support for hardware libraries

- Chapter 4: A complete description of FIRRTL, a new hardware compiler framework and intermediate platform-agnostic representation, and how it isolates the digital logic design from the underlying physical design/verification concerns through an ecosystem of automatic digital logic transformations. This chapter includes the following: (1) analysis of LLVM, an existing software compiler framework; (2) introduction of FIR-RTL's intermediate representation (IR); (3) description of value inference (e.g. widths) and its implementation; (4) support for arbitrary metadata throughout the compilation process; (5) the mechanisms for transforms to inspect and modify a design; (6) a description of interesting transformations; (7) an evaluation of the FIRRTL compiler framework

- Chapter 5: An introduction of Colla-Gen, an AOP-inspired approach as a user-facing language to express reusable design collateral, thus enabling an ecosystem of design collateral libraries. This chapter includes the following: (1) a detailed description of aspect-oriented programming (AOP), an analysis of its flaws, and an argument for its consideration within a hardware context; (2) an introduction to Colla-Gen illustrated with a physical design floorplanning example; (3) Colla-Gen's implementation and additional reusable libraries for generating design collateral are presented and discussed

- Chapter 6: A conclusion on the results of this thesis and a discussion of future directions of this research

- Appendix: A full specification of the FIRRTL intermediate representation

### 1.4 Previous Publication, Collaboration, and Funding

Some of the content and figures in this thesis are adapted from previous paper submissions that are the result of multiple collaborations. While the majority of the research content, design, and implementation was done by myself, other collaborators made direct contributions to content discussed in this thesis. The following details their contributions.

The first submission is "Reusability is FIRRTL Ground: Hardware Construction Languages, Compiler Frameworks, and Transformations" [23]. Jack Koenig improved FIRRTL's optimization passes and provided its evaluation in Chapter 4. Patrick Li contributed the idea of simplification transformations and a preliminary design of the FIRRTL language, the final form of which is included in the Appendix. Richard Lin, Chick Markley, and Jim Lawson contributed heavily to improvements to Chisel, the hardware construction language analyzed in this project. Angie Wang contributed a version of the memory-replacement transformation and its evaluation in Chapter 4. Albert Magyar contributed the double-pumped FPGA memory transformation and its evaluation in Chapter 4. Donggyu Kim contributed the decoupling and snapshotting transformations and their evaluation in Chapter 4, as well as collecting the data about RocketChip and OpenPiton source code used in Chapter 3. Colin Schmidt contributed the details of the case study and coverage results in Chapter 4. Krste Asanović and Jonathan Bachrach provided guidance and feedback in all stages of the paper.

The second submission is "ACED: A hardware library for generating DSP systems" [45]. Angie Wang contributed the background of interval analysis in Chapter 4. Paul Rigge, Chick Markley, Jonathan Bachrach, and Borivoje Nikolić contributed to the theory, conception, and implementation of the interval analysis.

The third submission is "Hammer: Enabling Reusable Physical Design" [47]. Edward Wang contributed the first draft of the description of the Hammer project in Chapter 2 as well as being a major collaborator to the floorplan collateral generator described in Chapter 5. Colin Schmidt had multiple significant contributions to the Hammer project and paper, while Borivoje Nikolić, Elad Alon, and Jonathan Bachrach provided valuable feedback to the final draft of the paper.

Research partially funded by DARPA CRAFT HR0011-16-C-0052 and HR0011-12-2-0016; Intel Science and Technology Center for Agile Design; Center for Future Architecture Research, a member of STARnet, a Semiconductor Research Corporation program sponsored by MARCO and DARPA; NSF-GRFP (DGE-1106400); ADEPT Lab industrial sponsors and affiliates Intel, Google, Siemens and SK Hynix; ASPIRE Lab industrial sponsors and affiliates Intel, Google, HPE, Huawei, LGE, Nokia, NVIDIA, Oracle, and Samsung. The author would also like to acknowledge the sponsors, students, and faculty of the Berkeley Wireless Research Center, ADEPT Lab and ASPIRE Lab. Any opinions, findings, conclusions, or recommendations in this thesis are solely those of the author and do not necessarily reflect the position or the policy of the sponsors.

## Chapter 2

## An Analysis and Proposal for Hardware Design Methodologies

Existing solutions cannot reduce the per-chip NRE costs because they fail to sufficiently support a hardware design ecosystem. This chapter provides an analysis of current methodologies including hardware languages, compilers, and CAD tools, as well as outlines their flaws which inhibit effective reuse of hardware designs and increase non-recurring engineering costs. In addition, a cursory description is included of Hammer, a sister project which provides useful and reusable tool abstractions; however, keeping design collateral in-sync with a generated design remains a problem.

This chapter is organized through a discussion of the following three hypotheses that account for the stagnation of hardware library development (which are preceded by addressing alternative but incorrect hypotheses):

- 1. Existing hardware description languages lack the expressivity to support hardware libraries

- 2. Diverse underlying implementations require RTL customization, limiting a design's reusability

- 3. Effective physical design, verification, emulation and instrumentation require additional design collateral which is too tool/platform/technology dependent and too brittle in face of design modifications

### 2.1 Incorrect Hypotheses

Software libraries are pervasive in software development because, through code reuse, they reduce development and verification costs of new applications. Modern software relies on thousands of libraries—Ubuntu 14.04 has approximately 35,000 packages installed natively.

In direct comparison, hardware designers do not commonly reuse modules from project to project, let alone develop extensive and reusable libraries. As mentioned earlier, the

### CHAPTER 2. AN ANALYSIS AND PROPOSAL FOR HARDWARE DESIGN METHODOLOGIES

hardware industry has increased its reuse of large complex custom IP blocks at the SoClevel, but these custom IP blocks are specialized and pose more integration challenges than a typical reusable library. The amount of reusable hardware IP is a far cry from the ubiquity and usability of software libraries.

One could claim the lack of hardware libraries is from a lack of effort; yet in this author's experience, many companies try, but fail, to establish internal reusable libraries of hardware components.

One could also claim the lack of hardware libraries is from a lack of an open-source community; yet, popular open-source software is often written by one or two contributors. D3[7], the popular JavaScript visualization library, was primarily written by a single engineer, but has still seen widespread use.

### 2.2 Hypothesis 1—Existing HDLs lack expressivity

Programming languages have seen significant improvements since the 1980s when the majority of popular hardware description languages (HDLs) were designed (Verilog, VHDL). Modern advancements in mainstream programming languages have made languages like Java, C++, Python, Perl, and Ruby very powerful. Object-orientation, polymorphism, and higher-order functions enable the use of good software engineering principles like abstraction, separation of concerns, and modularity; these ultimately encourage and enable code reuse. HDLs have been very slow to adopt these paradigms.

An adder reduction tree illustrates this problem: Verilog and VHDL cannot express recursive generate statements, so a designer must manually unroll the loop and calculate indices for every instance. The lack of parameterization precludes re-use when a tree of different width is required.

Another example is a module that filters packets. With current HDLs, either the filter module or an external module must encode the filter condition. The first approach violates the principle of separation of concerns, while the second violates encapsulation. However, higher-order functions provide an elegant software engineering solution to the problem.

SystemVerilog, created in 2002, attempts to improve on existing HDLs by mixing in modern ideas like object-oriented programming with classic Verilog elements. The result is an extremely complicated language—intractable to support and confusing to learn—that is still missing other modern features like higher-order functions. To the author's knowledge, no commercial SystemVerilog compiler implements the entire specification.

High-level synthesis (HLS) takes a different approach by having the user design in a higher level language, with a compiler translating down to RTL. The input language can be C-like [50][31][11][8][44], a parallel C-like language [13][36][37], general purpose [2], or domain specific [18][20][32][21][33][22]. Many HLS tools are evaluated on simplicity of use, performance relative to a hand-coded implementation, succinctness, and resource footprint; their ability to foster reusable hardware libraries is not usually considered.

## CHAPTER 2. AN ANALYSIS AND PROPOSAL FOR HARDWARE DESIGN METHODOLOGIES

Unfortunately, HLS approaches suffer from two competing concerns: (1) a more expressive source language enables better software engineering (and thus more reusability); (2) a more expressive source language is more difficult to translate to hardware and creates more compilation/abstraction layers that the user must understand to fine-tune their design.

# 2.3 Hypothesis 2—Underlying complexity requires RTL customization

In spite of the success of logic synthesis, many underlying constraints still influence RTL design.

ASIC implementations often require RTL customizations. For example, Verilog lacks an explicit memory construct; users must use a register array. In modern technologies, SRAMs are provided by the fabrication company because large memories often contribute to a design's critical path, area, and power. RTL designers must rewrite their design to replace these register arrays with black-boxed SRAMs; this eliminates any future reuse that does not use this ASIC technology or performance envelope.

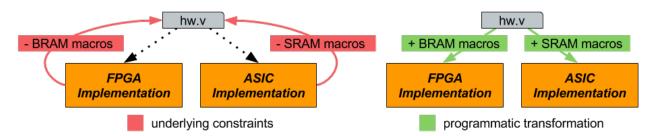

Figure 2.1: Underlying constraints for ASIC versus FPGA implementations means the same RTL cannot get good results on both platforms. This limits the reusability of any RTL design. To solve this problem, programmatic RTL transformations must take generic RTL and specialize it for a given platform.

FPGA implementations are no different; many FPGAs have hardened logic blocks to improve design quality. A designer can receive significant performance, power, or utilization advantages by modifying their RTL to be friendlier to a particular FPGA's synthesis tool. These changes, however, may be detrimental to an ASIC implementation or another FPGA implementation.

To solve this problem, some designers write a collection of custom scripts to do ad-hoc programmatic RTL modifications; these scripts are neither reusable, robust, nor composable.

Commercial CAD tools do not completely solve this problem either. While some do contain RTL-to-RTL transformations, CAD tools primarily focus on the separate problem of synthesis and place-and-route. Additionally, they are not organized in an open-source

## CHAPTER 2. AN ANALYSIS AND PROPOSAL FOR HARDWARE DESIGN METHODOLOGIES

compiler framework and are insufficient for custom flows that may have unsupported use cases.

One exception is Yosys[48], which is an open-source framework for Verilog RTL synthesis, and maps Verilog to ASIC standard cell libraries or Xilinx FPGAs. The main focus of Yosys is logic synthesis, not RTL to RTL transformations, and thus its internal design representation is very low level, and cannot represent higher-level constructs like aggregate types, width inference, and conditional assignment.

Separate from CAD tools, there exist stand-alone RTL modifiers, but many are closed source[6] and like commercial CAD tools cannot support custom flows. One exception is PyVerilog[42], which is an RTL-to-RTL modifier tailored specifically to Verilog. As such, it makes it difficult to act upon designer intent that is not directly represented in a Verilog construct. PyVerilog does not support SRAM inference or aggregate types, and these features would be very difficult to support given its internal circuit representation.

# 2.4 Hypothesis 3—Design collateral is necessary but not reusable

To obtain an ASIC implementation of a hardware design, its RTL must undergo many necessary and guided steps to obtain a tape-out-ready GDS. For example, one of these steps is place and route, the class of algorithms underlying physical design (physical realization of a logical design) which is generally considered to be NP-hard [40] [12]. As a result, designer intervention is often required to achieve high quality of results (QoR) within a reasonable timeframe. The dominant mode of designer intervention and interaction with CAD/EDA tools is through tool-specific TCL scripts which set constraints and run various physical design tasks in the tool. Place and route is one of many necessary-and-guided steps including standard cell synthesis, clock-tree synthesis, macro placement, IO cell selection and placement, and power strap specifications.

While existing CAD tools can perform all of these tasks, each step requires a significant amount of customization dependent on the following **orthogonal concerns**: the **logical design features** (SRAM size and number, signal fan-outs/fan-ins, bus bandwidths etc.), the **physical design features** (area constraints, shape constraints, desired frequency, floorplan) the **transistor technology** (restrictions on metal layers, SRAM macros and IO standard cells), and **CAD tools used** (specific placement directives, tool settings, flow structure).

Given the current status of interacting with EDA tools, the traditional approach towards "re-using" physical design effort is manual customization of tool vendor provided reference methodologies, essentially templates of physical design flow scripts e.g. To add a modicum of reuse, an approach is to use macro/string preprocessing, either within TCL itself or through other tools, to customize reference methodologies and generate tool scripts e.g. [35] [10] [14]. Macro/string preprocessing, however, has no awareness of the underlying physical design

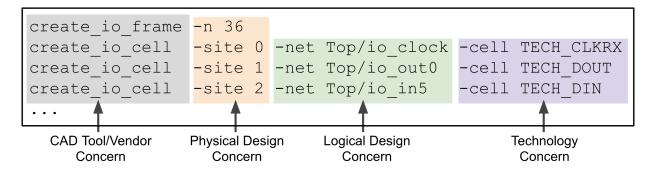

Figure 2.2: To create pad frames for an ASIC, the CAD tool expects to be told to create an IO frame. For each IO cell in the frame, one must use a tool-specific command to indicate its physical design-specific placement, its corresponding logical design-specific signal, and the technology-specific IO cell. Because this design collateral lacks any abstraction of concerns, these commands are impossible to reuse under technology, logical design, physical design, or CAD tool changes.

concepts; this approach gives rise to ad-hoc approaches which make it difficult to achieve safe programmatic re-use.

This lack of reusable design collateral is also present for both FPGA-implementations and efficient simulators. FPGA development requires many of the same steps as ASIC designs (synthesis, place and route) as well as requiring specific FPGA CAD tool directives in order to improve its clock frequency, LUT usage, and hard-block usage. Software simulators have an endless list of settings, flags, and debug features which improve debuggability, simulation speed, or both. Verification flows also require specific tools, commands, and other collateral in order to target the design (e.g. constrained-random criteria for improved coverage, or directives reducing the valid state-space for formal tools). All of this design collateral is heavily dependent on which tool or design used, regardless of function (e.g. feature-equivalent formal tools still employ unique API's which influence the associated design collateral).

Most manually created design collateral is contained within design tool scripts (see Figure 2.2). Because these scripts do not abstract these orthogonal **concerns**, changing one concern requires an entire rewrite of this design collateral (e.g. switching technologies, but preserving the tools, logical design and physical design). Figure 2.2 contains a snippet from the design collateral of a 28nm ASIC tapeout; every CAD tool command is directly dependent on every orthogonal concern, eliminating any reuse of this code if any one concern changes.

Design collateral is necessary for real products in ASIC, FPGA, simulator and verification flows. At the same time, it lacks abstraction and is manually written to a given design instance; this makes the design collateral non-reusable to changes in technology, design logic, physical design, or tools used.

# CHAPTER 2. AN ANALYSIS AND PROPOSAL FOR HARDWARE DESIGN METHODOLOGIES

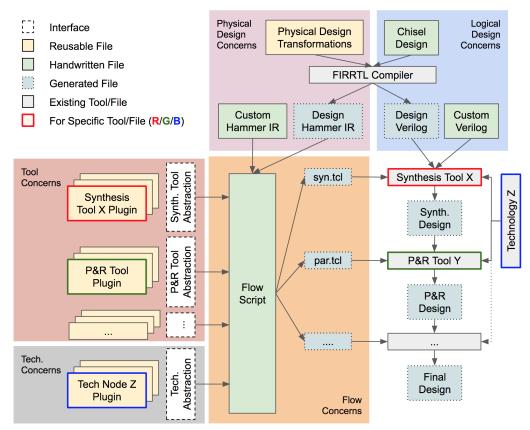

Figure 2.3: The overall architecture of the Hammer methodology showing the points of design entry, compilers/libraries, generated files/formats, and Hammer plugins, as well as the interactions between them.

### The Hammer Framework

To enable design collateral reuse, the Hammer framework is designed to develop abstractions for tool, technology, and physical design concerns; this enables writing design collateral that is only dependent on design features. Like how programming languages provide abstract classes as an implementation-agnostic interface (and thus make a program reusable across class implementations), Hammer provides an abstraction for these concerns. Hammer scripts are independent of physical design, technology, and tool concerns. This section is a brief overview of the main components of Hammer; see Figure 5.4 for a diagram of the components discussed below.

The Hammer IR is the primary standardized data exchange format of Hammer. The IR standardizes physical design constraints such as placement constraints and clock constraints. In addition, the Hammer IR also standardizes communication among and to Hammer plugins, including tool control (e.g. loading tools, etc.) and configuration options (e.g. number of CPUs). Users can generate Hammer IR directly from a logical design generator like

### CHAPTER 2. AN ANALYSIS AND PROPOSAL FOR HARDWARE DESIGN METHODOLOGIES

Chisel (e.g. retiming) by triggering a custom physical design transformation; these compiler transforms ingest annotations and emit the appropriate Hammer IR to implement the desired feature. Users can still explicitly pass physical design features by writing Hammer IR or writing a TCL hook.

The Hammer Tool Abstractions create a CAD-tool abstraction layer which consists of APIs for performing various physical design tasks, including synthesis and place and route. Different plugins implement the same interface for interoperability. To use Hammer tool plugins, physical design information and settings using the Hammer IR must be provided. Developers implement Hammer tool plugins as Python classes which consume Hammer IR and emit the appropriate TCL fragments to implement those features for a certain tool. TCL hooks allow expert users to bypass the abstraction by injecting TCL code directly into the generated flow, similar to how inline assembly allows injection of assembly into C.

The Hammer Technology Abstraction provides a standard data interchange format and corresponding Python library to encapsulate technology concerns. Hammer tool plugins are linked with a technology library so that they can perform actions involving technologies, like reading timing libraries or inserting filler cells. Creating a new technology plugin involves describing paths for components of the foundry-provided PDK, including standard cell libraries, timing databases, memories, layouts, and design rules. The interface can be bypassed by using TCL hooks to inject arbitrary TCL code that may include technologyspecific references/functions.

The Hammer Flow Driver, Hammer's interface for flow concerns (concerns about scheduling builds, build dependencies, tracking/managing build outputs, etc), orchestrates the ingestion of inputs/outputs and loads/calls tools, all via programmatic Python and JSON APIs. This allows users to build their own customized flow solutions using Hammer while decoupling build/flow concerns from the other four concerns, making it possible to use a variety of build tools (e.g. shell scripts, bazel, Make, SCons).

While Hammer scripts provide much of the reusability in ASIC flows, Hammer IR (Hammer's design collateral) is still heavily dependent on the design it is paired with. Manually writing Hammer IR to indicate a module's place-and-route floorplan will not work if the same module is later re-parameterized. *Design collateral must be generated in-sync with the generated design*. For this, another solution must be considered.

## Chapter 3

### Hardware Construction Languages

Expressive languages and programmatic customizations are a key component to enabling the development of reusable libraries. Previously, many influential works have introduced and expanded upon the concept of a hardware construction language, but this thesis revisits them in the sole context of providing a platform in which to develop hardware libraries. This chapter contains a discussion of hardware description languages through (1) an analysis of existing hardware description languages and their flaws, (2) an analysis of Chisel, a hardware construction language, as a primary tool for hardware libraries, and (3) an evaluation.

### 3.1 Limitations of Hardware Description Languages

As described in Chapter 2, hardware description languages like Verilog or VHDL were designed in the 1980s and have been slow to adopt modern programming improvements such as object-orientation, polymorphism, and higher-order functions. These features enable the use of good software engineering principles like abstraction, separation of concerns, and modularity; these ultimately encourage and enable more hardware design reuse. While SystemVerilog attempts to improve on existing HDLs by mixing in modern ideas like object-oriented programming with classic Verilog elements, the result is an extremely complicated language that is still missing other modern features like higher-order functions.

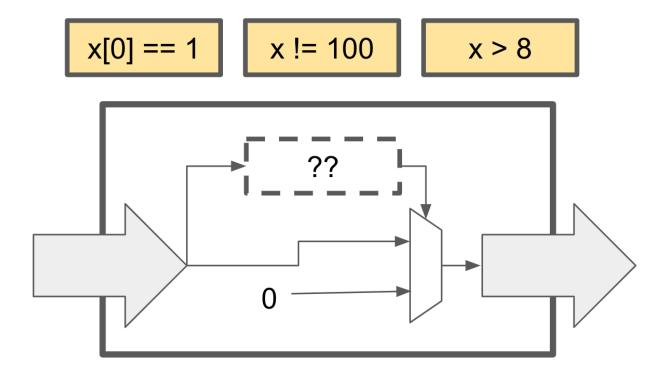

To illustrate this, consider a deeper dive into the example of a hardware module which filters incoming packets from a network (Figure 3.1). First, the module reads packets from the network; then, it checks if the packet violates its filtering condition. If true, the module writes the packet to the network. If false, it writes a zero'd packet to the network. There is one caveat however - the filtering condition depends on where the hardware module is instantiated.

Unfortunately, Verilog, VHDL, and SystemVerilog only support String, Integer, and Boolean parameters; our example requires a parameter that can generate the proper filtering condition hardware based on where the module is instantiated. Because these HDL's lack the capacity to express a higher-order parameter, the user cannot create this module

Figure 3.1: A module that filters packets by receiving them from a network, checking a filtering condition, and processing the packet accordingly. For different instantiations of this module, the filtering condition should be (1) 0th-bit is zero, (2) the signal is not 100, or (3) the signal is greater than 8. Because the design requires multiple of these filtering modules with unique filtering conditions, users cannot use an HDL because they lack these powerful parameters.

that is parameterized by the filtering condition; instead, a user must create separate modules for each separate filtering use case, even if the majority of the hardware block is reusable.

In industry, a common approach to address these types of examples is to write a custom program in a scripting language like Perl or Python which accepts these powerful parameters and generates a corresponding text file containing the corresponding HDL design. Unfortunately, this approach does not compose and requires special consideration within any build environment.

### 3.2 Hardware Construction Languages for Hardware Libraries

Hardware construction languages (HCLs) are a slightly different paradigm than HDLs for describing RTL circuits. Instead of expressing an RTL design directly, a user instead writes a program to construct the desired RTL design. Because HCL's require this programmatic approach, they are often created through embedding hardware construction capabilities in an existing programming language. Instead of being constrained to the limited generative capabilities of an HDL, designers have access to the rich control structures and abstractions of a general-purpose language, allowing modular, parameterizable, and reusable designs.

Chisel[3] is one of many embedded HCLs [15][38][43][30][39][5][29] and is hosted in Scala[34], a modern object-oriented and functional language.

Embedded HCLs, including Chisel, are software libraries with interfaces for constructing synthesizable RTL. For example, an object-oriented HCL might have classes representing registers and muxes:

```

// Represents synthesizable piece of hardware

abstract class HW {

// Emits corresponding HDL representation

def emit: String

}

class Register(name: String, width: Int)

extends HW { ...

def connect(r: HW) = ...

def emit = s"reg [${width-1}:0] $name;"

}

class Mux(cond: HW, ifTrue: HW, ifFalse: HW)

extends HW {...}

```

A designer can then create a register and hook it up by instantiating the **Register** object and calling its **connect** method:

```

class Top { ... // Start of program

val my_reg = new Register("my_reg", 32)

my_reg.connect(my_mux)

}

```

Language features like operator overloading can also cut verbosity:

```

class Top { ... // Start of program

// Equivalent to my_reg.connect(my_mux)

my_reg := my_mux

}

```

To generate the complete design, the user simply executes their HCL code; this process is called *elaboration*. Each HCL method call, including instantiations, builds up a data structure representing the hardware design instance. This design can then be emitted to an existing HDL.

Developing in a well-designed HCL can closely mimic the experience of writing in an HDL.

### **Enabling Hardware Libraries**

HCLs by themselves do not provide any new hardware abstractions. However, host language features allow designs to be more parameterizable and modular.

For example, Chisel users can write a recursive Scala function to construct an adderreduction tree, parameterized on bit-width. Unlike the explicitly unrolled version necessary in Verilog, the same generator could be re-used anywhere an adder tree is desired.

Similarly, a Chisel designer can write a filter module which takes, as a parameter, a higher-order-function that creates the condition-checking hardware. The user of this module then only needs to write the filtering condition, re-using the base filter structure.

Ultimately, the benefit of any HCL is the expressiveness provided by the host language; this opens the door for reusable hardware libraries.

### 3.3 Evaluating Chisel's Support for Hardware Libraries

An expressive language requires fewer lines of code to more fully parameterize a design. This parameterization enables reusing the same code in different contexts with different parameters, potentially generating radically different hardware.

The following evaluates Chisel with regards to its expressiveness, parameterizability, and ultimately its reusability.

#### Expressiveness

By using software engineering methods enabled by modern programming languages, one should expect fewer lines of code to express similar projects.

RocketChip[1] is an open-source hardware library, written in Chisel, that can generate many different instantiations of a symmetric multi-processor system (SMP). OpenPiton[4] is a research project, written primarily in Verilog and enhanced with some Python-Verilog generation scripts, that uses OpenSPARC cores with a custom interconnect and coherency framework.

OpenPiton and RocketChip have many similarities from 10,000 feet – both are SOC generators, containing cores, caches, network protocols, coherency domains, tests, and much more. Both are used for computer architecture research, have been realized in silicon, and boot Linux.

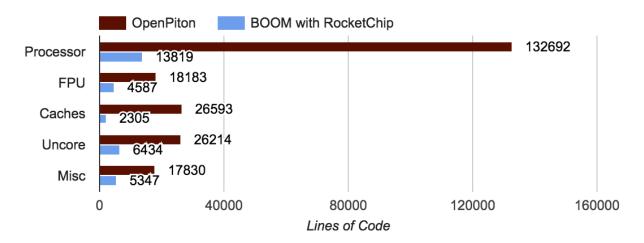

While clearly an apples-to-oranges comparison, Figure 3.2 depicts a comparison between the code bases. OpenPiton takes 3x and 10x more code to express similar hardware structures; the sheer magnitude of code size differences between OpenPiton and RocketChip cannot be explained solely by their differing feature sets. In addition, to the authors' knowledge, RocketChip's out-of-order core, BOOM[9], requires the fewest lines of code of any open-source out-of-order core implementation.

Figure 3.2: Similar hardware structures show significant differences in code size, ranging from between 3x to 10x. Because of their differing feature sets, this evaluation should not be taken as a strict comparison, but rather interpreted as a general trend that using Chisel enables a more expressive coding style.

While much of the OpenSPARC core was likely not entirely hand-written (tools like editor extensions could have been used), the comparison of language expressivity remains valid: Chisel is clearly more expressive than Verilog because RocketChip requires significantly less source code.

### Parameterizability

Parameterization precedes effective reusability - a flexibly parameterized module is more useful, and thus more reusable.

While it is difficult to quantitatively evaluate the flexibility, magnitude, and degree of parameterization that a general-purpose programming language provides an embedded HCL, the type and degree of RocketChip's parameterizability is described qualitatively:

- Out-of-order parameters: fetch width (1, 2, 4), issue width (1, 2, 3, 4), branch predictors (BTB, GShare, TAGE)

- **Data parallelism:** number of parallel data operations (4 through 32), precision (half, word, double)

- Multi-core: number of cores (1, 2, 4, 8, 16)

- Cache: size (64KB to 2MB), associativity (direct-mapped, two-way), type (scratch-pad, blocking, non-blocking), coherence policy (MSI, MESI)

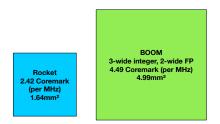

Note that the cross product of these parameters are all valid, and many (but not all) of these design points have been experimented with or even realized in silicon. Furthermore, many of these parameters are not simply bit-widths, but impact the control logic, interface definitions, and communication protocols. As shown in Figure 3.3, the different parameterizations can generate vastly different designs with very different microarchitectures, Coremark[17] performance results, and area numbers.

Figure 3.3: Two different configurations, a 3-issue out-of-order core and an in-order core, were pushed through the FIRRTL compiler framework and synthesized them with the Synopsis SAED educational standard cell library[19]. These designs are very different in their area footprint and Coremark performance; they are in fact very different processors generated using a large percentage of shared source code.

### Reusability

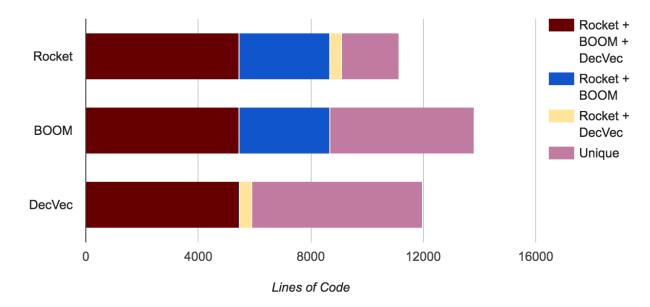

Three processors written in Chisel are analyzed next: (1) BOOM[9], RocketChip's out-oforder machine, (2) Rocket, a single-issue in-order core, and (3) DecVec, a decoupled vector co-processor, to understand whether parameterized designs foster reusability. As shown in Figure 3.4, approximately 5000 lines of code are shared with all three designs, and even more is shared between pairs of designs. In all, the three designs share half or more of their codebases with one another.

### 3.4 Summary

Hardware construction languages provide additional expressibility and parameterizability to hardware designers, greatly encouraging the development of reusable hardware libraries. While successful in their own right, HCL's lack the ability to fully separate their source code from underlying platforms or technologies. The next chapter discusses how a hardware compiler framework enables this separation, as well as providing additional capabilities to Chisel hardware libraries.

Figure 3.4: Three processors Rocket, BOOM and DecVec reuse each other's code. Modules used by all three designs include an ALU, a MulDiv unit, an ICache, a TLB, a Decoder, and an FPU. Modules used by Rocket and BOOM include a non-blocking data cache, a PTW, a CSR, and a BTB.

## Chapter 4

## FIRRTL: A Hardware Intermediate Representation and Compiler Framework

Like how software compilers transform general-purpose code into specialized assembly, a hardware compiler transforms general RTL into specialized RTL. The FIRRTL compiler enables this automatic transformation of a design, unlocking a huge amount of potential through optimizations and other generic transformations. This potential is best understood through two main features of the FIRRTL compiler framework: (1) its reusable transformations, and (2) its extensibility for customizations.

At first glance, writing an RTL transformation may seem like over-engineering; if a user wants to inline a module, why write an entire transformation when inlining manually is not very difficult? The key observation is that inlining is a common procedure required for most physical design implementations, and thus automation via transformation saves significant future manual effort. Indeed, writing a transformation only saves effort if its usecase is common enough that all future uses amortize the cost of the initial transformation development. This argument is similar to the argument in Chapter 1 for how reusable hardware libraries amortize their development costs over time. By making transformations easy to write and integrate within a compiler framework, the upfront development cost of a transformation is reduced and the number of worthwhile automatable tasks increases.

To motivate the need for an extendable hardware compiler infrastructure, consider the following example: a streaming digital-signal processing (DSP) hardware library. Every component in this library has a decoupled interface, where a queue of unknown size could be instantiated between each component. An unfortunate and unavoidable consequence of this library is that, if the queue size is zero, then the decoupled ready and valid signals between the components are vestigial yet form a combinational path. Ideally these signals would never be generated, but detecting this circumstance depends on knowing a neighbor's configuration; the local information available to a given library component generator is not sufficient.

Using an extendable hardware compiler framework enables this streaming DSP library to analyze the entire design topology and remove these vestigial combinational loops au-

## CHAPTER 4. FIRRTL: A HARDWARE INTERMEDIATE REPRESENTATION AND COMPILER FRAMEWORK 22

tomatically by writing and integrating their own custom transformation. Supporting this use-case requires the compiler framework to inspect and modify a design, be extendable for custom transformations, and support a robust mechanism for communicate information throughout the compilation process (e.g. which signals were generated by the library so other combinational paths remain untouched.)

This chapter contains a discussion of FIRRTL's hardware compiler framework (HCF) through the following topics: (1) analysis of LLVM, an existing software compiler framework; (2) introduction of FIRRTL's intermediate representation (IR); (3) description of value inference (e.g. widths) and its implementation; (4) support for arbitrary metadata throughout the compilation process; (5) the mechanisms for transforms to inspect and modify a design; (6) a description of interesting transformations; (7) an evaluation of the FIRRTL compiler framework.

### 4.1 Background

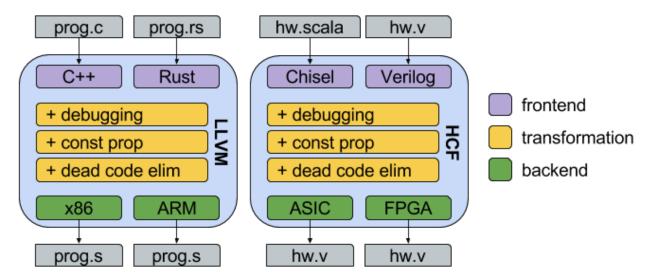

Modern software compiler frameworks, such as LLVM[27], consist of (1) frontends, (2) transformations, and (3) backends. A frontend parses programs written in a specific programming language (e.g. C++ or Rust) into a compiler-specific IR. IR-to-IR transformations such as optimization passes then can operate on and modify the program's structure. Finally, a backend converts the IR into a program in the target ISA, e.g. ARM or x86. This structure of translating an input language into an IR enables reusing transformations among multiple designs and languages.

Figure 4.1: LLVM can create a C++-to-x86 compiler or a Rust-to-ARM compiler, yet share internal transformations on LLVM-IR. Similarly, our HCF can create a Chisel-to-ASIC-Verilog compiler or Verilog-to-FPGA-Verilog compiler and share internal transformations.

### CHAPTER 4. FIRRTL: A HARDWARE INTERMEDIATE REPRESENTATION AND COMPILER FRAMEWORK 23

LLVM originated, like FIRRTL, as an academic project by Chris Lattner and advised by Vikram Adve in 2000 at the University of Illinois at Urbana-Champaign. Since these beginnings, the "compiler infrastructure project" has revolutionized compiler research by providing an open source, modular, and modern compiler.

The LLVM compiler has a modular design of many passes that operate on a common and well-defined intermediate representation (IR) of a program. This IR is independent of source program and target machine.

The LLVM's compiler infrastructure is composed of passes which operate in sequence on a program's IR. Each pass accepts a program's IR and returns a modified IR. They pipe together until the program is optimized, simplified, and instrumented.

Some passes require analyzing the program before modifying it, and many of these analyses can be shared among passes. However, other passes invalidate previously run analyses, which must be rerun. This presents an interesting challenge - how does the compiler know when to recompute analyses? Another challenge is pass dependency - some passes expect and require being run after other passes - how is this ordering done?

LLVM solves both of these challenges with a mechanism called pass scheduling and registration. As part of their interface, passes specify the following:

- any prerequisite passes (default is no other passes)

- any passes they invalidate/preserve (default is invalidating all other passes)

Note that references to prerequisite or invalidated passes is by name, which can be brittle to code modifications. Additionally, incorrect specification of prerequisites or invalidations can cause undetermined runtime behavior.

After passes are declared, they must be registered (either statically or dynamically) to a global *Pass Manager* with the following:

- Command-line option name

- Name of the pass

- Whether it walks and modifies the control-flow-graph

- Whether it is an analysis pass

LLVM has three pass categories: analysis passes, transform passes, and utility passes. Analysis passes compute information that other passes can use, and can be reused multiple times for multiple passes. Transform passes mutate the program in some way, and can use (or invalidate) analysis passes. Utility passes provide some utility that don't otherwise fit categorization, e.g. passes to extract functions to bitcode.

Each pass can take on one of a variety of traversal types. An *ImmutablePass* doesn't traverse the program but just reports statistics or other information. A *ModulePass* operates on the entire program and thus cannot optimize its execution. A *CallGraphSCCPass* traverses the program IR bottom up and can only access local information. Due to its traversal

behavior, it is possible to optimize its execution, but is tough to write one that is correct conceptually. A *FunctionPass* visits each function, independent of visiting other functions. This makes it easily parallelizable, conceptually simple, but has limited functionality. Finally, a *LoopPass* executes on each loop in the function, independent of all the other loops in the function.