## **UC Berkeley**

## **UC Berkeley Electronic Theses and Dissertations**

#### **Title**

Band-to-Band Tunnel Transistor Design and Modeling for Low Power Applications

#### **Permalink**

https://escholarship.org/uc/item/3b3328wb

#### **Author**

Jeon, Kanghoon

### **Publication Date**

2012

Peer reviewed|Thesis/dissertation

### Band-to-Band Tunnel Transistor Design and Modeling for Low Power Applications

By

### Kanghoon Jeon

A dissertation submitted in partial satisfaction of the

requirements for the degree of

**Doctor of Philosophy**

in

Engineering - Electrical Engineering and Computer Sciences

in the

**Graduate Division**

of the

University of California, Berkeley

Committee in charge:

Professor Chenming Hu, Chair Professor Tsu-Jae King Liu Professor Daryl C. Chrzan

Spring 2012

## Band-to-Band Tunnel Transistor Design and Modeling for Low Power Applications

Copyright © 2012

by

Kangoon Jeon

### **Abstract**

Band-to-Band Tunnel Transistor Design and Modeling for Low Power Applications

by

#### Kanghoon Jeon

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Chenming Hu, Chair

As the physical dimensions of the MOSFET have been scaling, the supply voltage has not scaled accordingly and thus the power density has been continuously increasing. This is mainly due to the fact that transistor operation requires carriers to go over the source side potential barrier which limits the subthreshold swing of a MOSFET to 60mV/dec at room temperature and thus inhibits the scaling of the threshold voltage. Tunneling devices utilizing the band-to-band tunneling mechanism have been known to overcome this fundamental limit.

In this thesis, the tunneling field-effect-transistor (TFET) is explored to replace conventional MOSFETs for low power applications. The band-to-band tunneling mechanism is looked into in order to develop a more accurate tunneling model that considers the change in effective mass during the transition between the conduction and valence band. Device simulator parameters are modified with this model and are used in designing the TFET. The silicon P-I-N structure TFET is studied through simulation and various experimental splits as a baseline for the TFET development. High tunneling currents are measured from a short channel device with a flash and spike anneal combination and a novel silicided source TFET using silicide induced dopant segregation is shown to achieve sub-60mV/dec subthreshold swing. Measurement and analysis methods of the transistor current and subthreshold swing to verify the TFET are discussed. Lower band gap Ge devices and Strained Si/Ge hetero-structure devices utilizing a lower effective bandgap are also explored to improve the performance of the TFET.

Dedicated to my family

# **Table of Contents**

| Acknowledgements                                     | vi |

|------------------------------------------------------|----|

| Chapter 1. Introduction                              | 1  |

| 1.1 Power Consumption Becoming a Major Concern       | 1  |

| 1.2 Possible Solution                                | 3  |

| 1.3 Thesis Outline                                   | 3  |

| 1.4 References                                       | 4  |

| Chapter 2. Modeling of Band-to-Band Tunneling        | 5  |

| 2.1 Introduction                                     | 5  |

| 2.2 Model Development                                | 5  |

| 2.3 Comparison to Simulation                         | 11 |

| 2.4 Summary                                          | 14 |

| 2.5 References                                       | 15 |

| Chapter 3. Silicon P-I-N Structure TFET              | 16 |

| 3.1 Introduction                                     | 16 |

| 3.2 Silicon P-I-N Structure TFET Process Flow Setup  | 18 |

| 3.3 Silicon P-I-N TFET Analysis                      | 22 |

| 3.4 Summary                                          | 25 |

| 3.5 References                                       | 26 |

| Chapter 4. Achieving sub-60mV/dec Subthreshold Swing | 27 |

| 4.1 Introduction                                     | 27 |

| 4.2 Silicided Source TFET Fabrication                | 28 |

| 4.3 Analysis of the Silicided Source TFET            | 30 |

| 4.4 Subthreshold Swing Data Quality Analysis         | 42 |

| 4.5 Selective Silicide Using Germanium               | 45 |

| 4.6 Summary                                          | 46 |

| 4.7 References                                       | 47 |

| Chapter 5. Improving the ON Current                               | 48 |

|-------------------------------------------------------------------|----|

| 5.1 Introduction                                                  | 48 |

| 5.2 P-I-N TFET with High I <sub>ON</sub> using Spike+Flash Anneal | 48 |

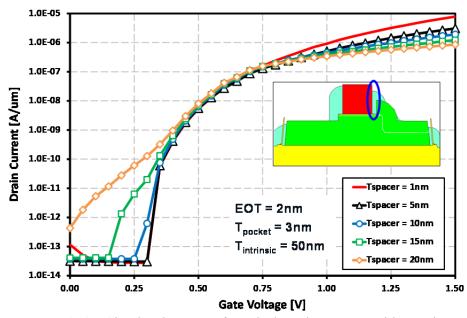

| 5.3 Undoped Vertical Pocket Structure TFET                        | 55 |

| 5.4 Summary                                                       | 61 |

| 5.5 References                                                    | 61 |

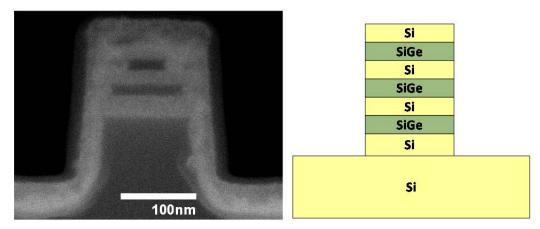

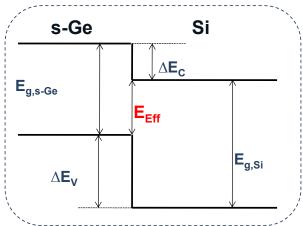

| Chapter 6. Si/Ge Hetero-structure TFETs                           | 63 |

| 6.1 Introduction                                                  | 63 |

| 6.2 Germanium P-I-N Structure TFET                                | 63 |

| 6.3 Si/Ge Hetero-structure TFET                                   | 65 |

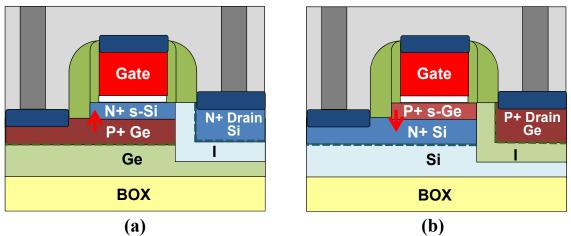

| 6.3.1 Germanium Source Hetero-tructure TFET                       | 65 |

| 6.3.2 Germanium Channel Hetero-structure TFET                     | 68 |

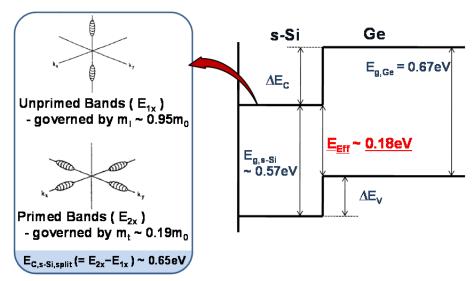

| 6.4 Si/Ge Strained Hetero-structure TFET                          | 70 |

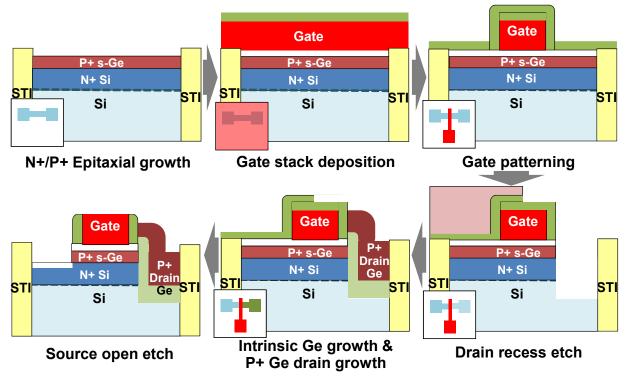

| 6.4.1 Vertical Pocket Strained Hetero-structure TFET              | 72 |

| 6.4.2 Lateral Strained Hetero-structure TFET                      | 74 |

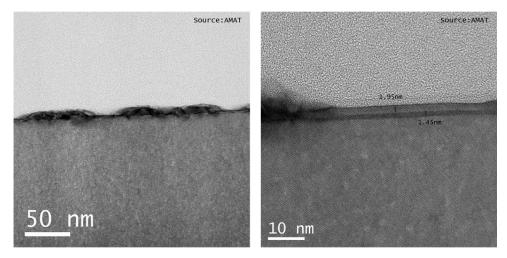

| 6.4.3 Strained Germanium Epitaxial Growth Experiments             | 76 |

| 6.5 Summary                                                       | 77 |

| 6.6 References                                                    | 78 |

| Chapter 7. Conclusions                                            | 79 |

| 7.1 Summary of Work                                               | 79 |

| 7.2 Future Directions                                             | 80 |

| 7.3 References                                                    | 82 |

## Acknowledgements

Firstly, I would like to express my sincere gratitude to my advisor Professor Chenming Hu for all his guidance, support and encouragement. I thank him for his unwavering energy, enthusiasm and interest in my work. It has led me to become a better engineer and researcher. I would also like to thank Professor Tsu-Jae King Liu for serving as the chair in my qualifying exam committee and for all her advice and valuable insight during our group meetings. I would like to thank Professor Daryl C. Chrzan for serving in both my qualifying exam committee and dissertation committee.

I would like to thank all the device group members for all their help and the wonderful experience. In particular I would like to thank Jemin Park and Changhwan Shin for being my closest friends. We started graduate school together and I thank them for their friendship and support throughout our years in Berkeley. I have been fortunate to have worked with great group-mates, Dr. Anupama Bowonder and Dr. Pratik Patel. I thank them for their support, help and friendship.

I would like to thank Dr. Wei-Yip Loh, Dr. Jungwoo Oh, Dr. Chang-Yong Kang, Dr. Casey Smith, Dr. Chanro Park, Dr. Byoung Gi Min, Dr. Prachant Mahji and Dr. Hsing-Huang Tseng for giving me the opportunity to fabricate TFETs at SEMATECH and for all their expertise, advice and help throughout the length of the project. I would like to thank Dr. Chorng-Ping Chang for allowing me the opportunity to experiment at Applied Materials and for all his advice.

I would like to thank the Korea Foundation for Advanced Studies (KFAS) for the financial support during my graduate studies and DARPA STEEP for funding and supporting this research.

Finally, I would like to thank my family for all their love, support and sacrifice. They have supported and encouraged me all throughout my life. I would not be here were it not for my parents and my brother. Lastly but most certainly not least, I would like to thank my lovely wife, Heejung Kim for her devoted love, support and companionship.

# Chapter 1

## Introduction

### 1.1 Power Consumption Becoming a Major Concern

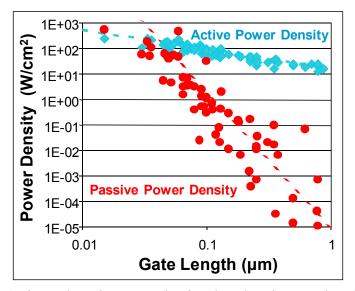

As the transistor has been scaling, the power consumption in modern microelectronic circuits have been continuously increasing. As can be seen in Figure 1.1 (a), the active as well as the passive power density is showing an continuous increase with scaling of the gate length. This is becoming a major concern in data centers due to cost increases in powering and cooling the servers. Mobile devices suffer from shorter battery life due to increased power consumption. In order to reduce the power density, the supply voltage has to scale in accordance to physical scaling dimensions which according to classical scaling rules keeps the power density constant.

**Figure 1.1** Active and passive power density plotted against gate length showing a continuous increase in power density [1.1]

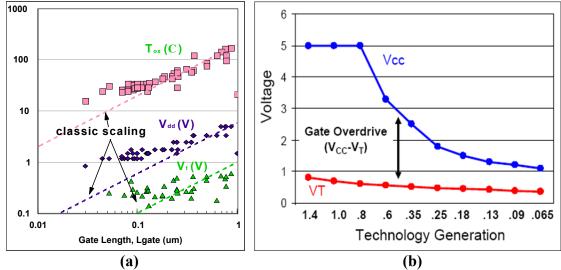

But as can be seen in the following figure, the supply voltage scaling has deviated from the classical scaling since 0.13µm technology generation and shows to be saturating at around 1V. This slowing down of supply voltage scaling has caused the continuous increase in power density.

**Figure 1.2** (a) Scaling of gate  $T_{OX}$ ,  $V_{dd}$  and  $V_t$  versus gate length shows deviation from classic scaling [1.1] (b)  $V_{CC}$  and  $V_T$  scaling trend versus technology generation shows a saturation in the voltage scaling [1.2]

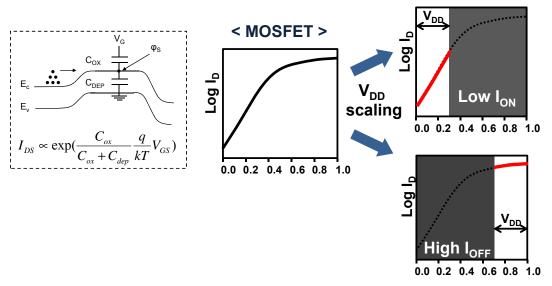

The MOSFET operates by having carriers travel over the source-side potential barrier. And since this is a thermal process, it is limited by kT/q which corresponds to a subthreshold swing of 60mV/dec. This limit in subthreshold swing has hindered the scaling of the threshold voltage as can be seen in Figure 1.2 and consequently the supply voltage. So in reducing the supply voltage of a MOSFET, a window must be chosen where one would sacrifice the  $I_{ON}$  and the other sacrificing  $I_{OFF}$  as shown in the following figure.

Figure 1.3 Operation of a MOSFET and supply voltage scaling scenarios

### 1.2 Possible Solution

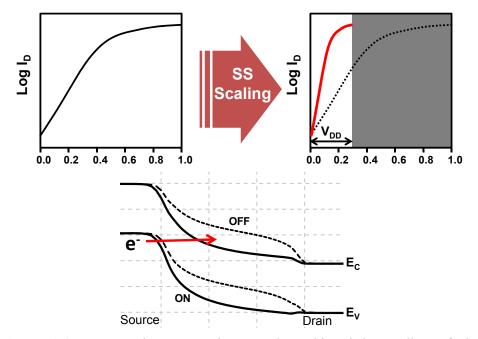

To achieve good ON/OFF performance at a lower supply voltage, we would have to find a way to scale down the subthreshold swing. That is, overcome the 60mV/dec limit in subthreshold swing of MOSFETs. In order to do this, a new current mechanism that does not involve carriers traveling over a potential barrier needs to be used. The band-to-band tunneling mechanism where electrons in the valence band travel through the barrier to the conduction band has been reported to be not subjected to this limit [1.3]. Tunneling Field-Effect Transistors (TFETs) have been explored by many researchers but have not been able to achieve a comparable performance to the conventional MOSFET [1.3~1.5]. More careful exploration into the structure and fabrication process design of the TFET is required for a low power alternative to the MOSFET.

**Figure 1.4** Low voltage operation can be achieved by scaling of the subthreshold swing (SS) with band-to-band tunneling

#### 1.3 Thesis Outline

The focus of this research is in exploring the band-to-band tunneling mechanism to be utilized as the main current mechanism of transistors in order to achieve the performance of MOSFETs at a much lower supply voltage with a less than 60mV/dec subthreshold swing. This will allow us to reduce the power consumption of electronic circuits by a considerable amount. In Chapter 2, the band-to-band tunneling model is examined to be applied to device simulation. Chapter 3 explores into the fabrication of TFETs with a baseline process flow development.

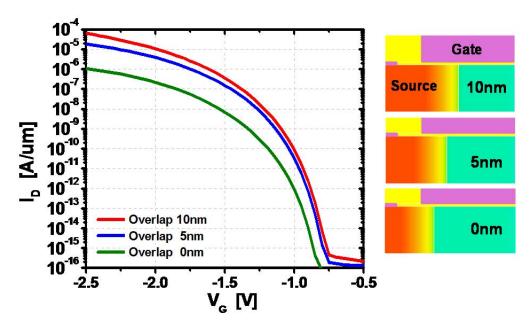

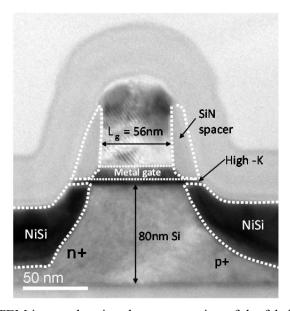

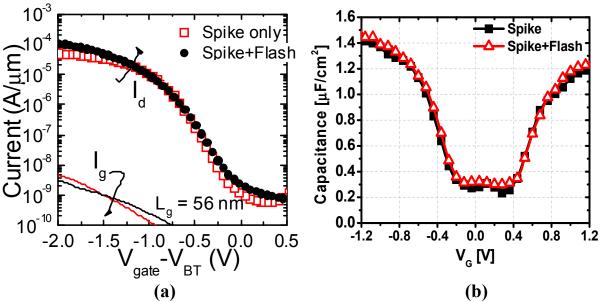

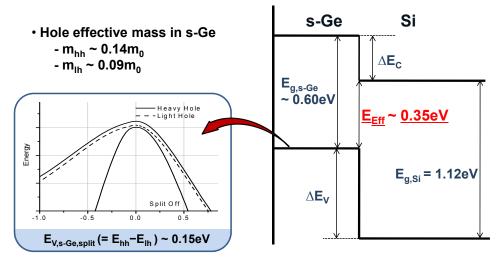

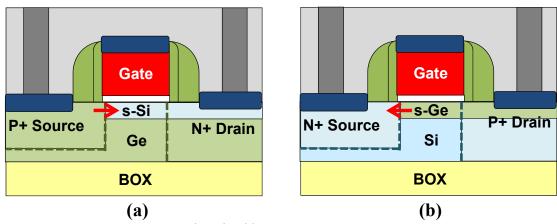

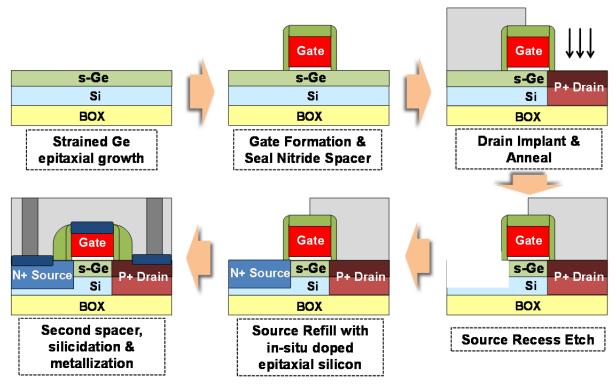

Electrical characterization of the TFETs is discussed as well. The subthreshold swing of the TFET is improved using silicidation induced dopant segregation and is dealt with in Chapter 4. Data screening criteria for TFET analysis are proposed [1.6]. In Chapter 5, we discuss structures to higher the drive current of TFETs and show improvements using increased gate-to-source overlap with spike+flash anneal combination [1.7~1.8]. Chapter 6 explores germanium TFET structures in homo- and hetero-structure configurations with silicon to better the performance. It is shown that biaxial strain between silicon and germanium will allow for a very low tunneling bandgap.

## 1.4 References

- [1.1] B. Meyerson, IBM, Semiconductor Conference, January 2004

- [1.2] Paul Packan, "Device and Circuit Interactions", *International Electron Devices Meeting* (IEDM) Short Course, 2007

- [1.3] W. Y. Choi, B.-K. Park, J. D. Lee, and T.-J. King Liu, "Tunneling Field-Effect Transistors (TFETs) With Subthreshold Swing (SS) Less Than 60 mV/dec", *IEEE Electron Device Letters*, vol. 28, no. 8, pp. 743-745, Aug. 2007

- [1.4] W. M. Reddick and G. A. Amaratunga, "Silicon surface tunnel transistor," *Applied Physics Letters*, vol. 67, no. 4, pp. 494-496, July 1995

- [1.5] C. Aydin, A. Zaslavsky, S. Luryi, S. Cristoloveanu, D. Mariolle, D. Fraboulet, S. Deleonibus, "Lateral interband tunneling transistor in silicon-on-insulator," Applied Physics Letters, vol. 84, no. 10, pp. 1780-1782, March 2004

- [1.6] K. Jeon, W.-Y. Loh, P. Patel, C.Y. Kang. J. Oh, A. Bowonder, C. Park, C.S. Park, C. Smith, P. Majhi, H.-H. Tseng, R. Jammy, T.-J.K. Liu, and Chenming Hu, "Si tunnel transistors with a novel silicided source and 46mV/dec swing," *VLSI Technology*, 2010 *Symposium on*, pp. 121-122, June 2010

- [1.7] W.-Y. Loh, K. Jeon, C. Y. Kang, J. Oh, P. Patel, C. Smith, J. Barnett, C. Park, T.-J. King Liu, H.-H. Tseng, P. Majhi, R. Jammy and C. Hu, "Sub-60nm Si Tunnel Field Effect Transistors with  $I_{ON} > 100 \mu A/\mu m$ ", *Proceedings of ESSDERC*, pp. 162-165, Sept. 2010

- [1.8] W.-Y. Loh, K. Jeon, C. Y. Kang, J. Oh, T.-J. King Liu, H.-H. Tseng, W. Xiong, P. Majhi, R. Jammy, and C. Hu, "Highly scaled ( $L_g \sim 56$ nm) gate-last Si tunnel field-effect transistors with  $I_{ON} > 100 \mu A/\mu m$ ", Solid-State Electronics, vol. 65–66, pp. 22-27, Nov.–Dec. 2011

# Chapter 2

# Modeling of Band-to-Band Tunneling

#### 2.1 Introduction

The band-to-band tunneling phenomenon which was first observed over 50 years ago in narrow bandgap germanium p-n junction diodes by Esaki [2.1], operates by having electrons travel through the forbidden bandgap and thus has been known to be able to overcome the 60mV/dec limit in subthreshold swing of conventional MOSFETs. This interband tunneling mechanism has been used in P-I-N structure TFETs and shown to have a steeper slope [2.2]. In spite of this steep slope, the on current of the TFET is much lower than conventional MOSFETs [2.3~2.4]. In order to achieve an increase in the on current a careful study of the tunneling mechanism is required.

In this chapter, the band-to-band tunneling mechanism is modeled and compared to that of the device simulator MEDICI. We start off with the form of Kane's tunneling model [2.5] where only one effective mass of the carrier is considered. It is expanded to consider the transition of the effective mass from the valence to the conduction band, inside the forbidden gap. Tunneling rates using this model is calculated for silicon and germanium then put into MEDICI for more exact silicon and germanium tunneling simulations. The dependence of the tunneling rate on effective masses is also studied.

### 2.2 Model Development

The exact form of the wave function throughout the band-to-band transition is required in order to calculate the tunneling probability accurately. Since the wave travels through the forbidden gap, the form of the wave vector inside the gap is required and inside the gap, the wave function undergoes a decay and is purely imaginary. This imaginary wave vector can be found if we consider the law of conservation of energy. If we assume there is no loss of energy

during the transition, the energy of the electron ending up in the conduction band should be equal to the sum of its energy at the start of tunneling in the valence band and the gained energy from the acceleration due to the electric field [2.6]. This is shown in the following equation,

$$\left(E_v - \frac{\hbar^2 k^2}{2m_v^*}\right) + qFx = E_c + \frac{\hbar^2 k^2}{2m_c^*}$$

(2.1)

where F denotes the electric field and  $m_c^*$  and  $m_v^*$  are valence and conduction band effective masses. Here we have assumed the momentum is conserved as well which means that there is no scattering involved. So this equation would not be exactly accurate for tunneling in indirect band-gap materials but for simplicity we do not consider the phonon interactions here. The indirect tunneling probability can be considered into the equation by adding a factor to the end of the equation for the phonon occupation number and probability of the scattering event. Another assumption that has been made in this equation is that the electric field is considered to be constant. Although in the actual case the field would not be constant throughout the transition, using the value of the average field agrees well with the path integral values [2.7].

Using (2.1) we can obtain the expression for the wave vector.

$$k = \frac{i}{\hbar} \sqrt{2m_r (E_g - qFx)}$$

(2.2)

where  $E_q = E_c - E_v$  and  $m_r$  is the reduce effective mass and is expressed as

$$\frac{1}{m_r} = \frac{1}{m_c^*} + \frac{1}{m_v^*} \tag{2.3}$$

Equation (2.2) works well within the energy conservation framework considered when deriving (2.1), but if we calculate the values of k throughout the transition from the valence band to conduction band, we can see that the equation has some flaws. Since the expression is purely imaginary it should reduce to zero at the band edges, that is at the beginning and end of the tunneling process in order to allow a smooth change in the wave vector. The imaginary wave vector does go to zero at the end of the tunneling process if we assume an average electric field which would be the band bending  $(E_g)$  divided by the distance. But at the beginning of tunneling (x = 0), the imaginary wave vector holds a large value. This cannot be true since the imaginary parts of the wave vector are zero in the valence band and this calls for a sudden jump in the imaginary wave vector, we consider a parabolic shape barrier for the band-to-band tunneling process.

$$k = i \frac{\sqrt{2m_r}}{\hbar} \sqrt{(qFx) \left(1 - \frac{qFx}{E_g}\right)}$$

(2.4)

The barrier which was triangular  $(E_g - qFx)$  in the previous equation is now parabolic  $(qFx)(1 - qFx/E_g)$  and reduces to zero at the beginning and end. The wave vector now shows a smooth transition at the band edges.

Equations (2.2) and (2.4) both consider the different effective masses in the conduction and valence band but during the transition, they lump the two masses into one reduced effective mass  $m_r$  and consider it constant throughout the whole tunneling process. This may not be an issue when the conduction and valence band effective masses are similar in value but when they differ substantially in value such as the case for InAs where  $m_c^* = 0.023m_0$  and  $m_v^* = 0.41m_0$  for heavy holes, the reduced effective mass will not model the transition accurately. Here  $m_0$  denotes the free electron mass. The tunneling electrons will behave more like electrons in the valence band when it is closer the valence band and like electrons in the conduction band when closer to the conduction band. So in order to model this transition of the effective masses, we use a linearly interpolated expression of the energies in each band as it transitions from the valence band to the conduction band [2.8].

$$\frac{\hbar^2 k_x^2}{2m_v^*} - \left(\frac{\hbar^2 k_x^2}{2m_v^*} - \frac{\hbar^2 k_x^2}{2m_c^*}\right) \frac{E}{E_g} + E_\perp = -E\left(1 - \frac{E}{E_g}\right)$$

(2.5)

Here, the direction of tunneling is chosen to be in the x direction, so  $k_x$  is used and the transverse energy is also added to consider the fact that not all the energy will contribute to the kinetic energy involved in the tunneling process and we assume the transverse energy is conserved. E denotes the energy gained from the electric field caused by the band bending which is qFx. Using this equation, the energy reduces to the energy in the valence band at the beginning of tunneling which only leaves  $m_v^*$  in the equation and to the energy in the conduction band at the end of tunneling leaving only  $m_c^*$ . This gives a more smooth and natural transition in the energies at the band edges. With this expression we can obtain a more accurate form of the wave vector inside the forbidden gap given as follows.

$$k_{x} = i \frac{\sqrt{2m_{v}^{*}}}{\hbar} \sqrt{\frac{E\left(1 - \frac{E}{E_{g}}\right) + E_{\perp}}{\left(1 - \left(1 - \frac{m_{v}^{*}}{m_{c}^{*}}\right) \frac{E}{E_{g}}\right)}}$$

(2.6)

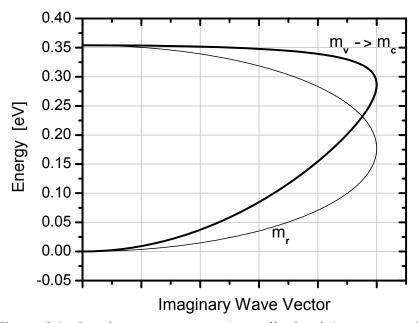

Figure 2.1 compares the imaginary wave vector of InAs using equation (2.4) and (2.6). It can be seen that when the transition between the masses are not considered, the wave vector shows a maximum at the exact center of the bandgap but with the transition considered, the maximum shifts towards the band with the smaller effective mass. This shows that the two effective masses have different contributions to the imaginary wave vector with the larger hole effective mass dominating in this case.

**Figure 2.1** Imaginary wave vector (normalized units) vs. energy inside the forbidden bandgap showing the asymmetric transition due to the large difference between the electron and hole effective masses

Now if we use the WKB (Wentzel-Kramers-Brillouin) approximation, we can calculate the tunneling probability. Here we assume a slowly varying potential compared to the wavelength of the electron. The tunneling probability is given as follows from the WKB approximation [2.9],

$$T \cong exp\left(2i\int_{x_1}^{x_2} k_x dx\right) \tag{2.7}$$

where  $x_1$  and  $x_2$  are the classical turning points representing the beginning and ending position of the band-to-band tunneling process. Here we can plug in the wave vector obtained in equation (2.6) to calculate the one dimensional tunneling probability.

$$T \cong exp\left(-2\int_{x_1}^{x_2} \frac{\sqrt{2m_v^*}}{\hbar} \sqrt{\frac{E\left(1 - \frac{E}{E_g}\right) + E_\perp}{\left(1 - \left(1 - \frac{m_v^*}{m_c^*}\right)\frac{E}{E_g}\right)}} dx\right)$$

(2.8)

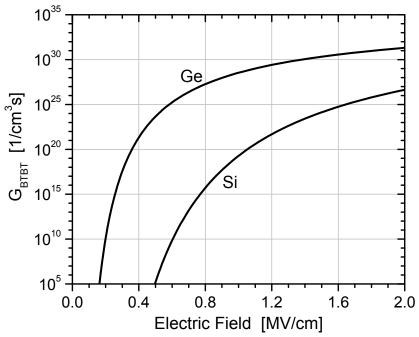

The transverse energy term is included to consider the energies in the other two dimensions which in the calculation of the tunneling probability increases the tunnel barrier and the probability quickly reduces to zero at large transverse energies. Due to this transverse energy term, an analytical form of the tunneling probability cannot be obtained and needs to be calculated numerically. Figure 2.2 shows the calculated Zener generation rate for silicon and germanium plotted against the average electric field.

**Figure 2.2** Calculated Zener generation rate is plotted against electric field for silicon and germanium. Higher tunneling rate is expected with a lower bandgap material at lower fields but lower bandgap material shows an earlier saturation.

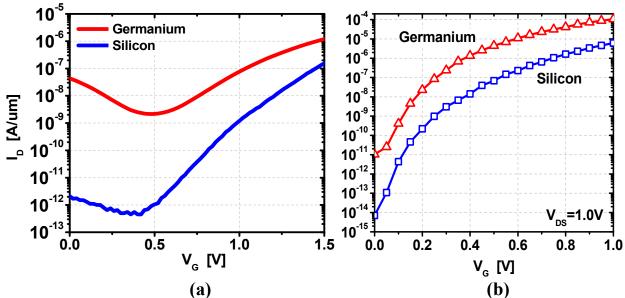

It can be seen that germanium with a lower bandgap, shows a larger Zener generation rate across the entire field range compared to silicon, especially in the low field regime. So in order to achieve high tunneling currents at low voltages, a lower bandgap material would be favorable. But a careful choice in the material is needed with the operation voltage and electric field in mind. For example, InAs with a direct bandgap of 0.36eV has a low density of states and thus shows to have a lower Zener generation rate at high fields compared to germanium with a bandgap of 0.66eV [2.10]. Therefore, depending on the operation voltage, germanium can be a more favorable material compared to InAs for TFETs.

Also in order to compare the performance of each material when used in a TFET, we need to compare the tunneling current for each material with equal tunneling distance. By integrating the tunneling probability and the velocity of the generated electrons in the whole momentum space, we can calculate the tunneling current.

$$J_{btbt} = q \iiint \frac{2}{h^3} |T|^2 v_x dp_x dp_y dp_z$$

(2.9)

Using the tunneling probability obtained in equation (2.8), we end up with the following tunneling current density equation.

$$J_{btbt} = \frac{4\pi q m_{v}^{*}}{h^{3}} (qV_{a}) \int exp \left( -2 \int_{0}^{d} \frac{\sqrt{2m_{v}^{*}}}{\hbar} \sqrt{\frac{(qFx)\left(1 - \frac{qFx}{E_{g}}\right) + E_{\perp}}{\left(1 - \left(1 - \frac{m_{v}^{*}}{m_{c}^{*}}\right) \frac{qFx}{E_{g}}\right)}} dx \right) dE_{\perp}$$

(2.10)

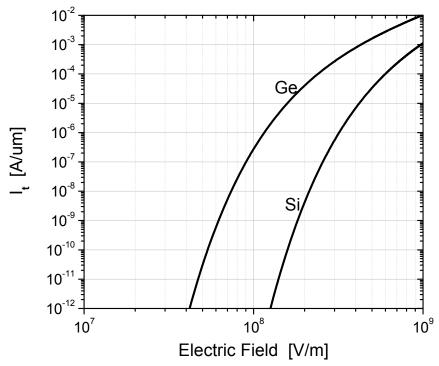

An analytic form of the double integral cannot be obtained as well since the transverse energy term is inside the exponent. The tunneling current is calculated numerically using Newton summation (Figure 2.3). The current was calculated for a tunneling width of 10nm.

**Figure 2.3** Tunneling current vs. electric field for silicon and germanium. The current was calculated for a tunneling width of 10nm.

Comparing with Figure 2.2, it can be seen that tunneling current does not increase in germanium as much as the Zener generation rate increases. This is due to the lower density of states in the lower bandgap material. The tunneling probability increases substantially but the resulting tunneling current is not increases as much due to the reduction in the number of carriers that can tunnel through the barrier, since the current is affected by the product of the two factors.

We can see that to achieve  $1mA/\mu m$ , it is practically impossible with silicon since it requires an electrical field of  $10^9$  V/m. This corresponds to a 1V drop in 1nm. But with germanium, we can obtain this amount of current at a more reasonable range of electric field of  $2\sim 3\times 10^8$  V/m by increasing the tunneling width to 20nm, since the tunneling current increases linearly with the tunneling width.

### 2.3 Comparison to Simulation

The model used in the device simulator MEDICI has the form of Kane's tunneling model. [2.11]

$$G_{BTBT} = A.BTBT \times \frac{F^{C.BTBT}}{E_a^{1/2}} \times exp\left(-B.BTBT \times \frac{E_g^{3/2}}{F}\right)$$

(2.11)

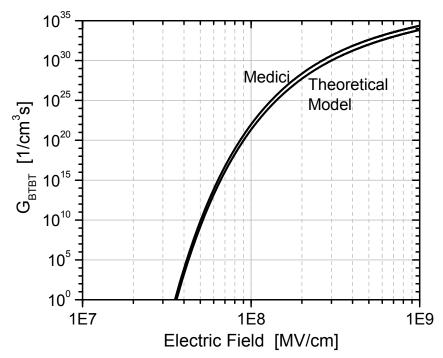

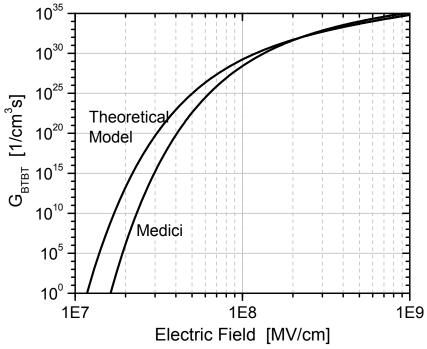

The parameters A.BTBT, B.BTBT and C.BTBT can be defined by the user. Only one set of default values are given which are  $3.5 \times 10^{21}$   $eV^{1/2}/cm \cdot s \cdot V^2$ ,  $22.5 \times 10^6$   $V/cm \cdot eV^{1/2}$  and 2.0 respectively. The Zener generation rate calculated with this model is plotted against the theoretically calculated rates for silicon in Figure 2.4.

**Figure 2.4** Zener generation rate model used by MEDICI and calculated values for silicon. The model agrees well with the calculated results for silicon

The tunneling rate at lower fields agrees fairly well with the theoretically calculated values but at electric fields of higher than  $10^8 V/m$ , MEDICI shows a higher tunneling probability. If we consider that the theoretical values were calculated for direct bandgap tunneling, the actual tunneling rate will be even lower than the calculated value.

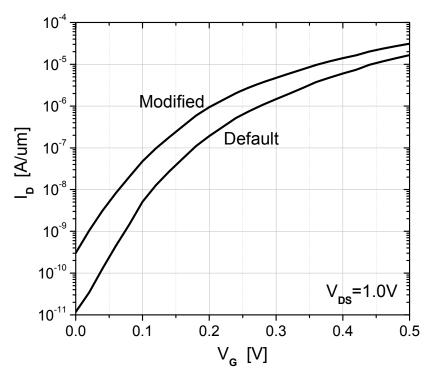

MEDICI's tunneling model given in (2.11) has a bandgap dependence term to be changed if different materials with different bandgaps are to be simulated. But the simulator only gives one set of parameter values and these values will not be correct since the tunneling characteristics are not only dependent on the bandgap. Figure 2.5 shows the tunneling rate of germanium calculated using the two models.

**Figure 2.5** Zener generation rate of germanium is plotted for the two models. There is a large difference in the lower field regions.

In the case of germanium a large difference in the rates can be observed in the lower field regions. At higher field values the two curves both saturate to similar tunneling rates but the theoretically calculated value shows orders of magnitude larger tunneling rates at fields below  $10^8 \ V/m$ . The tunneling parameters in MEDICI were changed to fit the calculated rate curve. They were found to be  $A.BTBT=9.5\times10^{20} eV^{1/2}/cm\cdot s\cdot V^2$ ,  $B.BTBT=16.7\times10^6 \ V/cm\cdot eV^{1/2}$  and C.BTBT=2.0. Using these new parameters, a p-i-n structure TFET structure with a p+ source and n+ drain was simulated. The drain current vs. gate bias for the case using the default parameters and that using the new parameters are plotted in Figure 2.6.

**Figure 2.6**  $I_D$  vs.  $V_G$  for a simple germanium p-i-n TFET structure. MEDICI shows lower tunneling currents in germanium.

As expected, the current obtained using new parameters show a higher on current. But due to the higher tunneling rate at lower fields, an increase in the off state current is also observed. It is shown that only the change of bandgap does not correctly model the tunneling characteristics.

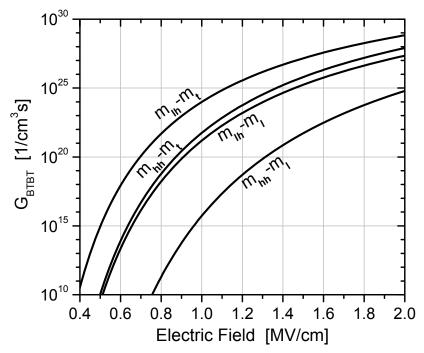

Since most of the tunneling occurs only one direction, in the lateral direction for p-i-n structure TFET's and vertically in pocket type structures, the tunneling electrons will only be subject to one kind of mass. That is, direction dependence in the effective mass also needs to be considered. In order to see how much the tunneling changes according to the directional masses, the tunneling probability from the heavy and light hole mass to longitudinal and transverse electron mass are calculated for each case.

The tunneling from the light hole to the transverse electron mass shows the highest rates since they are the smaller of the two. And accordingly the lowest generation rate is observed in the case of the heavy hole and longitudinal electron effective mass. The two rates differ by more than 10 orders in the lower field regions and approximately 4 orders at an electric field value of  $2 \times 10^8 \ V/m$ . The tunneling current can be increased a substantial amount by designing the device to have the dominant tunneling from the light hole in the direction of the traverse electron effective mass. This can be achieved by using strain to lift the light hole band above the heavy hole band to make the light hole tunneling to occur earlier than heavy holes. And the transverse mass dependency can be achieved by making the tunneling direction to be in the [100] crystal orientation direction for silicon.

**Figure 2.7** Zener generation rate from heavy and light hole mass to longitudinal and traverse effective mass

### 2.4 Summary

Band-to-band tunneling phenomenon was modeled considering the transition of the effective masses in the two bands. When this transition is not considered, the imaginary wave vector undergoes a parabolic shape change in the forbidden gap with the peak happening at the center of the forbidden bandgap regardless of the differences in effective masses. Whereas when the transition in the effective masses is considered, the peak is shifted towards the band with the heavier effective mass. The imaginary wave vector is calculated by using a linear interpolation of the energies as it transitions from the valence band to conduction band.

The band-to-band tunneling generation rate is calculated using this wave vector and compared to the tunneling parameters in MEDICI. Default silicon tunneling parameters show a good match to the calculated tunneling rate at low field regions but overestimate at high field regions. As for germanium, default parameters are the same as silicon except for the bandgap and thus give a much lower tunneling generation rate at lower fields compared to calculated values. Germanium TFET simulations are performed with modified tunneling parameters and are shown to be able to achieve higher tunneling currents than predicted using default parameters.

Effective mass dependent tunneling generation rate calculations show that by designing the TFET structure so that the tunneling occurs from the light hole band towards the direction where the transverse electron effective mass dominates, an increase in the tunneling current can be achieved.

### 2.5 References

- [2.1] L. Esaki, "New Phenomenon in Narrow Germanium p-n Junctions", *Physical Review*, vol. 109, pp. 603-604, 1958

- [2.2] W. Y. Choi, B.-K. Park, J. D. Lee, and T.-J. King Liu, "Tunneling Field-Effect Transistors (TFETs) With Subthreshold Swing (SS) Less Than 60 mV/dec", *IEEE Electron Device Letters*, vol. 28, no. 8, pp. 743-745, Aug. 2007

- [2.3] W. M. Reddick and G. A. Amaratunga, "Silicon surface tunnel transistor," *Applied Physics Letters*, vol. 67, no. 4, pp. 494-496, July 1995

- [2.4] C. Aydin, A. Zaslavsky, S. Luryi, S. Cristoloveanu, D. Mariolle, D. Fraboulet, S. Deleonibus, "Lateral interband tunneling transistor in silicon-on-insulator," *Applied Physics Letters*, vol. 84, no. 10, pp. 1780-1782, March 2004

- [2.5] E. O. Kane, "Theory of Tunneling," *Journal of Applied Physics*, vol. 32, no. 1, pp. 83-91, Jan. 1961

- [2.6] S. Wang, Fundamentals of Semiconductor Theory and Device Physics, pp. 481-492, Prentice Hall, New Jersey, 1989

- [2.7] P. Patel, "Steep Turn On/Off "Green" Tunnel Transistors," Ph.D. thesis, Department of Electrical Engineering and Computer Sciences, University of California at Berkeley, pp. 16, 2010

- [2.8] P. V. Dressendorfer, "Interface and Electron Tunneling Properties of Thin Oxides on Silicon," Ph.D. thesis, Department of Engineering and Applied Sciences, Yale University, pp. 235, 1978

- [2.9] D. J. Griffiths, Introduction to Quantum Mechanics, 2<sup>nd</sup> Edition, pp. 315-339, Prentice Hall, New Jersey, 2005

- [2.10] M.V. Fischetti, T.P. O'Regan, S. Narayanan, C. Sachs, J. Seonghoon, J. Kim, Y. Zhang, "Theoretical study of some physical aspects of electronic transport in nMOSFETs at the 10-nm gate-length," *IEEE Transactions on Electron Devices*, vol. 54, no. 9, pp. 2116-2136, Sept. 2007.

- [2.11] Taurus MEDICI User Manual, Version Y-2006.06, Synopsys, Mountain View, CA

# Chapter 3

## Silicon P-I-N Structure TFET

### 3.1 Introduction

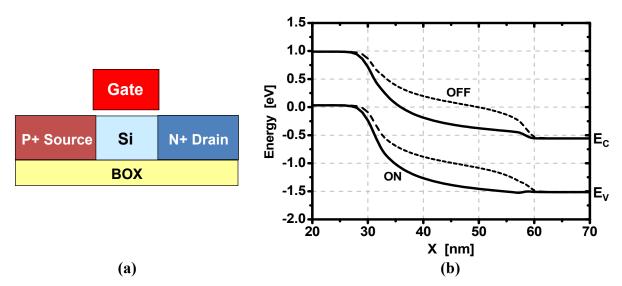

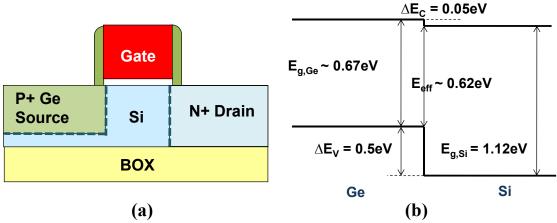

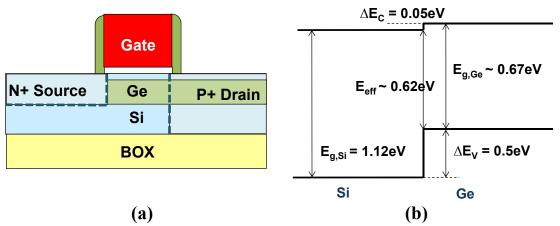

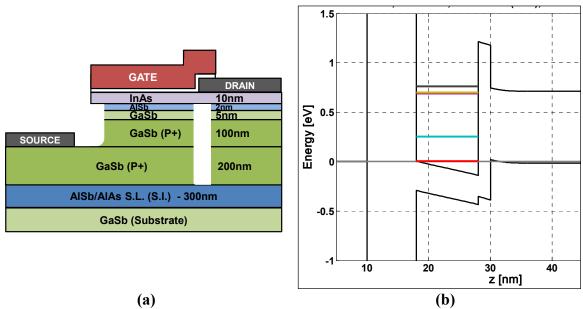

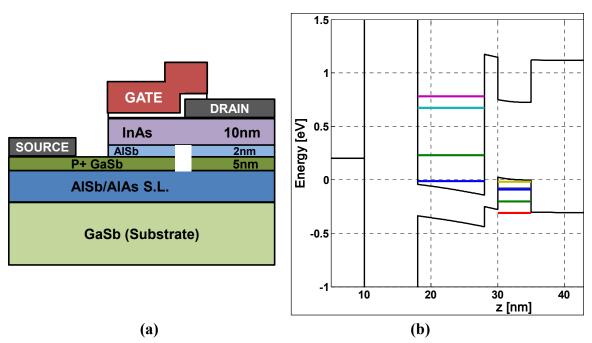

The simplest TFET is a gated P-I-N diode where the source and drain are highly doped with the gate controlling the band-to-band tunneling between the I-channel region and the P+ or N+ region by way of energy band bending in the I-channel region [3.1~3.5]. Figure 3.1 (a) shows an N-type P-I-N structure TFET. The gate induces an N+ channel to form at the surface of the I-channel region in this case and causes a P+/N+ junction to form at the source to channel interface. Figure 3.1 (b) shows the band diagram of the P-I-N structure TFET close to the surface.

**Figure 3.1 (a)** Illustration of a P-I-N structure TFET (N-type) **(b)** Band diagram of the P-I-N structure TFET close to the surface showing the ON and OFF state of the device.

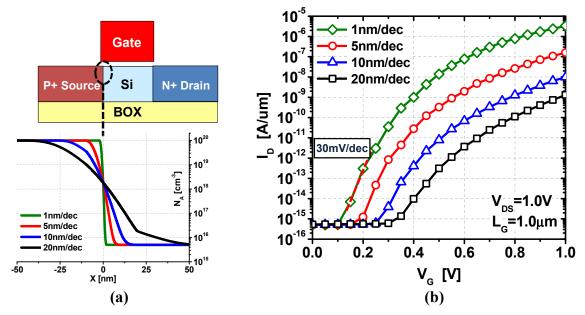

When the device is in the OFF state, the tunneling path for the electrons from the valence band of the source to the conduction band of the channel is cut off. As a positive gate bias is applied, the gate electric field pulls the band downward which causes the conduction band in the channel to overlap with the valence band of the source. When this overlap occurs the electrons in the valence band of the source are able to tunnel into the conduction band of the channel allowing a sudden increase in the drain current. And since the carriers are not flowing over a potential barrier the subthreshold swing is not subject to the 60mV/dec limit. But in order to achieve sub-60mV/dec, the tunnel barrier needs to be carefully designed. The thickness of the barrier that the electrons have to tunnel through corresponds to the integration range in the tunneling current equation derived in the previous chapter. And since the tunneling current is exponentially dependent on this integral, the output characteristics of the TFET can vary drastically depending on the design of the tunnel barrier. Figure 3.2 shows the simulation results of a 1.0µm channel length P-I-N silicon N-type TFET where the P+ source doping profile is varied using the device simulator MEDICI [3.6]. With the source doping gradient (lateral) changing from 1nm/dec to 20nm/dec, we can see in the I<sub>D</sub>-V<sub>G</sub> comparison that a large reduction in the tunneling current and degradation in the subthreshold swing. Also, it can be seen that in order to achieve a subthreshold swing of 30mV/dec, a 1nm/dec lateral source doping gradient is required.

**Figure 3.2** (a) Simulated P-I-N structure N-type TFET with varying source doping profile (b)  $I_D$ - $V_G$  curve of the P-I-N TFET showing a 1nm/dec source doping profile is required to achieve 30mV/dec subthreshold swing.

The fabrication of the P-I-N structure TFET is explored in this chapter. First we look into building a process flow for the P-I-N TFET. Process issues observed during the fabrication of the device are also mentioned and solutions to these process issues are given. Experimental results are given and various splits are compared in the analysis.

## 3.2 Silicon P-I-N Structure TFET Process Flow Setup

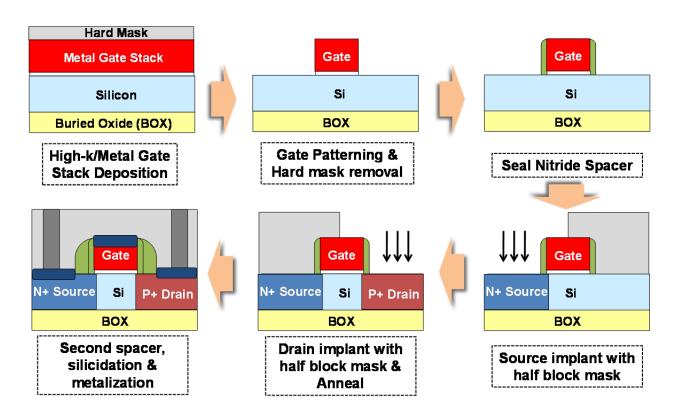

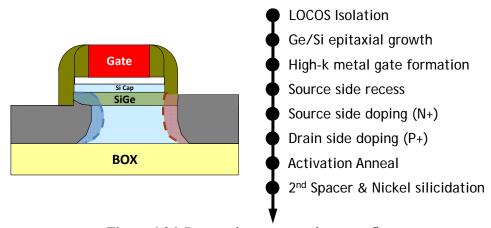

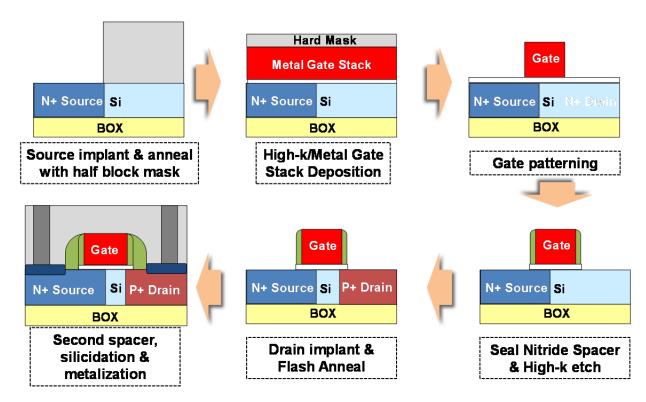

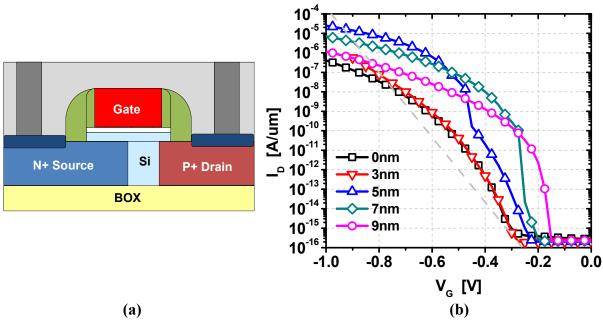

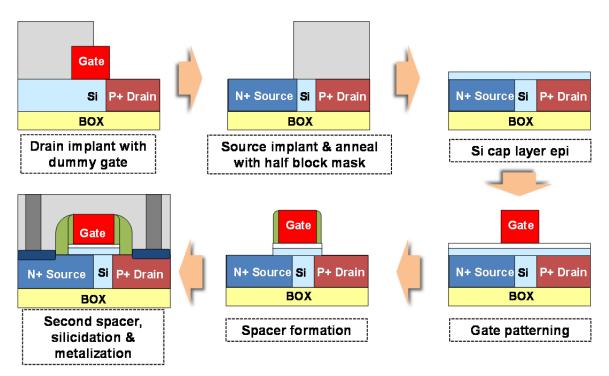

Since the P-I-N structure is the simplest TFET, this structure was chosen as the first experimental setup to study the TFET and be used as a baseline for subsequent structures to be fabricated. Due to the asymmetric nature of the P-I-N structure TFET, a self-aligned process similar to the process of a conventional MOSFET is not possible and the source and drain have to be formed separately. The P-I-N TFET process flow is developed using SOI wafers based on Sematech's CMOS process flow using a high-k metal gate process. The process flow is shown in the following figure.

Figure 3.3 P-I-N structure TFET process flow using CMOS mask set

First the SOI wafers were thinned down to 80nm and 40nm using thermal oxidation. Different thicknesses were chosen to see the effect of the SOI thickness to the TFET performance. Mesa isolation was chosen as the method for isolation and active region formation due to its simplicity and less number of steps compared to shallow trench isolation. Then the high-k gate stack is deposited with a mid-gap work function metal and poly-silicon as the gate. After the gate is patterned, a seal nitride spacer is formed to protect the sidewalls of the gate followed by source/drain implant. The source and drain are implanted using a half mask that is compatible with the CMOS mask set and implant conditions were chosen to that the source/drain junction will reach the bottom of the SOI substrate to reduce the junction area and thus limit the amount of junction leakage. This reduces the source/drain junction leakage by more than 2

orders of magnitude. Implant energy and dose splits were included as splits and the effect on the subthreshold swing were examined and will be discussed in the next section. Annealing of the dopants was done using spike anneal at 1050°C for 2 seconds or 5 seconds. Millisecond flash anneal was used as well in some splits. Finally after a second spacer is formed, self-aligned silicide process is done with nickel followed by metallization to M1 layer. Some lots were processed up to silicide without metallization and measured for a quicker turn around.

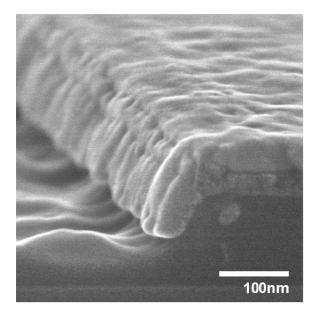

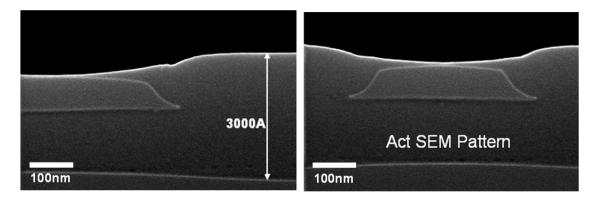

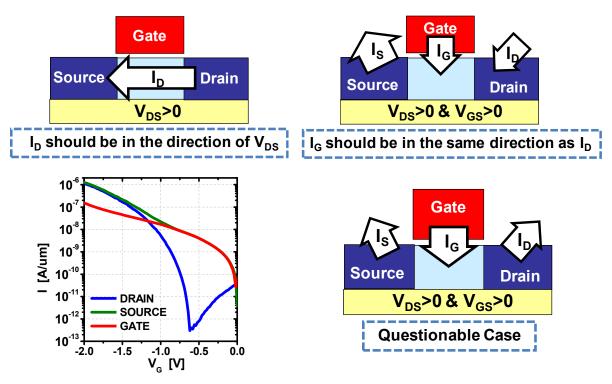

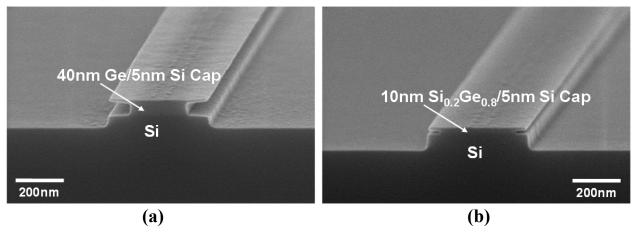

When mesa isolation is used for active definition on SOI wafers eliminating gate material stringers on the sidewalls of the mesa is an issue. This causes high gate leakage currents due to the increased overlap of the gate to source and drain regions. Also, the exposed regions of the gate dielectric on the sidewalls of the mesa get attacked during the subsequent cleans and implant making the dielectric weaker. And in some cases the poly gate stringer shorts with the source/drain region during silicide process. This phenomenon was observed in the first few lots that were fabricated using mesa isolation. Cross-section SEM images at the edge of active regions showing gate stack material stringers formed on the sidewalls are given in Figure 3.4. High gate currents were measured which caused the analysis of the tunneling current to be difficult. In some cases, we cannot tell whether the drain current is coming from the band-to-band tunneling or from the gate leakage. And when extremely high gate leakages are observed, the drain current showed to be flowing in the opposite direction of the drain bias which shows all the drain current is coming from the gate. Analysis and screening criteria of the tunneling current when gate currents are present are discussed in detail in Chapter 4.

**Figure 3.4** Cross-section SEM images showing gate material stringers formed on the sidewalls of the active regions.

In order to prevent from this happening in subsequent lots, the isolation method had to be changed. First shallow trench isolation that is used as a baseline in bulk wafers were considered

but this would require some process module development for it to be applied to SOI wafers and also increase the number of process steps in the isolation to be more than double of that required for the mesa isolation. Deliberately placing sidewall spacers on the active mesa using nitride or oxide was also considered but was not chosen due to the increase in number of steps.

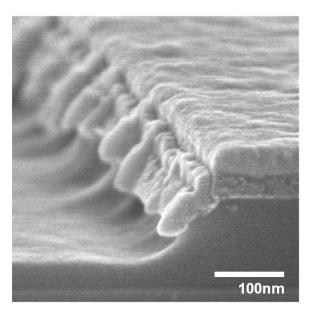

The solution chosen to eliminate this problem was LOCOS (LOCal Oxidation of Silicon). Using the LOCOS process, no process development was required and the increase in number of steps for the isolation was minimal. With the active etch changed to stop on silicon, only a thermal oxidation step was needed to be added to the process flow. A thermal oxide of 1000Å and 2000Å were grown for 40nm and 80nm of substrate thicknesses respectively. Figure 3.5 shows the cross-section SEM images of the active SEM patterns after the LOCOS isolation process. The LOCOS causes the width of the transistor to be reduced by a few 100nm which will have to be considered in small width devices. Also, the gate dielectric thickness increases at the active edges in the width direction due to the bird's beak of the LOCOS. But this actually helps in the operation of the TFET by eliminating early turn-on of the device at the edges from electric field concentration at the corner regions which would cause the subthreshold swing of the TFET to be less sharp.

**Figure 3.5** Cross-section SEM images of active region after LOCOS isolation process

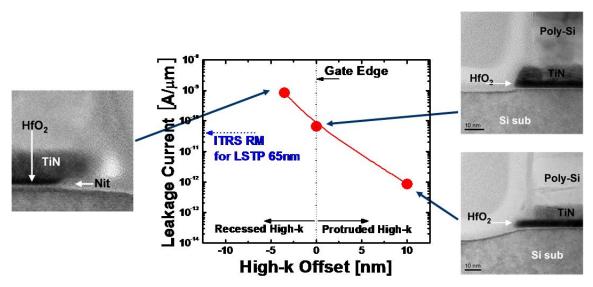

In addition to the LOCOS isolation, the gate stack etch process was changed to reduce the gate leakage even further. Kang showed that when the high-k gate dielectric is etched after a spacer is formed leaving a protruded high-k region under the gate metal and polysilicon, the gate leakage current can be reduced by reducing the edge leakage [3.7]. As shown in Figure 3.6, the gate leakage increases when recessed and decreases when protruding from the gate edge. The gate leakage shows to have an exponential dependence on the offset amount of the high-k gate dielectric to the gate edge at a ratio of approximately 1 decade per 5nm of high-k offset.

The process flow of the P-I-N TFET is changed so that during the gate patterning, only the gate polysilicon and metal are etched and leaving the high-k dielectric intact. Then the gate dielectric is etched after a seal nitride spacer is patterned to form a protruding high-k region. This reduces the amount of dielectric damage at the gate edge during the high dose source/drain implants.

Figure 3.6 Effects of gate edge profile on OFF state leakage [3.7]

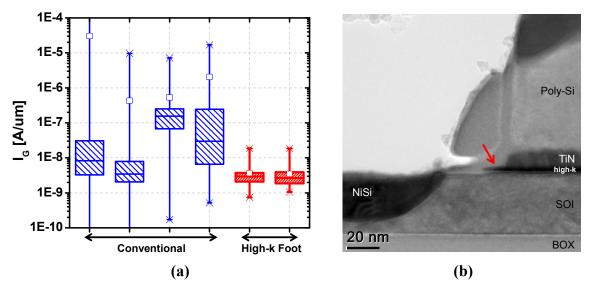

The patterned gate stack of a P-I-N TFET is shown in Figure 3.7 (b). As can be seen in the gate leakage comparison of Figure 3.7 (a), the mean gate leakage value shown as white squares was measured to decrease by at least 2 orders of magnitude. Also, the variation in the gate leakage was reduces substantially by using the high-k foot process.

**Figure 3.7** (a) Gate leakage current comparison between P-I-N TFET wafers with and without the protruding high-k foot process (b) TEM image showing the protruding high-k foot under the metal and polysilicon gate.

With the reduced gate leakage and improved gate leakage uniformity using the LOCOS isolation and modified high-k etch process this process was chosen as the baseline for the P-I-N TFET process flow.

### 3.3 Silicon P-I-N TFET Analysis

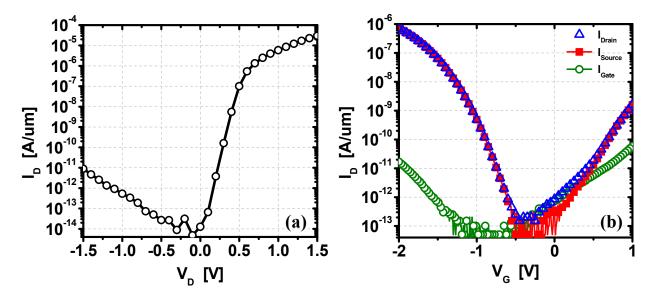

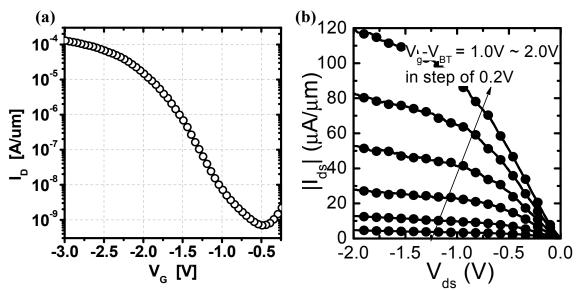

In this section the P-I-N measurement and analysis methods are discussed where various process splits are compared. Due to the non-self-aligned nature of the process flow of the P-I-N TFET, the first thing that needs to be checked is whether the half mask for the source and drain implants aligned correctly and formed a P-I-N diode. So, we measure the I-V characteristic between the source and drain with the gate open. Diode measurement for a 0.5µm channel length device with SOI thickness of 40nm is shown in Figure 3.8 (a). As you can see, with the N+ source grounded and P+ drain biased, a rectifying behavior can be observed and the slope of the diode I-V curve in the forward bias region is close to 60mV/dec showing a well behaved diode. If a misalignment occurs we would end up with the either N+ or P+ implanting both the source and drain and end up with an NMOS or PMOS. With this diode measurement we can verify that the half mask did not misalign and form a MOSFET accidently. We can also see the current ranges where the device will be limited by series resistance. From this measurements we see that current levels above 1µA/µm would be limited by the series resistance coming from the undoped channel and source/drain contacts. Another characteristic of this P-I-N TFET that we can obtain from the diode measurements would be the OFF state current of this device. By looking at the reverse bias measurement we can tell what OFF current levels to expect on an I<sub>D</sub>-V<sub>G</sub> measurement for the corresponding drain bias. Since steep subthreshold behavior in these tunneling devices usually occurs at low current ranges, especially in silicon [3.8, 3.9], we want the reverse bias current levels to be as low as possible for the intended operation voltage. Steep turn-on/turn-off behavior is generally not observed when these levels are high.

**Figure 3.8 (a)** P-I-N structure TFET diode measurement of a  $L_G$ =0.5 $\mu$ m device with gate open showing rectifying behavior **(b)** P-I-N TFET  $I_D$ - $V_G$  measurement (PFET) with  $V_D$  (P+) = -1V,  $T_{SOI}$ =40nm showing SS=128mV/dec

With the confirmation of a P-I-N structure formation, we next measure the  $I_D$ - $V_G$  characteristics to see the TFET performance. Figure 3.8 (b) shows the PFET  $I_D$ - $V_G$  characteristics of the same device with a drain (P+) bias of -1V. The source and gate currents are also measured to check that the current being measured is band-to-band tunneling current and not gate leakage current. We can see that even though the gate leakage is fairly low, it is comparable to the drain current between -0.5V and 0V and in this range the drain current is actually coming from the gate. So when measuring the subthreshold swing we should avoid measuring in these ranges. By plotting all three currents we can tell the source of the current. When the drain current is equal to the source current we know that it is tunneling current that is being measured. We also observe that due to the different lateral straggle of the implant species, the PFET shows a better performance compared to that of the NFET.

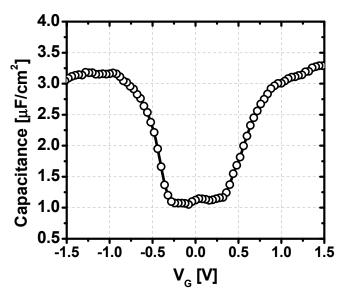

$30\text{\AA}$  HfO<sub>2</sub> high-k was used as the gate dielectric with a mid-gap workfunction gate metal. We can see that with the mid-gap workfunction gate metal, the turn-on of the device occurs around -0.5V which corresponds to approximately half the bandgap of silicon. C-V measurement of the P-I-N TFET can be easily measured in one measurement due to the fact that the source and drain provide the source for holes and electrons. C-V measurements of a  $20\mu m$  gate length and  $10\mu m$  wide P-I-N TFET is shown in Figure 3.9. The HfO<sub>2</sub> dielectric used in this device shows to give an equivalent oxide thickness of  $\sim 0.9 nm$ .

**Figure 3.9** C-V measurement of a 20 $\mu$ m gate length and 10 $\mu$ m width P-I-N TFET showing an EOT of ~0.9nm

The ON current for an overdrive ( $V_G$ - $V_T$ ) of 1.5V was measured to be  $7\times10^{-7}$ A/ $\mu$ m. The subthreshold swing of this device does not show a sub-60mV/dec behavior and is measured to be 128mV/dec. In order to see the effect of the implant conditions, different implant conditions were included as splits in a 80nm SOI lot and the minimum subthreshold swing in each case is given in Table 3.1. All devices were annealed using spike anneal at 1050°C for 5 seconds.

| Implant Condition  | Slope        |

|--------------------|--------------|

| BF2 / 15keV / 2E15 | 85.2 mV/dec  |

| BF2 / 18keV / 3e15 | 105.2 mV/dec |

| As / 55keV / 3E15  | 80.0 mV/dec  |

| As / 85keV / 2E15  | 147.4 mV/dec |

**Table 3.1** BF2 and As implant conditions splits and their measured minimum subthreshold swing values 80nm thick SOI devices.

As can be seen in the above table, higher energies resulted in larger swing values due to the larger lateral straggle. And PFET devices with As as the source dopant shows a steeper swing compared to the NFET with BF<sub>2</sub>. All the above conditions and experimental lots with a low 10 keV As implant did not show sub-60 mV/dec subthreshold swing. From these experimental results we can see that the abrupt lateral doping profile that is required for a sub-60 mV/dec subthreshold swing shown in Figure 3.2 is difficult to achieve using conventional ion implantation and anneal techniques.

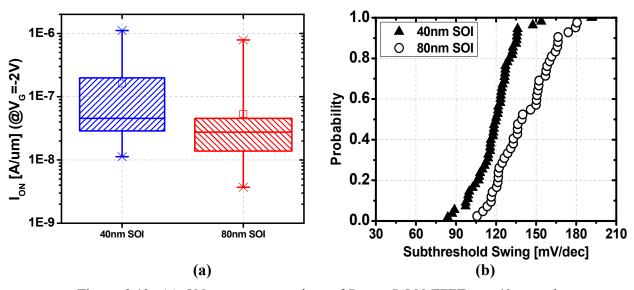

SOI thickness splits were also included and are compared in Figure 3.10. Both devices were fabricated with same implant and anneal conditions. We see that the thinner 40nm SOI devices a higher ON current and better subthreshold swing distribution. This shows that the thinner SOI devices have a better gate control of the tunneling current.

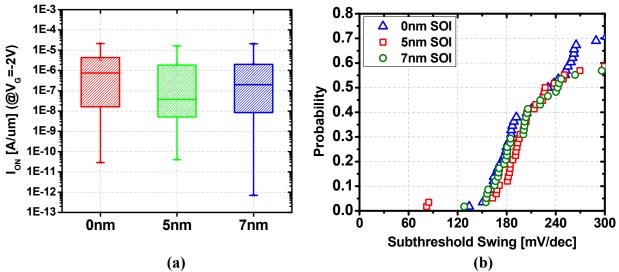

**Figure 3.10** (a) ON current comparison of P-type P-I-N TFETs on 40nm and 80nm SOI at  $V_G$ =-2V (b) Subthreshold swing distribution comparison

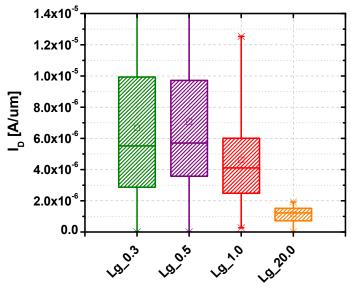

Although the current of a TFET is generated by band-to-band generation at the source, the generated electrons or holes have to flow through the channel to the drain just like a MOSFET. So, a similar gate length dependence of the device current is expected in a P-I-N TFET. As can be seen in the following figure, the mean value of the ON current (open squares) is shown to decrease with longer gate lengths. This shows that TFET performance can be improved with physical scaling of the device dimensions.

Figure 3.11 ON current versus gate length of P-type P-I-N TFETs at  $V_G$ =-2V

### 3.4 Summary

A baseline fabrication process flow for the silicon P-I-N structure TFET on SOI wafers was developed. Issues concerning gate stringers due to mesa isolation technique were overcome through LOCOS isolation developed for SOI wafers. The gate etch process is modified by forming a high-k foot in order to reduce the gate leakage caused by damages to the gate dielectric edge during gate etch, subsequent cleans and ion implantation process. It is shown that the gate leakage can be reduced by a considerable amount with improved uniformity by using this process.

When measuring these P-I-N structure TFETs, the diode behavior between the source and drain should always be measured to confirm the alignment of the source/drain implant half mask. All terminal current should be examined when measuring the I<sub>D</sub>-V<sub>G</sub> characteristics to measure real tunneling current. C-V behavior can be measured easily due to the structure having reservoirs for both electrons and holes. It is shown through simulation that a very abrupt lateral profile is required to achieve sub-60mV/dec subthreshold swing. Experimental results show the degradation in subthreshold swing with higher energy implant due to increased lateral straggle. SOI thickness dependence studies show a thinner SOI is preferred for better gate control resulting in lower subthreshold swing and higher drive current.

TFET ON current is measured to have similar gate length dependence seen in a MOSFET and will benefit from physical scaling of the device dimensions.

### 3.5 References

- [3.1] W. M. Reddick and G. A. Amaratunga, "Silicon surface tunnel transistor," *Applied Physics Letters*, vol. 67, no. 4, pp. 494-496, July 1995

- [3.2] C. Aydin, A. Zaslavsky, S. Luryi, S. Cristoloveanu, D. Mariolle, D. Fraboulet, S. Deleonibus, "Lateral interband tunneling transistor in silicon-on-insulator," *Applied Physics Letters*, vol. 84, no. 10, pp. 1780-1782, March 2004

- [3.3] K. K. Bhuwalka, M. Born, M. Schindler, M. Schmidt, T. Sulima and I. Eisele, "P-channel tunnel field-effect transistors down to Sub-50 nm channel lengths", *Japanese Journal of Applied Physics*, 45, pp. 3106-3109, 2006

- [3.4] W.-Y. Loh, K. Jeon, C. Y. Kang, J. Oh, P. Patel, C. Smith, J. Barnett, C. Park, T.-J. King Liu, H.-H. Tseng, P. Majhi, R. Jammy and C. Hu, "Sub-60nm Si Tunnel Field Effect Transistors with  $I_{ON} > 100 \mu A/\mu m$ ", *Proceedings of ESSDERC*, pp. 162-165, Sept. 2010

- [3.5] W.-Y. Loh, K. Jeon, C. Y. Kang, J. Oh, T.-J. King Liu, H.-H. Tseng, W. Xiong, P. Majhi, R. Jammy, and C. Hu, "Highly scaled ( $L_g \sim 56$ nm) gate-last Si tunnel field-effect transistors with  $I_{ON} > 100 \mu A/\mu m$ ", Solid-State Electronics, vol. 65–66, pp. 22-27, Nov.–Dec. 2011,

- [3.6] Taurus MEDICI User Manual, Version A-2007.12, Synopsys, Mountain View, CA

- [3.7] C. Y. Kang, R. Choi, S. H. Bae, S. C. Song, M. M. Hussain, C. Yong, D. Heh, G. Bersuker, and B. H. Lee, "Effects of Optimization of Gate Edge Profile on Sub-45 nm Metal Gate High-k Dielectric Metal Oxide Semiconductor Field Effect Transistors Characteristics", SSDM 2006

- [3.8] W. Y. Choi, B.-K. Park, J. D. Lee, and T.-J. King Liu, "Tunneling Field-Effect Transistors (TFETs) With Subthreshold Swing (SS) Less Than 60 mV/dec", *IEEE Electron Device Letters*, vol. 28, no. 8, pp. 743-745, Aug. 2007

- [3.9] K. Jeon, W.-Y. Loh, P. Patel, C. Y. Kang. J. Oh, A. Bowonder, C. Park, C. S. Park, C. Smith, P. Majhi, H.-H. Tseng, R. Jammy, T.-J. King Liu, and C. Hu, "Si tunnel transistors with a novel silicided source and 46mV/dec swing," *Symposium on VLSI Technology Digest*, pp. 121-122, June 2010

# Chapter 4

# Achieving sub-60mV/dec Subthreshold Swing

### 4.1 Introduction

As shown in the previous chapter, the doping profile required to achieve sub-60mV/dec subthreshold swing in a P-I-N structure is difficult to form with the conventional ion-implantation technique. Forming a highly doped junction with a sharp lateral profile is difficult to achieve due to the lateral straggle. The subsequent heat process to activate the dopants and anneal out the defect caused by the ion bombardment worsens the sharpness of this profile. This shows that a different technique needs to be used in forming the source junction profile where the tunneling is to occur.

It has been known that dopants tend to segregate during nickel silicidation forming a highly concentration region at the silicide to silicon interface [4.1]. Figure 4.1 shows the doping profiles achieved with nickel silicide. Segregation of both boron and arsenic can be seen at the silicide to silicon interface with high concentration and abrupt profile.

**Figure 4.1** (a) Arsenic and (b) boron SIMS profiles of segregated dopant profiles at NiSi/Si interface. (c) Dopant segregation process flow using nickel silicide. [4.1]

In this chapter the use of dopant segregation using nickel silicide is explored using the baseline process flow developed for the silicon P-I-N structure TFET. [4.2]

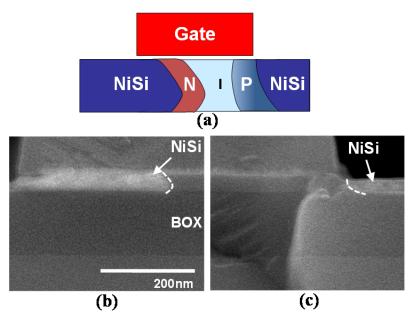

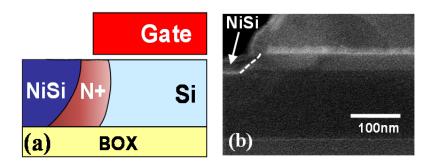

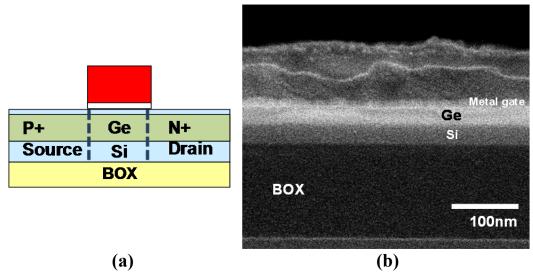

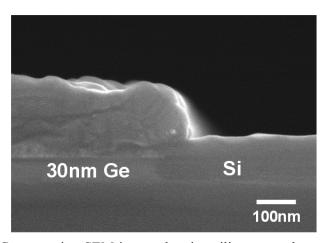

### 4.2 Silicided Source TFET Fabrication

Since the P-I-N structure TFET can be operated both as an n-type and a p-type device, it possesses an unwanted ambipolar behavior where the drain side tunneling can cause the off state current to increase. And since dopant segregation using nickel silicidation will cause both boron and arsenic to pile up enhancing tunneling in both the source and drain, a fabrication process flow where only the source side doping profile will be improved needs to be developed. We achieve this by a recess etch only in the source side, depriving the source silicidation process of silicon and causing the silicide to encroach under the gate in the source region. The drain side where all the silicon is intact will not undergo this process leaving a less abrupt drain profile. Figure 4.2 shows the process flow of the silicided source TFET using this technique. P-type devices where chosen for fabrication due to the lower diffusion coefficient and better segregation characteristic of arsenic seen in Figure 4.1.

Figure 4.2 Fabrication process flow of silicided source TFET

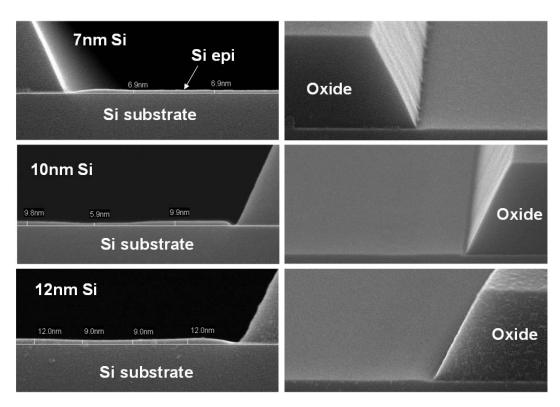

The starting wafers used were 100nm thick SOI wafers. The silicon substrate was thinned down to 40nm using thermal oxidation in order to have the dopant junction reach the buried oxide reducing the junction area and thus the leakage current. Also, this allows the nickel to fully silicide the source after recess etch. Mesa isolation was used in order to form the active regions for a simpler process. High-k gate dielectric (HfO<sub>2</sub> 30Å) is used to achieve low EOT and a midgap workfunction metal gate was used as the gate stack. The gate is patterned using a nitride hard mask. Then a thin seal nitride (~100Å) is deposited to protect the gate and gate dielectric edge during subsequent processes. The drain is formed using a photoresist half mask aligned to the center of the gate to cover the source side followed by boron ion-implantation. (BF<sub>2</sub>, 3×10<sup>15</sup> cm<sup>-2</sup>, 5keV) Then the drain side is covered and source implantation (As, 3×10<sup>15</sup> cm<sup>-2</sup>, 5keV) using a reverse mask. The source and drain dopants were annealed using spike anneal for 5 seconds at 1070°C. Then the source region was recessed using dry etch leaving about 20nm of silicon followed by a two-step nickel silicidation. A control wafer where the source region was not recess etched was also included in the split in order to comparison.

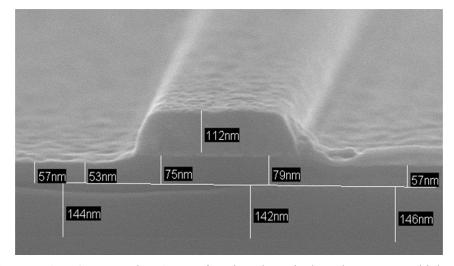

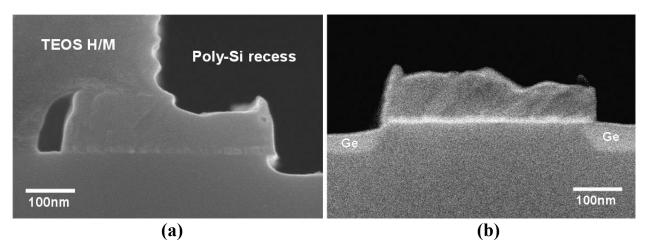

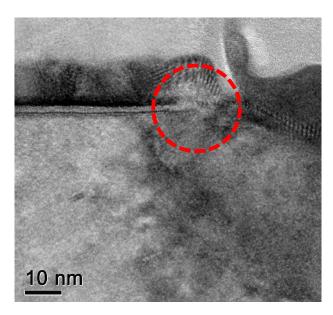

Figure 4.3 shows the cross-section diagram and cross-section SEM images of the fabricated silicided source TFET in the source and drain region. It can be seen in the figure that the substrate thickness in the source region is about half (20nm) that of the drain region due to the source-side silicon recess etch. And due to this recess etch, the silicidation reaction in the source side was deprived of silicon causing the nickel silicide to encroach into the channel under the gate pushing the dopants in. Where in the drain region which wasn't subject to recess etch, the silicide has not overlapped with the gate. The overlap of the silicide to gate in the source end was measure to be a few 100nm which caused short channel length ( $L_G < 0.25 \mu m$ ) devices to show an electrical short between the source and drain.

**Figure 4.3** (a) Silicided source TFET structure. Cross-section SEM images of silicided source TFET at (b) source (N+) region showing silicide encroachment under gate and (c) drain (P+) region without any gate-to-silicide overlap

Cross-section SEM images of the control wafer were also taken and are shown and compared with the silicided source TFET in Figure 4.4. It can be seen that without the source-side recess etch, the silicide did not encroach under the gate.

**Figure 4.4** Control P-I-N TFET (a) Structure and (b) cross-section SEM image showing no silicide to gate overlap.

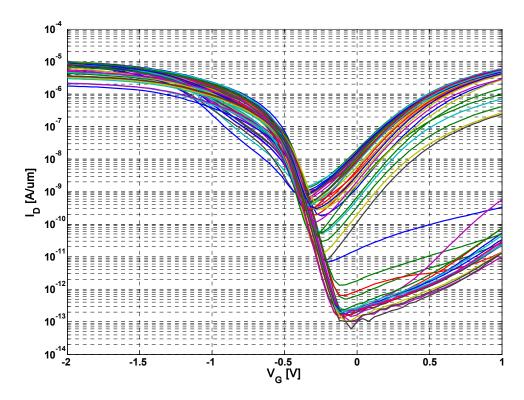

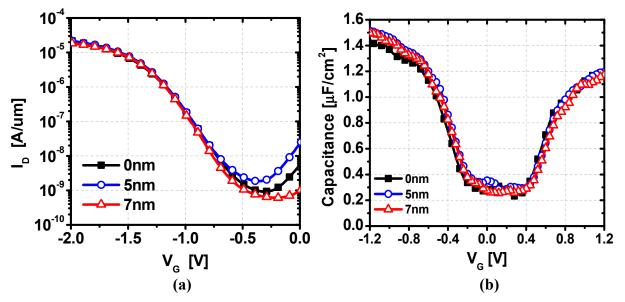

## 4.3 Analysis of the Silicided Source TFET

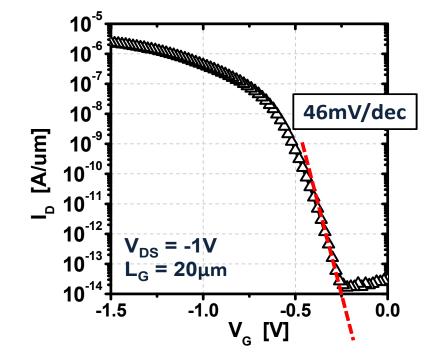

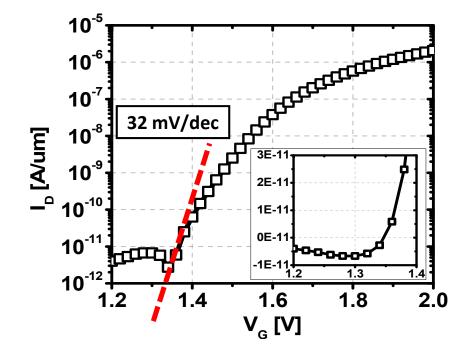

Electric characteristics of the silicided source TFET were measured and the  $I_D\text{-}V_G$  characteristics of a 20µm channel length device is shown in Figure 4.5 where the drain bias was held at -1V. As can be seen from the figure, a sub-60mV/dec subthreshold swing is observed and averages 46mV/dec over a decade of drain current at the steepest region. The subthreshold swing is not constant as expected from a TFET and gradually increases with saturation of tunneling occurring around  $0.1\mu\text{A}/\mu\text{m}$ . The leakage current of the device is measured to be very low in the  $10^{-14}\text{A}/\mu\text{m}$  range due to the long channel length and an  $I_{ON}/I_{OFF}$  ratio of  $7\times10^7$  is achieved for a 1V operation which is the highest reported for silicon TFETs. Table 4.1 compares the silicided source with reported TFET data.

Figure 4.5 Measured I<sub>D</sub>-V<sub>G</sub> of silicided source TFET (PFET)

|                                   | Ref. [4.3] | Ref.<br>[4.4] | Ref. [4.5] | This<br>Work |

|-----------------------------------|------------|---------------|------------|--------------|

| SS (mV/dec)                       | 52.8       | 42            | ~300       | 46           |

| $I_{ON}(\mu A/\mu m)$             | 12.1       | 0.01          | 1E-4       | 1.2          |

| I <sub>ON</sub> /I <sub>OFF</sub> | 1E4        | 1E4           | 1E2        | <b>7E7</b>   |

**Table 4.1** Comparison of silicided source TFET to reported silicon TFETs.  $(V_{DS}=V_{GS}-V_{BTBT}=1.0V)$

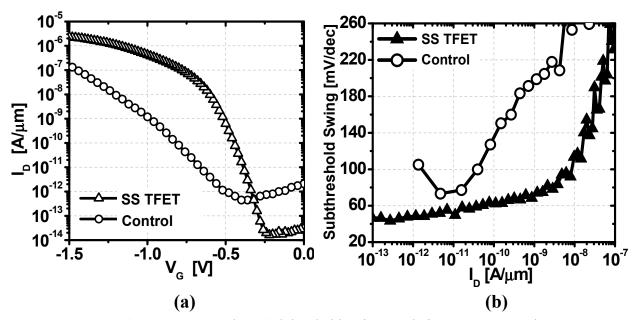

The silicided source TFET is compared to the control device processed with the P-I-N baseline flow without the source side recess etch and is given in Figure 4.6. Since the control device was not subject to dopant segregation with the nickel silicide and has a more gradual source doping profile, it shows a very slow increase in the drain current with respect to the gate bias and a lower drive current compared to the silicided source TFET. And as can be seen in the subthreshold swing versus drain current plot, not only does the control device not show a subthreshold swing that is lower than 60mV/dec but the swing value increases much faster than the silicided source TFET with respect to the drain current. In the silicided source TFET we can see that the sub-60mV/dec swing region extends over almost 3 decades of current and shows a very gradual increase. This shows that the silicide source TFET has a good control of band-to-band tunneling by the gate.

**Figure 4.6 (a)**  $I_D$ - $V_G$  and **(b)** Subthreshold swing vs. drain current comparison between the silicided source (SS) TFET and control TFET

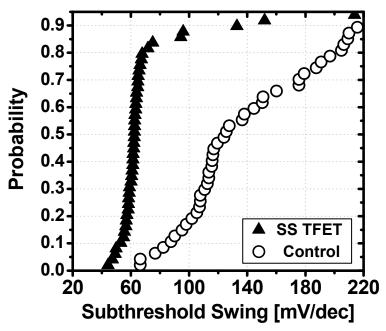

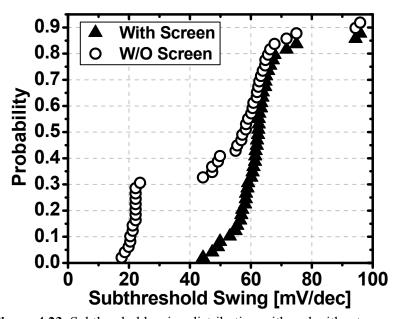

Statistical distribution of the minimum subthreshold swing of the silicided source TFET were also analyzed and is shown in Figure 4.7. The silicided source TFET shows more than 30% to have a sub-60mV/dec subthreshold swing whereas the control wafer does not show any. The variation in the subthreshold swing for the silicide source TFET is thought to be caused by the variation in the silicide edge roughness, shape and segregated dopant profile. But in comparison to the control TFET, the silicided source TFET shows a tighter distribution in the subthreshold swing indicating a better process control can be achieved with the dopant segregation compared to implant and anneal alone. The silicided source TFET was successfully reproduced in a different lot within a two month time frame achieving 47mV/dec subthreshold swing with similar distribution shown in Figure 4.7.

**Figure 4.7** Subthreshold swing distribution comparison between silicide source TFET and control TFET

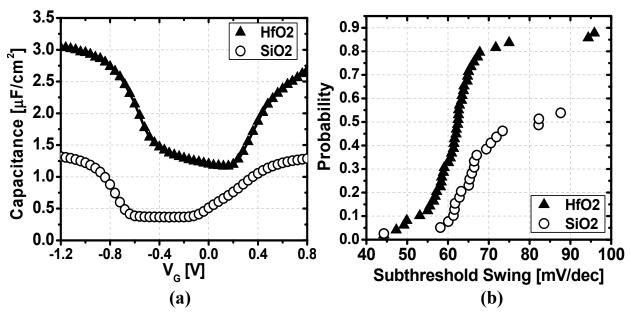

The silicided source TFET was also fabricated using in-situ steam generation (ISSG) SiO<sub>2</sub> as the gate dielectric in place of HfO<sub>2</sub>. Figure 4.8 shows the C-V measurement and statistical distribution of the subthreshold swing for both gate dielectrics. This shows the thinner equivalent oxide thickness (EOT) of the high-k dielectric with better gate control results in improved subthreshold swing.

**Figure 4.8 (a)** C-V and **(b)** Subthreshold swing distribution comparison between  $HfO_2$  and  $SiO_2$  gate dielectric

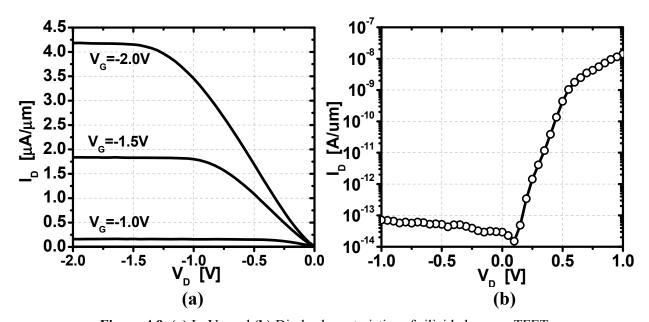

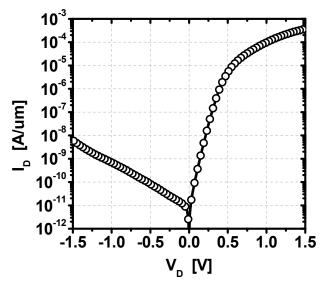

I<sub>D</sub>-V<sub>D</sub> characteristics of the silicided source TFET is shown in Figure 4.9 (a). We see that the drain current exhibits a nonlinear relation to the drain bias at low voltages. This is expected from a P-I-N structure TFET since the drain field has some control of the tunneling behavior at low voltages which has an exponential characteristic. I-V measurements with just biasing the source and drain of the device shows a rectifying behavior (Figure 4.9 (b)) confirm the formation of a diode between the source and drain. This shows that the device cannot be a MOSFET.

**Figure 4.9** (a) I<sub>D</sub>-V<sub>D</sub> and (b) Diode characteristics of silicided source TFET.

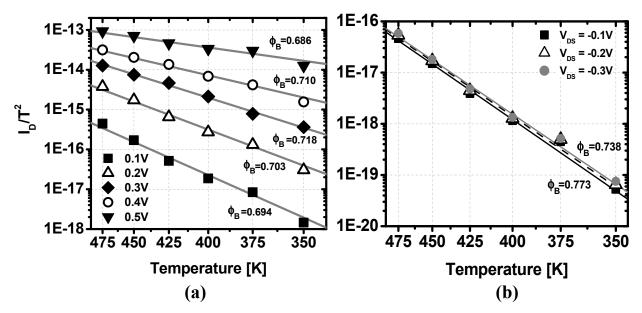

Although a distinct difference in the characteristics between the silicided source TFET and control TFET can be seen, we need to confirm the existence of segregated arsenic dopants at the silicide to silicon channel interface and that the nickel silicide did not pass the dopant front. In order to do this temperature dependence measurements of the inherent diode in the silicided source TFET were conducted and the barrier height for holes and electrons to the nickel silicide were calculated. The Schottky diode equation which is written as

$$I = AA^{**}T^{2}exp\left(-\frac{q\phi_{B}}{kT}\right)\left[exp\left(\frac{qV}{kT}\right) - 1\right]$$

(4.1)

where A is the area of the diode,  $A^{**}$  the effective Richardson constant and  $\phi_B$  the barrier height, can be manipulated to the following equations 4.2 and 4.3 for forward and reverse bias respectively [4.6].

$$ln\left(\frac{I_F}{T^2}\right) = \ln(AA^{**}) - \frac{q(\phi_B - V)}{kT}$$

(4.2)

$$ln\left(-\frac{I_R}{T^2}\right) = \ln(AA^{**}) - \frac{q\phi_B}{kT}$$

(4.3)

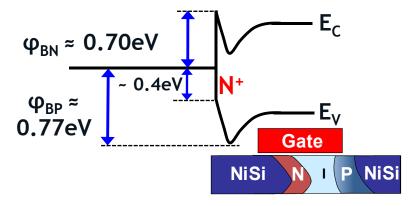

By plotting  $ln(I/T^2)$  against 1/T and finding the slop we can calculate the barrier height for electrons and holes. Figure 4.10 (a) and (b) shows the measurement results for the forward bias and reverse bias respectively. As can be seen in Figure 4.10 (a), the electron barrier height was measured to be relatively constant at  $\sim 0.7 \text{eV}$  for a forward bias range of 0.1V to 0.5V which agrees with known values for NiSi. However, in the reverse bias case, the hole barrier height was extracted to be 0.77 eV for a low reverse bias of -0.1V which is higher than the reported value of  $\sim 0.4 \text{eV}$  for NiSi. [4.7] The hole barrier height is also found to decrease with larger reverse bias. This indicates the presence of an n-type dopant layer at the silicide interface as illustrated in Figure 4.11.

**Figure 4.10** Temperature dependent diode measurement (a) Forward bias and (b) Reverse bias measurement with calculated electron and hole barrier height respectively.

**Figure 4.11** Energy band diagram of silicided source TFET at silicide to source interface showing band bending due to pile up of N-type dopants.

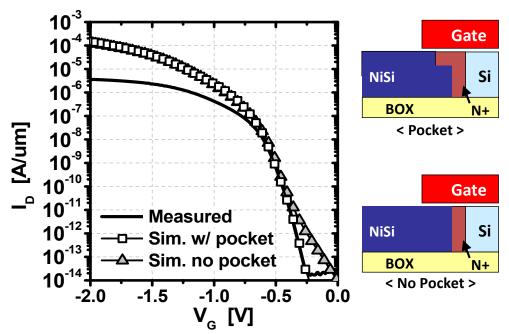

In addition to the sharp profile caused by dopant segregation, the wedge shape formed between the silicide and the gate dielectric plays a critical role in this device. It confines the band-bending to the thin wedge-shaped pocket region, thus creating a high electric field especially in the thin corner of the wedge. It also changes the direction of tunneling to be more vertical than lateral which gives the gate a better control of the turn-on. This is confirmed through MEDICI simulations [4.8]. As can be seen in Figure 4.12, simulation results for the silicide geometry that creates a thin doped pocket region shows steep turn-on matching the measured transfer characteristics, whereas simulation results for a vertical silicide interface (without the pocket) do not show sub-60mV/dec subthreshold swing. This shows that field concentration in the highly doped wedge pocket is critical in the performance of this device. The deviation between simulated and measured results seen for high current levels can be explained quantitatively by the high series resistance in the experimental device caused by the thinness of the nickel silicide (20nm) at the source. Lower series resistance and more controllable pocket geometry should improve the drive current of the device to hundreds of μA/μm [4.9].

**Figure 4.12** MEDICI simulation results showing the effect of the wedge shaped silicide pocket. Simulation results of structure with the pocket matches the measured current characteristics of the silicide source TFET

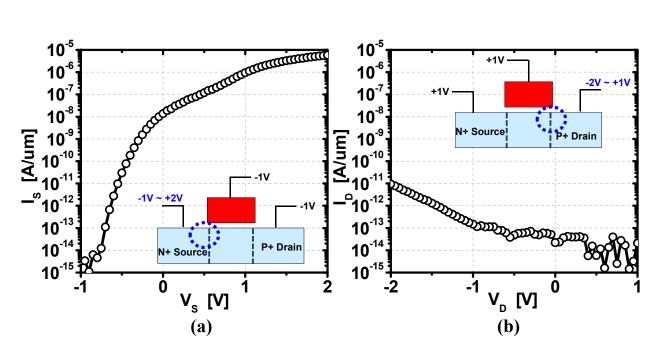

The effect of the wedge shape is also confirmed by measuring the gate induced tunneling currents in the source and drain separately using gate induced drain and source leakage (GIDL, GISL) measurement configurations. As can be seen in Figure 4.13, GISL current shows a sharp turn on due to the wedge shape of the silicide confining the gate electric field to a thin region at the surface. This allows for a more efficient band-to-band tunneling to occur. On the other hand, the drain side where the boron profile is more gradual and does not have the wedge shape silicide pocket, the gate field is spread out deeper into the substrate and less tunneling occurs due to the increased barrier thickness. This is displayed in the GIDL curve. The current shows a very gradual increase with the current level not reaching as high as GISL.

**Figure 4.13** Measured results and configuration for **(a)** GISL and **(b)** GIDL showing higher GISL current with sharper turn-on.

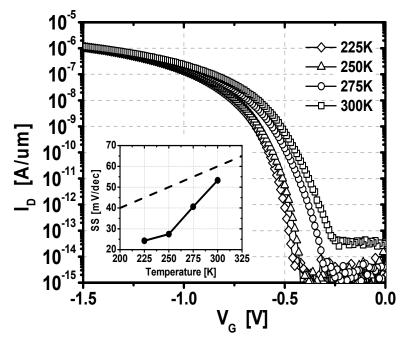

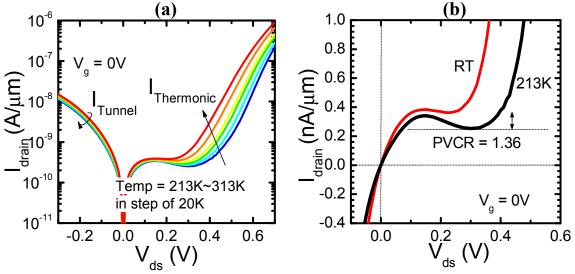

Temperature dependent  $I_D$ - $V_G$  measurements were carried out for the silicided source TFET to observe the change in the subthreshold swing with respect to temperature and are shown in Figure 4.14.

**Figure 4.14** Measured  $I_D$ - $V_G$  of silicided source TFET at various temperatures from 225K to 300K. Inset shows the measured subthreshold swing plotted against temperature.

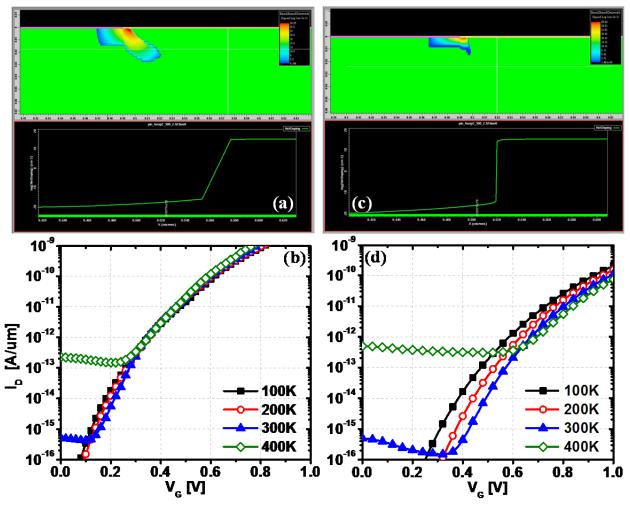

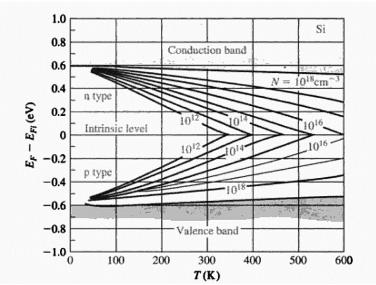

The general belief is that band-to-band tunneling devices will not show any dependence of the current on temperature. But this is not true since the band-to-band tunneling involves tunneling between filled states in the valence band and empty states in the conduction band and the filling of these states will behave differently with respect to changes in temperature. The Fermi level which also has a temperature dependence will also contribute to the dependence of the tunneling current as well. For example, depending on the doping level and the profile of the source, the band-to-band tunneling can occur in different regions in the source. Figure 4.15 shows MEDICI device simulation results of two cases where differences in doping profiles of the source causing different temperature dependence of the tunneling characteristics. Figure 4.15 (a) and (b) shows that when the tunneling occurs within a very highly doped region, the tunneling current does not show any voltage shift due to changes in temperature. This is due to the fact that the Fermi level of a highly doped region has a weak temperature dependence characteristic. On the other hand, when the tunneling occurs in a relatively low doped region as shown in Figure 4.15 (c) and (d), the tunneling I-V curve shows a larger shift in turn-on voltage with respect to temperature since the Fermi level shows a larger temperature relation at lower doping concentrations. (Figure 4.16)

**Figure 4.15** Measured results and configuration for **(a)** GISL and **(b)** GIDL showing higher GISL current with sharper turn-on.

**Figure 4.16** Position of Fermi level as a function of temperature for various doping concentrations [4.6]

Also, it has been shown that tunneling devices possess a different temperature dependence characteristic compared to that of a MOSFET. The tunneling device should show a nonlinear change in the subthreshold swing with respect to temperature whereas in a MOSFET it would be linear [4.10~4.11]. And we observe this dependence in the silicide source TFET. The subthreshold swing decreases with lower temperature but in a nonlinear fashion as can be seen in the inset of Figure 4.14.

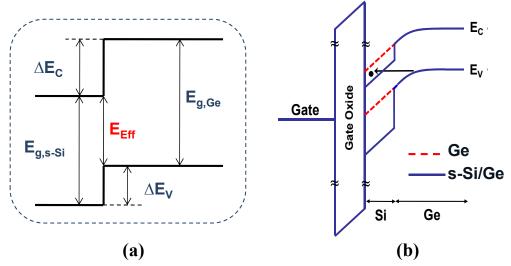

In an attempt to find the optimal thickness of the SOI and silicidation conditions which would generate the dopant segregation and the wedge shape, P-I-N silicon TFETs were fabricated on SOI wafers with two different substrate thickness and nickel silicide splits varying the deposited nickel thickness and anneal temperature. Table 4.2 gives the split table for this lot.

| Wafer # | Description                  |  |  |  |  |

|---------|------------------------------|--|--|--|--|

| 1       | 40nm SOI, 10nm Nickel (300C) |  |  |  |  |

| 2       | 40nm SOI, 15nm Nickel (300C) |  |  |  |  |

| 3       | 40nm SOI, 15nm Nickel (450C) |  |  |  |  |

| 4       | 30nm SOI, 10nm Nickel (300C) |  |  |  |  |

| 5       | 30nm SOI, 15nm Nickel (300C) |  |  |  |  |

| 6       | 30nm SOI, 15nm Nickel (450C) |  |  |  |  |

**Table 4.2** Split table for silicided source experiment varying SOI thickness, deposited nickel thickness and silicidation temperature

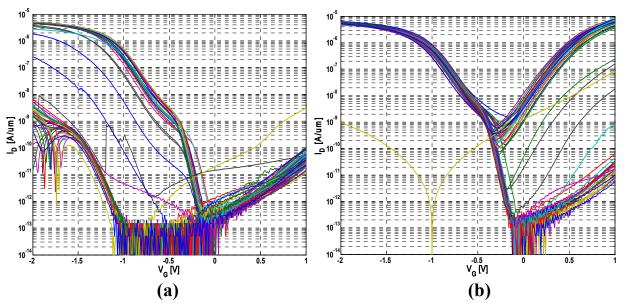

Figure 4.17 (a) and (b) shows the measured PFET  $I_D$ - $V_G$  of 20 $\mu$ m channel length devices for the wafer #03 and #04 listed in Table 4.2.

Figure 4.17 Measured  $I_D$ - $V_G$  of  $L_G$ =20 $\mu$ m TFETs (a) Wafer #03 (b) Wafer #04

As can be seen from the two figures, we can see that half of the devices in wafer #03 show conventional P-I-N silicon TFET characteristics without dopant segregation and half of the devices showing to behave more like the silicided source TFET. As for wafer #04, we can see half behaving like the silicided source TFET and the other half having ambipolar behavior. This suggests that wafer #04 with the thinner SOI thickness has more encroachment of the nickel silicide and the half that is showing the ambipolar behavior has both the arsenic and boron front to be pushed in by the silicidation process.

|       |          |       | 72.3  | 106.6 | 109.9 |       |       |      |       |      |       | х     | 62.7  | 167.0 |       |       |       |

|-------|----------|-------|-------|-------|-------|-------|-------|------|-------|------|-------|-------|-------|-------|-------|-------|-------|

|       |          | 214.6 | 59.6  | 116.3 | 89.3  | 62.9  |       |      |       |      | 56.1  | 60.3  | 59.5  | 64.4  | 59.5  |       |       |

|       | 157.9    | 103.3 | 109.6 | 107.3 | 65.8  | 118.5 | 62.2  |      |       | 58.1 | 61.8  | 61.3  | 103.3 | 97.7  | 95.4  | 66.2  |       |

| 104.0 | 113.3    | 109.2 | 105.8 | 100.7 | 61.8  | 62.0  | 110.9 | 62.0 | 121.5 | 61.2 | 61.1  | 57.5  | 61.4  | 87.6  | 133.9 | 89.2  | 62.6  |

| 110.9 | 110.5    | 87.6  | 65.5  | 60.2  | 61.3  | 61.1  | 60.3  | 62.2 | 60.1  | 60.0 | 51.2  | 60.2  | 176.8 | 138.9 | 123.2 | 107.8 | 102.0 |

| 103.2 | 109.6    | 110.3 | 55.4  | 62.8  | 61.9  | 64.8  | 61.2  | 61.3 | 59.8  | 54.2 | 58.6  | 63.1  | 155.1 | 196.7 | 136.2 | 129.3 | 90.9  |

|       | 105.3    | 105.9 | 125.1 | 62.0  | 66.4  | 62.4  | 64.8  |      |       | 60.2 | 129.0 | 162.4 | 169.0 | 111.6 | 201.2 | 198.1 |       |

|       |          | 82.4  | 93.0  | 124.4 | 134.0 | 65.3  |       |      |       |      | 103.3 | 201.3 | 194.0 | 187.5 | 205.6 |       |       |

|       |          |       | 98.0  | 103.0 | 66.5  |       |       |      |       |      |       | 209.1 | 204.2 | 202.5 |       |       |       |

|       | Wafer 03 |       |       |       |       |       |       |      |       |      |       | W     | afer  | 04    |       |       |       |

Figure 4.18 Wafer map of measured subthreshold swing

Figure 4.18 shows the wafer map of the steepest subthreshold swing of the 20µm channel length devices measure on the wafer. We can see that the lower right half of wafer #03 and upper left half of wafer #04 show a subthreshold swing value close to 60mV/dec. These devices correspond to the devices that show and I<sub>D</sub>-V<sub>G</sub> close to the silicided source TFET. A thickness variation of the SOI thickness was measured in both wafers and for wafer #03, the close to 60mV/dec subthreshold swing were measured in the area where the SOI thickness was on the thinner side and as for wafer #04, the thicker side showed this behavior with the thinner lower right half showing the ambipolar behavior. This suggests that with the silicide conditions for wafer #03, the thinner SOI gives the dopant segregation in the arsenic side where the boron dopants were not segregated with the nickel silicide. This is confirmed from MOSFET measurements on the wafer.

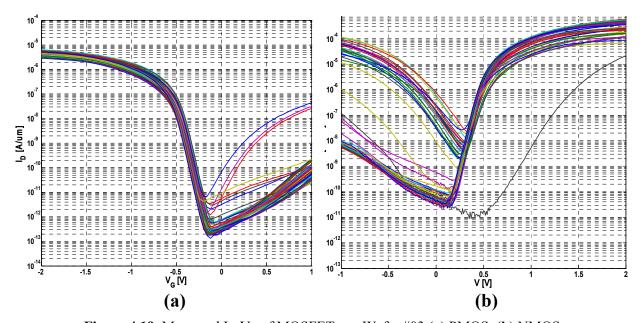

Figure 4.19 Measured I<sub>D</sub>-V<sub>G</sub> of MOSFETs on Wafer #03 (a) PMOS (b) NMOS

Figure 4.19 (a) and (b) shows the MOSFET ID-VG measurements of 0.6μm channel length NMOS devices and 10μm channel length PMOS devices. NMOS devices in the dies where the P-I-N TFET showed the dopant segregated like behavior shows and ambipolar behavior suggesting the nickel silicide has encroached close to or even passed the arsenic dopant front. As for the boron side, PMOS measurements show that most of the devices do not show this large ambipolar behavior which shows the boron dopant front is well beyond the silicide to silicon interface. On the other hand PMOS measurements of wafer #04 shown in Figure 4.20 shows to have a large portion of the devices showing ambipolar behavior and these dies correspond to the dies where the P-I-N TFET were measured to have the ambipolar behavior. This shows that the lower right region of the wafer with the thinner SOI thickness is sufficient to allow dopant segregation for both arsenic and boron for the silicide conditions of wafer #04.

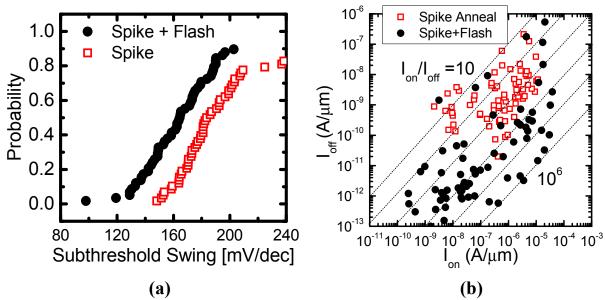

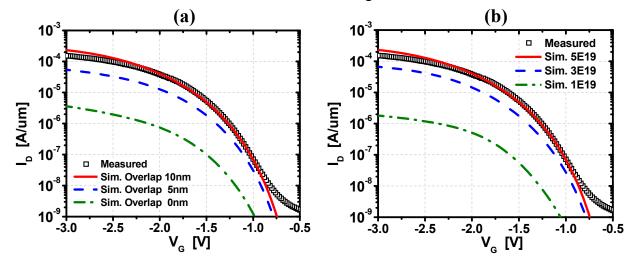

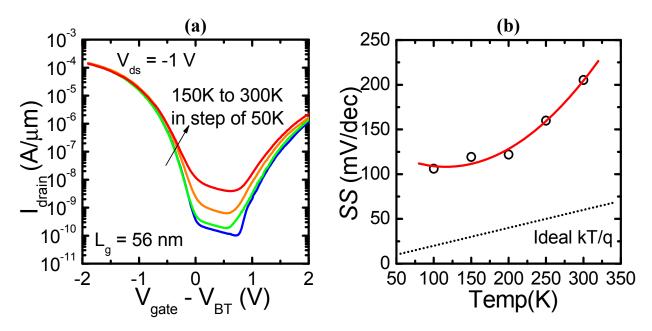

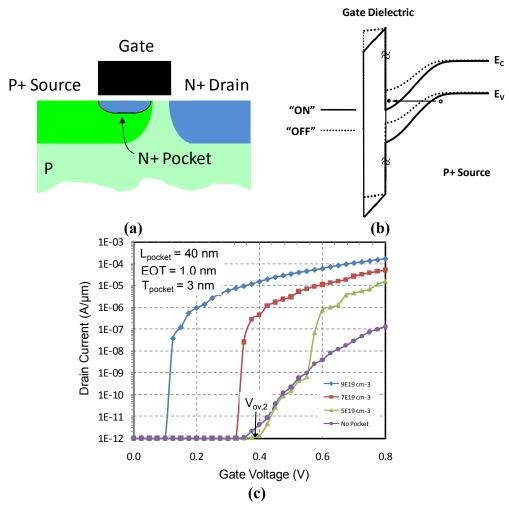

Figure 4.20 Measured I<sub>D</sub>-V<sub>G</sub> of PMOSFETs on Wafer #04